#### TISP4015H1BJ, TISP4025H1BJ, TISP4030H1BJ, TISP4040H1BJ

# VERY LOW VOLTAGE BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

## TISP40xxH1BJ VLV Overvoltage Protector Series

#### **Low Capacitance**

| 4015 | 78 pF |

|------|-------|

| 4030 | •     |

| 4040 |       |

#### **Digital Line Signal Level Protection**

- -ISDN

- -xDSL

#### Safety Extra Low Voltage, SELV, values

| Device | V <sub>DRM</sub><br>V | V <sub>(BO)</sub><br>V |

|--------|-----------------------|------------------------|

| '4015  | ± 8                   | ± 15                   |

| '4025  | ± 13                  | ± 25                   |

| '4030  | ± 15                  | ± 30                   |

| '4040  | ± 25                  | ± 40                   |

100 A "H" Series specified for: ITU-T recommendations K.20, K.45, K.21 FCC Part 68 and GR-1089-CORE

| Wave Shape Standard |                  | I <sub>TSP</sub> |

|---------------------|------------------|------------------|

| wave Snape          | Staridard        | Α                |

| 2/10 μs             | GR-1089-CORE     | 500              |

| 8/20 μs             | IEC 61000-4-5    | 400              |

| 10/160 μs           | FCC Part 68      | 200              |

| 10/700 µs           | ITU-T K.20/45/21 | 150              |

| 10/700 μS           | FCC Part 68      | 130              |

| 10/560 μs           | FCC Part 68      | 125              |

| 10/1000 μs          | GR-1089-CORE     | 100              |

# SMBJ Package (Top View) R(B) 1 2 T(A)

Terminals T and R correspond to the alternative line designators of A and B

#### Description

These devices are designed to limit overvoltages on digital telecommunication lines. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line. A single device provides 2-point protection and is typically used for the protection of transformer windings and low voltage electronics.

The protector consists of a symmetrical voltage-triggered bidirectional thyristor. Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on-state condition. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. The device switches off when the diverted current falls below the holding current value.

#### **How to Order**

| Device       | Package        | Carrier              | Order As         | Marking Code | Std. Qty. |

|--------------|----------------|----------------------|------------------|--------------|-----------|

| TISP40xxH1BJ | SMB (DO-214AA) | Embossed Tape Reeled | TISP 40xxH1BJR-S | 40xxH1       | 3000      |

Insert xx value corresponding to protection voltages of 15 V, 30 V and 40 V.

AUGUST 1999 - REVISED OCTOBER 2015

Specifications are subject to change without notice.

The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time. Users should verify actual device performance in their specific applications.

<sup>\*</sup>RoHS Directive 2002/95/EC Jan. 27, 2003 including annex and RoHS Recast 2011/65/EU June 8, 2011.

<sup>\*\*</sup> TISP4025H1BJ UL Recognition pending.

#### Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  | Symbol           | Value                                                       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------------------------------------------------|------|

| Repetitive peak off-state voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '4015<br>'4025<br>'4030<br>'4040 | V <sub>DRM</sub> | ± 8<br>± 13<br>± 15<br>± 25                                 | V    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)  2/10 µs (Telcordia GR-1089-CORE, 2/10 µs voltage wave shape)  8/20 µs (IEC 61000-4-5, combination wave generator, 1.2/50 voltage,  10/160 µs (FCC Part 68, 10/160 µs voltage wave shape)  5/310 µs (ITU-T K.20/45/21, 10/700 µs voltage wave shape)  5/320 µs (FCC Part 68, 9/720 µs voltage wave shape)  10/560 µs (FCC Part 68, 10/560 µs voltage wave shape)  10/1000 µs (Telcordia GR-1089-CORE, 10/1000 µs voltage wave shape) |                                  | ITSP             | ± 500<br>± 400<br>± 200<br>± 150<br>± 150<br>± 125<br>± 100 | А    |

| Non-repetitive peak on-state current (see Notes 1 and 2) 20 ms (50 Hz) full sine wave 16.7 ms (60 Hz) full sine wave 0.2 s 50 Hz/60 Hz a.c. 2 s 50 Hz/60 Hz a.c. 1000 s 50 Hz/60 Hz a.c.                                                                                                                                                                                                                                                                                                            |                                  | I <sub>TSM</sub> | 45<br>50<br>21<br>7<br>2                                    | А    |

| Initial rate of rise of current (2/10 waveshape)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  | di/dt            | 450                                                         | A/µs |

| Junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  | TJ               | -40 to +150                                                 | ° C  |

| Storage temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  | T <sub>stg</sub> | -65 to +150                                                 | ° C  |

NOTES: 1. Initially the device must be in thermal equilibrium with  $T_J$  = 25 °C.

#### Electrical Characteristics, $T_A = 25$ °C (Unless Otherwise Noted)

|                   | Parameter                             | Test Conditions                                                                                                                                                               | Min | Тур | Max                          | Unit |

|-------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------|------|

| I <sub>DRM</sub>  | Repetitive peak off-<br>state current | $V_D = V_{DRM}$                                                                                                                                                               |     |     | ± 5                          | μΑ   |

| V <sub>(BO)</sub> | Breakover voltage                     | di/dt = 0.8 A/ms                                                                                                                                                              |     |     | ± 15<br>± 25<br>± 30<br>± 40 | ٧    |

| V <sub>(BO)</sub> | Impulse breakover voltage             | dv/dt $\leq$ ±1000 V/ $\mu$ s, Linear voltage ramp,  Maximum ramp value = ±500 V  di/dt = ±12 A/ $\mu$ s, Linear current ramp,  Maximum ramp value = ±10 A  4015  4025 / 4030 |     |     | ± 33<br>± 57<br>± 74         | V    |

| I <sub>(BO)</sub> | Breakover current                     | di/dt = ±0.8 A/ms                                                                                                                                                             |     |     | ± 0.8                        | Α    |

| V <sub>T</sub>    | On-state voltage                      | $I_T = \pm 5 \text{ A}, t_W = 100 \ \mu\text{s}$                                                                                                                              |     |     | ±3                           | V    |

| I <sub>D</sub>    | Off-state current                     | $V_D = \pm 6 \text{ V}$ '4015<br>$V_D = \pm 11 \text{ V}$ '4025<br>$V_D = \pm 13 \text{ V}$ '4030<br>$V_D = \pm 22 \text{ V}$ '4040                                           |     |     | ±2                           | μΑ   |

| I <sub>H</sub>    | Holding current                       | $I_T = \pm 5 \text{ A, di/dt} = \pm 30 \text{ mA/ms}$                                                                                                                         | ±50 |     |                              | m A  |

<sup>2.</sup> The surge may be repeated after the device returns to its initial conditions.

## **BOURNS**®

#### Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|      | Parameter             | Test Conditions                                               |         | Min | Тур | Max | Unit |

|------|-----------------------|---------------------------------------------------------------|---------|-----|-----|-----|------|

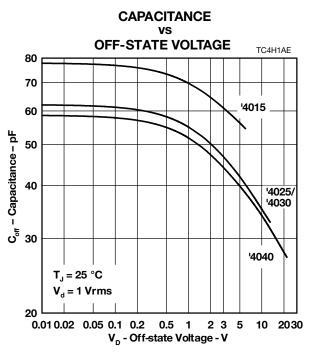

|      |                       | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = 0$           | '4015   |     | 78  | 100 |      |

|      |                       | '4025                                                         | / '4030 |     | 62  | 81  |      |

|      |                       |                                                               | '4040   |     | 59  | 77  |      |

|      |                       | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = 1 \text{ V}$ | '4015   |     | 70  | 90  |      |

| Coff | Off-state capacitance | '4025                                                         | / '4030 |     | 55  | 72  | pF   |

|      |                       |                                                               | '4040   |     | 52  | 68  |      |

|      |                       | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = 2 \text{ V}$ | '4015   |     | 65  | 85  |      |

|      |                       | '4025                                                         | / '4030 |     | 50  | 65  |      |

|      |                       |                                                               | '4040   |     | 47  | 61  |      |

#### **Thermal Characteristics**

|                                                           | Parameter                                                             | Test Conditions                                                                                                       | Min | Тур | Max  | Unit                 |

|-----------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|------|----------------------|

| R <sub>0.IA</sub> Junction to free air thermal resistance | EIA/JESD51-3 PCB, $I_T = I_{TSM(1000)}$ , $T_A = 25$ °C, (see Note 3) |                                                                                                                       |     | 115 | °C/W |                      |

| $R_{\theta JA}$                                           | ouncide to not an infinial resistance                                 | 265 mm x 210 mm populated line card,<br>4-layer PCB, I <sub>T</sub> = I <sub>TSM(1000)</sub> , T <sub>A</sub> = 25 °C |     | 52  |      | <i>5/</i> <b>V V</b> |

NOTE 3: EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5 A rated printed wiring track widths.

#### **Parameter Measurement Information**

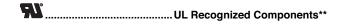

Figure 1. Voltage-Current Characteristic for T and R Terminals All Measurements are Referenced to the R Terminal

#### **Typical Characteristics**

Figure 2.

#### **Rating and Thermal Information**

#### **NON-REPETITIVE PEAK ON-STATE CURRENT**

#### **CURRENT DURATION** TI4MAJ 60 I<sub>SM(t)</sub> - Non-Repetitive Peak On-State Current - A 50 V<sub>GEN</sub> = 600 Vrms, 50/60 Hz 40 $R_{GEN} = 1.4*V_{GEN}/I_{TSM(t)}$ **EIA/JESD51-2 ENVIRONMENT** 30 EIA/JESD51-3 PCB $T_A = 25 \,^{\circ}C$ 20 15 10 8 7 6 5 4 3 0.01 0.1 10 100 1000 t-Current Duration-s

Figure 3.

#### **APPLICATIONS INFORMATION**

#### **Transformer Protection**

The inductance of a transformer winding reduces considerably when the magnetic core material saturates. Saturation occurs when the magnetizing current through the winding inductance exceeds a certain value. It should be noted that this is a different current to the transformed current component from primary to secondary. The standard inductance-current relationship is:

$$E = -\left(L\frac{di}{dt}\right)$$

where:

L = unsaturated inductance value in H

di = current change in A

dt = time period in s for current change di

E = winding voltage in V

Rearranging this equation and working large  $\Delta$  changes to saturation gives the useful circuit relationship of:

$$E x \Delta t = L x \Delta i$$

A transformer winding volt-second value for saturation gives the designer an idea of circuit operation under overvoltage conditions. The volt-second value is not normally quoted, but most manufacturers should provide it on request. A 50 V $\mu$ s winding will support rectangular voltage pulses of 50 V for 1  $\mu$ s, 25 V for 2  $\mu$ s, 1 V for 50  $\mu$ s and so on. Once the transformer saturates, primary to secondary coupling will be lost and the winding resistance, RW, shunts the overvoltage protector, Th1 - see Figure 4. This saturated condition is a concern for long duration impulses and a.c. fault conditions because the current capability of the winding wire may be exceeded. For example, if the on-state voltage of the protector is 1 V and the winding resistance is 0.2  $\Omega$ , the winding would bypass a current of 1/0.2 = 5 A, even through the protector was in the low voltage condition.

Figure 4. Transformer Saturation

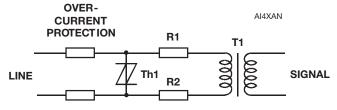

Figure 5 shows a generic protection arrangement. Resistors R1 and R2, together with the overcurrent protection, prevent excessive winding current flow under a.c. conditions. Normally these resistors would only be needed for special cases, e.g. some T1/E1 designs. Alternatively, a split winding could be used with a single resistor connecting the windings. This resistor could be by-passed by a small capacitor to reduce signal attenuation.

Figure 5. Transformer Winding Protection

Overcurrent protection upstream from the overvoltage protector can be fuse, PTC or thick film resistor based. For very high frequency circuits, fuse inductance due to spiral wound elements may need to be evaluated.

#### TISP® Device Voltage Selection

Normally, the working voltage value of the protector,  $V_{DRM}$ , would be chosen to be just greater than the peak signal amplitude over the equipment temperature range. This would give the lowest possible protection voltage,  $V_{(BO)}$ . This would minimize the peak voltage applied to the transformer winding and increase the time to core saturation.

In high frequency circuits, there are two further considerations. Low voltage protectors have a higher capacitance than high voltage protectors.

## BOURNS

#### TISP® Device Voltage Selection (Continued)

So a higher voltage protector might be chosen specifically to reduce the protector capacitive effects on the signal.

Low energy short duration spikes will be clipped by the protector. This will extend the spike duration and the data loss time. A higher protector voltage will reduce the data loss time. Generally, this will not be a significant factor for inter-conductor protection.

However, clipping is significant for protection to ground, where there is continuous low-level a.c. common mode induction. In some cases the induced a.c. voltage can be over 10 V. Repetitive clipping at the induced a.c. peaks by the protector would cause severe data corruption. The expected a.c. voltage induced should be added to the maximum signal level for setting the protector V<sub>DRM</sub> value.

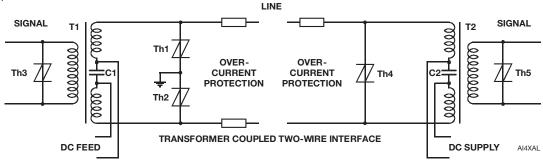

#### 2-Wire Digital Systems

Typical systems using a single twisted pair connection are: Integrated Services Digital Network (ISDN) and Pair Gain.

Signal level protection at the transformer winding is given by protectors Th3 and Th5. Typically these could be TISP4015H1 type devices with a 15 V voltage protection level.

Figure 6. 2-Wire System

Two line protection circuits are given; one referenced to ground using Th1 and Th2 (left) and the other inter-wire using protector Th4 (right) - see Figure 6. For ISDN circuits compliant to ETSI ETR 080:1993, ranges 1 and 2 can be protected by the following device types: TISP4095M3, TISP4095H3, TISP3095H3 (combines Th1 and Th2) and TISP7095H3 (combines Th1, Th2 and Th4). Ranges 4 through 5 can be protected by: TISP4145M3, TISP4145H3, TISP3145H3 (combines Th1 and Th2) and TISP7145H3 (combines Th1, Th2 and Th4). Device surge requirement, H or M, will be set by the overcurrent protection components and the standards complied with. Protection of just the d.c. feed to ETSI ranges is covered in the TISP5xxxH3 data sheet.

When loop test voltages exceed the normal d.c. feed levels, higher voltage protectors need to be selected. For two terminal protectors, for levels up to 190 V (135 V rms) the TISP4250, H3 or M3, can be used and for 210 V (150 V rms) the TISP4290, H3 or M3, can be used.

In Pair Gain systems, the protector V<sub>DRM</sub> is normally set by the d.c. feed value. The following series of devices have a 160 V working voltage at 25 °C: TISP4220M3, TISP4220H3, TISP3210H3 (combines Th1 and Th2) and TISP7210H3 (combines Th1, Th2 and Th4). These devices can be used on 150 V d.c. feed voltages down to an ambient temperature of -25 °C. Where the subscriber equipment may be exposed to POTS (Plain Old Telephone Service) voltage levels, protector Th4 needs a higher working voltage of about 275 V. Suitable device types are: TISP4350M3, TISP4350H3, TISP3350H3 (combines Th1 and Th2) and TISP7350H3 (combines Th1, Th2 and Th4).

The overcurrent protection for the overvoltage protector can be fuse, PTC or thick film resistor based. Its a.c. limiting capability should be less than the ratings of the intended overvoltage protector. Equipment complying with the year 2000 international K.20, K.21 and K.45 recommendations from the ITU-T, may be required to demonstrate protection coordination with the intended primary protector. Without adding series resistance, a simple series fuse overcurrent protection is likely to fail the equipment for this part of the recommendation.

If the d.c. feed consists of equal magnitude positive and negative voltage supplies, appropriately connected TISP5xxxH3 unidirectional protectors could replace Th1 and Th2.

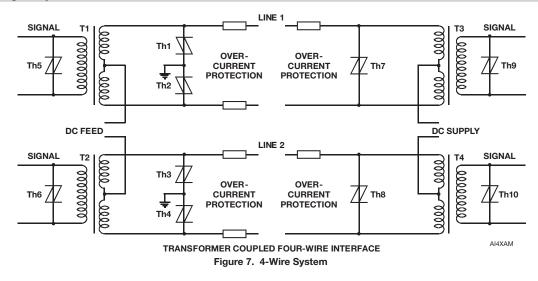

#### 4-Wire Digital Systems

A typical system using a two twisted pair connection is the High-bit-rate Digital Subscriber Line (HDSL) and the "S" interface of ISDN.

Figure 7 shows a generic two line system. HDSL tends to have ground referenced protection at both ends of the lines (Th1, Th2, Th3 and Th4). The ISDN "S" interface is often inside the premises and simple inter-wire protection is used at the terminating adaptor (Th7 and Th8). In all

Users should verify actual device performance in their specific applications.

#### 4-Wire Digital Systems

cases, signal protection, Th5, Th6, Th9 and Th10, can be TISP4015H1 type devices with a 15 V voltage protection level.

For an HDSL d.c. feed voltage of 180 V or less and operation down to an ambient of -25 °C, the following Th1, Th2, Th3 and Th4 protectors are suitable: TISP4250M3 or TISP4250H3, TISP3250H3 (combines Th1 and Th2 or Th3 and Th4) and TISP7250H3 (combines Th1, Th2 and Th7 or Th3. Th4 and Th8). Possible overcurrent protection components are covered in the 2-wire digital systems clause.

For ISDN interfaces powered with ±40 V (ETSI, ETS 300 012 1992) the following Th1, Th2, Th3 and Th4 protectors are suitable: TISP4070M3 or TISP4070H3 or TISP4070L3, TISP3070F3 or TISP3070H3 (combines Th1 and Th2 or Th3 and Th4) and TISP7070F3 or TISP7070H3 (combines Th1, Th2 and Th7 or Th3, Th4 and Th8). At the terminating adaptor, the Th7 and Th8 protectors do not "see" the d.c. feed voltage and should be selected to not clip the maximum signal level. Generally, the TISP40xxH1 series will be suitable.

Internal ISDN lines are not exposed to high stress levels and the chances of a.c. power intrusion are low (ETSI EN 300 386-2 1997). Accordingly, the equipment port protection needs are at a lower level than ports connected to outside lines.

#### **Home Phone Networking**

Using the existing house telephone wiring, home phone networking systems place the local network traffic in a high band above the POTS and ADSL (Asymmetrical Digital Subscriber Line) spectrum. Local network rates are 1 Mbps or more. To reject noise and harmonics, an in-line protection and 5 MHz to 10 MHz bandpass filter module is used for the equipment. These modules are available from magnetic component manufacturers (e.g. Bel Fuse Inc.) A typical circuit for the telephone line magnetics module is shown in Figure 8. Transformer T1 isolates the equipment from the house wiring. The isolated winding output is voltage limited by a very low-voltage protector, Th1. With a differential voltage of about 12 V peak to peak, the TISP4015H1 could be used for Th1. After filtering, connection is made to the differential transceiver of the processing IC.

Figure 8. Home Phone Networking Isolation/filter/protection Circuit

AUGUST 1999 - REVISED OCTOBER 2015

Specifications are subject to change without notice.

The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time. Users should verify actual device performance in their specific applications.

<sup>&</sup>quot;TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in the U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.

### **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

## Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru 4 moschip.ru 9