### **General Description**

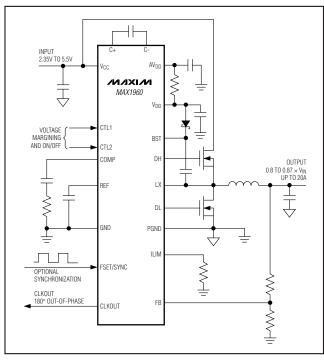

The MAX1960/MAX1961/MAX1962 high-current, high-efficiency voltage-mode step-down DC-DC controllers operate from a 2.35V to 5.5V input and generate output voltages down to 0.8V at up to 20A. An on-chip charge pump generates a regulated 5V for MOSFET drive. Additionally, adaptive dead-time drivers allow a wide variety of MOSFETs to be used without risking shoot-through.

Fixed-frequency PWM operation and external synchronization make these controllers suitable for telecom and datacom applications. The operating frequency is programmable to either 500kHz or 1MHz, or from 450kHz to 1.2MHz with an external clock. A clock output is provided to synchronize another converter for 180° out-of-phase operation. A high closed-loop bandwidth provides excellent transient response for applications with dynamic loads.

Lossless current sensing in the MAX1960 and MAX1961 is achieved by monitoring the drain-to-source voltage of the low-side external FET. The current limit is scalable to accommodate a wide variety of MOSFETs and load currents. The MAX1962 has 10% accurate sense-resistor-based current limiting.

The MAX1960 and MAX1962 have an adjustable output voltage from 0.8V to 4.95V. The MAX1961 and MAX1962 have four preset output voltages (1.5V, 1.8V, 2.5V, and 3.3V) and feature 0.5% voltage accuracy over temperature, line, and load variations. The MAX1960 and MAX1961 also feature voltage-margining control inputs that shift the output voltage up or down by 4% for system testing.

### Applications

ASIC, FPGA, DSP, and CPU Core and I/O Voltages Cellular Base Stations Telecom and Network Equipment Server and Storage Systems

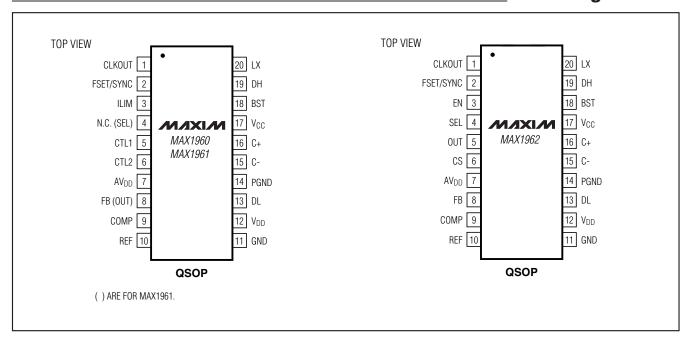

Pin Configurations and Selector Guide appear at the end of the data sheet.

#### \_\_\_\_Features

- ♦ 0.5% Accurate Output

- ♦ Operates from 2.35V to 5.5V Supply

- ♦ Generates Low Output Voltage Down to 0.8V

- ♦ On-Chip Charge Pump Provides 5V Gate Drive

- **♦** Ceramic or Electrolytic Capacitors

- ♦ 94% Efficiency

- ♦ External Synchronization from 450kHz to 1.2MHz

- ♦ 500kHz/1MHz Fixed-Frequency PWM Operation

- **♦ Fast Transient Response**

- ♦ Two Converters Can Operate 180° Out-of-Phase

- ♦ ±4% Voltage Margining for System Test

- **♦ 10% Accurate Current Sensing (MAX1962)**

- ♦ Adaptive Dead Time Prevents Shoot-Through

### Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |  |  |  |  |

|------------|----------------|-------------|--|--|--|--|

| MAX1960EEP | -40°C to +85°C | 20 QSOP     |  |  |  |  |

| MAX1961EEP | -40°C to +85°C | 20 QSOP     |  |  |  |  |

| MAX1962EEP | -40°C to +85°C | 20 QSOP     |  |  |  |  |

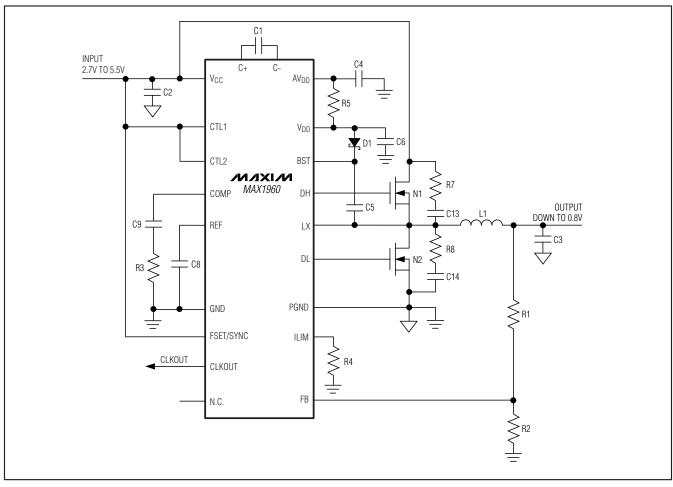

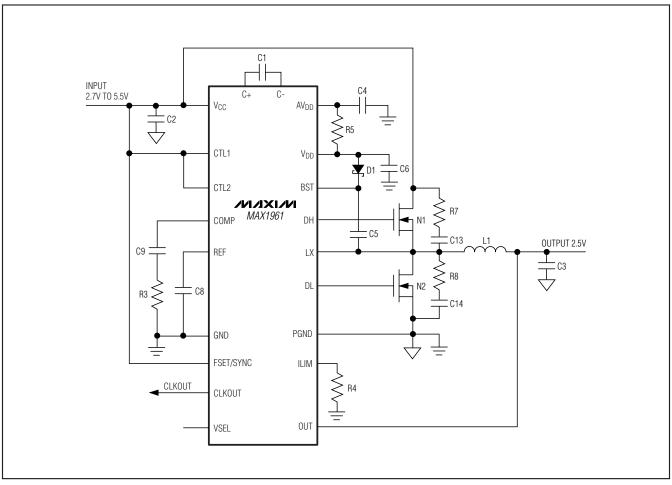

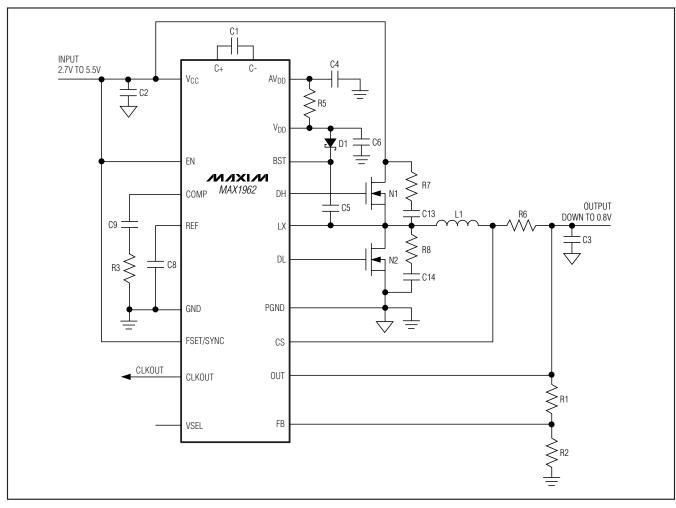

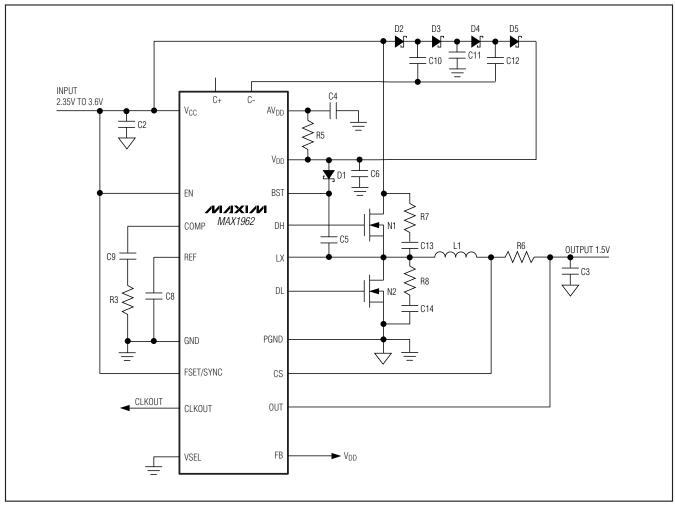

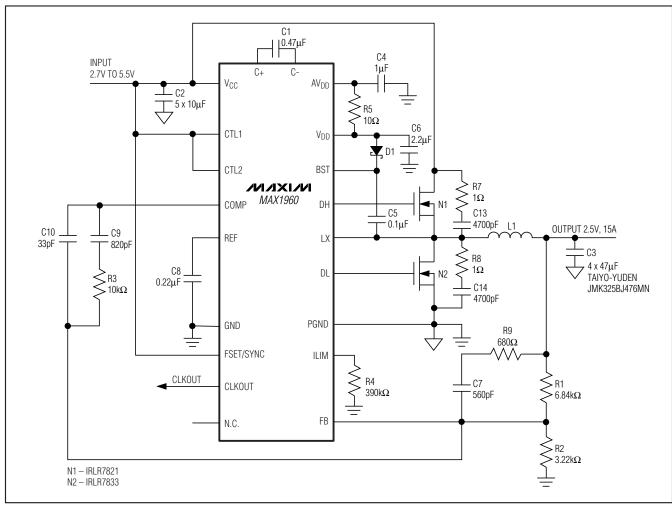

### **Typical Operating Circuit**

**Maxim Integrated Products**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , CTL_, CS, FSET/SYNC, SEL, EN, OUT to GND0.3V to +6V ILIM, COMP, REF, FB, CLKOUT, C- to GND0.3V to V <sub>AVDD</sub> + 0.3V C+ to GND0.3V to higher of V <sub>VCC</sub> + 1V or V <sub>VDD</sub> + 0.3V V <sub>DD</sub> , AV <sub>DD</sub> to GND0.3V to higher of V <sub>VCC</sub> - 0.3V or 6V DL to PGND0.3V to V <sub>VDD</sub> + 0.3V BST to GND0.3V to +12V DH to LX0.3V to +2V | Continuous Power Dissipation ( $T_A = +70^{\circ}\text{C}$ ) 20-Pin QSOP (derate up to $+70^{\circ}\text{C}$ ) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| LX to BST6V to +0.3V                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| PGND to GND, or Vpp to AVpp0.3V to +0.3V                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{VCC} = 3.3V, Circuits of Figures 9-12, T_A = 0^{\circ}C to +85^{\circ}C. Typical values are at T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                           | CONI                                                   | DITIONS                                    | MIN   | TYP   | MAX   | UNITS  |

|-------------------------------------|--------------------------------------------------------|--------------------------------------------|-------|-------|-------|--------|

| V <sub>CC</sub> Input Voltage Range |                                                        |                                            | 2.35  |       | 5.5   | V      |

| V <sub>CC</sub> Input Voltage UVLO  | Rising or falling, hyster                              | Rising or falling, hysteresis = 33mV (typ) |       |       |       | V      |

| V <sub>DD</sub> Input Voltage UVLO  | Rising or falling, hyster                              | Rising or falling, hysteresis = 44mV (typ) |       |       |       | V      |

| Output Voltage                      |                                                        |                                            | 0.8   |       |       | V      |

|                                     | MAX1960/MAX1962 (n                                     | neasured at FB)                            | 0.796 | 0.800 | 0.804 |        |

|                                     |                                                        | SEL = GND                                  | 1.492 | 1.500 | 1.508 |        |

| DC Output Accuracy                  | MAX1961/                                               | SEL = REF                                  | 1.791 | 1.800 | 1.809 | V      |

|                                     | MAX1962 (FB = V <sub>DD</sub> ),<br>measured at output | SEL not connected                          | 2.487 | 2.500 | 2.514 | ]      |

|                                     | mododrod di odiput                                     | SEL = V <sub>DD</sub>                      | 3.272 | 3.300 | 3.336 | 1      |

| Positive Voltage-Margining Shift    | MAX1960/MAX1961                                        |                                            | +3.8  | +4    | +4.2  | %      |

| Negative Voltage-Margining Shift    | MAX1960/MAX1961                                        | MAX1960/MAX1961                            |       | -4    | -4.2  | %      |

| Load Regulation Error               | 0V to full load                                        | 0V to full load                            |       | 0.08  |       | %      |

| Line Regulation Error               | V <sub>VCC</sub> = 2.7V to 5.5V                        |                                            |       | 0.1   |       | %      |

| FB Input Bias Current               |                                                        |                                            | -0.2  |       | +0.2  | μΑ     |

| Feedback Transconductance           |                                                        |                                            | 1     | 2     | 3     | mS     |

| COMP Discharge Resistance           | In shutdown                                            |                                            |       | 10    | 100   | Ω      |

| DC-DC Soft-Start Time               |                                                        |                                            |       | 1280  |       | cycles |

| 0 11 5                              | FSET/SYNC = GND                                        |                                            | 450   | 500   | 550   |        |

| Switching Frequency                 | FSET/SYNC = V <sub>CC</sub>                            | FSET/SYNC = V <sub>CC</sub>                |       |       | 1120  | kHz    |

| SYNC Frequency Range                |                                                        |                                            | 450   |       | 1200  | kHz    |

| Maximum Duty Cycle                  | f = 1MHz                                               |                                            | 80    | 83    |       | %      |

| Maximum Duty Cycle                  | f = 500kHz                                             |                                            | 90    | 92    |       | %      |

| Quiescent Supply Current            |                                                        |                                            |       | 11    | 15    | mA     |

| Shutdown Supply Current             |                                                        |                                            |       |       | 15    | μА     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VCC} = 3.3V, Circuits of Figures 9-12, T_A = 0^{\circ}C to +85^{\circ}C. Typical values are at T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                                                                 | C                                                           | MIN                                                        | TYP                     | MAX                      | UNITS |      |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|-------------------------|--------------------------|-------|------|

|                                                                                           | 2.7V ≤ V <sub>VCC</sub> ≤ 5.5V                              | 4.75                                                       |                         | 5.25                     | V     |      |

| V <sub>DD</sub> Output Voltage                                                            | $2.35V \le V_{VCC} \le 2.7$<br>= $4.7\mu$ F, C6 = $22\mu$ F | 4.45                                                       |                         | 5.25                     | V     |      |

|                                                                                           | 2.35V ≤ V <sub>VCC</sub> ≤ 3.6<br>50mA (circuit of Fig      | W with tripler, I <sub>LOAD</sub> = 1 to gure 12) (Note 1) | 4.75                    |                          | 5.25  | V    |

| Reference Voltage (No Load)                                                               |                                                             |                                                            | 1.269                   | 1.280                    | 1.291 | V    |

| Reference Load Regulation                                                                 | -50μA to +50μA                                              |                                                            |                         | 3                        |       | mV   |

| Positive Current-Limit Threshold                                                          |                                                             | $V_{OUT} = 0.8V$                                           | 44                      | 53                       | 62    | Į    |

| (VPGND - VLX)                                                                             | MAX1962                                                     | $V_{OUT} = 2.0V$                                           | 45                      | 50                       | 55    | mV   |

| (VEGIND VEX)                                                                              |                                                             | $V_{OUT} = 3.3V$                                           | 38                      | 48                       | 58    |      |

| Negative Current-Limit Threshold (VLX - VPGND)                                            | MAX1962, V <sub>OUT</sub> =                                 | 0.8V to 3.3V                                               | 38                      | 50                       | 68    | mV   |

| CS Bias Current                                                                           | MAX1962, V <sub>CS</sub> = 3                                | .3V                                                        |                         | 20                       | 50    | μΑ   |

| OUT Bias Current                                                                          | MAX1961/MAX196                                              | 2, V <sub>OUT</sub> = 3.3V                                 |                         | 30                       | 50    | μΑ   |

| Current-Limit Threshold (Positive Direction, Fixed, V <sub>PGND</sub> - V <sub>LX</sub> ) | MAX1960/MAX196                                              | 1, ILIM = V <sub>DD</sub>                                  | 58                      | 74                       | 90    | mV   |

| Current-Limit Threshold (Negative Direction, Fixed, V <sub>LX</sub> - V <sub>PGND</sub> ) | MAX1960/MAX196                                              | 50                                                         | 67                      | 85                       | mV    |      |

| Current-Limit Threshold (Positive                                                         | MAX1960/MAX196                                              | 100                                                        | 114                     | 135                      | mV    |      |

| Direction, Adjustable, VPGND - VLX)                                                       | $R_{ILIM} = 400k\Omega$                                     | 250                                                        | 279                     | 306                      |       |      |

| Current-Limit Threshold (Negative                                                         | MAX1960/MAX1961, $R_{ILIM} = 160$ kΩ                        |                                                            | 90                      | 107                      | 125   | .,,  |

| Direction, Adjustable, V <sub>LX</sub> - V <sub>PGND</sub> )                              | $R_{ILIM} = 400k\Omega$                                     |                                                            | 245                     | 271                      | 296   | mV   |

| Thermal-Shutdown Threshold                                                                | 15°C hysteresis                                             |                                                            |                         | +160                     |       | °C   |

| DH Gate-Driver On-Resistance                                                              | V <sub>BST</sub> - V <sub>LX</sub> = 5V, pt                 | ulling up or down                                          |                         | 1.8                      | 3.5   | Ω    |

| DL Gate-Driver On-Resistance (Pullup)                                                     | DL high state                                               |                                                            |                         | 1.8                      | 3.5   | Ω    |

| DL Gate-Driver On-Resistance (Pulldown)                                                   | DL low state                                                |                                                            |                         | 0.5                      | 1.6   | Ω    |

| <br>  Minimum Adaptive Dead Time                                                          | DH falling to DL ris                                        | ing                                                        |                         | 35                       |       | ns   |

| - William / Gapave Boad Time                                                              | DH rising to DL fall                                        |                                                            | 26                      |                          | 110   |      |

| <br>  FSET/SYNC Pulse Width                                                               | Minimum high time                                           | (Note 1)                                                   | 200                     |                          |       | i ns |

| F3E1/31NC Fulse Width                                                                     | Minimum low time (                                          | (Note 1)                                                   | 200                     |                          |       | 115  |

| FSET/SYNC Rise/Fall Time                                                                  | (Note 1)                                                    |                                                            |                         |                          | 100   | ns   |

| CTL_, FSET/SYNC, EN Input High Voltage                                                    | V <sub>VCC</sub> = 2.35V to 5.5V                            |                                                            | 2.0                     |                          |       | V    |

| CTL_, FSET/SYNC, EN Input Low Voltage                                                     | V <sub>VCC</sub> = 2.35V to 5.5V                            |                                                            |                         |                          | 0.8   | V    |

| CTL_, FSET/SYNC, EN Input Current                                                         |                                                             |                                                            | -1                      |                          | +1    | μΑ   |

| CLKOUT V <sub>OL</sub>                                                                    | Sinking 1mA                                                 |                                                            |                         | 0.01                     | 0.1   | V    |

| CLKOUT V <sub>OH</sub>                                                                    | Sourcing 1mA                                                |                                                            | V <sub>VCC</sub> - 0.2V | V <sub>VCC</sub> - 0.01V |       | V    |

| CLKOUT Rise/Fall Time                                                                     | C <sub>LOAD</sub> = 100pF (N                                | ote 1)                                                     |                         |                          | 40    | ns   |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{VCC} = 3.3V, Circuits of Figures 9-12, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 2)$

| PARAMETER                                                                                 | ARAMETER CONDITIONS                                                         |                                       | MIN      | TYP   | MAX   | UNITS |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------|----------|-------|-------|-------|

| V <sub>CC</sub> Input Voltage Range                                                       |                                                                             |                                       |          |       | 5.50  | V     |

| V <sub>CC</sub> Input Voltage UVLO                                                        | Rising or falling                                                           |                                       | 1.95     |       | 2.3   | V     |

| V <sub>DD</sub> Input Voltage UVLO                                                        | Rising or falling                                                           |                                       | 3.90     |       | 4.45  | V     |

| Output Voltage                                                                            |                                                                             |                                       | 0.8      |       |       | V     |

|                                                                                           | MAX1960/MAX1962 (mea                                                        | asured at FB)                         | 0.795    |       | 0.805 |       |

|                                                                                           |                                                                             | SEL = GND                             | 1.492    |       | 1.508 |       |

| DC Output Accuracy                                                                        | MAX1961/MAX1962                                                             | SEL = REF                             | 1.789    |       | 1.809 | V     |

|                                                                                           | (FB = V <sub>DD</sub> ),<br>measured at output                              | SEL not connected                     | 2.482    |       | 2.517 | j     |

|                                                                                           |                                                                             | 3.272                                 |          | 3.339 |       |       |

| Positive Voltage-Margining Shift                                                          | MAX1960/MAX1961                                                             | SEL = V <sub>DD</sub> MAX1960/MAX1961 |          |       | 4.2   | %     |

| Negative Voltage-Margining Shift                                                          | MAX1960/MAX1961                                                             |                                       | -3.8     |       | -4.2  | %     |

| FB Input Bias Current                                                                     | ·                                                                           |                                       | -0.2     |       | +0.2  | μA    |

| Feedback Transconductance                                                                 |                                                                             |                                       | 1        |       | 3     | mS    |

| COMP Discharge Resistance                                                                 | In shutdown                                                                 |                                       |          |       | 100   | Ω     |

| -                                                                                         | FSET/SYNC = GND                                                             |                                       | 450      |       | 550   |       |

| Switching Frequency                                                                       | FSET/SYNC = V <sub>CC</sub>                                                 | 880                                   |          | 1120  | kHz   |       |

| SYNC Frequency Range                                                                      | 1021,01110                                                                  |                                       | 450      |       | 1200  | kHz   |

| Maximum Duty Cycle                                                                        | f = 1MHz                                                                    | f - 1MHz                              |          |       | 1200  | %     |

| Maximum Duty Cycle                                                                        | f = 500kHz                                                                  |                                       | 80<br>90 |       |       | %     |

| Quiescent Supply Current                                                                  | , 335.W.IZ                                                                  |                                       |          |       | 15    | mA    |

| Shutdown Supply Current                                                                   |                                                                             |                                       |          |       | 15    | μA    |

| опасаеми варру ванена                                                                     | 2.7V ≤ V <sub>VCC</sub> ≤ 5.5V, I <sub>LOA</sub>                            | 4.75                                  |          | 5.25  | μ, τ  |       |

| V <sub>DD</sub> Output Voltage                                                            | $2.35V \le V_{VCC} \le 2.7V$ , I <sub>LO</sub> , C1 = 4.7µF, C6 = $22\mu$ F | 4.45                                  |          | 5.25  | V     |       |

|                                                                                           | 2.35V ≤ V <sub>VCC</sub> ≤ 3.6V with to 50mA (circuit of Figure             | 4.75                                  |          | 5.25  |       |       |

| Reference Voltage (No Load)                                                               |                                                                             |                                       | 1.267    |       | 1.291 | V     |

| Positive Current-Limit Threshold (Vcs - Vout)                                             | MAX1962, V <sub>OUT</sub> = 2V                                              |                                       | 45       |       | 56    | mV    |

| Negative Current-Limit Threshold (Vout - Vcs)                                             | MAX1962, V <sub>OUT</sub> = 2V                                              |                                       | 42       |       | 64    | mV    |

| CS Bias Current                                                                           | MAX1962, V <sub>CS</sub> = 3.3V                                             | MAX1962, Vcs = 3.3V                   |          |       | 50    | μΑ    |

| OUT Bias Current                                                                          | MAX1961/MAX1962, V <sub>OL</sub>                                            |                                       |          | 50    | μΑ    |       |

| Current-Limit Threshold (Positive Direction, Fixed, V <sub>PGND</sub> - V <sub>LX</sub> ) | MAX1960/MAX1961, ILIN                                                       | 58                                    |          | 90    | mV    |       |

| Current-Limit Threshold (Negative Direction, Fixed, V <sub>LX</sub> - V <sub>PGND</sub> ) | MAX1960/MAX1961, ILIN                                                       | 1 = V <sub>DD</sub>                   | 50       |       | 85    | mV    |

| Current-Limit Threshold (Positive                                                         | MAX1960/MAX1961, R <sub>ILI</sub>                                           | $M = 160k\Omega$                      | 100      |       | 135   |       |

| Direction, Adjustable, V <sub>PGND</sub> - V <sub>LX</sub> )                              | $R_{ILIM} = 400k\Omega$                                                     |                                       | 250      |       | 306   | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VCC} = 3.3V, Circuits of Figures 9-12, T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 2)$

| PARAMETER                                                    | CONDITIONS                                    | MIN            | TYP | MAX | UNITS |  |

|--------------------------------------------------------------|-----------------------------------------------|----------------|-----|-----|-------|--|

| Current-Limit Threshold (Negative                            | MAX1960/MAX1961, $R_{ILIM} = 160$ kΩ          | 90             |     | 125 | m\/   |  |

| Direction, Adjustable, V <sub>LX</sub> - V <sub>PGND</sub> ) | $R_{ILIM} = 400k\Omega$                       | 245            |     | 296 | mV    |  |

| DH Gate-Driver On-Resistance                                 | $V_{BST}$ - $V_{LX}$ = 5V, pulling up or down |                |     | 3.5 | Ω     |  |

| DL Gate-Driver On-Resistance (Pullup)                        | DL high state                                 |                |     | 3.5 | Ω     |  |

| DL Gate-Driver On-Resistance (Pulldown)                      | DL low state                                  |                |     | 1.6 | Ω     |  |

| FOFT/CVN/C Dulg a Width                                      | Minimum high time                             | 200            |     |     |       |  |

| FSET/SYNC Pulse Width                                        | Minimum low time                              | 200            |     |     | ns    |  |

| FSET/SYNC Rise/Fall Time                                     |                                               |                |     | 100 | ns    |  |

| CTL_, FSET/SYNC, EN Input High Voltage                       | V <sub>VCC</sub> = 2.35V to 5.5V              | 2.0            |     |     | V     |  |

| CTL_, FSET/SYNC, EN Input Low Voltage                        | V <sub>VCC</sub> = 2.35V to 5.5V              |                |     | 0.8 | V     |  |

| CTL_, FSET/SYNC, EN Input Current                            |                                               | -1             |     | +1  | μΑ    |  |

| CLKOUT V <sub>OL</sub>                                       | Sinking 1mA                                   |                |     | 0.1 | V     |  |

| CLKOUT V <sub>OH</sub>                                       | Sourcing 1mA                                  | Vvcc -<br>0.2V |     |     | V     |  |

| CLKOUT Rise/Fall Time                                        | C <sub>LOAD</sub> = 100pF                     |                |     | 40  | ns    |  |

Note 1: Guaranteed by design.

**Note 2:** Specifications at -40°C are guaranteed by design, and not production tested.

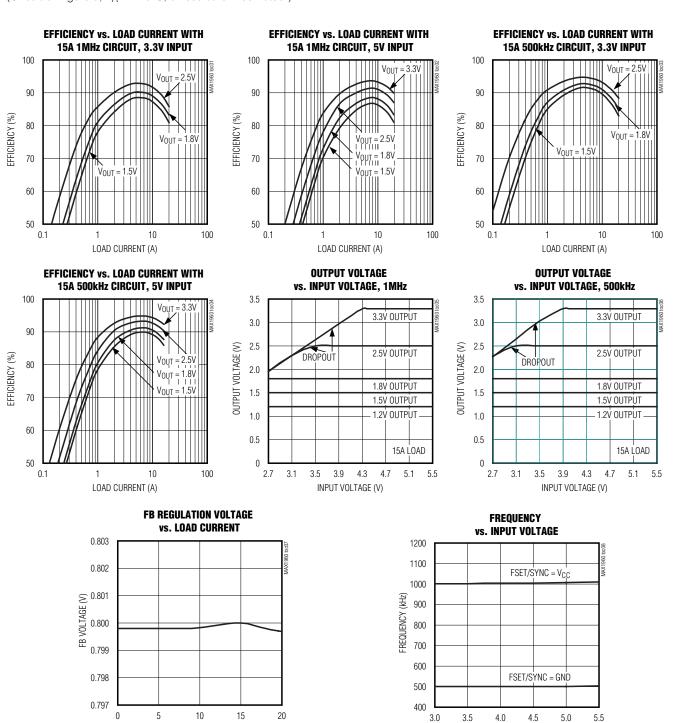

Typical Operating Characteristics

(Circuit of Figure 9,  $T_A = +25$ °C, unless otherwise noted.)

LOAD CURRENT (A)

INPUT VOLTAGE (V)

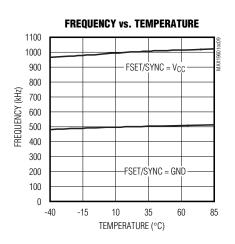

### Typical Operating Characteristics (continued)

(Circuit of Figure 9,  $T_A = +25$ °C, unless otherwise noted.)

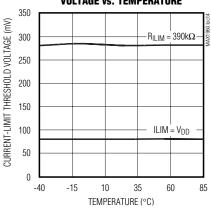

#### MAX1960/MAX1961 CURRENT-LIMIT THRESHOLD VOLTAGE vs. TEMPERATURE

\_Typical Operating Characteristics (continued)

(Circuit of Figure 9,  $T_A = +25$ °C, unless otherwise noted.)

3 \_\_\_\_\_\_*NIXIN*

### **Pin Description**

|         | PIN     |         |                  |                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1960 | MAX1961 | MAX1962 | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                             |

| 1       | 1       | 1       | CLKOUT           | Clock Output. Connect to FSET/SYNC of a second converter to operate 180° out-of-phase. CLKOUT swings from V <sub>CC</sub> to GND. CLKOUT is low in shutdown (see the <i>Operating Frequency and Synchronization</i> section).                                                                                                                                        |

| 2       | 2       | 2       | FSET/SYNC        | Frequency Set and Synchronization. Connect to GND for 500kHz operation, connect to V <sub>CC</sub> for 1MHz operation, or drive with clock signal to synchronize (between 450kHz and 1200kHz).                                                                                                                                                                       |

| 3       | 3       | _       | ILIM             | Current Limit. Connect a resistor from ILIM to GND to set the current-sense threshold voltage. Connect ILIM to $V_{DD}$ to select the default threshold of 75mV.                                                                                                                                                                                                     |

| _       | _       | 3       | EN               | Enable. Drive high for normal operation. Drive low or connect to GND for shutdown mode.                                                                                                                                                                                                                                                                              |

| _       | 4       | 4       | SEL              | Preset Output Voltage Select. Allows the output to be set to one of four preset voltages (1.5V, 1.8V, 2.5V, and 3.3V). For the MAX1962, FB must be connected to $V_{\rm DD}$ if SEL is to be used (see the <i>Setting the Output Voltage</i> section).                                                                                                               |

| 4       | _       | _       | N.C.             | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                             |

| _       | 8       | 5       | OUT              | Output. Connect to the output. Used to sense the output voltage for internal feedback and current sense.                                                                                                                                                                                                                                                             |

| 5       | 5       | _       | CTL1             | Control Pins. Controls voltage margining and shutdown. Connect both CTL1 and CTL2 high for normal operation. Connect both CTL1 and CTL2 low for shutdown. Connect CTL1 high and CTL2 low for +4% voltage margining. Connect CTL1 low                                                                                                                                 |

| 6       | 6       | _       | CTL2             | and CTL2 high for -4% voltage margining. If voltage margining is not to be used, connect CTL1 and CTL2 together and use to enable/shutdown the device.                                                                                                                                                                                                               |

| _       | _       | 6       | CS               | Current-Sense Input. Connect to the junction of the current-sense resistor and the inductor. The MAX1962 current-sense threshold is 50mV measured from CS to OUT.                                                                                                                                                                                                    |

| 7       | 7       | 7       | AV <sub>DD</sub> | Filtered Supply from $V_{DD}$ . Connect a 1µF bypass capacitor. $AV_{DD}$ is forced to $V_{CC}$ in shutdown. <b>Do not apply an external load to <math>AV_{DD}</math></b> .                                                                                                                                                                                          |

| 8       | _       | 8       | FB               | Feedback Input. The feedback threshold is 0.8V. Connect to the center of a resistive voltage-divider from the output to GND to set the output voltage to 0.8V or greater. On the MAX1962, connect FB to $V_{\rm DD}$ to select preset output voltages (see SEL).                                                                                                     |

| 9       | 9       | 9       | COMP             | Compensation Pin. COMP is forced to GND in shutdown, UVLO, or thermal fault.                                                                                                                                                                                                                                                                                         |

| 10      | 10      | 10      | REF              | Reference Output. V <sub>REF</sub> = 1.28V. Bypass with a 0.22µF capacitor to GND.                                                                                                                                                                                                                                                                                   |

| 11      | 11      | 11      | GND              | Analog Ground. Connect to the PC board analog ground plane. Connect the PC board analog ground plane and power ground planes with a single connection.                                                                                                                                                                                                               |

| 12      | 12      | 12      | V <sub>DD</sub>  | Charge-Pump Output. Provides regulated 5V to power the IC and gate drivers. Bypass with a 4.7 $\mu$ F ceramic capacitor for operating frequencies between 450kHz and 950kHz. Bypass with a 2.2 $\mu$ F ceramic capacitor for 1MHz operation. V <sub>DD</sub> is internally forced to V <sub>CC</sub> in shutdown. Do not apply an external load to V <sub>DD</sub> . |

| 13      | 13      | 13      | DL               | Low-Side MOSFET Synchronous Rectifier Gate-Driver Output. DL is high in shutdown.                                                                                                                                                                                                                                                                                    |

| 14      | 14      | 14      | PGND             | Power Ground. Connect to the PC board power ground plane.                                                                                                                                                                                                                                                                                                            |

### **Pin Description (continued)**

|         | PIN     |         |     | FUNCTION                                                                                                                     |  |  |  |  |  |

|---------|---------|---------|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MAX1960 | MAX1961 | MAX1962 |     |                                                                                                                              |  |  |  |  |  |

| 15      | 15      | 15      | C-  | Charge-Pump Flying Capacitor Negative Connection. Use a 0.47µF ceramic capacitor at 1MHz, and 1µF between 450kHz and 950kHz. |  |  |  |  |  |

| 16      | 16      | 16      | C+  | Charge-Pump Flying Capacitor Positive Connection. Use a 0.47µF ceramic capacitor at 1MHz and 1µF between 450kHz and 950kHz.  |  |  |  |  |  |

| 17      | 17      | 17      | Vcc | Input Supply to Charge Pump                                                                                                  |  |  |  |  |  |

| 18      | 18      | 18      | BST | Boost Capacitor Connection. Connect a 0.1µF ceramic capacitor from BST to LX.                                                |  |  |  |  |  |

| 19      | 19      | 19      | DH  | High-Side MOSFET Gate-Driver Output. DH is low in shutdown.                                                                  |  |  |  |  |  |

| 20      | 20      | 20      | LX  | Inductor Connection                                                                                                          |  |  |  |  |  |

### **Detailed Description**

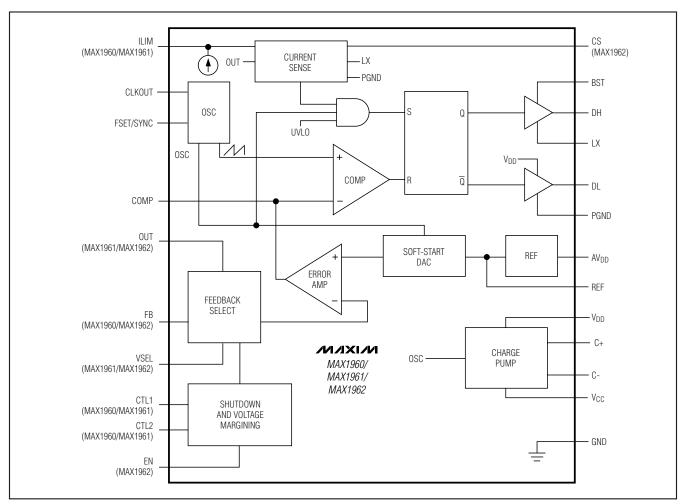

The MAX1960/MAX1961/MAX1962 are high-current, high-efficiency voltage-mode step-down DC-DC controllers that operate from 2.35V to 5.5V input and generate adjustable voltages down to 0.8V at up to 20A. An on-chip charge pump generates a regulated 5V for driving a variety of external N-channel MOSFETs.

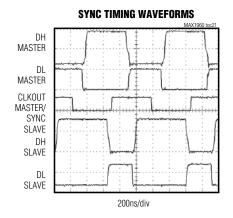

Constant frequency PWM operation and external synchronization make these controllers suitable for telecom and datacom applications. The operating frequency is programmed externally to either 500kHz or 1MHz, or from 450kHz to 1.2MHz with an external clock. A clock output is provided to synchronize another converter for 180° out-of-phase operation.

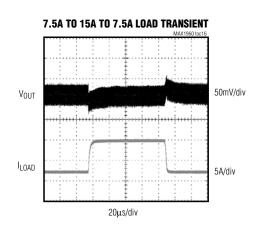

A high closed-loop bandwidth provides excellent transient response for applications with dynamic loads.

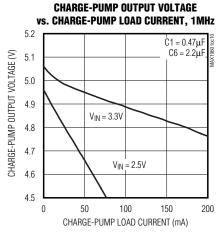

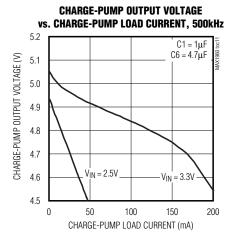

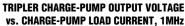

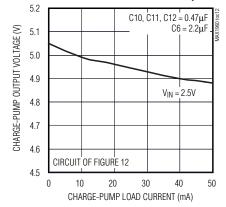

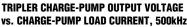

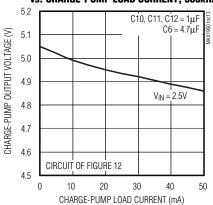

#### **Internal Charge Pump**

An on-chip regulated charge pump develops 5V at 50mA (max) with input voltages as low as 2.35V. The output of this charge pump provides power for the internal circuitry, bias for the low-side driver (DL), and the bias for the boost diode, which supplies the high-side MOSFET gate driver (DH). The charge pump is synchronized with the DL driver signal and operates at 1/2 the PWM frequency.

The external MOSFET gate charge is the dominant load for the charge pump and is proportional to the PWM switching frequency. The charge pump must supply chip-operating current plus adequate gate current for both MOSFETs at the selected operating frequency. The required charge-pump output current is given by the formula:

ITOTAL = IAVDD + fOSC (QG1 + QG2)

where  $I_{AVDD}$  is the current supplied to the IC through AVDD (typically 2mA),  $f_{OSC}$  is the PWM switching frequency,  $Q_{G1}$  is the gate charge of the high-side MOSFET, and  $Q_{G2}$  is the gate charge of the low-side MOSFET. The MOSFETs must be chosen such that  $I_{TOTAL}$  does not exceed 50mA. For example, with 1MHz operation,  $Q_{G1} + Q_{G2}$  should be less than 48nC.

#### **Voltage Margining and Shutdown**

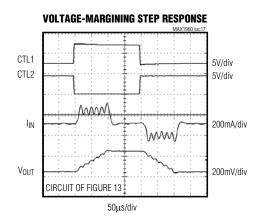

The voltage-margining feature on the MAX1960/MAX1961 shifts the output voltage up or down by 4%. This is useful for the automatic testing of systems at high and low supply conditions to find potential hardware failures. CTL1 and CTL2 control voltage margining as outlined in Table 1.

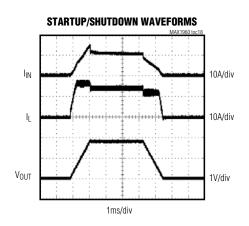

A shutdown feature is included on all three parts, which stops switching the output drivers and the charge pump, reducing the supply current to less than 15µA. For the MAX1962, drive EN high for normal operation, or low for shutdown. For the MAX1960/MAX1961, drive both CTL1 and CTL2 high for normal operation, or drive CTL1 and CTL2 low for shutdown. For a simple enable/shutdown function with no voltage margining, connect CTL1 and CTL2 together and drive as one input.

**Table 1. Voltage Margining Truth Table**

| CTL1 | CTL2 | FUNCTION                 |

|------|------|--------------------------|

| High | High | Normal operation         |

| High | Low  | +4% output-voltage shift |

| Low  | High | -4% output-voltage shift |

| Low  | Low  | Shutdown                 |

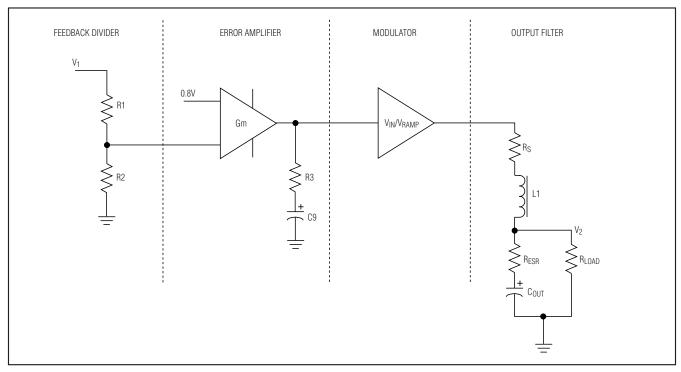

Figure 1. Functional Diagram

#### **MOSFET Gate Drivers**

The DH and DL drivers are designed to drive logic-level N-channel MOSFETs to optimize system cost and efficiency. MOSFETs with RDSON rated at VGS 4.5V are recommended. An adaptive dead-time circuit monitors the DL output and prevents the high-side MOSFET from turning on until DL is fully off. There must be a low-resistance, low-inductance path from the DL driver to the MOSFET gate for the adaptive dead-time circuit to work properly. Otherwise, the internal sense circuitry could interpret the MOSFET gate as "off" while there is actually still charge left on the gate. Use very short, wide traces measuring no more than 20 squares (50mils to 100mils wide if the MOSFET is 1 in from the IC).

#### **Undervoltage Lockout and Soft-Start**

There are two undervoltage lockout (UVLO) circuits on the MAX1960/MAX1961/MAX1962. The first UVLO circuit monitors VCC, which must be above 2.15V (typ) in order for the charge pump to operate. The second UVLO circuit monitors the output of the charge pump. The charge-pump output, VDD, must be above 4.2V (typ) in order for the PWM converter to operate. Both UVLO circuits inhibit switching and force DL high and DH low when either VCC or VDD are below their threshold. When the monitored voltages are above their thresholds, an internal soft-start timer ramps up the erroramplifier reference voltage. The ramp occurs in eighty 10mV steps. Full output voltage is reached 1.28ms after activation with a 1MHz operating frequency.

#### **Operating Frequency and Synchronization**

The MAX1960/MAX1961/MAX1962 operating frequency is set externally to either 500kHz or 1MHz. For 500kHz operation, connect FSET/SYNC to GND, or for 1MHz operation, connect FSET/SYNC to VDD. Alternately, an external clock from 450kHz to 1.2MHz can be applied to SYNC.

A clock output (CLKOUT) that is 180° out-of-phase with the internal clock is also provided. This allows a second converter to be synchronized, and operate 180° out-of-phase with the first. To do this, simply connect CLKOUT of the first converter to FSET/SYNC of the second converter. The first converter can be set internally to 500kHz or 1MHz for this mode of operation. When the first converter is synchronized to an external clock, CLKOUT is the inverse of external clock. See the SYNC Timing Waveform in the *Typical Operating Characteristics*.

### Lossless Current Limit (MAX1960/MAX1961)

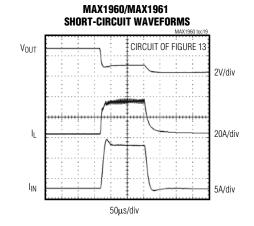

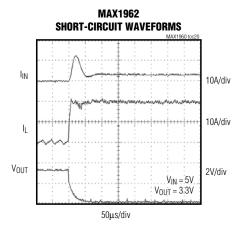

To prevent damage in the case of excessive load current or a short circuit, the MAX1960/MAX1961 use the low-side MOSFET's on-resistance (RDS(ON)) for current sensing. The current is monitored during the on-time of the low-side MOSFET. If the current-sense voltage (VPGND - VLX) rises above the current-limit threshold for more than 128 clock cycles, the controller turns off. The controller remains off until the input voltage is removed or the device is re-enabled with CTL1 and CTL2 (see the Setting the Current Limit section).

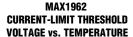

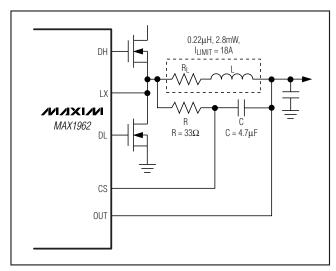

#### **Current-Sense Resistor (MAX1962)**

The MAX1962 uses a standard current-sense resistor in series with the inductor for a 10% accurate current-limit measurement. The current-sense threshold is 50mV. This provides accurate current sensing at all duty cycles without relying on MOSFET on-resistance. CS connects to the high-side (inductor side) of the current-sense resistor and OUT connects to the low-side (output side) of the current-sense resistor.

The current-sense resistor for the MAX1962 may also be replaced with a series RC network across the inductor. This method uses the parasitic resistance of the inductor for current sensing. This method is less accurate than using a current-sense resistor, but is lower cost and provides slightly higher efficiency. See the *Design Procedure* section for instructions on using this method.

#### **Dropout Performance**

The MAX1960/MAX1961/MAX1962 enter dropout when the input voltage is not sufficiently high to maintain output regulation. As input voltage is lowered, the duty cycle

increases until it reaches its maximum value, where the part enters dropout. With a switching frequency of 1MHz, the maximum duty cycle is about 83%. At 500kHz, the duty cycle can increase to about 92%, resulting in a lower dropout voltage. The duty cycle is dependent on the input voltage (V<sub>IN</sub>), the output voltage (V<sub>OUT</sub>), and the parasitic voltage drops in the MOSFETs and the inductor (V<sub>DROP(N1)</sub>, V<sub>DROP(N2)</sub>, V<sub>DROP(L)</sub>). Note that V<sub>DROP(L)</sub> includes the voltage drop due to the inductor's resistance, the drop across the current-sense resistor (if used), and any other resistive voltage drop from the LX switching node to the point where the output voltage is sensed. The duty cycle is found from:

$$D = \frac{V_{OUT} + V_{DROP(L)}}{V_{IN} - V_{DROP(N1)} - V_{DROP(N2)}}$$

### **Adaptive Dead Time**

The MAX1960/MAX1961/MAX1962 DL and DH MOSFET drivers have an adaptive dead-time circuit to prevent shoot-through current caused by high- and low-side MOSFET overlap. This allows a wide variety of MOSFETs to be used without matching FET dynamic characteristics. The DL driver will not go high until DH drives the high-side MOSFET gate to within 1V of its source (LX). The DH output will not go high until DL drives the low-side MOSFET gate to within 1V of ground.

### Design Procedure

Component selection is primarily dictated by the following criteria:

**Input voltage range.** The maximum value (V<sub>IN(MAX)</sub>) must accommodate the worst-case high input voltage. The minimum value (V<sub>IN(MIN)</sub>) must account for the lowest input voltage after drops due to connectors, fuses, and selector switches are considered.

**Maximum load current.** There are two values to consider: The *peak load current* (I<sub>LOAD(MAX)</sub>) determines the instantaneous component stresses and filtering requirements and is key in determining output capacitor requirements. I<sub>LOAD(MAX)</sub> also determines the inductor saturation rating and the design of the current-limit circuit. The *continuous load current* (I<sub>LOAD</sub>) determines the thermal stresses and is key in determining input capacitor requirements, MOSFET requirements, as well as those of other critical heat-contributing components.

Inductor operating point. This choice provides tradeoffs between size, transient response, and efficiency. Choosing higher inductance values results in lower inductor ripple current, lower peak current, lower switching losses, and, therefore, higher efficiency at the cost of slower transient response and larger size. Choosing lower inductance values results in large ripple currents, smaller size, and poorer efficiency, but have faster transient response.

#### **Setting the Output Voltage**

The MAX1961 has four output voltage presets selected by SEL. Table 2 shows how each of the preset voltages are selected. The MAX1962 also has four preset output voltages, but also is adjustable down to 0.8V. To use the preset voltages on the MAX1962, FB must be connected to VDD. SEL then selects the output voltage as shown in Table 2.

Both the MAX1960/MAX1962 feature an adjustable output that can be set down to 0.8V. To set voltages greater than 0.8V, Connect FB to a resistor-divider from the output (Figures 9 and 11). Use a resistor up to  $10k\Omega$  for R2 and select R1 according to the following equation:

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

where the feedback threshold,  $V_{FB} = 0.8V$ , and  $V_{OUT}$  is the output voltage.

#### Input Voltage Range

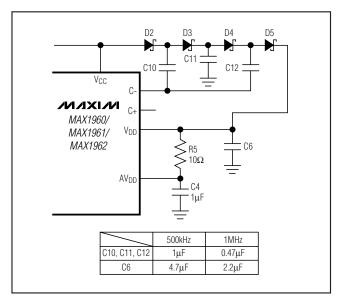

The MAX1960/MAX1961/MAX1962 have an input voltage range of 2.35V to 5.5V but cannot operate at both extremes with one application circuit. The standard charge-pump doubler application circuit operates with an input range of 2.7V to 5.5V (Figures 9, 10, and 11). In order to operate down to 2.35V, the charge pump must be configured as a tripler. This circuit, however, limits the maximum input voltage to 3.6V. The schematic for the tripler charge pump is shown in Figure 2. Note that the flying capacitor between C+ and C- has been removed and C+ is not connected.

#### **Inductor Selection**

Determine an appropriate inductor value with the following equation:

$$L = V_{OUT} \times \frac{V_{IN} - V_{OUT}}{V_{IN} \times f_{OSC} \times LIR \times I_{LOAD(MAX)}}$$

The inductor current ripple, LIR, is the ratio of peak-topeak inductor ripple current to the average continuous inductor current. An LIR between 20% and 40% pro-

### Table 2. Preset Voltages — MAX1961/MAX1962

| PRESET OUTPUT VOLTAGE | SEL           |

|-----------------------|---------------|

| 1.5V                  | GND           |

| 1.8V                  | REF           |

| 2.5V                  | No connection |

| 3.3V                  | $V_{DD}$      |

Figure 2. Tripler Charge-Pump Configuration.

vides a good compromise between efficiency and economy. Choose a low-loss inductor having the lowest possible DC resistance. Ferrite core type inductors are often the best choice for performance. The inductor saturation current rating must exceed IPFAK:

$$I_{PEAK} = I_{LOAD(MAX)} + \left(\frac{LIR}{2}\right) \times I_{LOAD(MAX)}$$

#### **Setting the Current Limit**

#### Lossless Current Limit (MAX1960/MAX1961)

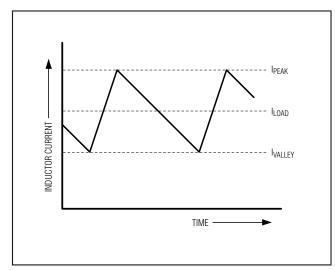

The MAX1960/MAX1961 use the low-side MOSFET's on-resistance (RDS(ON)) for current sensing. This method of current limit sets the maximum value of the inductor's "valley" current (Figure 3). If the inductor current is higher than the valley current-limit setting at the end of the clock period, the controller skips the DH pulse. When the first current-limit event is detected, the controller initi-

Figure 3. Inductor Current Waveform

ates a 128 clock cycle counter. If the current limit is present at the end of this count, the controller remains off until the input voltage is removed and re-applied, or the device is re-enabled with CTL1 and CTL2. The 128-cycle counter is reset when four successive DH pulses are observed, without activating the current limit.

At maximum load, the low excursion of inductor current, IVALLEY(MAX), is:

$$I_{VALLEY(MAX)} = I_{LOAD(MAX)} - \left(\frac{LIR}{2}\right) \times I_{LOAD(MAX)}$$

The current-limit threshold (V<sub>CLT</sub>) is set by connecting a resistor (R<sub>ILIM</sub>) from ILIM to GND. The range for this resistor is  $100k\Omega$  to  $400k\Omega$ . Set current-limit threshold as follows:

$$V_{CLT} = R_{ILIM} \times 0.714 \mu A$$

Connecting ILIM to  $V_{\mbox{\scriptsize DD}}$  sets the threshold to a default value of 75mV.

To prevent the current limit from falsely triggering,  $V_{CLT}$  divided by the low-side MOSFET  $R_{DS(ON)}$  must exceed the maximum value of  $I_{VALLEY}$ . The maximum value of low-side MOSFET  $R_{DS(ON)}$  should be used:

A limitation of sensing current across MOSFET on-resistance is that the MOSFET on-resistance varies significantly from MOSFET to MOSFET and over temperature. Consequently, this current-sensing method may not be suitable if a precise current limit is required. If better

Figure 4. Using the Inductor Resistance as a Current-Sense Resistor with the MAX1962

accuracy is needed, use the MAX1962 with a current-sense resistor.

#### Current-Sense Resistor (MAX1962)

The MAX1962 uses a current-sense resistor connected from the inductor to the output with Kelvin sense connections. The current-sense voltage is measured from CS to OUT, and has a fixed threshold of 50mV. The MAX1962 current limit is triggered when the peak voltage across the current-sense resistor, IPEAK × RSENSE, exceeds 50mV. Once current sense is triggered, the controller does not turn off, but continues to operate at the current limit. This method of current sensing is more precise due to the accuracy of the current-sense resistor. The cost of this precision is that it requires an extra component and is slightly less efficient due to the loss in the current-sense resistance.

#### Inductor Resistance Current Sense (MAX1962)

Alternately, the inductor resistance can be used to sense current in place of a current-sense resistor. To do this, connect a series RC network in parallel with the inductor (Figure 4). Choose a resistor value less than  $40\Omega$  to avoid offsets due to CS input current. Calculate the capacitor value from the formula C = 2L / (RL  $\times$  R). The effective current-sense resistance (RSENSE) equals RL. Current-sense accuracy then depends on the accuracy of the inductor resistance. Note that the current-sense signal is delayed due to the RC filter time constant. Consequently, inductor current may overshoot (by as much as 2x) when a fast short occurs.

#### **Output Capacitor Selection**

The output filter capacitor must have low enough effective series resistance (ESR) to meet output ripple and load transient requirements. In addition, the capacitance value must be high enough to absorb the inductor energy during load steps.

In applications where the output is subject to large load transients, low ESR is needed to prevent the output from dipping too low (V<sub>DIP</sub>) during a load step:

$$R_{ESR} \le \frac{V_{DIP}}{I_{LOADSTEP(MAX)}}$$

In applications with less severe load steps, maximum ESR may be governed by what is needed to maintain acceptable output voltage ripple:

$$R_{ESR} \le \frac{V_{RIPPLE(P-P)}}{LIR \times I_{LOAD(MAX)}}$$

To satisfy both load step and ripple requirements, select the lowest value from the above two equations.

The capacitor is usually selected by physical size, ESR, and voltage rating, rather than by capacitance value. With current tantalum, electrolytic, and polymer capacitor technology, the bulk capacitance will also be sufficient once the ESR requirement is satisfied.

When using low-capacity filter capacitors such as ceramic, capacitor size is usually determined by the capacitance needed to prevent voltage undershoot and overshoot during load transients. The overshoot voltage (VSOAR) is given by:

$$V_{SOAR} = \frac{L \times (I_{PEAK})^2}{2 \times V_{OUT} \times C_{OUT}}$$

Generally, once enough capacitance is in place to meet the overshoot requirement, undershoot at the rising load edge is no longer a problem.

#### **Input Capacitor Selection**

The input capacitor ( $C_{IN}$ ) reduces the current peaks drawn from the input supply and reduces noise injection. The source impedance to the input supply largely determines the value of  $C_{IN}$ . High source impedance requires high input capacitance. The input capacitor must meet the ripple current requirement ( $I_{RMS}$ ) imposed by the switching currents.

The RMS input ripple current is given by:

$$I_{RMS} = I_{LOAD} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

For optimal circuit reliability, choose a capacitor that has less than 10°C temperature rise at the peak ripple current.

#### **Compensation and Stability**

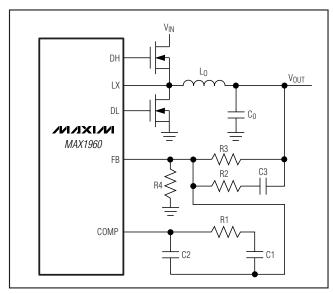

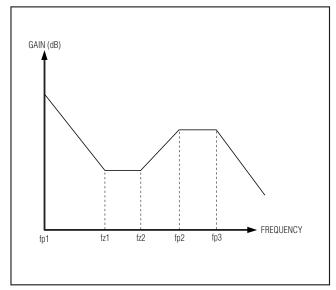

#### Compensation with Ceramic Output Capacitors

The high switching frequency range of the MAX1960/MAX1961/MAX1962 allows the use of ceramic output capacitors. Since the ESR of ceramic capacitors is very low typically, the frequency of the associated transfer function zero is higher than the unity-gain crossover frequency and the zero cannot be used to compensate for the double pole created by the output inductor and capacitor. The solution is Type 3 compensation (Figure 5), which takes advantage of local feedback to create two zeros and three poles (Figure 6). The frequency of the poles and zeros are described below:

$$f_{P1} = 0$$

$$f_{P2} = \frac{1}{2\pi \times R2 \times C3}$$

$$f_{P3} = \frac{1}{2\pi \times R1 \times \frac{C1 \times C2}{C1 + C2}}$$

$$f_{LC} = \frac{1}{2\pi \sqrt{L_0 \times C_0}}$$

$$f_{Z1} = \frac{1}{2\pi \times R1 \times C1}$$

$$f_{Z2} = \frac{1}{2\pi \times (R2 + R3) \times C3}$$

$$f_{ZESR} = \frac{1}{2\pi \times R_{ESR} \times C_0}$$

Unity-gain crossover frequency:

$$f_0 = R1 \times C3 \times \frac{V_{IN(MAX)}}{V_{RAMP}} \times \frac{1}{2\pi \times L_0 \times C_0}$$

Figure 5. Type 3 Compensation Network

where:

V<sub>IN(MAX)</sub> = Maximum input voltage

$V_{RAMP} = Oscillator ramp voltage = 0.85 \times 10^6/f_S$ , where  $f_S = switching frequency$

L<sub>O</sub> = Output inductance

Co = Output capacitance

The goal is to place the two zeros below crossover and the two poles above crossover so that crossover occurs with a single-pole slope. The compensation procedure is as follows:

Select the crossover frequency such that:

$$f_0 < f_{ZESR}$$

and  $f_0 < 1/5 \times f_S$

Select R1 such that:

$$R1>> \frac{2}{g_{mEA}}$$

where  $g_{mEA} = 2mS$ .

Place the first zero before the double pole:

$$C1 \ge \frac{1}{2\pi \times 0.75 \times f_{LC} \times R1}$$

Place the third pole at half the switching frequency:

$$C2 \ge \frac{1}{2\pi \times 0.5 \times f_S \times R1}$$

Figure 6. Transfer Function for Type 3 Compensation

If C2 < 10pF, it can be omitted.

$$C3 \le \frac{2\pi \times f_0 \times L_0 \times C_0 \times V_{RAMP}}{R1 \times V_{IN}}$$

Place the second pole after the ESR zero:

$$R2 \le \frac{1}{2\pi \times f_{7ESR} \times C3}$$

If:

$$R2 < \frac{1}{g_{mFA}}$$

where  $g_{mEA} = 2mS$

increase R1 and recalculate C1, C2, and C3.

Place the second zero at the double-pole frequency:

$$R3 \ge \frac{1}{2\pi \times f_{LC} \times C3} - R2$$

Set the output voltage:

$$R4 = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R3, V_{FB} = 0.8V$$

#### Compensation with Electrolytic Output Capacitors

The MAX1960/MAX1961/MAX1962 use a voltage-mode control scheme that regulates the output voltage by comparing the error-amplifier output (COMP) with a fixed internal ramp to produce the required duty cycle. The inductor and output capacitor create a double pole at the resonant frequency, which has gain drop of 40dB per decade, and phase shift of 180°. The error amplifier must compensate for this gain drop and phase shift in order to achieve a stable high-bandwidth, closed-loop system.

The basic regulator loop consists of a power modulator, an output feedback divider and an error amplifier. The power modulator has DC gain set by V<sub>IN</sub>/V<sub>RAMP</sub>, with a double pole set by the inductor and output capacitor, and a single zero set by the output capacitor (C<sub>O</sub>) and its equivalent series resistance (ESR). Below are equations that define the power modulator:

The DC gain of the power modulator is:

$$G_{MOD(DC)} = \frac{V_{IN}}{V_{RAMP}}$$

where  $V_{RAMP} = 0.85 \times 10^6$  / fs. The pole frequency due to the inductor and output capacitor is:

$$f_{PMOD} = \frac{1}{2\pi\sqrt{L_0C_0}}$$

The zero frequency due to the output capacitor's ESR is:

$$f_{ZESR} = \frac{1}{2\pi \times R_{ESR} \times C_O}$$

The output capacitor is usually comprised of several same value capacitors connected in parallel. With n capacitors in parallel, the output capacitance is:

$$C_O = n \times C_{FACH}$$

The total ESR is:

$$R_{ESR} = \frac{R_{ESR(EACH)}}{n}$$

The ESR zero (fzesr) for a parallel combination of capacitors is the same as for an individual capacitor.

The feedback divider has a gain of  $G_{FB} = V_{FB}/V_{OUT}$ , where  $V_{FB}$  is 0.8V.

The transconductance error amplifier has DC gain GEA(dc) of 80dB. A dominant pole is set by the compensation capacitor (C<sub>C</sub>), the amplifier output resistance (R<sub>O</sub>), and the compensation resistor (R<sub>C</sub>):

$$f_{PEA} = \frac{1}{2\pi \times C_C \times (R_0 + R_C)}$$

A zero is set by the compensation resistor and the compensation capacitor:

$$f_{ZEA} = \frac{1}{2\pi \times C_C \times R_C}$$

The total closed-loop gain must equal to unity at the crossover frequency, where the crossover frequency should be higher than  $f_{ZESR}$ , so that the -1 slope is used to cross over at unity gain. Also, the crossover frequency should be less than or equal to 1/5 the switching frequency.

$$f_{ZESR} < f_C \le \frac{f_S}{5}$$

The loop-gain equation at the crossover frequency is:

$$\frac{V_{FB}}{V_{OUT}} \times G_{EA(f_C)} \times G_{MOD(f_C)} = 1$$

where:

$$G_{EA(f_C)} = g_{mEA} \times R_C$$

and:

$$G_{MOD(f_C)} = G_{MOD(DC)} \times \frac{(f_{PMOD})2}{f_{ESR} \times f_C}$$

The compensation resistor, RC, is calculated from:

$$R_{C} = \frac{V_{OUT}}{g_{mEA} \times V_{FB} \times G_{MOD(f_{C})}}$$

where  $g_{mEA} = 2mS$ .

Due to the under-damped (Q > 1) nature of the output LC double pole, the error-amplifier compensation zero should be approximately 0.2fpMOD to provide good phase boost. CC is calculated from:

$$C_C = \frac{5}{2\pi \times R_C \times f_{PMOD}}$$

A small capacitor CF, can also be added from COMP to GND to provide high-frequency decoupling. CF will add another high-frequency pole (fPHF) to the error-amplifier response. This pole should be greater than 100 times the error-amplifier zero frequency to have negligible impact on the phase margin. This pole should also be less than half the switching frequency for effective decoupling:

Select a value for f<sub>PHF</sub> in the range given above, then solve for C<sub>F</sub> using the following equation:

$$C_F = \frac{1}{2\pi \times R_C \times f_{PHF}}$$

Below is a numerical example to calculate compensation values:

VIN = 3.3V

$V_{RAMP} = 0.85V$

$V_{OUT} = 1.8V$

$V_{FB} = 0.8V$

IOUT(max) = 15A

$C_0 = 2 \times 680 \mu F = 1360 \mu F$

$\mathsf{ESR} = 0.008\Omega \, / \, 2 = 0.004\Omega$

$L_0 = 0.22 \mu H$

$g_{mEA} = 2mS$

$f_S = 1MHz$

$$f_{PMOD} = \frac{1}{2\pi \times \sqrt{L_O \times C_O}}$$

$$= \frac{1}{2\pi \times \sqrt{0.22 \times 10^{-6} \times 1360 \times 10^{-6}}}$$

$$= \frac{2.01 \text{ kHz}}{2.01 \text{ kHz}}$$

$$f_{ZESR} = \frac{1}{2\pi \times C_{O} \times R_{ESR}}$$

$$= \frac{1}{2\pi \times 1360 \times 10^{-6} \times 0.004}$$

= 29.3kHz

Choose the crossover frequency (fc) in the range fZESR < fc < fs/5:

$$29.3kHz < f_C < 200kHz$$

Select f<sub>C</sub> = 100kHz, this meets the criteria above, and the bandwidth is high enough for good transient response.

The power modulator gain at fc is:

$$G_{MOD(fc)} = \frac{V_{IN}}{V_{RAMP}} \times \frac{(f_{PMOD})^2}{f_{ZESR} \times f_C}$$

$$= \frac{3}{0.85} \times \frac{(9201)^2}{29.3k\Omega \times 100k\Omega} = 0.102$$

Choose  $R_1=8.06k\Omega$ , then  $R_2=10k\Omega$  (see the Setting the Output Voltage section):

$$_{C} = \frac{V_{OUT}}{g_{mEA} \times V_{FB} \times G_{MOD(f_{C})}} = \frac{1.8}{0.002 \times 0.8 \times 0.102}$$

= 11k $\Omega$

$$C_C = \frac{5}{2\pi \times R_C \times f_{PMOD}} = \frac{5}{2\pi \times 11 \text{k}\Omega \times 9201} = 7863 \text{pF}$$

Select  $C_C = 8200pF$  (nearest standard capacitor value).

Select fphf in the range 100fzeA < fphf < 0.5fs.

184kHz < fphf < 500kHz

Select fphf = 250kHz, then solve for CF:

$$C_F = \frac{1}{2\pi \times R_C \times f_{PHF}} = \frac{1}{2\pi \times 11 k\Omega \times 250 kHz} = 58 pF$$

Select the nearest standard capacitor value  $C_F = 56 pF$ . Summary of feedback divider and compensation components:

$R_1 = 8.06k\Omega$

$R_2 = 10k\Omega$

$R_C = 11k\Omega$

$C_C = 8200pF$

$C_F = 56pF$

#### **Power MOSFET Selection**

When selecting a MOSFET, essential parameters include:

- (1) Total gate charge (QG)

- (2) Reverse transfer capacitance (CRSS)

- (3) On-resistance (RDS(ON))

Figure 7. Open-Loop Transfer Model

- (4) Gate threshold voltage (V<sub>TH(MIN)</sub>)

- (5) Turn-on/turn-off times

- (6) Turn-on/turn-off delays

At high switching rates, dynamic characteristics (parameters 1, 2, 5, and 6) that predict switching losses may have more impact on efficiency than RDS(ON), which predicts DC losses. QG includes all capacitance associated with charging the gate, and best performance is achieved with a low total gate charge. QG also helps predict the current needed to drive the gate at the selected operating frequency. This is very important because the output current from the charge pump is finite (50mA, max) and is used to drive the gates of the MOSFETs as well as provide bias for the IC. RDS(ON) is important as well, as it is used for current sensing in the MAX1960/MAX1961. RDS(ON) also causes power dissipation during the on-time of the MOSFET.

Choose Q<sub>G</sub> to be as low as possible. Ensure that:

$$Q_{G1} + Q_{G2} \le \frac{50\text{mA}}{f_S}$$

Choose RDS(ON) to provide the desired ILOAD(MAX) at the desired current-limit threshold voltage (see the *Setting the Current Limit* section).

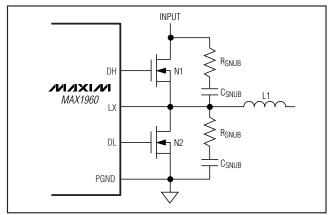

#### **MOSFET RC Snubber Circuit**

Fast-switching transitions can cause ringing due to resonating circuit parasitic inductance and capacitance at the switching nodes. This high-frequency ringing occurs at LX rising and falling transitions, and may introduce current-sensing errors and generate EMI. To dampen this ringing, a series RC snubber circuit can be added across each MOSFET switch (Figure 8). Typical values for the snubber components are CSNUB = 4700pF and RSNUB =  $1\Omega$ , however, the ideal values for snubber components will depend on circuit parasitics. Below is the procedure for selecting the component values of the series RC snubber circuit:

- 1) Connect a scope probe to measure V<sub>LX</sub> to GND, and observe the ringing frequency, f<sub>R</sub>.

- 2) Find the capacitor value (connected from LX to GND) that reduces the ringing frequency by half.

- The circuit parasitic capacitance, CPAR, at LX is then equal to 1/3 of the value of the added capacitance above.

Figure 8. RC Snubber Circuit

The circuit parasitic inductance, LPAR, is calculated by:

$$L_{PAR} = \frac{1}{(2\pi \times f_{R})^{2} \times C_{PAR}}$$

- 5) The resistor for critical dampening,  $R_{SNUB} = 2\pi x$   $f_R x L_{PAR}$ . The resistor value can be adjusted up or down to tailor the desired damping and the peak voltage excursion.

- 6) The capacitor, CSNUB, should be at least 2 to 4 times the value of the CPAR to be effective.

- 7) The snubber circuit power loss is dissipated in the resistor, PRSNUB, and can be calculated as:

$$P_{RSNUB} = C_{SNUB} \times (V_{IN})^2 \times f_S$$

where V<sub>IN</sub> is the input voltage, and fs is the switching frequency. Choose R<sub>SNUB</sub> power rating that exceeds the calculated power dissipation.

#### **MOSFET Power Dissipation**

Worst-case power dissipation occurs at duty factor extremes. For the high-side MOSFET, the worst-case power dissipation due to resistance occurs at minimum input voltage (VIN(MIN)):

$$\text{PD}_{\text{(N1RESISTIVE)}} = \frac{V_{\text{OUT}}}{V_{\text{IN(MIN)}}} \ \times \ I_{\text{LOAD}}^2 \ \times \ R_{\text{DS(ON)}}$$

The following formula calculates switching losses for the high-side MOSFET, but is only an approximation and not a substitute for evaluation:

$$\left(I_{L(PEAK)} \times t_{FALL} + I_{L(VALLEY)} \times t_{RISE}\right) \times \frac{V_{IN(MAX)}}{2} \times f_{S}$$

where  $V_{IN(MAX)}$  is the maximum value of the input voltage,  $t_{FALL}$  and  $t_{RISE}$  are the fall and rise time of the MOSFET,  $I_{L(PEAK)}$  and  $I_{L(VALLEY)}$  are the maximum peak and valley inductor current, and  $f_{S}$  is the PWM switching frequency:

$$IL(PEAK) = IOUT(MAX) \times (1 + 0.5 \times LIR)$$

and  $IL(VALLEY) = IOUT(MAX) \times (1 - 0.5 \times LIR)$

where LIR is the peak-to-peak inductor ripple current divided by the load current.

The total power dissipation in the high-side MOSFET is the sum of these two power losses:

PD(N1) = PD(N1RESISTIVE) + PD(N1SWITCHING)

For the low-side MOSFET, the worst-case power dissipation occurs at maximum input voltage:

$$P_{D(N2RESISTIVE)} = \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right) \times I_{LOAD}^2 \times R_{DS(ON)}$$

### **Applications Information**

#### **PC Board Layout Guidelines**

A properly designed PC board layout is important in any switching DC-DC converter circuit. If possible, mount the MOSFETs, inductor, input/output capacitors, and current-sense resistor on the top side. Connect the ground for these devices close together on a power-ground trace. Make all other ground connections to a separate analog ground plane. Connect the analog ground plane to power ground at a single point.

To help dissipate heat, place high-power components (MOSFETs, inductor, and current-sense resistor) on a large PC board area. Keep high-current traces short and wide to reduce the resistance in these traces. Also make the gate drive connections (DH and DL) short and wide, measuring 10 to 20 squares (50mils to 100mils wide if the MOSFET is 1in from the controller IC).

For the MAX1960/MAX1961, connect LX and PGND to the low-side MOSFET using Kelvin sense connections. For the MAX1962, connect CS and OUT to the current-sense resistor using Kelvin sense connections.

Place the REF capacitor, the BST diode and capacitor, and the charge-pump components as close as possible to the IC. If the IC is far from the input capacitors, bypass VCC to GND with a  $0.1\mu\text{F}$  or greater ceramic capacitor close to the VCC pin.

For an example PC board layout, see the MAX1960 evaluation kit.

**Table 3. Component List for Application Circuits**

| PART          | APP. CIRCUIT          | 15A OUTPUT 1MHz                                            | 15A OUTPUT 500kHz                                    |  |  |

|---------------|-----------------------|------------------------------------------------------------|------------------------------------------------------|--|--|

| C1            | 1, 2, 3               | 0.47µF ceramic capacitor                                   | 1μF ceramic capacitor                                |  |  |

| C2            | 1, 2, 3, 4            | 5 × 10μF ceramic capacitors                                | 5 × 10μF ceramic capacitors                          |  |  |

| C3            | 1, 2, 3, 4            | 2 x 680µF POSCAPs Sanyo 2R5TPD680M8                        | 2 x 680μF POSCAPs Sanyo 2R5TPD680M8                  |  |  |

| C4            | 1, 2, 3, 4            | 1µF ceramic capacitor                                      | 1μF ceramic capacitor                                |  |  |

| C5            | 1, 2, 3, 4            | 0.1µF ceramic capacitor                                    | 0.1µF ceramic capacitor                              |  |  |

| C6            | 1, 2, 3, 4            | 2.2µF ceramic capacitor                                    | 4.7µF ceramic capacitor                              |  |  |

| C8            | 1, 2, 3, 4            | 0.22µF ceramic capacitor                                   | 0.22µF ceramic capacitor                             |  |  |

| C9            | 1, 2, 3, 4            | (Table 4)                                                  | (Table 5)                                            |  |  |

| C10, C11, C12 | 4                     | 0.47µF ceramic capacitors                                  | 1μF ceramic capacitors                               |  |  |

| C13, C14      | 1, 2, 3, 4            | 4700pF ceramic capacitors                                  | 4700pF ceramic capacitors                            |  |  |

| D1            | 1, 2, 3, 4            | Schottky diode<br>Central CMSSH-3                          | Schottky diode<br>Central CMSSH-3                    |  |  |

| D2-D5         | 4                     | Schottky diodes<br>Central CMHSH5-2L                       | Schottky diodes<br>Central CMHSH5-2L                 |  |  |

| L1            | 1, 2, 3, 4            | $0.22\mu H$ , $1.7m\Omega$ inductor Sumida CDEP1040R2NC-50 | 0.45µH inductor<br>Sumida CDEP1040R4MC-50            |  |  |

| N1            | 1, 2, 3, 4            | N-channel MOSFET<br>International Rectifier IRLR7821       | N-channel MOSFET<br>International Rectifier IRLR7821 |  |  |

| N2            | 1, 2, 3, 4            | N-channel MOSFET<br>International Rectifier IRLR7833       | N-channel MOSFET<br>International Rectifier IRLR7833 |  |  |

| R1            | 1, 3                  | Sets output voltage                                        | Sets output voltage                                  |  |  |

| R2            | 1, 3                  | 10kΩ ±1% resistor                                          | 10kΩ ±1% resistor                                    |  |  |

| R3            | 1, 2, 3, 4            | (Table 4)                                                  | (Table 5)                                            |  |  |