# 73M1822/73M1922 MicroDAA Silicon DAA with Serial Interface

### Simplifying System Integration™

### DS\_1x22\_001

#### DESCRIPTION

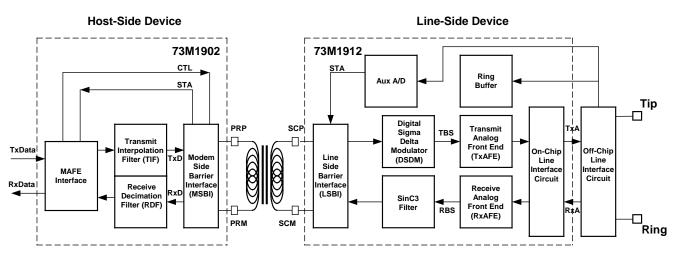

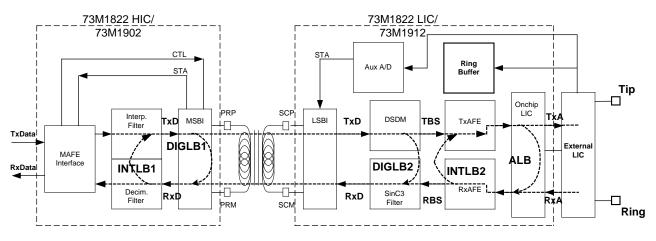

The 73M1822 MicroDAA<sup>™</sup> is the world's first single-package silicon Data Access Arrangement (DAA) for data/fax modem and voice applications. It provides a serial Modem Analog Front End (MAFE) interface to popular DSP/host processors to implement a globally compliant low-cost soft modem solution.

The 73M1822 MicroDAA is available as a two-chip configuration (the 73M1922) that consists of a 73M1902 Host-Side Device and a 73M1912 Line-Side Device. The MicroDAA integrates all codec and DAA functions necessary to achieve reliable PSTN connection worldwide.

The MicroDAA uses a small pulse transformer, which can achieve more than 6 kV isolation. Power may be supplied along with data through this barrier interface to achieve superior performance in weak loop current conditions. Inherently immune to RFI and other forms of common mode interference, the patented MicroDAA technology achieves global DAA compliance with unparalleled flexibility, reliability, and cost structure and requires less than 2 square inches of a single sided PCB.

The MicroDAA supports Caller ID Type I and II, ring detection, tip/ring polarity reversal detection, hook switch control, pulse dialing, regulation of loop current (DC mask), configurable line impedance matching, line in use and parallel pickup detection.

The MicroDAA integrates billing tone filters, external clock reference, audio monitor output, and requires only a small number of low cost and commonly available external components.

The MicroDAA incorporates a configurable sample rate circuit to support soft modem and DSP-based implementations of all speeds up to V.92 (56 Kbps). Sampling rates from 7.2 kHz to 16 kHz can be easily supported.

### DATA SHEET

### April 2010

#### APPLICATIONS

- V.92 modems

- Satellite Set Top Boxes

- Fax/Multifunction Peripherals (MFP)

- Point of Sale Terminals

- Voicemail Systems

- Industrial and medical telemetry

### FEATURES

- Meets FCC, ETSI ES 203 021-2, JATE, NET4 and other PTT standards

- Configurable PSTN termination

- Up to 8 mA minimum line current operation

- 0 dBm Transmit/Receive full scale

- THD --80 dB

- 16-bit codec up to 16 kHz sample rate

- Up to 56 Kbps (V.92) performance

- Configurable sample rates (7.2 16 kHz)

- Reference clock range of 9-40 MHz

- Crystal frequency range of 9-27 MHz

- MAFE I/F with Master, Slave and Daisy Chaining

- Billing tone reject filter

- Polarity reversal detection on-chip

- GPIO for user-configurable I/O port

- Call Progress Monitor

- 3.3 V Operation

- Industrial temperature range (-40° to +85° C)

- 6 kV isolation (73M1922)

- 4-5 kV isolation (73M1822)

- 8x8 mm 42-pin QFN (73M1822)

- 20-pin TSSOP or 5x5 mm 32-pin QFN (73M1922)

- RoHS compliant (6/6) lead-free package

# **Table of Contents**

| 1 | Introduction6 |                                                       |          |  |  |  |

|---|---------------|-------------------------------------------------------|----------|--|--|--|

| 2 | Pinou         | t                                                     | 8        |  |  |  |

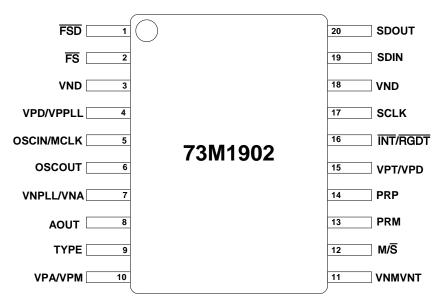

|   | 2.1           | 73M1902 20-Pin TSSOP Pinout                           | . 8      |  |  |  |

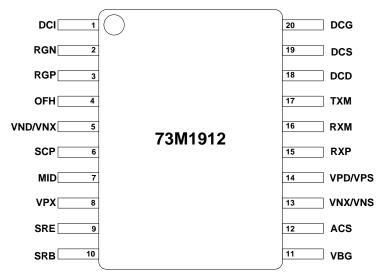

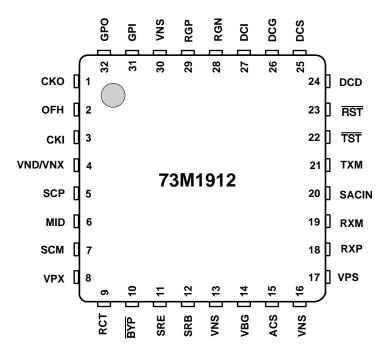

|   | 2.2           | 73M1912 20-Pin TSSOP Pinout                           | 10       |  |  |  |

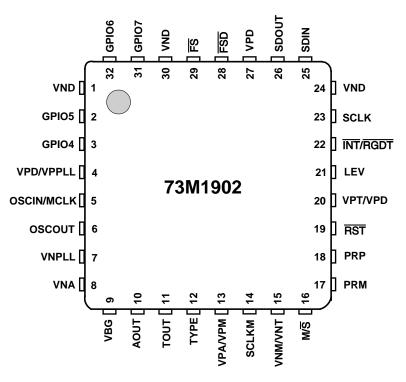

|   | 2.3           | 73M1902 32-Pin QFN Pinout                             | 11       |  |  |  |

|   | 2.4           | 73M1912 32-Pin QFN Pinout                             | 13       |  |  |  |

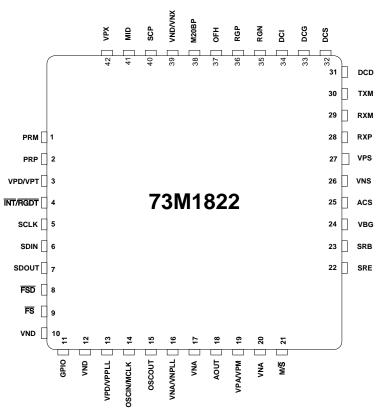

|   | 2.5           | 73M1822 Pinout                                        |          |  |  |  |

|   | 2.6           | Exposed Bottom Pad on 73M1x66B QFN Packages           | 16       |  |  |  |

| 3 | Electr        | ical Characteristics and Specifications               | 17       |  |  |  |

|   | 3.1           | Isolation Barrier Characteristics                     | 17       |  |  |  |

|   | 3.2           | Electrical Specifications                             | 17       |  |  |  |

|   |               | 3.2.1 Absolute Maximum Ratings                        |          |  |  |  |

|   |               | 3.2.2 Recommended Operating Conditions                |          |  |  |  |

|   |               | 3.2.3 DC Characteristics                              |          |  |  |  |

|   | 3.3           | Serial Interface Timing Specification                 |          |  |  |  |

|   | 3.4           | Analog Specifications                                 |          |  |  |  |

|   |               | 3.4.1 DC Specifications                               |          |  |  |  |

|   | o -           | 3.4.2 Call Progress Monitor                           | 20       |  |  |  |

|   | 3.5           | 73M1x22 Line-Side Electrical Specifications (73M1912) |          |  |  |  |

|   | 3.6           | Reference and Regulation                              |          |  |  |  |

|   | 3.7<br>3.8    | AC Signal Levels<br>DC Transfer Characteristics       |          |  |  |  |

|   | 3.8<br>3.9    | Transmit Path                                         |          |  |  |  |

|   | 3.9<br>3.10   | Receive Path                                          |          |  |  |  |

|   | 3.10          | Transmit Hybrid Cancellation                          |          |  |  |  |

|   | 3.12          | Receive Notch Filter                                  |          |  |  |  |

|   | 3.13          | Detectors                                             |          |  |  |  |

|   | 0110          | 3.13.1 Over-Voltage Detector                          |          |  |  |  |

|   |               | 3.13.2 Over-Current Detector                          |          |  |  |  |

|   |               | 3.13.3 Under-Voltage Detector                         | 27       |  |  |  |

|   |               | 3.13.4 Over-Load Detector                             | 27       |  |  |  |

| 4 | Appli         | cations Information                                   |          |  |  |  |

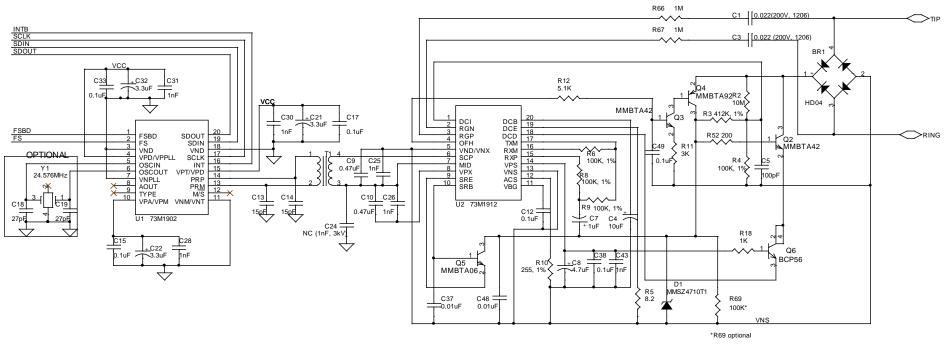

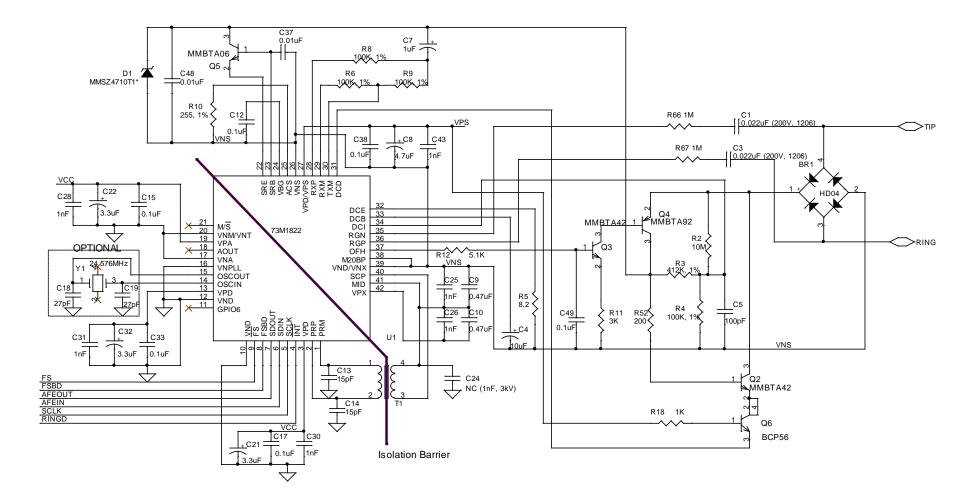

|   | 4.1           | Example Schematic of the 73M1922 and 73M1822          |          |  |  |  |

|   | 4.2           | Bill of Materials                                     |          |  |  |  |

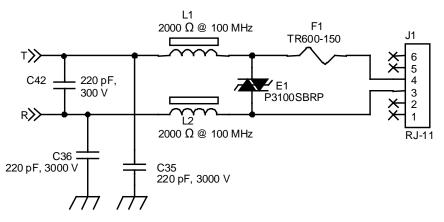

|   | 4.3           | Over-Voltage and EMI Protection                       | 31       |  |  |  |

|   | 4.4           | Isolation Barrier Pulse Transformer                   |          |  |  |  |

| 5 |               | ol and Status Registers                               |          |  |  |  |

|   | 5.1           | Line-Side Device Register Polling                     |          |  |  |  |

| 6 | Hardv         | vare Control Functions                                | 37       |  |  |  |

|   | 6.1           | Device Revision                                       |          |  |  |  |

|   | 6.2           | Interrupt Control                                     |          |  |  |  |

|   | 6.3           | Power Management                                      |          |  |  |  |

|   | 6.4           | Device Clock Management                               |          |  |  |  |

|   | 6.5           | GPIO Registers.                                       |          |  |  |  |

| _ | 6.6           | Call Progress Monitor                                 |          |  |  |  |

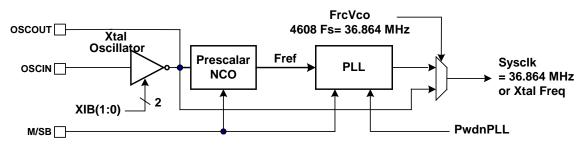

| 7 |               | and Sample Rate Management                            |          |  |  |  |

|   | 7.1           | Clock Generation with HIC (73M1902)                   |          |  |  |  |

|   | 7.2           | Crystal Oscillator                                    |          |  |  |  |

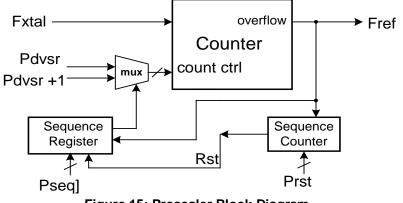

|   | 7.3           | PLL Prescaler                                         |          |  |  |  |

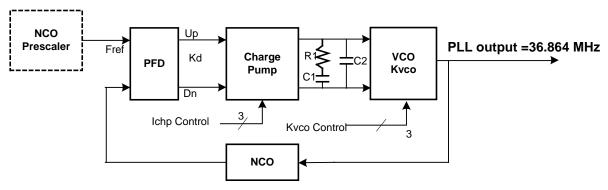

|   | 7.4<br>7.5    | PLL Circuit PLL System Timing Control                 | 42<br>15 |  |  |  |

| 0 |               |                                                       |          |  |  |  |

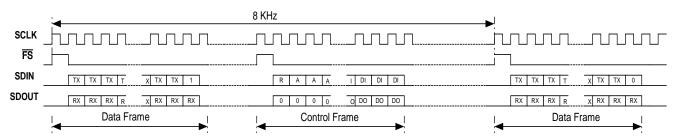

| 8 |               | Serial Interface                                      |          |  |  |  |

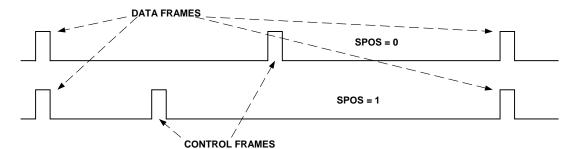

|   | 8.1<br>8.2    | Data and Control Frame Formats                        |          |  |  |  |

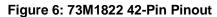

|   | 8.2<br>8.3    | Data and Control Frame Timing                         |          |  |  |  |

|   | 0.5           |                                                       | 40       |  |  |  |

|      | 8.4     | MicroDAA IN Master/Slave Configuration                           |    |

|------|---------|------------------------------------------------------------------|----|

|      | 8.5     | 73M1x22 Reset                                                    |    |

|      | 8.6     | 73M1x22 in Daisy Chain Configuration                             | 50 |

|      | 8.7     | MAFE Configuration Registers                                     |    |

|      | 8.8     | Slave Registers                                                  | 51 |

| 9    | Signa   | Processing                                                       | 52 |

|      | 9.1     | Transmit Path Signal Processing                                  |    |

|      |         | 9.1.1 General Description                                        |    |

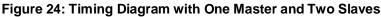

|      |         | 9.1.2 Total Transmit Path Response                               |    |

|      |         | 9.1.3 73M1x22 Transmit Spectrum                                  |    |

|      | 9.2     | Receive Path Signal Processing                                   |    |

|      |         | 9.2.1 General Description                                        |    |

|      |         | 9.2.2 Total Receive Path Response                                | 54 |

|      | 9.3     | Signal Control Functions                                         | 55 |

|      |         | 9.3.1 Transmit and Receive Level Control                         | 55 |

| 10   | Barrie  | r Information                                                    | 57 |

|      | 10.1    | Isolation Barrier                                                |    |

|      | 10.2    | Barrier Powered Options                                          |    |

|      |         | 10.2.1 Barrier Powered Operation                                 |    |

|      |         | 10.2.2 Line Powered Operations                                   |    |

|      | 10.3    | Synchronization of the Barrier                                   |    |

|      | 10.4    | Auxiliary A/D Converter                                          | 58 |

|      | 10.5    | Auto-Poll                                                        |    |

|      | 10.6    | Barrier Control Functions                                        |    |

|      | 10.7    | Line-Side Device Operating Modes                                 |    |

|      | 10.8    | Fail-Safe Operation of the Line-Side Device                      | 60 |

| 11   | Config  | gurable Direct Access Arrangement (DAA)                          | 61 |

|      | 11.1    | Pulse Dialing                                                    | 61 |

|      | 11.2    | DC Termination                                                   | 61 |

|      |         | 11.2.1 Current Limit Detection                                   |    |

|      | 11.3    | AC Termination                                                   |    |

|      | 11.4    | Billing Tone Rejection                                           |    |

|      | 11.5    | Trans-Hybrid Cancellation                                        | 65 |

|      | 11.6    | Direct Access Arrangement Control Functions                      |    |

|      | 11.7    | International Register Settings Table for DC and AC Terminations |    |

| 12   | Line S  | Sensing and Status                                               |    |

|      | 12.1    | Auxiliary A/D Converter                                          |    |

|      | 12.2    | Ring Detection                                                   | 70 |

|      | 12.3    | Line In Use Detection (LIU)                                      |    |

|      | 12.4    | Parallel Pick Up (PPU)                                           | 70 |

|      | 12.5    | Polarity Reversal Detection                                      |    |

|      | 12.6    | Off-hook Detection of Caller ID Type II                          |    |

|      | 12.7    | Voltage and Current Detection                                    |    |

|      | 12.8    | Under Voltage Detection (UVD)                                    |    |

|      | 12.9    | Over Voltage Detection (OVD)                                     |    |

|      |         | AC Signal Over Load Detection                                    |    |

|      | 12.11   | Over Current Detection (OID)                                     | 71 |

|      |         | Line Status Functions Control Functions                          |    |

| 13   | Loopt   | back and Testing Modes                                           | 75 |

| 14   | -       | mance                                                            |    |

|      | 14.1    | DC VI Characteristics                                            |    |

|      | 14.2    | Receive                                                          |    |

| 15   | Packa   | ge Layout                                                        | 79 |

| 16   |         | ing Information                                                  |    |

| -    |         | ct Information                                                   |    |

| 17   |         |                                                                  |    |

| Revi | ision H | istory                                                           | 82 |

# Figures

| Figure 1: Simple 73M1x22 Reference Block Diagram                                      | 6          |

|---------------------------------------------------------------------------------------|------------|

| Figure 2: 73M1902 20-Pin TSSOP Pinout                                                 |            |

| Figure 3: 73M1912 20-Pin TSSOP Pinout                                                 |            |

| Figure 4: 73M1902 32-Pin QFN Pinout                                                   |            |

| Figure 5: 73M1912 32-Pin QFN Pinout                                                   |            |

| Figure 6: 73M1822 42-Pin Pinout                                                       |            |

| Figure 7: MAFE Timing Diagram                                                         |            |

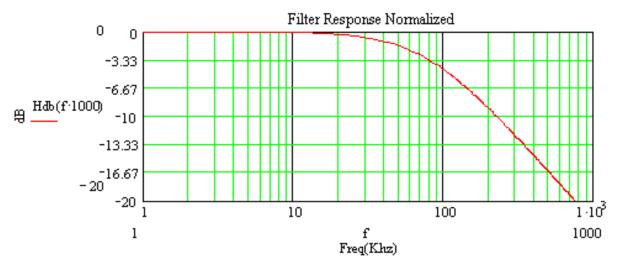

| Figure 8: Call Progress Monitor Frequency Response                                    |            |

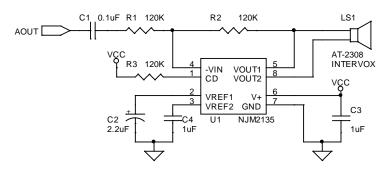

| Figure 9: Demo Board Circuit Connecting AOUT to a Speaker                             |            |

| Figure 10: Recommended Circuit for the 73M1922                                        |            |

| Figure 11: Recommended Circuit for the 73M1822                                        |            |

| Figure 12: Suggested Over-voltage Protection and EMI Suppression Circuit              |            |

| Figure 13: Clock Generation Block Diagram (assumes 8 kHz sample rate)                 |            |

| Figure 14: Crystal Oscillator with Configurable Load Current                          |            |

| Figure 15: Prescaler Block Diagram                                                    |            |

| Figure 16: PLL Block Diagram                                                          |            |

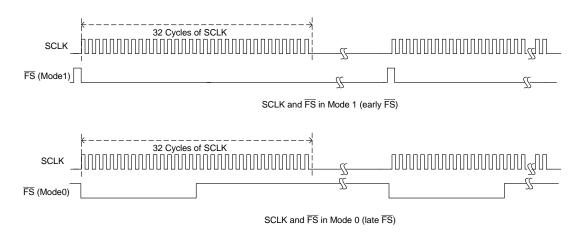

| Figure 17: Serial Port Timing Diagram                                                 |            |

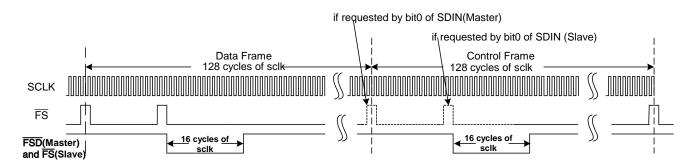

| Figure 18: Data and Control Frames Timing Diagram                                     |            |

| Figure 19: Control Frame Position versus SPOS.                                        |            |

| Figure 20: SCLK and $\overline{FS}$ with SCKM = 0                                     |            |

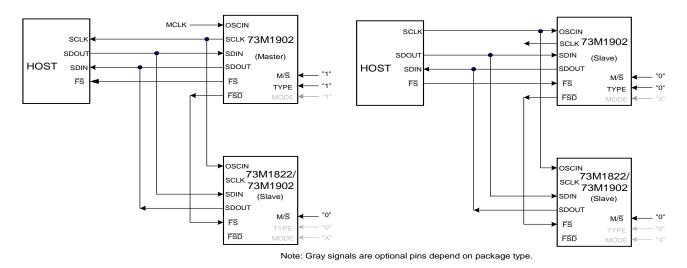

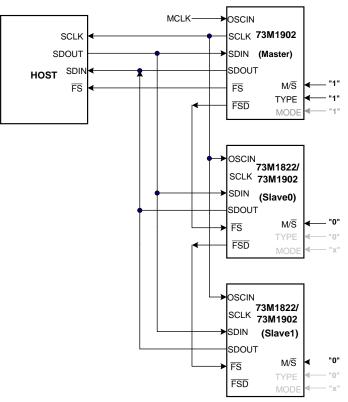

| Figure 21: Example Connections for Master and Slave Operation                         | . 40<br>49 |

| Figure 22: Master/Slave Serial Timing Diagram                                         |            |

| Figure 23: Daisy Chaining a Master and Two Slaves                                     | 50         |

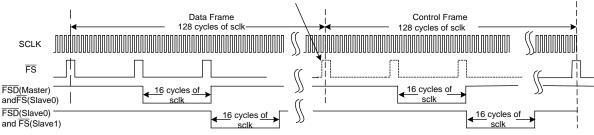

| Figure 24: Timing Diagram with One Master and Two Slaves                              |            |

| Figure 25: Transmit Path Overall Frequency Response to Fs (8 kHz)                     |            |

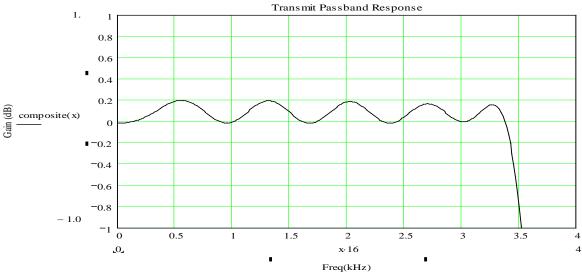

| Figure 26: Pass-Band Response of the Transmit Path                                    | 52         |

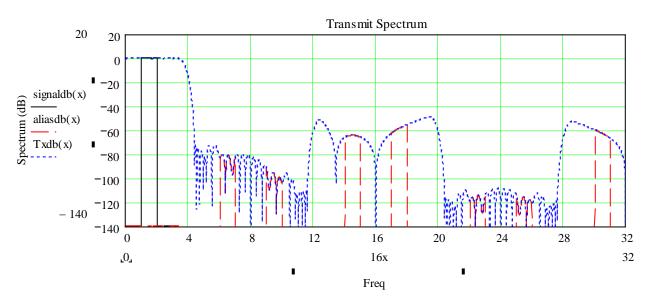

| Figure 27: Transmit Spectrum to 32 kHz.                                               |            |

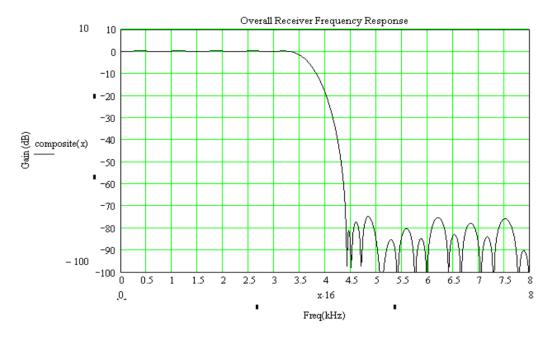

| Figure 28: Overall Frequency Response of the Receive Path                             |            |

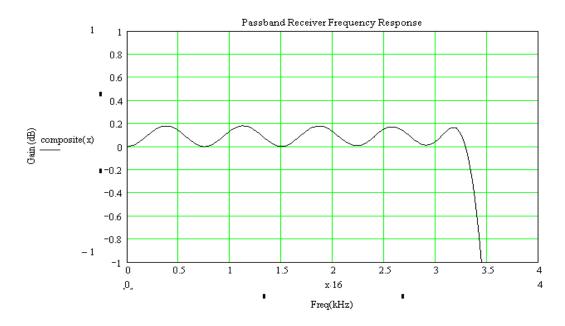

| Figure 29: Pass-band Response of the Overall Receive Path                             |            |

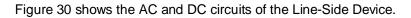

| Figure 30: Line-Side Device AC and DC Circuits                                        |            |

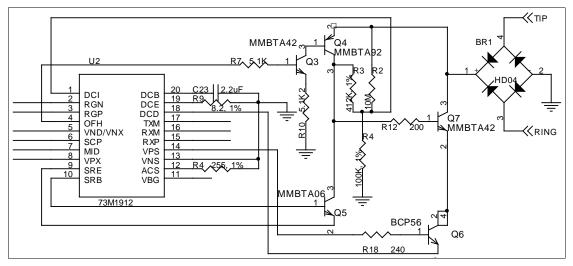

| Figure 31: DC-IV Characteristics                                                      |            |

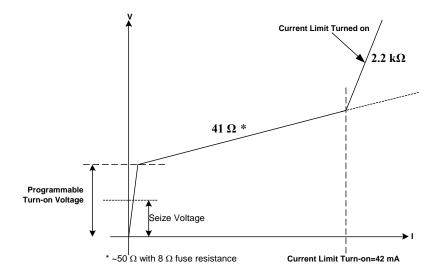

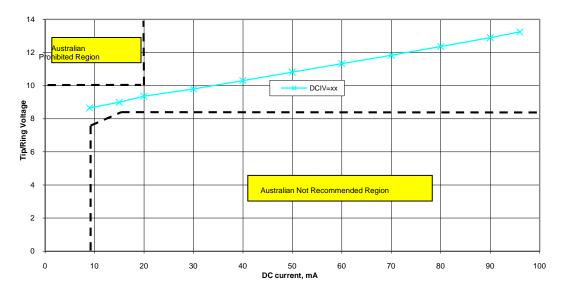

| Figure 32: Tip-Ring Voltage versus Current Using Different DCIV Settings              |            |

| Figure 33: Voltage versus Current in the Seize Mode is the Same for All DCIV Settings |            |

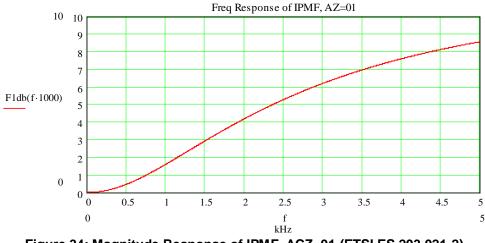

| Figure 34: Magnitude Response of IPMF, ACZ=01 (ETSI ES 203 021-2)                     |            |

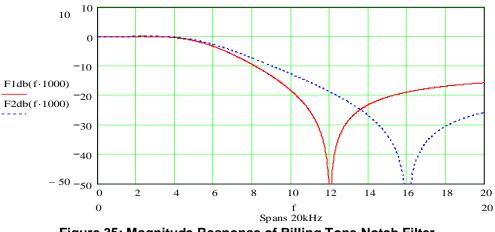

| Figure 35: Magnitude Response of Billing Tone Notch Filter                            |            |

| Figure 36: Loopback Modes Highlighted                                                 |            |

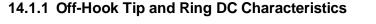

| Figure 37: Off-Hook Tip and Ring DC Characteristics                                   |            |

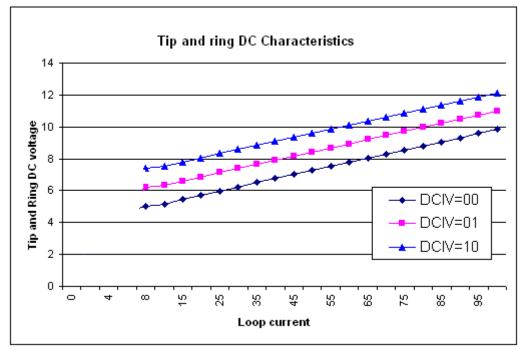

| Figure 38: ES 203 021-2 DC Mask with Current Limit Enabled                            | . / /      |

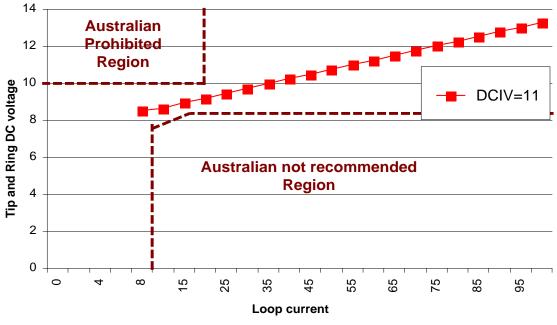

| Figure 39: Australian Hold State Characteristics                                      |            |

| Figure 39. Australian Hold State Characteristics                                      |            |

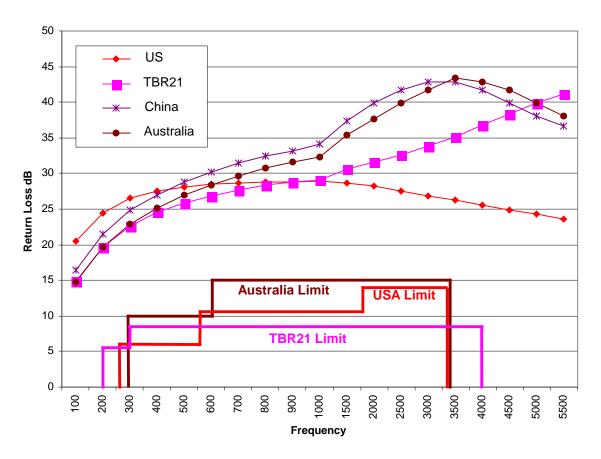

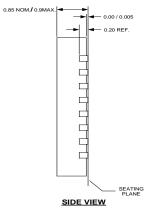

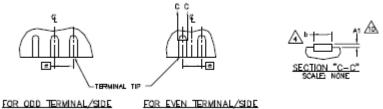

| Figure 40. Return Loss<br>Figure 41: 20-Pin TSSOP Package Dimensions                  |            |

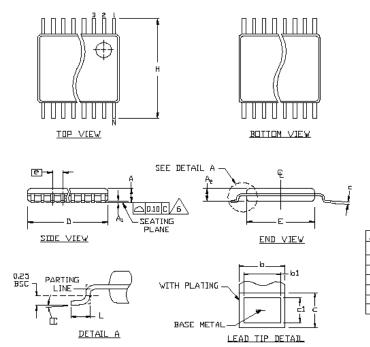

| Figure 41: 20-Pin TSSOF Package Dimensions                                            |            |

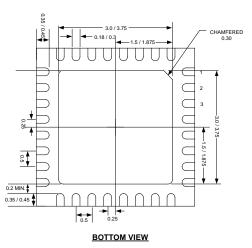

|                                                                                       |            |

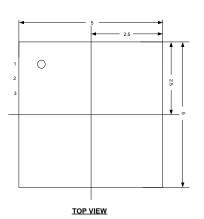

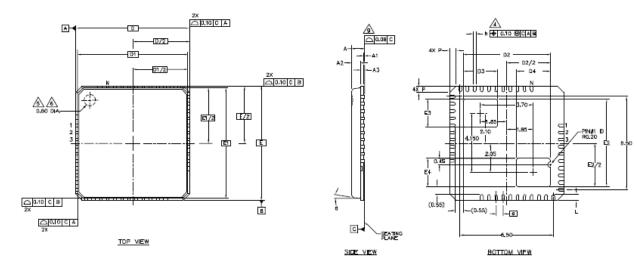

| Figure 43: 42-Pin QFN Package Dimensions                                              | . 80       |

# Tables

| Table 2: 73M1912 20-Pin TSSOP Pin Definitions.       10         Table 3: 73M1902 32-Pin QFN Pin Definitions.       11         Table 5: 73M1822 Pin QFN Pin Definitions       15         Table 6: Isolation Barrier Characteristics at 8 kHz Sample Rate.       17         Table 7: Absolute Maximum Device Ratings.       17         Table 8: Recommended Operating Conditions.       17         Table 9: DC Characteristics.       18         Table 11: Serial Data Port Timing at 8 kHz Sample Rate.       19         Table 11: Cefference Voltage Specification.       19         Table 12: Component Values for the Speaker Driver.       20         Table 13: Call Progress Monitor Specification       21         Table 14: Line-Side Absolute Maximum Ratings.       22         Table 15: VBG Specifications       22         Table 16: Waximum Transmit Levels.       23         Table 18: Transmit Path.       24         Table 19: Receive Path.       25         Table 20: Transmit Levels.       26         Table 21: Receive Notch Filter.       26         Table 22: Over-Voltage Detector.       27         Table 23: Over-Unald Detector.       27         Table 24: Under-Voltage Detector.       27         Table 25: Over-Load Detector.       27         Table 24: Compat                                                                                                                           | Table 1: 73M1902 20-Pin TSSOP Pin Definitions                       |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|

| Table 4: 73M1912 32-Pin QFIN PIn Definitions13Table 5: 73M1822 Pin Definitions15Table 6: Isolation Barrier Characteristics at 8 KHz Sample Rate17Table 7: Absolute Maximum Device Ratings17Table 9: DC Characteristics17Table 9: DC Characteristics18Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 KHz Sample Rate19Table 11: Cafference Voltage Specifications19Table 12: Component Values for the Speaker Driver20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels23Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path24Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Path25Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Linder-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 28: Compatible Pulse Transformer Sources32Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43 <td>Table 2: 73M1912 20-Pin TSSOP Pin Definitions</td> <td>. 10</td>                                          | Table 2: 73M1912 20-Pin TSSOP Pin Definitions                       | . 10 |

| Table 5: 73M1822 Pin Definitions15Table 6: Isolation Barrier Characteristics at 8 kHz Sample Rate17Table 7: Absolute Maximum Device Ratings17Table 8: Recommended Operating Conditions17Table 8: Recommended Operating Conditions17Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 kHz Sample Rate19Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels.23Table 17: Receive Path24Table 19: Receive Path25Table 21: Receive Path26Table 22: Transmit Hybrid Cancellation Characteristics26Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Cover-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 29: Transformer Characteristics32Table 31: Alphabetical Bit Map.33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24. S76 MHz44Table 34: Clock Generation Register Settings for Fxtal = 24. S76 MHz43Table 35: Clock Generation Register Settings for Fxtal = 27 MHz43Table 36: Clock Generation Register Settings for Fxtal = 24. S76 MHz44Table 37: P                                                                                              | Table 3: 73M1902 32-Pin QFN Pin Definitions                         | . 11 |

| Table 6: Isolation Barrier Characteristics at 8 kHz Sample Rate.       17         Table 7: Absolute Maximum Device Ratings       17         Table 8: Recommended Operating Conditions       17         Table 9: DC Characteristics       18         Table 10: Serial Data Port Timing at 8 kHz Sample Rate.       19         Table 11: Reference Voltage Specifications       19         Table 12: Component Values for the Speaker Driver       20         Table 13: Call Progress Monitor Specification       21         Table 14: Line-Side Absolute Maximum Ratings       22         Table 15: VBG Specifications       22         Table 16: Maximum Transmit Levels.       23         Table 17: Maximum DC Transmit Levels.       23         Table 18: Transmit Path.       24         Table 20: Transmit Hybrid Cancellation Characteristics.       26         Table 22: Over-Voltage Detector       27         Table 23: Over-Current Detector       27         Table 24: Cheerve Notch Filter.       26         Table 25: Over-Load Detector       27         Table 26: Reference Bill of Materials for T3M1822/T3M1922       30         Table 28: Compatible Pulse Transformer Sources       32         Table 29: Transformer Characteristics       32         Table 29: Transformer Characteristics       32<                                                                                                 | Table 4: 73M1912 32-Pin QFN Pin Definitions                         | . 13 |

| Table 7: Absolute Maximum Device Ratings17Table 8: Recommended Operating Conditions17Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 kHz Sample Rate19Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Inasmit Path24Table 18: Transmit Path24Table 20: Cover-Curent Hybrid Cancellation Characteristics26Table 21: Receive Path25Table 22: Over-Voltage Detector27Table 23: Over-Curent Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Over-Load Detector27Table 27: Reference Bill of Materials for 73M1822/73M192230Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 31: Alphabetical Bit Map33Table 31: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 216 MHz43Table 33: Clock Generation Register Settings for Fxtal = 216 MHz43Table 33: Signal Control55Table 34: Maphabetical Bit Map34Table 35: Clock Generation Register Settings for Fxtal = 27                                                                                                                          |                                                                     |      |

| Table 8: Recommended Operating Conditions.17Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 kHz Sample Rate.19Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver.20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels.22Table 17: Maximum DC Transmit Levels.23Table 19: Receive Path24Table 19: Receive Path26Table 20: Transmit Hybrid Cancellation Characteristics.26Table 22: Over-Voltage Detector.27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector.27Table 25: Over-Load Detector27Table 26: Corrent Bill of Materials for T3Mt822/T3M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Cock Generation Register Settings for Fxtal = 27 MHz43Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 33: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 35: Clock Generation Register Settings for Fxta                                                                   | Table 6: Isolation Barrier Characteristics at 8 kHz Sample Rate     | . 17 |

| Table 8: Recommended Operating Conditions.17Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 kHz Sample Rate.19Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver.20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels.22Table 17: Maximum DC Transmit Levels.23Table 19: Receive Path24Table 19: Receive Path26Table 20: Transmit Hybrid Cancellation Characteristics.26Table 22: Over-Voltage Detector.27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector.27Table 25: Over-Load Detector27Table 26: Corrent Bill of Materials for T3Mt822/T3M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Cock Generation Register Settings for Fxtal = 27 MHz43Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 33: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 35: Clock Generation Register Settings for Fxta                                                                   | Table 7: Absolute Maximum Device Ratings                            | . 17 |

| Table 9: DC Characteristics18Table 10: Serial Data Port Timing at 8 kHz Sample Rate.19Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver.20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path.24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Path26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Cover-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map.34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 9.216 MHz.43Table 34: Clock Generation Register Settings for Fxtal = 24.50 MHz.44Table 35: Clock Generation Register Settings for Fxtal = 24.50 MHz.43Table 36: Clock Generation Register Settings for Fxtal = 24.50 MHz.43Table 36: Clock Generation Register Settings for Fxtal = 24.50 MHz.43Table 36: Clock Generation Register Settings for                                                                   |                                                                     |      |

| Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Path25Table 22: Over-Voltage Detector27Table 23: Over-Voltage Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 29: Compatible Pulse Transformer Sources32Table 32: Clock Generation Register Map.34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 34: Clock Generation Register Settings for Fxtal = 27.000 MHz44Table 35: Clock Generation Register Settings for Fxtal = 24.300 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.35 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.55 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.55 MHz44 <td></td> <td></td>                                                           |                                                                     |      |

| Table 11: Reference Voltage Specifications19Table 12: Component Values for the Speaker Driver20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Path25Table 22: Over-Voltage Detector27Table 23: Over-Voltage Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 29: Compatible Pulse Transformer Sources32Table 32: Clock Generation Register Map.34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 34: Clock Generation Register Settings for Fxtal = 27.000 MHz44Table 35: Clock Generation Register Settings for Fxtal = 24.300 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.35 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.55 MHz44Table 36: Clock Generation Register Settings for Fxtal = 2.55 MHz44 <td>Table 10: Serial Data Port Timing at 8 kHz Sample Rate</td> <td>. 19</td> | Table 10: Serial Data Port Timing at 8 kHz Sample Rate              | . 19 |

| Table 12: Component Values for the Speaker Driver.20Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels.23Table 17: Maximum DC Transmit Levels.23Table 18: Transmit Path.24Table 19: Receive Path26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector.27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 29: Cock Generation Register Map.33Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 35: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 37: PLL System Timing Controls55Table 40: Transmit Gain Control55Table 41: Receive Gain Control55Table 42: DAc Control Functions55Table 44: DAA Control Functions55Table 44: DAA Control Functions55Table 44: DAA Control Functions55Table 44: DAA Control Functions56Table 45: Recommened Register Settin                                                                                                                                                    | Table 11: Reference Voltage Specifications                          | . 19 |

| Table 13: Call Progress Monitor Specification21Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path.24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 27. SMHz44Table 35: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 37: PLL System Timing Control55Table 37: Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Control55Table 37: PLL System Timing Control55Table 37: PLL System Timing Control55Table 44: DAA Control Functions59Table 43: Trans-Hybrid Cancellation65Table 43: Tran                                                                                                                         | Table 12: Component Values for the Speaker Driver                   | . 20 |

| Table 14: Line-Side Absolute Maximum Ratings22Table 15: VBG Specifications22Table 16: Maximum Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path.24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 25: Cover-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.576 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls55Table 38: Behavior of SCLK under SCKM48Table 39: Glock Generation Register Settings for Fxtal = 25.35 MHz44Table 39: Table 40: Transmit Gain Control56Table 41: Receive Gain Control55Table 43: Trans-Hybrid Cancellation55Table 44: DAA Control Functions55Tab                                                                                                                         |                                                                     |      |

| Table 15: VBG Specifications22Table 17: Maximum DC Transmit Levels22Table 17: Maximum DC Transmit Levels23Table 18: Transmit Path24Table 19: Receive Path26Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 26: Reference Bill of Materials for Figure 1231Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Clock Generation Register Settings for Fxtal = 27 MHz43Table 32: Clock Generation Register Settings for Fxtal = 24.076 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.576 MHz44Table 37: PLL System Timing Controls45Table 37: PLL System Timing Controls55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: DAA Control Functions55Table 43: Trans-Hybrid Cancellation56Table 44: DAA Control Functions55Table 44: DAA Control Functions55Table 44: Line Sensing Control Functions56Table 44: Line Sensing Control Functions55Table 44: Line Sensing Control Functions <t< td=""><td></td><td></td></t<>                                                                                              |                                                                     |      |

| Table 16: Maximum Transmit Levels.22Table 17: Maximum DC Transmit Levels.23Table 18: Transmit Path.24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics.26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector.27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector.27Table 25: Over-Load Detector.27Table 26: Reference Bill of Materials for 73M1822/73M1922.30Table 27: Reference Bill of Materials for Figure 12.31Table 28: Compatible Pulse Transformer Sources32Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 27 MHz43Table 34: Clock Generation Register Settings for Fxtal = 27 MHz43Table 35: Clock Generation Register Settings for Fxtal = 27 MHz43Table 36: Clock Generation Register Settings for Fxtal = 27 MHz43Table 36: Clock Generation Register Settings for Fxtal = 27 MHz43Table 36: Clock Generation Register Settings for Fxtal = 27 MHz43Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls55Table 40: Transmit Gain Control55Table 4                                                                   |                                                                     |      |

| Table 18: Transmit Path.24Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics.26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector.27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector.27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M1922.30Table 26: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map.33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls55Table 40: Transmit Gain Control55Table 41: Receive Gain Control55Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions59Table 44: Line Sensing Control Functions72                                                                                                                                                                                                                                     |                                                                     |      |

| Table 19: Receive Path25Table 20: Transmit Hybrid Cancellation Characteristics.26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Over-Load Detector27Table 27: Reference Bill of Materials for 73M1822/73M192230Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 43: Trans-Hybrid Cancellation55Table 44: DAA Control Functions56Table 43: Trans-Hybrid Cancellation55Table 44: DAA Control Functions59Table 45: Line Sensing Control Functions55Table 44: Line Sensing Control Functions55Table 45: Line Sensing Control Functions55Table 46: Line Sensing Control                                                                                                                         | Table 17: Maximum DC Transmit Levels                                | . 23 |

| Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.500 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 24.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 30: Signal Control Functions55Table 31: Trans-Hybrid Cancellation55Table 32: Trans-Hybrid Cancellation56Table 34: Trans-Hybrid Cancellation56Table 34: Clock Register Settings for International Compatibility69Table 34: Transmit Gain Control55Table 34: Transmit Gain Control55Table 34: Transmit Gain Control55Table 44: DAA Control Functions59Table 44: DAA Control                                                                                               | Table 18: Transmit Path                                             | .24  |

| Table 20: Transmit Hybrid Cancellation Characteristics26Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 24.500 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 24.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 30: Signal Control Functions55Table 31: Trans-Hybrid Cancellation55Table 32: Trans-Hybrid Cancellation56Table 34: Trans-Hybrid Cancellation56Table 34: Clock Register Settings for International Compatibility69Table 34: Transmit Gain Control55Table 34: Transmit Gain Control55Table 34: Transmit Gain Control55Table 44: DAA Control Functions59Table 44: DAA Control                                                                                               |                                                                     |      |

| Table 21: Receive Notch Filter26Table 22: Over-Voltage Detector27Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.000 MHz43Table 36: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 37: PLL System Timing Controls45Table 39: Signal Control Functions55Table 39: Signal Control Functions55Table 40: Trans-Hybrid Cancellation55Table 42: Barrier Control Functions56Table 44: DAA Control Functions55Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions65                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |      |

| Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions56Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                      |                                                                     |      |

| Table 23: Over-Current Detector27Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions56Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                      | Table 22: Over-Voltage Detector                                     | . 27 |

| Table 24: Under-Voltage Detector27Table 25: Over-Load Detector27Table 26: Reference Bill of Materials for 73M1822/73M192230Table 27: Reference Bill of Materials for Figure 1231Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |      |

| Table 25: Over-Load Detector.27Table 26: Reference Bill of Materials for 73M1822/73M1922.30Table 27: Reference Bill of Materials for Figure 12.31Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map.33Table 31: Alphabetical Bit Map.34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz.43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz.43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      |

| Table 26: Reference Bill of Materials for 73M1822/73M1922                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |      |

| Table 27: Reference Bill of Materials for Figure 12.31Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map.33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     |      |

| Table 28: Compatible Pulse Transformer Sources32Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |      |

| Table 29: Transformer Characteristics32Table 30: Control and Status Register Map33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |      |

| Table 30: Control and Status Register Map.33Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz.43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz.43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |      |

| Table 31: Alphabetical Bit Map34Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |      |

| Table 32: Clock Generation Register Settings for Fxtal = 27 MHz43Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 31: Alphabetical Bit Map                                      | . 34 |

| Table 33: Clock Generation Register Settings for Fxtal = 24.576 MHz.43Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz.43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |      |

| Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz.43Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions.65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                     |      |

| Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz.44Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions.65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 34: Clock Generation Register Settings for Fxtal = 9.216 MHz. | . 43 |

| Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz.44Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions.65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 35: Clock Generation Register Settings for Fxtal = 24.000 MHz | . 44 |

| Table 37: PLL System Timing Controls45Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions.65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 36: Clock Generation Register Settings for Fxtal = 25.35 MHz  | . 44 |

| Table 38: Behavior of SCLK under SCKM.48Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |      |

| Table 39: Signal Control Functions55Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |      |

| Table 40: Transmit Gain Control55Table 41: Receive Gain Control56Table 42: Barrier Control Functions59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |      |

| Table 41: Receive Gain Control56Table 42: Barrier Control Functions.59Table 43: Trans-Hybrid Cancellation65Table 44: DAA Control Functions.65Table 45: Recommended Register Settings for International Compatibility69Table 46: Line Sensing Control Functions.72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |      |