### **General Description**

The MAX6877/MAX6878/MAX6879 multivoltage power trackers/sequencers/supervisors monitor up to three system voltages and provide proper power-up and power-down control for systems requiring voltage tracking or sequencing. These devices ensure controlled voltage tracking within a specified range or sequencing in the proper order as system power supplies are enabled. The MAX6877/MAX6878/MAX6879 generate all required voltages and timing to control up to three external n-channel pass FETs for the OUT1/OUT2/OUT3 supply voltages (see the *Selector Guide* for different features of each device).

The MAX6877/MAX6878/MAX6879 feature adjustable undervoltage thresholds for each input supply. When all the voltages are above these adjustable thresholds, the devices turn on the external n-channel MOSFETs to either sequence or track the voltages to the system. During voltage-tracking mode, the voltage at the GATE of each MOSFET is increased to slowly bring up all supplies at a controlled slew rate. The MAX6877/MAX6878/MAX6879 feature an autoretry or latch-off mode with capacitor-adjusted timing.

These devices also provide a controlled power-down (tracking mode) when the system shuts off in an orderly manner. When an unexpected fault occurs, the outputs are all pulled down simultaneously with an internal  $100\Omega$  pulldown to help discharge capactive loads at the MOSFET's source. The MAX6877/MAX6878/MAX6879 feature independent internal charge pumps to fully enhance the external FETs for low-voltage drop at highpass current. The MAX6877 and MAX6878 also feature a power-good output with a selectable timeout period that can be used for system reset.

The MAX6877/MAX6878/MAX6879 are available in small 4mm x 4mm 24-pin and 16-pin thin QFN packages and are fully specified over the -40°C to +85°C extended operating temperature range.

#### **Applications**

Multivoltage Systems Networking Systems Telecom Storage Equipment

Servers/Workstations

Selector Guide appears at end of data sheet.

\_\_\_\_\_Features

- Pin-Selectable Tracking or Sequencing Control for Up to Three Supply Voltages

- ♦ Capacitor-Adjustable Power-Up/Down Tracking Slew Rate

- ♦ Capacitor-Adjustable Power-Up Sequencing Delay

- ♦ Internal Charge Pumps to Enhance External n-Channel FETs

- Capacitor-Adjustable Timeout Period Power-Good Output (MAX6877/MAX6878)

- ◆ Adjustable Undervoltage Lockout or Logic-Enable Input

- ♦ Internal 100Ω Pulldown for Each Output to Discharge Capacitive Load Quickly

- ♦ 0.5V to 5.5V Nominal IN\_/OUT\_ Range

- ♦ 2.7V to 5.5V Operating Voltage Range

- ♦ Immune to Short Voltage Transients

- Small 4mm x 4mm 24-Pin or 16-Pin Thin QFN Packages

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|-------------|----------------|-----------------|-------------|

| MAX6877ETG+ | -40°C to +85°C | 24 Thin QFN     | T2444-4     |

Ordering Information continued at end of data sheet.

+Denotes lead-free package.

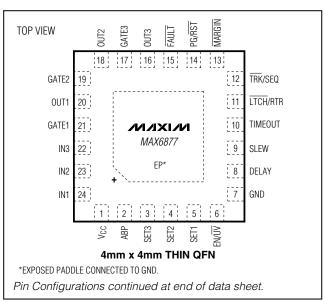

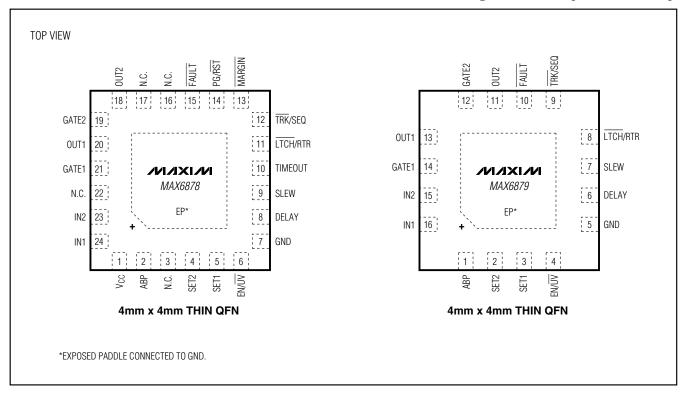

### **Pin Configurations**

\_\_\_\_\_\_ Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

IN1, IN2, IN3, V<sub>CC</sub> .....-0.3V to +6V

(All voltages referenced to GND, unless otherwise noted.)

| ABP                       |                                                                   |

|---------------------------|-------------------------------------------------------------------|

| 0.3V to the               | highest of V <sub>IN1</sub> - V <sub>IN3</sub> or V <sub>CC</sub> |

| SET1, SET2, SET3          | 0.3V to +6V                                                       |

| GATE1, GATE2, GATE3       | 0.3V to +12V                                                      |

| OUT1, OUT2, OUT3          |                                                                   |

| LTCH/RTR, TRK/SEQ, MARGIN |                                                                   |

| FAULT, PG/RST, EN/UV      | 0.3V to +6V                                                       |

| DELAY, SLEW, TIMEOUT      | 0.3V to +6V                                                       |

| OUT_ Current              | ±50mA                                                             |

| GND Current               | ±50mA                                                             |

| Input/Output Current (all pins except          |                |

|------------------------------------------------|----------------|

| OUT_ and GND)                                  | ±20mA          |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

| 16-Pin 4mm x 4mm Thin QFN                      |                |

| (derate 16.9mW/°C above +70°C)                 | 1349mW         |

| 24-Pin 4mm x 4mm Thin QFN                      |                |

| (derate 20.8mW/°C above +70°C)                 |                |

| Operating Temperature Range                    | 40°C to +85°C  |

| Storage Temperature Range                      | 65°C to +150°C |

| Maximum Junction Temperature                   |                |

| Lead Temperature (soldering, 10s)              | +300°C         |

|                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub>, IN1, IN2, or IN3 = +2.7V to +5.5V, EN/UV = MARGIN = ABP, T<sub>A</sub> = -40°C to +85°C, unless otherwise specified. Typical values are at  $T_A = +25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER                                             | SYMBOL              | CONDITIONS                                                                                                      | MIN    | TYP   | MAX    | UNITS |

|-------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|

| Operating Voltage Range                               | Vcc                 | Voltage on ABP (the highest of V <sub>CC</sub> or IN_) to ensure that PG/RST and FAULT are valid and GATE_ = 0V | 1.4    |       |        | V     |

|                                                       |                     | Voltage on ABP (the highest of V <sub>CC</sub> or IN_) to ensure the device is fully operational                | 2.7    |       | 5.5    |       |

| Supply Current                                        | Icc                 | V <sub>CC</sub> = 5.5V, IN1 = IN2 = IN3 = 3.3V, no load                                                         |        | 1.1   | 1.8    | mA    |

| SET_Threshold Range                                   | V <sub>TH</sub>     | SET_ falling, T <sub>A</sub> = +25°C                                                                            | 0.4925 | 0.5   | 0.5075 | V     |

| SET_ Threshold Harige                                 | VIH                 | SET_ falling, $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                                            | 0.4875 | 0.5   | 0.5125 | v     |

| SET_ Threshold Hysteresis                             | V <sub>TH_HYS</sub> | SET_ rising                                                                                                     |        | 0.5   |        | %     |

| SET_ Input Current                                    | ISET                | SET_ = 0.5V                                                                                                     | -100   |       | +100   | nA    |

| EN/UV Input Voltage                                   | V <sub>EN_R</sub>   | Input rising                                                                                                    |        | 1.286 |        | V     |

| Livov input voltage                                   | V <sub>EN_F</sub>   | Input falling                                                                                                   | 1.22   | 1.25  | 1.28   | ٧     |

| EN/UV Input Current                                   | I <sub>EN</sub>     |                                                                                                                 | -5     |       | +5     | μΑ    |

| EN/UV Input Pulse Width                               | t <sub>EN</sub>     | EN/UV falling, 100mV overdrive                                                                                  | 7      |       |        | μs    |

| DELAY, TIMEOUT Output Current                         | ID                  | (Notes 2, 3)                                                                                                    | 2.12   | 2.5   | 2.88   | μΑ    |

| DELAY, TIMEOUT Threshold<br>Voltage                   |                     | V <sub>CC</sub> = 3.3V                                                                                          |        | 1.25  |        | V     |

| SLEW Output Current (Note 4)                          | Is                  |                                                                                                                 | 22.5   | 25    | 27.5   | μΑ    |

| Track/Sequence Slew-Rate<br>Timebase Accuracy         | SR                  | C <sub>SLEW</sub> = 200pF (Note 4)                                                                              | -15    |       | +15    | %     |

| Timebase/C <sub>SLEW</sub> Ratio                      |                     | 100pF < C <sub>SLEW</sub> < 1nF (Note 4)                                                                        |        | 104   |        | kΩ    |

| Slew-Rate Accuracy during Power-<br>Up and Power-Down |                     | C <sub>SLEW</sub> = 200pF, ABP = 5.5V (Note 4)                                                                  | -50    |       | +50    | %     |

| Power-Good Threshold                                  | V <sub>TH_PG</sub>  | V <sub>OUT</sub> _ falling                                                                                      | 91.5   | 92.5  | 93.5   | %     |

/VI/IXI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

(VCC, IN1, IN2, or IN3 =  $\pm$ 2.7V to  $\pm$ 5.5V, EN/UV = MARGIN = ABP, T<sub>A</sub> =  $\pm$ 40°C to  $\pm$ 85°C, unless otherwise specified. Typical values are at T<sub>A</sub> =  $\pm$ 25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL                | CONDITIONS                                                                                                    | MIN          | TYP          | MAX          | UNITS        |

|-----------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|

| Power-Good Threshold Hysteresis               | V <sub>H</sub> YS_PG  | V <sub>OUT</sub> _ rising                                                                                     |              | 0.5          |              | %            |

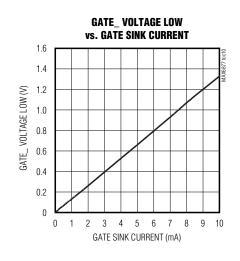

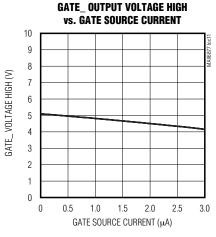

| GATE_ Output High                             | Vgoh                  | ISOURCE = 0.5µA                                                                                               | IN_ +<br>4.2 | IN_ +<br>5.0 | IN_ +<br>5.8 | V            |

| GATE_ Pullup Current                          | I <sub>GUP</sub>      | During power-up and power-down, VGATE_ = 1V                                                                   | 2.5          | 4            |              | μΑ           |

| CATE Dulldown Current                         | IGD                   | During power-up and power-down, VGATE_ = 5V                                                                   | 2.5          | 4            |              | μA           |

| GATE_ Pulldown Current                        | lone                  | When disabled, V <sub>GATE</sub> = 5V, V <sub>IN</sub> ≥ 2.7V                                                 |              | 9.5          |              | mA           |

|                                               | IGDS                  | When disabled, V <sub>GATE</sub> = 5V, V <sub>IN</sub> ≥ 4V                                                   |              | 20           |              | IIIA         |

| SET_ to GATE_ Delay                           | td-gate               | SET falling, 25mV overdrive                                                                                   |              | 6            |              | μs           |

| FAULT, PG/RST Output Low                      | VoL                   | V <sub>IN</sub> _ ≥ 2.7V, I <sub>SINK</sub> = 1mA, output asserted                                            |              |              | 0.3          | <sub>V</sub> |

| TAGET, Taynor Gulput Low                      | VOL                   | V <sub>IN</sub> _ ≥ 4.0V, I <sub>SINK</sub> = 4mA, output asserted                                            |              |              | 0.4          | V            |

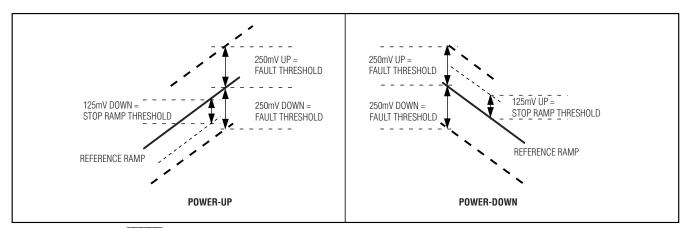

| Tracking Differential Voltage Stop<br>Ramp    | V <sub>TRK</sub>      | Differential between each of the OUT_ and the ramp voltage during power-up and power-down, Figure 10 (Note 5) | 75           | 125          | 180          | mV           |

| Tracking Differential Fault Voltage           | V <sub>TRK_</sub> F   | Differential between each of the OUT_ and the ramp voltage, Figure 10 (Note 5)                                | 200          | 250          | 310          | mV           |

| Tracking Differential Voltage<br>Hysteresis   |                       |                                                                                                               |              | 20           |              | %            |

| Power-Low Threshold                           | V <sub>TH_PL</sub>    | OUT_ falling                                                                                                  | 125          | 142          | 170          | mV           |

| Power-Low Hysteresis                          | V <sub>TH_PLHYS</sub> | OUT_ rising                                                                                                   |              | 10           |              | mV           |

| OUT to GND Pulldown Impedance                 |                       | V <sub>ABP</sub> > 2.7V (Note 6)                                                                              |              | 100          |              | Ω            |

| MARGIN, TRK/SEQ, LTCH/RTR<br>Pullup Current   | I <sub>IN</sub>       |                                                                                                               | 7            | 10           | 13           | μΑ           |

| MARGIN, TRK/SEQ, LTCH/RTR                     | V <sub>IL</sub>       |                                                                                                               |              |              | 0.8          | V            |

| Input Voltage                                 | VIH                   |                                                                                                               | 2.0          |              |              | v            |

| MARGIN, TRK/SEQ, LTCH/RTR<br>Glitch Rejection |                       |                                                                                                               |              | 100          |              | ns           |

- Note 1: Specifications guaranteed for the stated global conditions. 100% production tested at T<sub>A</sub> = +25°C and T<sub>A</sub> = +85°C. Specifications at T<sub>A</sub> = -40°C to +85°C are guaranteed by design. These devices meet the parameters specified when at least one of V<sub>CC</sub>, IN1/IN2/IN3 is between 2.7V to 5.5V, while the remaining IN1/IN2/IN3 are between 0 and 5.5V.

- Note 2: A current I<sub>D</sub> = 2.5µA ±15% is generated internally and is used to set the DELAY and TIMEOUT periods and used as a reference for t<sub>DELAY</sub> and t<sub>TIMEOUT</sub>.

- Note 3: The total DELAY is t<sub>DELAY</sub> = 200ms + (500kΩ x C<sub>DELAY</sub>). Leave DELAY unconnected for 200μs delay. The total TIMEOUT is t<sub>TIMEOUT</sub> = 200μs + (500kΩ x C<sub>TIMEOUT</sub>). Leave TIMEOUT unconnected for 200μs timeout.

- Note 4: A current Is = 25µA ±10% is generated internally and used as a reference for tFAULT, tRETRY, and slew rate.

- Note 5: During power-up, only the condition OUT\_ < ramp VTRK is checked in order to stop the ramp. However, both conditions OUT\_ < ramp VTRK\_F and OUT\_ > ramp + VTRK\_F cause a fault. During power-down, only the condition OUT > ramp + VTRK is checked in order to stop the ramp. However, both conditions OUT\_ < ramp VTRK\_F and OUT\_ > ramp + VTRK\_F cause a fault (see Figure 10). Therefore, if OUT1, OUT2, and OUT3 (during power-up tracking and power-down) differ by more than 2 x VTRK\_F, a fault condition is asserted.

- **Note 6:** A 100Ω pulldown to GND activated by a fault condition. See the *Internal Pulldown* section.

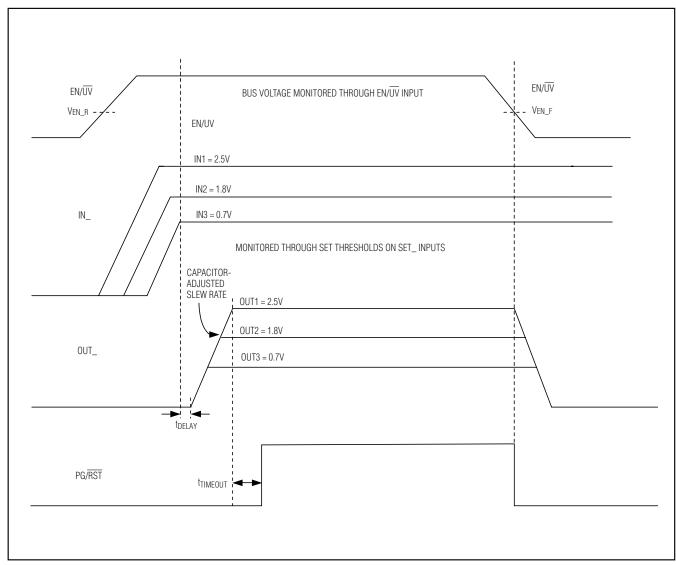

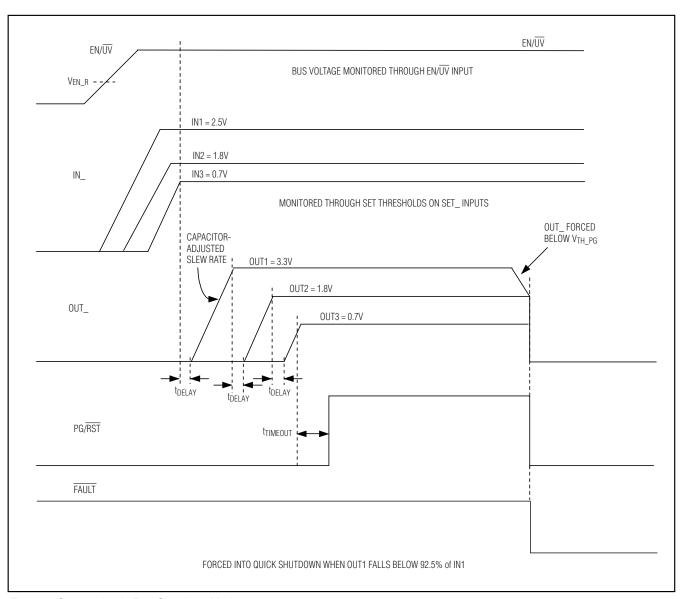

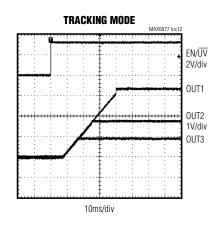

Figure 1. Tracking Timing Diagram in Normal Mode

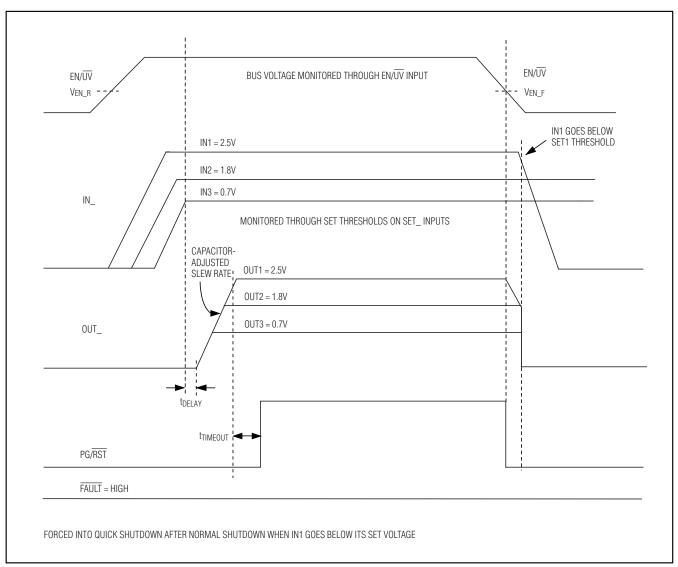

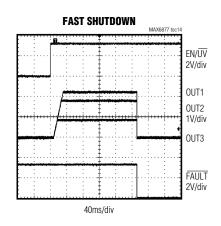

Figure 2. Tracking in Fast Shutdown Mode

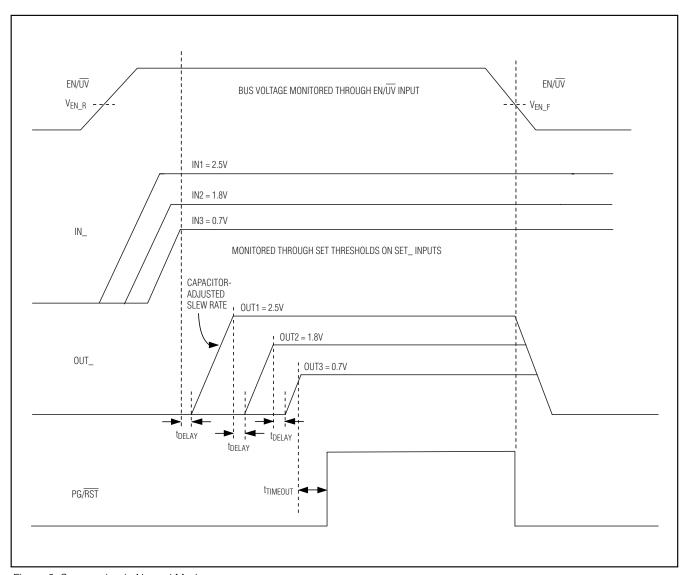

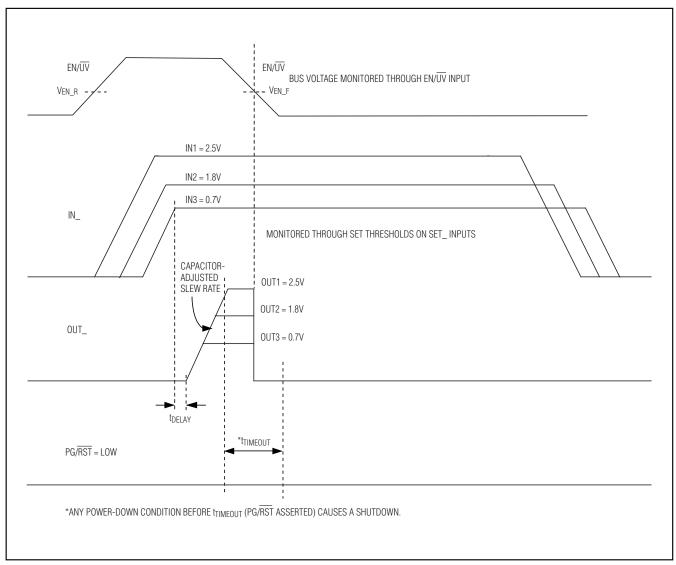

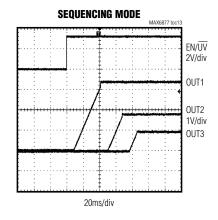

Figure 3. Sequencing in Normal Mode

Figure 4. Sequencing in Fast Shutdown Mode

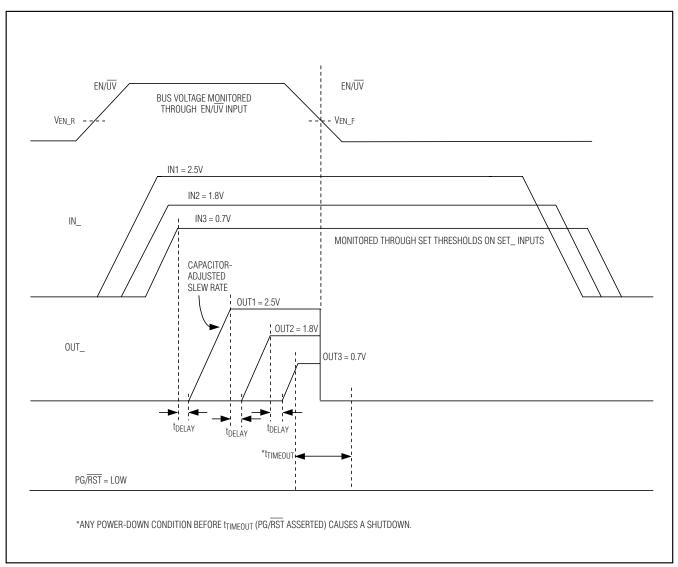

Figure 5. Timing Diagram (Aborted Tracking)

Figure 6. Timing Diagram (Aborted Sequencing)

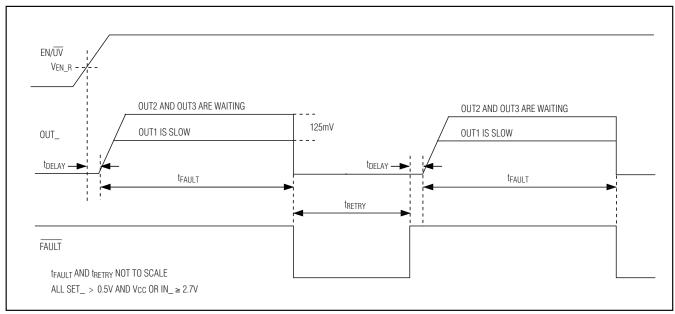

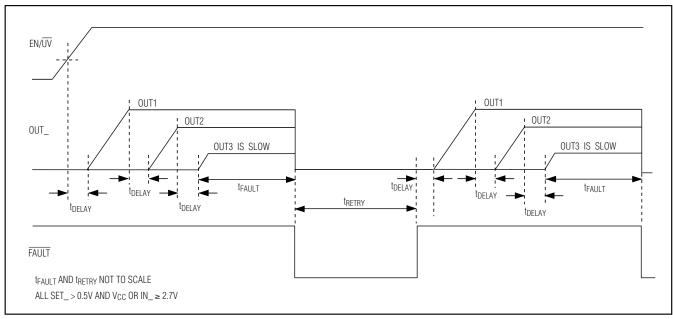

Figure 7. tFAULT and tRETRY Timing Diagram in Tracking

Figure 8. tFAULT and tRETRY Timing Diagram in Sequencing

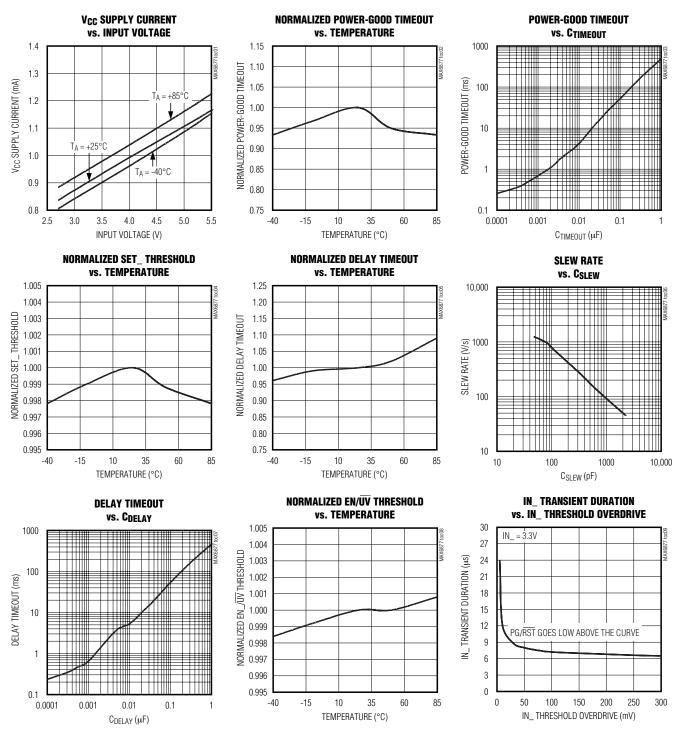

### Typical Operating Characteristics

(V<sub>CC</sub> = 2.7V to 5.5V, C<sub>SLEW</sub> = 200pF, EN =  $\overline{\text{MARGIN}}$  = ABP, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{CC} = 2.7V \text{ to } 5.5V, C_{SLEW} = 200pF, EN = \overline{MARGIN} = ABP, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN     |                  | PIN     |          | PIN                                                                                                                                                                                                                                                                                                                                                          |  | FINISTION |

|---------|------------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------|

| MAX6877 | MAX6878          | MAX6879 | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |  |           |

| 1       | 1                | _       | Vcc      | Optional Supply Voltage Input. Connect $V_{CC}$ to an alternate (i.e., always-on) supply if desired. Leave $V_{CC}$ unconnected, if not used. $V_{CC}$ allows IN_ supplies less than UVLO to be tracked. $V_{CC}$ is internally pulled down by a $100k\Omega$ resistor.                                                                                      |  |           |

| 2       | 2                | 1       | ABP      | Internal Supply Bypass Input. Bypass ABP with a 1µF capacitor to GND. ABP maintains the device supply voltage during rapid power-down conditions.                                                                                                                                                                                                            |  |           |

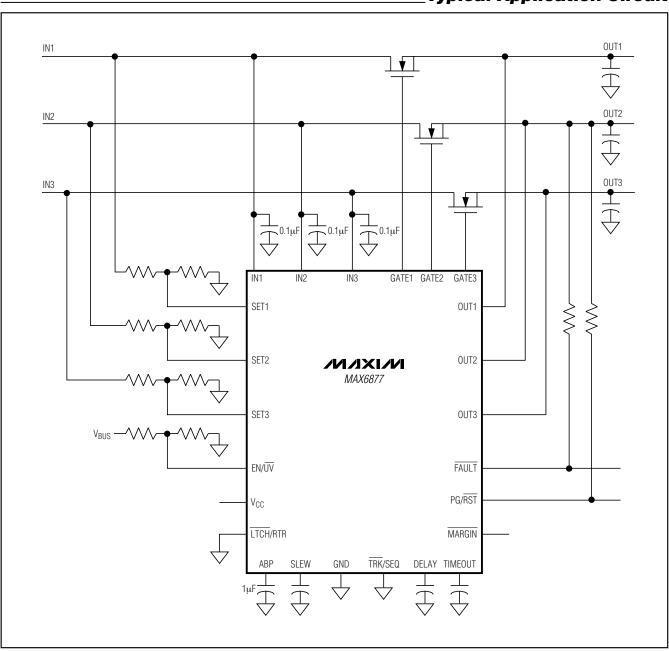

| 3       | _                | _       | SET3     | Externally Adjusted IN_ Undervoltage Lockout Threshold. Connect SET_ to                                                                                                                                                                                                                                                                                      |  |           |

| 4       | 4                | 2       | SET2     | an external resistor-divider network to set the desired undervoltage threshold                                                                                                                                                                                                                                                                               |  |           |

| 5       | 5                | 3       | SET1     | for each IN_ supply (see the <i>Typical Application Circuit</i> ). All SET_ inputs must be above the internal SET_ threshold (0.5V) to enable tracking or sequencing functionality.                                                                                                                                                                          |  |           |

| _       | 3, 16, 17,<br>22 | _       | N.C.     | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                     |  |           |

| 6       | 6                | 4       | EN/ŪV    | Logic-Enable Input or Undervoltage Lockout Monitor Input. $EN/\overline{UV}$ must be high $(EN/\overline{UV} > V_{EN_R})$ to enable voltage tracking or sequencing power-up operation. OUT_ begins tracking down when $EN/\overline{UV} < V_{EN_F}$ . Connect $EN/\overline{UV}$ to an external resistor-divider network to set the external UVLO threshold. |  |           |

| 7       | 7                | 5       | GND      | Ground                                                                                                                                                                                                                                                                                                                                                       |  |           |

| 8       | 8                | 6       | DELAY    | Tracking Startup/Sequence Delay Select Input. Connect a capacitor from DELAY to GND to select the desired delay period before tracking is enabled (after all SET_ inputs and EN/\overline{UV} are above their respective thresholds) or between supply sequences. Leave DELAY unconnected for the default 200\u03c4s delay period.                           |  |           |

| 9       | 9                | 7       | SLEW     | Slew-Rate Adjustment Input. Connect a capacitor from SLEW to GND to select the desired OUT_ slew rate.                                                                                                                                                                                                                                                       |  |           |

| 10      | 10               | _       | TIMEOUT  | PG/RST Timeout Period Adjust Input. PG/RST asserts high after the timeout period when all OUT_ exceed their IN_ referenced threshold. Connect a capacitor from TIMEOUT to GND to set the desired timeout period. Leave TIMEOUT unconnected for the default 200µs delay period.                                                                               |  |           |

| 11      | 11               | 8       | TTCH/RTR | Latch/Autoretry Selection Input. Drive LTCH/RTR low to select the latch mode. Connect LTCH/RTR to ABP or leave unconnected to select autoretry mode. LTCH/RTR is internally pulled up to ABP through a 10µA current source.                                                                                                                                  |  |           |

| 12      | 12               | 9       | TRK/SEQ  | Track/Sequence Select Input. Drive TRK/SEQ low to enable supply tracking function. Connect TRK/SEQ to ABP or leave it unconnected to enable supply sequencing. TRK/SEQ is internally pulled to ABP through a 10µA current source.                                                                                                                            |  |           |

| 13      | 13               | _       | MARGIN   | Margin Input, Active-Low. Drive MARGIN low to enable margin mode (see the Margin Input (MARGIN) section). The MARGIN functionality is disabled (returns to normal monitoring mode) after MARGIN returns high. MARGIN is internally pulled up to ABP through a 10μA current source.                                                                           |  |           |

### **Pin Description (continued)**

| PIN     |          | PIN .   |        | PIN                                                                                                                                                                                                                                                                        |  | FUNCTION |

|---------|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|

| MAX6877 | MAX6878  | MAX6879 | NAME   | FUNCTION                                                                                                                                                                                                                                                                   |  |          |

| 14      | 14       | _       | PG/RST | Power-Good Output, Open-Drain. PG_RST asserts high t <sub>TIMEOUT</sub> after all OUT_ voltages exceed the V <sub>TH_PG</sub> thresholds.                                                                                                                                  |  |          |

| 15      | 15       | 10      | FAULT  | Tracking Fault Alert Output, Active Low, Open-Drain. FAULT asserts low if a tracking failure is present for longer than the selected fault period or if tracking voltages fail by more than ±250mV. FAULT asserts low if any OUT_falls below the corresponding IN_voltage. |  |          |

| 16      | _        | _       | OUT3   | Channel 3 Monitored Output Voltage. Connect OUT3 to the source of an n-channel FET. A fault condition activates a $100\Omega$ pulldown to ground.                                                                                                                          |  |          |

| 17      | _        | _       | GATE3  | Gate Drive for External n-Channel FET. An internal charge pump boosts GATE3 to V <sub>IN3</sub> + 5V to fully enhance the external n-channel FET when power-up is complete.                                                                                                |  |          |

| 18      | 18       | 11      | OUT2   | Channel 2 Monitored Output Voltage. Connect OUT2 to the source of an n-channel FET. A fault condition activates a 100Ω pulldown to ground.                                                                                                                                 |  |          |

| 19      | 19       | 12      | GATE2  | Gate Drive for External n-Channel FET. An internal charge pump boosts GATE2 to V <sub>IN2</sub> + 5V to fully enhance the external n-channel FET when power-up is complete.                                                                                                |  |          |

| 20      | 20       | 13      | OUT1   | Channel 1 Monitored Output Voltage. Connect OUT1 to the source of an n-channel FET. A fault condition activates a 100Ω pulldown to ground.                                                                                                                                 |  |          |

| 21      | 21       | 14      | GATE1  | Gate Drive for External n-Channel FET. An internal charge pump boosts GATE1 to V <sub>IN1</sub> + 5V to fully enhance the external n-channel FET when power-up is complete.                                                                                                |  |          |

| 22      | _        | _       | IN3    | Supply Input Voltage. IN1, IN2, or IN3 must be greater than the internal undervoltage lockout ( $V_{ABP} = 2.7V$ ) to enable the tracking or sequencing                                                                                                                    |  |          |

| 23      | 23 23 15 |         | IN2    | functionality. Each IN_ input is simultaneously monitored by SET_ inputs to ensure all supplies have stabilized before power-up is enabled. If IN_ is connected to ground or left unconnected and SET_ is above 0.5V, then no-                                             |  |          |

| 24      | 24       | 16      | IN1    | sequencing control is performed on that channel. Each IN_ is internally pulled down by a 100k $\!\Omega$ resistor.                                                                                                                                                         |  |          |

| EP      | EP       | EP      | EP     | Exposed Paddle. Connect exposed paddle to ground.                                                                                                                                                                                                                          |  |          |

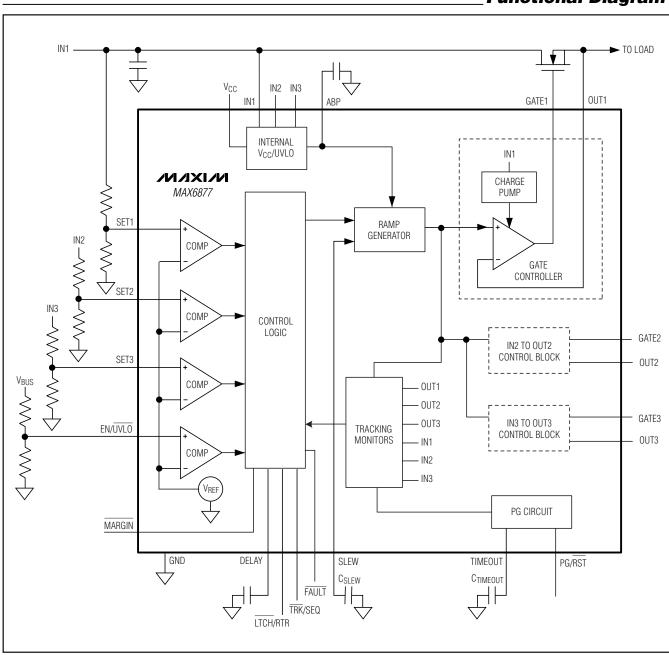

### **Functional Diagram**

### **Detailed Description**

The MAX6877/MAX6878/MAX6879 multivoltage power trackers/sequencers/supervisors monitor up to three system voltages and provide proper power-up and power-down control for systems requiring voltage tracking or sequencing. These devices ensure controlled voltage tracking with a specified range or sequencing in the proper order as system power supplies are enabled. The MAX6877/MAX6878/MAX6879 generate all required voltages and timing to control up to three external n-channel pass FETs for the OUT1/OUT2/OUT3 supply voltages (see the *Selector Guide* for different features of each device.)

The MAX6877/MAX6878/MAX6879 feature adjustable undervoltage thresholds for each input supply. When all the voltages are above these adjusted thresholds, the devices turn on the external n-channel MOSFETs to either sequence or track the voltages to the system. During the voltage-tracking mode, the voltage at the GATE of each MOSFET is increased to slowly bring up all supplies at a controlled slew rate. The voltage at the source (output) of each MOSFET is internally compared to a control ramp to maintain a low differential between each monitored supply. Tracking is dynamically adjusted to force all outputs to track within 125mV of the reference ramp. If for any reason any supplies fail to track within ±250mV of the reference ramp, the FAULT output is asserted, the power-up mode is terminated, and all outputs are quickly powered off. In sequencing mode, the outputs are turned on one after the other, OUT1 first and OUT3 last. The MAX6877/MAX6878/ MAX6879 feature an autoretry or latch-off mode with capacitor-adjusted timing.

These devices also provide a controlled power-down (tracking mode) when the system shuts off in an orderly manner. When an unexpected fault occurs, the outputs are all pulled down simultaneously with an internal  $100\Omega$  pulldown to help discharge capacitive loads at the MOSFET's source.

The MAX6877/MAX6878/MAX6879 feature independent internal charge pumps to fully enhance the external FETs for low-voltage drops at highpass currents. The MAX6877/MAX6878 also feature a power-good output with a selectable timeout period that can be used for system reset.

The MAX6877/MAX6878/MAX6879 monitor up to three voltages. Devices may be configured to exclude any IN\_. To disable the tracking or sequencing operation of any IN\_, connect the IN\_ to ground (or leave unconnected) and connect SET\_ to a voltage greater than 0.5V. The channel exclusion feature adds more flexibili-

ty to the device in a variety of different applications. As an example, the MAX6877 can track or sequence two voltages using IN1 and IN2 while IN3 is left disabled.

## Powering the MAX6877/MAX6878/MAX6879

These devices derive power from either the IN1, IN2, or IN3 voltage inputs or V<sub>CC</sub> (see the *Functional Diagram*). V<sub>CC</sub> or one of the IN\_ inputs must be at least +2.7V to ensure full device operation.

The highest input voltage on IN1/IN2/IN3 or V<sub>CC</sub> supplies power to the devices. Internal hysteresis ensures that the supply input that initially powers these devices continues to power the MAX6877/MAX6878/MAX6879 when multiple input voltages are within 100mV (typ) of each other.

#### ABP

ABP powers the analog circuitry. Bypass ABP to GND with a  $1\mu F$  ceramic capacitor installed as close to the device as possible. ABP takes the highest voltage of IN\_ or VCC. Do not use ABP to provide power to external circuitry. ABP maintains the device supply voltage during rapid power-down conditions.

## Tracking and Sequencing Modes (TRK/SEQ)

To enable the power-up/power-down voltage-tracking operation, drive  $\overline{TRK/SEQ}$  low (connect  $\overline{TRK/SEQ}$  to GND). To enable power-up sequencing and power-down tracking functions, drive  $\overline{TRK/SEQ}$  high (connect  $\overline{TRK/SEQ}$  to ABP) or leave it unconnected.  $\overline{TRK/SEQ}$  is internally pulled to ABP through a 10µA current source (see Figures 1 and 3).

#### Tracking

To operate in tracking mode, connect TRK/SEQ to GND. When  $V_{FN}/\overline{UV} > 1.25V$  and all SET inputs are above the internal SET\_ threshold (0.5V), the tracking process is initiated. The MAX6877/MAX6878/MAX6879 generate an internal reference ramp voltage that drives the control loops for the tracked voltages. The tracking functionality is monitored with a comparator control block for each output (see the Functional Diagram). The comparators monitor each OUT\_ voltage with respect to the common reference ramp voltage to ensure the OUT\_ voltages stay within 125mV of the reference ramp, monitor each tracked output voltage with respect to its source input voltage, and monitor each output voltage with respect to GND during powerup/retry cycles. If for any reason any supplies fail to track within ±250mV of the reference ramp, the FAULT output is asserted, the power-up mode is terminated, and all outputs are quickly powered off.

During ramp up, if an OUT\_ voltage is less than the reference ramp voltage by more than 125mV, the control loop dynamically stops the control ramp voltage from rising until the slow OUT\_ voltage catches up. If an OUT\_ voltage is greater or less than the reference ramp voltage by more than 250mV, a fault is signaled and a power-down phase is initiated.

The slew rate for the reference ramp voltage is capacitor adjustable. Connect a capacitor from SLEW to ground to select the desired OUT\_ slew rate. When all OUT\_ voltages have exceeded the VTH\_PG percentage of the IN\_ voltage (external n-channel FET is saturated), PG/RST asserts high after tTIMEOUT indicating successful tracking.

#### Sequencing

The sequencing operation can be initiated after all input conditions for power-up are met  $V_{EN/\overline{UV}} > 1.25V$  and all SET\_ inputs are above the internal SET\_ threshold (0.5V). In sequencing mode, the outputs are turned on sequentially, OUT1 first and OUT3 last. Before turning on each channel, a delay period occurs as in Figure 3 (programmable by connecting a capacitor from DELAY to ground). The power-up phase for each channel ends when its output voltage exceeds a fixed percentage (VTH\_PG) of the corresponding IN\_ voltage. When all channels have exceeded these thresholds, PG/RST asserts high after tTIMEOUT, indicating a successful sequence.

If there is a fault condition during the initial power-up sequence, the process is aborted.

When powering down, all outputs turn off simultaneously, tracking each other. No reverse power-down sequencing occurs.

#### **Power-Up and Power-Down**

During power-up, the OUT\_ is forced to follow the internal reference ramp voltage by an internal loop that controls the GATE\_ of the external MOSFET. This phase must be completed within the adjustable fault timeout period; otherwise, the part forces a shutdown on all GATE\_.

Once the power-up is completed, a power-down phase can be initiated by forcing  $V_{EN/\overline{UV}}$  below  $V_{EN\_F}$ . The reference voltage ramp ramps down at the capacitor-adjusted slew rate. The control-loop comparators monitor each OUT\_ voltage with respect to the common reference ramp voltage. During ramp down, if an OUT\_ voltage is greater than the reference ramp voltage by more than  $V_{TRK}$ , the control loop dynamically stops the control ramp voltage from decreasing until the slow OUT\_ voltage catches up. If an OUT\_ voltage is greater

or less than the reference ramp voltage by more than  $V_{TRK\_F}$ , a fault is signaled and the fast-shutdown mode is initiated. In fast-shutdown mode, a  $100\Omega$  pulldown resistor is connected from OUT\_ to GND to quickly discharge capacitance at OUT\_ and GATE \_ is pulled low with a strong IgDs current (see Figures 2 and 4).

Figures 5 and 6 show aborted tracking and sequencing modes. When EN/UV goes low before tTIMEOUT expires, all the outputs go low and the device goes into fast shutdown.

#### **Internal Pulldown**

To ensure that the OUT\_ voltages are not held high by a large output capacitance after a fault has occurred, there is a  $100\Omega$  internal pulldown at OUT\_. The pulldown ensures that all OUT\_ voltages are below VTH\_PL (referenced to GND) before power-up cycling is initiated. The internal pulldown also ensures a fast discharge of the output capacitor during fast shutdown and fault modes. The pulldowns are not present during normal operation.

#### **Stability Comment**

No external compensation is required for tracking or slew-rate control.

## Inputs IN1/IN2/IN3

The highest voltage on VCC, IN1, IN2, or IN3 supplies power to the device. The undervoltage threshold for each IN\_ supply is set with an external resistor-divider from each IN\_ to SET\_ to ground.

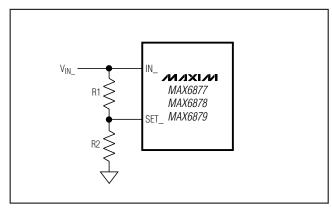

#### Undervoltage Lockout Threshold Inputs (SET\_)

The MAX6877 features three and the MAX6878/MAX6879 feature two externally adjustable IN\_ undervoltage lockout (UVLO) thresholds (SET1, SET2, SET3) to enable sequencing/tracking functionality. The undervoltage threshold for each IN\_ supply is set with an external resistor-divider from each IN\_ to SET\_ to ground (see Figure 9). All SET\_ inputs must be above the internal SET\_ threshold (0.5V) to enable tracking/sequencing functionality. Use the following formula to set the UVLO threshold:

$$V_{IN} = V_{TH} (R1 + R2) / R2$$

where  $V_{IN}$  is the undervoltage lockout threshold and  $V_{TH}$  is the 500mV SET threshold.

#### Margin Input (MARGIN)

MARGIN allows system-level testing while power supplies are below the normal ranges as adjusted by the SET inputs. Drive MARGIN low before varying system

Figure 9. Setting the Undervoltage (UVLO) Thresholds

voltages below the adjusted thresholds to avoid signaling an error. The state of PG/RST and FAULT outputs does not change while MARGIN is low. PG/RST, FAULT, and all monitoring functions are disabled while MARGIN is low. MARGIN makes it possible to vary the supplies without a need to adjust the thresholds to prevent tracker/sequencer alerts or faults. Drive MARGIN high or leave it unconnected for normal operating mode.

#### Slew-Rate Control Input (SLEW)

The reference ramp voltage slew rate during any controlled power-up/down phase can be programmed in the 90V/s to 950V/s range by connecting a capacitor (CSLEW) from SLEW to ground. Use the following formula to calculate the typical slew rate:

Slew Rate =  $(9.35 \times 10^{-8})/C_{SLEW}$

where slew rate is in V/s and C<sub>SLEW</sub> is in farads.

The capacitor at C<sub>SLEW</sub> also sets the FAULT timeout period (tFAULT) and FAULT retry timeout period (t<sub>RETRY</sub>) (see Table 1).

For example, if C<sub>SLEW</sub> = 100pF, we have t<sub>RETRY</sub> = 350ms, t<sub>FAULT</sub> = 21.91ms, slew rate = 935V/s. For example, if C<sub>SLEW</sub> = 1nF, we have t<sub>RETRY</sub> = 3.5s, t<sub>FAULT</sub> = 219ms, slew rate = 93.5V/s.

CSLEW is the capacitor on the SLEW pad, and must be large enough to make the parasitic capacitance negligible. CSLEW should be in the range of 100pF < CSLEW < 1nF.

Table 1. C<sub>SLEW</sub> Timing Formulas

| TIME PERIOD | FORMULAS                                       |

|-------------|------------------------------------------------|

| Slew Rate   | (9.35 x 10 <sup>-8</sup> ) / C <sub>SLEW</sub> |

| tretry      | 3.506 x 10 <sup>9</sup> x C <sub>SLEW</sub>    |

| tfault      | 2.191 x 10 <sup>8</sup> x C <sub>SLEW</sub>    |

#### Limiting Inrush Current

The capacitor connected at SLEW controls the OUT\_S slew rate, thus controlling the inrush current required to charge the load capacitor at the outputs (OUT\_). Using the programmed slew rate, limit the inrush current by using the following formula:

Inrush = Cout x SR

where  $I_{\text{INRUSH}}$  is in amperes,  $C_{\text{OUT}}$  is in farads, and SR is in V/s.

#### Delay Time Input (DELAY)

To adjust the desired delay period (tDELAY) before tracking/sequencing is enabled, connect a capacitor (CDELAY) between DELAY to ground (see Figures 1 to 8). The selected delay time is also enforced when EN/UV rises from low to high when all the input voltages (IN1/IN2/IN3) are present. Use the following formula to calculate the delay time:

$t_{DELAY} = 200\mu s + (500k\Omega \times C_{DELAY})$

where tDELAY is in µs and CDELAY is in farads. Leave DELAY unconnected for the default 200µs delay.

#### Timeout Period Input (TIMEOUT)

These devices feature a PG/RST timeout period. Connect a capacitor (CTIMEOUT) from TIMEOUT to ground to program the PG/RST timeout period. After all OUT\_ outputs exceed their IN\_ referenced thresholds (VTH\_PG), PG/RST remains low for the selected timeout period, tTIMEOUT (see Figure 3):

$t_{TIMEOUT} = 200\mu s + (500k\Omega \times C_{TIMEOUT})$

where tTIMEOUT is in  $\mu$ s and CTIMEOUT is in farads. Leave TIMEOUT unconnected for the default 200 $\mu$ s timeout delay.

#### Logic-Enable Input (EN/UV)

Drive logic EN/ $\overline{UV}$  input above  $V_{EN\_R}$  to initiate voltage tracking/sequencing during the power-up operation. Drive logic EN/ $\overline{UV}$  below  $V_{EN\_F}$  to initiate tracking power-down operation. Connect EN/ $\overline{UV}$  to an external resistor-divider network to set the external undervoltage lockout threshold.

#### OUT1/OUT2/OUT3

The MAX6877 monitors three and MAX6878/MAX6879 monitor two OUT\_ outputs to control the tracking/sequencing performance. After the internal supply (ABP) exceeds the minimum voltage (2.7V) requirements,  $EN/\overline{UV} > V_{EN\_R}$ , and IN1/IN2/IN3 are all greater than their adjusted SET\_ thresholds, OUT1/OUT2/OUT3 begin to track or sequence.

During fault conditions, an internal pulldown resistor (100 $\Omega$ ) on OUT\_ is enabled to help discharge load capacitance (100 $\Omega$  is connected for fast power-down control).

### Outputs GATE\_

The MAX6877/MAX6878/MAX6879 feature up to three GATE\_ outputs to drive up to three external n-channel FET gates. The following conditions must be met before GATE\_ begins enhancing the external n-channel FET\_:

- 1) All SET\_ inputs (SET1-SET3) are above their 0.5V thresholds.

- 2) At least one IN\_ input or VCC is above the minimum operating voltage (2.7V).

- 3)  $EN/\overline{UV} > 1.25V$ .

At power-up mode, GATE\_ voltages are enhanced by control loops so that all OUT\_ voltages track together at a capacitor-adjusted slew rate. Each GATE\_ is internally pulled up to 5V above its relative IN\_ voltage to fully enhance the external n-channel FET when power-up is complete.

#### FAULT

The MAX6877/MAX6878/MAX6879 include an open-drain, active-low tracking fault alarm output (FAULT). FAULT asserts low when a power-up phase is not completed within the specified fault period or if OUT\_ voltages are more than VTRK\_F.

The fault time period (tfault) is set through the capacitor at SLEW (Cslew). Use the following formula to estimate the fault timeout period:

$t_{FAULT} = 2.191 \times 10^8 \times C_{SLEW}$

Power-supply tracking operation should be completed within the selected fault timeout period (tFAULT). The total tracking time is extended when the devices must vary the control slew rate to allow slow supplies to catch up. If the external FET is too small (RDs is too high for the selected load current and IN\_ source current), the OUT\_ voltage may never reach the control ramp voltage. For a slew rate of 935V/s, a fault is signaled if all outputs have not stabilized within 22ms. For a slew rate of 93.5V/s, a fault is signaled if tracking takes too long (more than 219ms).

During power-up, only the condition, OUT\_ < ramp - VTRK, is monitored in order to stop the ramp. However, both conditions OUT < ramp - VTRK\_F and OUT\_ > ramp + VTRK\_F cause a fault. During power-down, only the condition OUT > ramp + VTRK is checked in order to stop the ramp. However, both conditions OUT\_ < ramp - VTRK\_F and OUT\_ > ramp + VTRK\_F cause a fault (see Figure 10). OUT1, OUT2, and OUT3 are tracked within VTRK\_F (mV) (power-up tracking and power-down), and if they differ by more than 2 x VTRK\_F a fault condition is asserted.

Retry time period (tretry) is defined as 16 x tfault. To calculate the retry time period use the following formula:

$tretry = 3.506 \times 10^{9} \times Cslew$

where tRETRY is in µs and CSLEW is in farads.

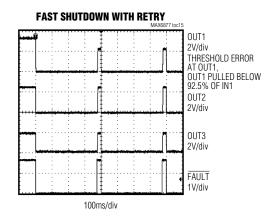

#### Autoretry and Latch-Off Functions (LTCH/RTR)

The MAX6877/MAX6878/MAX6879 feature latch-off or autoretry modes to power-on again after a fault condition has been detected. Connect LTCH/RTR to ground to set the latch-off mode. To select autoretry mode, connect LTCH/RTR to ABP or leave unconnected.

Figure 10. Stop Ramp FAULT Window During Power-Up and Power-Down

When a fault is detected, for a period of tRETRY, GATE\_remains off and the  $100\Omega$  pulldowns are turned on. After the tRETRY period, the device waits tDELAY and retries power-up if all power-up conditions are met (see Figure 8). These include all VSET\_ > 0.5V, EN/UV > VEN\_R, OUT\_ voltages < VTH\_PL. The autoretry period, tRETRY, is a function of CSLEW; see Table 1.

When the device is in latch mode and a fault occurs, FAULT asserts and all outputs are latched off. To unlatch OUT\_ after a fault disappears, cycle EN/UV or cycle VCC and the inputs (IN\_) below the 2.7V UVLO threshold. After EN/UV goes high, the device waits a tretry period then tries to power-up again. If VCC and all IN\_ are cycled below 2.7V, the device tries to power-up immediately.

#### Power-Good Output (PG/RST)

The MAX6877/MAX6878 include a power-good (PG/RST) output. PG/RST is an open-drain output and requires an external pullup resistor.

All the OUT\_ outputs must exceed their IN\_ referenced thresholds (IN\_ x V<sub>TH\_PG</sub>) for the selected reset timeout period t<sub>TIMEOUT</sub> (see the *TIMEOUT Period Input* section) before PG/RST asserts high. PG/RST stays low for the selected reset timeout period (t<sub>TIMEOUT</sub>) after all the OUT\_ voltages exceed their IN\_ referenced thresholds. PG/RST goes low when V<sub>SET\_</sub> < V<sub>TH</sub> or V<sub>EN/UV</sub> < V<sub>EN\_R</sub> (see Figure 3).

### Applications Information

#### **MOSFET Selection**

The external pass MOSFET is connected in series with the sequenced power-supply source. Since the load current and the MOSFET drain-to-source impedance (RDS) determine the voltage drop, the on characteristics of the MOSFET affect the load supply accuracy. The MAX6877/MAX6878/MAX6879 fully enhance the external MOSFET out of its linear range to ensure the lowest drain-to-source on-impedance. For highest supply accuracy/lowest voltage drop, select a MOSFET with an appropriate drain-to-source on-impedance with a gate-to-source bias of 4.5V to 6.0V.

#### **Layout and Bypassing**

For better noise immunity, bypass each of the IN\_inputs to GND with  $0.1\mu F$  capacitors installed as close to the device as possible. Bypass ABP to GND with a  $1\mu F$  capacitor installed as close to the device as possible. ABP is an internally generated voltage and must not be used to supply power to external circuitry.

#### **Selector Guide**

| PART    | CHANNEL | TIMEOUT<br>SELECTABLE | PG/RST MARGIN |     | Vcc |

|---------|---------|-----------------------|---------------|-----|-----|

| MAX6877 | 3       | Yes                   | Yes           | Yes | Yes |

| MAX6878 | 2       | Yes                   | Yes           | Yes | Yes |

| MAX6879 | 2       | No                    | No            | No  | No  |

### **Typical Application Circuit**

### \_Ordering Information (continued)

### \_\_Chip Information

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |  |

|-------------|----------------|-----------------|-------------|--|

| MAX6878ETG+ | -40°C to +85°C | 24 Thin QFN     | T2444-4     |  |

| MAX6879ETE+ | -40°C to +85°C | 16 Thin QFN     | T1644-4     |  |

<sup>+</sup>Denotes lead-free package.

### Pin Configurations (continued)

PROCESS: BICMOS

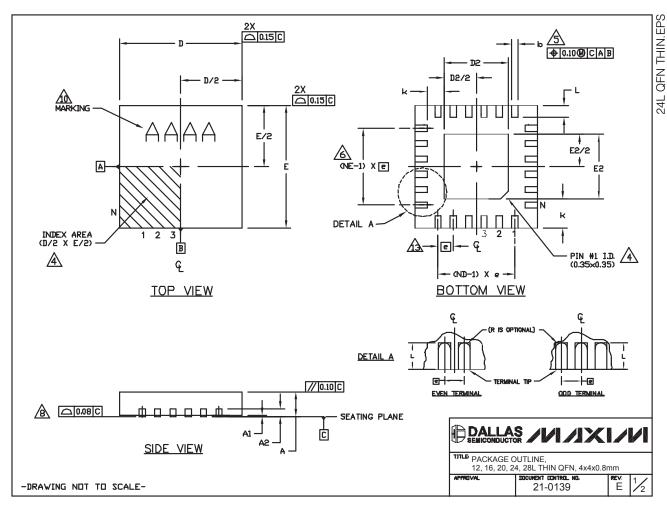

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|               | COMMON DIMENSIONS |         |      |        |       |      |           |       |           |         |      |           |         |      |      |

|---------------|-------------------|---------|------|--------|-------|------|-----------|-------|-----------|---------|------|-----------|---------|------|------|

| PKG           | 12                | 2L 4×   | 4    | 16     | L 4x  | 4    | 20        | )L 4× | 4         | 24L 4×4 |      |           | 28L 4×4 |      |      |

| REF.          | MIN.              | NDM.    | MAX. | MIN.   | NDM.  | MAX. | MIN.      | NOM.  | MAX.      | MIN.    | NDM. | MAX.      | MIN.    | NDM. | MAX. |

| Α             | 0.70              | 0.75    | 0.80 | 0.70   | 0.75  | 0.80 | 0.70      | 0.75  | 0.80      | 0.70    | 0.75 | 0.80      | 0.70    | 0.75 | 0.80 |

| A1            | 0.0               | 0.02    | 0.05 | 0.0    | 0.02  | 0.05 | 0.0       | 20.0  | 0.05      | 0.0     | 0.02 | 0.05      | 0.0     | 0.02 | 0.05 |

| A2            | 0.20 REF          |         | ٥    | .20 RE | F     | 0    | .20 RE    | F     | ٥         | 20 RE   | F    | 0.20 REF  |         |      |      |

| b             | 0.25              | 0.30    | 0.35 | 0.25   | 0.30  | 0.35 | 0.20      | 0.25  | 0.30      | 0.18    | 0.23 | 0.30      | 0.15    | 0.20 | 0.25 |

| D             | 3,90              | 4.00    | 4.10 | 3.90   | 4.00  | 4.10 | 3.90      | 4.00  | 4.10      | 3.90    | 4.00 | 4.10      | 3.90    | 4.00 | 4.10 |

| Ε             | 3.90              | 4.00    | 4.10 | 3.90   | 4.00  | 4.10 | 3.90      | 4.00  | 4.10      | 3.90    | 4.00 | 4.10      | 3.90    | 4.00 | 4.10 |

| 6             | _                 | 0.80 BS | C.   | 0.     | 65 BS | C.   | 0.50 BSC. |       | 0.50 BSC. |         |      | 0.40 BSC. |         |      |      |

| k             | 0.25              | -       | ı    | 0.25   | -     | ı    | 0.25      | -     | -         | 0.25    | -    | -         | 0.25    | -    | -    |

| L             | 0.45              | 0.55    | 0.65 | 0.45   | 0.55  | 0.65 | 0.45      | 0.55  | 0.65      | 0.30    | 0.40 | 0.50      | 0.30    | 0.40 | 0.50 |

| N             |                   | 12      |      |        | 16    | 51   |           | 20    |           |         | 24   |           |         | 28   |      |

| ND            | 3 4               |         |      | 5      |       |      | 6         |       |           | 7       |      |           |         |      |      |

| NE            | 3 4               |         |      | 5      |       | 6    |           |       | 7         |         |      |           |         |      |      |

| Jedec<br>Var. |                   | WGGB    |      |        | WGGC  |      | 1         | WGGD- | 1         | WGGD-2  |      |           | VGGE    |      |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |               |  |  |

|------------------------|------|------|------|------|------|------|---------------|--|--|

| PKG.                   |      | D2   |      |      | E5   |      | DOWN<br>BONDS |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | ALLOVED       |  |  |

| T1244-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |

| T1244-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND            |  |  |

| T1644-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |

| T1644-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND            |  |  |

| T2044-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |

| T2044-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO            |  |  |

| T2444-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |

| T2444-3                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | YES           |  |  |

| T2444-4                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | ND            |  |  |

| T2844-1                | 2.50 | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 | ND            |  |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL ∯1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL ∯1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN

THE ZONE INDICATED. THE TERMINAL ∯1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

⚠ DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

6 ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

$\Lambda$  MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. COPLANARITY SHALL NOT EXCEED 0.08mm

12. WARPAGE SHALL NOT EXCEEND 0.10mm

1 LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY

DALLAS /// // // //

PACKAGE OUTLINE, 12, 16, 20, 24, 28L THIN QFN, 4x4x0.8mm

Ε

DOCUMENT CONTROL NO. 21-0139

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

### **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

многоканальный

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

### Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9