# **Intel® Ethernet Switch FM4000**

24-Port 10G Ethernet L2/L3/L4 Switch/Router

**Datasheet**

**Networking Division (ND)**

#### **LEGAL**

By using this document, in addition to any agreements you have with Intel, you accept the terms set forth below.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright © 2013-2014, Intel Corporation. All Rights Reserved.

# **Revision History**

| Revision | Date               | Comments                                    |

|----------|--------------------|---------------------------------------------|

| 3.2      | March 26, 2014     | General update.                             |

| 3.1      | January 23, 2014   | General Update.                             |

| 3.0      | November 25, 2013  | General update.                             |

| 2.6      | April 22, 2013     | Added note preceding table in Section 16.5. |

| 2.5      | April 1, 2013      | Changed part number FM4104 to FM4105.       |

| 2.4      | April 7, 2011      | General update (see revision document).     |

| 2.3      | December 6, 2010   | General update (see revision document).     |

| 2.2      | January 5, 2010    | General update (see revision document).     |

| 2.1      | May 14, 2009       | General update (see revision document).     |

| 2.0      | February 10, 2009  | General update (see revision document).     |

| 1.4      | December 4, 2008   | General update (see revision document).     |

| 1.31     | October 7, 2008    | General update (see revision document).     |

| 1.2      | July 17, 2008      | General update.                             |

| 1.15     | July 11, 2008      | Formatting updates only.                    |

| 1.1      | July 1, 2008       | General update.                             |

| 1.0      | October 30, 2007   | Update to Preliminary Datasheet.            |

| 0.9      | October 3, 2007    | General update.                             |

| 0.55     | September 30, 2007 | General update (intermediate release).      |

| 0.50     | April 23, 2007     | General update.                             |

| 0.40     | February 19, 2007  | First release.                              |

NOTE: This page intentionally left blank.

# **Contents**

| 1.0 | Introdu    | ıction                                        | 11 |

|-----|------------|-----------------------------------------------|----|

| 1.1 | Scope      |                                               | 11 |

| 1.2 | Product A  | Applicability                                 | 11 |

| 1.3 | Documen    | t Organization                                | 12 |

| 1.4 | Definition | ns                                            | 13 |

| 2.0 | Archite    | cture Overview                                | 15 |

| 2.1 | Introduct  | ion to Architecture                           | 15 |

| 2.2 | Frame Pa   | rsing                                         | 18 |

|     | 2.2.1      | Layer 2                                       | 19 |

|     | 2.2.2      | Layer 3                                       | 20 |

|     | 2.2.3      | Deep Packet Inspection for IP frames          | 22 |

| 2.3 | Frame Pr   | ocessing Pipeline Overview                    | 22 |

|     | 2.3.1      | Frame Header                                  | 24 |

|     | 2.3.2      | Frame Trailer                                 | 25 |

|     | 2.3.3      | GloRT                                         | 26 |

|     | 2.3.4      | Ethernet Port Logic                           | 26 |

|     | 2.3.5      | Parsing                                       | 26 |

|     | 2.3.6      | FFU (Filtering and Forwarding Unit)           |    |

|     | 2.3.7      | ARP Unit                                      |    |

|     | 2.3.8      | Layer 2 Lookup Unit                           | 28 |

|     | 2.3.9      | GloRT Lookup                                  |    |

|     | 2.3.10     | Triggers and Link Aggregation Units           |    |

|     | 2.3.11     | Congestion Management                         |    |

|     | 2.3.12     | Packet Queues                                 |    |

|     | 2.3.13     | Packet Replicator                             |    |

|     | 2.3.14     | Egress Scheduler and Egress EPL               |    |

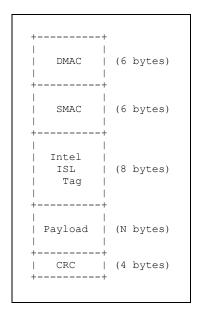

| 2.4 | Intel ISL  | Tag                                           |    |

|     | 2.4.1      | Frame Type (FTYPE)                            |    |

|     | 2.4.2      | VLAN Type (VTYPE) and Management Type (MTYPE) |    |

|     | 2.4.3      | Switch Priority (SWPRI)                       |    |

|     | 2.4.4      | User Bits (USER)                              |    |

|     | 2.4.5      | VLAN priority (VPRI)                          |    |

|     | 2.4.6      | VLAN CFI/DEI bit (VCFI)                       |    |

|     | 2.4.7      | VLAN ID (VID)                                 |    |

|     | 2.4.8      | Source GloRT (SGLORT)                         |    |

|     | 2.4.9      | Destination GloRT (DGLORT)                    |    |

| 2.5 |            |                                               |    |

| 2.6 | _          | odes                                          |    |

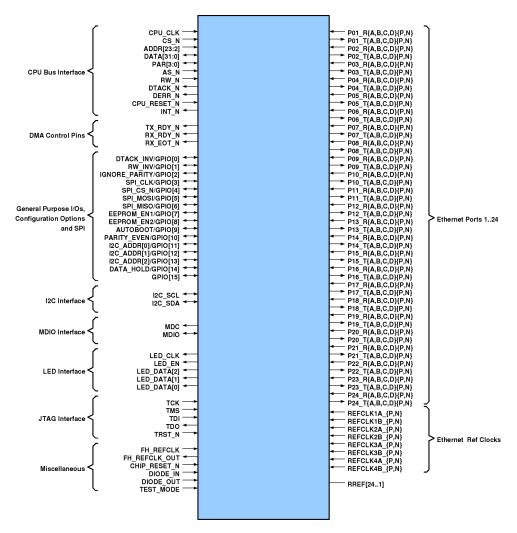

| 3.0 |            | scriptions                                    |    |

| 3.1 |            | /iew                                          |    |

| 3.2 |            | me Convention                                 |    |

| 3.3 | _          | Pin Descriptions                              |    |

| 3.3 | 3.3.1      | Ethernet Port Pins                            |    |

|     | 3.3.2      | Power Pins                                    |    |

|     | 3.3.3      | Bus Interface Pins                            |    |

|     | 3.3.4      | DMA Interface Pins                            |    |

|     | 3.3.5      | GPIOs and Strapping Pins                      |    |

|      | 3.3.6                  | I <sup>2</sup> C Pins                       | 45 |

|------|------------------------|---------------------------------------------|----|

|      | 3.3.7                  | MDIO Pins                                   | 45 |

|      | 3.3.8                  | LED Pins                                    | 45 |

|      | 3.3.9                  | JTAG Pins                                   | 46 |

|      | 3.3.10                 | Miscellaneous Pins                          | 46 |

| 4.0  | Etherne                | et Port Logic (EPL)                         | 47 |

| 4.1  | Overview               |                                             | 47 |

| 4.2  | SERDES                 |                                             | 48 |

|      | 4.2.1                  | PLL and Reference Frequency                 | 48 |

|      | 4.2.2                  | Adjusting Drive Strength and Pre-emphasis   | 49 |

|      | 4.2.3                  | Configuration of Polarity and Lane Ordering | 49 |

|      | 4.2.4                  | Testing Facilities                          | 50 |

|      | 4.2.5                  | Status and Interrupts                       | 52 |

|      | 4.2.6                  | Auto-negotiation                            | 52 |

|      | 4.2.7                  | Clause 73                                   | 53 |

|      | 4.2.8                  | Clause 37                                   | 56 |

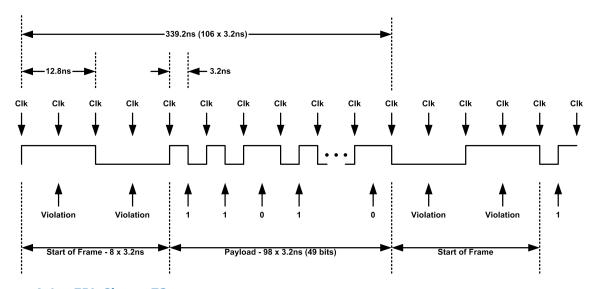

| 4.3  | Physical (             | Coding Sub-layer (PCS)                      | 58 |

|      | 4.3.1                  | Frame Format                                | 58 |

|      | 4.3.2                  | Local and Remote Faults                     | 59 |

|      | 4.3.3                  | Messaging                                   | 59 |

|      | 4.3.4                  | Balancing IFGs                              | 60 |

| 4.4  | MAC                    |                                             | 60 |

|      | 4.4.1                  | Frame Parsing                               | 61 |

|      | 4.4.2                  | Parser Errors                               | 61 |

|      | 4.4.3                  | Deep Packet Inspection for IP Frames        | 62 |

|      | 4.4.4                  | Deep Packet Inspection for Non-IP Frames    | 64 |

|      | 4.4.5                  | EPL Reset                                   | 64 |

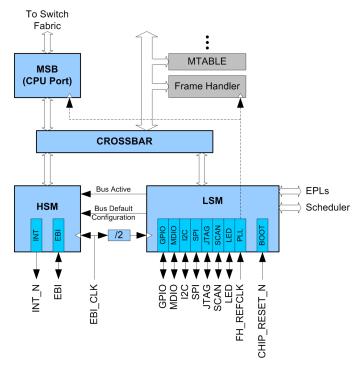

| 5.0  | Chip Ma                | anagement                                   | 67 |

| 5.1  | Overview               |                                             | 67 |

| 5.2  |                        | troller and Chip Reset                      |    |

| 5.3  | EEPROM                 | Boot Format                                 | 73 |

| 5.4  | Interrupt              | Controller                                  | 74 |

| 5.5  | I <sup>2</sup> C Contr | roller                                      | 77 |

| 5.6  | MDIO Co                | ntroller                                    | 82 |

| 5.7  | GPIO Cor               | ntroller                                    | 84 |

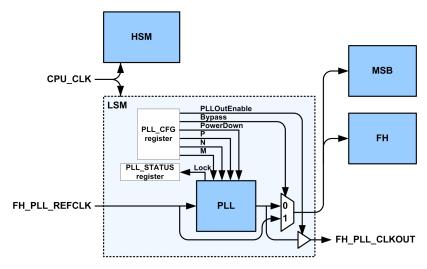

| 5.8  | Frame Ha               | andler PLL                                  | 85 |

| 5.9  | Frame Ti               | meout                                       | 86 |

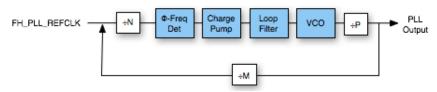

| 5.10 | LED                    |                                             | 87 |

| 5.11 | CPU Inter              | rface Controller                            | 88 |

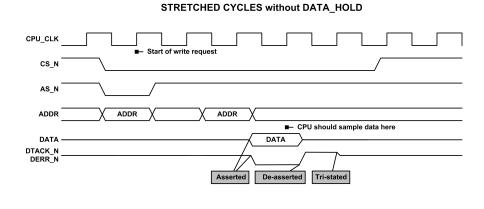

| 5.12 | CPU Bus                | Interface                                   | 89 |

|      | 5.12.1                 | Using DATA_HOLD                             | 90 |

|      | 5.12.2                 | Atomic Accesses                             | 91 |

|      | 5.12.3                 | Little and Big Endian Support               | 92 |

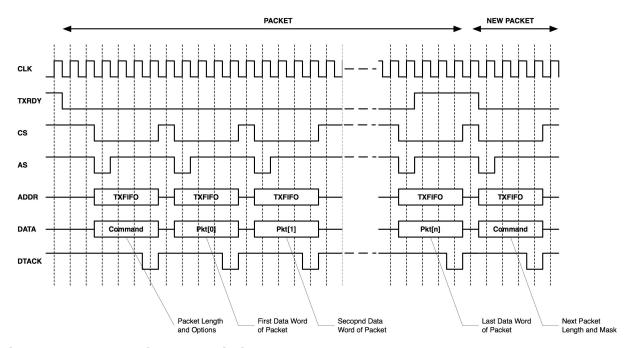

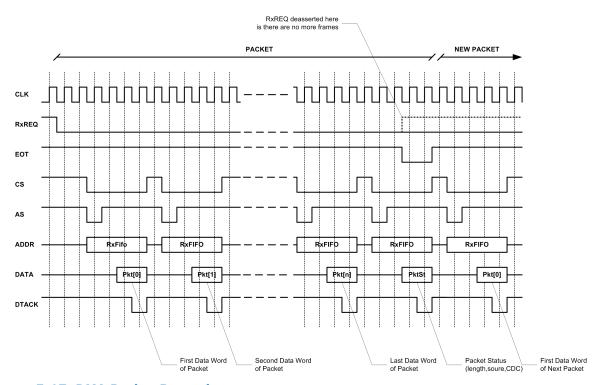

| 5.13 | CPU Fram               | ne Transfer                                 | 94 |

|      | 5.13.1                 | Packet Transmission                         | 95 |

|      | 5.13.2                 | Packet Reception                            |    |

|      | 5.13.2.1               | Little Endian Packet Transfer               | 97 |

|      | 5.13.2.2               | Big Endian Packet Transfer                  | 97 |

|      | 5.13.3                 | Packet Transfer DMA Timing                  | 98 |

| 5.14 | Packet Tr              | rapping, Logging and Mirroring              | 99 |

#### Contents-FM4000 Datasheet

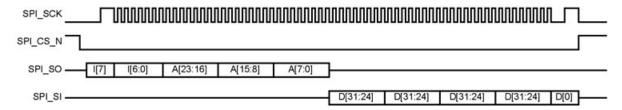

| 5.15 | SPI Interf | ace                                          | 101 |

|------|------------|----------------------------------------------|-----|

|      | 5.15.1     | SPI (Serial Peripheral Interface) Controller | 101 |

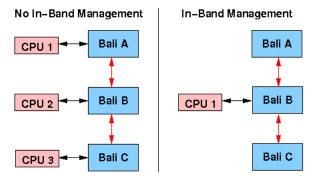

| 5.16 | In-Band N  | Management                                   | 103 |

|      | 5.16.1     | Overview                                     | 103 |

|      | 5.16.1.1   | Management By an Attached CPU                | 104 |

|      | 5.16.1.2   | Management By a Remote CPU                   | 104 |

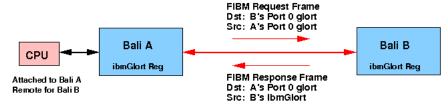

|      | 5.16.1.3   | Basic FIBM Topology                          | 104 |

|      | 5.16.1.4   | Other FIBM Topologies                        | 105 |

|      | 5.16.2     | Management Switch Bridge                     | 106 |

|      | 5.16.2.1   | Valid Frames                                 | 106 |

|      | 5.16.3     | FIBM Frames                                  | 107 |

|      | 5.16.3.1   | FIBM Frame Format                            | 107 |

|      | 5.16.3.2   | ISL Tag                                      | 108 |

|      | 5.16.3.3   | CRC Errors                                   | 108 |

|      | 5.16.4     | Reliable FIBM Communication                  | 109 |

|      | 5.16.4.1   | Sequence Numbers                             | 109 |

|      | 5.16.4.2   | Scratch Registers                            | 109 |

|      | 5.16.4.3   | Reading and Writing Idempotent Registers     | 109 |

|      | 5.16.4.4   | Writing Non-Idempotent Registers             | 109 |

|      | 5.16.4.5   | Reading Non-Idempotent Registers             | 110 |

|      | 5.16.4.6   | Interrupts                                   | 110 |

|      | 5.16.4.7   | Timing                                       | 110 |

|      | 5.16.5     | The FIBM Payload Format                      | 110 |

|      | 5.16.5.1   | FIBM Request Frame Payload Format            | 110 |

|      | 5.16.5.2   | FIBM Response Frame Payload Format           | 111 |

|      | 5.16.5.3   | Minimum FIBM Frame Payload Length            | 112 |

|      | 5.16.5.4   | Maximum FIBM Frame Payload Length            | 112 |

|      | 5.16.5.5   | FIBM Header Words                            | 112 |

|      | 5.16.6     | Interrupts and RESET                         | 113 |

|      | 5.16.6.1   | General Interrupt Handling                   | 113 |

|      | 5.16.6.2   | Disabling Interrupts                         | 114 |

|      | 5.16.6.3   | RESET Initiated by a Remote CPU              | 114 |

|      | 5.16.6.4   | Fatal Interrupts and Self Initiated RESET    | 114 |

|      | 5.16.6.5   | Boot After RESET                             | 115 |

| 5.17 | Counter R  | Rate Monitoring                              | 115 |

|      | 5.17.1     | Per-Monitor Configuration                    | 116 |

|      | 5.17.2     | Per-Monitor State                            | 116 |

|      | 5.17.3     | General Configuration                        | 117 |

| 5.18 | JTAG Inte  | rface                                        | 117 |

|      | 5.18.1     | Tap Controller                               | 118 |

|      | 5.18.2     | Instruction Register                         | 118 |

|      | 5.18.3     | Bypass Register                              | 118 |

|      | 5.18.4     | JTAG Scan Chain                              | 118 |

| 6.0  | Filtering  | g and Forwarding Unit (FFU)                  | 119 |

| 6.1  |            |                                              |     |

| 6.2  |            | ader Mapper                                  |     |

| 6.3  |            | vation and Overloading                       |     |

| 6.4  |            | ey Selection                                 |     |

| 6.5  |            | cading                                       |     |

| 6.6  |            | oings Examples                               |     |

|      |            |                                              |     |

| 6.7  | Ingress Ac  | tion                                                             | 128 |

|------|-------------|------------------------------------------------------------------|-----|

| 6.8  | Egress AC   | Ls                                                               | 131 |

| 7.0  | Routing     |                                                                  | 133 |

| 7.1  | Overview    |                                                                  | 133 |

|      | 7.1.1       | Multi-Chip Routing                                               | 134 |

| 7.2  | ARP Unit    |                                                                  | 135 |

| 7.3  | ARP_USED    | Table                                                            | 137 |

| 7.4  | IP Traps &  | ι Logs                                                           | 137 |

|      | 7.4.1       | Trapping of IGMP Frames                                          | 137 |

|      | 7.4.2       | Trapping of IP Frames with Options                               | 137 |

|      | 7.4.3       | Trapping and Logging of Frames with TTL=1 or TTL=0               | 138 |

|      | 7.4.4       | Trapping of Frames That Exceed MTU Size                          | 138 |

|      | 7.4.5       | Logging Redirectable IP Unicast Frames                           | 139 |

|      | 7.4.6       | Logging Routable IP Unicast Frames Received as Layer 2 Multicast | 139 |

| 8.0  | Layer 2     | Lookup                                                           | 141 |

| 8.1  | Overview    |                                                                  | 141 |

| 8.2  | VLANs       |                                                                  | 143 |

| 8.3  | MAC Addre   | ess Table                                                        | 145 |

| 8.4  | Layer 2 Lo  | ookup Flow                                                       | 146 |

| 8.5  | MA Table I  | Lookup, Learning and Aging                                       | 147 |

| 8.6  | MA Table I  | Management                                                       | 148 |

|      | 8.6.1       | Direct Table Access                                              | 148 |

|      | 8.6.2       | MAC Table Hardware-Accelerated Purging                           | 149 |

|      | 8.6.3       | MAC Table Change Notification FIFO                               | 149 |

|      | 8.6.4       | MA_TCN_FIFO Overflow Protection                                  | 152 |

|      | 8.6.5       | MA_TCN_FIFO Interrupts                                           |     |

| 8.7  | MAC Addre   | ess Security                                                     | 153 |

| 8.8  | Layer 2 Pr  | otocol Traps                                                     | 154 |

| 8.9  | IEEE 802.   | 1x – Port Access Control                                         | 154 |

| 9.0  | Port Ma     | pping and Packet Replication                                     | 157 |

| 9.1  | Overview    | of Port Mapping Unit                                             | 157 |

| 9.2  | Loopback    | Suppression                                                      | 159 |

| 9.3  | Link Aggre  | egation                                                          | 160 |

|      | 9.3.1       | Link Aggregation Glorts                                          | 160 |

|      | 9.3.2       | Filtering and Pruning                                            | 161 |

|      | 9.3.2.1     | Example A – LAG within One Switch                                | 162 |

|      | 9.3.2.2     | Example B – LAG within a Two-level Fat Tree                      | 163 |

| 9.4  | IP Multicas | sting                                                            | 167 |

|      | 9.4.1       | Getting a GloRT                                                  |     |

|      | 9.4.2       | Usage of Destination Mask and IP Multicast Table                 |     |

|      | 9.4.3       | Configuring MTable                                               | 169 |

| 10.0 | Frame H     | lashing                                                          | 171 |

| 10.1 | Overview    |                                                                  | 171 |

| 10.2 | , ,         | Hash                                                             |     |

| 10.3 |             | /4 Hash                                                          |     |

| 10.4 | FM2000 C    | ompatibility                                                     | 176 |

| 11.0 | Triggers    | 5                                                                | 177 |

| 11.1 | Overview    |                                                                  | 177 |

| 11.2 | Trigger Ma  | atch Conditions                                                  | 177 |

#### Contents-FM4000 Datasheet

|       | 11.2.1      | Configurable Trigger Precedence                   | 180 |

|-------|-------------|---------------------------------------------------|-----|

|       | 11.2.2      | Random Matching                                   | 180 |

| 11.3  | Trigger Ad  | tions                                             | 181 |

|       | 11.3.1      | Using Triggers to Undrop Frames                   | 183 |

|       | 11.3.2      | Rate Limiting                                     | 184 |

|       | 11.3.3      | Trigger Action Resolution                         | 184 |

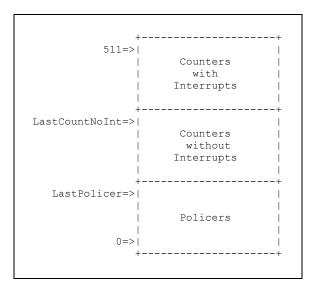

| 11.4  | Trigger Co  | ounters and Interrupts                            | 185 |

| 12.0  | QoS and     | l Congestion Management                           | 187 |

| 12.1  | Overview    |                                                   | 187 |

| 12.2  | Processing  | g of Frames with Trailing Errors                  | 188 |

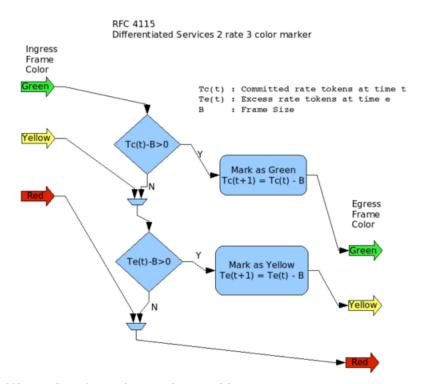

| 12.3  | Differentia | ated Services (DiffServ)                          | 189 |

| 12.4  | Processing  | priority                                          | 189 |

| 12.5  | Changing    | Priority                                          | 191 |

| 12.6  | Transmitt   | ng Priority                                       | 191 |

| 12.7  | Policing    |                                                   | 192 |

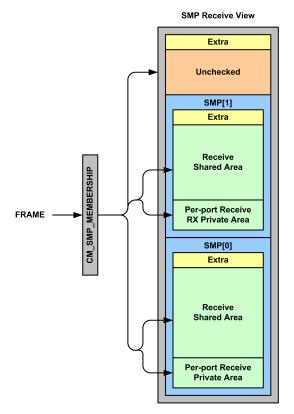

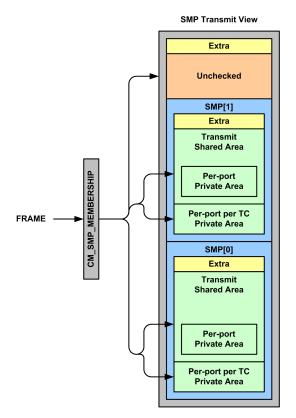

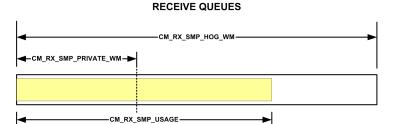

| 12.8  | Monitoring  | ر Memory                                          | 195 |

| 12.9  | Flow Cont   | rol and Rate Limiters                             | 200 |

| 12.10 | Congestio   | n Notification                                    | 204 |

|       | 12.10.1     | Virtual Output Queues Congestion Notifications    | 205 |

|       | 12.10.1.1   | VCN Frame Reaction                                | 207 |

|       | 12.10.2     | Class-Based Pause Frames                          | 207 |

|       | 12.10.3     | Fractional Congestion Notifications               | 208 |

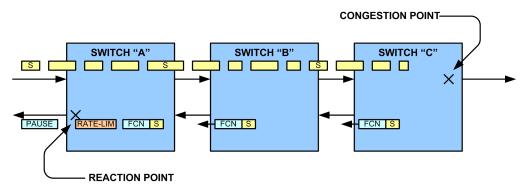

|       | 12.10.3.1   | FCN Rate Reaction                                 | 210 |

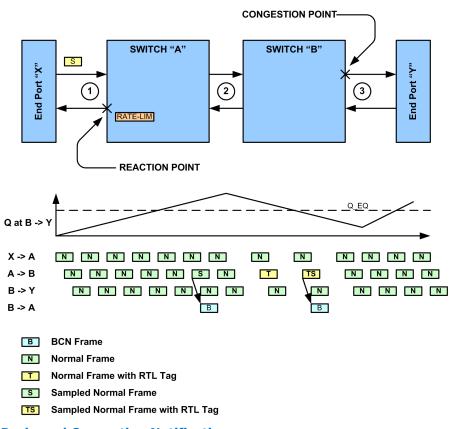

| 12.11 | Backward    | Congestion Notification                           | 211 |

|       | 12.11.1     | BCN Congestion Point                              | 215 |

|       | 12.11.1.1   | Sampling                                          | 215 |

|       | 12.11.1.2   | BCN Frame Generation                              | 216 |

|       | 12.11.2     | BCN Reaction Point                                | 216 |

|       | 12.11.2.1   | BCN Frame Reception                               | 216 |

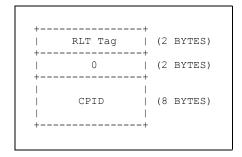

|       | 12.11.2.2   | Rate Limiter Tagging                              | 217 |

| 12.12 | Queue De    | lay Measurement                                   | 217 |

| 13.0  | Egress S    | Scheduling and Shaping                            | 219 |

| 13.1  | Introducti  | on                                                | 219 |

| 13.2  | Definition  | of terms                                          | 220 |

| 13.3  | Schedulin   | g Algorithm                                       | 221 |

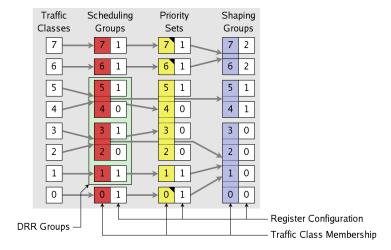

|       | 13.3.1      | Groups and Sets of Traffic Classes                | 221 |

|       | 13.3.2      | Group Eligibility                                 | 222 |

|       | 13.3.3      | Class Selection                                   | 223 |

|       | 13.3.4      | Algorithm Notes                                   | 223 |

| 13.4  | Scheduler   | Implementation                                    | 224 |

|       | 13.4.1      | Deficit Round-Robin                               | 224 |

|       | 13.4.2      | Bandwidth Shaping                                 | 226 |

| 13.5  | Configura   | ion                                               | 227 |

| 13.6  | Egress Sc   | neduling Examples                                 | 227 |

|       | 13.6.1      | Strict Priority                                   | 227 |

|       | 13.6.2      | Weight Controlled Priority Queuing                | 228 |

|       | 13.6.3      | Mixed Strict and Round-Robin Queues               | 228 |

|       | 13.6.4      | Nested Strict Prioritization                      | 229 |

|       | 13.6.5      | Deficit Round-Robin with Maximum Bandwidth Limits | 229 |

| 14.0  | Statistic   | s and Monitoring                                  | 231 |

#### FM4000 Datasheet—Contents

| 14.1 | Frame Co   | unters                                      | 231 |

|------|------------|---------------------------------------------|-----|

| 14.2 | Frame Mo   | nitoring                                    | 232 |

| 15.0 | Electric   | al Specification                            | 233 |

| 15.1 | Absolute   | Maximum Ratings                             | 233 |

| 15.2 | Recomme    | nded Operating Conditions                   | 233 |

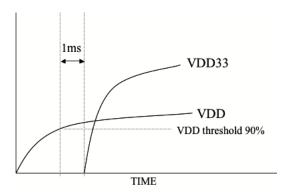

| 15.3 | Power Su   | pply Sequencing                             | 234 |

| 15.4 | DC Chara   | cteristics of LVTTL PADs                    | 235 |

| 15.5 | AC Timing  | Specifications                              | 238 |

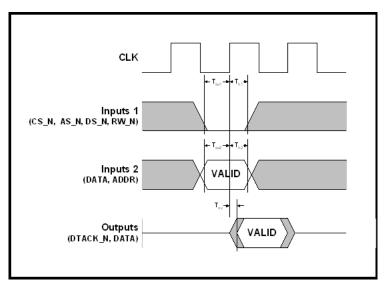

|      | 15.5.1     | CPU Interface, General Timing Requirements  | 241 |

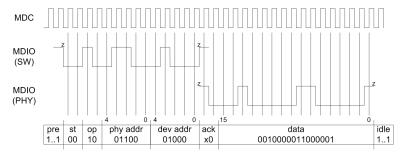

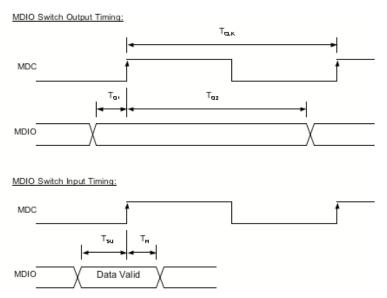

|      | 15.5.2     | MDIO Interface, General Timing Requirements | 242 |

|      | 15.5.3     | JTAG Interface                              | 243 |

| 16.0 | Mechan     | ical Specification                          | 245 |

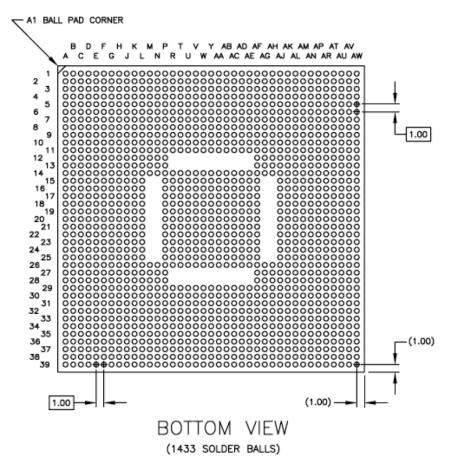

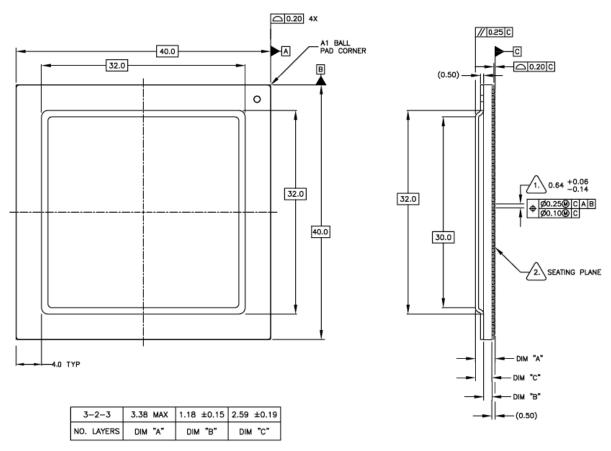

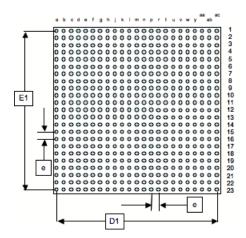

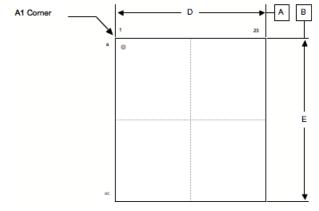

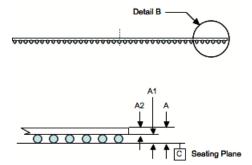

| 16.1 | 1433-Ball  | 40mm Package Dimensions                     | 246 |

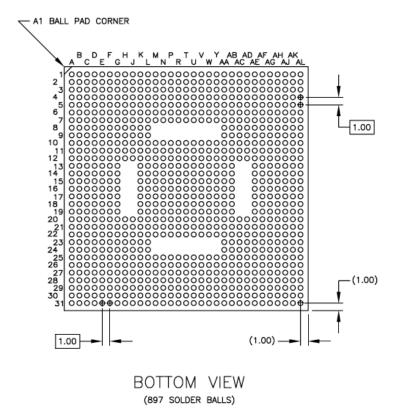

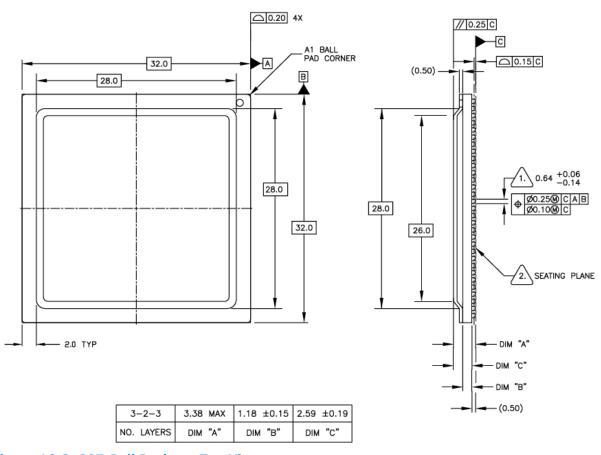

| 16.2 | 897-Ball 3 | 32mm Package Dimensions                     | 248 |

| 16.3 | 529-Ball 2 | 25mm Package Dimensions                     | 250 |

| 16.4 |            | ing                                         |     |

|      | 16.4.1     | Heat Sink Mounting Pressure                 | 252 |

| 16.5 |            | ons                                         |     |

# 1.0 Introduction

# 1.1 Scope

This functional specification is the basis for the data sheet for the Intel<sup>®</sup> Ethernet Switch FM4000 series devices, and provides information on the significantly-enhanced feature set over the FM2000 series in the areas of routing, access control lists, congestion management, network scaling, and management.

# 1.2 Product Applicability

The FM4000 represents a family of products with various port configurations and package sizes, which are listed in Table 1-1:

Table 1-1 FM4000 Products

| Part Number | 10 GbE Ports | 2.5 GbE/1 GbE Ports | Package Type |

|-------------|--------------|---------------------|--------------|

| FM4410      | 8            | 10                  | 529-ball     |

| FM4105      | 2            | 16                  | 897-ball     |

| FM4112      | 8            | 16                  | 897-ball     |

| FM4212      | 12           | 0                   | 1433-ball    |

| FM4224      | 24           | 0                   | 1433-ball    |

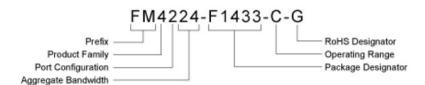

This document pertains to all variants of the FM4000 platform, although most references are specific to the 24-port 10 GbE version of the device. The part marking and number conventions for Intel Ethernet Switch Family devices are defined as follows:

Figure 1-1 Intel Ethernet Switch Family Part Number Convention

#### Key:

- Prefix "FM" identifies the device as an Intel Ethernet Switch Family product.

- Product Family Conveys information about the general capabilities of the device, as follows:

- 2 = FM2000 (L2)

- 3 = FM4000 with L2+ features

- 4 = FM4000 with full multi-layer feature set.

- **Port Configuration** Conveys information about the configuration of the ports on the device, as follows:

- 1 = Mostly single-SerDes interfaces (1 GbE, 2.5 GbE operation)

- 2 = Mostly quad-SerDes interfaces (10 GbE operation)

- **Aggregate Bandwidth** Identifies the approximate maximum bandwidth of the device configuration, calculated as:

```

((n x 10 GbE interfaces) + (m x 2.5 GbE interfaces))/10.

Example:

```

```

((4 \times 10 \text{ GbE}) + (12 \times 2.5 \text{ GbE}))/10 = 07.

```

- Package Designator Optional field. Identifies the package type and ball count of the device, as follows:

- B = Wire-bond BGA

- F = Flip-chip BGA

- **Operating Range** Identifies the operating conditions for which the device is certified to operate in the following case temperature ranges:

```

C = 0 \text{ to } +85

```

E = 0 to +105

$$I = -40 \text{ to } +115$$

• RoHS Designator — The presence of a "-G" means that the device is complaint with the RoHS requirements for restrictions on the use of hazardous substances. Compliance is via exemption #15 in the RoHS Directive Annex, which allows for the use of Pb (lead) in the solder bumps used for die attach in flip-chip packages. –G parts have lead-free solder balls on the exterior of the package for PC board die attach. Note that the non-RoHS compliant package meets the RoHS limits for the other five substances, but contains Pb in the external solder balls, which is not allowed by the RoHS directive, and in the solder bumps for die attach. This is often referred to as RoHS 5-of-6 compliant.

# 1.3 Document Organization

This document is organized as follows:

- Section 1.0, "Introduction"

- Section 2.0, "Architecture Overview"

- Section 3.0, "Pin Descriptions"

- Section 4.0, "Ethernet Port Logic (EPL)"

- Section 5.0, "Chip Management"

- Section 6.0, "Filtering and Forwarding Unit (FFU)"

- Section 7.0, "Routing"

- Section 8.0, "Layer 2 Lookup"

- Section 9.0, "Port Mapping and Packet Replication"

- Section 10.0, "Frame Hashing"

- Section 11.0, "Triggers"

- Section 12.0, "QoS and Congestion Management"

- Section 13.0, "Egress Scheduling and Shaping"

- Section 14.0, "Statistics and Monitoring"

- Section 15.0, "Electrical Specification"

- Section 16.0, "Mechanical Specification"

# 1.4 Definitions

#### **Table 1-2** Terminology Definitions

| Term          | Definition                                                                                                                                                                                                                                                                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| {A,B}         | Denotes a bit concatenation of variable A or B where A is most significant bit field and B is least significant bit field. Note that {0,A} means that 0s are added to the left (most significant bits) to pad to the desired size while {A,0} means padded to the right.                           |

| Bit Numbering | Bit 0 is the least-significant bit throughout the FM4000 architecture (even if Ethernet standards and specifications suggest otherwise).                                                                                                                                                           |

| Byte          | 8 bits.                                                                                                                                                                                                                                                                                            |

| Double Word   | 64 bits.                                                                                                                                                                                                                                                                                           |

| EBI           | External Bus Interface. Intel's term for the external CPU interface. EBI and CPU Interface are used interchangeably.                                                                                                                                                                               |

| FM2000        | The original member of the Intel Ethernet Switch Family, the FM2000 is a layer-2 10 GbE switch chip platform which forms the basis for many L2 switch product variants (including the FM2224, FM2212, FM2208, FM2112, FM2104, and FM2103).                                                         |

| FM4000        | The FM4000 series is an enhanced multi-layer 10 GbE switch chip platform, which are pin-compatible with their original FM2000 counterparts. The FM4xxx devices are full featured L3 routing devices plus other enhancements such as ACL's, congestion management, increased frame memory and more. |

| GloRT         | Intel-proprietary Global Resource Tag, which is used to pass global identification information from one FM4000 device to another in a network. GloRT is the proper "pronunciation", although other uses may appear in the document—and have the same meaning (e.g., glort, Glort, GLORT, etc.)     |

| Half-word     | 16 bits.                                                                                                                                                                                                                                                                                           |

#### **Table 1-2** Terminology Definitions (Continued)

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISL              | Intel-proprietary Inter- Switch Link tag, which is used to pass relevant management and control information from one FM4000 device to another in a network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Jumbo Frame      | The maximum jumbo frame size for FM4xxx devices is 16,376 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Logging          | Logging refers to a copy of the frame sent to a local CPU for monitoring purpose.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Mirroring        | Mirroring refers to a copy of the frame sent to another port for monitoring purpose.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Packet or Frame  | Packet — On a typical computer network, data is transmitted in the form of structured and modest-sized packets. Instead of transmitting arbitrary-length strings of data, structured packets Packet or Frame allow error checking and other relevant processing to occur on smaller easier-to-retransmit data. Packetized data also helps to alleviate traffic jams on the network when multiple nodes are contending for a shared network resource. Because packets are typically smaller than the complete data stream, techniques such as time-division multiplexing (TDM) can be used to share and interleave traffic, making it appear that multiple nodes are using the network resource at the same time. |

|                  | <b>Frame</b> — While a packet is a small block of data, a Frame is the definition of how packets of data are defined and transported on a specific network. When sending data over a network, both sides of the connection must agree on a common frame format (e.g., when a frame starts, when a frame ends, padding, etc.)                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Combining terms, an Ethernet packet is sent onto an Ethernet interface using an Ethernet frame format.  This document uses both terms interchangeably.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Register Type    | Registers are split into fields of the following types:  RO: Read-Only (This register cannot be programmed by software. Typically reports a status.)  RW: Read-Write (Reading returns the value written.)  CW1: Clear-on-Write-1 (Writing 1b to any bit clears that bit.)  CW0: Clear-on-Write-0 (Writing 0b to any bit clears that bit.)  CR: Clear-on-Read (Reading the register clears the register.)  RV: Reserved (For upward compatibility. Always write as zero, ignore on read.)                                                                                                                                                                                                                         |

| Segment          | A portion of a packet corresponding to one of the common architecturally-significant storage and processing "chunks" that has been defined in the architecture. In FM4xxx devices, a segment is 512 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Sub-segment      | A fragment of a segment that corresponds to the smallest architecturally-significant "atomic unit". In FM4xxx devices, a sub-segment is 64 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Trapping         | Trapping refers to special frames that are captured by the switch and redirected to a local CPU for processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Word             | 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| X[0N             | Denotes an array which indexes go from 0 through N inclusively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| X[N:0] or X[0:N] | Denotes a bit range within a variable. The bit range [0:N] indicates that the bit 0 is the most significant while bit range [N:0] indicates that the bit 0 is the least significant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# 2.0 Architecture Overview

## 2.1 Introduction to Architecture

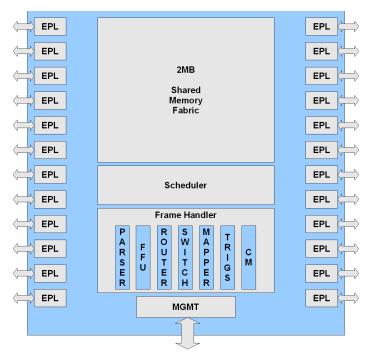

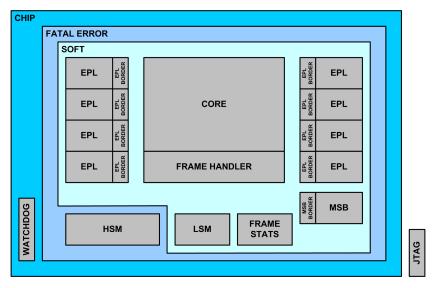

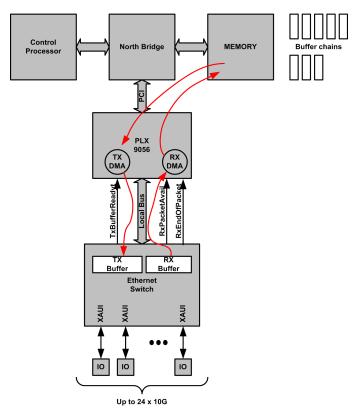

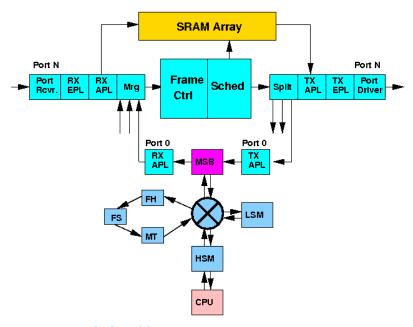

The main components in the Intel Ethernet Switch FM4000 architecture are shown in Figure 2-1.

Figure 2-1 FM4000 Block Diagram

#### **Definitions:**

- **EPL** The Ethernet Port Logic interfaces to the XAUI physical interface block, and implements the PCS and MAC layers for transmission and reception. The EPL parses incoming packets to extract the packet headers which are sent to the frame handler for packet processing while saving the entire packet in the shared memory. In the egress direction, the EPL receives segment pointers from the scheduler as well as extra data on the packet allowing the EPL to modify the packet on the way out if needed.

- **Shared Memory Fabric** The shared memory switch fabric stores incoming packets from ingress EPLs and forward them to egress EPLs upon request from the scheduler.

- **Frame Handler** The frame handler makes forwarding decision on the packet based on the frame header received from the EPL. The forwarding information is sent to the scheduler.

- **Scheduler** The scheduler manages free data segments, maintains receive and transmit queues and schedules packets for transmission. The free segments are forwarded as needed to the EPLs which use them to store incoming packets to the right location in the shared memory fabric. The scheduler keeps the list of the segments sent to each EPL and waits for the frame handler forwarding decision before placing the packet at the tail of the proper transmission queue. The scheduler then applies advanced scheduling algorithms to decide which packet to forward to the EPL, and then sends a segment list to the EPL, which uses those segments to retrieve the packet from memory

- **Management** The management block interfaces to the different components in the device to provide a coherent mechanism to manage the switch as an integrated system.

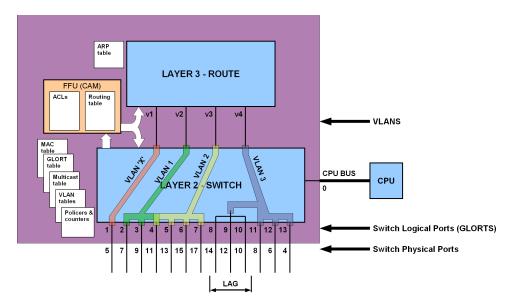

FM4000 operates as a one-arm IP router combined with an Ethernet layer 2 switch. This is shown in Figure 2-2. In this architecture, incoming packets are first associated with a VLAN (using the VTAG tag if present or by associating a default VLAN) and are then either switched within their respective VLANs or routed across VLANs or both. The decision to switch or route or drop depends on tables stored in the FFU (which includes a large ternary CAM to store IP route entries and access control lists), other tables located in the switch (such as MAC Address table) or in the router (such as ARP table) to complete the operation selected.

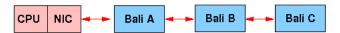

Figure 2-2 FM4000 Switch/Router Concept

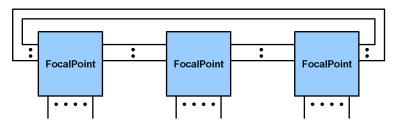

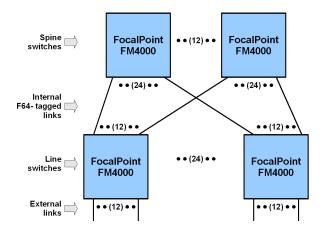

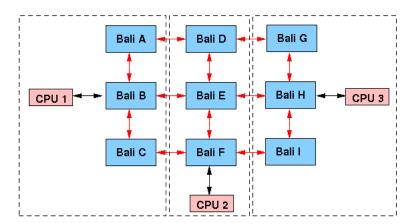

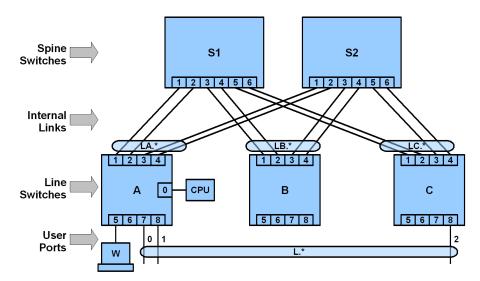

The switch includes a set of features such as global resource tags ("GloRTs"), distributed link aggregation, inter-switch tags and advance multicast distribution to allow a set of switches (cluster) to operate as a single switch as shown in the following two illustrations. Figure 2-3 shows a stack arrangement, while Figure 2-4 shows a fat-tree (Clos) architecture. Both examples allow exploitation of the full feature set through a F64 tag use on internal links.

Figure 2-3 FM4000 in a Stack Topology

Figure 2-4 FM4000 in a Tightly-Coupled Clos Topology

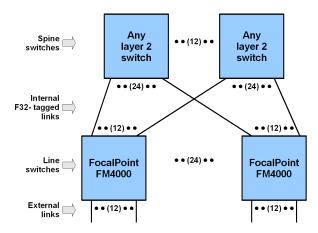

Figure 2-5 shows a fat-tree using non-Intel-tag-aware switches as spine switches. The loosely coupled architecture uses an F32 tag on internal links which is designed to be compatible with existing switches but only allows a subset of features to operate in this topology. The services not available in this architecture are distributed link aggregation and centralized management such as trapping and logging.

Figure 2-5 FM4000 in a Loosely-Coupled Clos Architecture

# 2.2 Frame Parsing

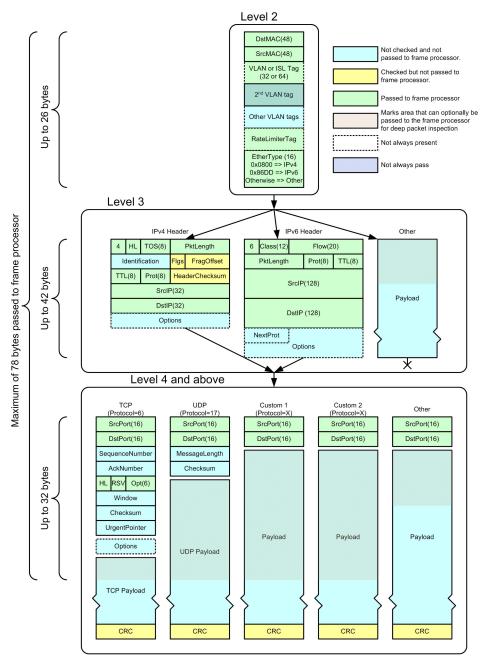

The frame parsing is shown in Figure 2-6. The packet received is always stored in the switch fabric. The job of the parser is to extract the useful fields from the header of the packet and present them to the frame processor for processing. The maximum number of bytes passed to the frame processor is 78 bytes.

Figure 2-6 Frame Parsing

### 2.2.1 Layer 2

The layer 2 processing is as follows:

- Destination MAC address

- Always forwarded to the frame handler.

- · Source MAC address

- Always forwarded to the frame handler.

- VLAN tags and ISL processing.

- The port logic supports different VLAN tag encapsulation.

- First, each port is statically configured to define if an ISL tag is expected. The following options are possible:

- **No ISL** If the port is not configured to expect an ISL tag, the parser checks if one of 3 VLAN types is recognized (0x8100 or one of the two user defined VLAN Ethernet type A or B) and, if there is a match, forwards the next 16 bits to the frame handler as VLAN PRI and VLAN ID. The parser then proceeds analyzing the next tags to detect VLAN stacking.

- **F32** The parser proceeds as for "No ISL" tag case, but also checks if an F32 tag is present after the VLAN and RLT tags. The F32 tag has a special configurable 16-bit Ethernet type which is followed by the source GloRT. If the F32 tag is found present, the source GloRT is captured and sent to the frame handler. If the F32 is not present, the frame handler associates the default source GloRT to this packet.

- **F64** The parser assumes the presence of a 64-bit tag immediately after the DMAC/SMAC addresses and forwards the content to the frame handler and marks the packet as F64 tagged. The parser then proceeds analyzing the next tags to detect VLAN stacking.

- **F96** The parser assumes presence of a 96-bit tag immediately after the DMAC/SMAC addresses and forwards the first 64 bits to the frame handler and skips over the next 32 bits and marks the packet as F64 tagged. The parser then proceeds analyzing the next tags to detect VLAN stacking.

- **X32** The parser assumes presence of a 32-bit tag immediately after the DMAC/SMAC address. It skips over the first 16 bits, assumes that the next 16 bits contain VLAN PRI and VLAN ID (as it would if the type were 0x8100) and forwards those to the frame handler and marks the packet as X32 tagged. Further stacking is not supported in this mode. The parser assumes that the Ethernet type follows immediately after this header.

- **X64** The parser assumes presence of a 64-bit tag immediately after the DMAC/SMAC address. It skips over the first 16 bits, assumes that the next 16 bits contain VLAN PRI and VLAN ID (as it would if the type were 0x8100), forwards those to the frame handler, marks the packet as X64 tagged and skips over the next 32 bits. Further stacking not supported in this mode. The parser assumes that the Ethernet type follows immediately after this header.

- X96 The parser assumes presence of a 64-bit tag immediately after the DMAC/SMAC address. It skips over the first 16 bits, assumes that the next 16 bits contains VLAN PRI and VLAN ID (as it would if the type were 0x8100), forwards those to the frame handler, skips over the next 64 bits and marks the packet as X96 tagged. Further stacking not supported in this mode. The parser assumes that the Ethernet type follows immediately after this header.

— VLAN stacking is supported for non-ISL tagged packets and for F32, F64 and F96 tagged packets. It is not supported for X32, X64 and X96 packets. The different frame formats are shown below. Note that the RLT and F32 tags are optional and that the EPL is configurable for the detection of those fields and if the Ethernet type that is reserved for those.

| DMAC              | DMAC              | DMAC              | DMAC              | DMAC              | DMAC              |   | DMAC              |   | DMAC              | DMAC              | DMAC              | DMAC              |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---|-------------------|---|-------------------|-------------------|-------------------|-------------------|

| SMAC              | SMAC              | SMAC              | SMAC              | SMAC              | SMAC              |   | SMAC              |   | SMAC              | SMAC              | SMAC              | SMAC              |

| VLAN Type B       | VLAN Type B       | VLAN Type B       | VLAN Type A       | VLAN Type B       | VLAN Type A       |   | VLAN Type 8100    |   | F64 or F96        | F64 or F96        | F64 or F96        | F64 or F96        |

| VLAN Type A       | VLAN Type A       | VLAN Type 8100    | VLAN Type 8100    | RLT<br>(optional) | RLT<br>(optional) |   | RLT<br>(optional) |   | VLAN Type A       | VLAN Type A       | VLAN Type 8100    | RLT<br>(optional) |

| VLAN Type 8100    | RLT<br>(optional) | RLT<br>(optional) | RLT<br>(optional) | F32<br>(optional) | F32<br>(optional) |   | F32<br>(optional) |   | VLAN Type 8100    | RLT<br>(optional) | RLT<br>(optional) | Ethernet Type     |

| RLT<br>(optional) | F32<br>(optional) | F32<br>(optional) | F32<br>(optional) | Ethernet Type     | Ethernet Type     |   | Ethernet Type     |   | RLT<br>(optional) | Ethernet Type     | Ethernet Type     |                   |

| F32<br>(optional) | Ethernet Type     | Ethernet Type     | Ethernet Type     |                   |                   |   |                   |   | Ethernet Type     |                   |                   | Payload           |

| Ethernet Type     |                   |                   |                   | Payload           | Payload           |   | Payload           |   |                   | Payload           | Payload           |                   |

|                   | Payload           | Payload           | Payload           |                   |                   |   |                   |   | Payload           |                   |                   |                   |

| Payload           |                   |                   |                   |                   |                   | J |                   |   |                   |                   |                   |                   |

|                   |                   |                   |                   |                   |                   |   |                   | l |                   |                   |                   |                   |

Figure 2-7 VLAN Stacking Options

- Any other VLAN stacking configuration is considered invalid. As soon as the parser determines

that an invalid combination is present, parsing stops and the Ethernet type of the packet is

captured where parsing stopped. Frames that come in with invalid VLAN tag combinations are

switched but cannot be routed.

- Rate Limiter Tag

- Optionally forwarded to the frame processor if present. The rate limiter tag is used during

congestion management in a tightly coupled system. The port can be configured to skip over

this field even if it is present. The RLT tag can be detected only if the VLAN stacking is one of

the options recognized.

- The rate limiter tag is not detected if the VLAN stack was considered invalid.

- Ethernet Type

- Always forwarded to the frame processor.

#### 2.2.2 Layer 3

FM4000 detects the presence of an IPv4 or IPv6 header by comparing the Ethernet types to the known values for IPv4 and IPv6 Ethernet types and by checking the version field (first 4 bits of the layer 3 header). If the Ethertype is 0x0800 (and the IP version is 4), the frame is parsed as IPv4 frame. If the Ethertype is 0x86dd (and the IP version is 6), the frame is parsed as IPv6. If the Ethertype is 0x8808, it is parsed as a MAC Control frame (most likely a PAUSE frame). In any other case, such as a length value (0x0000-0x0600) in this field, the parsing terminates. FM4000 does not attempt to parse LLC or SNAP encoded packets. The port may be configured to always stop parsing after layer 2, but when layer 3 parsing is required, it proceeds as follows:

#### IPv4:

- The parser always forwards the version, header length, TOS/DS field, packet length, TTL, layer 4 protocol, destination IP and source IP addresses to the frame processor.

- The parser also checks the presence of header options by checking the Internet Header Length (HL) field, stored in bits 4-7 of the IPv4 header. HL is the length of the IPv4 header in 32-bit words, including options. The minimum value of HL is 5, indicating no options; if HL > 5, then options are present. It is not necessary to parse the contents of the IPv4 options. The parser skips over all options.

- The parser also checks if the packet is a fragment, and if it is the first fragment. If it is the first fragment, the layer 4 is processed, otherwise, the parsing stops. The parser detects if it is the first fragment by checking that IPv4 fragment offset in bits 51-63 of the IPv4 header is 0.

- If there is an error during decoding (IP header checksum invalid, invalid HL, etc...), the packet is flagged as having a parse error and the frame is discarded and counted. Note that a trigger action could override the default disposition and possibly trap the packet to the local processor for further processing. Packets that have a parse error are never routed.

- The parser declares the frame as an IP multicast frame if the destination IP address is greater or equal to 224.0.0.0 and declares the frame as an IP unicast otherwise.

#### IPv6:

- The parser always forwards the class, flow, packet length, protocol, TTL, destination and source IP addresses to the frame processor.

- The parser is also capable of detecting the presence of options in the packet by comparing the

protocol field to the known options and skipping over the options if they are present. The parser

stops after the current header if the protocol in the next header does not match one of the

following:

**0x00** = IPv6 Hop-by-Hop Option (length 8N+8 bytes)

**0x2b** = Routing Header for IPv6 (length 8N+8 bytes)

**0x2c** = Fragment Header for IPv6 (length 8 bytes; N is always 0)

**0x3c** = Destination Options for IPv6 (length 8N+8 bytes)

**0x33** = Authentication Header (length **4N+8** bytes -- not the same as the other options)

- The parser also checks if the packet is a fragment, and if it is the first fragment. If it is the first fragment, the layer 4 is processed. Otherwise, the parsing stops. If an IPv6 packet is fragmented, it carries a Fragment Header option. If it has a Fragment Header, and the fragment offset (bits 16-28 of the Fragment Header option) is nonzero, this is not the first fragment.

- If there is an error during decoding (IP header checksum invalid, invalid HL, etc...), the packet is flagged as having a parse error and the frame is discarded and counted. Note that a trigger action could override the default disposition and possibly trap the packet to the local processor for further processing. Packets that have a parse error are never routed.

- The parser declares the frame as an IP multicast frame if the highest byte of the destination IP address is equal to 255 and declares the frame as an IP unicast otherwise.

#### Non IPv4 and IPv6 Packets:

• Each port can be configured to forward the first N bytes to the frame processor for processing. The bytes forwarded are mapped to the DIP, SIP, KEYA, KEYB fields of the Frame Filtering and Forwarding unit.

If the IP packet is fragmented, and this is not the first fragment, parsing terminates at this point because the layer 4 header is not available. The parser verifies the IPv4 fragment offset is in bits 51-63 of the IPv4 header; if the fragment offset is nonzero then this is not the first fragment.

If an IPv6 packet is fragmented, it carries a Fragment Header option. If it has a Fragment Header, and the fragment offset (bits 16-28 of the Fragment Header option) is nonzero, this is not the first fragment.

The port may also be configured to always stop parsing after layer 3, regardless of fragmentation. Any layer 4 fields that are either not parsed or not present due to fragmentation are treated as '0' in the frame processing pipeline.

### 2.2.3 Deep Packet Inspection for IP frames

FM4000 switches have the ability to forward additional frame header bytes to the Frame Handler. This capability is referred to as deep packet inspection. Up to a total of 78 bytes of frame header can be forwarded to the Frame Handler, consisting of normal header bytes and deep packet inspection bytes. This capability is detailed more in the Section 4.0, "Ethernet Port Logic (EPL)".

# 2.3 Frame Processing Pipeline Overview

FM4000 Frame Forwarding is designed to handle wire-speed layer 2/3/4 switching in the context of a single-chip or a multi-chip solution in a variety of topologies. The features offered are:

- Global routing across multi-chip in fat tree, ring or meshed topologies.

- Layer 2 switching with optional automatic address learning and security.

- Layer 3 routing for IPv4 and IPv6 including routing across multiple paths (ECMP).

- Basic and extended Access Control Lists (ACLs) for layer 2 / layer 3 / layer 4 and deep packet inspection.

- Snooping of IGMP v1, v2, and v3.

- Link aggregation across multiple links using various information from frame header to derive hashing function.

- Trapping special frames.

- · Triggers.

- Congestion Management.

- Logging and/or mirroring.

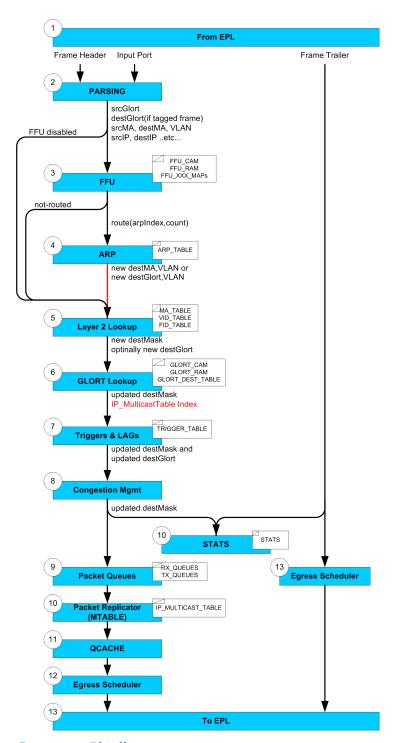

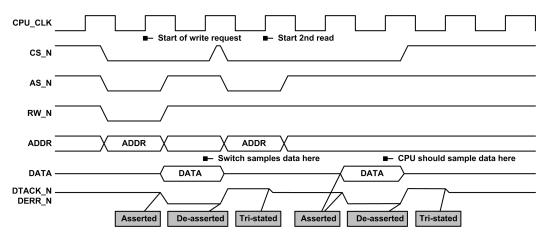

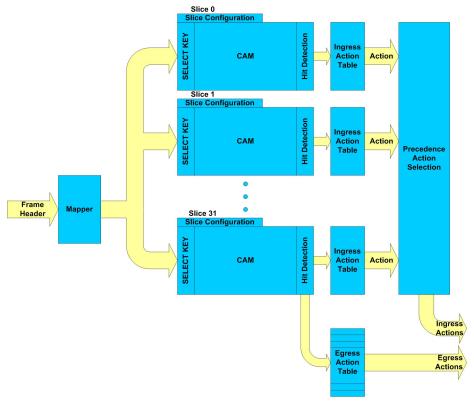

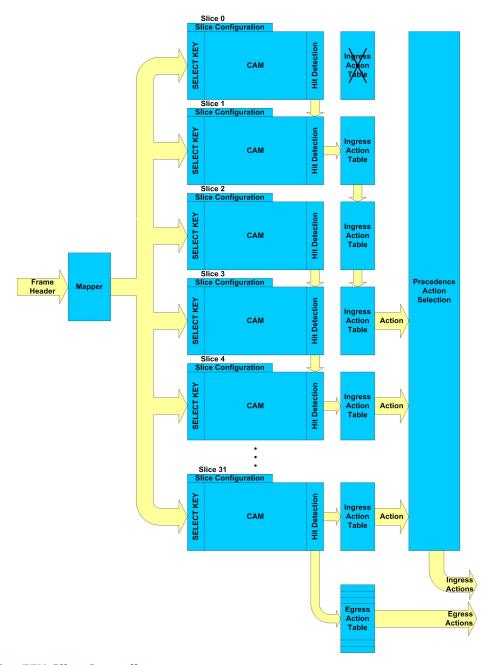

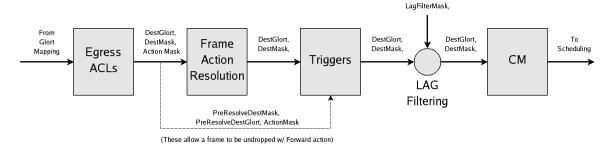

The frame processor pipeline is shown in Figure 2-8. The different elements of this pipeline are briefly described in Section 2.3.1 through Section 2.3.14.

Figure 2-8 Frame Processor Pipeline

#### 2.3.1 Frame Header

The frame header contains the following information:

- Source Port (5 bits)

- Source MAC Address (48 bits)

- Destination MAC Address (48 bits)

- VLAN (12 bits)

- 802.1p priority and CFI/DEI bit (4 bits)

- The 802.1p and CFI/DEI bit are processed as one 4-bit element inside the switch.

- Ethernet Type (16 bits)

- The frame Ethernet type is the first type field after VLAN and RLT tags.

- Type of IP packet (IPv4 or IPv6)

- Source IP (32 or 128 bits)

- Destination IP (32 or 128 bits)

- Layer 4 Source Port (16 bits)

- Layer 4 Destination Port (16 bits)

- Layer 4 Options (6 bits)

- Layer 4 Protocols (8 bits)

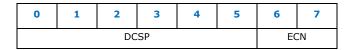

- IP TOS (8 bits)

- IP TTL (8 bits)

- IP Flow ID (20 bits)

- Deep packet inspection:

- Extra bytes extracted after the layer 4 decoding for IP packets and after layer 2 Ethernet type for non IP packets. These extra bytes are passed to the FFU for further processing.

#### ISL tag:

- Switch priority (4 bits)

- Source GLORT (16 bits)

- Destination GLORT (16 bits)

- User info (8 bits)

- Frame Type

**Note:** All non-applicable fields are automatically set to 0b.

The following provides information on how the frame processor forwards a frame.

- The chip always stores and forwards the first 64 bytes as a minimum.

- The chip must parse the entire header before determining an output port. So if more than 64 bytes of header are being parsed, the forwarding decision is not made until this is complete.

- The forwarding decision is made in parallel with receiving the frame. This requires 50-100 ns of processing time per frame.

- Once the frame destination is known, the frame pointer is put into the scheduler, which determines

the next frame to transmit. If the egress port is empty, this is a very small amount of time. If the

frame is corrupt (bad CRC), and this corruption can be detected before the frame is selected for

dequeue in the scheduler, the frame is dropped in the scheduler instead of being transmitted with

bad CRC.

- Once the frame is sent to the egress port, the egress port holds the frame for a some number of EPL cycles (between 6 and 32 cycles) before transmitting. If it gets an indication from the switch element that the frame has been queued enough to guarantee transmission, the hold is released and the frame starts to transmit immediately.

#### 2.3.2 Frame Trailer

The frame trailer contains the following information:

- · Packet Length

- End Of Frame Status (good CRC, bad CRC, symbol error, disparity error, oversize, undersize)

- For statistics

- Packet disposition (discard eligible or forward)

- Frame disposition, i.e. forward normally or discard if possible. Frames marked for discard eligibility:

- Do not cause MAC address learning or security violation events.

- Do not cause trigger interrupts.

- · Cancel PAUSE actions.

- Are not sampled for congestion notification purpose.

- Cancel procession of congestion notification frames.

- Are not forwarded if frame transmission has not yet started (in cut-through mode, the frame transmission may have already been started before the end of frame is received, and the discard flag may come too late to actually delete the frame).

- The following actions are not changed regardless of whether the frame is marked discard eligible or not:

- · Policers are still applied.

- FFU counters are still updated.

- Ingress rate-limiters are still active.

- · SFLOW is still performed.

- Memory management is still performed.

The EPL contains configuration options to select how to mark a frame (discard or forward) depending on the type of errors encountered. The default is to set the discard flag whenever the frame is erroneous for any reason.

#### Note:

End of frame status and packet disposition are used for different purposes. The end of frame status is used for statistics while the packet disposition is used to decide how to dispose of the packet. As an example, a frame with a bad CRC may optionally be marked as forward normally, but is still be counted as a frame with a bad CRC.

#### 2.3.3 GloRT

A GloRT (short for global resource tag) is a 16-bit number that can be used to identify a specific port, link aggregation group, multicast group, management frames or any other packet destination. The term GloRT is sometimes used interchangeably between GloRT values, GloRT actions and GloRT functions. Each FM4000 device must be configured with the following set of GloRTs:

- **Per-port Source GloRT** Whenever a frame arrives without an ISL tag, this source GloRT is associated with the frame. If the frame's source MAC address is learned, this GloRT value is stored in the MAC address table.

- **CPU GloRT** Whenever a frame is trapped or logged or mirrored to the CPU, the top 8 bits of the destination GloRT are set to this value (set in Frame Handler Register TRAP\_GLORT). The bottom eight bits are set to a Trap Code value, chosen by hardware to indicate the reason for sending the frame to the CPU. The set of defined trap codes is listed in Section 5.14.

In addition, other feature-specific GloRTs may also be configured:

- **RX Mirror GloRT** Using the Triggers, a copy of any ingress frame can be copied to one additional RX Mirror destination.

- **TX Mirror GloRT** FM4000 supports a single TX port mirror. All frames sent to a TX port can be copied to a configurable TX Mirror destination GloRT.

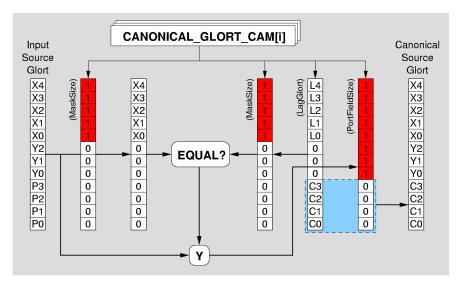

The mapping from GloRT to physical port involves a ternary CAM lookup. This allows the GloRT space to be allocated in a fairly arbitrary manner. The only structure required by the mapping function consists of: (1) a configurable bit range within link aggregation group GloRTs, used to identify individual physical port members; and (2) the fixed eight-bit CPU trap code field within the CPU GloRT.

### 2.3.4 Ethernet Port Logic

The Ethernet Port Logic includes the PCS and MAC layers and is responsible for extracting the Frame Header fields from the packets received while skipping over superfluous fields. The EPL is detailed in Section 4.0, "Ethernet Port Logic (EPL)".

#### 2.3.5 Parsing

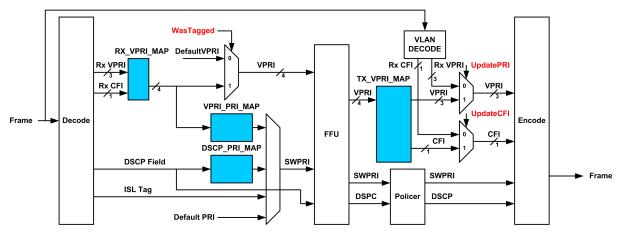

The frame header received is parsed and a switch priority is associated with the frame using one of the following fields:

- Switch priority (ISL tag)

- 802.1p priority

- TOS

- DiffServ

The priority association is detailed in Section 12.0, "QoS and Congestion Management".

## 2.3.6 FFU (Filtering and Forwarding Unit)

The parsed frame header is then presented to a frame Filtering and Forwarding unit which produces a set of orthogonal actions on the frame using different matching rules. The most common actions are: route, permit, deny, count, mirror, trap, and log. This is not an exhaustive list as the FFU also contains less common actions. The FFU contains a 32 x 512 x 36-bit flexible ternary CAM structure along with a set of control registers. The FFU also contains a mapper which maps known fields into smaller entities to improve CAM resource utilization. This mapper includes for example, recognition of specific MAC addresses, compression of IPv6 header and combinations of TCP/UDP port ranges. The FFU organization is detailed in Section 6.0, "Filtering and Forwarding Unit (FFU)".

The default action is "switch" and "permit" in case no matches are found in the FFU. The entire FFU can be disabled.

IP routing is normally done by loading a routing table into the FFU\_CAM (ordered by longest prefix match). Each entry in the table is loaded with a mask, a route entry and a 4-bit field that represents the router's MAC address along with a route action with information about the next hop. The route action includes information on how to index the ARP table.

An IP unicast frame is thus routed if it is addressed to the router's MAC address and is IPv4 (Ethertype is 0800 and header version is 4) or IPv6 (86DD and header version is 6) and the port and the VLAN associated with the frame are marked as routable. If the frame is not addressed to the router's MAC address or comes from a port or VLAN that is not routable, it is switched. If the frame is addressed to the router but is not IPv4 or IPv6, it is trapped to the CPU.

For IP multicast frames, if the frame is not IPv4 or IPv6, or its IP address does not start with the prefix used for IP multicast frames (bits 1110 for IPv4 or bits 1111 1111 for IPv6) and the port or VLAN is not routable, then the multicast frame is L2 switched only. If the frame is an IP frame with a proper IP multicast MAC address, the frame is both switched and routed at the same time. It needs to get switched to multicast destinations on the same VLAN, and also routed to multicast destinations on other VLANs. Although the frame is technically both switched and routed, FM4000 treats it more as being routed, because it looks up the frame by IP address in the FFU, rather than by MAC address in the MAC table. Other entries can coexist in the CAM to produce ACLs allowing specific frames to be denied or permitted and then optionally counted, logged, trapped or mirrored.

#### 2.3.7 ARP Unit

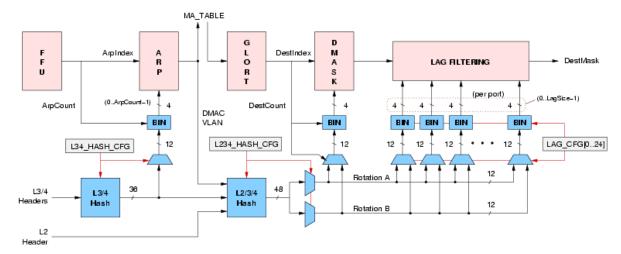

The route action includes an ARP Table index and the number of possible paths. If the number of paths is k, the FM4000 picks a number between 0 and k-1 to add to the ARP Table index, to get the actual index into the ARP table which is used to read the ARP table. This number is picked using a hash of the frame, using the hard threshold algorithm, which means using division (not modulo) to divide the hash range into equal-sized buckets.

The 16 K ARP table contains either a destination GloRT/VLAN or a MAC/VLAN address pair or a VLAN/ flag. The GloRT is typically used for IP multicasting (see Section 2.3.3 and Section 9.4) or for specialized multi-chip systems. The VLAN/MAC address is typically used for IP unicast traffic where the VLAN/MAC address specifies the next hop. The VLAN/flag is used for IPv6 unicast when the destination is retrieved from the lower 48 bits of the address. Multicast MAC addresses are classified after the ARP table.

**Note:** Disabling the FFU causes the routing step to be bypassed as well.

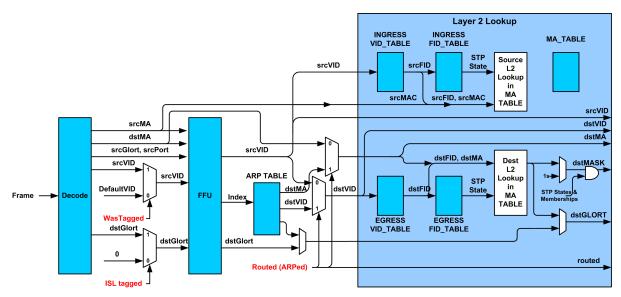

### 2.3.8 Layer 2 Lookup Unit

The layer 2 Lookup Unit includes a VLAN table (VID\_TABLE), a spanning-tree state table (FID\_TABLE) and a MAC address table (MA\_TABLE). The layer 2 lookup first uses the destination MAC address and the VLAN port to retrieve the logical destination port (GloRT) from the MA\_TABLE, and then uses the VLAN to retrieve a spanning-tree number and VLAN disposition, and uses the FID\_TABLE to retrieve the spanning tree state. If the destination address is unknown, the packet is flooded using a flood GloRT. The address can also be automatically learned or raise security violations depending on configuration of the switch.

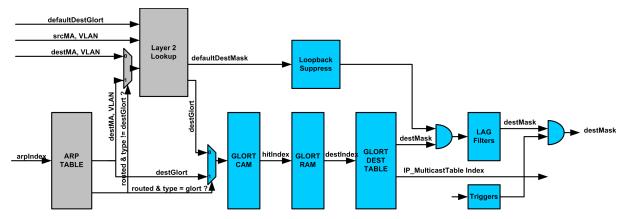

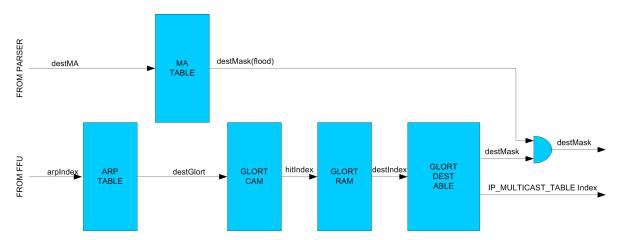

### 2.3.9 GloRT Lookup

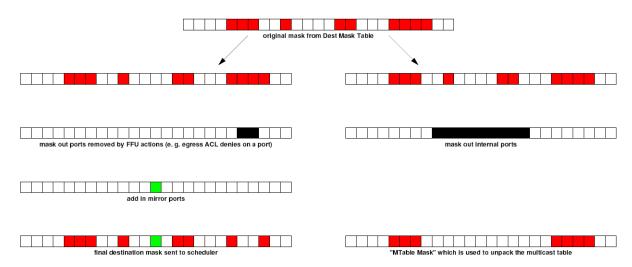

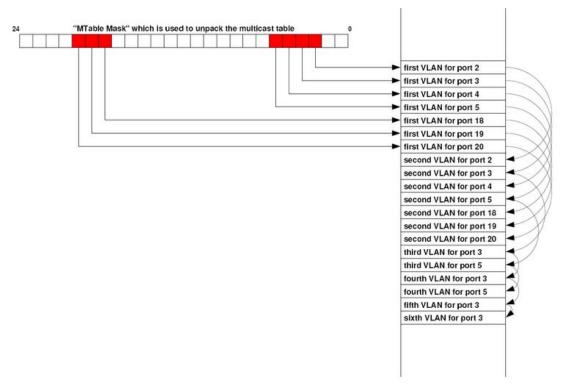

This unit is responsible to map a destination GloRT into a destination mask, IP multicast replicator index and to implement link aggregation.

There are multiple possible sources for the destination GloRTs:

- The frame may contain an ISL tag which contains the destination GloRT

- The FFU may trigger a route command which may include a new destination GloRT

- The ARP table may include a new destination GloRT

- The MAC table may include a new destination GloRT

- A default GloRT is assigned (GloRT-flood, GloRT-broadcast) otherwise

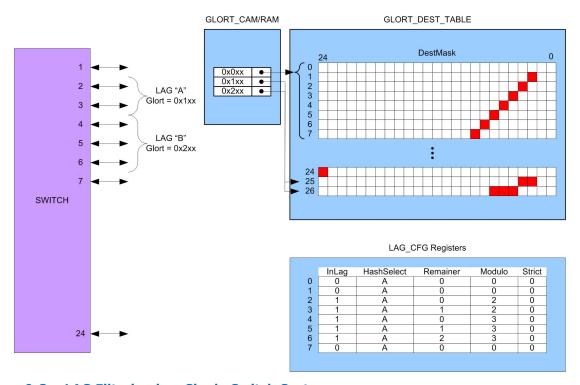

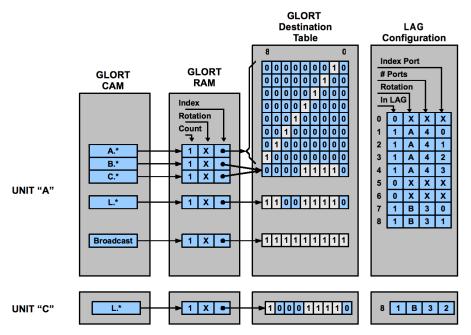

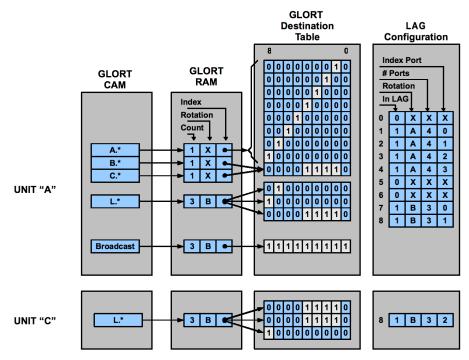

The GloRT Lookup Unit contains three tables: the GloRT CAM, the GloRT RAM and the Destination Table.

The GloRT CAM is a 256-entry ternary CAM used to search the destGloRT. The GloRT RAM is simply a RAM with one-to-one correspondence with the GloRT CAM, and which contains the data associated with each entry of the GloRT CAM. This data includes a base pointer to the destination table, the number of links in the group and one or two sub-indexes retrieved from the destination GloRT itself.

The unit uses this information to compute an index and retrieve a final destination mask which contains one bit per output port where the frame is delivered, along with an IP multicast index, which is only required if multicasting IP frames across multiple VLANs.

The unit also implements link aggregation pruning to load balance traffic across multiple links.

### 2.3.10 Triggers and Link Aggregation Units

The triggers are low-level elements that can be used to modify traffic flows. There are up to 64 triggers. The details of the triggers can be found in Section 11.0, "Triggers". The output of a trigger is a destination mask and an updated destination GloRT. The destination mask is ANDed with the link aggregation destination mask.

The link aggregation mask uses the result of hashing over the frame to determine which port of a link aggregation group is used to transmit the frame.

## 2.3.11 Congestion Management

The congestion management maintains information about the size of the different queues and can mark, discard and/or send congestion management frames back to the originator when the size of queues exceeds certain limits.

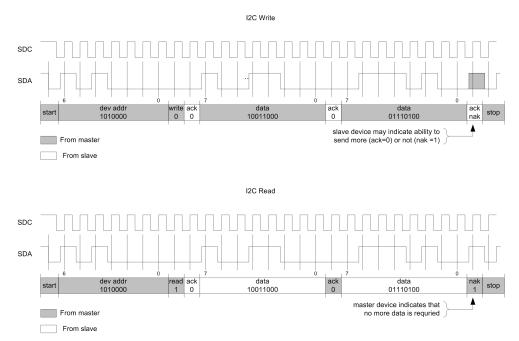

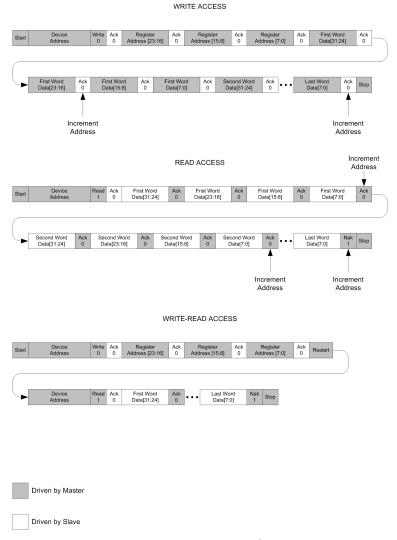

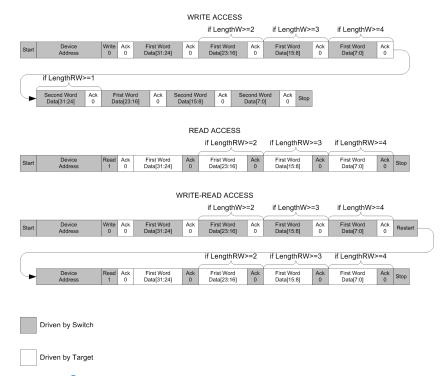

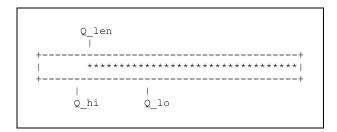

### 2.3.12 Packet Queues