# Integrated Digital Receiver/Rate Converter

AD1892

#### **FEATURES**

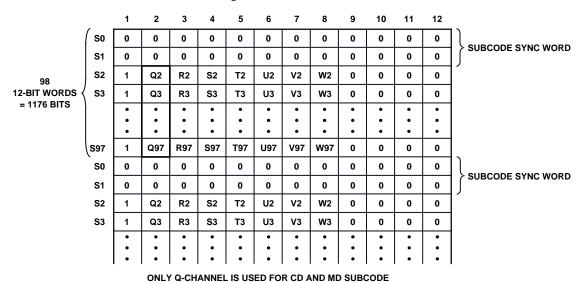

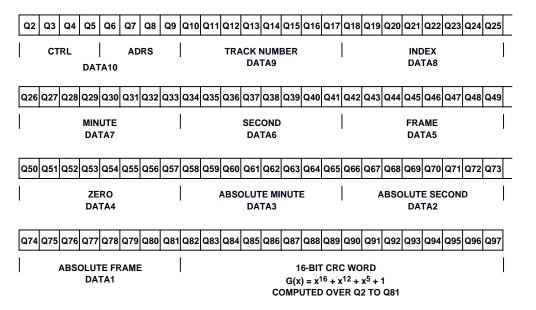

Complete EIAJ CP-340 (CP-1201), IEC-958, AES/EBU, S/PDIF Compatible Digital Audio Receiver and **Asynchronous Sample Rate Converter** Status Pins and Microprocessor Interfaces for Stand-Alone and Microcontroller-Oriented Operation Integrated Channel Status Buffer and Q-Channel Subcode Buffer (Supports EIAJ CP-2401) 20-Bit SamplePort® Architecture Provides Superb Jitter Rejection on Input Port Sample Rate Conversion from 8 kHz to 48 kHz with 1:5 Upsampling Range 1:0.85 Downsampling Range 120 dB Dynamic Range -113 dB THD+N @ 1 kHz CRC Calculation on Q-Channel Subcode (Consumer Mode Only) and on Channel Status (Pro Mode Only) Four-Wire SPI™ Compatible Serial Control Port

Power-Down Mode Single +5 V Supply

**Mute Input Pin**

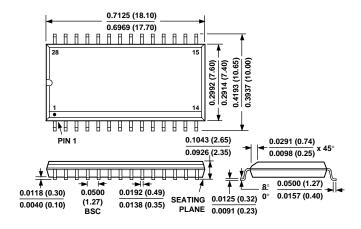

Flexible Three-Wire Serial Data Port with Left-Justified, Right-Justified and I<sup>2</sup>S-Compatible Modes 28-Lead SOIC Package

#### **APPLICATIONS**

DVD, DAT, MD, DCC and CD-R Recorders and Players Computer Multimedia Products DAB Receivers, Automotive Digital Audio Networks

#### PRODUCT OVERVIEW

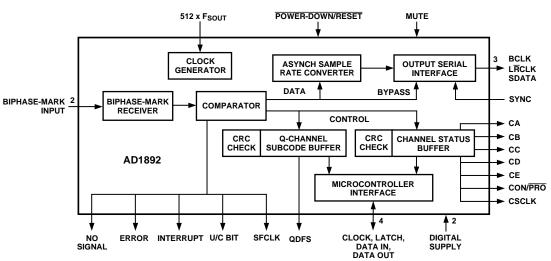

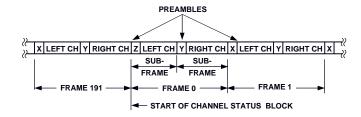

The AD1892 combines a CP-1201, CP-340, IEC-958, AES/EBU, S/PDIF compatible Digital Audio Receiver (DAR) with an asynchronous sample rate converter, allowing the user to specify the output sample rate of the received digital audio information. The DAR block features support for both Q-channel subcode information (to support CD, CD-R, MD and DAT digital audio formats) as well as Channel Status information. A microcontroller interface, with an SPI compatible serial port, allows full access to the 80-bit Q-Channel subcode buffer and to the 32-bit Channel Status buffer, as well as to the control and status registers. Additionally, key status information from the incoming subframes and the Channel Status buffer is reported on status output pins on the AD1892, so the AD1892 may be used in systems that do not include a microcontroller or microprocessor.

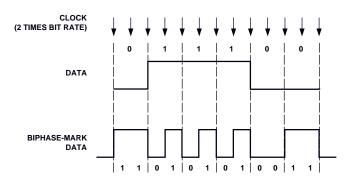

The asynchronous sample rate converter block is based on market leading AD1890 family SamplePort rate conversion technology. The AD1892 offers a 1:5 upsampling range, and will downsample from 48 kHz to 44.1 kHz. Input audio word widths up to 20 bits are supported, and output audio word widths of 16 or 20 are supported, with 120 dB of dynamic range and –113 dB THD+N. The rate converter inherently rejects jitter on the recovered clocks from the incoming biphase-mark encoded stream. Indeed, sample rate conversion is highly synergistic with digital audio reception, allowing the use of a fully digital phase locked loop clock recovery scheme with highly robust clock recovery and jitter rejection.

(continued on Page 4)

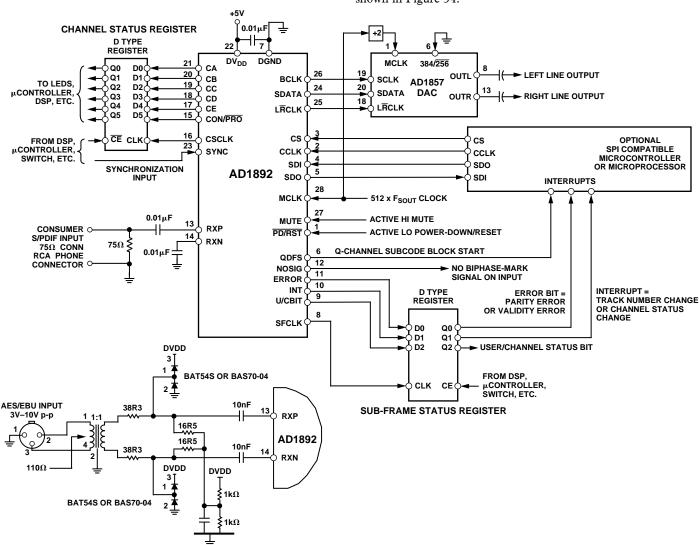

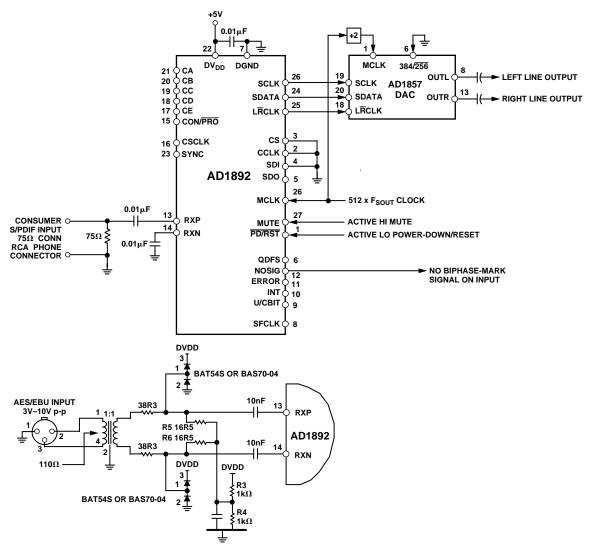

#### FUNCTIONAL BLOCK DIAGRAM

SamplePort is a registered trademark of Analog Devices, Inc. SPI is a trademark of Motorola, Inc.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

### AD1892-SPECIFICATIONS

#### TEST CONDITIONS UNLESS OTHERWISE NOTED

MCLK 25 MHz (512  $\times$  F<sub>SOUT</sub>)

Input Word Width 20 Bit Load Capacitance 100 pF All minimums and maximums tested except as noted.

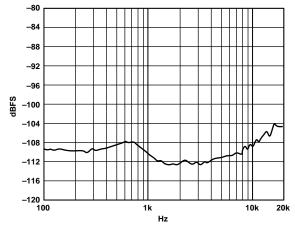

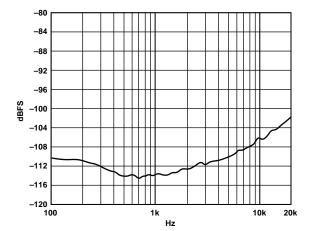

#### PERFORMANCE1

|                                               | Min | Typ | Max  | Units   |

|-----------------------------------------------|-----|-----|------|---------|

| Dynamic Range (20 Hz to 20 kHz, -60 dB Input) | 120 |     |      | dB      |

| Total Harmonic Distortion + Noise             |     |     |      |         |

| (20 Hz to 20 kHz, Full-Scale Input)           |     |     | -103 | dB      |

| (1 kHz Full-Scale Input)                      |     |     | -113 | dB      |

| (10 kHz Full-Scale Input)                     |     |     | -107 | dB      |

| Interchannel Phase Deviation                  |     |     | 0    | Degrees |

#### DIGITAL I/O1

|                                       | Min    | Тур     | Max | Units |

|---------------------------------------|--------|---------|-----|-------|

| $ m V_{IH}$                           | 2.4    |         |     | V     |

| $ m V_{IL}$                           |        |         | 0.8 | V     |

| $I_{IH} @ V_{IH} = +5.0 \text{ V}$    |        |         | 10  | μΑ    |

| $I_{IL} @ V_{IL} = 0 V$               |        |         | 10  | μA    |

| $V_{OH}$ @ $I_{OH} = -0.5 \text{ mA}$ | DVDD - | - (0.5) |     | V     |

| $V_{OL}$ @ $I_{OL} = 0.5 \text{ mA}$  |        |         | 0.5 | V     |

| Input Capacitance <sup>1</sup>        |        | 15      |     | pF    |

#### DIGITAL TIMING<sup>1</sup>

|                     |                                                    | Min            | Typ       | Max | Units |

|---------------------|----------------------------------------------------|----------------|-----------|-----|-------|

| $t_{MCP}$           | MCLK Duty Cycle <sup>1</sup>                       | 40             |           | 60  | %     |

| $F_{MCLK}$          | MCLK Frequency $(1/t_{MCP})^1$                     |                |           | 25  | MHz   |

| $t_{\mathrm{PDRP}}$ | PD/RST LO Pulsewidth                               | $10 \times MC$ | LK Period |     | ns    |

| $t_{ m BDM}$        | BCLK Propagation Delay from MCLK (to Falling Edge) |                |           | 30  | ns    |

| $t_{ m LDM}$        | $L\overline{R}CLK$ Propagation Delay from MCLK     |                |           | 30  | ns    |

| $t_{ m DDP}$        | Data Propagation Delay from MCLK                   |                |           | 30  | ns    |

| $t_{ m DDS}$        | Data Output Setup to BCLK                          | 1/2 BCL        | K Period  |     | ns    |

| $t_{ m DDH}$        | Data Output Hold from BCLK                         | 1/2 BCL        | K Period  |     | ns    |

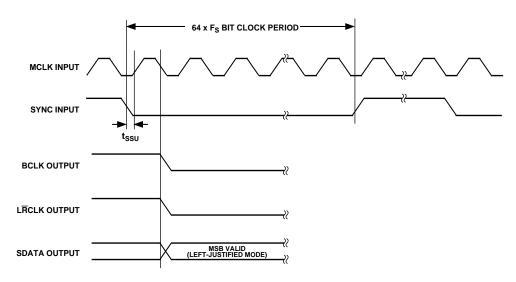

| $t_{SSU}$           | SYNC Falling Setup to MCLK Rising                  | 5              |           |     | ns    |

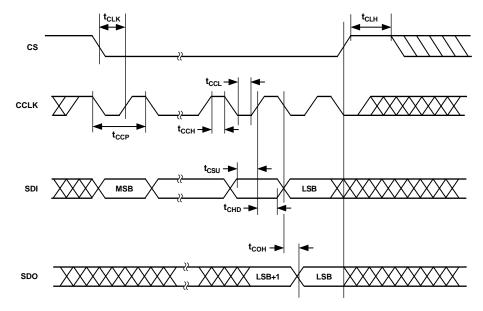

| $t_{CCH}$           | CCLK HI Pulsewidth                                 | 20             |           |     | ns    |

| $t_{CCL}$           | CCLK LO Pulsewidth                                 | 20             |           |     | ns    |

| $t_{CCP}$           | CCLK Period                                        | $8 \times MCL$ | K Period  |     | ns    |

| $t_{CSU}$           | SDI Setup                                          | 15             |           |     | ns    |

| $t_{ m CHD}$        | SDI Hold                                           | 10             |           |     | ns    |

| $t_{COH}$           | SDO Propagation Delay from CCLK                    |                |           | 30  | ns    |

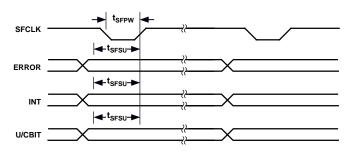

| $t_{SFPW}$          | SFCLK HI Pulsewidth <sup>1</sup>                   | 100            |           |     | ns    |

| $t_{SFSU}$          | U/CBIT, INT, ERROR Setup to SFCLK                  | 100            |           |     | ns    |

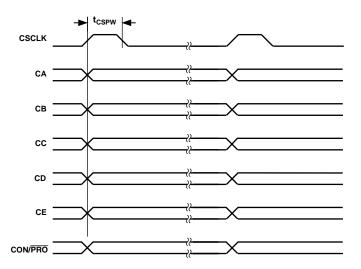

| $t_{CSPW}$          | CSCLK HI Pulsewidth <sup>1</sup>                   | 100            |           |     | ns    |

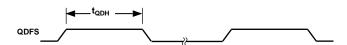

| $t_{\mathrm{QDH}}$  | QDFS HI Pulsewidth <sup>1</sup>                    | 1000           |           |     | ns    |

| $t_{CLH}$           | CS HI Pulsewidth                                   | $10 \times MC$ | LK Period |     | ns    |

| $t_{CLK}$           | CS Falling Edge to CCLK Rising                     | $3 \times MCL$ | K Period  |     | ns    |

| $t_{RS}$            | PD/RST Rising to MCLK Rising Edge (Only Required   |                |           |     |       |

|                     | for Synchronizing Multiple Parts)                  | 5              |           |     | ns    |

#### DIGITAL RS-422 RECEIVERS (RXP, RXN Pins Only)

|                                          | Min | Typ | Max | Units  |

|------------------------------------------|-----|-----|-----|--------|

| Input Resistance                         |     | 20  |     | kΩ     |

| Min Differential AES/EBU or S/PDIF Input | 200 |     |     | mV p-p |

| Input Hysteresis                         |     | 20  |     | mV     |

-2- REV. 0

#### **POWER**

|                                                                                    | Min | Typ | Max | Units |

|------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supplies                                                                           |     |     |     |       |

| Voltage, DV <sub>DD</sub>                                                          | 4.5 |     | 5.5 | V     |

| Operational Current, $I_{DD}$ (DV <sub>DD</sub> = +5.0 V)                          |     | 50  | 60  | mA    |

| Power-Down Current, $I_{DD}$ (DV <sub>DD</sub> = +5.0 V) ( $\overline{PD/RST}$ LO) |     | 3   | 6   | mA    |

| Dissipation <sup>1</sup>                                                           |     |     |     |       |

| Operational (DV <sub>DD</sub> = $+5.0 \text{ V}$ )                                 |     | 250 | 300 | mW    |

| Power-Down (DV <sub>DD</sub> = +5.0 V) ( $\overline{PD/RST}$ LO)                   |     | 15  | 30  | mW    |

#### TEMPERATURE RANGE

|                           | Min        | Max  | Units |

|---------------------------|------------|------|-------|

| Specifications Guaranteed | -40        | +85  | °C    |

| Storage                   | <b>-55</b> | +125 | °C    |

#### ABSOLUTE MAXIMUM RATINGS<sup>2</sup>

|                          | Min  | Max             | Units |

|--------------------------|------|-----------------|-------|

| DV <sub>DD</sub> to DGND | -0.3 | 7.0             | V     |

| DC Input Voltage         | -0.3 | $DV_{DD} + 0.3$ | V     |

| Soldering                |      | +300            | °C    |

|                          |      | 10              | sec   |

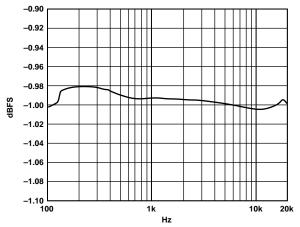

#### DIGITAL FILTER CHARACTERISTICS1

|                                                                | Min | Max    | Units |

|----------------------------------------------------------------|-----|--------|-------|

| Passband Ripple (0 kHz to 20 kHz) ( $F_S = 44.1 \text{ kHz}$ ) |     | ±0.015 | dB    |

| Group Delay (LRCLK = 50 kHz)                                   | 700 | 3000   | μs    |

#### NOTES

<sup>1</sup>Guaranteed, not tested.

Specifications subject to change without notice.

#### **ORDERING GUIDE**

| Model      | Temperature Range | Package Description | Package Options   |

|------------|-------------------|---------------------|-------------------|

| AD1892JR   | −40°C to +85°C    | 28-Lead SOIC        | R-28              |

| AD1892JRRL | −40°C to +85°C    | 28-Lead SOIC        | R-28 on 13" Reels |

#### CAUTION-

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1892 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

<sup>&</sup>lt;sup>2</sup>Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(continued from Page 1)

#### PRODUCT OVERVIEW (Continued)

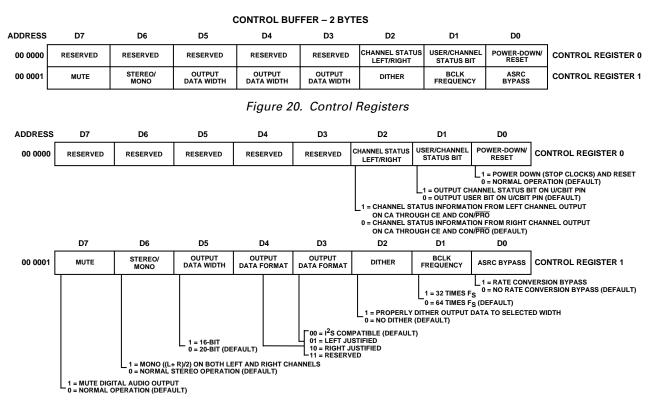

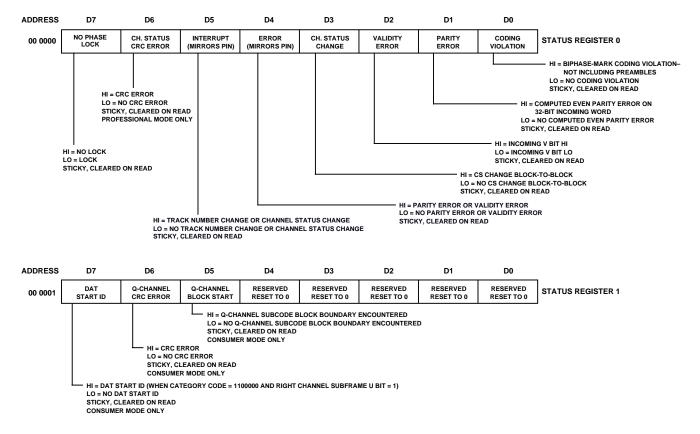

In addition to the Q-channel subcode and Channel Status buffers, the AD1892 includes two 8-bit control registers and two 8-bit status registers. The output data interface may be configured in left-justified, I²S-justified and right-justified modes. The AD1892 includes hardware power-down/reset and mute control inputs, and power-down/reset and mute may also be invoked through write to bits in the control registers. The AD1892 operates from a master clock that must be synchronous with the output sample rate at  $512 \times F_8$ . Cyclic Redundancy Coding (CRC) error detection is performed over the full 80 bits of the received Q-channel subcode information in consumer mode, as well as the full 192 bits of the received Channel Status information in professional mode.

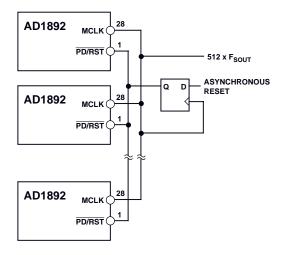

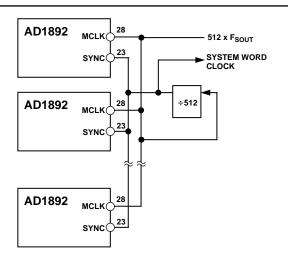

The AD1892 includes a SYNC input (Pin 23) that allows multiple AD1892s in a system to be synchronized to a common LEFT/RIGHT clock.

The AD1892 is offered in a 28-lead SOIC package. It operates over the industrial temperature range from -40°C to +85°C at a supply voltage from 4.5 V to 5.5 V. The only external components required to support the AD1892 are power supply decoupling capacitors.

#### **DEFINITIONS**

#### **Dynamic Range**

The ratio of a full-scale input signal to the integrated noise in the passband (0 kHz to  $\approx 20$  kHz), expressed in decibels (dB). Dynamic range is measured with a -60 dB input signal and "60 dB" arithmetically added to the result. This measurement technique is consistent with the recommendations of the Audio Engineering Society (AES17-1991) and the Electronic Industries Association of Japan (EIAJ CP-307).

#### **Total Harmonic Distortion + Noise**

Total Harmonic Distortion plus Noise (THD+N) is defined as the ratio of the square root of the sum of the squares of the values of the harmonics and noise to the value of the fundamental input frequency. It is usually expressed in percent (%) or decibels.

#### **Interchannel Phase Deviation**

Difference in input sampling times between stereo channels, expressed as a phase difference in degrees between 1 kHz inputs.

#### **Group Delay**

The time interval required for the frequency components of an input pulse to appear at the converter's output, expressed in milliseconds (ms). More precisely, the derivative of radian phase with respect to radian frequency at a given frequency.

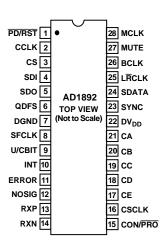

#### AD1892 PIN LIST

| Biphase-Ma | ırk Serial | Input |

|------------|------------|-------|

|            |            |       |

| Pin Name | SOIC | I/O | Description                                                                               |

|----------|------|-----|-------------------------------------------------------------------------------------------|

| RXP      | 13   | I   | Positive differential biphase-mark serial digital audio receiver input. 20 mV hysteresis. |

| RXN      | 14   | I   | Negative differential biphase-mark serial digital audio receiver input. 20 mV hysteresis. |

#### **Serial Output Interface**

| Pin Name | SOIC | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

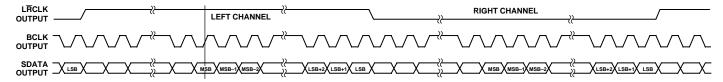

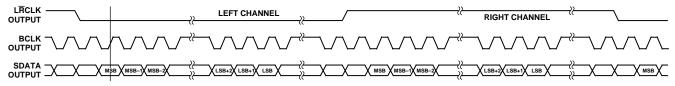

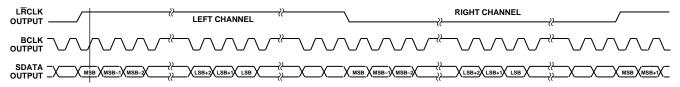

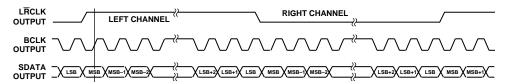

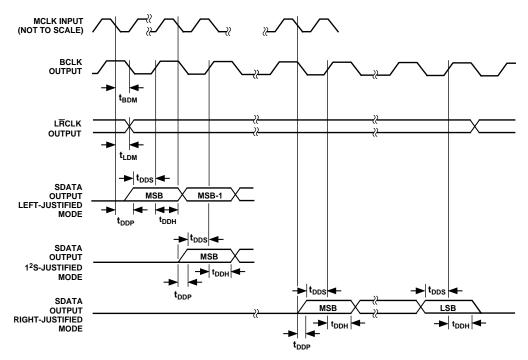

| SDATA    | 24   | 0   | Serial output, MSB first, containing two channels of 16 to 20 bits (default) of twos-complement data per channel, depending on control register settings. The data can be configured in I <sup>2</sup> S-justified (default), left-justified, and right-justified orientations, depending on control register settings. See Figure 36 for timing.                                                                                                                                                        |

| BCLK     | 26   | О   | Bit clock output for output data. Frequency is either $32 \times F_S$ (packed mode) or $64 \times F_S$ (default), depending on control register settings. See Figure 36 for timing.                                                                                                                                                                                                                                                                                                                      |

| LRCLK    | 25   | О   | LEFT/RIGHT clock output for output data. Runs continuously and is a synchronous divide-down from MCLK (MCLK/512). See Figure 36 for timing.                                                                                                                                                                                                                                                                                                                                                              |

| SYNC     | 23   | I   | The SYNC input allows multiple AD1892s in a system to be phase and group delay synchronized to the same LEFT/ $\overline{RIGHT}$ clock. The SYNC signal resets internal AD1892 counters such that 512 MCLK cycles after the falling edge of SYNC, the AD1892 data will be valid, and the AD1892 L $\overline{R}$ CLK signal will change state. It is recommended that the SYNC input be used only when the AD1892 is in the $64 \times F_{SOUT}$ BCLK mode (default configuration). GND when not in use. |

#### **Decoded Channel Status Outputs**

| Pin Name | SOIC | I/O | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA       | 21   | 0   | In consumer or professional mode, CA is the inverse of Channel Status Bit 1, Byte 0 $\overline{\text{C1}}$ , audio/nonaudio). CA = 0 indicates nonaudio, CA = 1 indicates audio. CA = 0 can be used to indicate Dolby AC-3 encoded data.                                                                                                                           |

| СВ       | 20   | O   | In consumer mode, CB is the inverse of Channel Status Bit 2, Byte 0 ( $\overline{C2}$ , copy/copyright). CB = 0 indicates copy permitted/copyright not asserted; CB = 1 indicates copy inhibited/copyright asserted. In professional mode, CB is defined as EM0, the least significant bit of the two bits that encodes the emphasis status of the audio material. |

-4- REV. 0

#### **Decoded Channel Status Outputs (Continued)**

| Pin Name | SOIC    | I/O | Desci                                                                                                                        | ription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CC       | 19      | 0   | indica                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | audio m                                                                                                                                                                        | naterial has                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                            | tatus Bit 3, Byte 0 ( $\overline{C3}$ , pre-emphasis). CC = 0 aphasized; CC = 1 indicates that the audio material                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|          |         |     | In professional mode, CC is the most significant bit of the two bits that encodes the emphasis status of the audio material. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |         |     | Table I illustrates the professional mode emphasis encoding.                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |         |     |                                                                                                                              | Table I. Professional Mode Emphasis Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |         |     | A                                                                                                                            | D1892                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                | BYTE (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |         |     |                                                                                                                              | utput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                | Channel Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                            | Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|          |         |     | CC                                                                                                                           | CB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C2                                                                                                                                                                             | C3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C4                                                                                                                                                                                                                                         | Status  Emphasis not indicated Passivan defaults to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

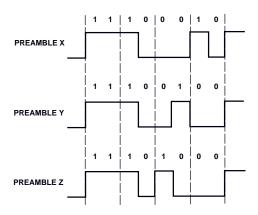

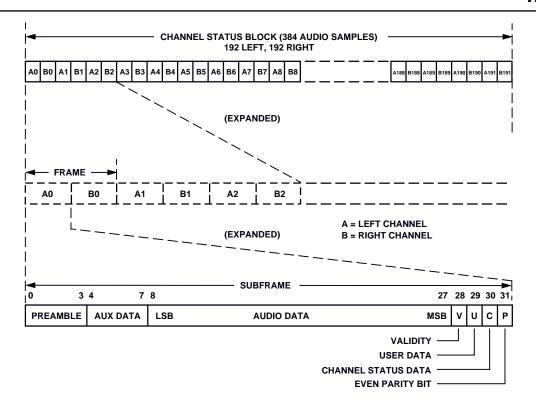

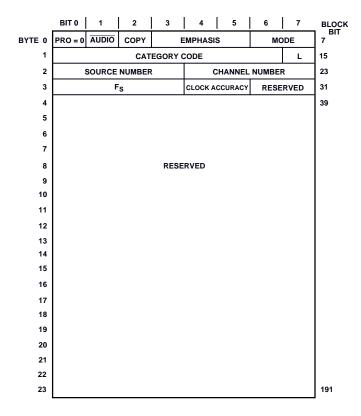

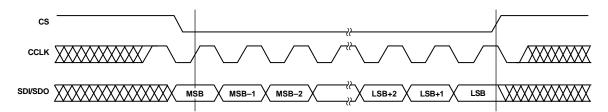

|          |         |     | 1                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                          | Emphasis not indicated. Receiver defaults to no emphasis with manual override enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |