## Low Noise, Fast, Quad Universal Filter Building Block

#### **FEATURES**

- Four Filters in a 0.3 Inch Wide Package

- Maximum Center Frequency: 140kHz

- Customized Version with Internal Resistors Available

- One Half the Noise of the LTC1059/LTC1060/ LTC1061 Devices

- Maximum Clock Frequency: 7MHz

- Clock-to-Center Frequency Ratio of 50:1 and 100:1 Simultaneously Available

- Power Supplies: ±2.375V to ±8V

- Low Offsets

- Low Harmonic Distortion

- Available in 24-Pin DIP and SO Wide Packages

## **APPLICATIONS**

- Anti-Aliasing Filters

- Wide Frequency Range Tracking Filters

- Spectral Analysis

- Loop Filters

## DESCRIPTION

The LTC®1064 consists of four high speed, low noise switched-capacitor filter building blocks. Each filter building block, together with an external clock and three to five resistors can provide various 2nd order functions like lowpass, highpass, bandpass and notch. The center frequency of each 2nd order function can be tuned with an external clock, or a clock and resistor ratio. For Q  $\leq$  5, the center frequency range is from 0.1Hz to 100kHz. For Q  $\leq$  3, the center frequency range can be extended to 140kHz. Up to 8th order filters can be realized by cascading all four 2nd order sections. Any classical filter realization (such as Butterworth, Cauer, Bessel and Chebyshev) can be formed.

A customized monolithic version of the LTC1064 including internal thin film resistors can be obtained for high volume applications. Consult LTC Marketing for details.

LTC and LT are registered trademarks of Linear Technology Corporation. LTCMOS is a trademark of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

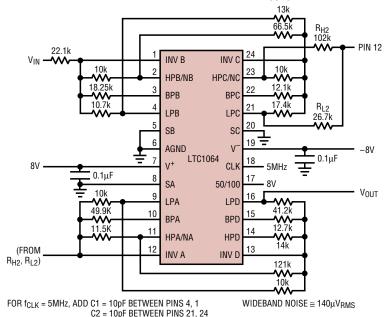

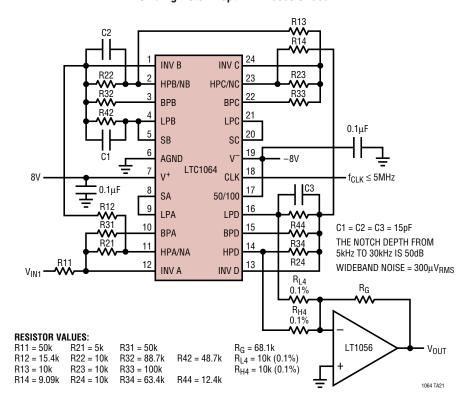

## TYPICAL APPLICATION

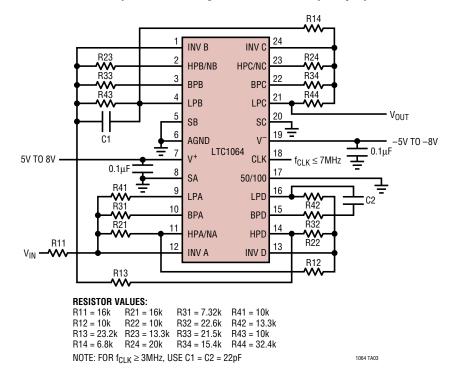

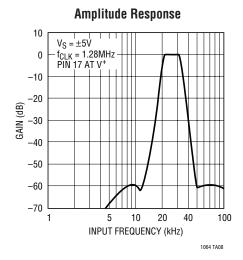

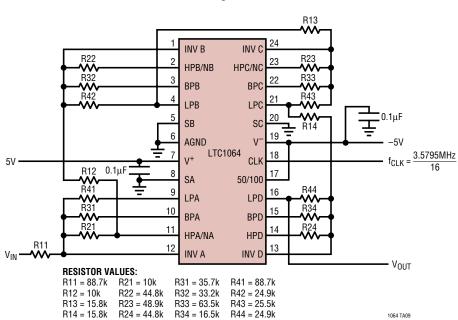

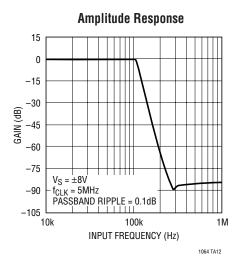

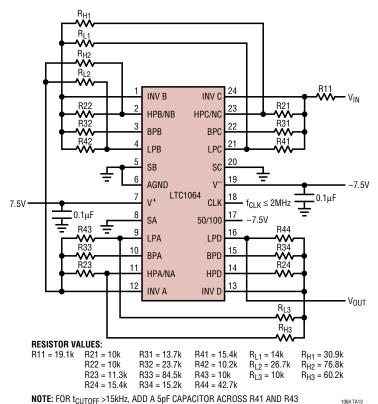

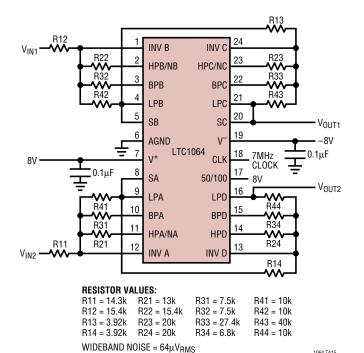

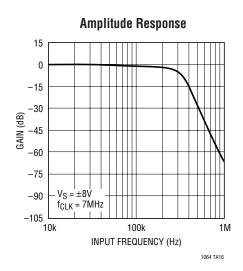

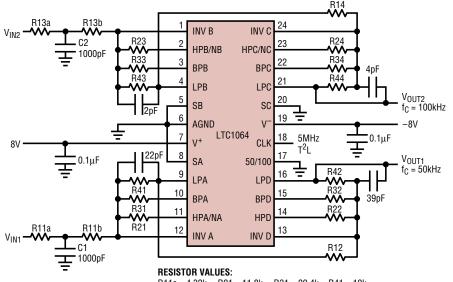

Clock-Tunable 8th Order Cauer Lowpass Filter with f<sub>CUTOFF</sub> up to 100kHz

1064 TA01

C3 = 27pF BETWEEN PINS 9, 12

1064fb

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

Storage Temperature Range ...... -65°C to 150°C Lead Temperature (Soldering, 10 sec) ...... 300°C

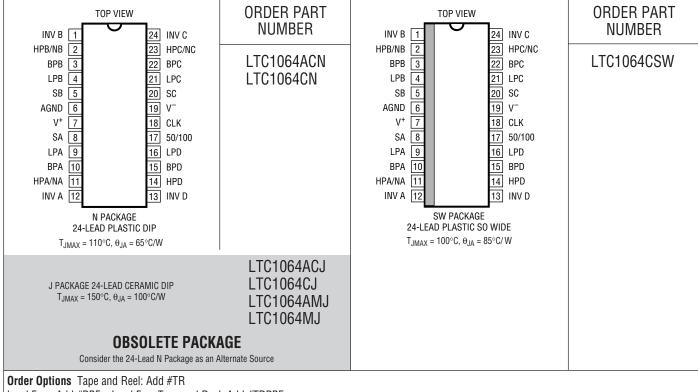

## PACKAGE/ORDER INFORMATION

Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF Lead Free Part Marking: http://www.linear.com/leadfree/

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** (Internal Op Amps) The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| PARAMETER                                  | CONDITIONS               |   | MIN    | TYP  | MAX | UNITS  |

|--------------------------------------------|--------------------------|---|--------|------|-----|--------|

| Operating Supply Voltage Range             |                          |   | ±2.375 |      | ±8  | V      |

| Voltage Swings                             | $V_S = \pm 5V, R_L = 5k$ |   | ±3.2   | ±3.6 |     | V      |

|                                            |                          | • | ±3.1   |      |     | V      |

| Output Short-Circuit Current (Source/Sink) | $V_S = \pm 5V$           |   |        | 3    |     | mA     |

| DC Open-Loop Gain                          | $V_S = \pm 5V, R_L = 5k$ |   |        | 80   |     | dB     |

| GBW Product                                | V <sub>S</sub> = ±5V     |   |        | 7    |     | MHz    |

| Slew Rate                                  | V <sub>S</sub> = ±5V     |   |        | 10   |     | V/µs   |

|                                            |                          |   |        |      |     | 1064fb |

| PARAMETER                                                                     |                               | CONDITIONS                                                                                                                                                                                |   | MIN | TYP           | MAX           | UNITS             |

|-------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---------------|---------------|-------------------|

| Center Frequency Range, f <sub>0</sub>                                        |                               | $V_S = \pm 8V, Q \le 3$                                                                                                                                                                   |   |     | 0.1 to 140    |               | kHz               |

| Input Frequency Range                                                         |                               |                                                                                                                                                                                           |   |     | 0 to 1        |               | MHz               |

| Clock-to-Center Frequency<br>Ratio, f <sub>CLK</sub> /f <sub>0</sub>          | LTC1064<br>LTC1064A (Note 2)  | f <sub>CLK</sub> = 1MHz, f <sub>0</sub> = 20kHz, Pin 17 High<br>Sides A, B, C: Mode 1,<br>R1 = R3 = 5k, R2 = 5k, Q = 10,                                                                  | • |     | 50 ± 0.3      | 50 ± 0.8      | %<br>%            |

|                                                                               |                               | Sides D: Mode 3, R1 = R3 = 50k<br>R2 = R4 = 5k                                                                                                                                            | • |     |               | $50 \pm 0.9$  | %                 |

|                                                                               | LTC1064<br>LTC1064A (Note 2)  | Same as Above, Pin 17 Low, f <sub>CLK</sub> = 1MHz<br>f <sub>0</sub> = 10kHz<br>Sides A, B, C                                                                                             |   |     | $100 \pm 0.3$ | 100 ± 0.8     | %                 |

|                                                                               |                               | Side D                                                                                                                                                                                    | • |     |               | $100 \pm 0.0$ | /0                |

| Clock-to-Center Frequency<br>Ratio, Side-to-Side Matching                     | LTC1064<br>LTC1064A (Note 2)  | f <sub>CLK</sub> = 1MHz                                                                                                                                                                   | • |     | 0.4           | 1             | %<br>%            |

| Clock-to-Center Frequency<br>Ratio, f <sub>CLK</sub> /f <sub>0</sub> (Note 3) | LTC1064<br>LTC1064A (Note 2)  | $f_{CLK} = 4MHz, f_0 = 80kHz, Pin 17 High$<br>Sides A, B, C: Mode 1, $V_S = \pm 7.5V$<br>R1 = R3 = 50k, R2 = 5k, Q = 5<br>Side D: Mode 3, R1 = R3 = 50k<br>R2 = R4 = 5k, $f_{CLK} = 4MHz$ |   |     | 50 ± 0.6      | 50 ± 1.3      | %<br>%            |

|                                                                               | LTC1064<br>LTC1064 A (Note 2) | Same as Above, Pin 17 Low f <sub>CLK</sub> = 4MHz, f <sub>O</sub> = 40kHz                                                                                                                 |   |     | $100 \pm 0.6$ | 100 ± 1.3     | %<br>%            |

| Q Accuracy                                                                    |                               | Sides A, B, C: Mode 1, Q = 10<br>Side D: Mode 3, f <sub>CLK</sub> = 1MHz                                                                                                                  | • |     | ±2<br>±3      | 6<br>8        | %<br>%            |

| f <sub>0</sub> Temperature Coefficient                                        |                               | Mode 1, 50:1, f <sub>CLK</sub> < 2MHz                                                                                                                                                     |   |     | ±1            |               | ppm/°C            |

| Q Temperature Coefficient                                                     |                               | Mode 1, 100:1, f <sub>CLK</sub> < 2MHz                                                                                                                                                    |   |     | ±5            |               | ppm/°C            |

|                                                                               |                               | Mode 3, f <sub>CLK</sub> < 2MHz                                                                                                                                                           |   |     | ±5            |               | ppm/°C            |

| DC Offset Voltage                                                             | V <sub>OS1</sub> (Table 1)    | f <sub>CLK</sub> = 1MHz, 50:1 or 100:1                                                                                                                                                    | • |     | 2             | 15            | mV                |

|                                                                               | V <sub>OS2</sub> (Table 1)    | f <sub>CLK</sub> = 1MHz, 50:1 or 100:1                                                                                                                                                    | • |     | 3             | 45            | mV                |

|                                                                               | V <sub>OS3</sub> (Table 1)    | f <sub>CLK</sub> = 1MHz, 50:1 or 100:1                                                                                                                                                    | • |     | 3             | 45            | mV                |

| Clock Feedthrough                                                             |                               | f <sub>CLK</sub> < 1MHz                                                                                                                                                                   |   |     | 0.2           |               | mV <sub>RMS</sub> |

| Maximum Clock Frequency                                                       |                               | Mode 1, Q < 5, $V_S \ge \pm 5V$                                                                                                                                                           |   |     | 7             |               | MHz               |

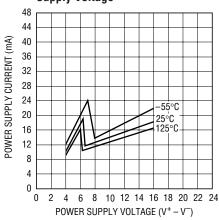

| Power Supply Current                                                          |                               |                                                                                                                                                                                           | • | 9   | 12            | 23<br>26      | mA<br>mA          |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: Contact LTC Marketing.

Note 3: Not tested, guaranteed by design.

Table 1. Output DC Offsets, One 2nd Order Section

| MODE | V <sub>OSN</sub><br>PINS 2, 11, 14, 23                                                                              | V <sub>OSBP</sub><br>PINS 3, 10, 15, 22 | V <sub>OSLP</sub><br>PINS 4, 9, 16, 21                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1    | $V_{OS1}[(1/Q) + 1 +   H_{OLP}  ] - V_{OS3}/Q$                                                                      | V <sub>OS3</sub>                        | $V_{OSN} - V_{OS2}$                                                                                         |

| 1b   | $V_{OS1}[(1/Q) + 1 + (R2/R1)] - V_{OS3}/Q$                                                                          | V <sub>OS3</sub>                        | $\sim (V_{OSN} - V_{OS2})[1 + (R5/R6)]$                                                                     |

| 2    | $V_{0S1}$ [(1 + (R2/R1) + (R2/R3) + (R2/R4) - $V_{0S3}$ (R2/R3)] $\times$ [R4/(R2 + R4)] + $V_{0S2}$ [R2/(R2 + R4)] | V <sub>OS3</sub>                        | V <sub>OSN</sub> – V <sub>OS2</sub>                                                                         |

| 3    | V <sub>0S2</sub>                                                                                                    | V <sub>OS3</sub>                        | V <sub>0S1</sub> [1 + (R4/R1) + (R4/R2) + (R4/R3)]<br>- V <sub>0S2</sub> (R4/R2) - V <sub>0S3</sub> (R4/R3) |

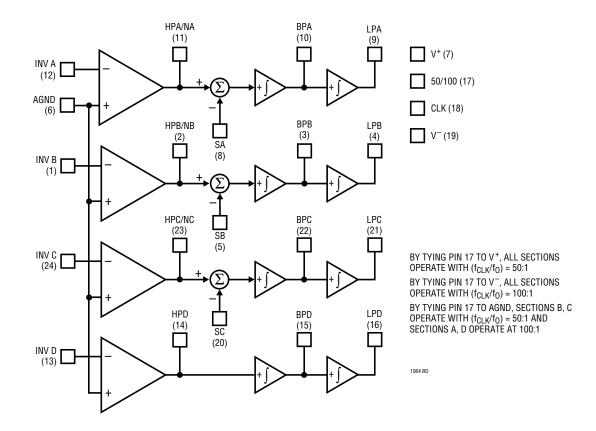

## **BLOCK DIAGRAM**

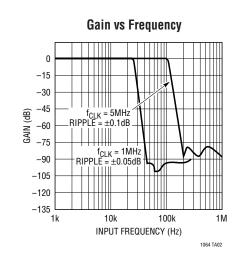

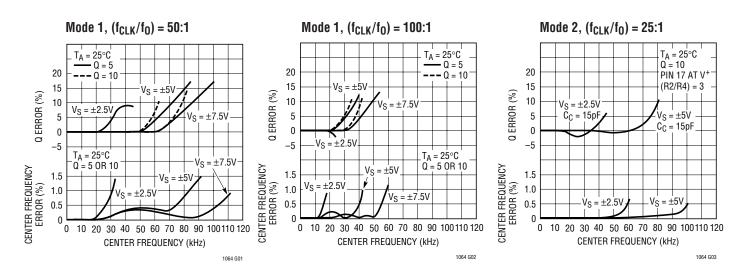

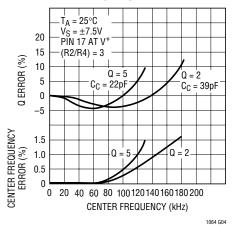

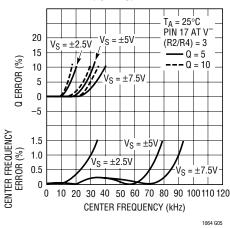

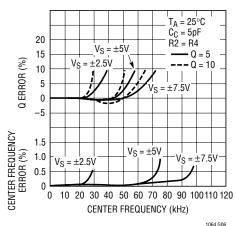

## TYPICAL PERFORMANCE CHARACTERISTICS

LINEAR

## TYPICAL PERFORMANCE CHARACTERISTICS

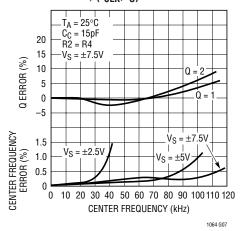

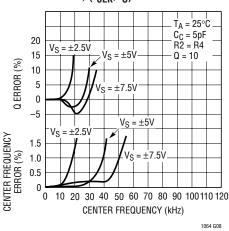

Mode 2,  $(f_{CLK}/f_0) = 25:1$

Mode 2,  $(f_{CLK}/f_0) = 50:1$

Mode 3,  $(f_{CLK}/f_0) = 50:1$

Mode 3,  $(f_{CLK}/f_0) = 50:1$

Mode 3,  $(f_{CLK}/f_0) = 100:1$

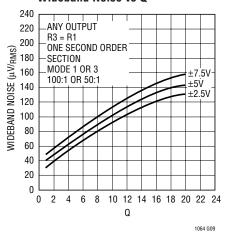

Wideband Noise vs Q

Power Supply Current vs Supply Voltage

1064 G10

Harmonic Distortion, 8th Order LP Butterworth,  $f_C = 20 kHz$ , THD = 0.015% for  $3V_{RMS}$  Input

1004 011

#### PIN FUNCTIONS

$V^+$ ,  $V^-$  (Pins 7, 19): Power Supplies. They should be bypassed with a  $0.1\mu F$  ceramic capacitor. Low noise, nonswitching power supplies are recommended. The device operates with a single 5V supply and with dual supplies. The absolute maximum operating power supply voltage is  $\pm 8V$ .

**CLK (Pin 18):** Clock. For  $\pm 5\text{V}$  supplies the logic threshold level is 1.4V. For  $\pm 8\text{V}$  and 0V to 5V supplies the logic threshold levels are 2.2V and 3V respectively. The logic threshold levels vary  $\pm 100\text{mV}$  over the full military temperature range. The recommended duty cycle of the input clock is 50%, although for clock frequencies below 500kHz, the clock "on" time can be as low as 200ns. The maximum clock frequency for  $\pm 5\text{V}$  supplies is 4MHz. For  $\pm 7\text{V}$  supplies and above, the maximum clock frequency is 7MHz.

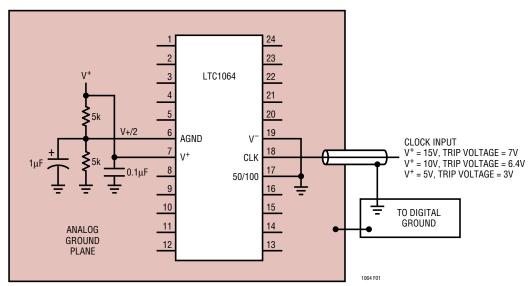

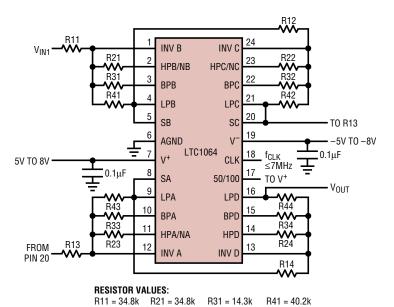

**AGND (Pin 6):** Analog Ground. When the LTC1064 operates with dual supplies, Pin 6 should be tied to system ground. When the LTC1064 operates with a single positive supply, the analog ground pin should be tied to 1/2 supply and it should be bypassed with a  $1\mu F$  solid tantalum in parallel with a  $0.1\mu F$  ceramic capacitor, Figure 1. The positive input of all the internal op amps, as well as the common reference of all the internal switches, are internally tied to the analog ground pin. Because of this, a very "clean" ground is recommended.

**50/100 (Pin 17):** By tying Pin 17 to V<sup>+</sup>, all filter sections operate with a clock-to-center frequency ratio internally set at 50:1. When Pin 17 is at mid-supplies, sections B and C operate with  $(f_{CLK}/f_0) = 50:1$  and sections A and D operate at 100:1. When Pin 17 is shorted to the negative supply pin, all filter sections operate with  $(f_{CLK}/f_0) = 100:1$ .

NOTE: PINS 5, 8, 20, IF NOT USED, SHOULD BE CONNECTED TO PIN 6

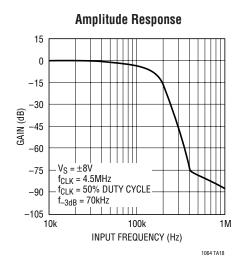

Figure 1. Single Supply Operation

LINEAR

## APPLICATIONS INFORMATION

#### ANALOG CONSIDERATIONS

#### **Grounding and Bypassing**

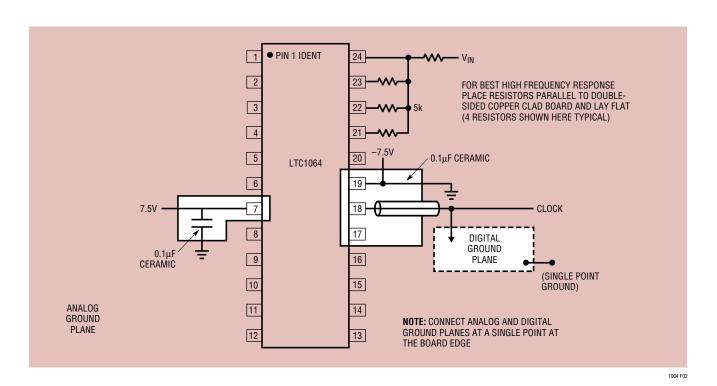

The LTC1064 should be used with separated analog and digital ground planes and single point grounding techniques.

Pin 6 (AGND) should be tied directly to the analog ground plane.

Pin 7 (V<sup>+</sup>) should be bypassed to the ground plane with a  $0.1\mu F$  ceramic capacitor with leads as short as possible. Pin 19 (V<sup>-</sup>) should be bypassed with a  $0.1\mu F$  ceramic capacitor. For single supply applications, V<sup>-</sup> can be tied to the analog ground plane.

For good noise performance,  $V^+$  and  $V^-$  must be free of noise and ripple.

All analog inputs should be referenced directly to the single point ground. The clock inputs should be shielded from and/or routed away from the analog circuitry and a separate digital ground plane used.

Figure 2 shows an example of an ideal ground plane design for a 2-sided board. Of course this much ground plane will not always be possible, but users should strive to get as close to this as possible. Protoboards are not recommended.

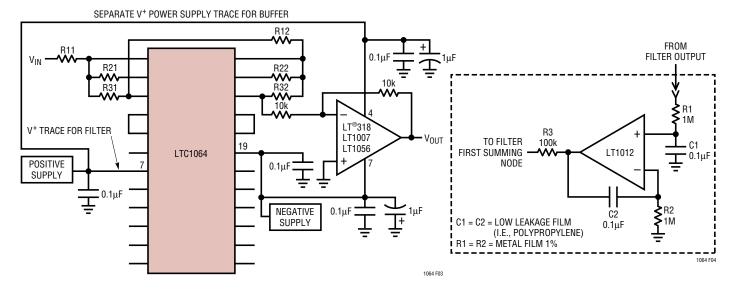

#### **Buffering the Filter Output**

When driving coaxial cables and  $1\times$  scope probes, the filter output should be buffered. This is important especially when high Qs are used to design a specific filter. Inadequate buffering may cause errors in noise, distortion, Q and gain measurements. When  $10\times$  probes are used, buffering is usually not required. An inverting buffer is recommended especially when THD tests are performed. As shown in Figure 3, the buffer should be adequately bypassed to minimize clock feedthrough.

Figure 2. Example Ground Plane Breadboard Technique for LTC1064

1064fb

### APPLICATIONS INFORMATION

#### Offset Nulling

Lowpass filters may have too much DC offset for some users. A servo circuit may be used to actively null the offsets of the LTC1064 or any LTC switched-capacitor filter. The circuit shown in Figure 4 will null offsets to better than  $300\mu V$ . This circuit takes seconds to settle because of the integrator pole frequency.

#### Noise

All the noise performance mentioned excludes the clock feedthrough. Noise measurements will degrade if the already described grounding bypassing and buffering techniques are not practiced. The graph Wideband Noise vs Q in the Typical Performance Characteristics section is a very good representation of the noise performance of this device.

Figure 3. Buffering the Output of a 4th Order Bandpass Realization

Figure 4. Servo Amplifier

## **MODES OF OPERATION**

#### PRIMARY MODES

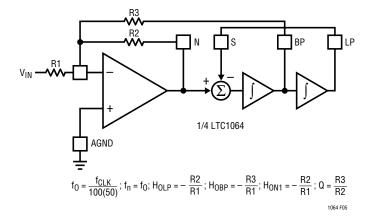

#### Mode 1

In Mode 1, the ratio of the external clock frequency to the center frequency of each 2nd order section is internally fixed at 50:1 or 100:1. Figure 5 illustrates Mode 1 providing 2nd order notch, lowpass and bandpass outputs. Mode 1 can be used to make high order Butterworth lowpass filters; it can also be used to make low Q notches and for cascading 2nd order bandpass functions tuned at the same center frequency with unity gain. Mode 1 is faster than Mode 3. Note that Mode 1 can only be implemented with three of the four LTC1064 sections because Section D has no externally available summing node. Section D, however, can be internally connected in Mode 1 upon special request.

Figure 5. Mode 1: 2nd Order Filter Providing Notch, Bandpass and Lowpass

1064fb

### **MODES OF OPERATION**

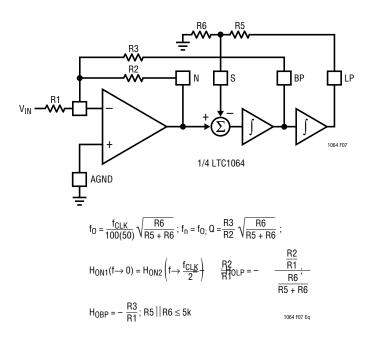

#### Mode 3

Mode 3 is the second of the primary modes. In Mode 3, the ratio of the external clock frequency to the center frequency of each 2nd order section can be adjusted above or below 50:1 or 100:1. Side D of the LTC1064 can only be connected in Mode 3. Figure 6 illustrates Mode 3, the classical state variable configuration, providing highpass, bandpass and lowpass 2nd order filter functions. Mode 3 is slower than Mode 1. Mode 3 can be used to make high order all-pole bandpass, lowpass, highpass and notch filters.

When the internal clock-to-center frequency ratio is set at 50:1, the design equations for Q and bandpass gain are different from the 100:1 case. This was done to provide speed without penalizing the noise performance.

$$\begin{split} \text{MODE 3 (100:1):} \qquad & f_0 = \frac{f_{CLK}}{100} \, \sqrt{\frac{R2}{R4}} \; ; \, Q = \frac{R3}{R2} \, \sqrt{\frac{R2}{R4}} \; ; \, H_{OHP} = - \, \frac{R2}{R1} \; ; \\ & H_{OBP} = - \, \frac{R3}{R1} ; \, H_{OLP} = - \, \frac{R4}{R1} \\ \\ \text{MODE 3 (50:1):} \qquad & f_0 = \frac{f_{CLK}}{50} \, \sqrt{\frac{R2}{R4}} \; ; \, Q = \frac{1.005 \, \sqrt{\frac{R2}{R4}}}{\frac{R2}{R3} \, - \, \frac{R2}{16R4}} \; ; \\ & H_{OHP} = - \, \frac{R2}{R1} \; ; \, H_{OBP} = - \, \frac{\frac{R3}{R1}}{1 \, - \, \frac{R3}{16R4}} \; ; \, H_{OLP} = - \, \frac{R4}{R1} \end{split}$$

**NOTE:** THE 50:1 EQUATIONS FOR MODE 3 ARE DIFFERENT FROM THE EQUATIONS FOR MODE 3 OPERATIONS OF THE LTC1059, LTC1060 AND LTC1061. START WITH  $f_0$ , CALCULATE R2/R4, SET R4; FROM THE Q VALUE, CALCULATE R3:

$$f_0, \text{ CALCULATE R2/R4, SET R4; FROM THE Q VALUE, CALCULATE R3:}$$

$$R3 = \frac{R2}{\frac{1.005}{Q} \sqrt{\frac{R2}{R4} + \frac{R2}{16R4}}} \text{; THEN CALCULATE R1 TO SET}$$

$$\text{THE DESIRED GAIN.}$$

$$\text{$^{1064 \, F066 \, Eq}$}$$

Figure 6. Mode 3: 2nd Order Filter Providing Highpass, Bandpass and Lowpass

#### **SECONDARY MODES**

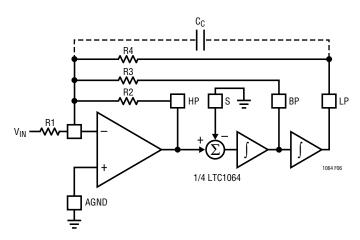

#### Mode 1b

Mode 1b is derived from Mode 1. In Mode 1b, Figure 7, two additional resistors R5 and R6 are added to alternate the amount of voltage fed back from the lowpass output into the input of the SA (or SB or SC) switched-capacitor summer. This allows the filter's clock-to-center frequency ratio to be adjusted beyond 50:1 or 100:1. Mode 1b maintains the speed advantages of Mode 1.

Figure 7. Mode 1b: 2nd Order Filter Providing Notch, Bandpass and Lowpass

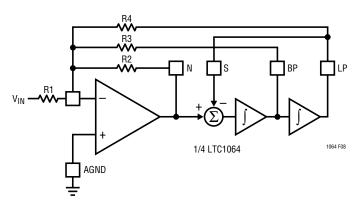

#### Mode 2

Mode 2 is a combination of Mode 1 and Mode 3, as shown in Figure 8. With Mode 2, the clock-to-center frequency ratio  $f_{CLK}/f_0$  is always less than 50:1 or 100:1. The advantage of Mode 2 is that it provides less sensitivity to resistor tolerances than does Mode 3. As in Mode 1, Mode 2 has a notch output which depends on the clock frequency and the notch frequency is therefore less than the center frequency  $f_0$ .

When the internal clock-to-center frequency ratio is set at 50:1, the design equations for Q and bandpass gain are different from the 100:1 case.

## **MODES OF OPERATION**

$$\begin{split} \text{MODE 2 (100:1):} \qquad f_0 = & \frac{f_{CLK}}{100} \sqrt{1 + \frac{R2}{R4}} \; ; \; f_n = \frac{f_{CLK}}{50} \; ; \; Q = \frac{R3}{R2} \; \sqrt{1 + \frac{R2}{R4}} \; ; \; H_{0LP} = -\frac{\frac{R2}{R1}}{1 + \frac{R2}{R4}} \; ; \\ & H_{0BP} = -\frac{R3}{R1} \; ; \; H_{0N1}(f \rightarrow 0) = -\frac{\frac{R2}{R1}}{1 + \frac{R2}{R4}} \; ; \; H_{0N2}\left(f \rightarrow \frac{f_{CLK}}{2}\right) \qquad \frac{R2}{R1} \; ; \\ & MODE 2 (50:1): \qquad f_0 = \frac{f_{CLK}}{50} \sqrt{1 + \frac{R2}{R4}} \; ; \; f_n = \frac{f_{CLK}}{50} \; ; \; Q = \frac{1.005 \; \sqrt{1 + \frac{R2}{R4}}}{\frac{R2}{R3} \; - \frac{R2}{16R4}} \; ; \; H_{0LP} = -\frac{\frac{R2}{R1}}{1 + \frac{R2}{R4}} \; ; \end{split}$$

$H_{OBP} = -\frac{\frac{R3}{R1}}{1-\frac{R3}{16R4}} \; ; \; H_{ON1}(f \rightarrow 0) = -\frac{\frac{R2}{R1}}{1+\frac{R2}{R4}} ; \; H_{ON2} = \left(f \rightarrow \frac{f_{CLK}}{2}\right) \quad -\frac{R2}{R1}$  **NOTE**: THE 50:1 EQUATIONS FOR MODE 2 ARE DIFFERENT FROM THE EQUATIONS FOR MODE 2 OPERATION OF THE LTC1059. LTC1060 AND LTC1061. START WITH

$$R3 = \frac{R2}{\frac{1.005}{Q}\sqrt{1+\frac{R2}{R4}+\frac{R2}{16R4}}} \; ; \text{ THEN CALCULATE R1 TO SET THE DESIRED GAIN.}$$

f<sub>O</sub>, CALCULATE R2/R4, SET R4; FROM THE Q VALUE, CALCULATE R3:

Figure 8. Mode 2: 2nd Order Filter Providing Notch, Bandpass and Lowpass

#### Mode 3a

This is an extension of Mode 3 where the highpass and lowpass outputs are summed through two external resistors  $R_H$  and  $R_L$  to create a notch. This is shown in Figure 9. Mode 3a is more versatile than Mode 2 because the notch frequency can be higher or lower than the center frequency of the 2nd order section. The external op amp of Figure 9 is not always required. When cascading the sections of the LTC1064, the highpass and lowpass

outputs can be summed directly into the inverting input of the next section. The topology of Mode 3a is useful for elliptic highpass and notch filters with clock-to-cutoff frequency ratios higher than 100:1. This is often required to extend the allowed input signal frequency range and to avoid premature aliasing.

When the internal clock-to-center frequency ratio is set at 50:1, the design equations for Q and bandpass gain are different from the 100:1 case.

$$\text{MODE 3a (100:1):} \quad f_0 = \frac{f_{CLK}}{100} \sqrt{\frac{R_1}{R^2}}; f_n = \frac{f_{CLK}}{100} \sqrt{\frac{R_1}{R_1}}; \text{ $H_{OHP} = -\frac{R^2}{R^3}$; $H_{OHP} = -\frac{R^3}{R^3}$; $H_{OLP} = -\frac{R^3}$$

Figure 9. Mode 3a: 2nd Order Filter Providing Highpass, Bandpass, Lowpass and Notch

LINEAR

1064fb

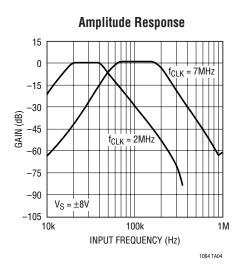

#### Wideband Bandpass: Ratio of High to Low Corner Frequency Equal to 2

#### 8th Order Bandpass Filter with 2 Stopband Notches

#### RESISTOR VALUES:

R11 = 46.95k R21 = 10k R31 = 38.25k R41 = 11.81k

NOTE 1: THE V $^+$ , V $^-$  PINS SHOULD BE BYPASSED WITH A  $0.1\mu F$  TO  $0.22\mu F$  CERAMIC CAPACITOR, RIGHT AT THE PINS.

**NOTE 2:** THE RATIOS OF ALL (R2/R4) RESISTORS SHOULD BE MATCHED TO BETTER THAN 0.25%. THE REMAINING RESISTORS SHOULD BE BETTER THAN 0.5% ACCURATE.

1064 TA07

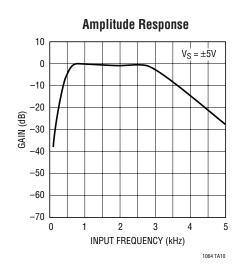

#### **C-Message Filter**

1064fb

LINEAR TECHNOLOGY

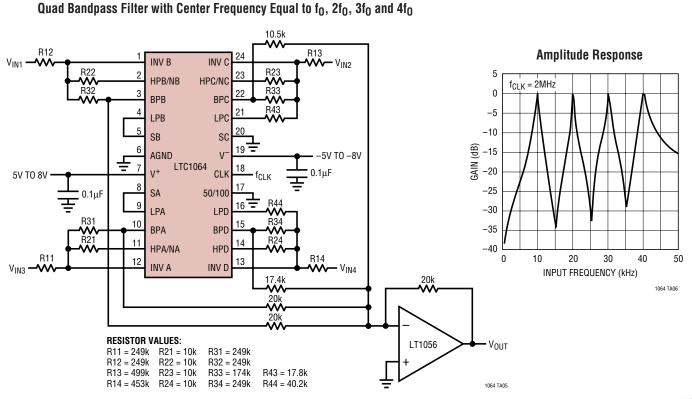

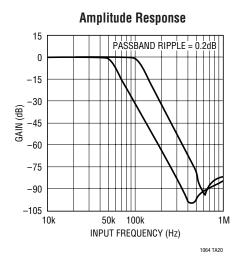

8th Order Chebyshev Lowpass Filter with a Passband Ripple of 0.1dB and Cutoff Frequency up to 100kHz

FOR  $f_{CLK} > 3MHz$ , ADD C2 = 10pF ACROSS R42 C3 = 10pF ACROSS R43 C4 = 10pF ACROSS R44

WIDEBAND NOISE =  $170\mu V_{RMS}$

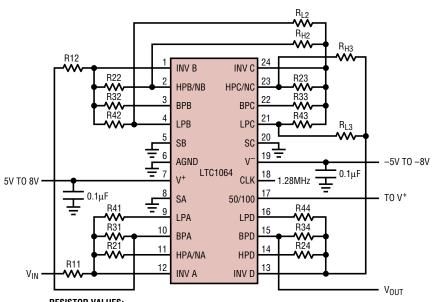

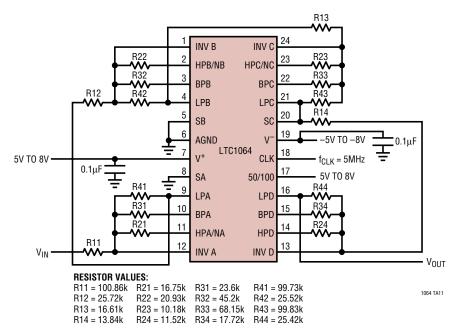

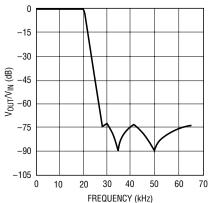

8th Order Clock-Sweepable Lowpass Elliptic Antialiasing Filter

8TH ORDER CLOCK-SWEEPABLE LOWPASS ELLIPTIC ANTIALIASING FILTER MAINTAINS, FOR 0.1Hz  $\leq$  f<sub>CUTOFF</sub>  $\leq$  20kHz, A  $\pm$ 0.1dB MAX PASSBAND ERROR AND 72dB MIN STOPBAND

THD = 70dB (0.03%) FOR V<sub>IN</sub> = 3V<sub>RMS</sub>, f<sub>CLK</sub>/f<sub>CUTOFF</sub> = 100:1. THIS FILTER AVAILABLE AS LTC1064-1 WITH INTERNAL THIN FILM RESISTORS

ATTENUATION AT  $1.5 \times f_{\text{CUTOFF}}$ TOTAL WIDEBAND NOISE =  $150\mu V_{RMS}$ ,

#### Dual 4th Order Bessel Filter with 140kHz Cutoff Frequency

# 8th Order Linear Phase (Bessel) Filter with $\frac{f_{CLK}}{f_{-3dB}} = \frac{65}{1}$

1064 TA15

R12 = 10.5k

R13 = 12.7kR14 = 20k

R22 = 45.3k

R23 = 34.8k

R24 = 34.8k

WIDEBAND NOISE =  $70\mu V_{RMS}$

R32 = 22.1k

R33 = 24.3k

R34 = 13.3k

R42 = 39.2k

R43 = 20k

R44 = 20k

#### Dual 5th Order Chebyshev Lowpass Filter with 50kHz and 100kHz Cutoff Frequencies

RESISTOR VALUES:

R11a = 4.32k R21 = 11.8k R31 = 29.4k R41 = 10k

R11b = 27.4k R22 = 20k R32 = 21.5k R42 = 31.6k

R12 = 10.5k R23 = 11.8k R33 = 29.4k R43 = 10k

R13a=3k R24=20k R34=21.6k R44=31.6k R13b=29.4k R14=10.5k R34=21.6k R44=31.6k R44=31.

## PACKAGE DESCRIPTION

## PACKAGE DESCRIPTION

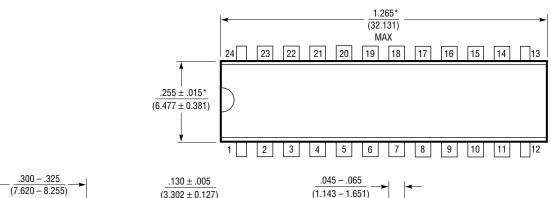

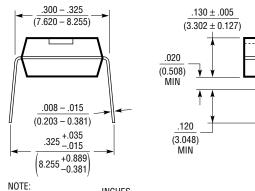

#### N Package 24-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

.100

(2.54)

BSC

1. DIMENSIONS ARE MILLIMETERS

.065 (1.651) TYP

$.018 \pm .003$

$(0.457 \pm 0.076)$

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

## PACKAGE DESCRIPTION

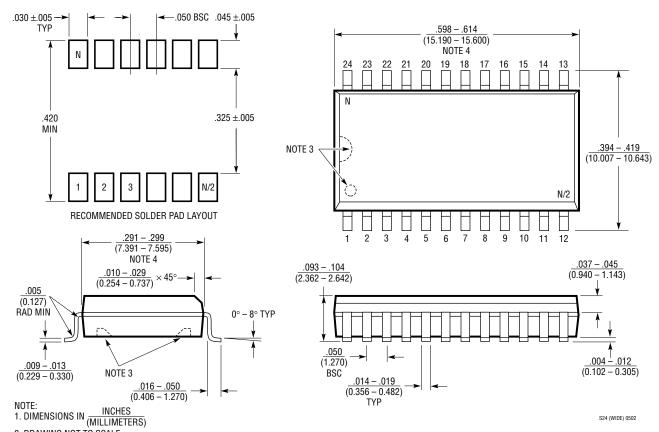

#### **SW Package** 24-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

- 2. DRAWING NOT TO SCALE

- 2. DRAWING NOT TO SCALE

3. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS.

THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

4. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

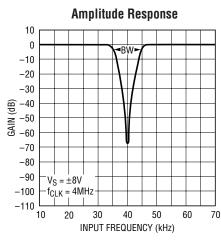

Clock-Tunable, 30kHz to 90kHz 8th Order Notch Filter Providing Notch Depth in Excess of 60dB

## **RELATED PARTS**

| PART NUMBER    | DESCRIPTION                                     | COMMENT                                                        |

|----------------|-------------------------------------------------|----------------------------------------------------------------|

| LTC1061        | Triple Universal Filter Building Block          | Three Filter Building Blocks in a 20-Pin Package               |

| LTC1068 Series | Quad Universal Building Blocks                  | f <sub>CLK</sub> :f <sub>0</sub> = 25:1, 50:1, 100:1 and 200:1 |

| LTC1164        | Low Power, Quad Universal Filter Building Block | Low Noise, Low Power Pin-for-Pin LTC1064 Compatible            |

| LTC1264        | High Speed, Quad Universal Building Block       | Up to 250kHz Center Frequency                                  |

#### **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9