# High Performance DSP-Based Motor Controller

# ADMC300

#### TARGET APPLICATIONS Industrial Drives, Servo Drives, Variable Speed Drives, **Electric Vehicles FEATURES** 25 MIPS Fixed-Point DSP Core Single Cycle Instruction Execution (40 ns) **ADSP-2100 Family Code Compatible Independent Computational Units** ALU **Multiplier/Accumulator Barrel Shifter Multifunction Instructions Single Cycle Context Switch Powerful Program Sequencer** Zero Overhead Looping **Conditional Instruction Execution Two Independent Data Address Generators Memory Configuration** 4K × 24-Bit Program Memory RAM 2K × 24-Bit Program Memory ROM 1K × 16-Bit Data Memory RAM **High-Resolution Multichannel ADC System** Five Independent 16-Bit Sigma-Delta ADCs 76 dB SNR Typical (ENOB > 12 Bits) Arranged in Two Independently Clocked Banks **Differential or Single-Ended Inputs** Programmable Sample Frequency to 32.5 kHz

Flexible Synchronization of ADC and PWM Subsystems **Independent Offset Calibration for Each Channel Two Dedicated ADC Interrupts** Internal 2.5 V Reference **Three Multiplexer Control Pins for External Expansion** Hardware or Software Convert Start **Individual Power-Down for Each Bank Three-Phase PWM Generation Subsystem 16-Bit Dedicated PWM Generator** Edge Resolution to 40 ns **Programmable Dead Time Programmable Minimum Pulsewidth Double Update Mode Allows Duty Cycle Adjustment on Half Cycle Boundaries Special Features for Brushless DC Motors** Hardwired Polarity Control **External Dedicated Asynchronous Shutdown Pin** (PWMTRIP) Additional Shutdown Pins in I/O System Individual Enable/Disable of Each Output **High Frequency Chopping Mode Transparent Transition to Overmodulation** Range with Duty Cycles of 100% **Programmable Interrupt Controller Manages Priority** and Masking of 11 Peripheral Interrupts

(Continued on Page 7)

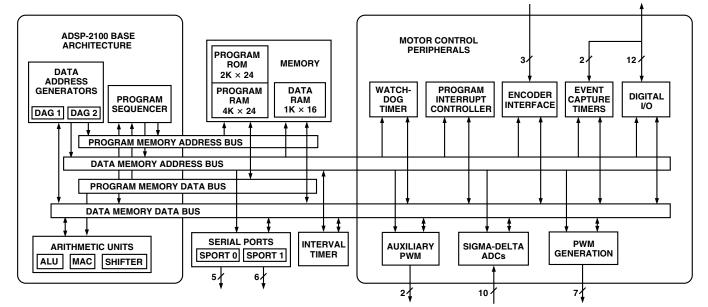

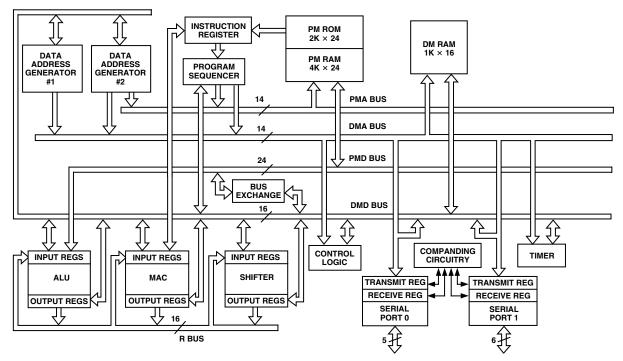

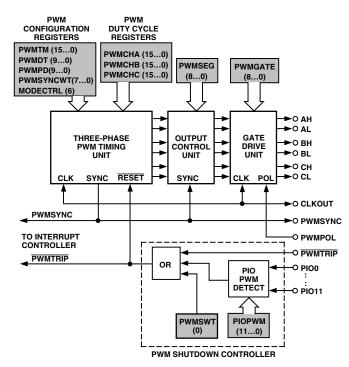

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2000

# ADMC300-SPECIFICATIONS

# **RECOMMENDED OPERATING CONDITIONS** $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, T_{AMB} = -40^{\circ}C to +85^{\circ}C, CLKIN = 12.5 MHz, unless otherwise noted)$

|                  |                               | B Gr | ade  |       |

|------------------|-------------------------------|------|------|-------|

| Paramete         | er                            | Min  | Max  | Units |

| V <sub>DD</sub>  | Digital Supply Voltage        | 4.50 | 5.50 | V     |

| AV <sub>DD</sub> | Analog Supply Voltage         | 4.50 | 5.50 | V     |

| T <sub>AMB</sub> | Ambient Operating Temperature | -40  | +85  | °C    |

### **ELECTRICAL CHARACTERISTICS**

| Paramete         | er                                                     | Test Conditions                    | Min            | Max  | Unit |

|------------------|--------------------------------------------------------|------------------------------------|----------------|------|------|

| V <sub>IH</sub>  | Hi-Level Input Voltage <sup>1, 2</sup>                 | @ V <sub>DD</sub> = Max            | 2.0            |      | V    |

| VIL              | Lo-Level Input Voltage <sup>1, 2</sup>                 | $\tilde{@}$ V <sub>DD</sub> = Min  |                | 0.8  | V    |

| V <sub>OH</sub>  | Hi-Level Output Voltage <sup>1, 3</sup>                | $\tilde{@}$ V <sub>DD</sub> = Min, | 2.4            |      | V    |

|                  |                                                        | $I_{OH} = -1.0 \text{ mA}$         |                |      |      |

|                  |                                                        | @ V <sub>DD</sub> = Min,           | $V_{DD} - 0.3$ |      | V    |

|                  |                                                        | $I_{OH} = -0.1 \text{ mA}$         |                |      |      |

| V <sub>OL</sub>  | Lo-Level Output Voltage <sup>1, 3</sup>                | @ V <sub>DD</sub> = Min,           |                | 0.4  | V    |

|                  |                                                        | $I_{OL} = 2.0 \text{ mA}$          |                |      |      |

| $I_{IH}$         | Hi-Level Input Current <sup>4</sup>                    | @ V <sub>DD</sub> = Max,           |                | 10   | μA   |

|                  |                                                        | $V_{IN} = V_{DD} Max$              |                |      |      |

| $I_{IH}$         | Hi-Level <b>PWMTRIP</b> , PIO0–PIO11 Current           | @ V <sub>DD</sub> = Max,           |                | 100  | μA   |

|                  |                                                        | $V_{IN} = V_{DD} Max$              |                |      |      |

| $I_{IH}$         | Hi-Level PWMPOL Current                                | @ V <sub>DD</sub> = Max,           |                | 10   | μA   |

|                  |                                                        | $V_{IN} = V_{DD} Max$              |                |      |      |

| $I_{IL}$         | Lo-Level Input Current <sup>4</sup>                    | @ V <sub>DD</sub> = Max,           |                | 10   | μA   |

|                  |                                                        | $V_{IN} = 0 V$                     |                |      |      |

| $I_{IL}$         | Lo-Level <b>PWMTRIP</b> , PIO0–PIO11 Current           | @ $V_{DD}$ = Max,                  |                | 10   | μA   |

|                  |                                                        | $V_{IN} = 0 V$                     |                |      |      |

| $I_{IL}$         | Lo-Level PWMPOL Current                                | @ $V_{DD} = Max$ ,                 |                | 100  | μA   |

|                  | -                                                      | $V_{IN} = 0 V$                     |                |      |      |

| I <sub>OZH</sub> | Hi-Level Three-State Leakage Current <sup>5</sup>      | @ $V_{DD} = Max$ ,                 |                | 10   | μA   |

| _                |                                                        | $V_{IN} = V_{DD} Max$              |                |      |      |

| I <sub>OZL</sub> | Lo-Level Three-State Leakage Current <sup>5</sup>      | @ $V_{DD} = Max$ ,                 |                | 10   | μA   |

| _                |                                                        | $V_{IN} = 0 V$                     |                |      | _    |

| I <sub>DD</sub>  | Digital Power Supply Current (Dynamic) <sup>6, 7</sup> | $@V_{DD} = Max$                    |                | 100  | mA   |

| I <sub>DD</sub>  | Analog Power Supply Current (Disabled) <sup>8</sup>    | $(a) AV_{DD} = V_{DD} = Max$       |                | 100  | μA   |

| I <sub>DD</sub>  | Analog Power Supply Current (Ref Only)                 |                                    |                | 6.5  | mA   |

| I <sub>DD</sub>  | Analog Power Supply Current (Ref + BankA)              | $ (a) AV_{DD} = V_{DD} = Max $     |                | 11.0 | mA   |

| I <sub>DD</sub>  | Analog Power Supply Current (Ref + BankB)              | $(a) AV_{DD} = V_{DD} = Max$       |                | 13.0 | mA   |

| I <sub>DD</sub>  | Analog Power Supply Current (Ref + BankA/B)            | (a) $AV_{DD} = V_{DD} = Max$       |                | 18.0 | mA   |

NOTES

<sup>1</sup>Bidirectional pins: PIO0–PIO11, RFS0, RFS1, TFS0, TFS1, SCLK0, SCLK1. <sup>2</sup>Input only pins: PWMTRIP, PWMPOL, RESET, EIA, EIB, EIZP, DR1A, DR1B, DR0, CLKIN.

<sup>3</sup>Output pins: PWMSYNC, CL, CH, BL, BH, AL, AH, MUX0-MUX2, AUX0, AUX1, CLKOUT, DT0, DT1.

<sup>4</sup>Input only pins: RESET, EIA, EIB, EIZP, DR1A, DR1B, DR0, CLKIN.

<sup>5</sup>Three-stateable pins: DT0, DT1, RFS0, RFS1, TFS0, TFS1, SCLK0, SCLK1.

<sup>6</sup>Current reflects device operating with no output loads.

<sup>7</sup>Dynamic condition refers to continuous operation of the DSP core, ADC banks and PWM generation in single update mode with PWMTM = 0x0480, ADCDIVA = ADCDIVB = 0x180. The encoder inputs are quiescent.

<sup>8</sup>Disabled refers to powering down both ADC banks and the internal reference generation circuit by setting Bits 10, 11 and 12 of the ADCCTRL register. Current is total current from AV<sub>DD</sub> supply.

Specifications subject to change without notice.

# **ANALOG-TO-DIGITAL CONVERTER** $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, V_{REFIN} = 2.50 V, T_{AMB} = -40^{\circ}C \text{ to } +85^{\circ}C, CLKIN = 12.5 \text{ MHz}, unless otherwise noted}$

| Parameter             |                                                  | Test Conditions                         | Min | Тур    | Max        | Unit  |

|-----------------------|--------------------------------------------------|-----------------------------------------|-----|--------|------------|-------|

| Signal-to-N           | oise Ratio <sup>1</sup> (SNR)                    | $a V_{DD} = 5.0 V,$                     | 72  | 76     |            | dB    |

| Total Harm            | onic Distortion <sup>1</sup> (THD)               | $(a) f_{\rm s} = 32.55 \text{ kHz},$    |     |        | -70        | dB    |

| Common-M              | Iode Rejection Ratio <sup>2</sup> (CMRR)         | $\hat{a}$ $f_{IN} = 1.017 \text{ kHz},$ |     |        | -82        | dB    |

| Channel-Ch            | annel Crosstalk <sup>3</sup>                     | $\overrightarrow{ADCDIVn} = 0x180,$     |     |        | -76        | dB    |

| Gain Error            |                                                  | V1-V5 = 4.0 V p-p                       |     |        | 5          | %     |

| Gain                  |                                                  | $V1N-V5N = V_{REFIN} = 2.5 V$           |     | 10,600 |            | LSB/V |

| $V_{IN}$              | Analog Input Range <sup>4</sup>                  |                                         | 0   |        | $V_{DD}$   | V     |

| V <sub>DIFF</sub>     | Analog Input Voltage (Differential) <sup>4</sup> |                                         |     |        | $V_{DD}/2$ | V     |

| VOFFSET               | DC Offset Voltage <sup>5</sup>                   |                                         |     |        | 55         | mV    |

| f <sub>MOD, MAX</sub> | Maximum Sigma-Delta Modulator Rate               | ADCDIVA = 0x180                         |     |        | 2.08       | MHz   |

|                       |                                                  | ADCDIVB = 0x180                         |     |        |            |       |

| f <sub>S, MAX</sub>   | Maximum ADC Sample Rate <sup>6</sup>             | ADCDIVA = 0x180                         |     |        | 32.55      | kHz   |

|                       |                                                  | ADCDIVB = 0x180                         |     |        |            |       |

| V <sub>REFIN</sub>    | Reference Input Voltage <sup>7</sup>             |                                         | 2.4 | 2.5    | 2.6        | v     |

| R <sub>IN</sub>       | Equivalent Input Resistance <sup>8</sup>         |                                         |     | 25     |            | kΩ    |

NOTES

<sup>1</sup>SNR measured with ADC channel configured in single-ended mode. SNR measurement does not include harmonic distortion, THD includes first six harmonics. The effective number of bits (ENOB) is related to the SNR by SNR = 6.02 (ENOB) +1.76 dB. Input signal filtered at 1.5 kHz.

<sup>2</sup>Input signal applied to both pins of input differential pair of ADC channel.

<sup>3</sup>Input signal applied to four ADC channels, dc applied to fifth, measurement taken at fifth ADC channel.

<sup>4</sup>Peak-peak input voltage in differential input configuration is half that in single-ended mode.

<sup>5</sup>This offset may be corrected for, using the ADC calibration feature.

<sup>6</sup>At maximum sigma-delta modulator rate of 2.08 MHz.

<sup>7</sup>Input reference pins: REFINA, REFINB.

<sup>8</sup>Analog signal input pins: V1-V5, V1N-V5N.

Specifications subject to change without notice.

# **VOLTAGE REFERENCE** $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, T_{AMB} = -40^{\circ}C$ to +85°C, CLKIN = 12.5 MHz, unless otherwise noted)

| Parameter                           |                | Test Conditions | Min  | Тур | Max  | Unit |

|-------------------------------------|----------------|-----------------|------|-----|------|------|

| V <sub>REF</sub>                    | Voltage Level  |                 | 2.25 |     | 2.75 | V    |

|                                     | Source Current |                 |      |     | -100 | μA   |

| Power Supply Rejection Ratio (PSRR) |                |                 | -5   |     | 5    | mV/V |

Specifications subject to change without notice.

# **PULSEWIDTH MODULATOR** $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, T_{AMB} = -40^{\circ}C \text{ to } +85^{\circ}C, CLKIN = 12.5 \text{ MHz, unless}$ otherwise noted)

| Paramete          | r                                 | Test Conditions    | Min    | Тур | Max   | Unit |

|-------------------|-----------------------------------|--------------------|--------|-----|-------|------|

|                   | Counter Resolution <sup>1</sup>   |                    |        |     | 16    | Bits |

|                   | Edge Resolution                   | Double Update Mode |        | 40  |       | ns   |

| T <sub>D</sub>    | Programmable Dead Time            |                    | 0      |     | 81.84 | μs   |

|                   | Programmable Dead Time Increments |                    |        | 80  |       | ns   |

| T <sub>MIN</sub>  | Programmable Pulse Deletion       |                    | 0      |     | 40.92 | μs   |

|                   | Programmable Deletion Increments  |                    |        | 40  |       | ns   |

| f <sub>PWM</sub>  | PWM Frequency Range <sup>1</sup>  |                    | 191    |     |       | Hz   |

| T <sub>SYNC</sub> | PWMSYNC Pulsewidth                |                    | 0.04   |     | 10.24 | μs   |

| f <sub>CHOP</sub> | Gate Drive Chop Frequency         |                    | 0.0244 | 1   | 6.25  | MHz  |

NOTES

<sup>1</sup>Resolution varies with PWM switching frequency, 191 Hz = 16 bits, 3.05 kHz = 12 bits, 48.8 kHz = 8 bits (12.5 MHz CLKIN) in single update mode. Specifications subject to change without notice.

# ADMC300-SPECIFICATIONS

**ENCODER INTERFACE UNIT**  $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, T_{AMB} = -40^{\circ}C \text{ to } +85^{\circ}C, CLKIN = 12.5 \text{ MHz, unless}$  otherwise noted)

| Parameter             |                                         | Test Conditions | Min | Тур | Max | Unit |

|-----------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>ENC, MAX</sub> | Maximum Encoder Pulse Rate <sup>1</sup> |                 |     |     | 3.1 | MHz  |

NOTES

<sup>1</sup>Assumes perfect quadrature encoder signals. Specifications subject to change without notice.

# **AUXILIARY PWM OUTPUTS** $(V_{DD} = AV_{DD} = 5 V \pm 10\%, GND = AGND = 0 V, T_{AMB} = -40^{\circ}C \text{ to } +85^{\circ}C, CLKIN = 12.5 \text{ MHz, unless}$ otherwise noted)

ParameterTest ConditionsMinTypMaxUnitResolution<br/>f\_AUXPWM88Bits<br/>kHz

Specifications subject to change without notice.

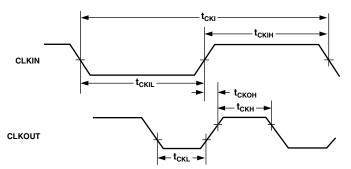

### **TIMING PARAMETERS**

| Parameter                                                                 |                                                                                                                                                                                                                                                                                                           | Min                                                                        | Max | Unit           |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|----------------|

| to half the i<br>yields a 40<br>0.5 t <sub>CKI</sub> per<br>specification | ed as 0.5 $t_{CKI}$ . The ADMC300 uses an input clock with a frequency equal nstruction rate; a 12.5 MHz input clock (which is equivalent to 80 ns) ns processor cycle (equivalent to 25 MHz). $t_{CK}$ values within the range of iod should be substituted for all relevant timing parameters to obtain |                                                                            |     |                |

| Timing Requ<br>t <sub>CKI</sub><br>t <sub>CKIL</sub><br>t <sub>CKIH</sub> | uirements:<br>CLKIN Period<br>CLKIN Width Low<br>CLKIN Width High                                                                                                                                                                                                                                         | 80<br>20<br>20                                                             | 150 | ns<br>ns<br>ns |

| Switching C<br>t <sub>CKL</sub><br>t <sub>CKH</sub><br>t <sub>CKOH</sub>  | Tharacteristics:<br>CLKOUT Width Low<br>CLKOUT Width High<br>CLKIN High to CLKOUT High                                                                                                                                                                                                                    | $\begin{array}{c} 0.5 \ t_{CK} - 10 \\ 0.5 \ t_{CK} - 10 \\ 0 \end{array}$ | 20  | ns<br>ns<br>ns |

| <b>Control Si</b><br>Timing Requ                                          | -                                                                                                                                                                                                                                                                                                         | $5 t_{CK}^{1}$                                                             |     | ns             |

| PWM Shu<br>Timing Requ<br>t <sub>PWMTPW</sub><br>t <sub>PIOPWM</sub>      | tdown Signals<br>uirements:<br>PWMTRIP Width Low<br>PIO Width Low                                                                                                                                                                                                                                         | 3 t <sub>CK</sub><br>3 t <sub>CK</sub>                                     |     | ns<br>ns       |

NOTES

<sup>1</sup>Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles assuming stable CLKIN (not including crystal oscillator start-up time).

Specifications subject to change without notice.

Figure 1. Clock Signals

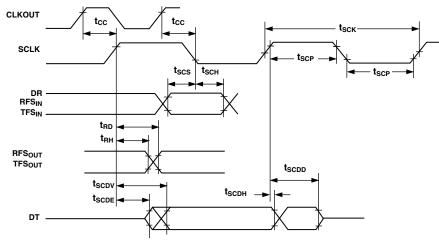

| Paramete          | r                                           | Min                  | Max                       | Unit |

|-------------------|---------------------------------------------|----------------------|---------------------------|------|

| Serial Por        | rts                                         |                      |                           |      |

| Timing Req        | nuirements:                                 |                      |                           |      |

| t <sub>SCK</sub>  | SCLK Period                                 | 50                   |                           | ns   |

| t <sub>SCS</sub>  | DR/TFS/RFS Setup before SCLK Low            | 5                    |                           | ns   |

| t <sub>SCH</sub>  | DR/TFS/RFS Hold after SCLK Low              | 10                   |                           | ns   |

| t <sub>SCP</sub>  | SCLK <sub>IN</sub> Width                    | 20                   |                           | ns   |

| Switching (       | Characteristics:                            |                      |                           |      |

| t <sub>CC</sub>   | CLKOUT High to SCLK <sub>OUT</sub>          | 0.25 t <sub>CK</sub> | 0.25 t <sub>CK</sub> + 15 | ns   |

| t <sub>SCDE</sub> | SCLK High to DT Enable                      | 0                    |                           | ns   |

| t <sub>SCDV</sub> | SCLK High to DT Valid                       |                      | 20                        | ns   |

| t <sub>RH</sub>   | TFS/RFS <sub>OUT</sub> Hold after SCLK High | 0                    |                           | ns   |

| t <sub>RD</sub>   | TFS/RFS <sub>OUT</sub> Delay from SCLK High |                      | 20                        | ns   |

| t <sub>SCDH</sub> | DT Hold after SCLK High                     | 0                    |                           | ns   |

| t <sub>SCDD</sub> | SCLK High to DT Disable                     |                      | 20                        | ns   |

Specifications subject to change without notice.

Figure 2. Serial Ports

#### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage (V <sub>DD</sub> )       | 0.3 V to +7.0 V                                         |

|-----------------------------------------|---------------------------------------------------------|

| Supply Voltage (AV <sub>DD</sub> )      | 0.3 V to +7.0 V                                         |

| Input Voltage                           | $.3 \text{ V to V}_{\text{DD}} + 0.3 \text{ V}$         |

| Output Voltage Swing0                   | $.3 \text{ V to } \text{V}_{\text{DD}} + 0.3 \text{ V}$ |

| Operating Temperature Range (Ambient) . | 40°C to +85°C                                           |

| Storage Temperature Range | $\dots \dots -65^{\circ}C$ to $+150^{\circ}C$ |

|---------------------------|-----------------------------------------------|

| Lead Temperature (5 sec)  | +280°C                                        |

\*Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

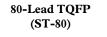

#### **ORDERING GUIDE**

| Model                                          | Temperature    | Instruction | Package                                                                                         | Package |

|------------------------------------------------|----------------|-------------|-------------------------------------------------------------------------------------------------|---------|

|                                                | Range          | Rate        | Description                                                                                     | Option  |

| ADMC300BST<br>ADMC300-ADVEVALKIT<br>ADMC300-PB | -40°C to +85°C | 25 MHz      | 80-Lead Plastic Thin Quad Flatpack (TQFP)<br>Development Tool Kit<br>Evaluation/Processor Board | ST-80   |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADMC300 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

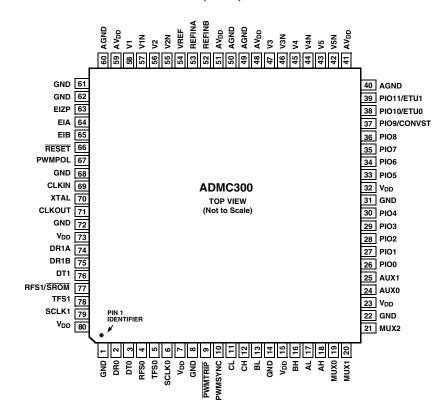

#### PIN FUNCTION DESCRIPTIONS

| Pin<br>No. | Pin<br>Type | Pin<br>Name     | Pin<br>No. | Pin<br>Type | Pin<br>Name     | Pin<br>No. | Pin<br>Type | Pin<br>Name      | Pin<br>No. | Pin<br>Type | Pin<br>Name     |

|------------|-------------|-----------------|------------|-------------|-----------------|------------|-------------|------------------|------------|-------------|-----------------|

| 1          | GND         | GND             | 21         | 0           | MUX2            | 41         | SUP         | AV <sub>DD</sub> | 61         | GND         | GND             |

| 2          | Ι           | DR0             | 22         | GND         | GND             | 42         | Ι           | V5N              | 62         | GND         | GND             |

| 3          | 0           | DT0             | 23         | SUP         | V <sub>DD</sub> | 43         | Ι           | V5               | 63         | I           | EIZP            |

| 4          | I/O         | RFS0            | 24         | 0           | AUX0            | 44         | Ι           | V4N              | 64         | I           | EIA             |

| 5          | I/O         | TFS0            | 25         | 0           | AUX1            | 45         | Ι           | V4               | 65         | I           | EIB             |

| 6          | I/O         | SCLK0           | 26         | I/O         | PIO0            | 46         | Ι           | V3N              | 66         | I           | RESET           |

| 7          | SUP         | V <sub>DD</sub> | 27         | I/O         | PIO1            | 47         | Ι           | V3               | 67         | I           | PWMPOL          |

| 8          | GND         | GND             | 28         | I/O         | PIO2            | 48         | SUP         | AV <sub>DD</sub> | 68         | GND         | GND             |

| 9          | Ι           | PWMTRIP         | 29         | I/O         | PIO3            | 49         | GND         | AGND             | 69         | I           | CLKIN           |

| 10         | 0           | PWMSYNC         | 30         | I/O         | PIO4            | 50         | GND         | AGND             | 70         | 0           | XTAL            |

| 11         | 0           | CL              | 31         | GND         | GND             | 51         | SUP         | AV <sub>DD</sub> | 71         | 0           | CLKOUT          |

| 12         | 0           | CH              | 32         | SUP         | V <sub>DD</sub> | 52         | Ι           | REFINB           | 72         | GND         | GND             |

| 13         | 0           | BL              | 33         | I/O         | PIO5            | 53         | Ι           | REFINA           | 73         | SUP         | V <sub>DD</sub> |

| 14         | GND         | GND             | 34         | I/O         | PIO6            | 54         | 0           | VREF             | 74         | I           | DR1A            |

| 15         | SUP         | V <sub>DD</sub> | 35         | I/O         | PIO7            | 55         | Ι           | V2N              | 75         | I           | DR1B            |

| 16         | 0           | BH              | 36         | I/O         | PIO8            | 56         | Ι           | V2               | 76         | 0           | DT1             |

| 17         | 0           | AL              | 37         | I/O         | PIO9/CONVST     | 57         | Ι           | V1N              | 77         | I/O         | RFS1/SROM       |

| 18         | 0           | AH              | 38         | I/O         | PIO10/ETU0      | 58         | I           | V1               | 78         | I/O         | TFS1            |

| 19         | 0           | MUX0            | 39         | I/O         | PIO11/ETU1      | 59         | SUP         | AV <sub>DD</sub> | 79         | I/O         | SCLK1           |

| 20         | 0           | MUX1            | 40         | GND         | AGND            | 60         | GND         | AGND             | 80         | SUP         | V <sub>DD</sub> |

PIN CONFIGURATION 80-Lead Plastic Thin Quad Flatpack (TQFP) (ST-80)

(Continued from Page 1)

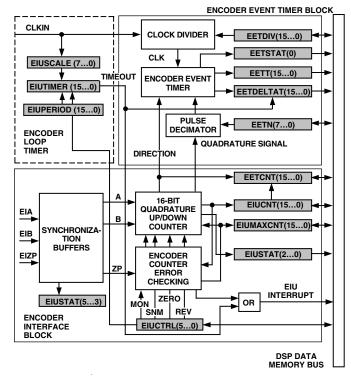

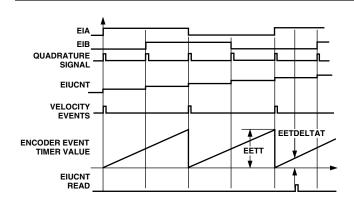

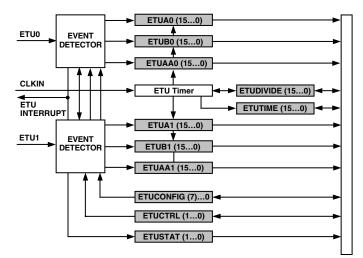

Flexible Encoder Interface Subsystem **Incremental Encoder Interface** Dedicated Three Pin Interface (EIA, EIB, EIZP) **16-Bit Quadrature Counter** Input Encoder Signals to 3.1 MHz **Optional Use of Zero Marker to Reset Counter** Single North Marker Mode—Permits Single **Reset of Counter On Only First Zero Marker Status Bits to Read Encoder Inputs Companion Encoder Event System for Accuracy Enhancements at Low Speeds** Associated EIU Loop Timer Permits Regular, Programmable Updating of All Encoder and **Event Timer Registers EIU Timer Can Also Be Used as General Purpose** Timer If Not Linked to EIU Block Peripheral I/O (PIO) Subsystem 12-Pin Digital I/O Port Bit Configurable as Input or Output Each Pin Configurable as Rising Edge, Falling Edge, High Level or Low Level Interrupt Four Dedicated PIO Interrupts for PIO0 to PIO3 **One Combined Interrupt for PIO4 to PIO11** Each I/O Line Configurable as PWM Trip Source **Two 8-Bit Auxiliary PWM Outputs** Synthesized Analog Output Fixed 48.8 kHz Operation 0 to 99.6% Duty Cycle **Event Timer Unit Two Event Timer Channels with Dedicated Event** Capture Blocks Permits Timing of Duty-Cycle, Period and Frequency **Configurable Event Definition Dedicated Event Timer Interrupt Event Timer Readable On-the-Fly 16-Bit Watchdog Timer Programmable 16-Bit Interval Timer with Prescaler Two Double Buffered Synchronous Serial Ports** Four Boot Load Protocols via SPORT1 E<sup>2</sup>PROM/SROM Booting UART Booting (SCI Compatible) with Autobaud Feature Synchronous Master Booting with Autobaud Feature Synchronous Slave Booting with Autobaud Feature Debugger Interface via SPORT1 with Autobaud (UART and Synchronous Supported) **ROM Utilities Full Debugger for Program Development Preprogrammed Math Functions** Preprogrammed Motor Control Functions-Vector Transformations 80-Lead TQFP Package Industrial Temperature Range -40°C to +85°C

#### **GENERAL DESCRIPTION**

The ADMC300 is a single-chip DSP-based controller, suitable for high performance control of ac induction motors, permanent magnet synchronous motors and brushless dc motors. The ADMC300 integrates a 25 MIPS, fixed-point DSP core with a complete set of motor control peripherals that permits fast, efficient development of servo motor controllers.

The DSP core of the ADMC300 is the ADSP-2171, which is completely code compatible with the ADSP-2100 DSP family and combines three computational units, data address generators and a program sequencer. The computational units comprise an ALU, a multiplier/accumulator (MAC) and a barrel shifter. The ADSP-2171 adds new instructions for bit manipulation, multiplication (X squared), biased rounding and global interrupt masking. In addition, two flexible, double-buffered, bidirectional, synchronous serial ports are included in the ADMC300.

The ADMC300 provides  $4K \times 24$ -bit program memory RAM,  $2K \times 24$ -bit program memory ROM and  $1K \times 16$ -bit data memory RAM. The program and data memory RAM can be boot loaded through the serial port from either a serial SROM/ $E^2$ PROM, asynchronous (UART) connection, or synchronous connection. The program memory ROM includes a monitor that adds software debugging features through the serial port. In addition, a number of pre-programmed mathematical and motor control functions are included in the program memory ROM.

The motor control peripherals of the ADMC300 comprise a high performance, five channel ADC system that uses sigmadelta conversion technology offering a typical signal-to-noise ratio (SNR) of 76 dB, equivalent to 12 bits. In addition, a 16-bit center-based PWM generation unit can be used to produce high accuracy PWM signals with minimal processor overhead. The ADMC300 also contains a flexible encoder interface unit for position sensor feedback, two auxiliary PWM outputs, twelve lines of digital I/O, a two-channel event capture system, a 16-bit watchdog timer, a 16-bit interval timer and a programmable interrupt controller that manages all peripheral interrupts.

Figure 3. DSP Core Block Diagram

#### **DSP CORE ARCHITECTURE OVERVIEW**

Figure 3 is an overall block diagram of the DSP core of the ADMC300, which is based on the fixed-point ADSP-2171. The ADSP-2171 flexible architecture and comprehensive instruction set allows the processor to perform multiple operations in parallel. In one processor cycle (40 ns with a 12.5 MHz CLKIN) the DSP core can:

- Generate the next program address.

- Fetch the next instruction.

- Perform one or two data moves.

- Update one or two data address pointers.

- Perform a computational operation.

This all takes place while the processor continues to:

- Receive and transmit through the serial ports.

- Decrement the interval timer.

- Generate PWM signals.

- Convert the ADC input signals.

- Operate the encoder interface unit.

- Operate all other peripherals including the auxiliary PWM and event timer subsystem.

The processor contains three independent computational units: the arithmetic and logic unit (ALU), the multiplier/accumulator (MAC) and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add, multiply/ subtract operations with 40 bits of accumulation. The shifter performs logical and arithmetic shifts, normalization, denormalization, and derive exponent operations. The shifter can be used to efficiently implement numeric format control including floatingpoint representations.

The internal result (R) bus directly connects the computational units so that the output of any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps and subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the ADMC300 executes looped code with zero overhead; no explicit jump instructions are required to maintain the loop. Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches from data memory and program memory. Each DAG maintains and updates four address pointers (I registers). Whenever the pointer is used to access data (indirect addressing), it is post-modified by the value in one of four modify (M) registers. A length value may be associated with each pointer (L registers) to implement automatic modulo addressing for circular buffers. The circular buffering feature is also used by the serial ports for automatic data transfers to and from on-chip memory. DAG1 generates only data memory address but provides an optional bit-reversal capability. DAG2 may generate either program or data memory addresses, but has no bit-reversal capability.

Efficient data transfer is achieved with the use of five internal buses:

- Program Memory Address (PMA) Bus

- Program Memory Data (PMD) Bus

- Data Memory Address (DMA) Bus

- Data Memory Data (DMD) Bus

- Result (R) Bus

Program memory can store both instructions and data, permitting the ADMC300 to fetch two operands in a single cycle one from program memory and one from data memory. The ADMC300 can fetch an operand from on-chip program memory and the next instruction in the same cycle.

The ADMC300 writes data from its 16-bit registers to the 24-bit program memory using the PX register to provide the lower eight bits. When it reads data (not instructions) from 24-bit program memory to a 16-bit data register, the lower eight bits are placed in the PX register.

The ADMC300 can respond to a number of distinct DSP core and peripheral interrupts. The DSP core interrupts include serial port receive and transmit interrupts, timer interrupts, software interrupts and external interrupts. The motor control peripherals also produce interrupts to the DSP core.

The two serial ports (SPORTs) provide a complete synchronous serial interface with optional companding in hardware and a wide variety of framed and unframed data transmit and receive modes of operation. Each SPORT can generate an internal programmable serial clock or accept an external serial clock. Boot loading of both the program and data memory RAM of the ADMC300 is through the serial port SPORT1.

A programmable interval counter is also included in the DSP core and can be used to generate periodic interrupts. A 16-bit count register (TCOUNT) is decremented every n processor cycles, where n–1 is a scaling value stored in the 8-bit TSCALE register. When the value of the counter reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

The ADMC300 instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Each instruction is executed in a single 40 ns processor cycle (for a 12.5 MHz CLKIN). The ADMC300 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools support program development. For further information on the DSP core, refer to the *ADSP-2100 Family User's Manual, Third Edition*, with particular reference to the ADSP-2171.

#### **Serial Ports**

The ADMC300 incorporates two complete synchronous serial ports (SPORT0 and SPORT1) for serial communication and multiprocessor communication. Following is a brief list of capabilities of the ADMC300 SPORTs. Refer to the *ADSP-2100 Family User's Manual, Third Edition*, for further details.

- SPORTs are bidirectional and have a separate, doublebuffered transmit and receive section.

- SPORTs can use an external serial clock or generate their own serial clock internally.

- SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated. Frame synchronization signals are active high or inverted, with either of two pulsewidths and timings.

- SPORTs support serial data word lengths from 3 bits to 16 bits and provide optional A-law and μ-law companding according to ITU (formerly CCITT) recommendation G.711.

- SPORT receive and transmit sections can generate unique interrupts on completing a data word transfer.

- SPORTs can receive and transmit an entire circular buffer of data with only one overhead cycle per data word. An interrupt is generated after a data buffer transfer.

- SPORT0 has a multichannel interface to selectively receive and transmit a 24-word or 32-word, time-division multiplexed, serial bitstream.

- SPORT1 can be configured to have two external interrupts (IRQ0 and IRQ1), and the Flag In and Flag Out signals. The internally generated serial clock may still be used in this configuration.

- SPORT1 is the default input for program and data memory boot loading. The RFS1 pin can be configured internal to the ADMC300 as an SROM/E<sup>2</sup>PROM reset signal.

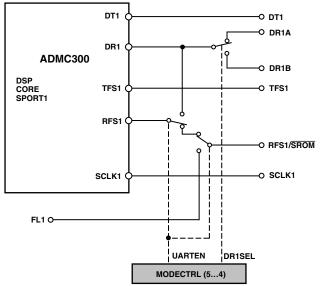

- SPORT1 has two data receive pins (DR1A and DR1B). The DR1A pin is intended for synchronous boot loading from the external SROM/E<sup>2</sup>PROM. The DR1B pin can be used as the data receive pin for boot loading from an external UART (SCI compatible) or synchronous connection, as the data receive pin for the debugger communicating over the debugger interface, or as the data receive pin for a general purpose SPORT after booting. These two pins are internally multiplexed onto the one DR1 port of the SPORT. The particular data receive pin selected is determined by a bit in the MODECTRL register.

#### PIN FUNCTION DESCRIPTION

The ADMC300 is available in an 80-lead TQFP package. Table I contains the pin descriptions.

#### Table I. Pin List

| Pin<br>Group<br>Name | #<br>of<br>Pins | Input/<br>Output | Function                                                               |

|----------------------|-----------------|------------------|------------------------------------------------------------------------|

| RESET                | 1               | I                | Processor Reset Input.                                                 |

| SPORT0               | 5               | I/O              | Serial Port 0 Pins (TFS0, RFS0, DT0, DR0, SCLK0).                      |

| SPORT1               | 6               | I/O              | Serial Port 1 Pins (TFS1,<br>RFS1, DT1, DR1A, DR1B,<br>SCLK1).         |

| CLKOUT               | 1               | 0                | Processor Clock Output.                                                |

| CLKIN, XTAL          | 2               | I, O             | External Clock or Quartz Crystal Connection Point.                     |

| PIO0-PIO11           | 12              | I/O              | Digital I/O Port, External Con-<br>vert Start and Event Timer<br>Pins. |

| AUX0-AUX1            | 2               | 0                | Auxiliary PWM Outputs.                                                 |

| AH–CL                | 6               | 0                | PWM Outputs.                                                           |

| PWMTRIP              | 1               | Ι                | PWM Trip Signal.                                                       |

| PWMPOL               | 1               | Ι                | PWM Polarity Pin.                                                      |

| PWMSYNC              | 1               | 0                | PWM Synchronization Pin.                                               |

| V1-V5                | 5               | Ι                | Noninverting Inputs of the Dif-<br>ferential ADCs' Input Amplifiers.   |

| V1N-V5N              | 5               | Ι                | Inverting Inputs of the Differen-<br>tial ADCs' Input Amplifiers.      |

| REFINA–<br>REFINB    | 2               | Ι                | Voltage reference inputs for ADCs.                                     |

| VREF                 | 1               | 0                | Voltage Reference Output.                                              |

| MUX0-MUX2            | 3               | 0                | Multiplexer Control Lines.                                             |

| EIA, EIB, EIZP       | 3               | Ι                | Encoder Interface Pins.                                                |

| $AV_{DD}$            | 4               |                  | Analog Power Supply.                                                   |

| AGND                 | 4               |                  | Analog Ground.                                                         |

| V <sub>DD</sub>      | 6               |                  | Digital Power Supply.                                                  |

| GND                  | 9               |                  | Digital Ground.                                                        |

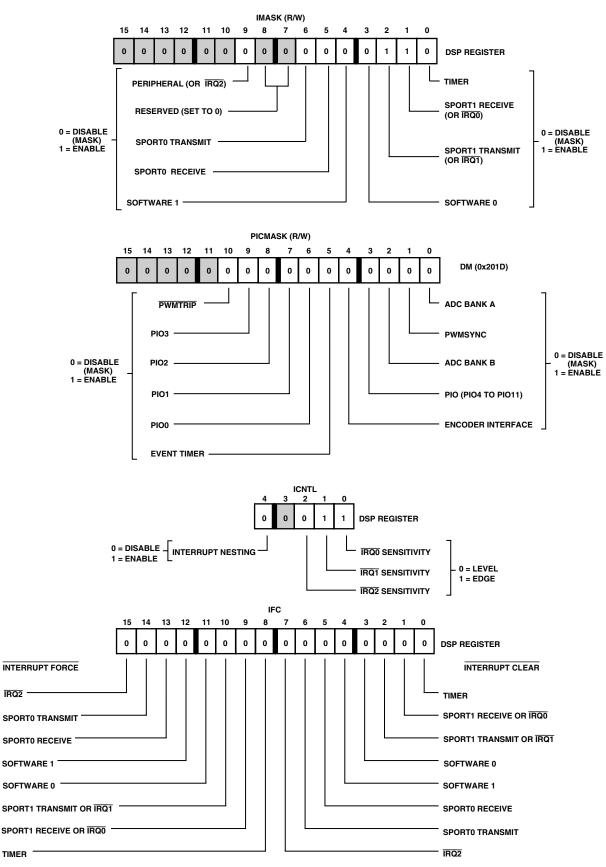

#### **INTERRUPT OVERVIEW**

The ADMC300 can respond to nineteen different interrupt sources, eight of which are internal DSP core interrupts and eleven interrupts from the motor control peripherals. The eight DSP core interrupts comprise the peripheral ( $\overline{IRQ2}$ ), SPORT0 receive, SPORT0 transmit, SPORT1 receive (or IRO0), SPORT1 transmit (or  $\overline{IRQ1}$ ), two software and the interval timer interrupts. In addition, the motor control peripherals add eleven interrupts that include two ADC, two PWM, five peripheral I/O, one encoder interface and one event timer interrupt. The interrupts are internally prioritized and individually maskable. All peripheral interrupts are multiplexed into the DSP core through the peripheral IRQ2 interrupt. The programmable interrupt controller manages the masking and vector addressing of all eleven peripheral interrupts. A detailed description of the operation of the entire interrupt system of the ADMC300 is given later, after a more detailed description of the various peripheral systems.

#### **Memory Map**

The ADMC300 has two distinct memory types; program memory and data memory. In general, program memory contains user code and coefficients, while the data memory is used to store variables and data during program execution. Both program memory RAM and ROM is provided on the ADMC300. Program memory RAM is arranged in two noncontiguous  $2K \times 24$ -bit blocks, one starting at address 0x0000 and the other at 0x1800. Program memory ROM is located at address 0x0800. Data memory is arranged as a  $1K \times 16$ -bit block starting at address 0x3800. The motor control peripherals are memory mapped into a region of the data memory space starting at 0x2000. The complete program and data memory maps are given in Tables II and III respectively.

| <b>Fable II.</b> | Program | Memory | Мар |

|------------------|---------|--------|-----|

|------------------|---------|--------|-----|

| Address Range | Memory<br>Type | Function                                |

|---------------|----------------|-----------------------------------------|

| 0x0000-0x005F | RAM            | Interrupt Vector Table                  |

| 0x0060-0x071F | RAM            | User Program Space                      |

| 0x0720-0x07DF | RAM            | Reserved by Debugger                    |

| 0x07E0-0x07FF | RAM            | Reserved by Monitor                     |

| 0x0800-0x0E20 | ROM            | ROM Monitor                             |

| 0xE21–0xFD6   | ROM            | ROM Math and Motor<br>Control Utilities |

| 0xFD7–0x0FFF  | ROM            | Reserved                                |

| 0x1000–0x17FF |                | Unused                                  |

| 0x1800–0x1FFF | RAM            | User Program Space                      |

| 0x2000–0x3FFF |                | Unused                                  |

| Table III. | Data Memory | Map |

|------------|-------------|-----|

|------------|-------------|-----|

| Address Range                                   | Memory<br>Type | Function                                                          |

|-------------------------------------------------|----------------|-------------------------------------------------------------------|

| 0x0000-0x1FFF<br>0x2000-0x20FF<br>0x2100-0x37FF |                | Unused<br>Memory Mapped Registers<br>Unused                       |

| 0x3800-0x3B5F<br>0x3B60-0x3BFF<br>0x3C00-0x3FFF | RAM<br>RAM     | User Data Space<br>Reserved by Monitor<br>Memory Mapped Registers |

#### **ROM Code**

The  $2K \times 24$ -bit block of program memory ROM starting at address 0x0800 contains a monitor function that is used to download and execute user programs via the serial port. In addition, the monitor function supports an interactive mode in which commands are received and processed from a host. An example of such a host is the Windows<sup>®</sup>-based Motion Control Debugger that is part of the software development system for the ADMC300. In the interactive mode, the host can access both the internal DSP and peripheral motor control registers of the ADMC300, read and write to both program and data memory, implement breakpoints and perform single-step and run/halt operation as part of the program debugging cycle.

In addition to the monitor function, the program memory ROM contains a number of useful mathematical and motor control utilities that can be called as subroutines from the user code. A complete list of these ROM functions is given in Table IV. The start address of the function in the program memory ROM is also given. Refer to the *ADMC300 DSP Motor Controller Developer's Reference Manual* for more details of the ROM functions.

Windows is a registered trademark of Microsoft Corporation.

#### Table IV. ROM Utilities

| Utility    | Address | Function                         |

|------------|---------|----------------------------------|

| PER_RST    | 0x07E4  | Peripheral Reset.                |

| UMASK      | 0x0E21  | Limits Unsigned Value to Given   |

|            |         | Range.                           |

| PUT_VECTOR | 0x0E28  | Facilitates User Setup of Vector |

|            |         | Table.                           |

| SMASK      | 0x0E35  | Limits Signed Value to Given     |

|            |         | Range.                           |

| ADMC_COS   | 0x0E55  | Cosine Function.                 |

| ADMC_SIN   | 0x0E5C  | Sine Function.                   |

| ARCTAN     | 0x0E72  | Arctangent Function.             |

| RECIPROCAL | 0x0E94  | Reciprocal (1/x) Function.       |

| SQRT       | 0x0EAA  | Square Root Function.            |

| LN         | 0x0EE4  | Natural Logarithm Function.      |

| LOG        | 0x0EE7  | Logarithm (Base 10) Function.    |

| FLTONE     | 0x0F03  | Fixed Point to Floating Point    |

|            |         | Conversion.                      |

| FIXONE     | 0x0F08  | Floating Point to Fixed Point    |

|            |         | Conversion.                      |

| FPA        | 0x0F0C  | Floating Point Addition.         |

| FPS        | 0x0F1B  | Floating Point Subtraction.      |

| FPM        | 0x0F2B  | Floating Point Multiplication.   |

| FPD        | 0x0F34  | Floating Point Division.         |

| FPMACC     | 0x0F55  | Floating Point Multiply and      |

|            |         | Accumulate.                      |

| PARK       | 0x0F77  | Forward and Reverse Park         |

|            |         | Transformation (Vector           |

|            |         | Rotation).                       |

| REV CLARK  | 0x0F8B  | Reverse Clark Transformation.    |

| FOR_CLARK  | 0x0FA1  | Forward Clark Transformation.    |

| SDIVQINT   | 0x0FAB  | Unsigned Single Precision        |

|            |         | Division (Integer).              |

| SDIVQ      | 0x0FB4  | Unsigned Single Precision        |

|            |         | Division (Fractional).           |

| EXIT       | 0x0FC6  | Exit to Debugger after Running   |

| •          |         | User Program.                    |

#### SYSTEM INTERFACE

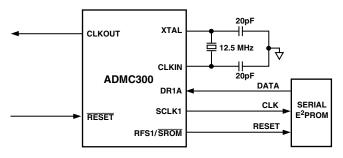

Figure 4 shows a basic system configuration for the ADMC300 with an external crystal and serial  $E^2$ PROM for boot loading of program and data memory RAM.

Figure 4. Basic System Configuration

#### **Clock Signals**

The ADMC300 can be clocked by either a crystal or a TTLcompatible clock signal. The CLKIN input cannot be halted, changed during operation or operated below the specified minimum frequency during normal operation. If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal is connected to the CLKIN pin of the ADMC300. In this mode, with an external clock signal, the XTAL pin must be left unconnected. The ADMC300 uses an input clock with a frequency equal to half the instruction rate; a 12.5 MHz input clock yields a 40 ns processor cycle (which is equivalent to 25 MHz). Normally instructions are executed in a single processor cycle. All device timing is relative to the internal instruction rate, which is indicated by the CLKOUT signal.

Because the ADMC300 includes an on-chip oscillator circuit, an external crystal may be used instead of a clock source, as shown in Figure 4. The crystal should be connected across the CLKIN and XTAL pins, with two capacitors as shown in Figure 4. A parallel-resonant, fundamental frequency, microprocessor-grade crystal should be used. A clock output signal (CLKOUT) is generated by the processor at the processor's cycle rate of twice the input frequency.

#### Reset

The  $\overline{\text{RESET}}$  signal initiates a master reset of the ADMC300. The  $\overline{\text{RESET}}$  signal must be asserted during the power-up sequence to assure proper initialization.  $\overline{\text{RESET}}$  during initial power-up must be held long enough to allow the internal clock to stabilize. If  $\overline{\text{RESET}}$  is activated any time after power-up, the clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for the crystal oscillator circuit to stabilize after a valid  $V_{DD}$  is applied to the processor, and for the internal phase-locked loop (PLL) to lock onto the specific crystal frequency. A minimum of 2000 CLKIN cycles ensures that the PLL has locked, but does not include the crystal oscillator start-up time. During this power-up sequence, the <u>RESET</u> signal should be held low. On any subsequent resets, the <u>RESET</u> signal must meet the minimum pulsewidth specification, t<sub>RSP</sub>.

If an RC circuit is used to generate the  $\overline{\text{RESET}}$  signal, the use of an external Schmitt trigger is recommended.

The master reset sets all internal stack pointers to the empty stack condition, masks all interrupts, initializes DSP core registers and performs a full reset of all of the motor control peripherals. When the  $\overline{\text{RESET}}$  line is released, the first instruction is fetched from internal program memory ROM at location 0x0800. The internal monitor code at this location then commences the boot-loading sequence over the serial port, SPORT1.

#### **Boot Loading**

On power-up or reset, the ADMC300 is configured so that execution begins at the internal PM ROM at address 0x0800. This starts execution of the internal monitor function that first performs some initialization functions and copies a default interrupt vector table to addresses 0x0000–0x005F of program memory RAM. The monitor next attempts to boot load from an external SROM or E<sup>2</sup>PROM on SPORT1 using the three wire connection of Figure 4. The monitor program first toggles the RFS1/ SROM pin of the ADMC300 to reset the serial memory device. If an SROM or E<sup>2</sup>PROM is connected to SPORT1, data is clocked into the ADMC300 at a rate CLKOUT/26. Both

program and data memory RAM can be loaded from the SROM/  $E^2$ PROM. After the boot load is complete, program execution begins at address 0x0060. This is where the first instruction of the user code should be placed.

If boot loading from an  $E^2$ PROM is unsuccessful, the monitor code reconfigures SPORT1 as a UART and attempts to receive commands from an external device on this serial port. The monitor then waits for a byte to be received over SPORT1, locks onto the baud rate of the external device (autobaud feature) and takes in a header word that tells it with what type of device it is communicating. There are six alternatives:

- A UART boot loader such as a Motorola 68HC11 SCI port.

- A synchronous slave boot loader (the clock is external).

- A synchronous master boot loader (the ADMC300 provides the clock).

- A UART debugger interface.

- A synchronous master debugger interface.

- A synchronous slave debugger interface.

With the debugger interface, the monitor enters interactive mode in which it processes commands received from the external device.

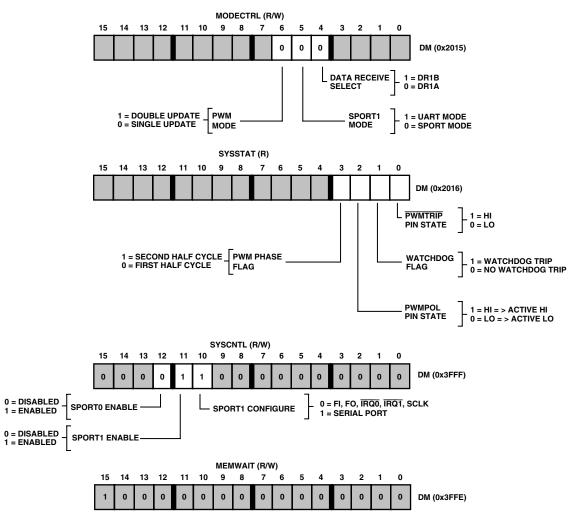

#### **DSP** Control Registers

The DSP core has a system control register, SYSCNTL, memory mapped at DM (0x3FFF). SPORT0 is enabled when Bit 12 is set, disabled when this bit is cleared. SPORT1 is enabled when Bit 11 is set, disabled when this bit is cleared. SPORT1 is configured as a serial port when Bit 10 is set, or as flags and interrupt lines when this bit is cleared. For proper operation of the ADMC300, all other bits in this register must be cleared (which is their default).

The DSP core has a wait state control register, MEMWAIT, memory mapped at DM (0x3FFE). For proper operation of the ADMC300, this register must always contain the value 0x8000 (which is the default).

The configuration of both the SYSCNTL and MEMWAIT registers of the ADMC300 is shown at the end of the data sheet.

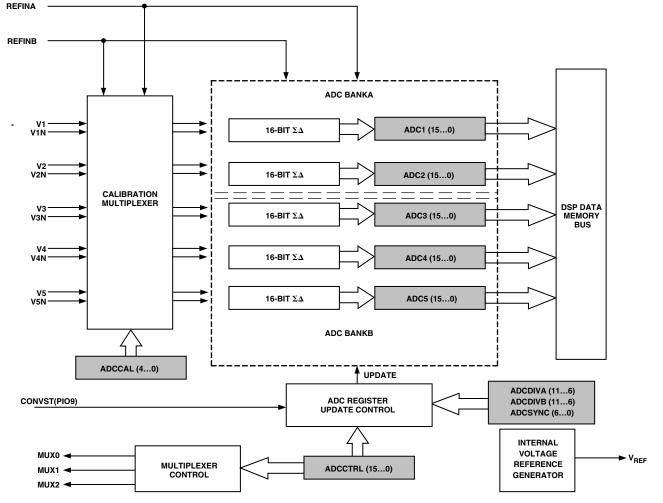

#### ANALOG-TO-DIGITAL CONVERSION SYSTEM

A functional block diagram of the ADC system of the ADMC300 is shown in Figure 5. The ADC system provides the high performance conversion required for precision applications. It integrates five completely independent analog-to-digital converters based on sigma-delta conversion technology. Each ADC channel may

Figure 5. Functional Block Diagram of ADC System of ADMC300

be configured as either a differential or single-ended input for maximum flexibility in interfacing to external sensors and inputs. The sigma-delta converter consists of two stages, a modulator and a sinc filter, that combine to produce a 16-bit conversion. For each channel, signal-to-noise ratios of 76 dB may be achieved, corresponding to greater than 12 bits of resolution from each converter. Input signals up to 16.27 kHz may be converted.

For maximum flexibility, the five ADCs are arranged as two banks; ADC1 and ADC2 forming Bank A, and ADC3, ADC4 and ADC5 forming Bank B. The characteristics of each bank, such as sampling rate, internal or external conversion, synchronization to the PWM block, operating modes, may be controlled independently. The ADC registers of each bank may be loaded from an internal signal whose frequency may be programmed as a precise fraction of the CLKIN frequency. Alternatively, the ADCs may be updated by an external signal on the CONVST pin. There are two dedicated ADC interrupts; one for each bank of converters that can be used to signal that the ADCs of the particular bank have been updated.

The ADC system also contains a built-in calibration function that may be used to null any offsets within the ADC converters. Each ADC channel may be placed in the calibration state individually or in combination with other channels.

In addition, the ADC system provides three multiplexer control pins that may be used in conjunction with an external multiplexer to permit external signal expansion.

There is a separate reference input for each bank of converters. However, the ADMC300 also provides a reference output that could be buffered and used as a reference source for either or both banks.

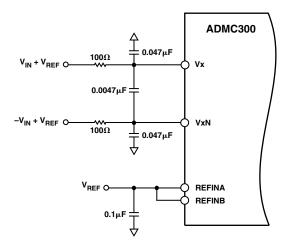

#### Input Configuration

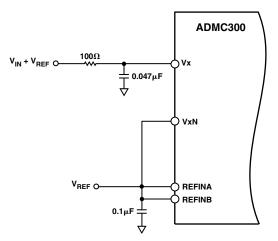

The input to each ADC may be applied to the ADMC300 in either a single-ended or differential configuration. In many cases, a single-ended configuration is easier to provide but the differential connection permits the reduction of common-mode noise from the input signal. Each ADC input may be configured for single-ended or differential inputs as appropriate, completely independent of the other channels. Figure 6 illustrates a typical differential configuration for the inputs of one ADC channel of the ADMC300. The input signals are applied to pins Vx and VxN (for example V1 and V1N). For correct operation and maximum input dynamic range, the inputs signals should be centered on the reference voltage level, V<sub>REF</sub>. Therefore, the signal applied to the Vx pin should be  $V_{IN} + V_{REF}$ , where V<sub>IN</sub> is the analog input voltage. The corresponding signal applied to the inverting terminal of the differential input, VxN, is then  $-V_{IN} + V_{REF}$  so that the differential signal applied to the ADC input is actually 2  $V_{IN}$ .

The input RC combination of  $100 \Omega$  and  $0.047 \mu$ F provides a first-order low-pass antialiasing filter with a cutoff frequency of 34 kHz. An advantage to sigma-delta ADCs is that the initial (analog) signal filtering required for antialiasing is much more modest than that required by other ADCs. With the sigma-delta ADC, the input filter needed for the analog signal only has to cut off at one-half of the modulator frequency, rather than the lower effective sampling frequency. For the ADMC300, the modulator runs 64 times faster than the sampling frequency. Thus for a 32.5 kHz sampling rate, the modulator frequency is 2.08 MHz, meaning the needed cutoff for the analog input signal is 1.04 MHz. Therefore, a simple first order filter, such

as the RC filter shown in Figure 6, which provides a more than 30 dB attenuation to signals above 1 MHz (3 dB at 34 kHz) is adequate. The additional antialiasing band limiting required by the Nyquist criterion for the 32.5 kHz sampling rate (a cutoff of 16.25 kHz) is supplied by the high order sinc filter in the digital domain.

*Figure 6. Differential Configuration for ADC Input of ADMC300*

Figure 7. Single-Ended Configuration for ADC Input of ADMC300

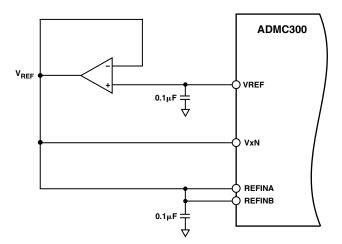

Figure 8. Connection of Internal Voltage Reference of ADMC300

The corresponding configuration for single-ended operation is shown in Figure 7, where the inverting input is now tied directly to the reference voltage level. The noninverting input is  $V_{IN} + V_{REF}$ . An antialiasing filter with a cutoff at 34 kHz is included on this input. Clearly, the differential input voltage swing in this configuration is half that of the differential configuration. Therefore, when operating in single-ended mode, the input voltage,  $V_{IN}$ , may be twice as large as that when operating differentially.

To ensure correct operation, a 0.1  $\mu$ F, high-quality capacitor must be included at the reference input pins. A 0.1  $\mu$ F capacitor should also be used at the VREF pin, even if external references are used.

In both Figures 6 and 7, it is assumed that an external precision reference is used to provide the reference voltage level,  $V_{REF}$ . For optimum operation, a high-performance 2.5 V reference such as the AD580 is recommended. This reference is applied directly to both input reference pins, REFINA and REFINB, and is also applied to any external bias circuitry used to produce the ADC input signals. For a lower cost solution, the ADMC300 also provides a reference output that may be used to provide the  $V_{REF}$  signal. The reference output is available at the VREF pin. For correct operation, a 0.1 µF capacitor is required at this pin even if the internal reference is not used. In addition, it is recommended that the  $V_{REF}$  signal be buffered in a unity-gain stage prior to use, as shown in Figure 8. Of course, since there are two separate reference inputs, pins REFINA and REFINB, the two banks of ADCs may be run differently, if required.

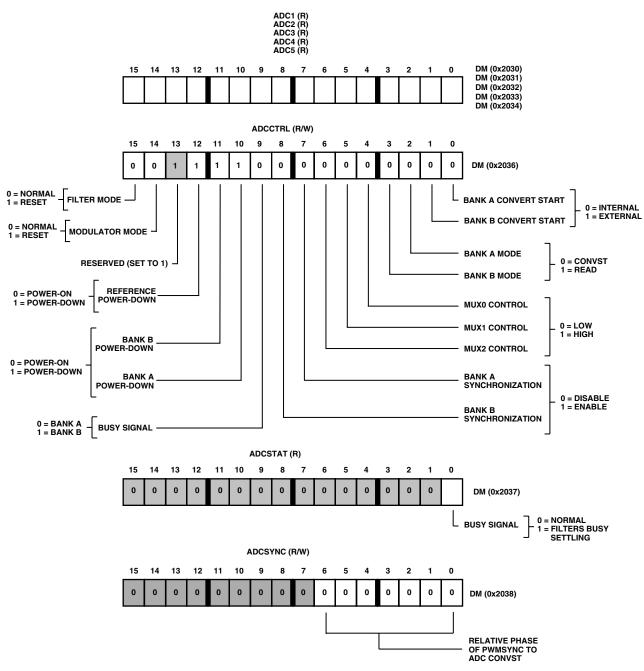

#### ADC Register Update

The sigma-delta converters of the ADMC300 operate at a highly oversampled rate. A number of control bits in the ADCCTRL register are used to control when and how data is latched into the ADC data registers of each bank. The data registers of each bank may be latched at a regular rate based on either an internal or an external convert start signal. Bits 0-1 of the ADCCTRL register determine whether the convert start signal is internal or external. Bit 0 controls the operation of Bank A and Bit 1 controls the operation of Bank B. If either of these bits is set to 1, the data registers of the corresponding ADC bank are latched within two CLKIN cycles of the occurrence of a rising edge on the CONVST pin (PIO9). Alternatively, if either bit is set to zero, internal mode is selected and the ADCs of the particular bank are updated at a regular rate, determined by the contents of the appropriate ADC sample frequency division register, ADCDIVA or ADCDIVB.

Bits 2–3 of the ADCCTRL register can be used to place the ADC banks in an alternative read mode. The read mode is enabled by setting these bits to 1, effectively disabling the convert start mode. In the read mode, the ADC registers of the particular bank are continuously updated at a rate equal to half the DSP clock rate, so that data is effectively available on demand. Bit 2 of the ADCCTRL register is used to place ADC Bank A in read mode, while Bit 3 is used for Bank B.

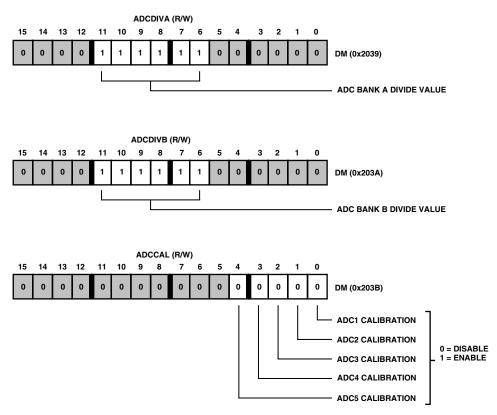

#### **ADC Sample Rate Selection**

Internal convert start mode is selected by clearing Bits 0 and 2 of the ADCCTRL register for Bank A and Bits 1 and 3 for Bank B. In this mode, the ADC data registers are updated at a regular rate that is determined by the ADC clock divide registers, ADCDIVA and ADCDIVB. Therefore, each bank can be configured for independent update rates by writing different values to the two registers. When Bank A and Bank B are configured for independent update rates, it is important that the REFINA and REFINB pins are driven by separate voltage reference sources to avoid excessive crosstalk between banks. The ADCDIVA and ADCDIVB registers are 6-bit registers aligned in Bits 6–11 and the value written to these registers is used to divide the CLKIN frequency to provide the ADC update rate. A 12-bit value is written to these registers, but since Bits 0–5 are ignored, the value should be an integer multiple of 64 or 0x040. The resultant ADC update rates for Banks A and B may be expressed as:

$$f_{S,A} = \frac{f_{CLKIN}}{ADCDIVA}$$

$$f_{S,B} = \frac{f_{CLKIN}}{ADCDIVB}$$

where  $f_{CLKIN}$  is the CLKIN frequency, equal to half the DSP instruction rate. Therefore, writing a value of 0x180 (= 384) gives an ADC update rate of 32.55 kHz with a CLKIN frequency of 12.5 MHz. The maximum value that can be written to these registers is 0xFC0, corresponding to an update rate of 3.1 kHz. Since the maximum update rate is limited to 32.55 kHz, the permissible range of ADC divide values is 0x180 to 0xFC0 in steps of 0x040.

Each ADC channel contains an input modulator that oversamples the input signal at a high rate. The modulator sample frequency is automatically set by the internal ADC control to be exactly 64 times the ADC update rate determined by the ADC divide registers. This corresponds to an oversample ratio of 64. Therefore, in the case where ADCDIVA = 0x180, the input modulators of ADC Bank A sample the input signal at 2.08 MHz and the data registers ADC1 and ADC2 are updated at the 32.55 kHz rate.

#### Synchronization of ADC and PWM Systems

In motor control applications, it is advantageous to synchronize the operation of the ADC system to the PWM pulse generation. The ADMC300 permits separate control of such synchronization for each ADC bank and permits sophisticated definition of the particular way that the ADC and PWM systems are synchronized. Operation of Bank A of the ADC may be synchronized to the PWM by setting Bit 7 of the ADCCTRL register. Similarly, setting Bit 8 of the ADCCTRL register enables synchronization of Bank B to the PWM.

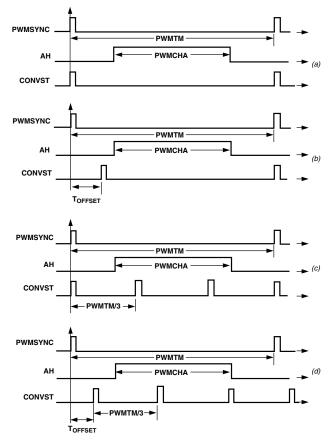

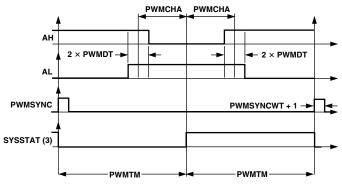

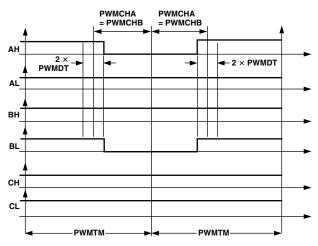

At its simplest, the ADC and PWM systems may be programmed to operate at the same frequency and be synchronized to one another so that the ADC data registers are automatically updated at the start of each PWM period. This mode of operation is illustrated in Figure 9(a) and is enabled by writing identical values to the PWM period register, PWMTM, and the ADC divide register, ADCDIVA or ADCDIVB. Synchronization is subsequently enabled by setting Bit 7 (for Bank A) or Bit 8 (for Bank B) of the ADCCTRL register.

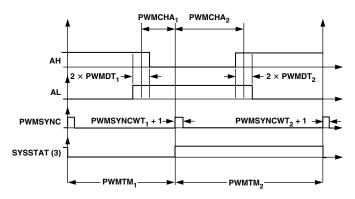

Additionally, a separate control register, ADCSYNC may be used to phase shift the update of the ADC registers to some suitably defined instant within the PWM period. In this mode, the frequencies of the PWM and ADC register updating are still the same but phase shifted relative to one another. This mode is illustrated in Figure 9 (b). Again, the PWM period register and ADC divide registers are loaded with the same value. However, the offset of the ADC update within the PWM period is programmed using the ADCSYNC register. The ADCSYNC register is a 7-bit register so that the ADC sample period is effectively subdivided into 128 equal time slices. The value written to the ADCSYNC register is the number of such time slices before the PWMSYNC pulse that the CONVST pulse is active. In other words, the occurrence of the CONVST pulse lags the PWMSYNC pulse of Figure 9 (b) by a time, T<sub>OFFSET</sub>, that can be expressed as a fraction of the ADC update period:

$$T_{OFFSET} = \frac{(128 - ADCSYNC)}{128} \left(\frac{ADCDIVn}{f_{CLKIN}}\right)$$

Therefore, for the case where ADCDIVA is 0x180 and ADCSYNC is 0x060, the CONVST pulse will lag the PWMSYNC pulse by a quarter of the ADC update period, or 7.68 µs, with a 12.5 MHz CLKIN. The ability to phase shift the ADC update relative to the PWMSYNC pulse is available only in single update mode of the PWM.

It is also possible to operate the ADCs at a faster update rate than the PWM switching frequency and still maintain synchronism, as illustrated in Figure 9 (c). In this example, the value written to the ADCDIV registers is three times larger than the value written to the PWMTM register, so that the ADC update rate is three times faster than the PWM switching frequency. Synchronism is maintained by setting Bits 7 and 8 of the ADCCTRL register. In addition, it is possible to introduce a

Figure 9. (a) Synchronization of ADC and PWM at Same Frequency with No Offset, (b) Synchronization of ADC and PWM at Same Frequency with Offset, (c) Synchronization of ADC and PWM with No Offset and ADC Update at Three Times the PWM Frequency (d) Synchronization of ADC and PWM at Different Frequencies with Offset (PWM Is Operating in Single Update Mode)

phase shift between the ADC update and PWMSYNC pulses while operating at different frequencies, as illustrated by Figure 9 (d). The offset is defined by the ADCSYNC register as a fraction of the ADC update period in an identical manner to before.

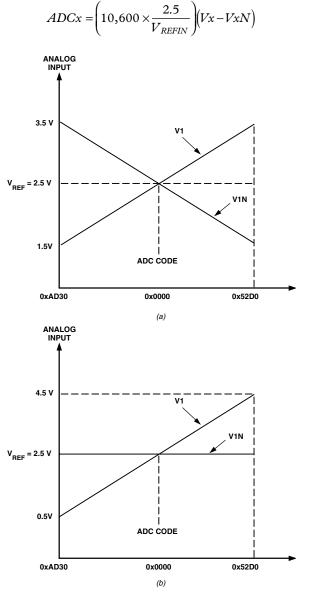

#### **ADC Transfer Characteristics**

Each ADC converter of the ADMC300 consists of an input modulator stage and a decimation filter stage that produces the final conversion result. The output of the decimation filters are 16-bit, left-aligned, two's complement representation of the input signal,  $V_{IN}$ . The ideal ADC transfer characteristics for both single-ended and differential modes are shown in Figure 10. The transfer characteristics of the ADC when operated in the differential configuration are shown in Figure 10 (a) and for the single-ended configuration in Figure 10 (b). The peak-peak input voltage is 4 V.

The output code of the ADCs is typically given by:

*Figure 10. (a) Typical Transfer Characteristic of the ADC in Differential Input Configuration (b) Typical Transfer Characteristic of the ADC in Single-Ended*

#### ADC Group Delay

The digital filters of the ADCs carry out two important functions. First, they remove the out-of-band quantization noise, which has been suitably shaped by the noise-shaping circuits of the input modulator stages. The digital filters then decimate the high frequency bitstream from the modulators to a lower rate 16-bit word. The lower rate is set by the ADC divide registers for the respective ADC banks as described previously. The antialiasing decimation filter may be modeled by the Z-domain transfer function:

$$H_{SINC}(Z) = \left[\frac{1}{64} \left(\frac{1 - z^{-64}}{1 - z^{-1}}\right)\right]^3$$

Associated with the sinc filters is a group delay that may be approximated by:

$$t_{\phi} = \frac{1.5}{f_S}$$

where  $f_S$  is the update rate of the particular ADC channel. In order to minimize the impact of the group delay on the overall performance of the control system, it is advantageous to oversample the ADCs at a rate faster than the PWM frequency.

#### ADC Calibration

The ADC system of the ADMC300 has a calibration feature that may be used to null any offsets in the ADC channels. There is a 5-bit ADC calibration register, ADCCAL that has a dedicated bit for each ADC channel. Setting the appropriate bit of the ADCCAL register will place the respective ADC channel in the offset calibration state. Bit 0 controls ADC1, Bit 1 controls ADC2, etc. When the appropriate bit of the ADCCAL register is set, the two input pins associated with that ADC channel are effectively disconnected from the pins of the ADMC300 and connected internally to the reference voltage. After waiting for the settling time of the decimation filters, the resultant ADC code is a measure of the offset for that particular ADC channel. This number should be saved in memory and used to correct all further measurements from that channel.

#### **ADC Interrupt Generation**

Two dedicated interrupts are associated with the ADC system of the ADMC300, one for each of the ADC banks. The interrupts are generated after the ADC data registers of the particular bank have been updated by either an internal or external CONVST pulse. Interrupts are not generated when the ADCs are in the read mode. There are separate interrupt vector locations associated with each of the interrupt sources. The ADC Bank A interrupt is the highest priority interrupt with its vector address at program memory location 0x0030. The Bank B interrupt is the third highest priority interrupt with a vector address of 0x0038. Each interrupt has a four word space in the vector table. The sequencing and masking of these interrupts is managed by the Programmable Interrupt Controller (PIC) block described later.

#### ADC Multiplexer Control

The ADMC300 has three digital output pins, MUX2, MUX1 and MUX0, that can be used to drive an external multiplexer to feed additional analog inputs to the ADCs if required. Using these control lines, up to eight analog signals could be externally multiplexed into each ADC channel, allowing expansion up to 40 analog inputs. The state of the three multiplexer pins is directly controlled from the ADCCTRL register, using Bits 4–6. Bit 4 of the ADCCTRL register directly controls the MUX0 pin, so that setting this bit will place a HI level on the MUX0 pin. Similarly, Bit 5 directly controls the MUX1 pin and Bit 6 controls the MUX2 pin.

Because of the finite impulse response of the decimation filters of the ADCs, it is usually only slower dynamic signals that are multiplexed into the ADCs. In a typical motor control system, such signals may comprise the dc link voltage, the output of various temperature sensors, reference inputs, etc.

#### **ADC Status**

Because of the dynamic characteristics of the decimation filters of the sigma-delta converters, it is necessary to allow the impulse response of the filters to decay before meaningful, accurate data is available. There is a one-bit status register, ADCSTAT, in the ADMC300 that indicates whether or not valid data is available from the ADC. Bit 0 of the ADCSTAT register is asserted while the decimation filters are settling to indicate that data is not yet valid. This BUSY bit can be programmed to represent the status of the decimation filters of either Bank A or Bank B by programming Bit 9 of the ADCCTRL register. The BUSY bit will go active for four ADC sample periods any time that ADCCTRL, ADCCAL or ADCSYNC are written to. If Bit 9 of the ADCCTRL register is cleared, the BUSY bit will go active any time ADCDIVA is written to, and the four ADC sample period width of the BUSY pulse will be four ADC Bank A sample periods. If Bit 9 of the ADCCTRL register is set, the BUSY bit will go active any time the ADCDIVB register is written to, and the four ADC sample period width of the BUSY pulse will be four ADC Bank B sample periods. It is still possible to read the ADC data registers while the BUSY signal is asserted. However, care must be taken in the interpretation of such data.

#### **ADC Power-Down and Reset Features**

The ADC section of the ADMC300 has certain power-down features that may be used to reduce the overall power consumption of the part. Each bank of the ADC system may be individually powered down if all channels of that bank are not used in a particular application. Setting Bit 10 of the ADCCTRL register will power down the input modulators of both ADC channels of ADC Bank A. Similarly, setting Bit 11 of the ADCCTRL register will power down the three ADC channels of Bank B. Clearing these bits will enable the input modulators of the respective banks. On power-up, both Bits 10 and 11 of the ADCCTRL register are set by default, so that all five input modulator stages are disabled. To operate the required ADC channels, the appropriate bits in the ADCCTRL register must be cleared.

In addition, setting Bit 12 of the ADCCTRL register will power down the internal reference circuitry. Further power reduction is possible if this reference circuitry is powered down. However, this bit has an effect only if both ADC banks are also powered down. Clearing Bit 12 of the ADCCTRL register will enable the internal reference circuitry.

It is also possible to force a reset of all five input modulators of the ADC system by setting Bit 14 of the ADCCTRL register. Setting Bit 15 of the ADCCTRL register will force a reset of the decimation filters in all five ADC channels. In order to come out of input modulator reset or decimation filter reset, the respective bit must be cleared. On power-up, these bits are cleared so that both the modulators and the decimation filters come up in the normal mode. It is recommended that prior to use, a full reset be performed.

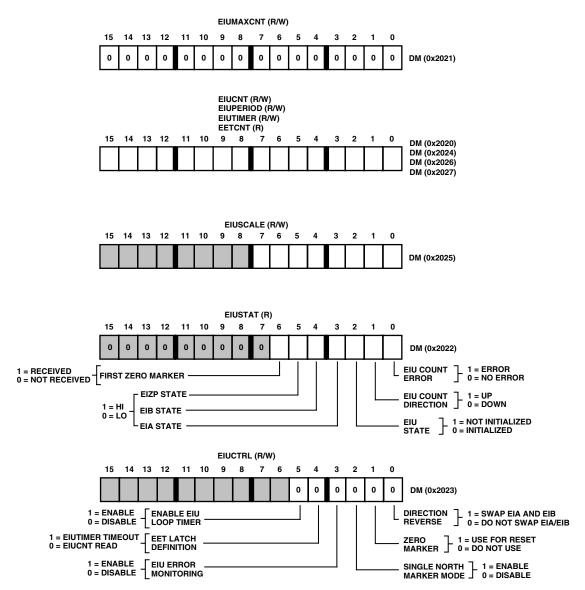

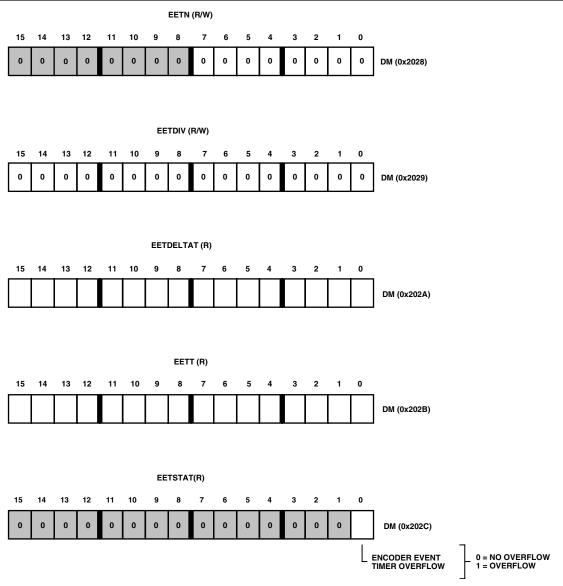

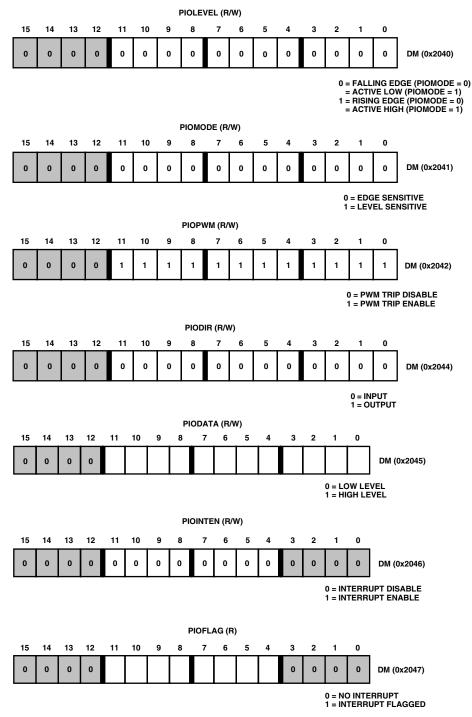

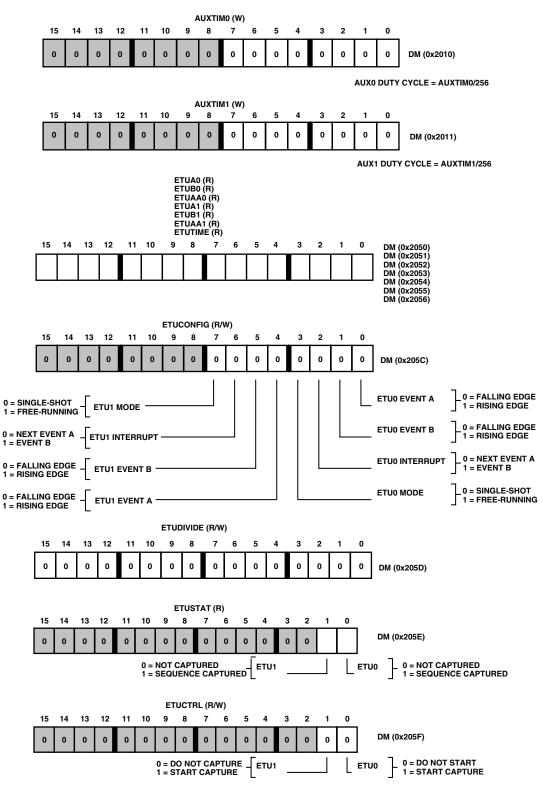

#### ADC Registers

The composition of all the data registers associated with the ADC system of the ADMC300 is shown at the end of the data sheet. The reset values are shown for certain bits, where appropriate.

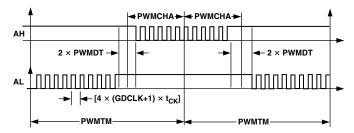

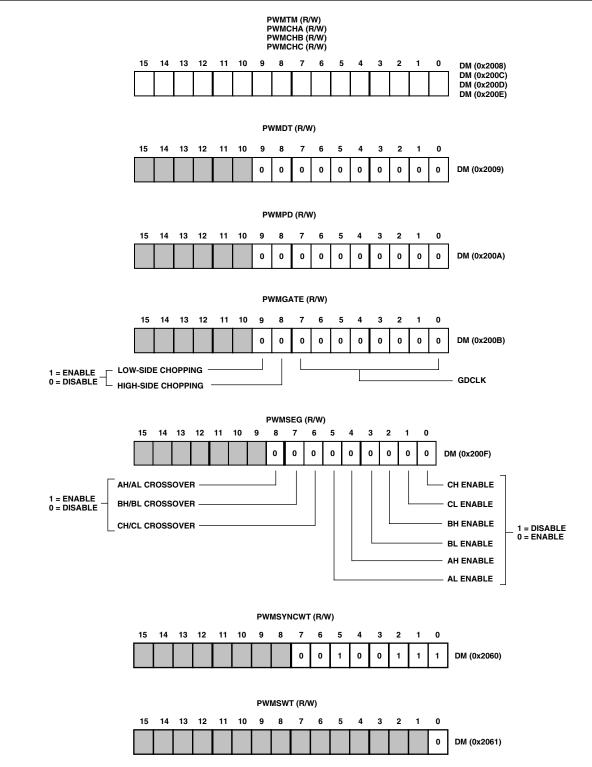

#### THREE-PHASE PWM CONTROLLER

The PWM generator block of the ADMC300 is a flexible, programmable, three-phase PWM waveform generator that can be programmed to generate the required switching patterns to drive a three-phase voltage source inverter for ac induction (ACIM) or permanent magnet synchronous (PMSM) motor control. In addition, the PWM block contains special functions that considerably simplify the generation of the required PWM switching patterns for control of the electronically commutated motor (ECM) or brushless dc motor (BDCM).