**DATASHEET**

## SX1276/77/78/79 - 137 MHz to 1020 MHz Low Power Long Range Transceiver

## **GENERAL DESCRIPTION**

The SX1276/77/78/79 transceivers feature the LoRa<sup>TM</sup> long range modem that provides ultra-long range spread spectrum communication and high interference immunity whilst minimising current consumption.

Using Semtech's patented LoRa<sup>TM</sup> modulation technique SX1276/77/78/79 can achieve a sensitivity of over -148dBm using a low cost crystal and bill of materials. The high sensitivity combined with the integrated +20 dBm power amplifier yields industry leading link budget making it optimal for any application requiring range or robustness. LoRa<sup>TM</sup> provides significant advantages in both blocking and selectivity over conventional modulation techniques, solving the traditional design compromise between range, interference immunity and energy consumption.

These devices also support high performance (G)FSK modes for systems including WMBus, IEEE802.15.4g. The SX1276/77/78/79 deliver exceptional phase noise, selectivity, receiver linearity and IIP3 for significantly lower current consumption than competing devices.

### ORDERING INFORMATION

| Part Number  | Delivery   | MOQ / Multiple      |

|--------------|------------|---------------------|

| SX1276IMLTRT | T&R        | 3000 pieces         |

| SX1277IMLTRT | T&R        | 3000 pieces         |

| SX1278IMLTRT | T&R        | 3000 pieces         |

| SX1279IMLTRT | T&R        | 3000 pieces         |

| SX1276WS     | Wafer Form | 1 Wafer (2000 dies) |

- QFN 28 Package Operating Range [-40;+85°C]

- Pb-free, Halogen free, RoHS/WEEE compliant product

## **KEY PRODUCT FEATURES**

- ◆ LoRa<sup>TM</sup> Modem

- 168 dB maximum link budget

- +20 dBm 100 mW constant RF output vs. V supply

- +14 dBm high efficiency PA

- Programmable bit rate up to 300 kbps

- High sensitivity: down to -148 dBm

- ◆ Bullet-proof front end: IIP3 = -11 dBm

- Excellent blocking immunity

- Low RX current of 9.9 mA, 200 nA register retention

- Fully integrated synthesizer with a resolution of 61 Hz

- ◆ FSK, GFSK, MSK, GMSK, LoRa<sup>TM</sup>and OOK modulation

- Built-in bit synchronizer for clock recovery

- Preamble detection

- 127 dB Dynamic Range RSSI

- Automatic RF Sense and CAD with ultra-fast AFC

- Packet engine up to 256 bytes with CRC

- Built-in temperature sensor and low battery indicator

## **APPLICATIONS**

- Automated Meter Reading.

- Home and Building Automation.

- Wireless Alarm and Security Systems.

- Industrial Monitoring and Control

- Long range Irrigation Systems

# DATASHEET

| Sect | tion                                                  | Page |

|------|-------------------------------------------------------|------|

| 1. 0 | General Description                                   | 9    |

| 1.1  | ·                                                     |      |

| 1.2  | Product Versions                                      | 10   |

| 1.3  | B. Pin Diagram                                        | 10   |

| 1.4  | -                                                     |      |

| 1.5  | 5. Package Marking                                    | 12   |

| 2. E | Electrical Characteristics                            |      |

| 2.1  | . ESD Notice                                          | 13   |

| 2.2  | 2. Absolute Maximum Ratings                           | 13   |

| 2.3  | 3. Operating Range                                    | 13   |

| 2.4  | . Thermal Properties                                  | 13   |

| 2.5  | 5. Chip Specification                                 | 14   |

|      | 2.5.1. Power Consumption                              | 14   |

|      | 2.5.2. Frequency Synthesis                            | 14   |

|      | 2.5.3. FSK/OOK Mode Receiver                          | 16   |

|      | 2.5.4. FSK/OOK Mode Transmitter                       | 17   |

|      | 2.5.5. Electrical Specification for LoRaTM Modulation | 19   |

|      | 2.5.6. Digital Specification                          | 22   |

| 3. 8 | SX1276/77/78/79 Features                              | 23   |

| 3.1  | . LoRaTM Modem                                        | 24   |

| 3.2  | P. FSK/OOK Modem                                      | 24   |

| 4. S | SX1276/77/78/79 Digital Electronics                   | 25   |

| 4.1  | The LoRaTM Modem                                      | 25   |

|      | 4.1.1. Link Design Using the LoRaTM Modem             | 26   |

|      | 4.1.2. LoRaTM Digital Interface                       | 34   |

|      | 4.1.3. Operation of the LoRaTM Modem                  |      |

|      | 4.1.4. Frequency Settings                             | 37   |

|      | 4.1.5. Frequency Error Indication                     |      |

|      | 4.1.6. LoRaTM Modem State Machine Sequences           |      |

|      | 4.1.7. Modem Status Indicators                        |      |

| 4.2  |                                                       |      |

|      | 4.2.1. Bit Rate Setting                               |      |

|      | 4.2.2. FSK/OOK Transmission                           |      |

|      | 4.2.3. FSK/OOK Reception                              |      |

|      | 4.2.4. Operating Modes in FSK/OOK Mode                |      |

|      | 4.2.5. Startup Times                                  |      |

|      | 4.2.6. Receiver Startup Options                       |      |

|      | 4.2.7. Receiver Restart Methods                       |      |

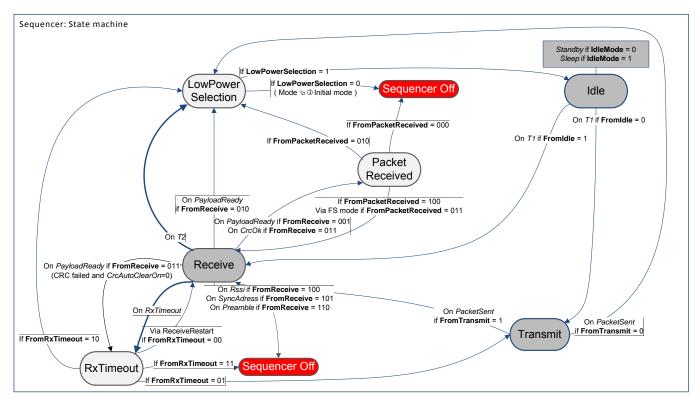

|      | 4.2.8. Top Level Sequencer                            | 61   |

# DATASHEET

| Se | ection                                             | Page |

|----|----------------------------------------------------|------|

|    | 4.2.9. Data Processing in FSK/OOK Mode             | 65   |

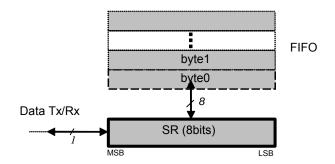

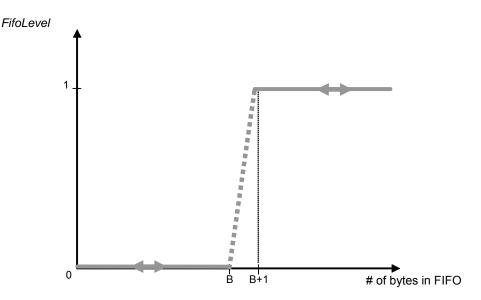

|    | 4.2.10. FIFO                                       | 66   |

|    | 4.2.11. Digital IO Pins Mapping                    | 69   |

|    | 4.2.12. Continuous Mode                            | 70   |

|    | 4.2.13. Packet Mode                                | 71   |

|    | 4.2.14. io-homecontrol® Compatibility Mode         | 79   |

|    | 4.3. SPI Interface                                 | 80   |

| 5. | SX1276/77/78/79 Analog & RF Frontend Electronics   | 81   |

|    | 5.1. Power Supply Strategy                         | 81   |

|    | 5.2. Low Battery Detector                          | 81   |

|    | 5.3. Frequency Synthesis                           | 81   |

|    | 5.3.1. Crystal Oscillator                          | 81   |

|    | 5.3.2. CLKOUT Output                               | 82   |

|    | 5.3.3. PLL                                         | 82   |

|    | 5.3.4. RC Oscillator                               | 82   |

|    | 5.4. Transmitter Description                       | 83   |

|    | 5.4.1. Architecture Description                    | 83   |

|    | 5.4.2. RF Power Amplifiers                         | 83   |

|    | 5.4.3. High Power +20 dBm Operation                | 84   |

|    | 5.4.4. Over Current Protection                     | 85   |

|    | 5.5. Receiver Description                          | 85   |

|    | 5.5.1. Overview                                    | 85   |

|    | 5.5.2. Receiver Enabled and Receiver Active States | 85   |

|    | 5.5.3. Automatic Gain Control In FSK/OOK Mode      | 85   |

|    | 5.5.4. RSSI in FSK/OOK Mode                        | 86   |

|    | 5.5.5. RSSI and SNR in LoRaTM Mode                 | 87   |

|    | 5.5.6. Channel Filter                              | 88   |

|    | 5.5.7. Temperature Measurement                     | 89   |

| 6. | Description of the Registers                       | 90   |

|    | 6.1. Register Table Summary                        | 90   |

|    | 6.2. FSK/OOK Mode Register Map                     | 93   |

|    | 6.3. Band Specific Additional Registers            | 106  |

|    | 6.4. LoRaTM Mode Register Map                      | 108  |

| 7. | Application Information                            | 116  |

|    | 7.1. Crystal Resonator Specification               | 116  |

|    | 7.2. Reset of the Chip                             | 116  |

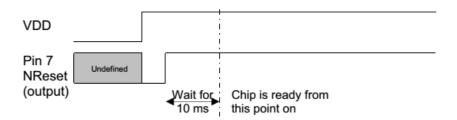

|    | 7.2.1. POR                                         | 116  |

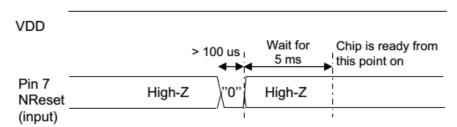

|    | 7.2.2. Manual Reset                                | 117  |

|    | 7.3. Top Sequencer: Listen Mode Examples           | 117  |

# DATASHEET

| S  | ecti | on                                   | Page |

|----|------|--------------------------------------|------|

|    | 7.   | 7.3.1. Wake on Preamble Interrupt    | 117  |

|    | 7.   | '.3.2. Wake on SyncAddress Interrupt | 120  |

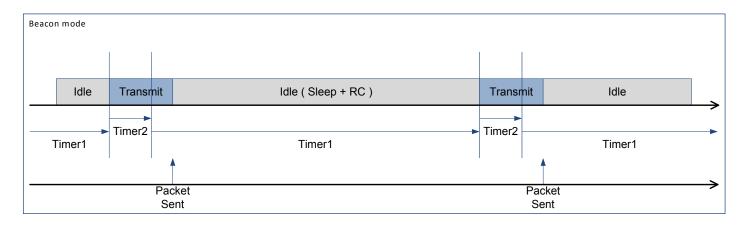

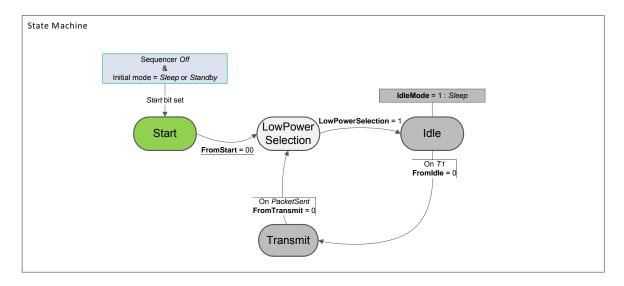

|    | 7.4. | Top Sequencer: Beacon Mode           | 123  |

|    | 7.   | '.4.1. Timing diagram                | 123  |

|    | 7.   | 7.4.2. Sequencer Configuration       | 123  |

|    | 7.5. |                                      |      |

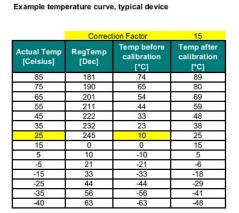

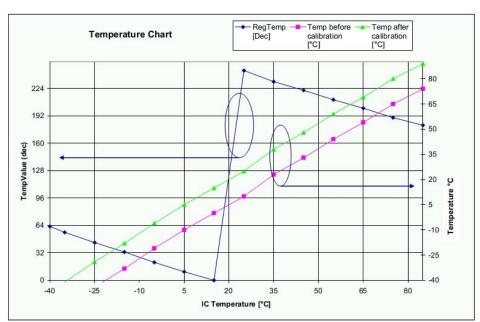

|    | 7.6. | Example Temperature Reading          | 126  |

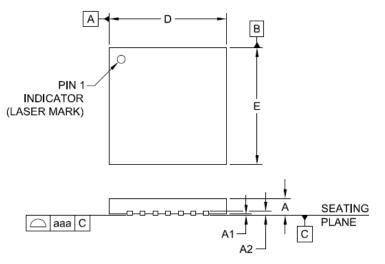

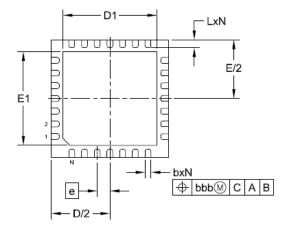

| 8. | Pa   | ackaging Information                 |      |

|    | 8.1. | Package Outline Drawing              | 128  |

|    | 8.2. |                                      |      |

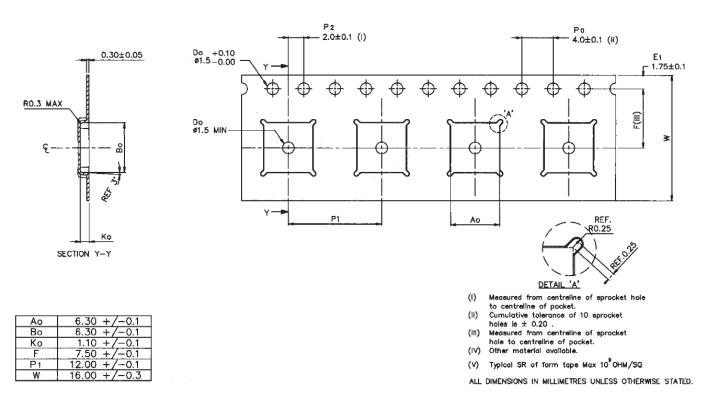

|    | 8.3. | Tape & Reel Information              | 130  |

|    | 8.4. | Wafer Delivery                       | 130  |

| 9. | Re   | evision History                      | 131  |

# DATASHEET

| Section                                                                     | Page |

|-----------------------------------------------------------------------------|------|

| Table 1. SX1276/77/78/79 Device Variants and Key Parameters                 | 10   |

| Table 2. Pin Description                                                    | 11   |

| Table 3. Absolute Maximum Ratings                                           | 13   |

| Table 4. Operating Range                                                    | 13   |

| Table 5. Thermal Properties                                                 | 13   |

| Table 6. Power Consumption Specification                                    | 14   |

| Table 7. Frequency Synthesizer Specification                                | 14   |

| Table 8. FSK/OOK Receiver Specification                                     | 16   |

| Table 9. Transmitter Specification                                          | 17   |

| Table 10. LoRa Receiver Specification                                       | 19   |

| Table 11. Digital Specification                                             | 22   |

| Table 12. Example LoRaTM Modem Performances, 868MHz Band                    | 25   |

| Table 13. Range of Spreading Factors                                        | 27   |

| Table 14. Cyclic Coding Overhead                                            | 27   |

| Table 15. LoRa Bandwidth Options                                            | 28   |

| Table 16. LoRaTM Operating Mode Functionality                               | 36   |

| Table 17. LoRa CAD Consumption Figures                                      | 45   |

| Table 18. DIO Mapping LoRaTM Mode                                           | 46   |

| Table 19. Bit Rate Examples                                                 | 47   |

| Table 20. Preamble Detector Settings                                        | 53   |

| Table 21. RxTrigger Settings to Enable Timeout Interrupts                   | 54   |

| Table 22. Basic Transceiver Modes                                           | 54   |

| Table 23. Receiver Startup Time Summary                                     | 57   |

| Table 24. Receiver Startup Options                                          | 60   |

| Table 25. Sequencer States                                                  |      |

| Table 26. Sequencer Transition Options                                      | 62   |

| Table 27. Sequencer Timer Settings                                          | 63   |

| Table 28. Status of FIFO when Switching Between Different Modes of the Chip |      |

| Table 29. DIO Mapping, Continuous Mode                                      | 69   |

| Table 30. DIO Mapping, Packet Mode                                          | 69   |

| Table 31. CRC Description                                                   |      |

| Table 32. Frequency Bands                                                   |      |

| Table 33. Power Amplifier Mode Selection Truth Table                        | 83   |

| Table 34. High Power Settings                                               |      |

| Table 35. Operating Range, +20dBm Operation                                 |      |

| Table 36. Operating Range, +20dBm Operation                                 |      |

| Table 37. Trimming of the OCP Current                                       |      |

| Table 38. LNA Gain Control and Performances                                 |      |

| Table 39. RssiSmoothing Options                                             | 86   |

# DATASHEET

| Section                                                | Pa                       | age |

|--------------------------------------------------------|--------------------------|-----|

| Table 40. Available RxBw Settings                      |                          | 88  |

| Table 41. Registers Summary                            |                          | 90  |

| Table 42. Register Map                                 |                          | 93  |

| Table 43. Low Frequency Additional Registers           | 10                       | 06  |

|                                                        | 10                       |     |

| Table 45. Crystal Specification                        | 11                       | 16  |

| Table 46. Listen Mode with PreambleDetect Condition Se | ettings11                | 19  |

| Table 47. Listen Mode with PreambleDetect Condition R  | ecommended DIO Mapping1  | 19  |

| Table 48. Listen Mode with SyncAddress Condition Setti | ngs12                    | 22  |

| Table 49. Listen Mode with PreambleDetect Condition R  | ecommended DIO Mapping12 | 22  |

|                                                        | 12                       |     |

| Table 51. Revision History                             | 13                       | 31  |

|                                                        |                          |     |

# DATASHEET

| Sectio     | n                                                                              | Page |

|------------|--------------------------------------------------------------------------------|------|

| Figure 1.  | Block Diagram                                                                  | 9    |

| Figure 2.  | Pin Diagrams                                                                   | 10   |

| Figure 3.  | Marking Diagram                                                                | 12   |

| Figure 4.  | SX1276/77/78/79 Block Schematic Diagram                                        | 23   |

| Figure 5.  | LoRaTM Modem Connectivity                                                      | 26   |

| Figure 6.  | LoRaTM Packet Structure                                                        | 29   |

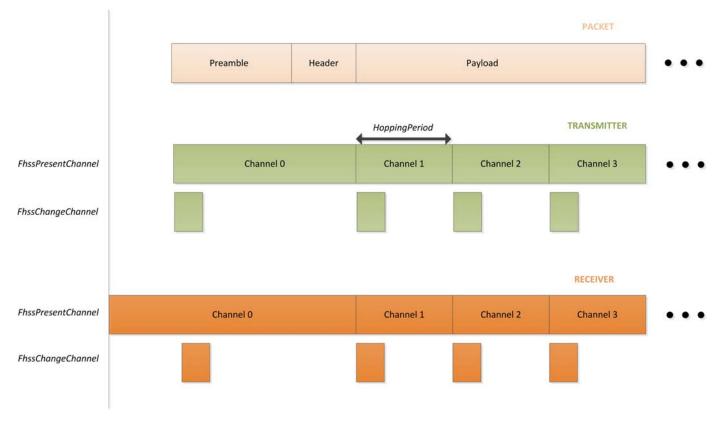

| Figure 7.  | Interrupts Generated in the Case of Successful Frequency Hopping Communication | 33   |

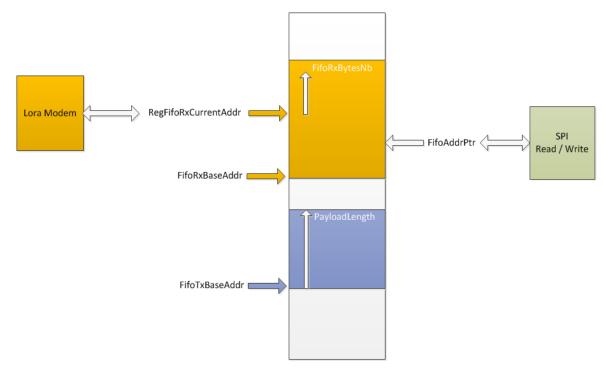

| Figure 8.  | LoRaTM Data Buffer                                                             | 34   |

| Figure 9.  | LoRaTM Modulation Transmission Sequence.                                       | 38   |

| Figure 10. | LoRaTM Receive Sequence.                                                       | 39   |

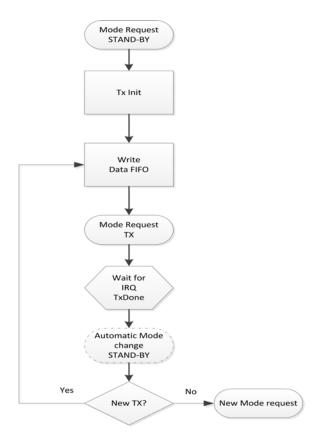

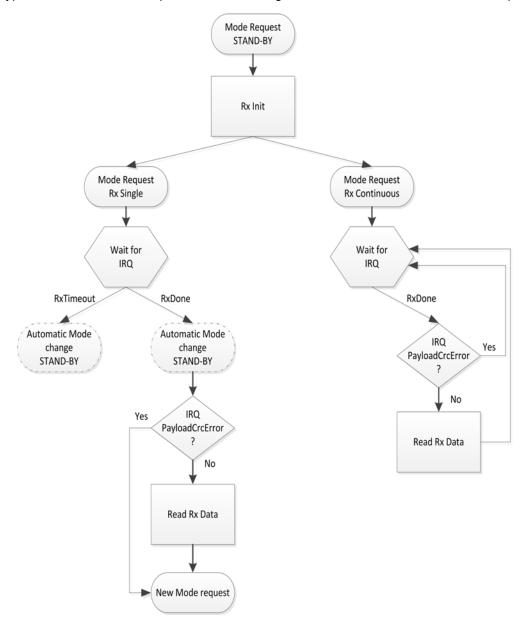

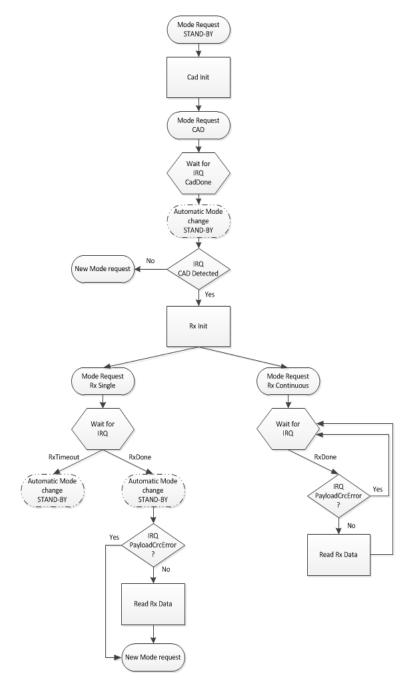

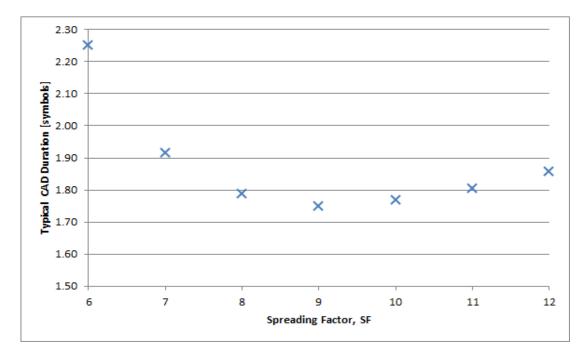

| Figure 11. | LoRaTM CAD Flow                                                                | 43   |

| Figure 12. | CAD Time as a Function of Spreading Factor                                     | 44   |

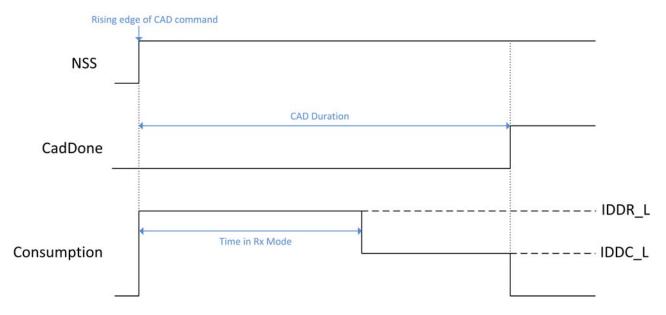

| Figure 13. | Consumption Profile of the LoRa CAD Process                                    | 45   |

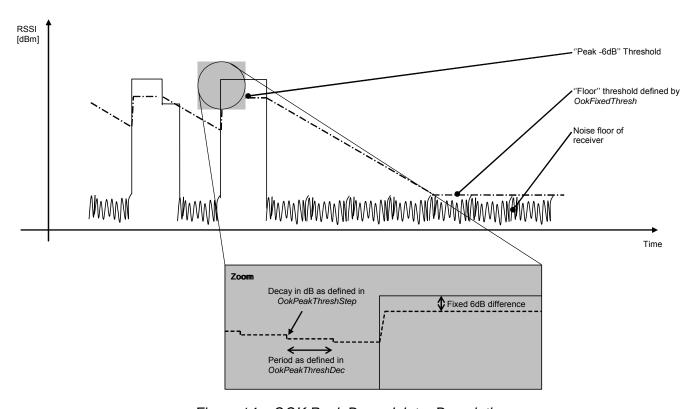

| Figure 14. | OOK Peak Demodulator Description                                               | 49   |

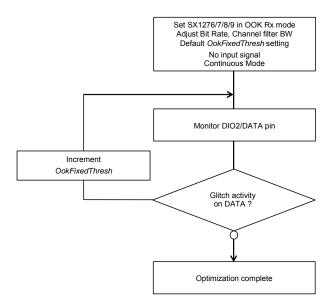

| Figure 15. | Floor Threshold Optimization                                                   | 50   |

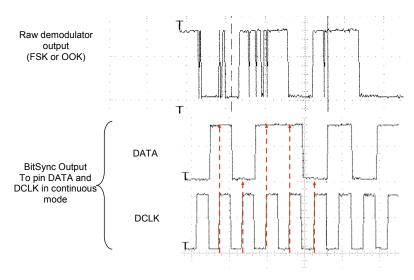

| Figure 16. | Bit Synchronizer Description                                                   | 51   |

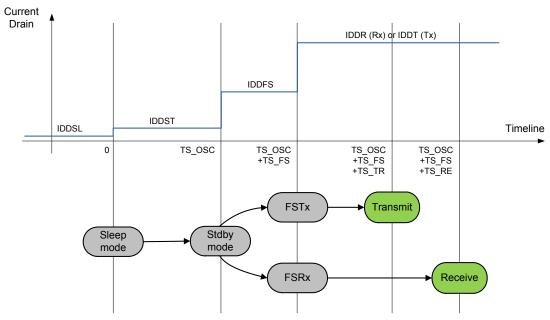

| Figure 17. | Startup Process                                                                | 56   |

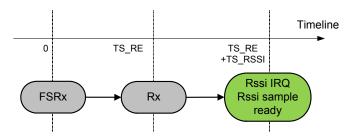

| Figure 18. | Time to RSSI Sample                                                            | 57   |

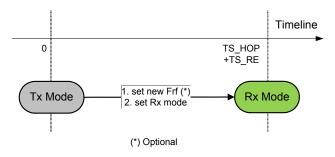

| Figure 19. | Tx to Rx Turnaround                                                            | 58   |

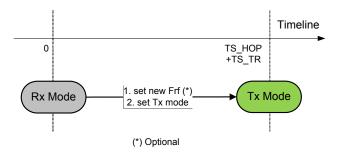

| Figure 20. | Rx to Tx Turnaround                                                            | 58   |

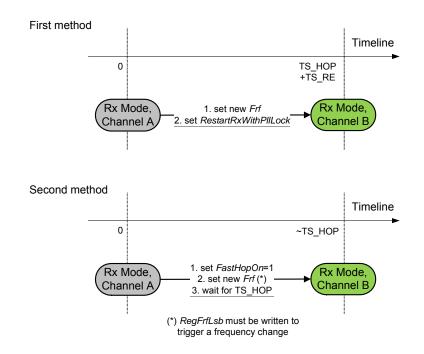

| Figure 21. | Receiver Hopping                                                               | 59   |

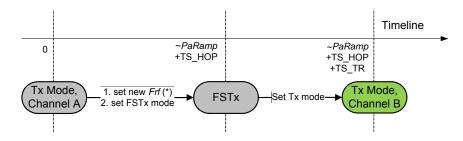

| Figure 22. | Transmitter Hopping                                                            | 59   |

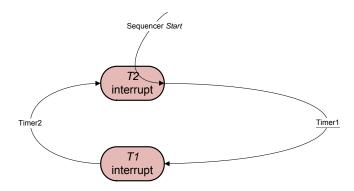

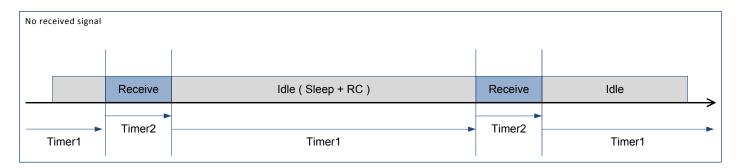

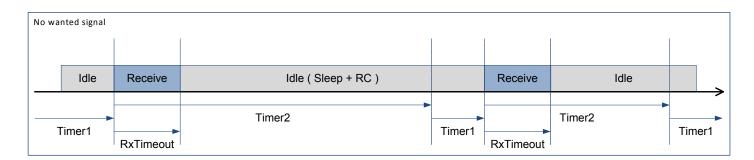

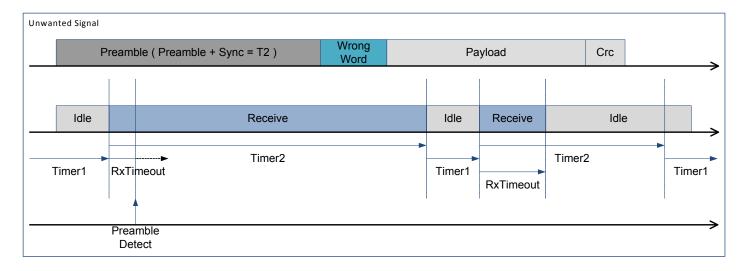

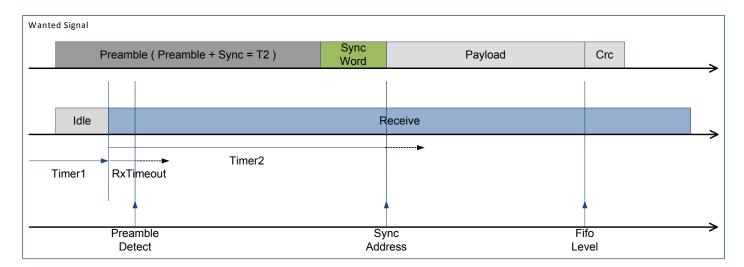

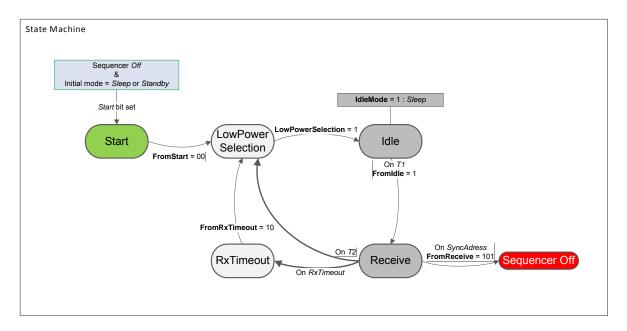

| Figure 23. | Timer1 and Timer2 Mechanism                                                    | 63   |

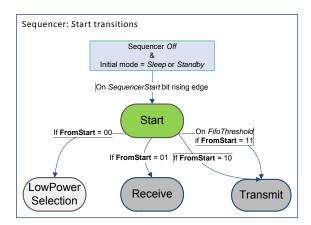

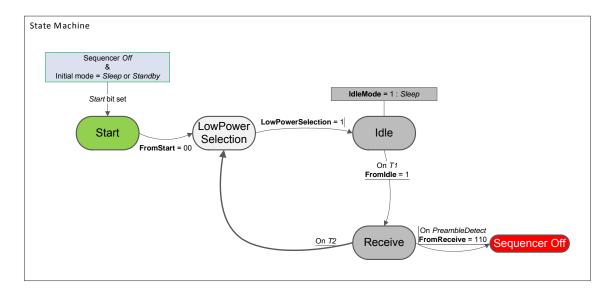

| Figure 24. | Sequencer State Machine                                                        | 64   |

| Figure 25. | SX1276/77/78/79 Data Processing Conceptual View                                | 65   |

| Figure 26. | FIFO and Shift Register (SR)                                                   | 66   |

| Figure 27. | FifoLevel IRQ Source Behavior                                                  | 67   |

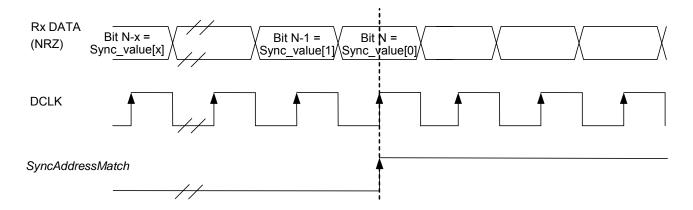

| Figure 28. | Sync Word Recognition                                                          | 68   |

| Figure 29. | Continuous Mode Conceptual View                                                | 70   |

| Figure 30. | Tx Processing in Continuous Mode                                               | 70   |

| Figure 31. | Rx Processing in Continuous Mode                                               | 71   |

| Figure 32. | Packet Mode Conceptual View                                                    | 72   |

| Figure 33. | Fixed Length Packet Format                                                     | 73   |

| Figure 34. | Variable Length Packet Format                                                  | 74   |

| Figure 35. | Unlimited Length Packet Format                                                 | 74   |

| Figure 36. | Manchester Encoding/Decoding                                                   | 78   |

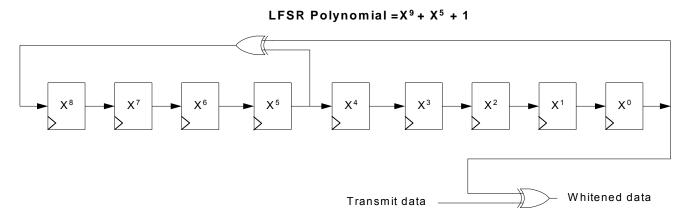

| Figure 37. | Data Whitening Polynomial                                                      | 79   |

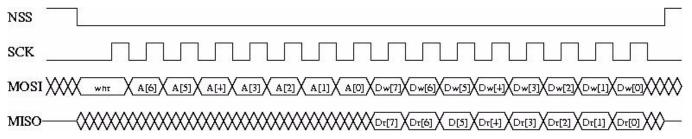

|            | SPI Timing Diagram (single access)                                             |      |

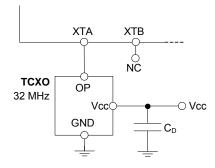

| Figure 39. | TCXO Connection                                                                | 81   |

|            |                                                                                |      |

# DATASHEET

| Section    |                                                               | Page |

|------------|---------------------------------------------------------------|------|

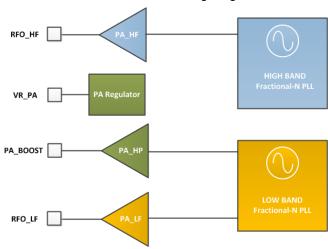

| Figure 40. | RF Front-end Architecture Shows the Internal PA Configuration | 83   |

| Figure 41. | Temperature Sensor Response                                   | 89   |

| Figure 42. | POR Timing Diagram                                            | 116  |

| Figure 43. | Manual Reset Timing Diagram                                   | 117  |

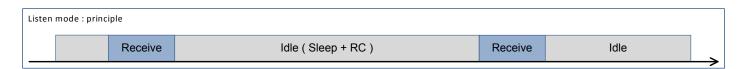

| Figure 44. | Listen Mode: Principle                                        | 117  |

| Figure 45. | Listen Mode with No Preamble Received                         | 118  |

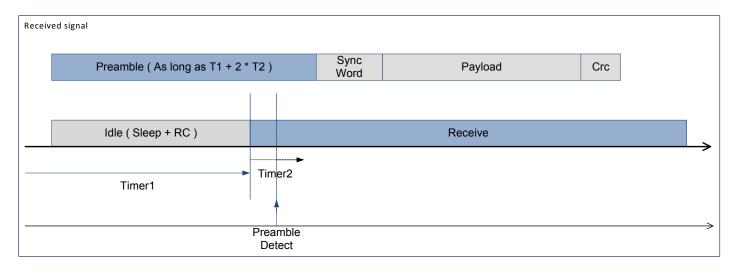

| Figure 46. | Listen Mode with Preamble Received                            | 118  |

| Figure 47. | Wake On PreambleDetect State Machine                          | 119  |

| Figure 48. | Listen Mode with no SyncAddress Detected                      | 120  |

| Figure 49. | Listen Mode with Preamble Received and no SyncAddress         | 120  |

| Figure 50. | Listen Mode with Preamble Received & Valid SyncAddress        | 121  |

| Figure 51. | Wake On SyncAddress State Machine                             | 121  |

| Figure 52. | Beacon Mode Timing Diagram                                    | 123  |

| Figure 53. | Beacon Mode State Machine                                     | 123  |

| Figure 54. | Example CRC Code                                              | 125  |

| Figure 55. | Example Temperature Reading                                   | 126  |

| Figure 56. | Example Temperature Reading (continued)                       | 127  |

| Figure 57. | Package Outline Drawing                                       | 128  |

| Figure 58. | Recommended Land Pattern                                      | 129  |

| Figure 59. | Tape and Reel Information                                     | 130  |

|            |                                                               |      |

**DATASHEET**

## 1. General Description

The SX1276/77/78/79 incorporates the LoRa<sup>TM</sup> spread spectrum modem which is capable of achieving significantly longer range than existing systems based on FSK or OOK modulation. At maximum data rates of LoRa<sup>TM</sup> the sensitivity is 8dB better than FSK, but using a low cost bill of materials with a 20ppm XTAL LoRa<sup>TM</sup> can improve receiver sensitivity by more than 20dB compared to FSK. LoRa<sup>TM</sup> also provides significant advances in selectivity and blocking performance, further improving communication reliability. For maximum flexibility the user may decide on the spread spectrum modulation bandwidth (BW), spreading factor (SF) and error correction rate (CR). Another benefit of the spread modulation is that each spreading factor is orthogonal - thus multiple transmitted signals can occupy the same channel without interfering. This also permits simple coexistence with existing FSK based systems. Standard GFSK, FSK, OOK, and GMSK modulation is also provided to allow compatibility with existing systems or standards such as wireless MBUS and IEEE 802.15.4g.

The SX1276 and SX1279 offer bandwidth options ranging from 7.8 kHz to 500 kHz with spreading factors ranging from 6 to 12, and covering all available frequency bands. The SX1277 offers the same bandwidth and frequency band options with spreading factors from 6 to 9. The SX1278 offers bandwidths and spreading factor options, but only covers the lower UHF bands.

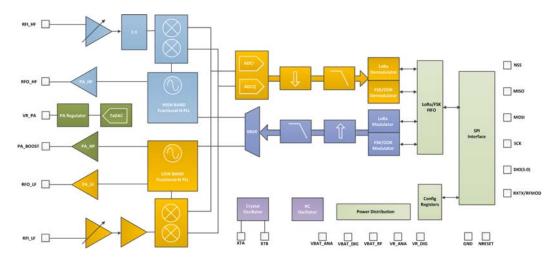

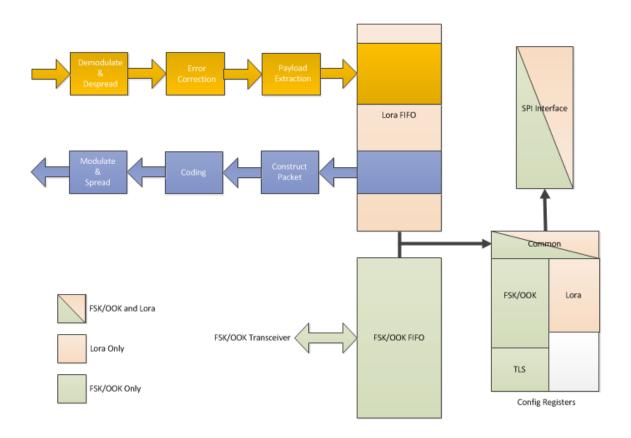

### 1.1. Simplified Block Diagram

Figure 1. Block Diagram

**DATASHEET**

### 1.2. Product Versions

The features of the four product variants are detailed in the following table.

Table 1 SX1276/77/78/79 Device Variants and Key Parameters

| Part Number | Frequency Range | Spreading Factor | Bandwidth     | Effective Bitrate | Est. Sensitivity |

|-------------|-----------------|------------------|---------------|-------------------|------------------|

| SX1276      | 137 - 1020 MHz  | 6 - 12           | 7.8 - 500 kHz | .018 - 37.5 kbps  | -111 to -148 dBm |

| SX1277      | 137 - 1020 MHz  | 6 - 9            | 7.8 - 500 kHz | 0.11 - 37.5 kbps  | -111 to -139 dBm |

| SX1278      | 137 - 525 MHz   | 6- 12            | 7.8 - 500 kHz | .018 - 37.5 kbps  | -111 to -148 dBm |

| SX1279      | 137 - 960MHz    | 6- 12            | 7.8 - 500 kHz | .018 - 37.5 kbps  | -111 to -148 dBm |

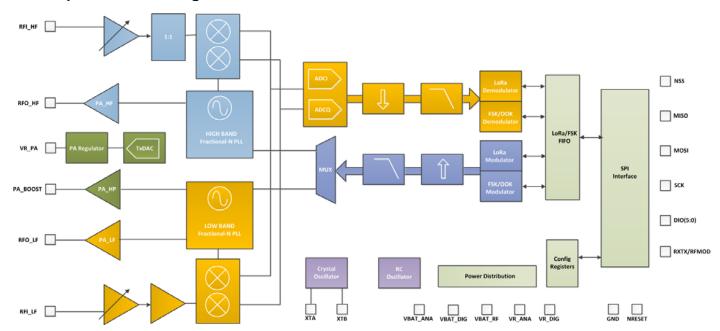

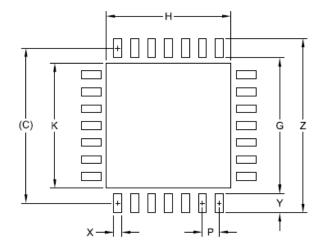

## 1.3. Pin Diagram

The following diagram shows the pin arrangement of the QFN package, top view.

Figure 2. Pin Diagrams

DATASHEET

# 1.4. Pin Description

Table 2 Pin Description

| Number | Name              | Туре              | Description                                        |

|--------|-------------------|-------------------|----------------------------------------------------|

|        | SX1276/77/79/(78) | SX1276/77/79/(78) | SX1276/77/79/(78)                                  |

| 0      | GROUND            | -                 | Exposed ground pad                                 |

| 1      | RFI_LF            | I                 | RF input for bands 2&3                             |

| 2      | VR_ANA            | -                 | Regulated supply voltage for analogue circuitry    |

| 3      | VBAT_ANA          | -                 | Supply voltage for analogue circuitry              |

| 4      | VR_DIG            | -                 | Regulated supply voltage for digital blocks        |

| 5      | XTA               | I/O               | XTAL connection or TCXO input                      |

| 6      | XTB               | I/O               | XTAL connection                                    |

| 7      | NRESET            | I/O               | Reset trigger input                                |

| 8      | DIO0              | I/O               | Digital I/O, software configured                   |

| 9      | DIO1/DCLK         | I/O               | Digital I/O, software configured                   |

| 10     | DIO2/DATA         | I/O               | Digital I/O, software configured                   |

| 11     | DIO3              | I/O               | Digital I/O, software configured                   |

| 12     | DIO4              | I/O               | Digital I/O, software configured                   |

| 13     | DIO5              | I/O               | Digital I/O, software configured                   |

| 14     | VBAT_DIG          | -                 | Supply voltage for digital blocks                  |

| 15     | GND               | -                 | Ground                                             |

| 16     | SCK               | I                 | SPI Clock input                                    |

| 17     | MISO              | 0                 | SPI Data output                                    |

| 18     | MOSI              | I                 | SPI Data input                                     |

| 19     | NSS               | I                 | SPI Chip select input                              |

| 20     | RXTX/RF_MOD       | 0                 | Rx/Tx switch control: high in Tx                   |

| 21     | RFI_HF (GND)      | I (-)             | RF input for band 1 (Ground)                       |

| 22     | RFO_HF (GND)      | O (-)             | RF output for band 1 (Ground)                      |

| 23     | GND               | -                 | Ground                                             |

| 24     | VBAT_RF           | -                 | Supply voltage for RF blocks                       |

| 25     | VR_PA             | -                 | Regulated supply for the PA                        |

| 26     | GND               | -                 | Ground                                             |

| 27     | PA_BOOST          | 0                 | Optional high-power PA output, all frequency bands |

| 28     | RFO_LF            | 0                 | RF output for bands 2&3                            |

## **DATASHEET**

## 1.5. Package Marking

SX1276 yyww XXXXXX XXXXXX 0 SX1277 yyww XXXXXXX XXXXXXX

0 SX1278 yyww **XXXXXXX** XXXXXXX

SX1279 yyww XXXXXX XXXXXXX

| TOP MARK  |   |  |  |

|-----------|---|--|--|

| CHAR ROWS |   |  |  |

| דודודודוד | 5 |  |  |

Marking for the 6 x 6 mm MLPQ 28ld Lead package:

nnnnnn = Part Number (Example: SX1276) yyww = Date Code (Example: 1352) xxxxxxx = Semtech Lot No. (Example: EA90101) 0101-10) XXXXXXX

Figure 3. Marking Diagram

**DATASHEET**

### 2. Electrical Characteristics

### 2.1. ESD Notice

The SX1276/77/78/79 is a high performance radio frequency device. It satisfies:

- Class 2 of the JEDEC standard JESD22-A114 (Human Body Model) on all pins.

- Class III of the JEDEC standard JESD22-C101 (Charged Device Model) on all pins

## 2.2. Absolute Maximum Ratings

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Table 3 Absolute Maximum Ratings

| Symbol | Description          | Min  | Max  | Unit |

|--------|----------------------|------|------|------|

| VDDmr  | Supply Voltage       | -0.5 | 3.9  | V    |

| Tmr    | Temperature          | -55  | +115 | ° C  |

| Tj     | Junction temperature | -    | +125 | ° C  |

| Pmr    | RF Input Level       | -    | +10  | dBm  |

Note Specific ratings apply to +20 dBm operation (see Section 5.4.3).

### 2.3. Operating Range

Table 4 Operating Range

| Symbol | Description                       | Min | Max | Unit |

|--------|-----------------------------------|-----|-----|------|

| VDDop  | Supply voltage                    | 1.8 | 3.7 | V    |

| Тор    | Operational temperature range     | -40 | +85 | °C   |

| Clop   | Load capacitance on digital ports | -   | 25  | pF   |

| ML     | RF Input Level                    | -   | +10 | dBm  |

Note A specific supply voltage range applies to +20 dBm operation (see Section 5.4.3).

### 2.4. Thermal Properties

Table 5 Thermal Properties

| Symbol   | Description                                                        | Min | Тур    | Max | Unit |

|----------|--------------------------------------------------------------------|-----|--------|-----|------|

| THETA_JA | Package $	heta_{ja}$ (Junction to ambient)                         | -   | 22.185 | -   | °C/W |

| THETA_JC | Package $	heta_{j_{\mathcal{C}}}$ (Junction to case ground paddle) | -   | 0.757  | -   | °C/W |

**DATASHEET**

## 2.5. Chip Specification

The tables below give the electrical specifications of the transceiver under the following conditions: Supply voltage VDD=3.3 V, temperature = 25 °C, FXOSC = 32 MHz,  $F_{RF}$  = 169/434/868/915 MHz (see specific indication), Pout = +13dBm, 2-level FSK modulation without pre-filtering, FDA = 5 kHz, Bit Rate = 4.8 kb/s and terminated in a matched 50 Ohm impedance, shared Rx and Tx path matching, unless otherwise specified.

Note Specification whose symbol is appended with "\_LF" corresponds to the performance in Band 2 and/or Band 3, as described in section 5.3.3. "\_HF" refers to the upper Band 1

### 2.5.1. Power Consumption

Table 6 Power Consumption Specification

| Symbol  | Description                                             | Conditions                                                                                                                         | Min         | Тур                   | Max              | Unit           |

|---------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|------------------|----------------|

| IDDSL   | Supply current in Sleep mode                            |                                                                                                                                    | -           | 0.2                   | 1                | uA             |

| IDDIDLE | Supply current in Idle mode                             | RC oscillator enabled                                                                                                              | -           | 1.5                   | -                | uA             |

| IDDST   | Supply current in Standby mode                          | Crystal oscillator enabled                                                                                                         | -           | 1.6                   | 1.8              | mA             |

| IDDFS   | Supply current in Synthesizer mode                      | FSRx                                                                                                                               | -           | 5.8                   | -                | mA             |

| IDDR    | Supply current in Receive mode                          | LnaBoost Off, band 1<br>LnaBoost On, band 1<br>Bands 2&3                                                                           |             | 10.8<br>11.5<br>12.0  |                  | mA             |

| IDDT    | Supply current in Transmit mode with impedance matching | RFOP = +20 dBm, on PA_BOOST<br>RFOP = +17 dBm, on PA_BOOST<br>RFOP = +13 dBm, on RFO_LF/HF pin<br>RFOP = + 7 dBm, on RFO_LF/HF pin | -<br>-<br>- | 120<br>87<br>29<br>20 | -<br>-<br>-<br>- | mA<br>mA<br>mA |

### 2.5.2. Frequency Synthesis

Table 7 Frequency Synthesizer Specification

| Symbol | Description                                          | Conditions                    |                            | Min                      | Тур         | Max                                     | Unit |

|--------|------------------------------------------------------|-------------------------------|----------------------------|--------------------------|-------------|-----------------------------------------|------|

| FR     | Synthesizer frequency range                          | Programmable<br>(*for SX1279) | Band 3<br>Band 2<br>Band 1 | 137<br>410<br>862 (*779) | -<br>-<br>- | 175 (*160)<br>525 (*480)<br>1020 (*960) | MHz  |

| FXOSC  | Crystal oscillator frequency                         |                               |                            | -                        | 32          | -                                       | MHz  |

| TS_OSC | Crystal oscillator wake-up time                      |                               |                            | -                        | 250         | -                                       | us   |

| TS_FS  | Frequency synthesizer wake-up time to PllLock signal | From Standby mode             |                            | -                        | 60          | -                                       | us   |

# DATASHEET

| TS_HOP | Frequency synthesizer hop time at most 10 kHz away from the target frequency | 200 kHz step<br>1 MHz step<br>5 MHz step<br>7 MHz step<br>12 MHz step<br>20 MHz step | -<br>-<br>-<br>-<br>- | 20<br>20<br>50<br>50<br>50<br>50<br>50 | -<br>-<br>-<br>-<br>- | us<br>us<br>us<br>us<br>us |

|--------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|----------------------------------------|-----------------------|----------------------------|

|        |                                                                              | 25 MHz step                                                                          | -                     | 50                                     | -                     | us                         |

| FSTEP  | Frequency synthesizer step                                                   | FSTEP = FXOSC/2 <sup>19</sup>                                                        | -                     | 61.0                                   | -                     | Hz                         |

| FRC    | RC Oscillator frequency                                                      | After calibration                                                                    | -                     | 62.5                                   | -                     | kHz                        |

| BRF    | Bit rate, FSK                                                                | Programmable values (1)                                                              | 1.2                   | -                                      | 300                   | kbps                       |

| BRA    | Bit rate Accuracy, FSK                                                       | ABS(wanted BR - available BR)                                                        | -                     | -                                      | 250                   | ppm                        |

| BRO    | Bit rate, OOK                                                                | Programmable                                                                         | 1.2                   | -                                      | 32.768                | kbps                       |

| BR_L   | Bit rate, LoRa Mode                                                          | From SF6, BW=500kHz to<br>SF12, BW=7.8kHz                                            | 0.018                 | -                                      | 37.5                  | kbps                       |

| FDA    | Frequency deviation, FSK (1)                                                 | Programmable<br>FDA + BRF/2 =< 250 kHz                                               | 0.6                   | -                                      | 200                   | kHz                        |

Note: For Maximum Bit rate, the maximum modulation index is 0.5.

**DATASHEET**

### 2.5.3. FSK/OOK Mode Receiver

All receiver tests are performed with RxBw = 10 kHz (Single Side Bandwidth) as programmed in *RegRxBw*, receiving a PN15 sequence. Sensitivities are reported for a 0.1% BER (with Bit Synchronizer enabled), unless otherwise specified. Blocking tests are performed with an unmodulated interferer. The wanted signal power for the Blocking Immunity, ACR, IIP2, IIP3 and AMR tests is set 3 dB above the receiver sensitivity level.

Table 8 FSK/OOK Receiver Specification

| Symbol   | Description                                                                                                 | Conditions                                                                                                                                                      | Min              | Тур                                 | Max              | Unit                            |

|----------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|------------------|---------------------------------|

| RFS_F_LF | Direct tie of RFI and RFO pins,<br>shared Rx, Tx paths FSK sensitiv-<br>ity, highest LNA gain.<br>Bands 2&3 | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s*<br>FDA = 20 kHz, BR = 38.4 kb/s**<br>FDA = 62.5 kHz, BR = 250 kb/s*** | -<br>-<br>-<br>- | -121<br>-117<br>-107<br>-108<br>-95 | -<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm |

|          | Split RF paths, the RF switch insertion loss is not accounted for. Bands 2&3                                | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s*<br>FDA = 20 kHz, BR = 38.4 kb/s**<br>FDA = 62.5 kHz, BR = 250 kb/s*** | -<br>-<br>-<br>- | -123<br>-119<br>-109<br>-110<br>-97 | -<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm |

|          | Direct tie of RFI and RFO pins,<br>shared Rx, Tx paths FSK sensitiv-<br>ity, highest LNA gain.<br>Band 1    | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s*<br>FDA = 20 kHz, BR = 38.4 kb/s**<br>FDA = 62.5 kHz, BR = 250 kb/s*** | -<br>-<br>-<br>- | -119<br>-115<br>-105<br>-105<br>-92 |                  | dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_F_HF | Split RF paths, <i>LnaBoost</i> is turned on, the RF switch insertion loss is not accounted for.  Band 1    | FDA = 5 kHz, BR = 1.2 kb/s<br>FDA = 5 kHz, BR = 4.8 kb/s<br>FDA = 40 kHz, BR = 38.4 kb/s*<br>FDA = 20 kHz, BR = 38.4 kb/s**<br>FDA = 62.5 kHz, BR = 250 kb/s*** | -<br>-<br>-<br>- | -123<br>-119<br>-109<br>-109<br>-96 | -<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_O    | OOK sensitivity, highest LNA gain shared Rx, Tx paths                                                       | BR = 4.8 kb/s<br>BR = 32 kb/s                                                                                                                                   | -                | -117<br>-108                        | -                | dBm<br>dBm                      |

| CCR      | Co-Channel Rejection, FSK                                                                                   |                                                                                                                                                                 | -                | -9                                  | -                | dB                              |

| ACR      | Adjacent Channel Rejection                                                                                  | FDA = 5 kHz, BR=4.8kb/s<br>Offset = +/- 25 kHz or +/- 50kHz<br>Band 1<br>Band 2<br>Band 3                                                                       | -<br>-<br>-      | 50<br>56<br>60                      | -<br>-<br>-      | dB<br>dB<br>dB                  |

| BI_HF    | Blocking Immunity, Band 1                                                                                   | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                                                                                                 | -<br>-<br>-      | 71<br>76<br>84                      | -<br>-<br>-      | dB<br>dB<br>dB                  |

| BI_LF    | Blocking Immunity, Bands 2&3                                                                                | Offset = +/- 1 MHz<br>Offset = +/- 2 MHz<br>Offset = +/- 10 MHz                                                                                                 | -<br>-<br>-      | 71<br>72<br>78                      | -<br>-<br>-      | dB<br>dB<br>dB                  |

# **DATASHEET**

| IIP2    | 2nd order Input Intercept Point<br>Unwanted tones are 20 MHz<br>above the LO             | Highest LNA gain                                                    | -      | +55        | -   | dBm        |

|---------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------|------------|-----|------------|

| IIP3_HF | 3rd order Input Intercept point<br>Unwanted tones are 1MHz and<br>1.995 MHz above the LO | Band 1<br>Highest LNA gain G1<br>LNA gain G2, 5dB sensitivity hit   |        | -11<br>-6  | -   | dBm<br>dBm |

| UDO 1.5 | 3rd order Input Intercept point Unwanted tones are 1MHz and 1.995 MHz above the LO       | Band 2<br>Highest LNA gain G1<br>LNA gain G2, 2.5dB sensitivity hit | -<br>- | -22<br>-15 |     | dBm<br>dBm |

| IIP3_LF |                                                                                          | Band 3<br>Highest LNA gain G1<br>LNA gain G2, 2.5dB sensitivity hit | -      | -15<br>-11 | -   | dBm<br>dBm |

| BW_SSB  | Single Side channel filter BW                                                            | Programmable                                                        | 2.7    | -          | 250 | kHz        |

| IMR     | Image Rejection                                                                          | Wanted signal 3dB over sensitivity BER=0.1%                         | -      | 50         | -   | dB         |

| IMA     | Image Attenuation                                                                        |                                                                     | -      | 57         | -   | dB         |

| DR_RSSI | RSSI Dynamic Range                                                                       | AGC enabled Min Max                                                 | -      | -127<br>0  | -   | dBm<br>dBm |

<sup>\*</sup> RxBw = 83 kHz (Single Side Bandwidth)

### 2.5.4. FSK/OOK Mode Transmitter

Table 9 Transmitter Specification

| Symbol         | Description                                                         | Conditions                                   | Min    | Тур       | Max | Unit       |

|----------------|---------------------------------------------------------------------|----------------------------------------------|--------|-----------|-----|------------|

| RF_OP          | RF output power in 50 ohms on RFO pin (High efficiency PA).         | Programmable with steps  Max  Min            | -<br>- | +14<br>-1 |     | dBm<br>dBm |

| ΔRF_<br>OP_V   | RF output power stability on RFO pin versus voltage supply.         | VDD = 2.5 V to 3.3 V<br>VDD = 1.8 V to 3.7 V | -      | 3<br>8    | -   | dB<br>dB   |

| RF_OPH         | RF output power in 50 ohms, on PA_BOOST pin (Regulated PA).         | Programmable with 1dB steps Max Min          | -      | +17<br>+2 | -   | dBm<br>dBm |

| RF_OPH_<br>MAX | Max RF output power, on PA_BOOST pin                                | High power mode                              | -      | +20       | -   | dBm        |

| ∆RF_<br>OPH_V  | RF output power stability on PA<br>BOOST pin versus voltage supply. | VDD = 2.4 V to 3.7 V                         | -      | +/-1      | -   | dB         |

| ΔRF_T          | RF output power stability versus temperature on PA_BOOST pin.       | From T = -40 °C to +85 °C                    | -      | +/-1      | -   | dB         |

<sup>\*\*</sup> RxBw = 50 kHz (Single Side Bandwidth)

<sup>\*\*\*</sup> RxBw = 250 kHz (Single Side Bandwidth)

# DATASHEET

| PHN Transmitter Pha |                                                                | 169 MHz, Band 3 10kHz Offset 50kHz Offset 400kHz Offset 1MHz Offset      | -<br>-<br>- | -118<br>-118<br>-128<br>-134 | -<br>-<br>- | dBc/<br>Hz |

|---------------------|----------------------------------------------------------------|--------------------------------------------------------------------------|-------------|------------------------------|-------------|------------|

|                     | Transmitter Phase Noise                                        | 433 MHz, Band 2  10kHz Offset 50kHz Offset 400kHz Offset 1MHz Offset     | -<br>-<br>- | -110<br>-110<br>-122<br>-129 | -<br>-<br>- | dBc/<br>Hz |

|                     |                                                                | 868/915 MHz, Band 1  10kHz Offset 50kHz Offset 400kHz Offset 1MHz Offset | -<br>-<br>- | -103<br>-103<br>-115<br>-122 | -<br>-<br>- | dBc/<br>Hz |

| ACP                 | Transmitter adjacent channel power (measured at 25 kHz offset) | BT=1. Measurement conditions as defined by EN 300 220-1 V2.3.1           | -           | -                            | -37         | dBm        |

| TS_TR               | Transmitter wake up time, to the first rising edge of DCLK     | Frequency Synthesizer enabled, <i>PaR-amp</i> = 10us, BR = 4.8 kb/s      | -           | 120                          | -           | us         |

**DATASHEET**

# 2.5.5. Electrical Specification for LoRa<sup>TM</sup> Modulation

The table below gives the electrical specifications for the transceiver operating with LoRa<sup>TM</sup> modulation. Following conditions apply unless otherwise specified:

- Supply voltage = 3.3 V

- Temperature = 25° C

- ◆ f<sub>XOSC</sub> = 32 MHz

- ◆ bandwidth (BW) = 125 kHz

- Spreading Factor (SF) = 12

- ◆ Error Correction Code (EC) = 4/6

- ◆ Packet Error Rate (PER)= 1%

- CRC on payload enabled

- Output power = 13 dBm in transmission

- Payload length = 64 bytes

- ◆ Preamble Length = 12 symbols (programmed register *PreambleLength=8*)

- With matched impedances

Table 10 LoRa Receiver Specification

| Symbol    | Description                                                                              | Conditions                                                                                                     | Min.             | Тур                          | Max              | Unit                 |

|-----------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------|------------------------------|------------------|----------------------|

| IDDR_L    | Supply current in receiver LoRa <sup>TM</sup>                                            | Bands 2&3, BW=7.8 to 62.5 kHz<br>Bands 2&3, BW = 125 kHz<br>Bands 2&3, BW = 250 kHz<br>Bands 2&3, BW = 500 kHz | -<br>-<br>-      | 11.0<br>11.5<br>12.4<br>13.8 | -<br>-<br>-      | mA<br>mA<br>mA<br>mA |

|           | mode, <i>LnaBoost</i> off                                                                | Band 1, BW=7.8 to 62.5 kHz<br>Band 1, BW = 125 kHz<br>Band 1, BW = 250 kHz<br>Band 1, BW = 500 kHz             | -<br>-<br>-<br>- | 9.9<br>10.3<br>11.1<br>12.6  | -<br>-<br>-<br>- | mA<br>mA<br>mA<br>mA |

| IDDT_L    | Supply current in transmitter mode                                                       | RFOP = 13 dBm<br>RFOP = 7 dBm                                                                                  | -                | 28<br>20                     | -                | mA<br>mA             |

| IDDT_H_L  | Supply current in transmitter mode with an external impedance transformation             | Using PA_BOOST pin<br>RFOP = 17 dBm                                                                            | -                | 90                           | -                | mA                   |

| BI_L      | Blocking immunity,<br>CW interferer                                                      | offset = +/- 1 MHz<br>offset = +/- 2 MHz<br>offset = +/- 10 MHz                                                | -                | 89<br>94<br>100              | -                | dB<br>dB<br>dB       |

| IIP2_L    | 2nd order Input Intercept Point<br>Unwanted tones are 20 MHz above<br>the LO             | Highest LNA gain                                                                                               | -                | +55                          | -                | dBm                  |

| IIP3_L_HF | 3rd order Input Intercept point<br>Unwanted tones are 1MHz and 1.995<br>MHz above the LO | Band 1<br>Highest LNA gain G1<br>LNA gain G2, 5dB sensitivity hit                                              | -                | -11<br>-6                    | -                | dBm<br>dBm           |

# DATASHEET

| Symbol      | Description                                                                                                              | Conditions                                                            | Min.                  | Тур                                                  | Max                   | Unit                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|------------------------------------------------------|-----------------------|-----------------------------------------------|

| IIP3_L_LF   | 3rd order Input Intercept point<br>Unwanted tones are 1MHz and 1.995<br>MHz above the LO                                 | Band 2<br>Highest LNA gain G1<br>LNA gain G2,2.5dB sensitivity hit    | -<br>-                | -22<br>-15                                           | -<br>-                | dBm<br>dBm                                    |

| RFS_L10_HF  | RF sensitivity, Long-Range Mode, highest LNA gain, <i>LnaBoost</i> for Band 1, using split Rx/Tx path 10.4 kHz bandwidth | SF = 6<br>SF = 7<br>SF = 8<br>SF = 11                                 | -<br>-<br>-           | -131<br>-134<br>-138<br>-146                         | -<br>-<br>-           | dBm<br>dBm<br>dBm<br>dBm                      |

| RFS_L62_HF  | RF sensitivity, Long-Range Mode, highest LNA gain, <i>LnaBoost</i> for Band 1, using split Rx/Tx path 62.5 kHz bandwidth | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12 | -<br>-<br>-<br>-<br>- | -121<br>-126<br>-129<br>-132<br>-135<br>-137<br>-139 | -<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_L125_HF | RF sensitivity, Long-Range Mode, highest LNA gain, <i>LnaBoost</i> for Band 1, using split Rx/Tx path 125 kHz bandwidth  | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12 | -<br>-<br>-<br>-<br>- | -118<br>-123<br>-126<br>-129<br>-132<br>-133<br>-136 | -<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_L250_HF | RF sensitivity, Long-Range Mode, highest LNA gain, <i>LnaBoost</i> for Band 1, using split Rx/Tx path 250 kHz bandwidth  | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12 | -<br>-<br>-<br>-<br>- | -115<br>-120<br>-123<br>-125<br>-128<br>-130<br>-133 | -<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_L500_HF | RF sensitivity, Long-Range Mode, highest LNA gain, <i>LnaBoost</i> for Band 1, using split Rx/Tx path 500 kHz bandwidth  | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12 | -<br>-<br>-<br>-<br>- | -111<br>-116<br>-119<br>-122<br>-125<br>-128<br>-130 | -<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| RFS_L7.8_LF | RF sensitivity, Long-Range Mode, highest LNA gain, Band 2 or 3, using split Rx/Tx path 7.8 kHz bandwidth                 | SF = 12<br>SF = 11                                                    | -                     | -148<br>-145                                         |                       | dBm<br>dBm                                    |

| RFS_L10_LF  | RF sensitivity, Long-Range Mode,<br>highest LNA gain, Band 3,<br>10.4 kHz bandwidth                                      | SF = 6<br>SF = 7<br>SF = 8                                            | -<br>-<br>-           | -132<br>-136<br>-138                                 | -<br>-<br>-           | dBm<br>dBm<br>dBm                             |

| RFS_L62_LF  | RF sensitivity, Long-Range Mode,<br>highest LNA gain, Band 3,<br>62.5 kHz bandwidth                                      | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12 | -<br>-<br>-<br>-<br>- | -123<br>-128<br>-131<br>-134<br>-135<br>-137<br>-140 | -<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

# DATASHEET

| Symbol      | Description                                                                                                   | Conditions                                                                                          | Min.                  | Тур                                                          | Max                        | Unit                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------|----------------------------|------------------------------------------------------|

| RFS_L125_LF | RF sensitivity, Long-Range Mode, highest LNA gain, Band 3,                                                    | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9                                                                | -<br>-<br>-           | -121<br>-125<br>-128<br>-131                                 | -<br>-<br>-                | dBm<br>dBm<br>dBm<br>dBm                             |

|             | 125 kHz bandwidth                                                                                             | SF = 10<br>SF = 11<br>SF = 12                                                                       | -<br>-<br>-           | -134<br>-136<br>-137                                         | -<br>-<br>-                | dBm<br>dBm<br>dBm                                    |

| RFS_L250_LF | RF sensitivity, Long-Range Mode,<br>highest LNA gain, Band 3<br>250 kHz bandwidth                             | SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11                                          | -<br>-<br>-<br>-      | -118<br>-122<br>-125<br>-128<br>-131<br>-133                 | -<br>-<br>-<br>-           | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm               |

| RFS_L500_LF | RF sensitivity, Long-Range Mode,<br>highest LNA gain, Band 3<br>500 kHz bandwidth                             | SF = 12<br>SF = 6<br>SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12                    | -<br>-<br>-<br>-<br>- | -134<br>-112<br>-118<br>-121<br>-124<br>-127<br>-129<br>-130 | -<br>-<br>-<br>-<br>-<br>- | dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm<br>dBm |

| CCR_LCW     | Co-channel rejection<br>Single CW tone = Sens +6 dB<br>1% PER                                                 | SF = 7<br>SF = 8<br>SF = 9<br>SF = 10<br>SF = 11<br>SF = 12                                         | -<br>-<br>-<br>-      | 5<br>9.5<br>12<br>14.4<br>17<br>19.5                         | -<br>-<br>-<br>-           | dB<br>dB<br>dB<br>dB<br>dB                           |

| CCR_LL      | Co-channel rejection                                                                                          | Interferer is a LoRa <sup>TM</sup> signal using same BW and same SF. Pw = Sensitivity + 3 dB        |                       | -6                                                           |                            | dB                                                   |

| ACR_LCW     | Adjacent channel rejection                                                                                    | Interferer is 1.5*BW_L from the wanted signal center frequency 1% PER, Single CW tone = Sens + 3 dB |                       |                                                              |                            |                                                      |

|             |                                                                                                               | SF = 7<br>SF = 12                                                                                   | -                     | 60<br>72                                                     | -                          | dB<br>dB                                             |

| IMR_LCW     | Image rejection after calibration.                                                                            | 1% PER, Single CW tone = Sens +3 dB                                                                 | -                     | 66                                                           | -                          | dB                                                   |

| FERR_L      | Maximum tolerated frequency offset between transmitter and receiver, no sensitivity degradation, SF6 thru 12  | All BW, +/-25% of BW The tighter limit applies (see below)                                          |                       | +/-25%                                                       |                            | BW                                                   |

|             | Maximum tolerated frequency offset between transmitter and receiver, no sensitivity degradation, SF10 thru 12 | SF = 12<br>SF = 11<br>SF = 10                                                                       | -50<br>-100<br>-200   | -<br>-<br>-                                                  | 50<br>100<br>200           | ppm<br>ppm<br>ppm                                    |

**DATASHEET**

## 2.5.6. Digital Specification

Conditions: Temp = 25° C, VDD = 3.3 V, FXOSC = 32 MHz, unless otherwise specified.

Table 11 Digital Specification

| Symbol              | Description                        | Conditions                                             | Min | Тур | Max | Unit |

|---------------------|------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| V <sub>IH</sub>     | Digital input level high           |                                                        | 0.8 | -   | -   | VDD  |

| V <sub>IL</sub>     | Digital input level low            |                                                        | -   | -   | 0.2 | VDD  |

| V <sub>OH</sub>     | Digital output level high          | Imax = 1 mA                                            | 0.9 | -   | -   | VDD  |

| V <sub>OL</sub>     | Digital output level low           | Imax = -1 mA                                           | -   | -   | 0.1 | VDD  |

| F <sub>SCK</sub>    | SCK frequency                      |                                                        | -   | -   | 10  | MHz  |

| t <sub>ch</sub>     | SCK high time                      |                                                        | 50  | -   | -   | ns   |

| t <sub>cl</sub>     | SCK low time                       |                                                        | 50  | -   | -   | ns   |

| t <sub>rise</sub>   | SCK rise time                      |                                                        | -   | 5   | -   | ns   |

| t <sub>fall</sub>   | SCK fall time                      |                                                        | -   | 5   | -   | ns   |

| t <sub>setup</sub>  | MOSI setup time                    | From MOSI change to SCK rising edge.                   | 30  | -   | -   | ns   |

| t <sub>hold</sub>   | MOSI hold time                     | From SCK rising edge to MOSI change.                   | 20  | -   | -   | ns   |

| t <sub>nsetup</sub> | NSS setup time                     | From NSS falling edge to SCK rising edge.              | 30  | -   | -   | ns   |

| t <sub>nhold</sub>  | NSS hold time                      | From SCK falling edge to NSS rising edge, normal mode. | 100 | -   | -   | ns   |

| t <sub>nhigh</sub>  | NSS high time between SPI accesses |                                                        | 20  | -   | -   | ns   |

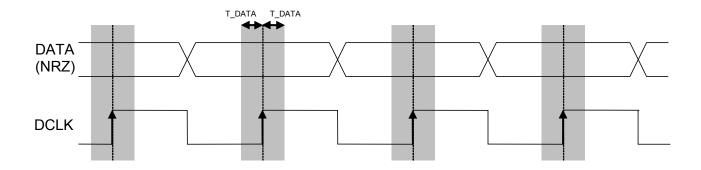

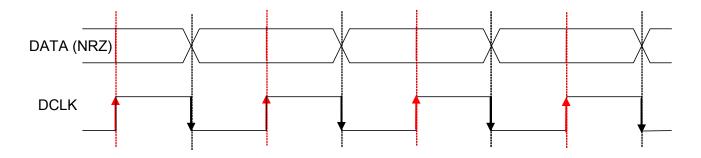

| T_DATA              | DATA hold and setup time           |                                                        | 250 | -   | -   | ns   |

**DATASHEET**

### 3. SX1276/77/78/79 Features

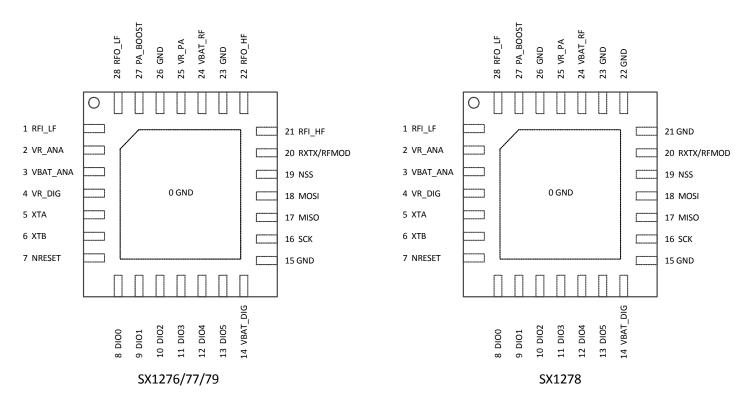

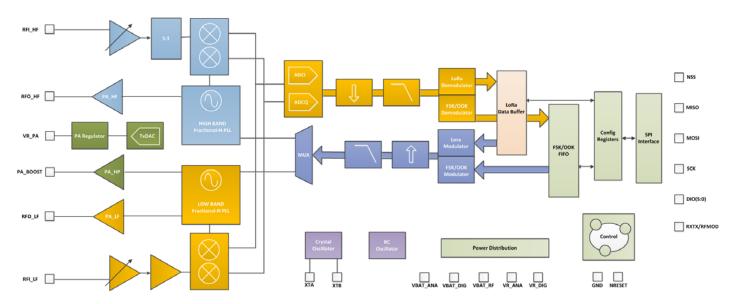

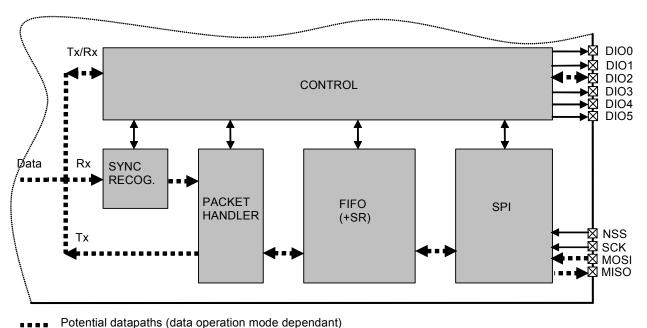

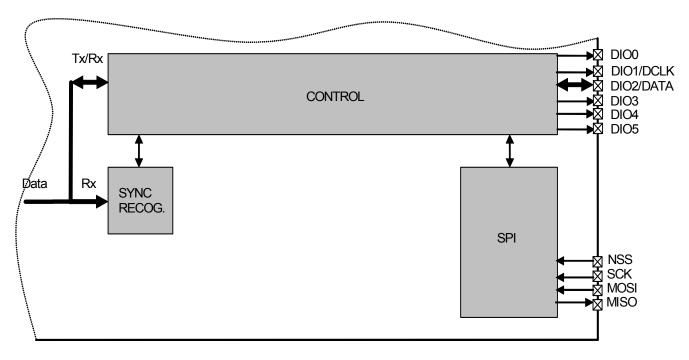

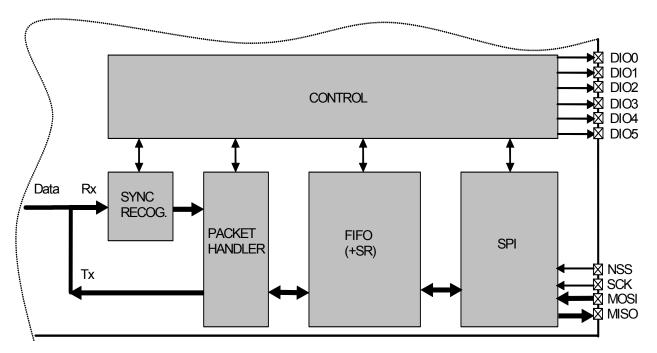

This section gives a high-level overview of the functionality of the SX1276/77/78/79 low-power, highly integrated transceiver. The following figure shows a simplified block diagram of the SX1276/77/78/79.

Figure 4. SX1276/77/78/79 Block Schematic Diagram

SX1276/77/78/79 is a half-duplex, low-IF transceiver. Here the received RF signal is first amplified by the LNA. The LNA inputs are single ended to minimize the external BoM and for ease of design. Following the LNA inputs, the conversion to differential is made to improve the second order linearity and harmonic rejection. The signal is then down-converted to inphase and quadrature (I&Q) components at the intermediate frequency (IF) by the mixer stage. A pair of sigma delta ADCs then perform data conversion, with all subsequent signal processing and demodulation performed in the digital domain. The digital state machine also controls the automatic frequency correction (AFC), received signal strength indicator (RSSI) and automatic gain control (AGC). It also features the higher-level packet and protocol level functionality of the top level sequencer (TLS), only available with traditional FSK and OOK modulation schemes.

The frequency synthesizers generate the local oscillator (LO) frequency for both receiver and transmitter, one covering the lower UHF bands (up to 525 MHz), and the other one covering the upper UHF bands (from 779 MHz). The PLLs are optimized for user-transparent low lock time and fast auto-calibrating operation. In transmission, frequency modulation is performed digitally within the PLL bandwidth. The PLL also features optional pre-filtering of the bit stream to improve spectral purity.

SX1276/77/78/79 feature three distinct RF power amplifiers. Two of those, connected to RFO\_LF and RFO\_HF, can deliver up to +14 dBm, are unregulated for high power efficiency and can be connected directly to their respective RF receiver inputs via a pair of passive components to form a single antenna port high efficiency transceiver. The third PA, connected to the PA\_BOOST pin and can deliver up to +20 dBm via a dedicated matching network. Unlike the high efficiency PAs, this high-stability PA covers all frequency bands that the frequency synthesizer addresses.

SX1276/77/78/79 also include two timing references, an RC oscillator and a 32 MHz crystal oscillator.

**DATASHEET**

All major parameters of the RF front end and digital state machine are fully configurable via an SPI interface which gives access to SX1276/77/78/79's configuration registers. This includes a mode auto sequencer that oversees the transition and calibration of the SX1276/77/78/79 between intermediate modes of operation in the fastest time possible.

The SX1276/77/78/79 are equipped with both standard FSK and long range spread spectrum (LoRa<sup>TM</sup>) modems. Depending upon the mode selected either conventional OOK or FSK modulation may be employed or the LoRa<sup>TM</sup> spread spectrum modem.

### 3.1. LoRa<sup>TM</sup> Modem

The LoRa<sup>TM</sup> modem uses a proprietary spread spectrum modulation technique. This modulation, in contrast to legacy modulation techniques, permits an increase in link budget and increased immunity to in-band interference. At the same time the frequency tolerance requirement of the crystal reference oscillator is relaxed - allowing a performance increase for a reduction in system cost. For a detailed description of the design trade-offs and operation of the SX1276/77/78/79 please consult Section 4.1 of the datasheet.

### 3.2. FSK/OOK Modem

In FSK/OOK mode the SX1276/77/78/79 supports standard modulation techniques including OOK, FSK, GFSK, MSK and GMSK. The SX1276/77/78/79 is especially suited to narrow band communication thanks the low-IF architecture employed and the built-in AFC functionality. For full information on the FSK/OOK modem please consult Section 4.2 of this document.

**DATASHEET**

# 4. SX1276/77/78/79 Digital Electronics

## 4.1. The LoRa<sup>TM</sup> Modem

The LoRa<sup>TM</sup> modem uses spread spectrum modulation and forward error correction techniques to increase the range and robustness of radio communication links compared to traditional FSK or OOK based modulation. Examples of the performance improvement possible, for several possible settings, are summarised in the table below. Here the spreading factor and error correction rate are design variables that allow the designer to optimise the trade-off between occupied bandwidth, data rate, link budget improvement and immunity to interference.

Table 12 Example LoRa<sup>TM</sup> Modem Performances, 868MHz Band

| Bandwidth<br>(kHz) | Spreading Factor | Coding rate | Nominal Rb<br>(bps) | Sensitivity<br>indication<br>(dBm) | Frequency<br>Reference |  |

|--------------------|------------------|-------------|---------------------|------------------------------------|------------------------|--|

| 10.4               | 6                | 4/5         | 782                 | -131                               |                        |  |

|                    | 12               | 4/5         | 24                  | -147                               | тсхо                   |  |

| 20.8               | 6                | 4/5         | 1562                | -128                               |                        |  |

|                    | 12               | 4/5         | 49                  | -144                               |                        |  |

| 62.5               | 6                | 4/5         | 4688                | -121                               |                        |  |

|                    | 12               | 4/5         | 146                 | -139                               | \                      |  |

| 125                | 6                | 4/5         | 9380                | -118                               | XTAL                   |  |

|                    | 12               | 4/5         | 293                 | -136                               |                        |  |

For European operation the range of crystal tolerances acceptable for each sub-band (of the ERC 70-03) is given in the specifications table. For US based operation a frequency hopping mode is available that automates both the LoRa<sup>TM</sup> spread spectrum and frequency hopping spread spectrum processes.

Another important facet of the LoRa<sup>TM</sup> modem is its increased immunity to interference. The LoRa<sup>TM</sup> modem is capable of co-channel GMSK rejection of up to 20 dB. This immunity to interference permits the simple coexistence of LoRa<sup>TM</sup> modulated systems either in bands of heavy spectral usage or in hybrid communication networks that use LoRa<sup>TM</sup> to extend range when legacy modulation schemes fail.

Notes - for all bandwidths lower than 62.5 kHz, it is advised to use a TCXO as a frequency reference. This is required to meet the frequency error tolerance specifications given in the Electrical Specification

<sup>-</sup> Higher spreading factors and longer transmission times impose more stringent constraints on the short term frequency stability of the reference. Please get in touch with a Semtech representative to implement extremely low sensitivity products.

DATASHEET

# 4.1.1. Link Design Using the LoRa<sup>TM</sup> Modem

#### 4.1.1.1. Overview

The LoRa<sup>TM</sup> modem is setup as shown in the following figure. This configuration permits the simple replacement of the FSK modem with the LoRa<sup>TM</sup> modem via the configuration register setting *RegOpMode*. This change can be performed on the fly (in Sleep operating mode) thus permitting the use of both standard FSK or OOK in conjunction with the long range capability. The LoRa<sup>TM</sup> modulation and demodulation process is proprietary, it uses a form of spread spectrum modulation combined with cyclic error correction coding. The combined influence of these two factors is an increase in link budget and enhanced immunity to interference.

Figure 5. LoRa<sup>TM</sup> Modem Connectivity

A simplified outline of the transmit and receive processes is also shown above. Here we see that the LoRa<sup>TM</sup> modem has an independent dual port data buffer FIFO that is accessed through an SPI interface common to all modes. Upon selection of LoRa<sup>TM</sup> mode, the configuration register mapping of the SX1276/77/78/79 changes. For full details of this change please consult the register description of Section 6.

So that it is possible to optimise the LoRa<sup>TM</sup> modulation for a given application, access is given to the designer to three critical design parameters. Each one permitting a trade off between link budget, immunity to interference, spectral occupancy and nominal data rate. These parameters are spreading factor, modulation bandwidth and error coding rate.

**DATASHEET**

#### 4.1.1.2. Spreading Factor

The spread spectrum LoRa<sup>TM</sup> modulation is performed by representing each bit of payload information by multiple chips of information. The rate at which the spread information is sent is referred to as the symbol rate (Rs), the ratio between the nominal symbol rate and chip rate is the spreading factor and represents the number of symbols sent per bit of information. The range of values accessible with the LoRa<sup>TM</sup> modem are shown in the following table.

Table 13 Range of Spreading Factors

| SpreadingFactor<br>(RegModulationCfg) | Spreading Factor (Chips / symbol) | LoRa Demodulator<br>SNR |

|---------------------------------------|-----------------------------------|-------------------------|

| 6                                     | 64                                | -5 dB                   |

| 7                                     | 128                               | -7.5 dB                 |

| 8                                     | 256                               | -10 dB                  |

| 9                                     | 512                               | -12.5 dB                |

| 10                                    | 1024                              | -15 dB                  |

| 11                                    | 2048                              | -17.5 dB                |

| 12                                    | 4096                              | -20 dB                  |

Note that the spreading factor, *SpreadingFactor*, must be known in advance on both transmit and receive sides of the link as different spreading factors are orthogonal to each other. Note also the resulting signal to noise ratio (SNR) required at the receiver input. It is the capability to receive signals with negative SNR that increases the sensitivity, so link budget and range, of the LoRa receiver.

#### **Spreading Factor 6**

SF = 6 Is a special use case for the highest data rate transmission possible with the LoRa modem. To this end several settings must be activated in the SX1276/77/78/79 registers when it is in use. These settings are only valid for SF6 and should be set back to their default values for other spreading factors:

- Set SpreadingFactor = 6 in RegModemConfig2

- The header must be set to Implicit mode.

- Set the bit field DetectionOptimize of register RegLoRaDetectOptimize to value "0b101".

- Write 0x0C in the register RegDetectionThreshold.

#### 4.1.1.3. Coding Rate

To further improve the robustness of the link the LoRa<sup>TM</sup> modem employs cyclic error coding to perform forward error detection and correction. Such error coding incurs a transmission overhead - the resultant additional data overhead per transmission is shown in the table below.

Table 14 Cyclic Coding Overhead

| CodingRate<br>(RegTxCfg1) | Cyclic Coding<br>Rate | Overhead Ratio |

|---------------------------|-----------------------|----------------|

| 1                         | 4/5                   | 1.25           |

| 2                         | 4/6                   | 1.5            |

| 3                         | 4/7                   | 1.75           |

| 4                         | 4/8                   | 2              |

**DATASHEET**

Forward error correction is particularly efficient in improving the reliability of the link in the presence of interference. So that the coding rate (and so robustness to interference) can be changed in response to channel conditions - the coding rate can optionally be included in the packet header for use by the receiver. Please consult Section 4.1.1.6 for more information on the LoRa<sup>TM</sup> packet and header.

#### 4.1.1.4. Signal Bandwidth

An increase in signal bandwidth permits the use of a higher effective data rate, thus reducing transmission time at the expense of reduced sensitivity improvement. There are of course regulatory constraints in most countries on the permissible occupied bandwidth. Contrary to the FSK modem which is described in terms of the single sideband bandwidth, the LoRa<sup>TM</sup> modem bandwidth refers to the double sideband bandwidth (or total channel bandwidth). The range of bandwidths relevant to most regulatory situations is given in the LoRa<sup>TM</sup> modem specifications table (see Section 2.5.5).

Table 15 LoRa Bandwidth Options

| Bandwidth<br>(kHz) | Spreading Factor | Coding rate | Nominal Rb<br>(bps) |

|--------------------|------------------|-------------|---------------------|

| 7.8                | 12               | 4/5         | 18                  |

| 10.4               | 12               | 4/5         | 24                  |

| 15.6               | 12               | 4/5         | 37                  |

| 20.8               | 12               | 4/5         | 49                  |

| 31.2               | 12               | 4/5         | 73                  |

| 41.7               | 12               | 4/5         | 98                  |

| 62.5               | 12               | 4/5         | 146                 |

| 125                | 12               | 4/5         | 293                 |

| 250                | 12               | 4/5         | 586                 |

| 500                | 12               | 4/5         | 1172                |

Note In the lower band (169 MHz), the 250 kHz and 500 kHz bandwidths are not supported.

## 4.1.1.5. LoRa<sup>TM</sup> Transmission Parameter Relationship

With a knowledge of the key parameters that can be controlled by the user we define the LoRa<sup>TM</sup> symbol rate as:

$$Rs = \frac{BW}{2^{SF}}$$

where BW is the programmed bandwidth and SF is the spreading factor. The transmitted signal is a constant envelope signal. Equivalently, one chip is sent per second per Hz of bandwidth.

**DATASHEET**

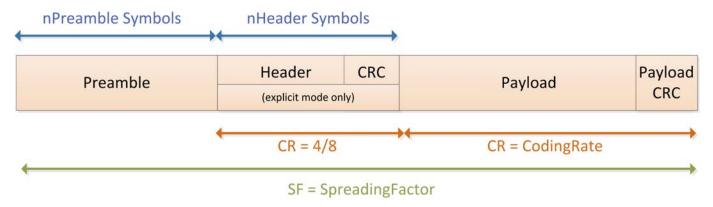

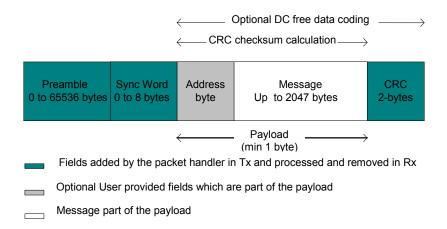

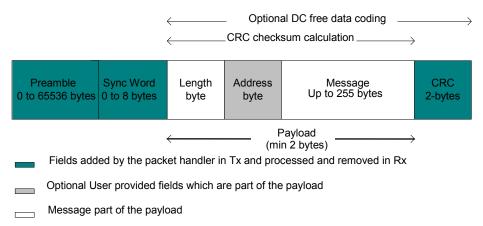

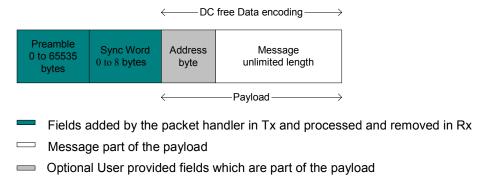

### 4.1.1.6. LoRa<sup>TM</sup> Packet Structure

The LoRa<sup>TM</sup> modem employs two types of packet format, explicit and implicit. The explicit packet includes a short header that contains information about the number of bytes, coding rate and whether a CRC is used in the packet. The packet format is shown in the following figure.

The LoRa<sup>TM</sup> packet comprises three elements:

- ◆ A preamble.

- An optional header.