# Industrial I/V Output Driver, Single-Supply, 55 V Maximum Supply, Programmable Ranges

# AD5751

#### FEATURES

Current output ranges: 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA ±0.03% FSR typical total unadjusted error (TUE) ±5 ppm/°C typical output drift 2% overrange Voltage output ranges: 0 V to 5 V, 0 V to 10 V, 0 V to 40 V ±0.02% FSR typical total unadjusted error (TUE) ±3 ppm/°C typical output drift Overrange capability on all ranges Flexible serial digital interface **On-chip output fault detection PEC error checking Asynchronous CLEAR function** Power supply range AV<sub>DD</sub>: 12 V (± 10%) to 55 V (maximum) Output loop compliance to AV<sub>DD</sub> – 2.75 V Temperature range: -40°C to +105°C 32-lead 5 mm × 5 mm LFCSP package

#### APPLICATIONS

Process control Actuator control PLCs

Rev. A

#### **GENERAL DESCRIPTION**

The AD5751 is a single-channel, low cost, precision, voltage/ current output driver with hardware or software programmable output ranges. The software ranges are configured via an SPI-/ MICROWIRE<sup>™</sup>-compatible serial interface. The AD5751 targets applications in PLC and industrial process control. The analog input to the AD5751 is provided from a low voltage, single-supply digital-to-analog converter (DAC) and is internally conditioned to provide the desired output current/voltage range.

The output current range is programmable across three current ranges: 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA.

Voltage output is provided from a separate pin that can be configured to provide 0 V to 5 V, 0 V to 10 V, and 0 V to 40 V output ranges. An overrange is available on the voltage ranges.

Analog outputs are short-circuit and open-circuit protected and can drive capacitive loads of 1  $\mu$ F and inductive loads of 0.1 H.

The device is specified to operate with a power supply range from 10.8 V to 55 V. Output loop compliance is 0 V to  $AV_{DD} - 2.75$  V.

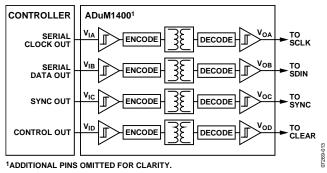

The flexible serial interface is SPI and MICROWIRE compatible and can be operated in 3-wire mode to minimize the digital isolation required in isolated applications. The interface also features an optional PEC error checking feature using CRC-8 error checking, useful in industrial environments where data communication corruption can occur.

The device also includes a power-on reset function ensuring that the device powers up in a known state (0 V or tristate) and an asynchronous CLEAR pin that sets the outputs to zeroscale/midscale voltage output or the low end of the selected current range.

An HW SELECT pin is used to configure the part for hardware or software mode on power-up.

Table 1. Related Device

| Part Number | Description                                                                |

|-------------|----------------------------------------------------------------------------|

| AD5422      | Single-channel, 16-bit, serial input current source and voltage output DAC |

# TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

| General Description1                          |

| Revision History                              |

| Functional Block Diagram 3                    |

| Specifications                                |

| Timing Characteristics7                       |

| Absolute Maximum Ratings                      |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions10 |

| Typical Performance Characteristics           |

| Current Output15                              |

| Terminology                                   |

| Theory of Operation                           |

| Software Mode                                 |

| Currrent Output Architecture                  |

| Driving Inductive Loads23                     |

| Power-On State of the AD575123                |

| Default Registers at Power-On24               |

| Reset Function                                |

#### **REVISION HISTORY**

| 5/10—Rev. 0 to Rev. A                  |   |

|----------------------------------------|---|

| Changes to Table 2, Power Requirements | 6 |

10/09—Revision 0: Initial Version

07269-001

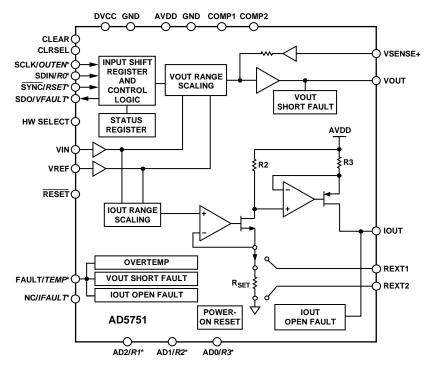

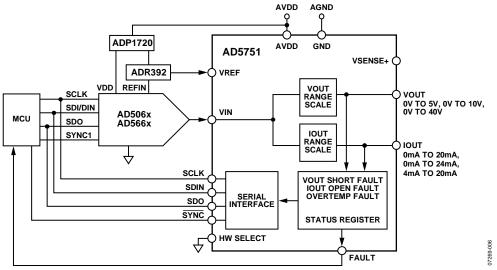

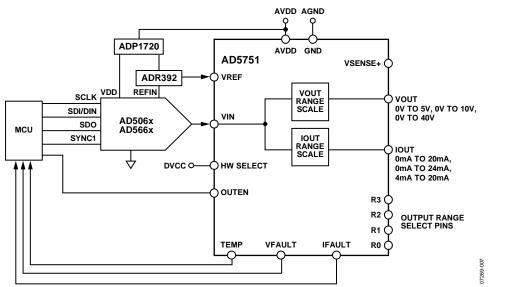

### FUNCTIONAL BLOCK DIAGRAM

\*DENOTES SHARED PIN. SOFTWARE MODE DENOTED BY REGULAR TEXT, HARDWARE MODE DENOTED BY *ITALIC* TEXT. FOR EXAMPLE, FOR FAULT/*TEMP* PIN, IN SOFTWARE MODE, THIS PIN TAKES ON FAULT FUNCTION. IN HARDWARE MODE, THIS PIN TAKES ON *TEMP* FUNCTION.

Figure 1. Functional Block Diagram

### SPECIFICATIONS

$AV_{DD}$  = 12 V (± 10%) to 55 V (maximum),  $DV_{CC}$  = 2.7 V to 5.5 V, GND = 0 V. IOUT:  $R_{LOAD}$  = 300  $\Omega$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 2.

| Parameter <sup>1</sup>                 | Min   | Тур        | Max   | Unit       | Test Conditions/Comments                                                                                  |

|----------------------------------------|-------|------------|-------|------------|-----------------------------------------------------------------------------------------------------------|

| INPUT VOLTAGE RANGE                    |       |            |       |            | Output unloaded                                                                                           |

|                                        |       | 0 to 4.096 |       | V          |                                                                                                           |

| Input Leakage Current                  | -1    |            | +1    | μA         |                                                                                                           |

| REFERENCE INPUT                        |       |            |       |            |                                                                                                           |

| Reference Input Voltage                |       | 4.096      |       | V          | External reference must be exactly as stated,<br>otherwise, accuracy errors show up as error<br>in output |

| Input Leakage Current                  | -1    |            | +1    | μΑ         |                                                                                                           |

| VOLTAGE OUTPUT                         |       |            |       |            |                                                                                                           |

| Output Voltage Ranges                  | 0     |            | 5     | V          |                                                                                                           |

|                                        | 0     |            | 10    | V          | AVDD must have minimum 1.3 V headroom<br>or >11.3 V                                                       |

|                                        | 0     |            | 40    | V          |                                                                                                           |

| Output Voltage Overranges <sup>2</sup> | 0     |            | 6     | V          | Programmable overranges; see Detailed<br>Description of Features section                                  |

|                                        | 0     |            | 12    | V          |                                                                                                           |

|                                        | 0     |            | 44    | V          |                                                                                                           |

| Accuracy                               |       |            |       |            |                                                                                                           |

| Total Unadjusted Error (TUE)           |       |            |       |            |                                                                                                           |

| B Version <sup>3</sup>                 | -0.1  |            | +0.1  | % FSR      |                                                                                                           |

|                                        | -0.05 | ±0.02      | +0.05 | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

| A Version3                             | -0.3  |            | +0.3  | % FSR      |                                                                                                           |

|                                        | -0.1  | ±0.05      | +0.1  | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

| Relative Accuracy (INL)                | -0.02 | ±0.005     | +0.02 | % FSR      |                                                                                                           |

| Dead Band on Output, RTI               | -14   | 8          | +14   | mV         | Referred to 4.096 V input range                                                                           |

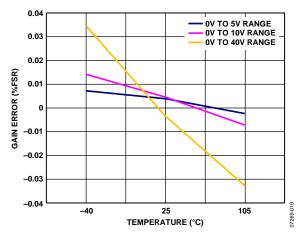

| Offset Error                           | -5    |            | +5    | mV         | 0 V to 10 V range                                                                                         |

|                                        | -4    | ±0.5       | +4    | mV         | $T_A = 25^{\circ}C$ , 0 V to 10 V range                                                                   |

|                                        | -3    |            | +3    | mV         | 0 V to 5 V range                                                                                          |

|                                        | -2.2  | ±0.3       | +2.2  | mV         | $T_A = 25^{\circ}C$ , 0 V to 5 V range                                                                    |

|                                        | -20   |            | +20   | mV         | 0 V to 40 V range                                                                                         |

|                                        | -17   | ±0.5       | +17   | mV         | $T_A = 25^{\circ}C$ , 0 V to 40 V range                                                                   |

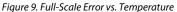

| Gain Error                             | -0.05 |            | +0.05 | % FSR      | 0 V to 5 V, 0 V to 10 V range                                                                             |

|                                        | -0.04 | ±0.015     | +0.04 | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

|                                        | -0.09 |            | +0.09 | % FSR      | 0 V to 40 V range                                                                                         |

|                                        | -0.05 | ±0.02      | +0.05 | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

| Gain Error TC <sup>4</sup>             |       | ±0.5       |       | ppm FSR/°C | All ranges                                                                                                |

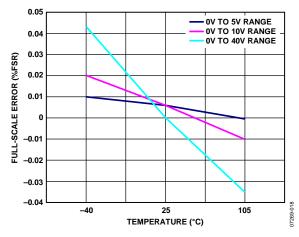

| Full-Scale Error                       | -0.05 |            | +0.05 | % FSR      | 0 V to 5 V, 0 V to 10 V range                                                                             |

|                                        | -0.04 | ±0.015     | +0.04 | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

|                                        | -0.09 |            | +0.09 | % FSR      | 0 V to 40 V range                                                                                         |

|                                        | -0.05 | ±0.02      | +0.05 | % FSR      | $T_A = 25^{\circ}C$                                                                                       |

| Full-Scale Error TC <sup>4</sup>       |       | ±1.5       |       | ppm FSR/°C | All ranges                                                                                                |

| OUTPUT CHARACTERISTICS <sup>4</sup>    |       |            |       |            |                                                                                                           |

| Headroom                               |       |            | 1.3   | V          | Output unloaded                                                                                           |

| Short-Circuit Current                  |       | 15         |       | mA         |                                                                                                           |

| Load                                   |       |            |       |            |                                                                                                           |

|                                        | 1     |            |       | kΩ         | For specified performance, 0 V to 5 V and 0 V to 10 V ranges                                              |

|                                        | 5     |            |       | kΩ         | For specified performance, 0 V to 40 V range                                                              |

| Parameter <sup>1</sup>                 | Min        | Тур         | Max        | Unit       | Test Conditions/Comments                                         |

|----------------------------------------|------------|-------------|------------|------------|------------------------------------------------------------------|

| Capacitive Load Stability              |            |             |            |            | $T_A = 25^{\circ}C$                                              |

| $R_{LOAD} = \infty$                    |            |             | 1          | nF         |                                                                  |

| $R_{IOAD} = 1 k\Omega$                 |            |             | 1          | nF         |                                                                  |

| $R_{LOAD} = \infty$                    |            |             | 2          | μF         | External compensation capacitor required;                        |

|                                        |            |             | _          |            | see Driving Large Capacitive Loads section                       |

| DC Output Impedance                    |            | 0.12        |            | Ω          |                                                                  |

| Settling Time                          |            |             |            |            |                                                                  |

| 0 V to 5 V Range, ¼ to ¾ Step          |            | 7           |            | μs         | Specified with 2 k $\Omega \parallel$ 220 pF, ±0.05%             |

| 0 V to 5 V Range, 40 mV Input Step     |            | 4.5         |            | μs         | Specified with 2 k $\Omega$    220 pF, ±0.05%                    |

| 0 V to 40 V Range, ¼ to ¾ Step         |            | 15.8        |            | μs         | Specified with 5 k $\Omega \parallel$ 220 pF, ±0.05%             |

| Slew Rate                              |            | 2           |            | V/µs       | Specified with 1 kΩ    220 pF                                    |

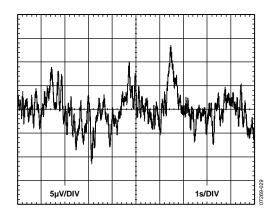

| Output Noise                           |            | 3.5         |            | μV rms     | 0.1 Hz to 10 Hz bandwidth                                        |

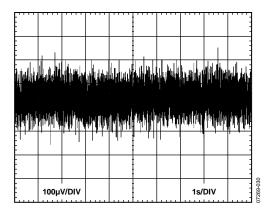

|                                        |            | 45.5        |            | μV rms     | 100 kHz bandwidth; specified with 2 k $\Omega$                   |

|                                        |            |             |            | P          | 220 pF                                                           |

| Output Noise Spectral Density          |            | 165         |            | nV/√Hz     | Measured at 10 kHz; specified with 2 k $\Omega \parallel 220$ pF |

| AC PSRR                                |            | 65          |            | dB         | 200 mV, 50 Hz/60 Hz sine wave                                    |

|                                        |            | 10          |            |            | superimposed on power supply voltage                             |

|                                        |            | 10          |            | μV/V       |                                                                  |

| CURRENT OUTPUT                         | 0          |             | 24         |            |                                                                  |

| Output Current Ranges                  | 0          |             | 24         | mA         |                                                                  |

|                                        | 0          |             | 20         | mA         |                                                                  |

|                                        | 3.92       |             | 20         | mA         |                                                                  |

| Output Current Overranges <sup>2</sup> | 0          |             | 24.5       | mA         | See Detailed Description of Features sectio                      |

|                                        | 0          |             | 20.4       | mA         | See Detailed Description of Features sectio                      |

|                                        | 3.92       |             | 20.4       | mA         | See Detailed Description of Features sectio                      |

| ACCURACY (INTERNAL Rset)               |            |             |            |            |                                                                  |

| Total Unadjusted Error (TUE)           |            |             |            |            |                                                                  |

| B Version3                             | -0.2       |             | +0.2       | % FSR      |                                                                  |

|                                        | -0.08      | ±0.03       | +0.08      | % FSR      | T <sub>A</sub> = 25°C                                            |

| A Version3                             | -0.5       | _0.00       | +0.5       | % FSR      |                                                                  |

| Aveisions                              | -0.3       | ±0.15       | +0.3       | % FSR      | $T_A = 25^{\circ}C$                                              |

|                                        |            |             |            |            | $T_A = 25 C$                                                     |

| Relative Accuracy (INL)                | -0.02      | ±0.01       | +0.02      | % FSR      |                                                                  |

| Offset Error                           | -16        |             | +16        | μа         |                                                                  |

|                                        | -10        | +5          | +10        | μа         | $T_A = 25^{\circ}C$                                              |

| Offset Error TC <sup>4</sup>           |            | ±3          |            | ppm FSR/°C |                                                                  |

| Dead Band on Output, RTI               |            | 8           | +14        | mV         | Referred to 4.096 V input range                                  |

| Gain Error                             | -0.2       |             | +0.2       | % FSR      |                                                                  |

|                                        | -0.125     | ±0.02       | +0.125     | % FSR      | $T_A = 25^{\circ}C$                                              |

| Gain TC⁴                               |            | ±10         |            | ppm FSR/°C |                                                                  |

| Full-Scale Error                       | -0.2       |             | +0.2       | % FSR      |                                                                  |

|                                        | -0.125     | ±0.02       | +0.125     | % FSR      | T <sub>A</sub> = 25°C                                            |

| Full-Scale TC <sup>₄</sup>             | 0.125      | ±0.02<br>±4 | 10.125     | ppm FSR/°C |                                                                  |

| ACCURACY (EXTERNAL R <sub>SET</sub> )  |            |             |            |            |                                                                  |

| Total Unadjusted Error (TUE)           |            |             |            |            |                                                                  |

| B Version3                             | -0.1       |             | +0.1       | % FSR      |                                                                  |

|                                        | -0.08      | ±0.03       | +0.08      | % FSR      | $T_A = 25^{\circ}C$                                              |

| A Version3                             | -0.3       |             | +0.3       | % FSR      |                                                                  |

|                                        | -0.1       | ±0.02       | +0.1       | % FSR      | $T_A = 25^{\circ}C$                                              |

| Relative Accuracy (INL)                | -0.02      | ±0.01       | +0.02      | % FSR      |                                                                  |

| Offset Error                           | -14        | -0.01       | +0.02      | μA         |                                                                  |

| Onset Entri                            | -14<br>-11 | +5          | +14<br>+11 | μα         | $T_A = 25^{\circ}C$                                              |

| Offset Error TC <sup>4</sup>           |            | +3<br>±2    | TII        | ppm FSR/°C |                                                                  |

|                                        |            |             | . 1 4      |            |                                                                  |

| Dead Band on Output, RTI               | 0.00       | 8           | +14        | mV         | Referred to 4.096 V input range                                  |

| Gain Error                             | -0.08      |             | +0.08      | % FSR      |                                                                  |

|                                        | -0.07      | ±0.02       | +0.07      | % FSR      | $T_A = 25^{\circ}C$                                              |

| Parameter <sup>1</sup>                | Min          | Тур           | Max                     | Unit       | Test Conditions/Comments                                                                           |

|---------------------------------------|--------------|---------------|-------------------------|------------|----------------------------------------------------------------------------------------------------|

| Gain TC⁴                              |              | ±1            |                         | ppm FSR/°C |                                                                                                    |

| Full-Scale Error                      | -0.1         |               | +0.1                    | % FSR      |                                                                                                    |

|                                       | -0.07        | ±0.02         | +0.07                   | % FSR      | $T_A = 25^{\circ}C$                                                                                |

| Full-Scale TC <sup>₄</sup>            |              | ±2            |                         | ppm FSR/°C |                                                                                                    |

| OUTPUT CHARACTERISTICS <sup>4</sup>   |              |               |                         |            |                                                                                                    |

| Current Loop Compliance Voltage       | 0            |               | AV <sub>DD</sub> - 2.75 | V          |                                                                                                    |

| Resistive Load                        |              |               |                         |            | Chosen such that compliance is not exceeded                                                        |

| Inductive Load                        | See test cor | nditions/comr | nents column            | н          | Needs appropriate capacitor at higher<br>inductance values; see Driving Inductive<br>Loads section |

| Settling Time                         |              |               |                         |            |                                                                                                    |

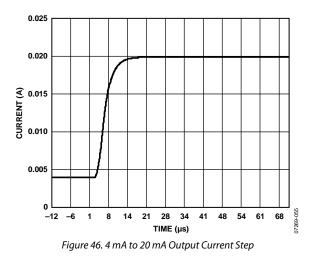

| 4 mA to 20 mA, Full-Scale Step        |              | 8.5           |                         | μs         | 250 Ω load                                                                                         |

| 120 µA Step, 4 mA to 20 mA Range      |              | 1.2           |                         | μs         | 250 Ω load                                                                                         |

| DC PSRR                               |              |               | 1                       | μA/V       |                                                                                                    |

| Output Impedance                      |              | 130           |                         | MΩ         |                                                                                                    |

| DIGITAL INPUTS <sup>₄</sup>           |              |               |                         |            | JEDEC compliant                                                                                    |

| Input High Voltage, V⊩                | 2            |               |                         | V          |                                                                                                    |

| Input Low Voltage, V⊾                 |              |               | 0.8                     | V          |                                                                                                    |

| Input Current                         | -1           |               | +1                      | μA         | Per pin                                                                                            |

| Pin Capacitance                       |              | 5             |                         | pF         | Per pin                                                                                            |

| DIGITAL OUTPUTS <sup>4</sup>          |              |               |                         |            |                                                                                                    |

| FAULT, IFAULT, TEMP, VFAULT           |              |               |                         |            |                                                                                                    |

| V <sub>OL</sub> , Output Low Voltage  |              |               | 0.4                     | V          | 10 kΩ pull-up resistor to DVCC                                                                     |

|                                       |              | 0.6           |                         | V          | At 2.5 mA                                                                                          |

| V <sub>он</sub> , Output High Voltage | 3.6          |               |                         | V          | 10 kΩ pull-up resistor to DVCC                                                                     |

| SDO                                   |              |               |                         |            |                                                                                                    |

| Vol, Output Low Voltage               | 0.5          | 0.5           |                         | V          | Sinking 200 μA                                                                                     |

| V <sub>он</sub> , Output High Voltage | DVCC - 0.5   | DVCC – 0.5    |                         | V          | Sourcing 200 µA                                                                                    |

| High Impedance Output<br>Capacitance  |              | 3             |                         | pF         |                                                                                                    |

| High Impedance Leakage Current        | -1           |               | +1                      | μA         |                                                                                                    |

| POWER REQUIREMENTS                    | 1            |               |                         | T          |                                                                                                    |

| AV <sub>DD</sub>                      | 10.8         |               | 55                      | V          |                                                                                                    |

| DVcc                                  |              |               |                         |            |                                                                                                    |

| Input Voltage                         | 2.7          |               | 5.5                     | V          |                                                                                                    |

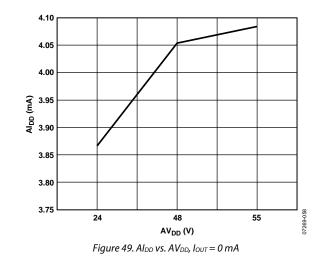

| Aldd                                  |              | 4.4           | 5.6                     | mA         | Output unloaded, output disabled                                                                   |

|                                       |              | 5.2           | 6.2                     | mA         | Current output enabled                                                                             |

|                                       |              | 5.2           | 6.2                     | mA         | Voltage output enabled                                                                             |

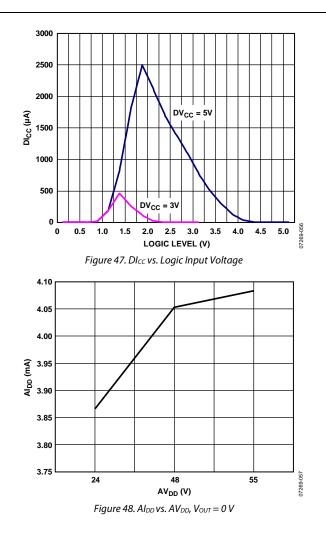

| Dlcc                                  |              | 0.3           | 1                       | mA         | $V_{IH} = DVCC, V_{IL} = GND$                                                                      |

| Power Dissipation                     |              | 108           |                         | mW         | AVDD = 24 V, outputs unloaded                                                                      |

<sup>1</sup> Temperature range: -40°C to +105°C; typical at +25°C.

<sup>2</sup> Overranges are nominal; gain and offset are not trimmed as per nominal ranges.

<sup>3</sup> Specification includes gain and offset errors, over temperature, and drift after 1000 hours, T<sub>A</sub> = 125°C.

<sup>4</sup> Guaranteed by characterization, but not production tested.

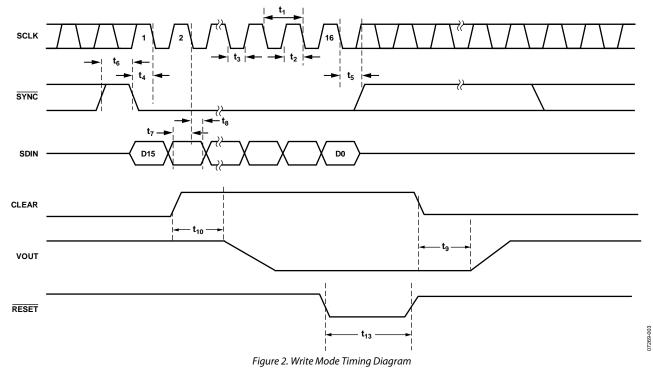

#### **TIMING CHARACTERISTICS**

$AV_{DD}$  = 12 V (± 10%) to 55 V (maximum),  $DV_{CC}$  = 2.7 V to 5.5 V, GND = 0 V. VOUT:  $R_{LOAD}$  = 2 k $\Omega$  (5 k $\Omega$  for 0 V to 40 V range),  $C_L$  = 200 pF, IOUT:  $R_{LOAD}$  = 300  $\Omega$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 3.                  |                                              |        |                                                                                                             |  |

|---------------------------|----------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------|--|

| Parameter <sup>1, 2</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                                 |  |

| t <sub>1</sub>            | 20                                           | ns min | SCLK cycle time                                                                                             |  |

| t <sub>2</sub>            | 8                                            | ns min | SCLK high time                                                                                              |  |

| t <sub>3</sub>            | 8                                            | ns min | SCLK low time                                                                                               |  |

| t4                        | 5                                            | ns min | SYNC falling edge to SCLK falling edge setup time                                                           |  |

| t <sub>5</sub>            | 10                                           | ns min | 16 <sup>th</sup> SCLK falling edge to SYNC rising edge (on 24 <sup>th</sup> SCLK falling edge if using PEC) |  |

| t <sub>6</sub>            | 5                                            | ns min | Minimum SYNC high time (write mode)                                                                         |  |

| t7                        | 5                                            | ns min | Data setup time                                                                                             |  |

| t <sub>8</sub>            | 5                                            | ns min | Data hold time                                                                                              |  |

| <b>t</b> 9, <b>t</b> 10   | 1.5                                          | µs max | CLEAR pulse low/high activation time                                                                        |  |

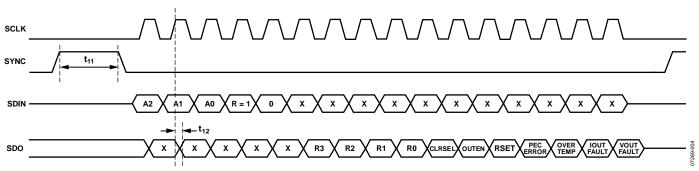

| t11                       | 5                                            | ns min | Minimum SYNC high time (read mode)                                                                          |  |

| <b>t</b> <sub>12</sub>    | 40                                           | ns max | SCLK rising edge to SDO valid (SDO $C_L = 15 \text{ pF}$ )                                                  |  |

| <b>t</b> <sub>13</sub>    | 10                                           | ns min | RESET pulse low time                                                                                        |  |

$^1$  Guaranteed by characterization, but not production tested.  $^2$  All input signals are specified with  $t_R$  =  $t_F$  = 5 ns (10% to 90% of DV<sub>CC</sub>) and timed from a voltage level of 1.2 V.

#### **Timing Diagrams**

Figure 3. Readback Mode Timing Diagram

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 4.

| Parameter                       | Rating                                                            |

|---------------------------------|-------------------------------------------------------------------|

| AVDD to GND                     | –0.3 V to +58 V                                                   |

| DVCC to GND                     | –0.3 V to +7 V                                                    |

| Digital Inputs to GND           | –0.3 V to DV <sub>cc</sub> + 0.3 V, or 7 V<br>(whichever is less) |

| Digital Outputs to GND          | –0.3 V to DV <sub>cc</sub> + 0.3 V, or 7 V<br>(whichever is less) |

| VREF to GND                     | –0.3 V to +7 V                                                    |

| VSENSE+ to GND                  | –0.3 V to AV <sub>DD</sub>                                        |

| VIN to GND                      | –0.3 V to +7 V                                                    |

| VOUT, IOUT to GND               | -0.3 V to AV <sub>DD</sub>                                        |

| Operating Temperature Range     |                                                                   |

| Industrial                      | –40°C to +105°C                                                   |

| Storage Temperature Range       | –65°C to +150°C                                                   |

| Junction Temperature (TJ max)   | 125°C                                                             |

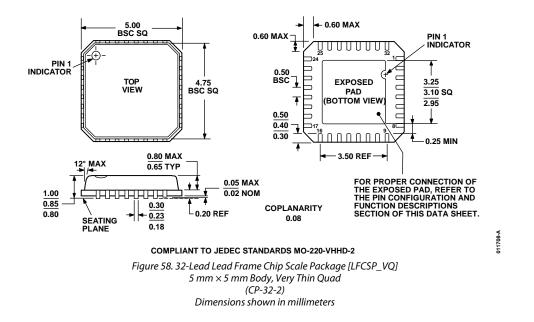

| 32-Lead LFCSP Package           |                                                                   |

| $\theta_{JA}$ Thermal Impedance | 28°C/W                                                            |

| Lead Temperature                | JEDEC industry standard                                           |

| Soldering                       | J-STD-020                                                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

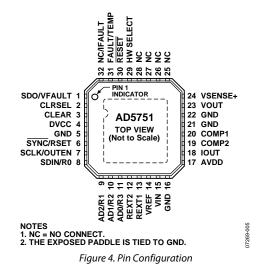

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                  |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SDO/VFAULT | Serial Data Output (SDO). In software mode, this pin is used to clock data from the input shift register in readback mode. Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK. This pin is a CMOS output.               |

|         |            | Short-Circuit Fault Alert (VFAULT). In hardware mode, this pin acts as a short-circuit fault alert pin and is<br>asserted low when a short-circuit error is detected. This pin is an open-drain output and must be<br>connected to a pull-up resistor.       |

| 2       | CLRSEL     | In hardware or software mode, this pin selects the clear value, either zero-scale or midscale code. In software mode, this pin is implemented as a logic OR with the internal CLRSEL bit.                                                                    |

| 3       | CLEAR      | Active High Input. Asserting this pin sets the output current/voltage to zero-scale code or midscale code of range selected (user-selectable). CLEAR is a logic OR with the internal clear bit. See the Asynchronous Clear (CLEAR) section for more details. |

|         |            | In software mode, during power-up, the CLEAR pin level determines the power-on condition of the voltage channel, which can be active 0 V or tristate.                                                                                                        |

| 4       | DVCC       | Digital Power Supply.                                                                                                                                                                                                                                        |

| 5       | GND        | Ground Connection.                                                                                                                                                                                                                                           |

| 6       | SYNC/RSET  | Positive Edge-Sensitive Latch (SYNC). In software mode, a rising edge parallel loads the input shift register data into the AD5751, also updating the output.                                                                                                |

|         |            | Resistor Select (RSET). In hardware mode, this pin selects whether the internal or the external current sense resistor is used.                                                                                                                              |

|         |            | If RSET = 0, the external sense resistor is chosen.                                                                                                                                                                                                          |

|         |            | If RSET = 1, the internal sense resistor is chosen.                                                                                                                                                                                                          |

| 7       | SCLK/OUTEN | Serial Clock Input (SCLK). In software mode, data is clocked into the input shift register on the falling edge of SCLK. This pin operates at clock speeds up to 50 MHz.                                                                                      |

|         |            | Output Enable (OUTEN). In hardware mode, this pin acts as an output enable pin.                                                                                                                                                                              |

| 8       | SDIN/R0    | Serial Data Input (SDIN). In software mode, data must be valid on the falling edge of SCLK.                                                                                                                                                                  |

|         |            | Range Decode Bit (R0). In hardware mode, this pin, in conjunction with R1, R2, and R3, selects the output current/voltage range setting on the part.                                                                                                         |

| 9       | AD2/R1     | Device Addressing Bit (AD2). In software mode, this pin, in conjunction with AD0 and AD1, allows up to eight devices to be addressed on one bus.                                                                                                             |

|         |            | Range Decode Bit (R1). In hardware mode, this pin, in conjunction with R0, R2, and R3, selects the output current/voltage range setting on the part.                                                                                                         |

| Pin No.        | Mnemonic       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10             | AD1/R2         | Device Addressing Bit (AD1). In software mode, this pin, in conjunction with AD0 and AD2, allows up to eight devices to be addressed on one bus.                                                                                                                                                                                                                                                                                                         |

|                |                | Range Decode Bit (R2). In hardware mode, this pin, in conjunction with R0, R1, and R3, selects the output current/voltage range setting on the part.                                                                                                                                                                                                                                                                                                     |

| 11             | AD0/R3         | Device Addressing Bit (AD0). In software mode, this pin, in conjunction with AD1 and AD2, allows up to eight devices to be addressed on one bus.                                                                                                                                                                                                                                                                                                         |

|                |                | Range Decode Bit (R3). In hardware mode, this pin, in conjunction with R0, R1, and R2, selects the output current/voltage range setting on the part.                                                                                                                                                                                                                                                                                                     |

| 12, 13         | REXT2, REXT1   | A 15 k $\Omega$ external current setting resistor can be connected between the REXT1 and REXT2 pins to improve the IOUT temperature drift performance.                                                                                                                                                                                                                                                                                                   |

| 14             | VREF           | Buffered Reference Input.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15             | VIN            | Buffered Analog Input (0 V to 4.096 V).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16             | GND            | Ground Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17             | AVDD           | Positive Analog Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18             | IOUT           | Current Output.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19, 20         | COMP2, COMP1   | Optional Compensation Capacitor Connections for the Voltage Output Buffer. These are used to drive<br>higher capacitive loads on the output. These pins also reduce overshoot on the output. Care should be<br>taken when choosing the value of the capacitor connected between the COMP1 and COMP2 pins<br>because it has a direct influence on the settling time of the output. See the Driving Large Capacitive<br>Loads section for further details. |

| 21             | GND            | Ground Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22             | GND            | Ground Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23             | VOUT           | Buffered Analog Output Voltage.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24             | VSENSE+        | Sense Connection for the Positive Voltage Output Load Connection.                                                                                                                                                                                                                                                                                                                                                                                        |

| 25, 26, 27, 28 | NC             | No Connect. Can be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 29             | HW SELECT      | This part is used to configure the part to hardware or software mode.<br>HW SELECT = 0 selects software control.<br>HW SELECT = 1 selects hardware control.                                                                                                                                                                                                                                                                                              |

| 30             | RESET          | In software mode, this pin resets the part to its power-on state. Active low.                                                                                                                                                                                                                                                                                                                                                                            |

|                |                | In hardware mode, there is no reset. If using the part in hardware mode, the RESET pin should be tied high.                                                                                                                                                                                                                                                                                                                                              |

| 31             | FAULT/TEMP     | Fault Alert (FAULT). In software mode, this pin acts as a general fault alert pin. It is asserted low when an open-circuit, short-circuit, overtemperature error, or PEC interface error is detected. This pin is an open-drain output and must be connected to a pull-up resistor.                                                                                                                                                                      |

|                |                | Overtemperature Fault (TEMP). In hardware mode, this pin acts as an overtemperature fault pin. It is asserted low when an overtemperature error is detected. This pin is an open-drain output and must be connected to a pull-up resistor.                                                                                                                                                                                                               |

| 32             | NC/IFAULT      | No Connect (NC). In software mode, this pin is a no connect. Instead, tie this pin to GND.                                                                                                                                                                                                                                                                                                                                                               |

|                |                | Open-Circuit Fault Alert (IFAULT). In hardware mode, this pin acts as an open-circuit fault alert pin. It is asserted low when an open-circuit error is detected. This pin is an open-drain output and must be connected to a pull-up resistor.                                                                                                                                                                                                          |

| 33 (EPAD)      | Exposed paddle | The exposed paddle is tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                       |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

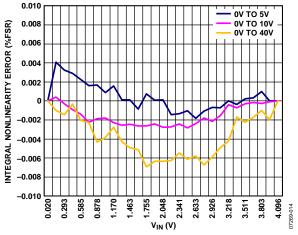

Figure 5. Integral Nonlinearity Error vs. V<sub>IN</sub>

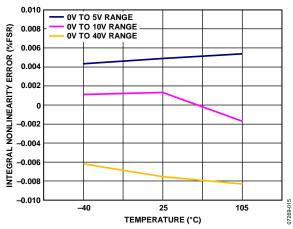

Figure 6. Integral Nonlinearity Error vs. Temperature

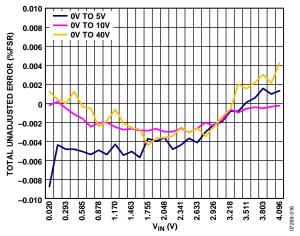

Figure 7. Total Unadjusted Error vs. V<sub>IN</sub>

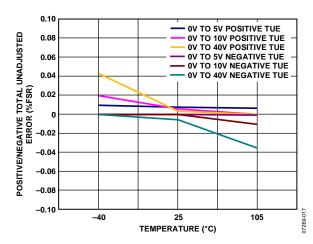

Figure 8. Total Unadjusted Error vs. Temperature

Figure 10. Gain Error vs. Temperature

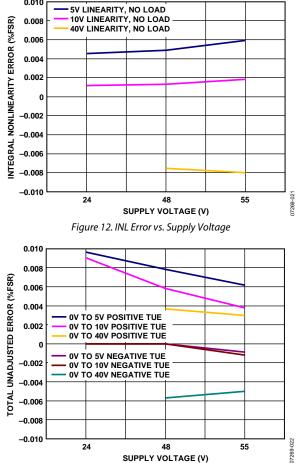

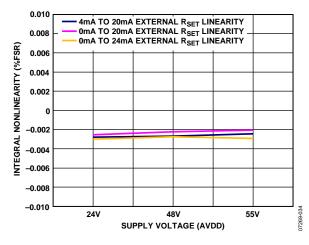

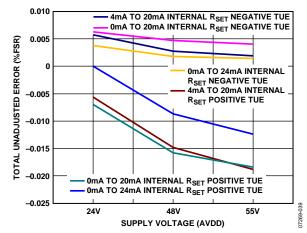

Figure 13. Total Unadjusted Error vs. Supply Voltage

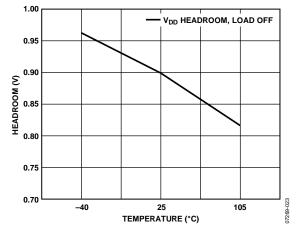

Figure 14. AVDD Headroom, 0 V to 10 V Range, Output Set to 10 V, Load Off

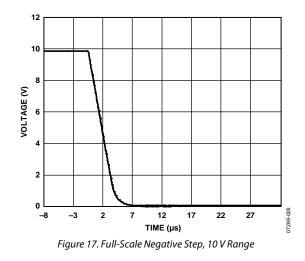

Figure 16. Full-Scale Positive Step, 10 V Range

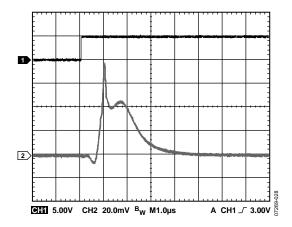

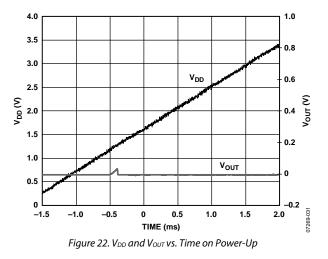

Figure 18.  $V_{OUT}$  vs. Time on Power-Up, Load =  $2 k\Omega \parallel 200 pF$

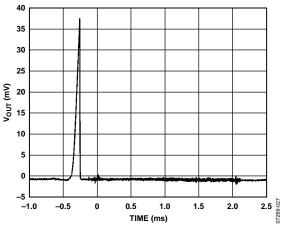

Figure 19.  $V_{OUT}$  Enable Glitch, Load = 2 k $\Omega \parallel 1$  nF

Figure 20. Peak-to-Peak Noise (0.1 Hz to 10 Hz Bandwidth)

Figure 21. Peak-to-Peak Noise (100 kHz Bandwidth)

#### **CURRENT OUTPUT**

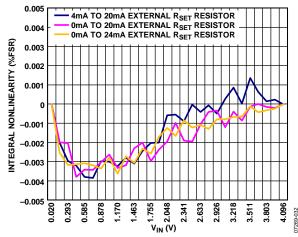

Figure 23. Integral Nonlinearity Error vs. VIN, External RSET Resistor

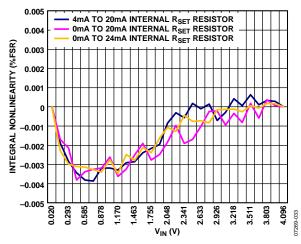

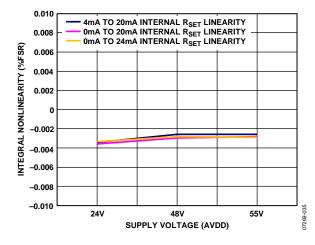

Figure 24. Integral Nonlinearity Error vs. VIN, Internal RSET Resistor

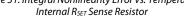

Figure 25. Integral Nonlinearity Current Mode, External RSET Sense Resistor

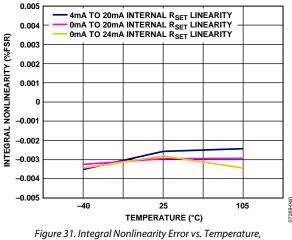

Figure 26. Integral Nonlinearity Current Mode, Internal RSET Sense Resistor

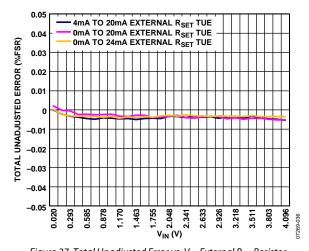

Figure 27. Total Unadjusted Error vs. VIN, External R<sub>SET</sub> Resistor

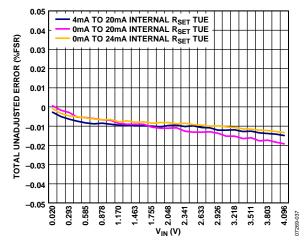

Figure 28. Total Unadjusted Error vs. VIN, Internal RSET Resistor

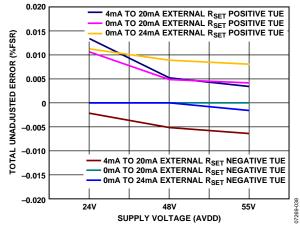

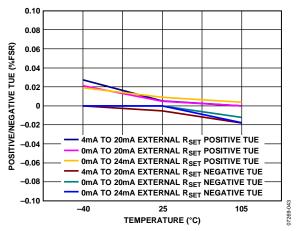

Figure 29. Total Unadjusted Error Current Mode, External RSET Sense Resistor

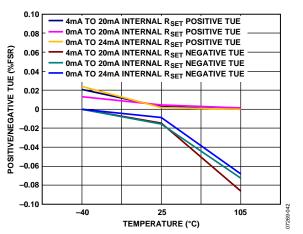

Figure 30. Total Unadjusted Error Current Mode, Internal RSET Sense Resistor

Figure 32. Integral Nonlinearity Error vs. Temperature, External R<sub>SET</sub> Sense Resistor

Figure 33. Total Unadjusted Error vs. Temperature, Internal R<sub>SET</sub> Sense Resistor

Figure 34. Total Unadjusted Error vs. Temperature, External R<sub>SET</sub> Sense Resistor

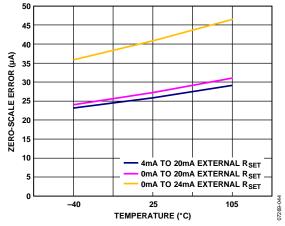

Figure 35. Zero-Scale Error vs. Temperature, External RSET Sense Resistor

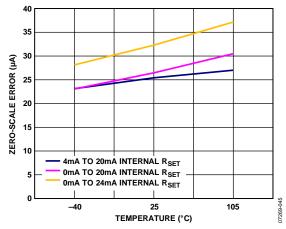

Figure 36. Zero-Scale Error vs. Temperature, Internal R<sub>SET</sub> Sense Resistor

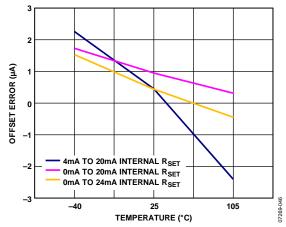

Figure 37. Offset Error vs. Temperature, Internal RSET Sense Resistor

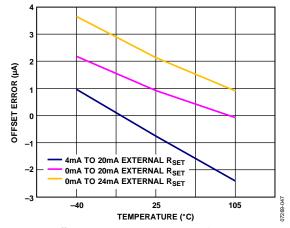

Figure 38. Offset Error vs. Temperature, External RSET Sense Resistor

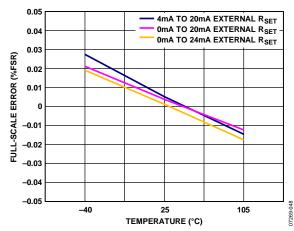

Figure 39. Full-Scale Error vs. Temperature, External RSET Sense Resistor

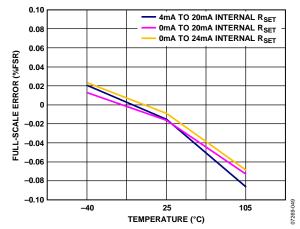

Figure 40. Full-Scale Error vs. Temperature, Internal R<sub>SET</sub> Sense Resistor

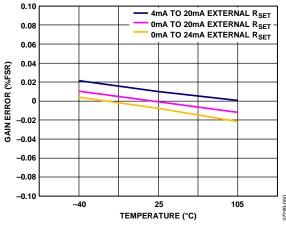

Figure 41. Gain Error vs. Temperature, External R<sub>SET</sub> Sense Resistor

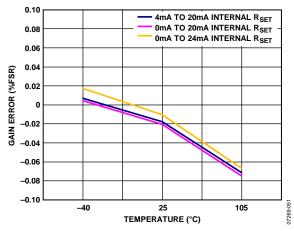

Figure 42. Gain Error vs. Temperature, Internal R<sub>SET</sub> Sense Resistor

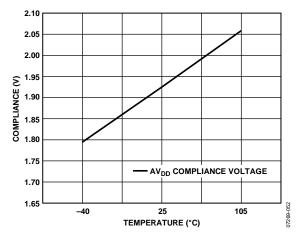

Figure 43. Output Compliance vs. Temperature Tested When  $I_{OUT} = 10.8$  mA, 0 mA to 24 mA Range Selected

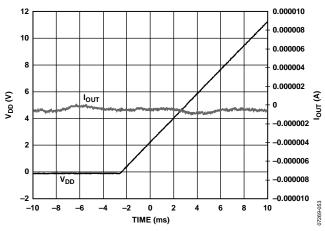

Figure 44. Output Current vs. Time on VDD Power-Up

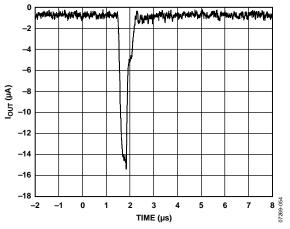

Figure 45. Output Current vs. Time on Output Enable, 0 mA to 20 mA Range

### **TERMINOLOGY**

#### Total Unadjusted Error (TUE)

TUE is a measure of the output error taking all the various errors into account: INL error, offset error, gain error, and output drift over supplies, temperature, and time. TUE is expressed as a percentage of full-scale range (% FSR).

#### Relative Accuracy or Integral Nonlinearity (INL)

INL is a measure of the maximum deviation, in % FSR, from a straight line passing through the endpoints of the output driver transfer function. A typical INL vs. input voltage plot is shown in Figure 5.

#### **Full-Scale Error**

Full-scale error is the deviation of the actual full-scale analog output from the ideal full-scale output. Full-scale error is expressed as a percentage of full-scale range (% FSR).

#### Full-Scale TC

Full-scale TC is a measure of the change in the full-scale error with a change in temperature. It is expressed in ppm FSR/°C.

#### **Gain Error**

Gain error is a measure of the span error of the output. It is the deviation in slope of the output transfer characteristic from the ideal expressed in % FSR. A plot of gain error vs. temperature is shown in Figure 10.

#### **Gain Error TC**

Gain error TC is a measure of the change in gain error with changes in temperature. Gain error TC is expressed in ppm FSR/°C.

#### Zero-Scale Error

Zero-scale error is the deviation of the actual zero-scale analog output from the ideal zero-scale output. Zero-scale error is expressed in millivolts (mV).

#### Zero-Scale TC

Zero-scale TC is a measure of the change in zero-scale error with a change in temperature. Zero-scale error TC is expressed in ppm FSR/°C.

#### **Offset Error**

Offset error is a measurement of the difference between the actual VOUT and the ideal VOUT expressed in millivolts (mV) in the linear region of the transfer function. It can be negative or positive.

#### **Output Voltage Settling Time**

Output voltage settling time is the amount of time it takes for the output to settle to a specified level for a half-scale input change.

#### Slew Rate

The slew rate of a device is a limitation in the rate of change of the output voltage. The output slewing speed is usually limited by the slew rate of the amplifier used at its output. Slew rate is measured from 10% to 90% of the output signal and is expressed in  $V/\mu s$ .

#### **Current Loop Voltage Compliance**

Current loop voltage compliance is the maximum voltage at the IOUT pin for which the output current is equal to the programmed value.

#### **Power-On Glitch Energy**

Power-on glitch energy is the impulse injected into the analog output when the AD5751 is powered on. It is specified as the area of the glitch in nV-sec.

#### Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output is affected by changes in the power supply voltage.

### **THEORY OF OPERATION**

The AD5751 is a single-channel, low cost, precision, voltage/ current output driver with hardware or software programmable output ranges. The software ranges are configured via an SPI-/ MICROWIRE-compatible serial interface. The hardware ranges are programmed using the range pins (R0 to R3). The analog input to the AD5751 is provided from a low voltage, single-supply DAC (0 V to 4.096 V), which is internally conditioned to provide the desired output current/voltage range.

The output current range is programmable across three ranges: 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA. The voltage output is provided from a separate pin that can be configured to provide 0 V to 5 V, 0 V to 10 V, and 0 V to 40 V output ranges. An overrange of 20% is available on the 5 V and 10 V output voltage ranges, and of 10% on the 0 V to 40 V range. The VOUT and IOUT pins can be connected together. An overrange of 2% is available on the 0 mA to 20 mA, 0 mA to 24 mA, and 4 mA to 20 mA current ranges. The current and voltage outputs are available on separate pins. Only one output can be enabled at one time. The output range is selected by programming the R3 to R0 bits in the control register (see Table 7 and Table 8).

Figure 50 and Figure 51 show a typical configuration of AD5751 in software mode and in hardware mode, respectively, in an output module system. The HW SELECT pin chooses whether the part is configured in software or hardware mode. The analog input to the AD5751 is provided from a low voltage, single-supply DAC such as the AD506x or AD566x, which can provide an output range of 0 V to 4.096 V. The supply and reference for the DAC, as well as the reference for the AD5751, can be supplied from a reference such as the ADR392. The AD5751 can operate with a single supply up to 55 V.

#### SOFTWARE MODE

In current mode, software-selectable output ranges include 0 mA to 20 mA, 0 mA to 24 mA, or 4 mA to 20 mA.

In voltage mode, software-selectable output ranges include 0 V to 5 V, 0 V to 10 V, 0 V to 40 V.

Figure 50. Typical System Configuration in Software Mode (Pull-Up Resistors Not Shown for Open-Drain Outputs)

Figure 51. Typical System Configuration in Hardware Mode Using Internal DAC Reference (Pull-Up Resistors Not Shown for Open-Drain Outputs)

Table 6. Suggested Parts for Use with the AD5751

| DAC           | Reference           | Power                | Resolution/Accuracy | Description                                         |

|---------------|---------------------|----------------------|---------------------|-----------------------------------------------------|

| AD5660        | Internal            | ADP1720 <sup>1</sup> | 16-bit/12-bit       | Mid end system, single channel, internal reference  |

| AD5664R       | Internal            | N/A                  | 16-bit/12-bit       | Mid end system, quad channel, internal reference    |

| AD5668        | Internal            | N/A                  | 16-bit/12-bit       | Mid end system, octal channel, internal reference   |

| AD5060        | ADR434              | ADP1720              | 16-bit/16-bit       | High end system, single channel, external reference |

| AD5064/AD5066 | ADR434              | N/A                  | 16-bit/16-bit       | High end system, quad channel, external reference   |

| AD5662        | ADR392 <sup>2</sup> | ADR3922              | 16-bit/12-bit       | Mid end system, single channel, external reference  |

| AD5664        | ADR3922             | N/A                  | 16-bit/12-bit       | Mid end system, quad channel, external reference    |

$^{\rm 1}$  ADP1720 input range up to 28 V.

<sup>2</sup> ADR392 input range up to 15 V.

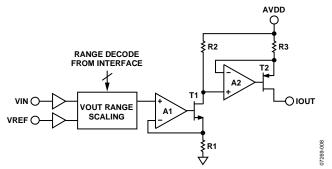

#### **CURRRENT OUTPUT ARCHITECTURE**

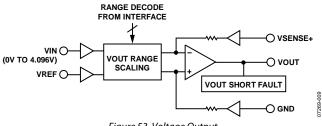

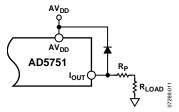

The voltage input from the analog input VIN core (0 V to 4.096 V) is either converted to a current (see Figure 52), which is then mirrored to the supply rail so that the application simply sees a current source output with respect to an internal reference voltage, or it is buffered and scaled to output a software-selectable unipolar voltage range (see Figure 53). The reference is used to provide internal offsets for range and gain scaling. The selectable output range is programmable through the digital interface (software mode) or via the range pins (R0 to R3) (hardware mode).

#### **DRIVING INDUCTIVE LOADS**

When driving inductive or poorly defined loads, connect a  $0.01 \,\mu\text{F}$  capacitor between IOUT and GND. This ensures stability with loads beyond 50 mH. There is no maximum capacitance limit. The capacitive component of the load may cause slower settling.

#### Voltage Output Amplifier

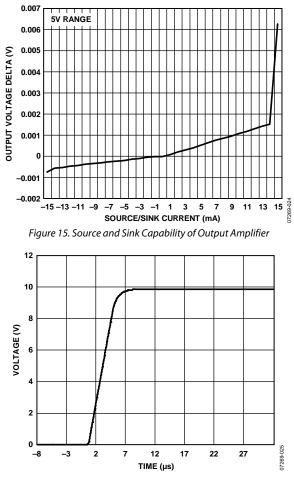

The voltage output amplifier is capable of driving a load of 1 k $\Omega$  (for 0 V to 5 V and 0 V to 10 V ranges) and a load of 5 k $\Omega$  (for 0 V to 40 V range) and capacitive loads up to 2  $\mu$ F (with an external compensation capacitor on the COMP1 and COMP2 pins). The source and sink capabilities of the output amplifier can be seen in Figure 15. The slew rate is 2 V/µs.

Internal to the device, there is a 2.5 M $\Omega$  resistor connected between VOUT and VSENSE+. If a fault condition occurs, these resistors act to protect the AD5751 by ensuring that the amplifier loop is closed so that the part does not enter into an open-loop condition.

The current and voltage are output on separate pins and cannot be output simultaneously. This allows the user to tie both the current and voltage output pins together and configure the end system as a single-channel output.

#### **Driving Large Capacitive Loads**

The voltage output amplifier is capable of driving capacitive loads of up to 1  $\mu F$  with the addition of a nonpolarized compensation capacitor between the COMP1 and COMP2 pins.

Without the compensation capacitor, up to 20 nF capacitive loads can be driven. Care should be taken to choose an appropriate value for the  $C_{COMP}$  capacitor. This capacitor, while allowing the AD5751 to drive higher capacitive loads and reduce overshoot, increases the settling time of the part and therefore affects the bandwidth of the system. Considered values of this capacitor should be in the range of 0 nF to 4 nF depending on the trade-off required between settling time, overshoot, and bandwidth.

#### **POWER-ON STATE OF THE AD5751**

On power-up, the AD5751 senses whether hardware or software mode is loaded and sets the power-up conditions accordingly.

In software SPI mode, the power-up state of the output is dependent on the state of the CLEAR pin. If the CLEAR pin is pulled high, the part powers up, driving an active 0 V on the output. If the CLEAR pin is pulled low, the part powers up with the voltage output channel in tristate mode. In both cases, the current output channel powers up in the tristate condition (0 mA). This allows the voltage and current outputs to be connected together if desired.

To put the part into normal operation, the user must set the OUTEN bit in the control register to enable the output and, in the same write, set the output range configuration using the R3 to R0 range bits. If the CLEAR pin is still high (active) during this write, the part automatically clears to its normal clear state as defined by the programmed range and by the CLRSEL pin or the CLRSEL bit (see the Asynchronous Clear (CLEAR) section for more details). The CLEAR pin must be taken low to operate the part in normal mode.

The CLEAR pin is typically driven directly from a microcontroller. In cases where the power supply for the AD5751 supply is independent of the microcontroller power supply, the user can connect a weak pull-up resistor to DVCC or a pull-down resistor to ground to ensure that the correct power-up condition is achieved independent of the microcontroller. A 10 k $\Omega$  pull-up/ pull-down resistor on the CLEAR pin should be sufficient for most applications.

If hardware mode is selected, the part powers up to the conditions defined by the R3 to R0 range bits and the status of the OUTEN or CLEAR pin. It is recommended to keep the output disabled when powering up the part in hardware mode.

#### **DEFAULT REGISTERS AT POWER-ON**

The AD5751 power-on-reset circuit ensures that all registers are loaded with zero code.

In software SPI mode, the part powers up with all outputs disabled (OUTEN bit = 0). The user must set the OUTEN bit in the control register to enable the output and, in the same write, set the output range configuration using the R3 to R0 bits.

If hardware mode is selected, the part powers up to the conditions defined by the R3 to R0 bits and the status of the OUTEN pin. It is recommended to keep the output disabled when powering up the part in hardware mode.

#### **RESET FUNCTION**

In software mode, the part can be reset using the  $\overrightarrow{\text{RESET}}$  pin (active low) or the reset bit (reset = 1). A reset disables both the current and voltage outputs to their power-on condition. The user must write to the OUTEN bit to enable the output and, in the same write, set the output range configuration. The  $\overrightarrow{\text{RESET}}$ pin is a level sensitive input; the part stays in reset mode as long as the  $\overrightarrow{\text{RESET}}$  pin is low. The reset bit clears to 0 following a reset command to the control register.

In hardware mode, there is no reset. If using the part in hardware mode, the  $\overrightarrow{\text{RESET}}$  pin should be tied high.

#### OUTEN

In software mode, the output can be enabled or disabled using the OUTEN bit in the control register. When the output is disabled, both the current and voltage channels go into tristate. The user must set the OUTEN bit to enable the output and simultaneously set the output range configuration.

In hardware mode, the output can be enabled or disabled using the OUTEN pin. When the output is disabled, both the current and voltage channels go into tristate. The user must write to the OUTEN pin to enable the output. It is recommended that the output be disabled when changing the ranges.

#### SOFTWARE CONTROL

Software control is enabled by connecting the HW SELECT pin to ground. In software mode, the AD5751 is controlled over a versatile 3-wire serial interface that operates at clock rates up to 50 MHz. It is compatible with SPI, QSPI<sup>™</sup>, MICROWIRE, and DSP standards.

#### Input Shift Register

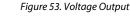

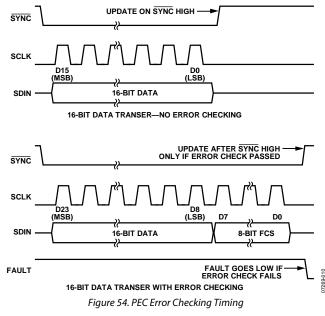

The input shift register is 16 bits wide. Data is loaded into the device MSB first as a 16-bit word under the control of a serial clock input, SCLK. Data is clocked in on the falling edge of SCLK. The input shift register consists of 16 control bits, as shown in Table 7. The timing diagram for this write operation is shown in Figure 2. The first three bits of the input shift register are used to set the hardware address of the AD5751 device on the printed circuit board (PCB). Up to eight devices can be addressed per board.

Bit D11, Bit D1, and Bit D0 must always be set to 0 during any write sequence.

Table 7. Input Shift Register Contents for a Write Operation—Control Register

MSB LSB D15 D14 D13 D10 D7 D6 D5 D4 D3 D2 D0 D12 D11 D9 **D8** D1 A2 A1 A0 R/W 0 R3 R2 R1 RO CLRSEL OUTEN Clear RSET Reset 0 0

Table 8. Input Shift Register Descriptions for Control Register

| Bit        | Descri                                                                                                                            | Description |    |                                                            |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|----|------------------------------------------------------------|--|--|--|--|--|

| A2, A1, A0 | Used in association with the AD2, AD1, and AD0 external pins to determine which part is being addressed by the system controller. |             |    |                                                            |  |  |  |  |  |

|            | A2                                                                                                                                | A1          | A0 | Function                                                   |  |  |  |  |  |

|            | 0                                                                                                                                 | 0           | 0  | Addresses part with Pin AD2 = 0, Pin AD1 = 0, Pin AD0 = 0. |  |  |  |  |  |

|            | 0                                                                                                                                 | 0           | 1  | Addresses part with Pin AD2 = 0, Pin AD1 = 0, Pin AD0 = 1. |  |  |  |  |  |

|            | 0                                                                                                                                 | 1           | 0  | Addresses part with Pin AD2 = 0, Pin AD1 = 1, Pin AD0 = 0. |  |  |  |  |  |

|            | 0                                                                                                                                 | 1           | 1  | Addresses part with Pin AD2 = 0, Pin AD1 = 1, Pin AD0 = 1. |  |  |  |  |  |

|            | 1                                                                                                                                 | 0           | 0  | Addresses part with Pin AD2 = 1, Pin AD1 = 0, Pin AD0 = 0. |  |  |  |  |  |

|            | 1                                                                                                                                 | 0           | 1  | Addresses part with Pin AD2 = 1, Pin AD1 = 0, Pin AD0 = 1. |  |  |  |  |  |

|            | 1                                                                                                                                 | 1           | 0  | Addresses part with Pin AD2 = 1, Pin AD1 = 1, Pin AD0 = 0. |  |  |  |  |  |

|            | 1                                                                                                                                 | 1           | 1  | Addresses part with Pin AD2 = 1, Pin AD1 = 1, Pin AD0 = 1. |  |  |  |  |  |

| R/W        | Indicates a read from or a write to the addressed register.                                                                       |             |    |                                                            |  |  |  |  |  |

| Bit            | Description                                                                                                                     |                                                                                       |                      |                                     |                                                                  |                                                                |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------|-------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| R3, R2, R1, R0 | Selects the output configuration in conjunction with RSET.                                                                      |                                                                                       |                      |                                     |                                                                  |                                                                |  |  |  |  |  |

|                | RSET                                                                                                                            | R3                                                                                    | R2                   | R1                                  | RO                                                               | Output Configuration                                           |  |  |  |  |  |