## DATASHEET

## TW6816

FN7753 Rev. 0.00 July 7, 2011

## 4-CH Audio/Video Decoders with 66MHz PCI Interface

#### **Features**

#### Video Decoder

- NTSC (M, 4.43) and PAL (B, D, G, H, I, M, N, N combination), PAL (60), SECAM support with automatic format detection

- Software selectable analog inputs allows any of 4 CVBS per one video ADC

- Four 10-bit ADCs and analog clamping circuit for CVBS

- Fully programmable static gain or automatic gain control for the Y channel

- Programmable white peak control for CVBS channel

- 4-H adaptive comb filter Y/C separation

- PAL delay line for color phase error correction

- Image enhancement with 2D peaking and CTI.

- Digital sub-carrier PLL for accurate color decoding

- Digital Horizontal PLL for synchronization processing and pixel sampling

- Advanced synchronization processing and sync detection for handling non-standard and weak signal

- Programmable hue, brightness, saturation, contrast, sharpness, Gamma control, and noise suppression

- Automatic color control and color killer

- Detection of level of copy protection according to Macrovision standard

- Programmable output cropping

#### Video Scaler

- High quality horizontal filtered scaling with arbitrary scale down ratio

- Phase accuracy better than 1/32 pixel

- Selectable anti-alias filter

#### **Audio Capture**

- Four 10-bit ADC for Analog Sound digitizing

- Programmable Sampling rate

#### **PCI**

- 66MHz/33MHz PCI with M66EN interface

- PCI Rev. 2.2-3.0 compliant

- ACPI support

- Integrated Video/Audio DMA controller

- Support both selectable one real-time video and 4x switching non real-time video

#### **Miscellaneous**

- Programmable RGB and YCbCr color space conversion

- 400Kbps Two-wire MPU serial bus Master interface

- Power-down mode

- Single 27MHz crystal for all standards

- 5V tolerant I/O

- 1.8 V power supply

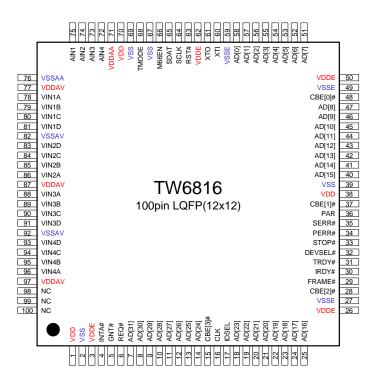

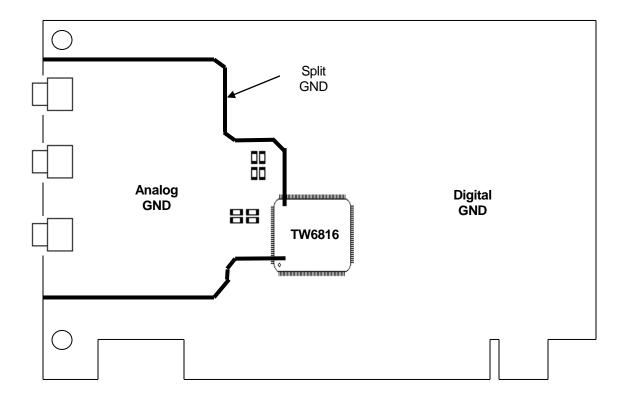

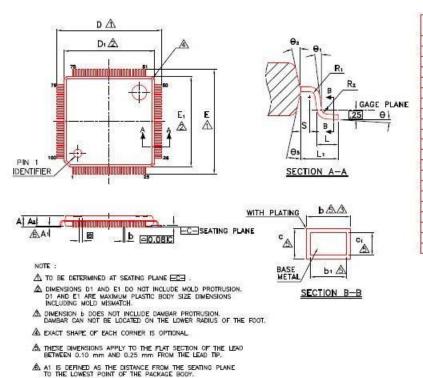

- 100-pin LQFP package

# **Function Description**

VIN1D RGB/YUV/ VIN1C Video FIFO Video YCbCr VIN1B 10-Bit ADC Decoder Format VIN1A Converter VIN2D RGB/YUV/ VIN2C Video YCbCr Video VIN2B 10-Bit ADC AGC HV Scaler DMA Decoder Format FIFO VIN2A Converte Video In VIN3D RGB/YUV/ VIN3C Video YCbCr Video VIN3B AGC 10-Bit ADC HV Scaler DMA Decoder Format FIFO VIN3A Converter VIN4D RGB/YUV/ VIN4C Video YCbCr Video VIN4B AGC 10-Bit ADC **HV** Scaler DMA Decoder Format FIFO VIN4A Converter PCI Bus PCI Interface Audio Gain Audio Decimation DMA AIN1 10-Bit ADC Format FIFO Control Filter Converter Audio Gain AIN2 10-Bit ADC DMA Format FIFO Control Filter Converter Audio Gain Decimation Audio AIN3 10-Bit ADC Format DMA Control Filter FIFO Converter Audio Gain Audio Decimation AIN4 10-Bit ADC Format DMA FIFO Control Filter Converter 2-wire Serial Bus 2-wire Serial Bus Master

Figure 1: TW6816 Block Diagram

# **Ordering Information**

| PART NUMBER   | PART            | PACKAGE                   |

|---------------|-----------------|---------------------------|

| (Note 1)      | MARKING         | (Pb-free)                 |

| TW6816-LA1-GR | TW6816 DALA1-GR | 100 LEAD LQFP (12mmx12mm) |

#### Note:

1. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# **Table of Contents**

| Function Description                                                              |                                                    |

|-----------------------------------------------------------------------------------|----------------------------------------------------|

| Ordering Information                                                              |                                                    |

| Video Decoder                                                                     |                                                    |

| Video Decoder Overview                                                            | 7                                                  |

| Analog Front-end                                                                  | 7                                                  |

| Sync Processing                                                                   | 8                                                  |

| Color Decoding                                                                    | 9                                                  |

| Component Processing                                                              | 11                                                 |

| Power Management                                                                  | 12                                                 |

| Down-scaling and Cropping                                                         |                                                    |

| Video Data Format Conversion                                                      | 15                                                 |

| GAMMA Correction                                                                  |                                                    |

|                                                                                   |                                                    |

| Byte Swapping                                                                     |                                                    |

| Color Formats                                                                     | 10                                                 |

| Serial BUS Interface                                                              |                                                    |

| Audio Processing                                                                  |                                                    |

| Audio Clock                                                                       | 18                                                 |

| Analog Audio Input                                                                |                                                    |

| PCI Interface                                                                     | 19                                                 |

| Interfacing to Serial EEPROM                                                      | 19                                                 |

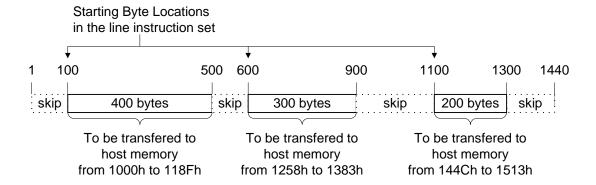

| DMA Controller Instructions                                                       |                                                    |

| Filter Curves                                                                     |                                                    |

| Filter Curves                                                                     |                                                    |

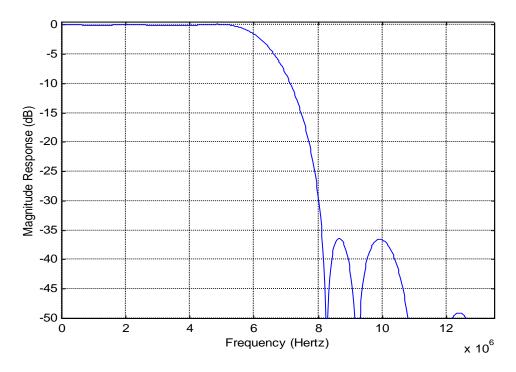

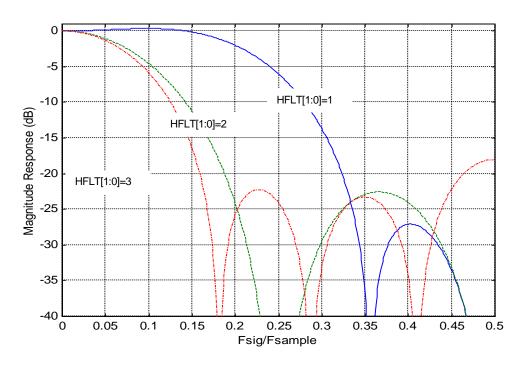

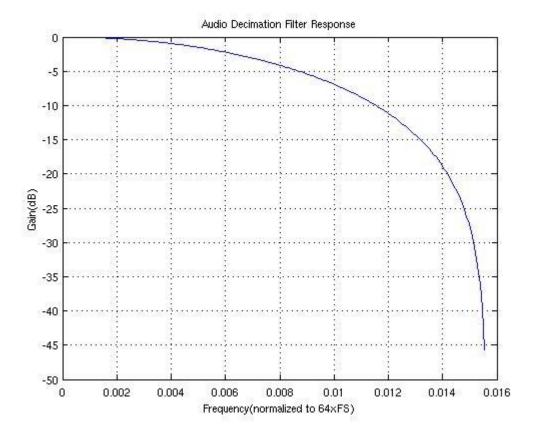

| Decimation filter                                                                 |                                                    |

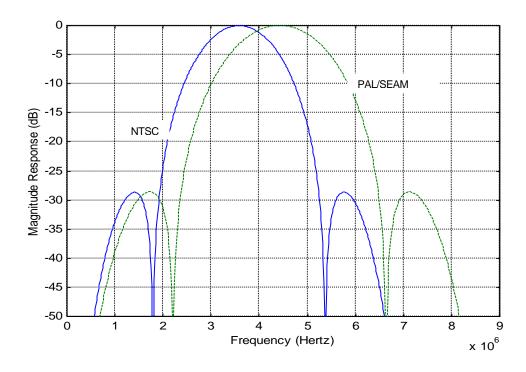

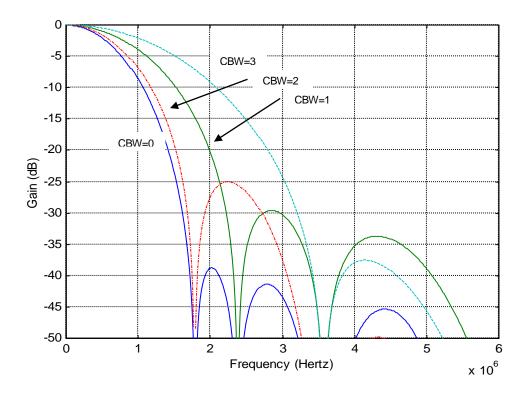

| Chroma Band Pass Filter Curves                                                    | 22                                                 |

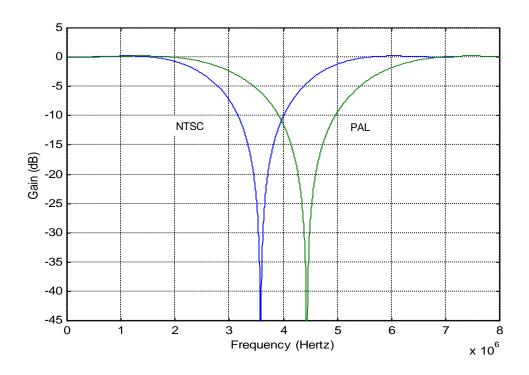

| Luma Notch Filter Curve for NTSC and PAL                                          |                                                    |

|                                                                                   |                                                    |

| Chrominance Low-Pass Filter Curve                                                 |                                                    |

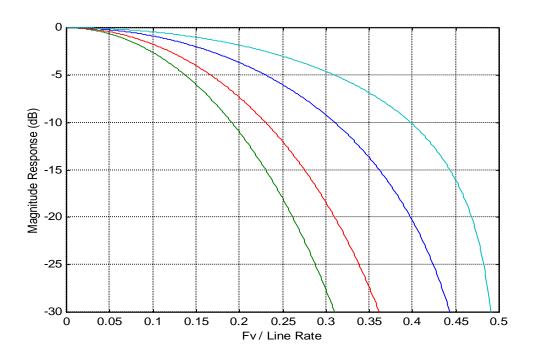

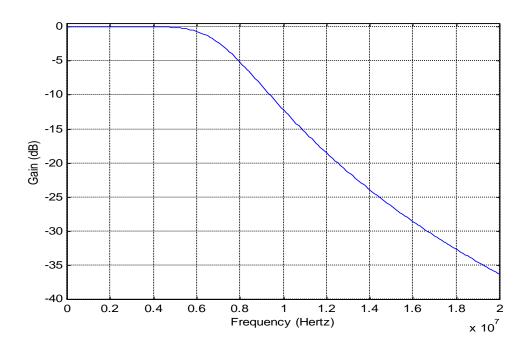

| Horizontal Scaler Pre- Filter Curves                                              |                                                    |

| Vertical Interpolation Filter Curves                                              |                                                    |

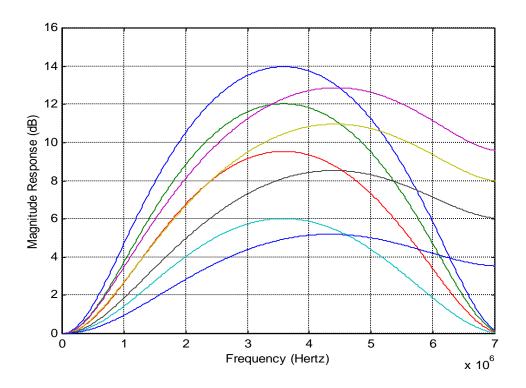

| Peaking Filter Curves                                                             |                                                    |

| Peaking Filter Curves                                                             |                                                    |

| Anti-aliasing Filter Curves                                                       |                                                    |

|                                                                                   | 26                                                 |

| Control Registers                                                                 | 20                                                 |

| Control Registers                                                                 | 26                                                 |

| Register Description                                                              | 26                                                 |

| Register DescriptionPCI Function 0/1/2/3 Configuration Space Registers for        | 26                                                 |

| Register DescriptionPCI Function 0/1/2/3 Configuration Space Registers for Video  | 26<br>27                                           |

| Register Description PCI Function 0/1/2/3 Configuration Space Registers for Video | 26<br>27<br>27                                     |

| Register Description PCI Function 0/1/2/3 Configuration Space Registers for Video | 26<br>27<br>27<br>27                               |

| Register Description                                                              | 26<br>27<br>27<br>27<br>28                         |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28                         |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28                         |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28                   |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28<br>28             |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28<br>28             |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28<br>28<br>28       |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29 |

| Register Description                                                              | 26<br>27<br>27<br>28<br>28<br>28<br>28<br>29<br>29 |

| Register Description                                                              | 2627272828282829293030                             |

| Register Description                                                              | 262727282828282929293031                           |

| Register Description                                                              | 262727282828282929293031                           |

| Register Description                                                              | 262727282828282929303131                           |

| Register Description                                                              | 262727282828282929303131                           |

| Register Description                                                              | 2627272828282829293031313636                       |

| Register Description                                                              | 262727282828282929303131313333                     |

| Register Description                                                              | 2627272828282829293031313637                       |

| Register Description                                                              | 2627272828282829293031363737                       |

| Register Description                                                              | 2627272828282929303131333737                       |

| Register Description                                                              | 2627272828282929303131333737                       |

| Register Description                                                              | 26272728282828293031313136373737                   |

| Register Description                                                              | 2627272828282829303131363737373337                 |

| Register Description                                                              | 2627272828282829293031313637373737373738           |

| Register Description                                                              | 262727282828282929303131363737373733733734034040   |

| Register Description                                                              | 26272728282829293031313737373737373940             |

| Register Description                                                              | 2627272828282929303131373737373737394041           |

| Register Description                                                              | 2627272828282929303131333737373737394141           |

| Register Description                                                              | 2627272828282929303131333737373737394141           |

| 0x054 - MR VIDEO SUBSYS43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x058 – DEVICE ID43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x058 - SUBSYSTEM ID43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x060 - VADCKPOL44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x064 – I2C RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x078 – M66EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x204 – Decoder Status Register 1 (STATUS1)44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x208 – Input Format (INFORM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x210 – GAMMA and HSYNC Delay Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x218 – Analog Control Register (ACNTL)46<br>0x21C – Cropping Register High (CROP_HI)46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x220 – Vertical Delay Register Low (VDELAY_LO)46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x224 – Vertical Delay Register Low (VDLLAT_LO)40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x228 – Horizontal Delay Register Low (HDELAY_LO)47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x22C – Horizontal Active Register Low (HACTIVE_LO) 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x230 – Control Register I (CNTRL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x234 - Vertical Scaling Register, Low (VSCALE_LO) 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x238 – Scaling Register High (SCALE_HI)48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x23C - Horizontal Scaling Register Low (HSCALE_LO)48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x240 - BRIGHTNESS Control Register (BRIGHT)49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x244 - CONTRAST Control Register (CONTRAST)49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x248 – SHARPNESS Control Register I (SHARPNESS)49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x24C - Chroma (U) Gain Register (SAT_U)49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x250 – Chroma (V) Gain Register (SAT_V)50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x254 – Hue Control Register (HUE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x25C – Vertical Sharpness (VSHARP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x268 – Analog Control II51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x270 – Standard Selection (SDT)51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x274 – Standard Selection (SDTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x278 – NT50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x280 – Clamping Gain (CLMPG)52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x284 – Individual AGC Gain (IAGC)53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x288 – AGC Gain (AGCGAIN)53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x28C – White Peak Threshold (PEAKWT)53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x290- Clamp level (CLMPL)53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x294- Sync Amplitude (SYNCT)53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x298 – Sync Miss Count Register (MISSCNT)54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x29C - Clamp Position Register (PCLAMP)54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A0 – Vertical Control I (VCNTL1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x248 — Color Killer Level Control (CKILL) 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x2A8 - Color Killer Level Control (CKILL)55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x2A8 – Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 – Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 – Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)       55         0x2AC - Comb Filter Control (COMB)       55         0x2B0 - Luma Delay and H Filter Control (LDLY)       55         0x2B4 - Miscellaneous Control I (MISC1)       55         0x2B8 - LOOP Control Register (LOOP)       56         0x2BC - Miscellaneous Control II (MISC2)       56         0x2C0 - Macrovision Detection (MVSN)       57         0x2C4 - Decoder Chip STATUS II (STATUS2)       58         0x2C8 - H Monitor (HFREF)       58         0x2CC - CLAMP MODE (CLMD)       58         0x2D0 - ID Detection Control (IDCNTL)       58         0x2D4 - Clamp Control I (CLCNTL1)       59                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2CC - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59                                                                                                                                                                                                                                                                                              |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60                                                                                                                                                                                                                         |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3BC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Vertical Active Low (F2VACTIVE_LO)         60                                                                                                                                                  |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Horizontal Delay Low (F2HDELAY_LO)         60                                                                                                                                                  |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Horizontal Delay Low (F2HDELAY_LO)         60           0x3EC - Field2 Horizontal Active Low (F2HACTIVE_LO)         60                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         56           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Horizontal Delay Low (F2HDELAY_LO)         60           0x3E5 - Field2 Horizontal Active Low (F2HACTIVE_LO)         60           0x3E7 - Field2 Control (F2CNT)         61                     |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         55           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Horizontal Delay Low (F2VACTIVE_LO)         60           0x3E5 - Field2 Horizontal Active Low (F2HACTIVE_LO)         61           0x3F4 - Field2 Vertical Scaling Low (F2VSCALE_LO)         61 |

| 0x2A8 - Color Killer Level Control (CKILL)         55           0x2AC - Comb Filter Control (COMB)         55           0x2B0 - Luma Delay and H Filter Control (LDLY)         55           0x2B4 - Miscellaneous Control I (MISC1)         56           0x2B8 - LOOP Control Register (LOOP)         56           0x2BC - Miscellaneous Control II (MISC2)         56           0x2C0 - Macrovision Detection (MVSN)         57           0x2C4 - Decoder Chip STATUS II (STATUS2)         58           0x2C8 - H Monitor (HFREF)         58           0x2C0 - CLAMP MODE (CLMD)         58           0x2D0 - ID Detection Control (IDCNTL)         58           0x2D4 - Clamp Control I (CLCNTL1)         59           0x3DC - Field2 Cropping High (F2CROP_HI)         59           0x3E0 - Field2 Vertical Delay Low (F2VDELAY_LO)         60           0x3E4 - Field2 Horizontal Delay Low (F2HDELAY_LO)         60           0x3E5 - Field2 Horizontal Active Low (F2HACTIVE_LO)         60           0x3E7 - Field2 Control (F2CNT)         61                     |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x2A8 - Color Killer Level Control (CKILL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |