# MIC2103/04

75V, Synchronous Buck Controllers featuring Adaptive On-Time Control

#### Hyper Speed Control<sup>™</sup> Family

### **General Description**

The Micrel MIC2103/04 are constant-frequency, synchronous buck controllers featuring a unique adaptive ON-time control architecture. The MIC2103/04 operates over an input supply range from 4.5V to 75V and can be used to supply up to 15A of output current. The output voltage is adjustable down to 0.8V with a guaranteed accuracy of  $\pm$ 1%. The device operates with programmable switching frequency from 200kHz to 600kHz.

Micrel's Hyper Light Load<sup>™</sup> architecture provides the same high-efficiency and ultra fast transient response as the Hyper Speed Control architecture under the medium to heavy loads, but also maintains high efficiency under light load conditions by transitioning to variable frequency, discontinuous-mode operation.

The MIC2103/04 offers a full suite of protection features to ensure protection of the IC during fault conditions. These include under-voltage lockout to ensure proper operation under power-sag conditions, internal soft-start to reduce inrush current, fold-back current limit, "hiccup" mode shortcircuit protection and thermal shutdown.

All support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

#### Features

- Hyper Speed Control architecture enables

- High delta V operation ( $V_{IN}$  = 75V and  $V_{OUT}$  = 1.2V)

- Any Capacitor<sup>TM</sup> stable

- 4.5V to 75V input voltage

- 0.8V Reference Voltage with ±1% accuracy

- 200kHz to 600kHz, programmable switching frequency

- Hyper Light Load Control (MIC2103 only)

- Hyper Speed Control (MIC2104 only)

- Enable input, Power-Good output

- Built-in 5V regulator for single-supply operation

- Programmable current limit and fold-back "hiccup" mode short-circuit protection

- 5ms internal soft-start, internal compensation, and thermal shutdown

- Supports safe start-up into a pre-biased output

- -40°C to +125°C junction temperature range

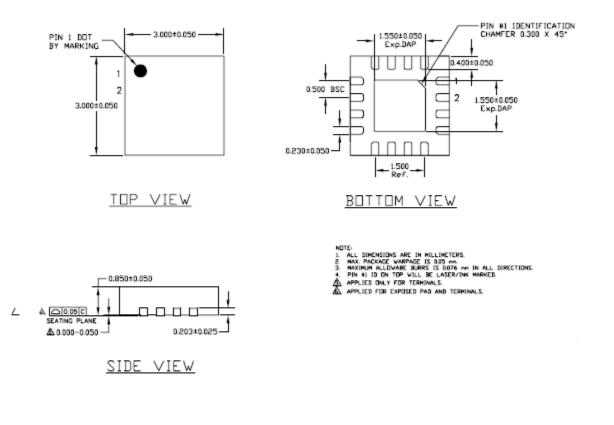

- Available in 16-pin 3mm x 3mm MLF<sup>®</sup> package

### Applications

- Distributed power systems

- Networking/Telecom Infrastructure

- Printers, scanners, graphic cards and video cards

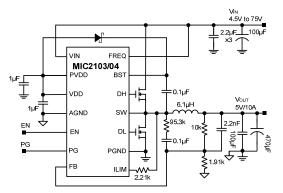

### **Typical Application**

Hyper Speed Control, Hyper Light Load and Any Capacitor are trademarks of Micrel, Inc. MLF and *Micro*LeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

### **Ordering Information**

| Part Number | Switching<br>Frequency | Features            | Package              | Junction<br>Temperature Range | Lead Finish |

|-------------|------------------------|---------------------|----------------------|-------------------------------|-------------|

| MIC2103YML  | 200kHz to 600kHz       | Hyper Light Load    | 16-pin 3mm x 3mm MLF | –40°C to +125°C               | Pb-Free     |

| MIC2104YML  | 200kHz to 600kHz       | Hyper Speed Control | 16-pin 3mm x 3mm MLF | –40°C to +125°C               | Pb-Free     |

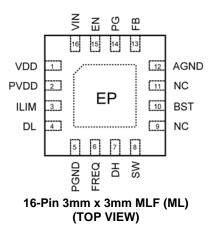

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDD      | Internal +5V linear regulator output. VDD is the internal supply bus for the device. A 1µF ceramic capacitor from VDD to AGND is required for decoupling. In the applications with VIN<+5.5V, VDD should be tied to VIN to by-pass the linear regulator.                                                                                                                                                                                                   |

| 2          | PVDD     | 5V supply input for the low-side N-channel MOSFET driver, which can be tied to VDD externally. A $1\mu$ F ceramic capacitor from PVDD to PGND is recommended for decoupling.                                                                                                                                                                                                                                                                               |

| 3          | ILIM     | Current Limit Setting. Connect a resistor from SW to ILIM to set the over-current threshold for the converter.                                                                                                                                                                                                                                                                                                                                             |

| 4          | DL       | Low-Side Drive output. High-current driver output for external low-side MOSFET of a buck converter. The DL driving voltage swings from ground to $V_{DD}$ . Adding a small resistor between DL pin and the gate of the low-side N-channel MOSFET can slow down the turn-on and turn-off speed of the MOSFET.                                                                                                                                               |

| 5          | PGND     | Power Ground. PGND is the return path for the buck converter power stage. The PGND pin connects to the sources of low-side N-Channel external MOSFET, the negative terminals of input capacitors, and the negative terminals of output capacitors. The return path for the power ground should be as small as possible and separate from the Signal ground (AGND) return path.                                                                             |

| 6          | FREQ     | Switching Frequency Adjust input. Tie this pin to VIN to operate at 600kHz and place a resistor divider to reduce the frequency.                                                                                                                                                                                                                                                                                                                           |

| 7          | DH       | High-Side Drive output. High-current driver output for external high-side MOSFET of a buck converter. The DH driving voltage is floating on the switch node voltage ( $V_{SW}$ ). Adding a small resistor between DH pin and the gate of the high-side N-channel MOSFET can slow down the turn-on and turn-off speed of the MOSFET.                                                                                                                        |

| 8          | SW       | Switch Node and Current-Sense input. High current output driver return. The SW pin connects directly to the switch node. Due to the high-speed switching on this pin, the SW pin should be routed away from sensitive nodes. The SW pin also senses the current by monitoring the voltage across the low-side MOSFET during OFF time. In order to sense the current accurately, connect the low-side MOSFET drain to the SW pin using a Kelvin connection. |

# Pin Description (Continued)

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                            |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 11      | NC       | No connection.                                                                                                                                                                                                                                                                                          |

| 10         | BST      | Voltage Supply Pin input for the high-side N-channel MOSFET driver, which can be powered by a bootstrapped circuit connected between VDD and SW, using a Schottky diode and a $0.1\mu$ F ceramic capacitor. Adding a small resistor at BST pin can slow down the turn-on speed of the high-side MOSFET. |

| 12         | AGND     | Signal ground for VDD and the control circuitry, which is connected to Thermal Pad electronically. The signal ground return path should be separate from the power ground (PGND) return path.                                                                                                           |

| 13         | FB       | Feedback input. Input to the transconductance amplifier of the control loop. The FB pin is regulated to 0.8V. A resistor divider connecting the feedback to the output is used to set the desired output voltage.                                                                                       |

| 14         | PG       | Power Good output. Open Drain Output, an external pull-up resistor to VDD or external power rails is required.                                                                                                                                                                                          |

| 15         | EN       | Enable input. A logic signal to enable or disable the buck converter operation. The EN pin is CMOS compatible. Logic high enables the device, logic low shutdowns the regulator. In the disable mode, the $V_{DD}$ supply current for the device is minimized to 0.7mA typically.                       |

| 16         | VIN      | Supply voltage. The VIN operating voltage range is from 4.5V to 75V. A 1µF ceramic capacitor from VIN to AGND is required for decoupling.                                                                                                                                                               |

| EP         | ePad     | Exposed Pad. Connect the EPAD to PGND plain on the PCB to improve the thermal performance.                                                                                                                                                                                                              |

# Absolute Maximum Ratings<sup>(1)</sup>

| V <sub>IN</sub><br>V <sub>DD</sub> , V <sub>PVDD</sub> |                                   |

|--------------------------------------------------------|-----------------------------------|

| $V_{SW}, V_{FREQ}, V_{ILIM}, V_{EN}$                   | –0.3V to (V <sub>IN</sub> +0.3V)  |

| $V_{BST}$ to $V_{SW}$                                  | –0.3V to 6V                       |

| V <sub>BST</sub>                                       | –0.3V to 82V                      |

| V <sub>PG</sub>                                        | –0.3V to (V <sub>DD</sub> + 0.3V) |

| V <sub>FB</sub>                                        | –0.3V to (V <sub>DD</sub> + 0.3V) |

| PGND to AGND                                           | –0.3V to +0.3V                    |

| Junction Temperature                                   | +150°C                            |

| Storage Temperature (T <sub>s</sub> )                  | 65°C to +150°C                    |

| Lead Temperature (soldering, 10sec).                   | 260°C                             |

| ESD Rating <sup>(2)</sup>                              | ESD Sensitive                     |

# Operating Ratings<sup>(3)</sup>

| Supply Voltage (V <sub>IN</sub> )                                        | 4.5V to 75V           |

|--------------------------------------------------------------------------|-----------------------|

| Enable Input (V <sub>EN</sub> )                                          | 0V to V <sub>IN</sub> |

| V <sub>SW</sub> , V <sub>FEQ</sub> , V <sub>ILIM</sub> , V <sub>EN</sub> | 0V to V <sub>IN</sub> |

| Junction Temperature (T <sub>J</sub> )                                   | –40°C to +125°C       |

| Junction Thermal Resistance                                              |                       |

| 3mm x 3mm MLF-16 (θ <sub>JA</sub> )                                      | 50.8°C/W              |

| 3mm x 3mm MLF-16 (θ <sub>JC</sub> )                                      | 25.3°C/W              |

# Electrical Characteristics<sup>(4)</sup>

$V_{IN} = 48V, V_{OUT} = 5V, V_{BST} - V_{SW} = 5V; T_A = 25^{\circ}C, unless noted. Bold values indicate -40^{\circ}C \le T_J \le +125^{\circ}C.$

| Parameter                                             | Condition                             | Min   | Тур | Max   | Units |

|-------------------------------------------------------|---------------------------------------|-------|-----|-------|-------|

| Power Supply Input                                    | ·                                     |       |     |       |       |

| Input Voltage Range (V <sub>IN</sub> ) <sup>(5)</sup> |                                       | 4.5   |     | 75    | V     |

| Quiescent Supply Current (MIC2103)                    | V <sub>FB</sub> = 1.5V                |       | 400 | 750   | μA    |

| Quiescent Supply Current (MIC2104)                    | V <sub>FB</sub> = 1.5V                |       | 2.1 | 3     | mA    |

| Shutdown Supply Current                               | SW unconnected, V <sub>EN</sub> = 0V  |       | 0.1 | 10    | μA    |

| VDD Supply                                            | ·                                     |       |     |       |       |

| VDD Output Voltage                                    | $V_{IN}$ = 7V to 75V, $I_{DD}$ = 10mA | 4.8   | 5.2 | 5.4   | V     |

| VDD UVLO Threshold                                    | V <sub>DD</sub> rising                | 3.8   | 4.2 | 4.6   | V     |

| VDD UVLO Hysteresis                                   |                                       |       | 400 |       | mV    |

| Load Regulation                                       | $I_{DD} = 0$ to 40mA                  | 0.6   | 2   | 3.6   | %     |

| Reference                                             |                                       |       |     |       |       |

| Foodbook Deference Vieltage                           | T <sub>J</sub> = 25°C (±1.0%)         | 0.792 | 0.8 | 0.808 | v     |

| Feedback Reference Voltage                            | -40°C ≤ T <sub>J</sub> ≤ 125°C (±2%)  | 0.784 | 0.8 | 0.816 |       |

| FB Bias Current                                       | V <sub>FB</sub> = 0.8V                |       | 5   | 500   | nA    |

| Enable Control                                        |                                       |       |     |       |       |

| EN Logic Level High                                   |                                       | 1.8   |     |       | V     |

| EN Logic Level Low                                    |                                       |       |     | 0.6   | V     |

| EN Hysteresis                                         |                                       |       | 200 |       | mV    |

| EN Bias Current                                       | V <sub>EN</sub> = 48V                 |       | 23  | 40    | μA    |

# **Electrical Characteristics**<sup>(4)</sup> (Continued)

$V_{\text{IN}} = 48 \text{V}, \text{ } V_{\text{OUT}} = 5 \text{V}, \text{ } V_{\text{BST}} - \text{V}_{\text{SW}} = 5 \text{V}; \text{ } T_{\text{A}} = 25^{\circ}\text{C}, \text{ } \text{unless noted}. \text{ } \textbf{Bold } \text{values indicate } -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq +125^{\circ}\text{C}.$

| Oscillator                           |                                             |                          |     |     |                   |

|--------------------------------------|---------------------------------------------|--------------------------|-----|-----|-------------------|

| Switching Frequency                  | V <sub>FREQ</sub> = V <sub>IN</sub>         | 400                      | 600 | 750 | - kHz             |

|                                      | V <sub>FREQ</sub> = 50%V <sub>IN</sub>      |                          | 300 |     | KIIZ              |

| Maximum Duty Cycle                   |                                             |                          | 85  |     | %                 |

| Minimum Duty Cycle                   | V <sub>FB</sub> > 0.8V                      |                          | 0   |     | %                 |

| Minimum Off-Time                     |                                             | 140                      | 200 | 260 | ns                |

| Soft Start                           |                                             |                          |     |     |                   |

| Soft-Start time                      |                                             |                          | 5   |     | ms                |

| Short Circuit Protection             | ·                                           |                          |     |     |                   |

| Current-Limit Threshold              | V <sub>FB</sub> = 0.79V                     | -30                      | -14 | 0   | mV                |

| Short-Circuit Threshold              | V <sub>FB</sub> = 0V                        | -23                      | -7  | 9   | mV                |

| Current-Limit Source Current         | V <sub>FB</sub> = 0.79V                     | 60                       | 80  | 100 | μA                |

| Short-Circuit Source Current         | V <sub>FB</sub> = 0V                        | 27                       | 36  | 47  | μA                |

| FET Drivers                          | ·                                           |                          |     |     | ·                 |

| DH, DL Output Low Voltage            | I <sub>SINK</sub> = 10mA                    |                          |     | 0.1 | V                 |

|                                      |                                             | V <sub>PVDD</sub> - 0.1V |     |     |                   |

| DH, DL Output High Voltage           | I <sub>SOURCE</sub> = 10mA                  | Or                       |     |     | V                 |

|                                      |                                             | V <sub>BST</sub> - 0.1V  |     |     |                   |

| DH On-Resistance, High State         |                                             |                          | 2.1 | 3.3 | Ω                 |

| DH On-Resistance, Low State          |                                             |                          | 1.8 | 3.3 | Ω                 |

| DL On-Resistance, High State         |                                             |                          | 1.8 | 3.3 | Ω                 |

| DL On-Resistance, Low State          |                                             |                          | 1.2 | 2.3 | Ω                 |

| SW, BST Leakage Current              |                                             |                          |     | 50  | μA                |

| Power Good                           |                                             |                          |     |     |                   |

| Power Good Threshold Voltage         | Sweep V <sub>FB</sub> from Low to High      | 85                       | 90  | 95  | %V <sub>OUT</sub> |

| Power Good Hysteresis                | Sweep $V_{FB}$ from High to Low             |                          | 6   |     | %V <sub>OUT</sub> |

| Power Good Delay Time                | Sweep V <sub>FB</sub> from Low to High      |                          | 100 |     | μs                |

| Power Good Low Voltage               | $V_{FB}$ < 90% x $V_{NOM}$ , $I_{PG}$ = 1mA |                          | 70  | 200 | mV                |

| Thermal Protection                   |                                             |                          |     | •   |                   |

| Over-Temperature Shutdown            | T <sub>J</sub> Rising                       |                          | 160 |     | °C                |

| Over-Temperature Shutdown Hysteresis |                                             |                          | 4   |     | °C                |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

3. The device is not guaranteed to function outside operating range.

4. Specification for packaged product only.

5. The application is fully functional at low  $V_{DD}$  (supply of the control section) if the external MOSFETs have low voltage  $V_{TH}$ .

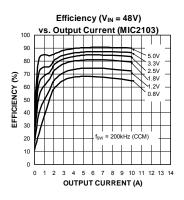

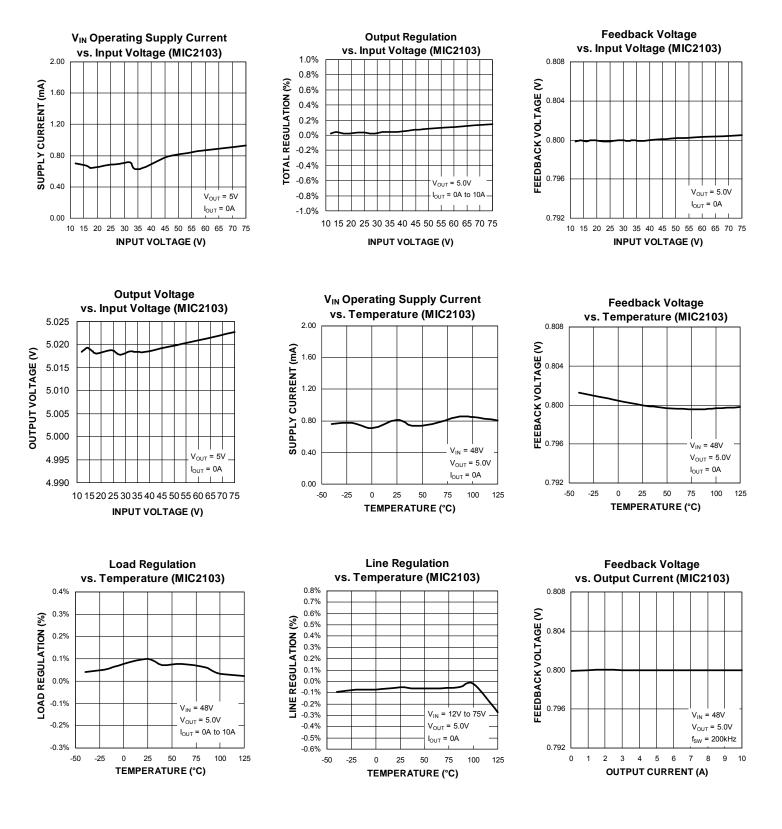

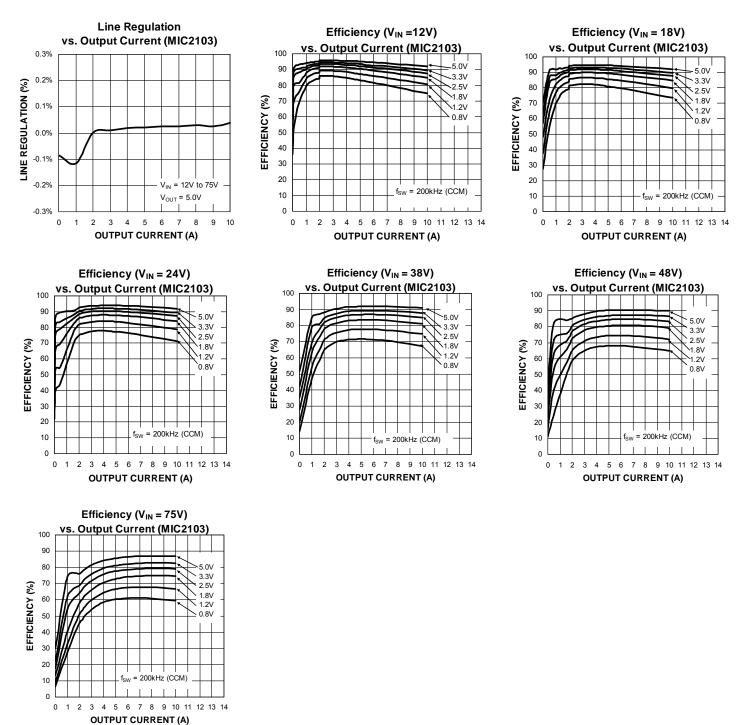

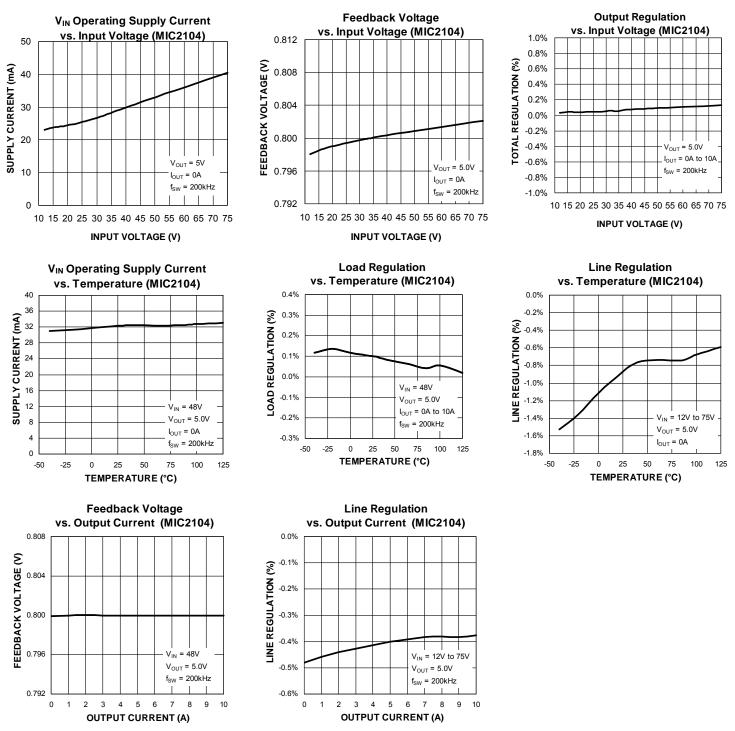

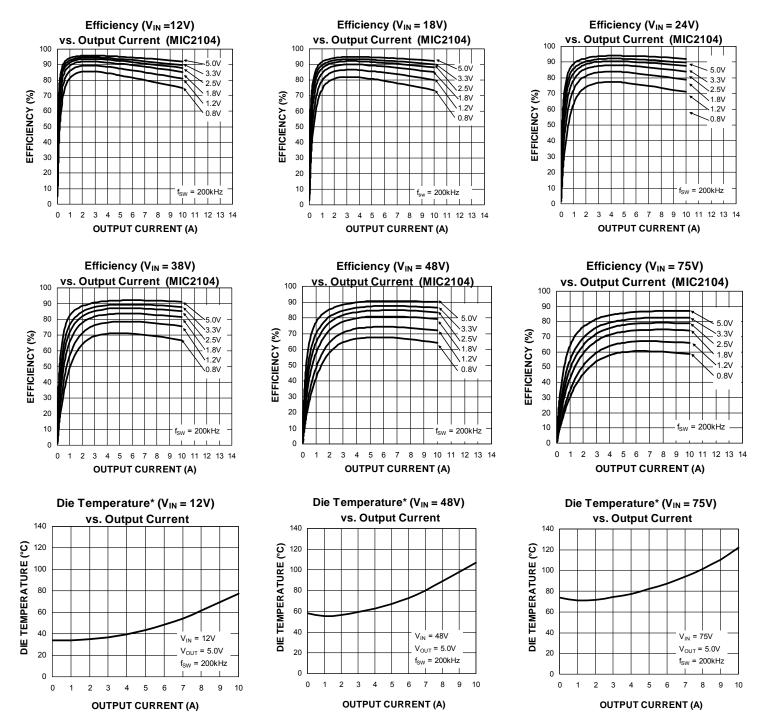

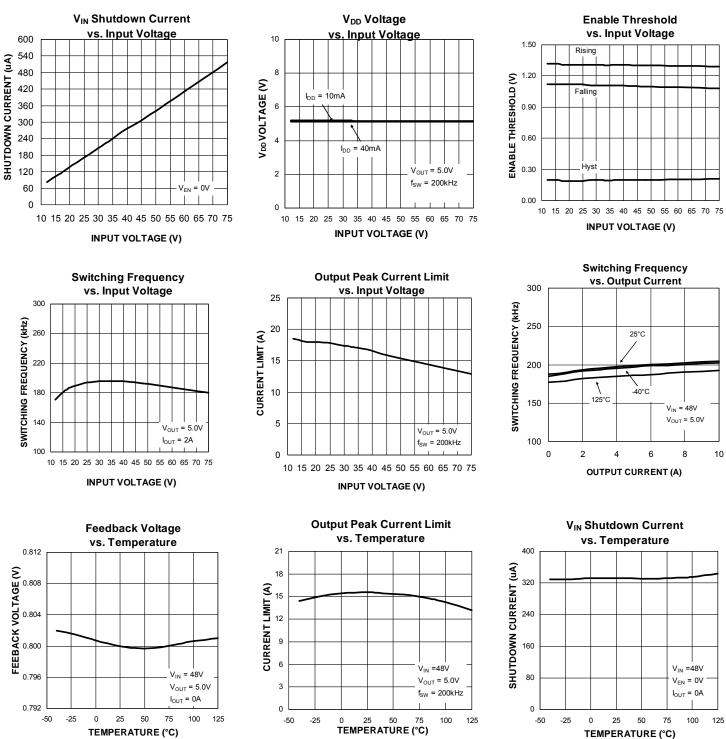

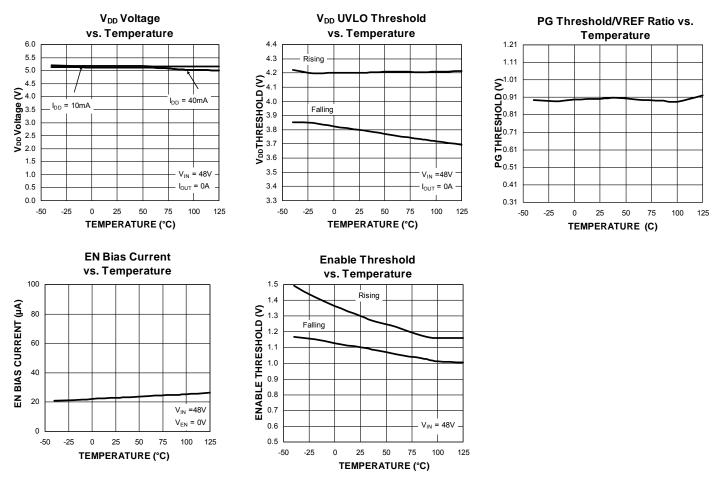

# **Typical Characteristics**

\* Case Temperature: The temperature measurement was taken at the hottest point on the MIC2103 case mounted on a 5 square inch PCB, see Thermal Measurement section. Actual results will depend upon the size of the PCB, ambient temperature and proximity to other heat emitting components.

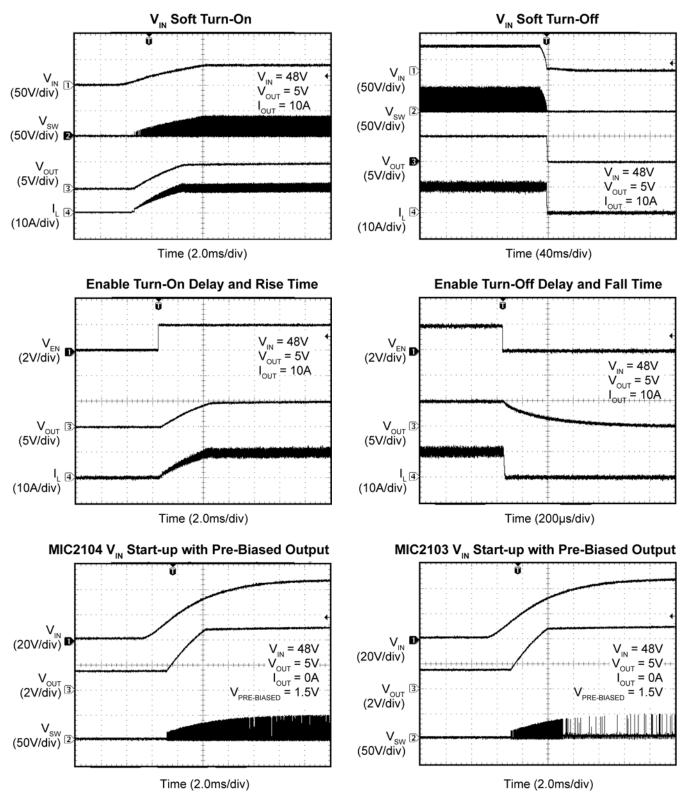

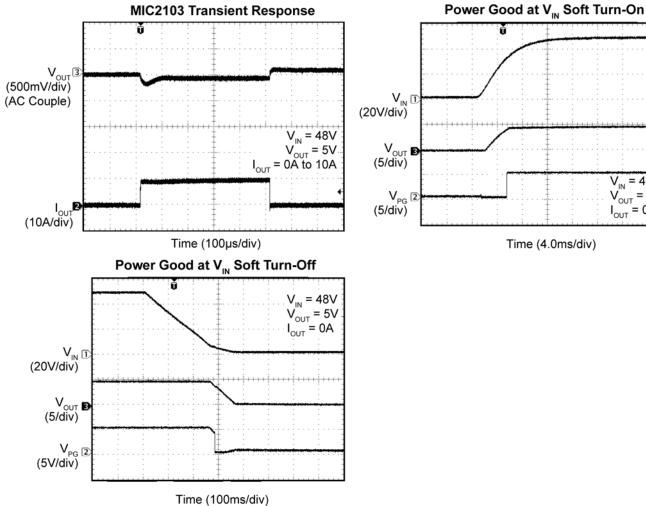

### **Functional Characteristics**

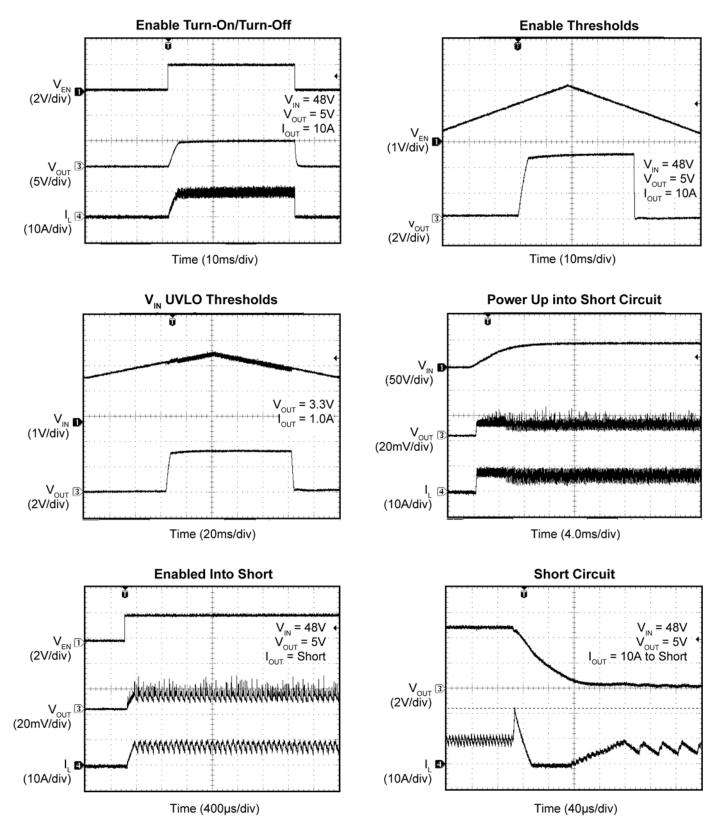

### **Functional Characteristics (Continued)**

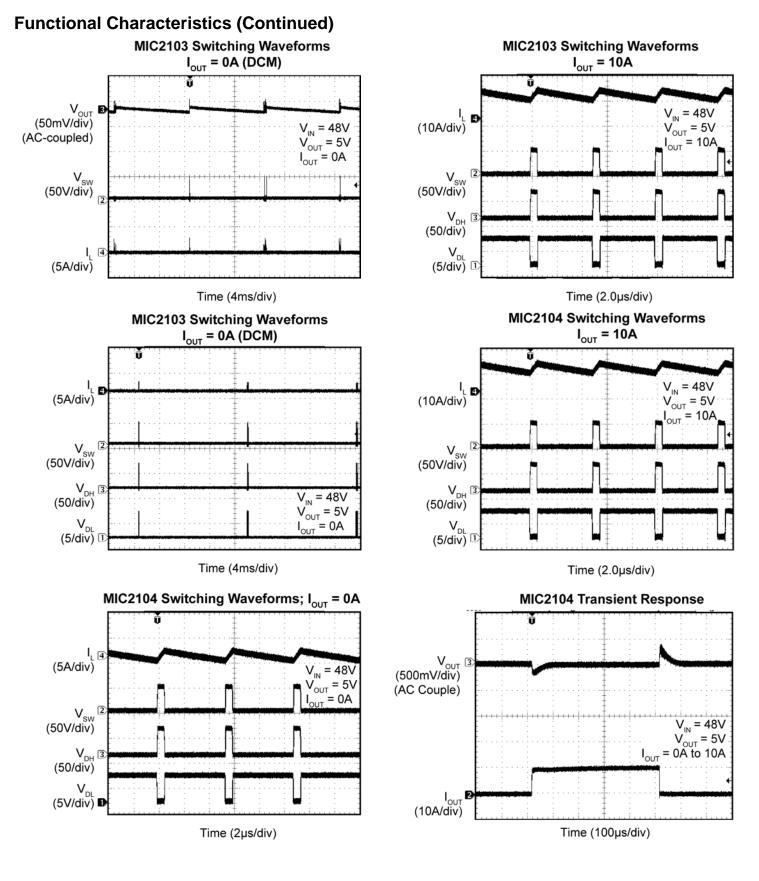

### **Functional Characteristics (Continued)**

M9999-080712-A

$V_{IN} = 48V$  $V_{OUT} = 5V$  $I_{OUT} = 0A$

Ŭ

Time (4.0ms/div)

# **Functional Characteristics (Continued)**

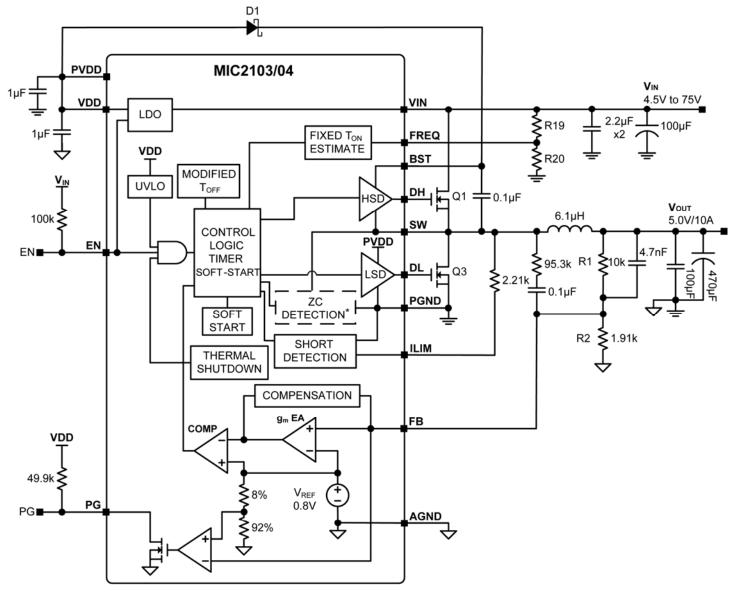

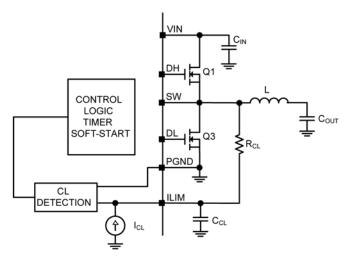

### **Functional Diagram**

ZC DETECTION\* -- MIC2103 ONLY

Figure 1. MIC2103/04 Functional Diagram

### **Functional Description**

The MIC2103/04 are adaptive on-time synchronous buck controllers built for high-input voltage to low-output voltage conversion applications. They are designed to operate over a wide input voltage range, from 4.5V to 75V, and the output is adjustable with an external resistive divider. An adaptive on-time control scheme is employed to obtain a constant switching frequency and to simplify the control compensation. Over-current protection is implemented by sensing low-side MOSFET's  $R_{DS(ON)}$ . The device features internal soft-start, enable, UVLO, and thermal shutdown.

#### Theory of Operation

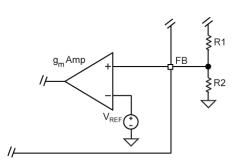

Figure 1 illustrates the block diagram of the MIC2103/04. The output voltage is sensed by the MIC2103/04 feedback pin FB via the voltage divider R1 and R2, and compared to a 0.8V reference voltage  $V_{REF}$  at the error comparator through a low-gain transconductance (g<sub>m</sub>) amplifier. If the feedback voltage decreases and the amplifier output is below 0.8V, then the error comparator will trigger the control logic and generate an ON-time period. The ON-time period length is predetermined by the "Fixed t<sub>ON</sub> Estimator" circuitry:

$$t_{ON(estimated)} = \frac{V_{OUT}}{V_{IN} \times f_{SW}}$$

(Eq. 1)

where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the power stage input voltage, and  $f_{SW}$  is the switching frequency.

At the end of the ON-time period, the internal high-side driver turns off the high-side MOSFET and the low-side driver turns on the low-side MOSFET. The OFF-time period length depends upon the feedback voltage in most cases. When the feedback voltage decreases and the output of the  $g_m$  amplifier is below 0.8V, the ON-time period is triggered and the OFF-time period ends. If the OFF-time period determined by the feedback voltage is less than the minimum OFF-time  $t_{OFF(min)}$ , which is about 200ns, the MIC2103/04 control logic will apply the  $t_{OFF(min)}$  instead.  $T_{OFF(min)}$  is required to maintain enough energy in the boost capacitor ( $C_{BST}$ ) to drive the high-side MOSFET.

The maximum duty cycle is obtained from the 200ns  $t_{\text{OFF(min)}}$ :

$$D_{MAX} = \frac{t_{S} - t_{OFF(MIN)}}{t_{S}} = 1 - \frac{200ns}{t_{S}}$$

(Eq. 2)

where  $t_S = 1/f_{SW}$ . It is not recommended to use MIC2103/04 with a OFF-time close to  $t_{OFF(min)}$  during steady-state operation.

The adaptive ON-time control scheme results in a constant switching frequency in the MIC2103/04. The actual ON-time and resulting switching frequency will vary with the different rising and falling times of the external MOSFETs. Also, the minimum  $t_{ON}$  results in a lower switching frequency in high  $V_{IN}$  to  $V_{OUT}$  applications. During load transients, the switching frequency is changed due to the varying OFF-time.

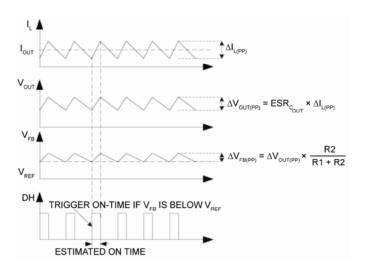

To illustrate the control loop operation, we will analyze both the steady-state and load transient scenarios. For easy analysis, the gain of the  $g_m$  amplifier is assumed to be 1. With this assumption, the inverting input of the error comparator is the same as the feedback voltage.

Figure 2 shows the MIC2103/04 control loop timing during steady-state operation. During steady-state, the  $g_m$  amplifier senses the feedback voltage ripple, which is proportional to the output voltage ripple plus injected voltage ripple, to trigger the ON-time period. The ON-time is predetermined by the  $t_{ON}$  estimator. The termination of the OFF-time is controlled by the feedback voltage ripple, which occurs when V<sub>FB</sub> falls below V<sub>REF</sub>, the OFF period ends and the next ON-time period is triggered through the control logic circuitry.

Figure 2. MIC2103/04 Control Loop Timing

Figure 3a shows the operation of the MIC2103/04 during a load transient. The output voltage drops due to the sudden load increase, which causes the V<sub>FB</sub> to be less than V<sub>REF</sub>. This will cause the error comparator to trigger an ON-time period. At the end of the ON-time period, a minimum OFF-time t<sub>OFF(min)</sub> is generated to charge C<sub>BST</sub> since the feedback voltage is still below V<sub>REF</sub>. Then, the next ON-time period is triggered due to the low feedback voltage. Therefore, the switching frequency changes during the load transient, but returns to the nominal fixed frequency once the output has stabilized at the new load current level. With the varying duty cycle and switching frequency, the output recovery time is fast and the output voltage deviation is small in MIC2103/04 converter.

Figure 3a. MIC2103/04 Load Transient Response

Unlike true current-mode control, the MIC2103/04 uses the output voltage ripple to trigger an ON-time period. The output voltage ripple is proportional to the inductor current ripple if the ESR of the output capacitor is large enough.

In order to meet the stability requirements, the MIC2103/04 feedback voltage ripple should be in phase with the inductor current ripple and are large enough to be sensed by the  $g_m$  amplifier and the error comparator. The recommended feedback voltage ripple is 20mV~100mV over full input voltage range. If a low ESR output capacitor is selected, then the feedback voltage ripple may be too small to be sensed by the g<sub>m</sub> amplifier and the error comparator. Also, the output voltage ripple and the feedback voltage ripple are not necessarily in phase with the inductor current ripple if the ESR of the output capacitor is very low. In these cases, ripple injection is required to ensure proper operation. Please refer to "Ripple Injection" subsection in Application Information for more details about the ripple injection technique.

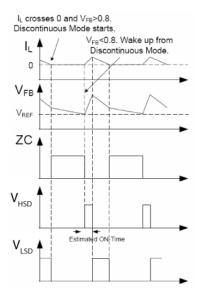

#### Discontinuous Mode (MIC2103 only)

In continuous mode, the inductor current is always greater than zero; however, at light loads, the MIC2103 is able to force the inductor current to operate in discontinuous mode. Discontinuous mode is where the inductor current falls to zero, as indicated by trace ( $I_L$ ) shown in Figure 3b. During this period, the efficiency is optimized by shutting down all the non-essential circuits and minimizing the supply current. The MIC2103 wakes up and turns on the high-side MOSFET when the feedback voltage V<sub>FB</sub> drops below 0.8V.

The MIC2103 has a zero crossing comparator (ZC Detection) that monitors the inductor current by sensing the voltage drop across the low-side MOSFET during its ON-time. If the  $V_{FB} > 0.8V$  and the inductor current goes slightly negative, then the MIC2103 automatically powers down most of the IC circuitry and goes into a low-power mode.

Once the MIC2103 goes into discontinuous mode, both LSD and HSD are low, which turns off the high-side and low-side MOSFETs. The load current is supplied by the output capacitors and  $V_{OUT}$  drops. If the drop of  $V_{OUT}$ causes  $V_{\text{FB}}$  to go below  $V_{\text{REF}},$  then all the circuits will wake up into normal continuous mode. First, the bias reduced currents of most circuits durina the discontinuous mode are restored, then a t<sub>ON</sub> pulse is triggered before the drivers are turned on to avoid any possible glitches. Finally, the high-side driver is turned on. Figure 3b shows the control loop timing in discontinuous mode.

Figure 3b. MIC2103 Control Loop Timing (Discontinuous Mode)

During discontinuous mode, the bias current of most circuits are reduced. As a result, the total power supply current during discontinuous mode is only about  $400\mu$ A, allowing the MIC2103 to achieve high efficiency in light load applications.

#### Soft-Start

Soft-start reduces the power supply input surge current at startup by controlling the output voltage rise time. The input surge appears while the output capacitor is charged up. A slower output rise time will draw a lower input surge current.

The MIC2103/04 implements an internal digital soft-start by making the 0.8V reference voltage  $V_{REF}$  ramp from 0 to 100% in about 6ms with 9.7mV steps. Therefore, the output voltage is controlled to increase slowly by a staircase  $V_{FB}$  ramp. Once the soft-start cycle ends, the related circuitry is disabled to reduce current consumption.  $V_{DD}$  must be powered up at the same time or after  $V_{IN}$  to make the soft-start function correctly.

#### **Current Limit**

The MIC2103/04 uses the  $R_{\text{DS}(\text{ON})}$  and external resistor connected from ILIM pin to SW node to decide the current limit.

Figure 4. MIC2103/04 Current Limiting Circuit

In each switching cycle of the MIC2103/04 converter, the inductor current is sensed by monitoring the low-side MOSFET in the OFF period. The sensed voltage V(ILIM) is compared with the power ground (PGND) after a blanking time of 150nS. In this way the drop voltage over the resistor  $R_{CL}$  ( $V_{CL}$ ) is compared with the drop over the bottom FET generating the short current limit. The small capacitor ( $C_{CL}$ ) connected from ILIM pin to PGND filters the switching node ringing during the off time allowing a better short limit measurement. The time constant

created by  $R_{\text{CL}}$  and  $C_{\text{CL}}$  should be much less than the minimum off time.

The  $V_{CL}$  drop allows programming of short limit through the value of the resistor ( $R_{CL}$ ), If the absolute value of the voltage drop on the bottom FET is greater than  $V_{CL'}$  in that case the V(ILIM) is lower than PGND and a short circuit event is triggered. A hiccup cycle to treat the short event is generated. The hiccup sequence including the soft start reduces the stress on the switching FETs and protects the load and supply for severe short conditions.

The short circuit current limit can be programmed by using the following formula.

$$\mathsf{R}_{\mathsf{CL}} = \frac{(I_{\mathit{CLIM}} - \Delta_{\mathit{PP}} \times 0.5) \times R_{\mathit{DS(ON)}} + V_{\mathit{CL}}}{I_{\mathit{CL}}} \qquad (\mathsf{Eq. 3})$$

Where  $I_{SH}$  = Desired Current limit

$\Delta_{PP}$  = Inductor current peak to peak

$R_{DS(ON)}$  = On resistance of low-side power MOSFET

$V_{\text{CL}}$  = Current limit threshold, the typical value is 14mV in EC table

$I_{\text{CL}}$  = Current Limit source current, the typical value is  $80 \mu A$  in EC table.

In case of hard short, the short limit is folded down to allow an indefinite hard short on the output without any destructive effect. It is mandatory to make sure that the inductor current used to charge the output capacitance during soft start is under the folded short limit, otherwise the supply will go in hiccup mode and may not be finishing the soft start successfully.

The MOSFET  $R_{DS(ON)}$  varies 30 to 40% with temperature; therefore, it is recommended to add a 50% margin to IcL in the above equation to avoid false current limiting due to increased MOSFET junction temperature rise. It is also recommended to connect SW pin directly to the drain of the Iow-side MOSFET to accurately sense the MOSFETs R<sub>DS(ON)</sub>.

#### MOSFET Gate Drive

The MIC2103/04 high-side drive circuit is designed to switch an N-Channel MOSFET. Figure 1 shows a bootstrap circuit, consisting of D1 (a Schottky diode is recommended) and  $C_{BST}$ . This circuit supplies energy to the high-side drive circuit. Capacitor  $C_{BST}$  is charged while the low-side MOSFET is on and the voltage on the SW pin is approximately 0V. When the high-side MOSFET driver is turned on, energy from  $C_{BST}$  is used to turn the MOSFET on. As the high-side MOSFET turns on, the voltage on the SW pin increases to approximately  $V_{IN}$ . Diode D1 is reverse biased and  $C_{BST}$  floats high while continuing to keep the high-side MOSFET on. The bias current of the high-side driver is less than 10mA so a  $0.1\mu$ F to  $1\mu$ F is sufficient to hold

the gate voltage with minimal droop for the power stroke (high-side switching) cycle, i.e.,  $\Delta BST = 10mA \times 3.33 \mu s/0.1 \mu F = 333 mV$ . When the low-side MOSFET is turned back on,  $C_{BST}$  is recharged through D1. A small resistor  $R_G$ , which is in series with  $C_{BST}$ , can be used to slow down the turn-on time of the high-side N-channel MOSFET.

The drive voltage is derived from the V<sub>DD</sub> supply voltage. The nominal low-side gate drive voltage is V<sub>DD</sub> and the nominal high-side gate drive voltage is approximately V<sub>DD</sub> – V<sub>DIODE</sub>, where V<sub>DIODE</sub> is the voltage drop across D1. An approximate 30ns delay between the high-side and low-side driver transitions is used to prevent current from simultaneously flowing unimpeded through both MOSFETs.

### **Application Information**

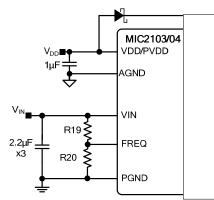

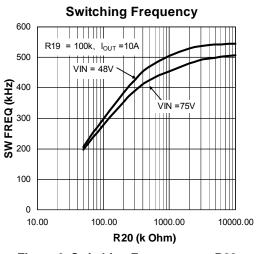

#### Setting the Switching Frequency

The MIC2103/04 are adjustable-frequency, synchronous buck controllers featuring a unique adaptive on-time control architecture. The switching frequency can be adjusted between 200kHz and 600kHz by changing the resistor divider network consisting of R19 and R20.

Figure 5. Switching Frequency Adjustment

The following formula gives the estimated switching frequency:

$$f_{SW\_ADJ} = f_O \times \frac{R20}{R19 + R20}$$

(Eq. 4)

Where  $f_0$  = Switching Frequency when R19 is 100k and R20 being open,  $f_0$  is typically 550kHz. For a more precise setting, it is recommended to use the following graph:

Figure 6. Switching Frequency vs. R20

#### **MOSFET Selection**

The MIC2103/04 controllers work from input voltages of 4.5V to 75V and have an internal 5V V<sub>DD</sub> LDO. This internal V<sub>DD</sub> LDO provides power to turn the external N-Channel power MOSFETs for the high-side and low-side switches. For applications where V<sub>DD</sub> < 5V, it is necessary that the power MOSFETs used are sub-logic level and are in full conduction mode for V<sub>GS</sub> of 2.5V. For applications when V<sub>DD</sub> > 5V; logic-level MOSFETs, whose operation is specified at V<sub>GS</sub> = 4.5V must be used.

There are different criteria for choosing the high-side and low-side MOSFETs. These differences are more significant at lower duty cycles. In such an application, the high-side MOSFET is then required to switch as quickly as possible in order to minimize transition losses, whereas the low-side MOSFET can switch slower, but must handle larger RMS currents. When the duty cycle approaches 50%, the current carrying capability of the high-side MOSFET starts to become critical.

It is important to note that the on-resistance of a MOSFET increases with increasing temperature. A 75°C rise in junction temperature will increase the channel resistance of the MOSFET by 50% to 75% of the resistance specified at 25°C. This change in resistance must be accounted for when calculating MOSFET power dissipation and in calculating the value of current limit. Total gate charge is the charge required to turn the MOSFET on and off under specified operating conditions (VDs and VGs). The gate charge is supplied by the MIC2103/04 gate-drive circuit. At 200kHz switching frequency, the gate charge can be a significant source of power dissipation in the MIC2103/04. At low output load, this power dissipation is noticeable as a reduction in efficiency. The average current required to drive the high-side MOSFET is:

$$I_{G[high-side]}(avg) = Q_G \times f_{SW}$$

(Eq. 5)

where:

$I_{G[high-side]}(avg)$  = Average high-side MOSFET gate current

$Q_G$  = Total gate charge for the high-side MOSFET taken from the manufacturer's data sheet for  $V_{GS}$  =  $V_{DD}$ .

f<sub>SW</sub> = Switching Frequency

The low-side MOSFET is turned on and off at  $V_{DS} = 0$  because an internal body diode or external freewheeling diode is conducting during this time. The switching loss for the low-side MOSFET is usually negligible. Also, the

gate-drive current for the low-side MOSFET is more accurately calculated using  $C_{\rm ISS}$  at  $V_{\rm DS}$  = 0 instead of gate charge.

For the low-side MOSFET:

$$I_{G[low-side]}(avg) = C_{ISS} \times V_{GS} \times f_{SW}$$

(Eq. 6)

Since the current from the gate drive comes from the  $V_{DD}$ , the power dissipated in the MIC2103/04 due to gate drive is:

$$(Eq. 7)$$

$$P_{GATEDRIVE} = V_{DD} \times (I_{G[high-side]}(avg) + I_{G[low-side]}(avg))$$

A convenient figure of merit for switching MOSFETs is the on resistance multiplied by the total gate charge;  $R_{DS(ON)} \times Q_G$ . Lower numbers translate into higher efficiency. Low gate-charge logic-level MOSFETs are a good choice for use with the MIC2103/04. Also, the  $R_{DS(ON)}$  of the low-side MOSFET will determine the current-limit value. Please refer to "Current Limit" subsection is *Functional Description* for more details.

Parameters that are important to MOSFET switch selection are:

- Voltage rating

- On-resistance

- Total gate charge

The voltage ratings for the high-side and low-side MOSFETs are essentially equal to the power stage input voltage  $V_{HSD}$ . A safety factor of 20% should be added to the  $V_{DS}(max)$  of the MOSFETs to account for voltage spikes due to circuit parasitic elements.

The power dissipated in the MOSFETs is the sum of the conduction losses during the on-time ( $P_{CONDUCTION}$ ) and the switching losses during the period of time when the MOSFETs turn on and off ( $P_{AC}$ ).

$$P_{SW} = P_{CONDUCTION} + P_{AC}$$

(Eq. 8)

$$P_{\text{CONDUCTION}} = I_{\text{SW}(\text{RMS})}^2 \times R_{\text{DS}(\text{ON})}$$

(Eq. 9)

$$P_{AC} = P_{AC(off)} + P_{AC(on)}$$

(Eq. 10)

where:

$R_{DS(ON)}$  = On-resistance of the MOSFET switch D = Duty Cycle = V<sub>OUT</sub> / V<sub>HSD</sub>

Making the assumption that the turn-on and turn-off

transition times are equal; the transition times can be approximated by:

$$t_{T} = \frac{C_{ISS} \times V_{IN} + C_{OSS} \times V_{HSD}}{I_{G}}$$

(Eq. 11)

where:

$C_{ISS}$  and  $C_{OSS}$  are measured at  $V_{DS}$  = 0 I<sub>G</sub> = Gate-drive current

The total high-side MOSFET switching loss is:

$$P_{AC} = (V_{HSD} + V_D) \times I_{PK} \times t_T \times f_{SW}$$

(Eq. 12)

where:

$t_T$  = Switching transition time  $V_D$  = Body diode drop (0.5V)  $f_{SW}$  = Switching Frequency

The high-side MOSFET switching losses increase with the switching frequency and the input voltage  $V_{HSD}$ . The low-side MOSFET switching losses are negligible and can be ignored for these calculations.

#### **Inductor Selection**

Values for inductance, peak, and RMS currents are required to select the output inductor. The input and output voltages and the inductance value determine the peak-to-peak inductor ripple current. Generally, higher inductance values are used with higher input voltages. Larger peak-to-peak ripple currents will increase the power dissipation in the inductor and MOSFETs. Larger output ripple currents will also require more output capacitance to smooth out the larger ripple current. Smaller peak-to-peak ripple currents require a larger inductance value and therefore a larger and more expensive inductor.

A good compromise between size, loss and cost is to set the inductor ripple current to be equal to 20% of the maximum output current.

The inductance value is calculated by Equation 13:

$$L = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times f_{sw} \times 20\% \times I_{OUT(max)}}$$

(Eq. 13)

where:

$f_{SW}$  = Switching frequency 20% = Ratio of AC ripple current to DC output current  $V_{IN(max)}$  = Maximum power stage input voltage

The peak-to-peak inductor current ripple is:

$$\Delta I_{L(pp)} = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{V_{IN(max)} \times f_{sw} \times L}$$

(Eq. 14)

The peak inductor current is equal to the average output current plus one half of the peak-to-peak inductor current ripple.

$$I_{L(pk)} = I_{OUT(max)} + 0.5 \times \Delta I_{L(pp)}$$

(Eq. 15)

The RMS inductor current is used to calculate the  $I^2R$  losses in the inductor.

$$I_{L(RMS)} = \sqrt{I_{OUT(max)}^{2} + \frac{\Delta I_{L(PP)}^{2}}{12}}$$

(Eq. 16)

Maximizing efficiency requires the proper selection of core material and minimizing the winding resistance. The high frequency operation of the MIC2103/04 requires the use of ferrite materials for all but the most cost sensitive applications. Lower cost iron powder cores may be used but the increase in core loss will reduce the efficiency of the power supply. This is especially noticeable at low output power. The winding resistance decreases efficiency at the higher output current levels. The winding resistance must be minimized although this usually comes at the expense of a larger inductor. The power dissipated in the inductor is equal to the sum of the core and copper losses. At higher output loads, the core losses are usually insignificant and can be ignored. At lower output currents, the core losses can be a significant contributor. Core loss information is usually available from the magnetic vendor.

Copper loss in the inductor is calculated by Equation 17:

$$P_{INDUCTOR(Cu)} = I_{L(RMS)}^{2} \times R_{WINDING}$$

(Eq. 17)

The resistance of the copper wire,  $R_{WINDING}$ , increases with the temperature. The value of the winding resistance used should be at the operating temperature.

$P_{WINDING(Ht)} = R_{WINDING(20^{\circ}C)} \times (1 + 0.0042 \times (T_H - T_{20^{\circ}C})) (Eq. 18)$

where:

$T_H$  = temperature of wire under full load

$T_{20^{\circ}C}$  = ambient temperature

$R_{WINDING(20^{\circ}C)}$  = room temperature winding resistance (usually specified by the manufacturer)

#### **Output Capacitor Selection**

The type of the output capacitor is usually determined by its ESR (equivalent series resistance). Voltage and RMS current capability are two other important factors for selecting the output capacitor. Recommended capacitor types are tantalum, low-ESR aluminum electrolytic, OS-CON and POSCAP. The output capacitor's ESR is usually the main cause of the output ripple. The output capacitor ESR also affects the control loop from a stability point of view. The maximum value of ESR is calculated:

$$\mathsf{ESR}_{\mathsf{C}_{\mathsf{OUT}}} \leq \frac{\Delta \mathsf{V}_{\mathsf{OUT}(\mathsf{pp})}}{\Delta \mathsf{I}_{\mathsf{L}(\mathsf{PP})}} \tag{Eq. 19}$$

where:

$\Delta V_{OUT(pp)}$  = peak-to-peak output voltage ripple  $\Delta I_{L(PP)}$  = peak-to-peak inductor current ripple

The total output ripple is a combination of the ESR and output capacitance. The total ripple is calculated in Equation 20:

$$\Delta V_{\text{OUT}(\text{pp})} = \sqrt{\left(\frac{\Delta I_{\text{L}(\text{PP})}}{C_{\text{OUT}} \times f_{\text{SW}} \times 8}\right)^2 + \left(\Delta I_{\text{L}(\text{PP})} \times \text{ESR}_{C_{\text{OUT}}}\right)^2}$$

(Eq. 20)

where:

D = duty cycle  $C_{OUT}$  = output capacitance value  $f_{sw}$  = switching frequency

As described in the "Theory of Operation" subsection in *Functional Description*, the MIC2103/04 requires at least 20mV peak-to-peak ripple at the FB pin to make the  $g_m$  amplifier and the error comparator behave properly. Also, the output voltage ripple should be in phase with the inductor current. Therefore, the output voltage ripple caused by the output capacitors value should be much

smaller than the ripple caused by the output capacitor ESR. If low ESR capacitors, such as ceramic capacitors, are selected as the output capacitors, a ripple injection method should be applied to provide enough feedback voltage ripple. Please refer to the "Ripple Injection" subsection for more details.

The voltage rating of the capacitor should be twice the output voltage for a tantalum and 20% greater for aluminum electrolytic or OS-CON. The output capacitor RMS current is calculated in Equation 21:

$$I_{C_{OUT}(RMS)} = \frac{\Delta I_{L(PP)}}{\sqrt{12}}$$

(Eq. 21)

The power dissipated in the output capacitor is:

$$P_{\text{DISS}(C_{\text{OUT}})} = I_{C_{\text{OUT}}(\text{RMS})}^{2} \times \text{ESR}_{C_{\text{OUT}}}$$

(Eq. 22)

#### **Input Capacitor Selection**

The input capacitor for the power stage input  $V_{IN}$  should be selected for ripple current rating and voltage rating. Tantalum input capacitors may fail when subjected to high inrush currents, caused by turning the input supply on. A tantalum input capacitor's voltage rating should be at least two times the maximum input voltage to maximize reliability. Aluminum electrolytic, OS-CON, and multilayer polymer film capacitors can handle the higher inrush currents without voltage de-rating. The input voltage ripple will primarily depend on the input capacitor's ESR. The peak input current is equal to the peak inductor current, so:

$$\Delta V_{\rm IN} = I_{\rm L(pk)} \times \rm ESR_{\rm CIN}$$

(Eq. 23)

The input capacitor must be rated for the input current ripple. The RMS value of input capacitor current is determined at the maximum output current. Assuming the peak-to-peak inductor current ripple is low:

$$I_{CIN(RMS)} \approx I_{OUT(max)} \times \sqrt{D \times (1-D)}$$

(Eq. 24)

The power dissipated in the input capacitor is:

$$P_{\text{DISS(CIN)}} = I_{\text{CIN(RMS)}}^{2} \times \text{ESR}_{\text{CIN}}$$

(Eq. 25)

#### Voltage Setting Components

The MIC2103 requires two resistors to set the output voltage as shown in Figure 7:

Figure 7. Voltage-Divider Configuration

The output voltage is determined by the equation:

$$V_{OUT} = V_{FB} \times (1 + \frac{R1}{R2})$$

(Eq. 26)

where,  $V_{FB}$  = 0.8V. A typical value of R1 can be between  $3k\Omega$  and  $10k\Omega$ . If R1 is too large, it may allow noise to be introduced into the voltage feedback loop. If R1 is too small in value, it will decrease the efficiency of the power supply, especially at light loads. Once R1 is selected, R2 can be calculated using:

$$R2 = \frac{V_{FB} \times R1}{V_{OUT} - V_{FB}}$$

(Eq. 27)

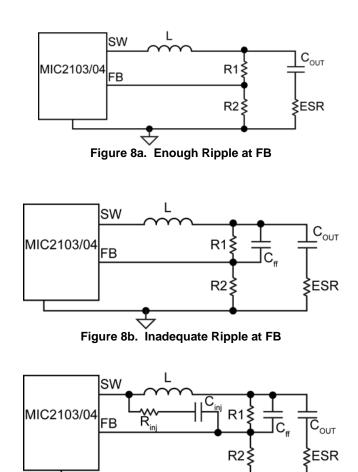

#### **Ripple Injection**

The V<sub>FB</sub> ripple required for proper operation of the MIC2103/04 g<sub>m</sub> amplifier and error comparator is 20mV to 100mV. However, the output voltage ripple is generally designed as 1% to 2% of the output voltage. For a low output voltage, such as a 1V, the output voltage ripple is only 10mV to 20mV, and the feedback voltage ripple is less than 20mV. If the feedback voltage ripple is so small that the g<sub>m</sub> amplifier and error comparator cannot sense it, then the MIC2103/04 will lose control and the output voltage is not regulated. In order to have some amount of V<sub>FB</sub> ripple, a ripple applications.

The applications are divided into three situations according to the amount of the feedback voltage ripple:

1. Enough ripple at the feedback voltage due to the large ESR of the output capacitors.

As shown in Figure 8a, the converter is stable without any ripple injection. The feedback voltage ripple is:

$$\Delta V_{FB(pp)} = \frac{R2}{R1 + R2} \times ESR_{C_{OUT}} \times \Delta I_{L(pp)}$$

(Eq. 28)

where  $\Delta I_{L(pp)}$  is the peak-to-peak value of the inductor current ripple.

2. Inadequate ripple at the feedback voltage due to the small ESR of the output capacitors.

The output voltage ripple is fed into the FB pin through a feed-forward capacitor  $C_{\rm ff}$  in this situation, as shown in Figure 8b. The typical  $C_{\rm ff}$  value is between 1nF and 100nF. With the feed-forward capacitor, the feedback voltage ripple is very close to the output voltage ripple:

$$\Delta V_{FB(pp)} \approx ESR \times \Delta I_{L(pp)} \tag{Eq. 29}$$

3. Virtually no ripple at the FB pin voltage due to the very-low ESR of the output capacitors:

Figure 8c. Invisible Ripple at FB

In this situation, the output voltage ripple is less than 20mV. Therefore, additional ripple is injected into the FB pin from the switching node SW via a resistor  $R_{inj}$  and a capacitor  $C_{inj}$ , as shown in Figure 8c. The injected ripple is:

$$\Delta V_{FB(pp)} = V_{IN} \times K_{div} \times D \times (1 - D) \times \frac{1}{f_{SW} \times \tau}$$

(Eq. 30)

$$K_{div} = \frac{R1//R2}{R_{ini} + R1//R2}$$

(Eq. 31)

where:

$V_{IN}$  = Power stage input voltage D = Duty cycle  $f_{SW}$  = Switching frequency  $\tau$  = (R1//R2//R<sub>inj</sub>) × C<sub>ff</sub>

In Equations 30 and 32, it is assumed that the time constant associated with  $C_{\rm ff}$  must be much greater than the switching period:

$$\frac{1}{f_{SW} \times \tau} = \frac{T}{\tau} \ll 1$$

(Eq. 32)

If the voltage divider resistors R1 and R2 are in the  $k\Omega$  range, then a  $C_{\rm ff}$  of 1nF to 100nF can easily satisfy the large time constant requirements. Also, a 100nF injection capacitor  $C_{\rm inj}$  is used in order to be considered as short for a wide range of the frequencies.

The process of sizing the ripple injection resistor and capacitors is:

**Step 1.** Select  $C_{\rm ff}$  to feed all output ripples into the feedback pin and make sure the large time constant assumption is satisfied. Typical choice of  $C_{\rm ff}$  is 1nF to 100nF if R1 and R2 are in k $\Omega$  range.

**Step 2.** Select R<sub>inj</sub> according to the expected feedback voltage ripple using Equation 33:

$$K_{div} = \frac{\Delta V_{FB(pp)}}{V_{IN}} \times \frac{f_{SW} \times \tau}{D \times (1 - D)}$$

(Eq. 33)

Then the value of R<sub>inj</sub> is obtained as:

$$R_{inj} = (R1//R2) \times (\frac{1}{K_{div}} - 1)$$

(Eq. 34)

**Step 3.** Select  $C_{inj}$  as 100nF, which could be considered as short for a wide range of the frequencies.

### PCB Layout Guidelines

# Warning: To minimize EMI and output noise, follow these layout recommendations.

PCB Layout is critical to achieve reliable, stable and efficient performance. A ground plane is required to control EMI and minimize the inductance in power, signal and return paths.

The following guidelines should be followed to insure proper operation of the MIC2103 converter.

#### IC

- The 1µF ceramic capacitors, which are connected to the VDD and PVDD pins, must be located right at the IC. The VDD pin is very noise sensitive and placement of the capacitor is very critical. Use wide traces to connect to the VDD and PGND pins.

- The signal ground pin (GND) must be connected directly to the ground planes. Do not route the GND pin to the PGND pin on the top layer.

- Place the IC close to the point of load (POL).

- Use fat traces to route the input and output power lines.

- Signal and power grounds should be kept separate and connected at only one location.

#### **Input Capacitor**

- Place the input capacitor next.

- Place the input capacitors on the same side of the board and as close to the MOSFETs as possible.

- Place several vias to the ground plane close to the input capacitor ground terminal.

- Use either X7R or X5R dielectric input capacitors. Do not use Y5V or Z5U type capacitors.

- Do not replace the ceramic input capacitor with any other type of capacitor. Any type of capacitor can be placed in parallel with the input capacitor.

- If a Tantalum input capacitor is placed in parallel with the input capacitor, it must be recommended for switching regulator applications and the operating voltage must be derated by 50%.

- In "Hot-Plug" applications, a Tantalum or Electrolytic bypass capacitor must be used to limit the overvoltage spike seen on the input supply with power is suddenly applied.

#### **RC Snubber**

• Place the RC snubber on the same side of the board and as close to the SW pin as possible.

#### Inductor

- Keep the inductor connection to the switch node (SW) short.

- Do not route any digital lines underneath or close to the inductor.

- Keep the switch node (SW) away from the feedback (FB) pin.

- The SW pin should be connected directly to the drain of the low-side MOSFET to accurate sense the voltage across the low-side MOSFET.

- To minimize noise, place a ground plane underneath the inductor.

#### **Output Capacitor**

- Use a wide trace to connect the output capacitor ground terminal to the input capacitor ground terminal.

- Phase margin will change as the output capacitor value and ESR changes. Contact the factory if the output capacitor is different from what is shown in the BOM.

- The feedback trace should be separate from the power trace and connected as close as possible to the output capacitor. Sensing a long high-current load trace can degrade the DC load regulation.

#### MOSFETs

- Low-side MOSFET gate drive trace (DL pin to MOSFET gate pin) must be short and routed over a ground plane. The ground plane should be the connection between the MOSFET source and PGND.

- Chose a low-side MOSFET with a high C<sub>GS</sub>/C<sub>GD</sub> ratio and a low internal gate resistance to minimize the effect of dv/dt inducted turn-on.

- Do not put a resistor between the Low-side MOSFET gate drive output and the gate.

- Use a 4.5V  $V_{GS}$  rated MOSFET. Its higher gate threshold voltage is more immune to glitches than a 2.5V or 3.3V rated MOSFET. MOSFETs that are rated for operation at less than 4.5V  $V_{GS}$  should not be used.

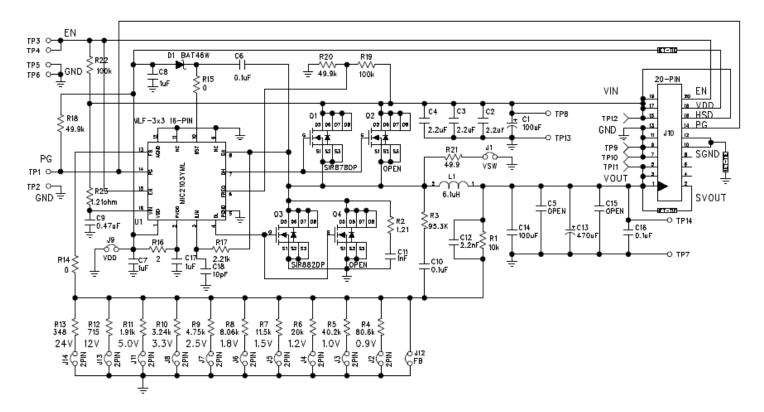

### **Evaluation Board Schematic**

Figure 9. Schematic of MIC2103/04 Evaluation Board (J1, J9, J12, R14, and R21 are for testing purposes)

### **Bill of Materials**

| Item        | Part Number        | Manufacturer             | Description                                     | Qty |  |

|-------------|--------------------|--------------------------|-------------------------------------------------|-----|--|

| C1          | EEU-FC2A101        | Panasonic <sup>(1)</sup> | 100µF Aluminum Capacitor, 100V                  | 1   |  |

|             | GRM32ER72A225K     | Murata <sup>(2)</sup>    | 2.2µF/100V Ceramic Capacitor, X7R, Size 1210    |     |  |

| C2, C3, C4  | C3225X7R2A225K     | TDK <sup>(3)</sup>       |                                                 |     |  |

|             | 12101C225KAT2A     | AVX <sup>(4)</sup>       |                                                 |     |  |

|             | GRM32ER60J107ME20L | Murata                   |                                                 |     |  |

| C14         | 12106D107MAT2A     | AVX                      | 100µF/6.3V Ceramic Capacitor, X5R, Size 1210    |     |  |

|             | C3225X5ROJ107M     | TDK                      |                                                 |     |  |

|             | GRM188R71H104KA93D | Murata                   |                                                 |     |  |

| C6, C16     | 06035C104KAT2A     | AVX                      | 0.1µF/50V Ceramic Capacitor, X7R, Size 0603     | 2   |  |

|             | C1608X7R1H104K     | TDK                      |                                                 |     |  |

|             | GRM188R70J105KA01D | Murata                   | 1µF/6.3V Ceramic Capacitor, X7R, Size 0603      |     |  |

| C7, C8, C17 | 06036C105KAT2A     | AVX                      |                                                 |     |  |

|             | C1608X5R0J105K     | TDK                      |                                                 |     |  |

|             | GRM21BR72A474KA73  | Murata                   | - 0.47µF/100V Ceramic Capacitor, X7R, Size 0805 |     |  |

| C9          | 08051C474KAT2A     | AVX                      |                                                 |     |  |

| 010         | GRM188R72A104KA35D | Murata                   | 0.1µF/100V Ceramic Capacitor, X7R, Size 0603    |     |  |

| C10         | C1608X7S2A104K     | TDK                      | 0.1µF/100V,X7S,0603                             |     |  |

|             | GRM188R72A102KA01D | Murata                   | 1nF/100V Cermiac Capacitor, X7R, Size 0603      |     |  |

| C11         | 06031C102KAT2A     | AVX                      |                                                 |     |  |

|             | C1608X7R2A102K     | TDK                      |                                                 |     |  |

|             | GRM188R72A222KA01D | Murata                   |                                                 |     |  |

| C12         | 06031C222KAT2A     | AVX                      | 2.2nF/100V Cermiac Capacitor, X7R, Size 0603    | 1   |  |

|             | C1608X7R2A222K     | TDK                      | -                                               |     |  |

| 040         | 6SEPC470MX         | Sanyo <sup>(5)</sup>     | 470µF/6.3V, 7m-ohms, OSCON                      | 1   |  |

| C13         | 6SEPC470M          | Sanyo                    | 470μF/6.3V, 7m-ohms, OSCON                      |     |  |

| C15 (OPEN)  | 6TPB470M           | Sanyo                    | 470µF/6.3V, POSCAP                              |     |  |

| C5 (OPEN)   | GRM32ER60J107ME20L | Murata                   | 100µF/6.3V Ceramic Capacitor, X7R, Size 1210    |     |  |

| C18         | GCM1885C2A100JA16D | Murata                   | 10pF, 100V, 0603, NPO                           | 1   |  |

|             | 06031A100JAT2A     | AVX                      |                                                 |     |  |

| D1          | BAT46W-TP          | MCC <sup>(6)</sup>       | 100V Small Signal Schottky Diode, SOD123        | 1   |  |

| L1          | CDEP147NP-6R1MC-95 | Sumida <sup>(7)</sup>    | 6.1µH Inductor, 14.8A RMS Current               | 1   |  |

#### Notes:

1. Panasonic: <u>www.panasonic.com</u>.

- 2. Murata: <u>www.murata.com</u>.

- 3. TDK: <u>www.tdk.com</u>.

- 4. AVX: <u>www.avx.com</u>

- 5. Sanyo: <u>www.sanyo.com</u>.

- 6. MCC.: <u>www.mccsemi.com</u>.

- 7. Sumida: <u>www.sumida.com</u>.

# **Bill of Materials (Continued)**

| Item          | Part Number       | Manufacturer                | Description                           | Qty |

|---------------|-------------------|-----------------------------|---------------------------------------|-----|

| Q1            | SIR878DP          | Vishay <sup>(8)</sup>       | MOSFET, N-CH, Power SO-8              | 1   |

| Q3            | SIR882DP          | Vishay                      | MOSFET, N-CH, Power SO-8              | 1   |

| Q2, Q4 (OPEN) |                   |                             |                                       |     |

| R1            | CRCW060310K0FKEA  | Vishay Dale                 | 10kΩ Resistor, Size 0603, 1%          | 1   |

| R2, R23       | CRCW08051R21FKEA  | Vishay Dale                 | 1.21Ω Resistor, Size 0805, 5%         | 2   |

| R3            | CRCW060395K30FKEA | Vishay Dale                 | 95.3kΩ Resistor, Size 0603, 1%        | 1   |

| R4            | CRCW060380K6FKEA  | Vishay Dale                 | 80.6kΩ Resistor, Size 0603, 1%        | 1   |

| R5            | CRCW060340K2FKEA  | Vishay Dale                 | 40.2kΩ Resistor, Size 0603, 1%        | 1   |

| R6            | CRCW060320K0FKEA  | Vishay Dale                 | 20kΩ Resistor, Size 0603, 1%          | 1   |

| R7            | CRCW060311K5FKEA  | Vishay Dale                 | 11.5kΩ Resistor, Size 0603, 1%        | 1   |

| R8            | CRCW06038K06FKEA  | Vishay Dale                 | 8.06kΩ Resistor, Size 0603, 1%        | 1   |

| R9            | CRCW06034K75FKEA  | Vishay Dale                 | 4.75kΩ Resistor, Size 0603, 1%        | 1   |

| R10           | CRCW06033K24FKEA  | Vishay Dale                 | 3.24kΩ Resistor, Size 0603, 1%        | 1   |

| R11           | CRCW06031K91FKEA  | Vishay Dale                 | 1.91kΩ Resistor, Size 0603, 1%        | 1   |

| R12 (OPEN)    | CRCW0603715R0FKEA | Vishay Dale                 | 715Ω Resistor, Size 0603, 1%          |     |

| R13 (OPEN)    | CRCW0603348R0FKEA | Vishay Dale                 | 348Ω Resistor, Size 0603, 1%          |     |

| R14, R15      | CRCW06030000FKEA  | Vishay Dale                 | 0Ω Resistor, Size 0603, 5%            | 2   |

| R16           | CRCW08052R0FKEA   | Vishay Dale                 | 2Ω Resistor, Size 0805, 5%            | 1   |

| R17           | CRCW06032K21FKEA  | Vishay Dale                 | 2.21kΩ Resistor, Size 0603, 1%        | 1   |

| R18, R20      | CRCW060349K9FKEA  | Vishay Dale                 | 49.9kΩ Resistor, Size 0603, 1%        | 2   |

| R19, R22      | CRCW0603100K0FKEA | Vishay Dale                 | 100kΩ Resistor, Size 0603, 1%         | 2   |

| R21           | CRCW060349R9FKEA  | Vishay Dale                 | 49.9Ω Resistor, Size 0603, 1%         | 1   |

| 114           | MIC2103YML        | Micrel. Inc. <sup>(9)</sup> | 75V Synohronous Buck DC DC Controller | 1   |

| U1            | MIC2104YML        |                             | 75V Synchronous Buck DC-DC Controller |     |

Notes:

8. Vishay: <u>www.vishay.com</u>.

9. Micrel, Inc.: <u>www.micrel.com</u>.

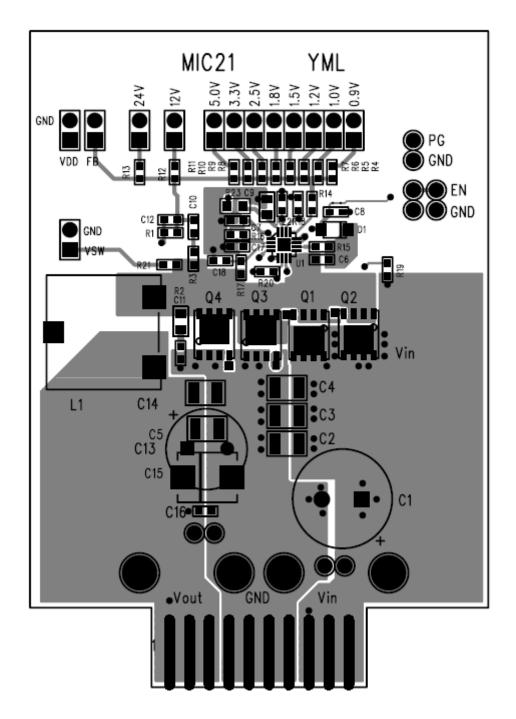

### **PCB** Layout

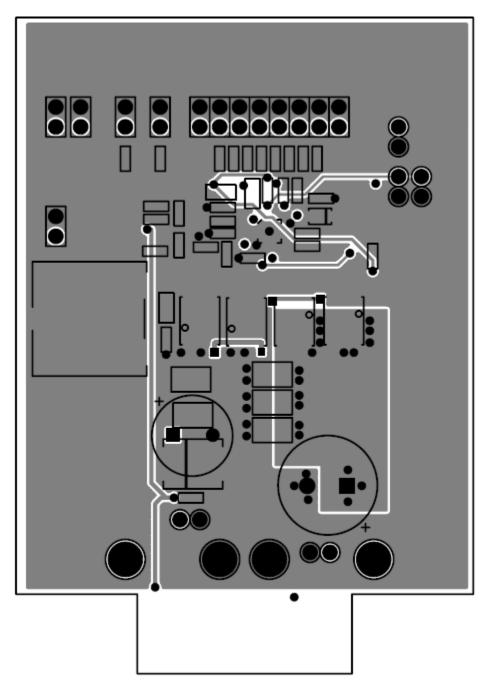

Figure 10. MIC2103/04 Evaluation Board Top Layer

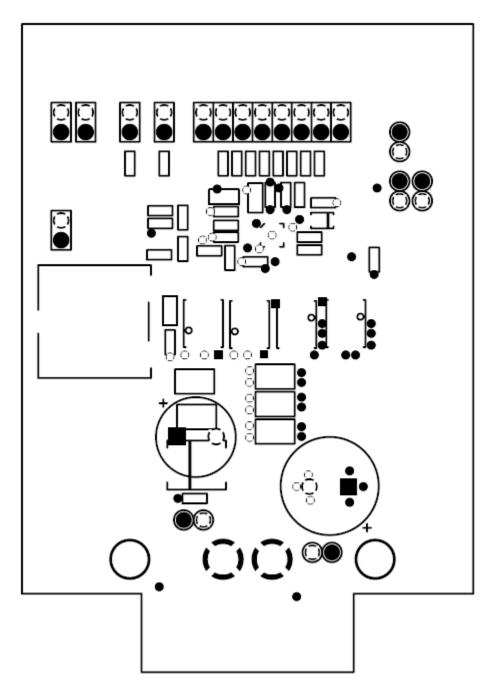

# PCB Layout (Continued)

Figure 11. MIC2103/04 Evaluation Board Mid-Layer 1 (Ground Plane)

# PCB Layout (Continued)

# PCB Layout (Continued)

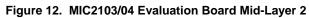

Figure 13. MIC2103/04 Evaluation Board Bottom Layer

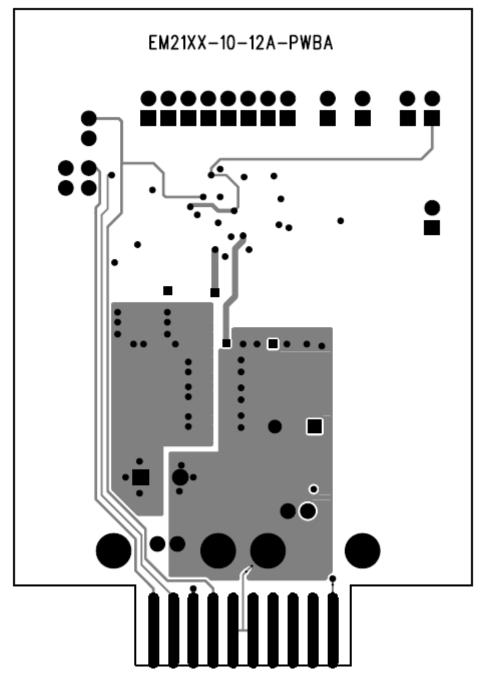

### **Recommended Land Pattern**

Red circle indicates Thermal Via. Size should be .300mm – .350mm in diameter and it should be connected to GND plane for maximum thermal performance. ALL UNITS ARE IN mm, TOLERANCE  $\pm 0.05$ , IF NOT NOTED LP # MLF33D-16LD-LP-1

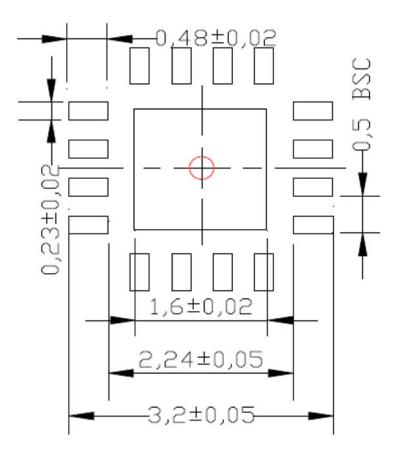

### **Package Information**

16-Pin 3mm × 3mm MLF (ML)

# MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2012 Micrel, Incorporated.

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

#### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9