## BALLAS SEMICONDUCTOR

## DS21354/DS21554 3.3V/5V E1 Single-Chip Transceivers

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS21354/DS213554 single-chip transceivers (SCTs) contain all the necessary functions to connect to E1 lines. The devices are upward-compatible versions of the DS2153 and DS2154 SCTs. The on-board clock/data recovery circuitry coverts the AMI/HDB3 E1 waveforms to an NRZ serial stream. Both devices automatically adjust to E1 22AWG (0.6mm) twistedpair cables from 0 to over 2km in length. They can generate the necessary G.703 waveshapes for both  $75\Omega$ coax and  $120\Omega$  twisted cables. The on-board jitter attenuator (selectable to either 32 bits or 128 bits) can be placed in either the transmit or receive data paths. The framer locates the frame and multiframe boundaries and monitors the data stream for alarms. It is also used for extracting and inserting signaling data, Si, and Sa-bit information. The on-board HDLC controller can be used for Sa-bit links or DS0s. The devices contain a set of internal registers that the user can access to control the operation of the units. Quick access through the parallel control port allows a single controller to handle many E1 lines. The devices fully meet all the latest E1 specifications, including ITU-T G.703, G.704, G.706, G.823, G.732, and I.431, ETS 300 011, 300 233, and 300 166, as well as CTR12 and CTR4.

#### **PIN CONFIGURATION**

#### FEATURES

- Complete E1 (CEPT) PCM-30/ISDN-PRI Transceiver Functionality

- On-Board Long- and Short-Haul Line Interface for Clock/Data Recovery and Waveshaping

- 32-Bit or 128-Bit Crystal-Less Jitter Attenuator

- Frames to FAS, CAS, CCS, and CRC4 Formats

- Integral HDLC Controller with 64-Byte Buffers Configurable for Sa Bits, DS0, or Sub-DS0 Operation

- Dual Two-Frame Elastic Store Slip Buffers that can Connect to Asynchronous Backplanes up to 8.192MHz

- Interleaving PCM Bus Operation

- 8-Bit Parallel Control Port that can be used Directly on Either Multiplexed or Nonmultiplexed Buses (Intel or Motorola)

- Extracts and Inserts CAS Signaling

- Detects and Generates Remote and AIS Alarms

- Programmable Output Clocks for Fractional E1, H0, and H12 Applications

- Fully Independent Transmit and Receive Functionality

- Full Access to Si and Sa Bits Aligned with CRC-4 Multiframe

- Four Separate Loopback Functions for Testing Functions

- Large Counters for Bipolar and Code Violations, CRC4 Codeword Errors, FAS Word Errors, and E Bits

- IEEE 1149.1 JTAG-Boundary Scan Architecture

- Pin Compatible with DS2154/52/352/552 SCTs

- 3.3V (DS21354) or 5V (DS21554) Supply; Low-Power CMOS

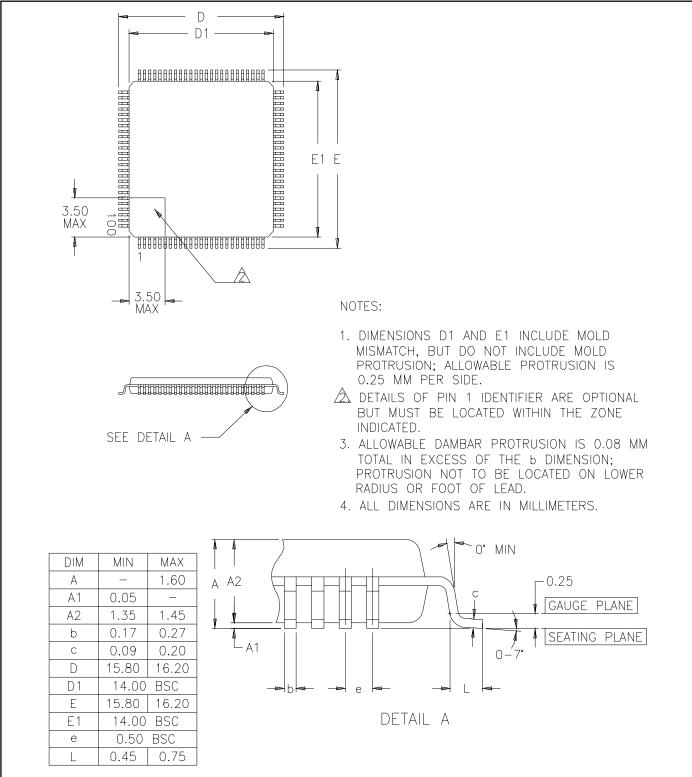

- 100-pin LQFP package (14mm x 14mm)

#### **ORDERING INFORMATION**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS21354L  | 0°C to +70°C   | 100 LQFP    |

| DS21354LN | -40°C to +85°C | 100 LQFP    |

| DS21554L  | 0°C to +70°C   | 100 LQFP    |

| DS21554LN | -40°C to +85°C | 100 LQFP    |

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

## TABLE OF CONTENTS

| 1.  | INTRODUCTION.                                                                                                                                                                                                                                                                                                              | 6                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     | 1.1. FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                | 8                                      |

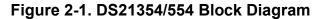

| 2.  | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                              | 9                                      |

| 3.  | PIN DESCRIPTION.                                                                                                                                                                                                                                                                                                           | 10                                     |

|     | <ul> <li>3.1. PIN FUNCTION DESCRIPTION</li> <li>3.1.1. Transmit-Side Pins</li> <li>3.1.2. Receive-Side Pins</li> <li>3.1.3. Parallel Control Port Pins</li> <li>3.1.4. JTAG Test Access Port Pins</li> <li>3.1.5. Interleave Bus Operation Pins</li> <li>3.1.6. Line Interface Pins</li> <li>3.1.7. Supply Pins</li> </ul> | .14<br>.17<br>.20<br>.22<br>.22<br>.22 |

| 4.  | PARALLEL PORT                                                                                                                                                                                                                                                                                                              | 25                                     |

|     | 4.1. REGISTER MAP                                                                                                                                                                                                                                                                                                          | .25                                    |

| 5.  | CONTROL, ID, AND TEST REGISTERS                                                                                                                                                                                                                                                                                            | 30                                     |

|     | <ul> <li>5.1. POWER-UP SEQUENCE</li> <li>5.2. SYNCHRONIZATION AND RESYNCHRONIZATION</li> <li>5.3. FRAMER LOOPBACK</li> <li>5.4. AUTOMATIC ALARM GENERATION</li> <li>5.5. REMOTE LOOPBACK</li> <li>5.6. LOCAL LOOPBACK</li> </ul>                                                                                           | 32<br>36<br>38<br>40                   |

| 6.  | STATUS AND INFORMATION REGISTERS                                                                                                                                                                                                                                                                                           | 43                                     |

|     | 6.1. CRC4 SYNC COUNTER                                                                                                                                                                                                                                                                                                     | .45                                    |

| 7.  | ERROR COUNT REGISTERS                                                                                                                                                                                                                                                                                                      | 50                                     |

|     | <ul> <li>7.1. BPV OR CODE VIOLATION COUNTER</li></ul>                                                                                                                                                                                                                                                                      | .51<br>.51                             |

| 8.  | DS0 MONITORING FUNCTION                                                                                                                                                                                                                                                                                                    | 53                                     |

| 9.  | SIGNALING OPERATION                                                                                                                                                                                                                                                                                                        | 56                                     |

|     | 9.1. PROCESSOR-BASED SIGNALING         9.2. HARDWARE-BASED SIGNALING         9.2.1. Receive Side         9.2.2. Transmit Side                                                                                                                                                                                              | .58<br>.58                             |

| 10. | PER-CHANNEL CODE GENERATION AND LOOPBACK                                                                                                                                                                                                                                                                                   | 60                                     |

|     | <ul> <li>10.1. TRANSMIT-SIDE CODE GENERATION</li></ul>                                                                                                                                                                                                                                                                     | .60<br>.61                             |

| 11. | CLOCK BLOCKING REGISTERS                                                                                                                                                                                                                                                                                                   | 63                                     |

| <b>12. ELASTIC STORES OPERAT</b>                                                                                                  | - ION                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                                                                                                                   |                                                                 |

| 13. ADDITIONAL (SA) AND INT                                                                                                       | ERNATIONAL (SI) BIT OPERATION                                   |

| 13.2. INTERNAL REGISTER SCH                                                                                                       | 66<br>EME BASED ON DOUBLE FRAME<br>EME BASED ON CRC4 MULTIFRAME |

| 14. HDLC CONTROLLER FOR                                                                                                           | THE SA BITS OR DS0                                              |

| 14.2. HDLC STATUS REGISTERS<br>14.3. BASIC OPERATION DETAIL<br>14.3.1. Example: Receive an HDL<br>14.3.2. Example: Transmit an HD | 70<br>5                                                         |

| <b>15. LINE INTERFACE FUNCTIO</b>                                                                                                 | NS80                                                            |

| 15.2. TRANSMIT WAVESHAPING AND<br>15.3. JITTER ATTENUATOR<br>15.4. PROTECTED INTERFACES                                           | COVERY                                                          |

| 16. JTAG BOUNDARY SCAN A                                                                                                          | RCHITECTURE AND TEST ACCESS PORT                                |

| 16.2. TEST REGISTERS                                                                                                              |                                                                 |

|                                                                                                                                   | PERATION                                                        |

|                                                                                                                                   |                                                                 |

| 18. FUNCTIONAL TIMING DIAG                                                                                                        | RAMS                                                            |

|                                                                                                                                   |                                                                 |

| <b>19. OPERATING PARAMETERS</b>                                                                                                   | 5                                                               |

| 20. AC TIMING PARAMETERS                                                                                                          | AND DIAGRAMS                                                    |

| 20.2. NONMULTIPLEXED BUS AC CH<br>20.3. RECEIVE-SIDE AC CHARACTER                                                                 | CTERISTICS                                                      |

| 21. PACKAGE INFORMATION.                                                                                                          |                                                                 |

## LIST OF FIGURES

| Figure 2-1. DS21354/554 Block Diagram                                             | 9   |

|-----------------------------------------------------------------------------------|-----|

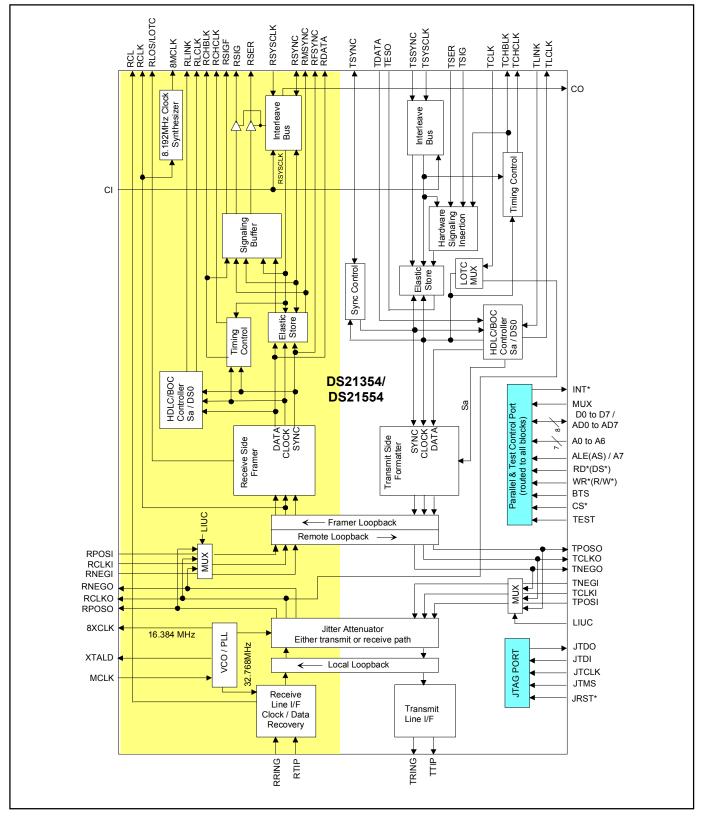

| Figure 15-1. Basic External Analog Connections                                    | 83  |

| Figure 15-2. Optional Crystal Connection                                          | 83  |

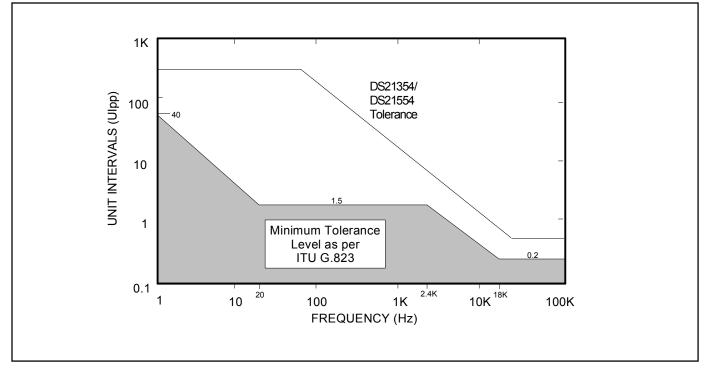

| Figure 15-3. Jitter Tolerance                                                     |     |

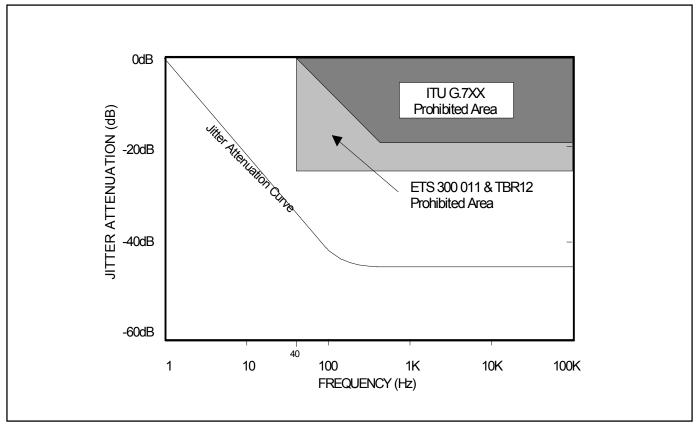

| Figure 15-4. Jitter Attenuation                                                   | 84  |

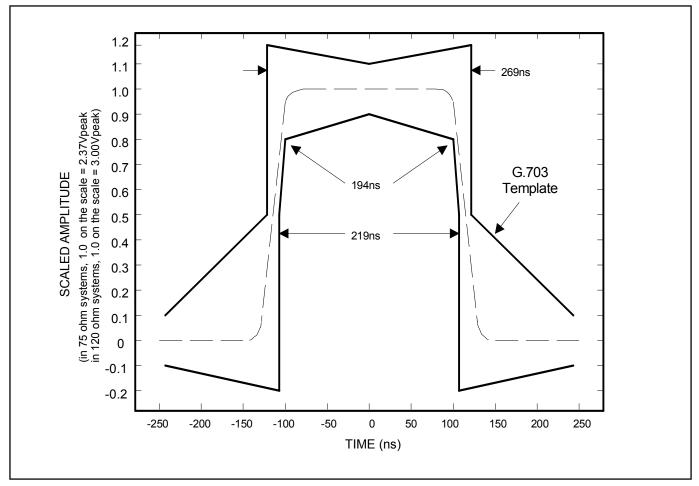

| Figure 15-5. Transmit Waveform Template                                           | 85  |

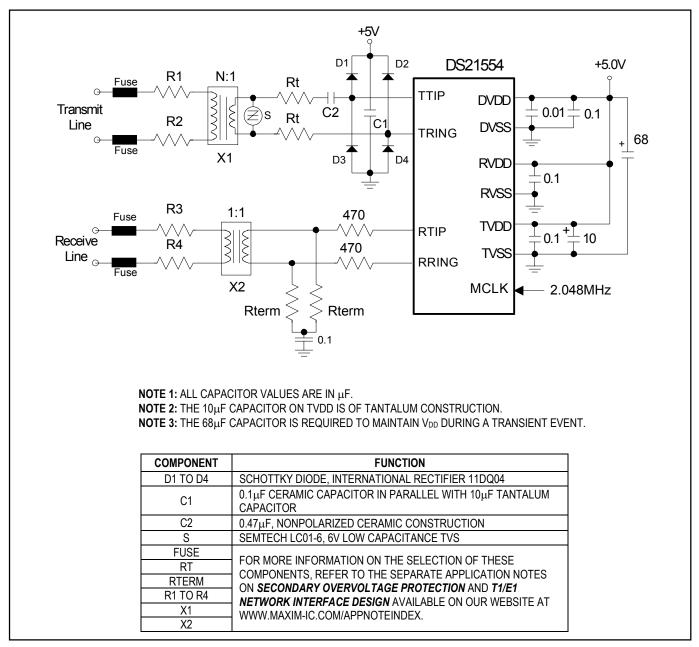

| Figure 15-6. Protected Interface Example for the DS21554                          | 87  |

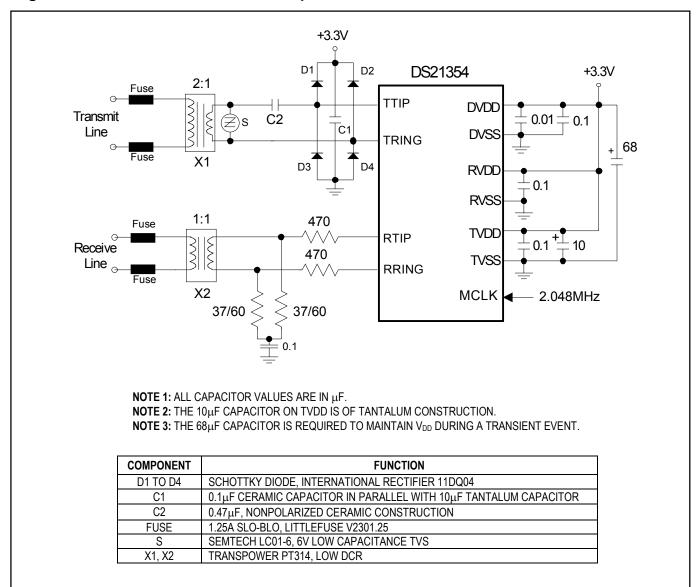

| Figure 15-7. Protected Interface Example for the DS21354                          | 88  |

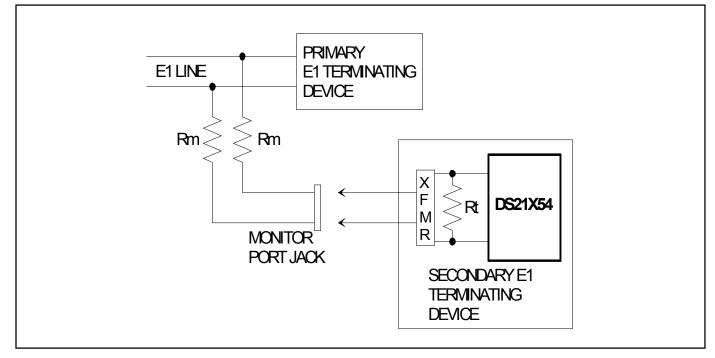

| Figure 15-8. Typical Monitor Port Application                                     | 89  |

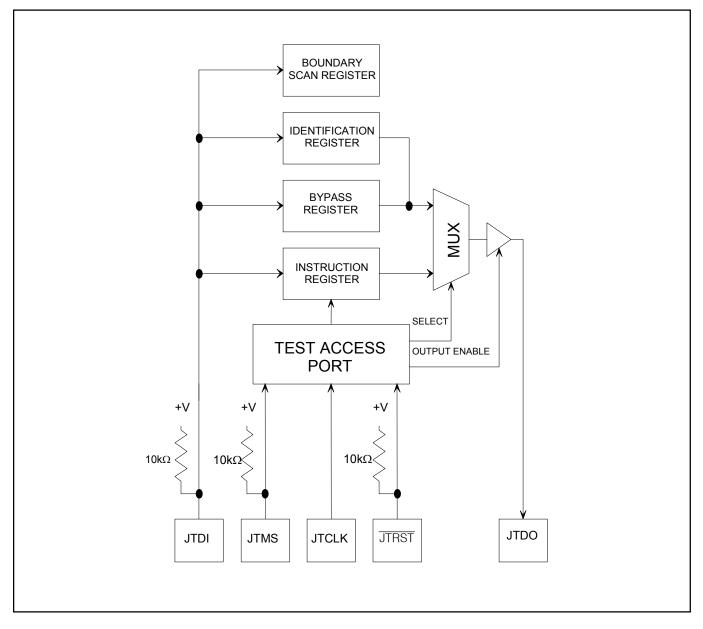

| Figure 16-1. JTAG Functional Block Diagram                                        | 91  |

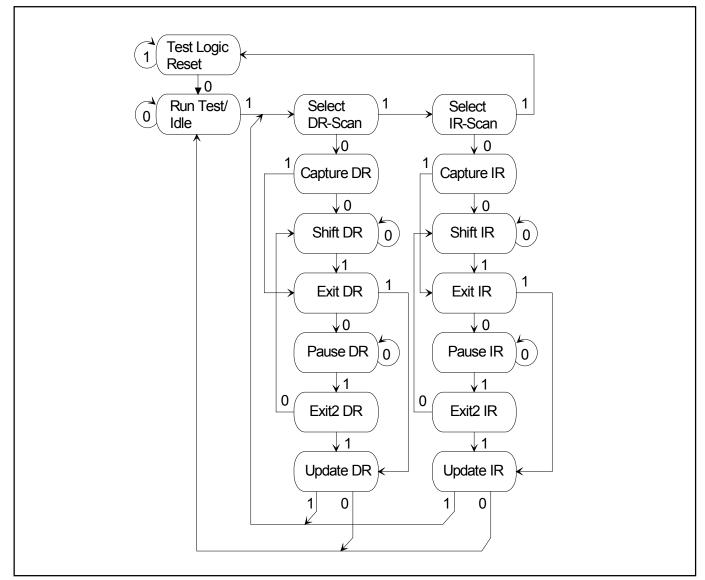

| Figure 16-2. TAP Controller State Diagram                                         | 94  |

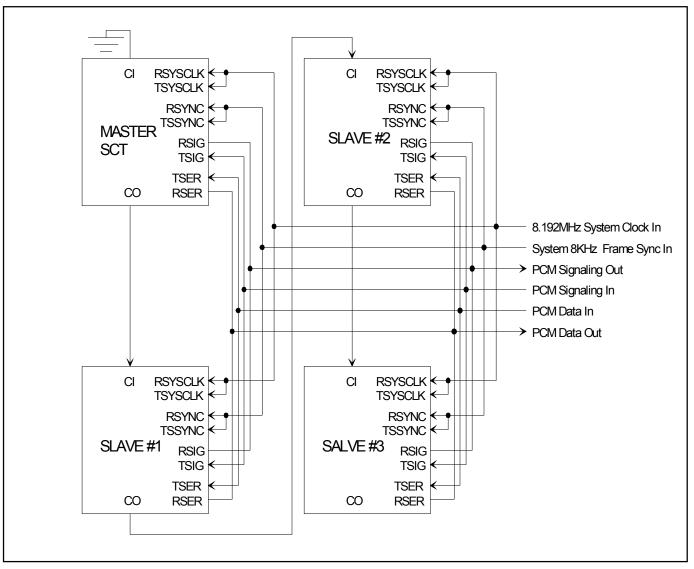

| Figure 17-1. IBO Basic Configuration Using Four SCTs                              | 99  |

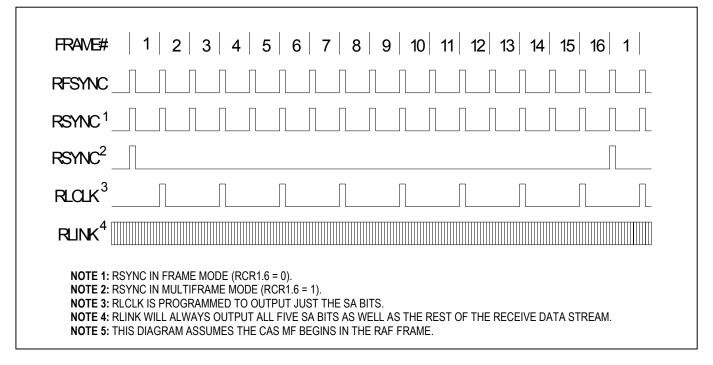

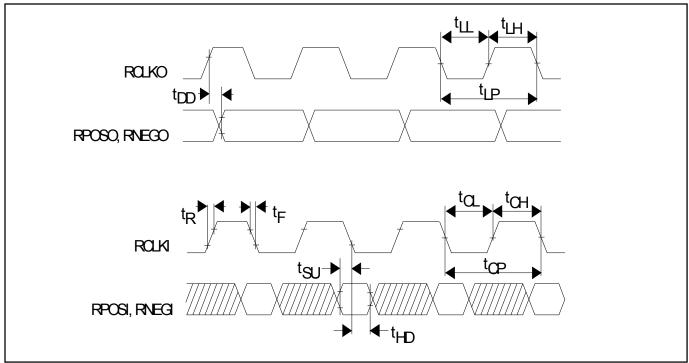

| Figure 18-1. Receive-Side Timing                                                  | 100 |

| Figure 18-2. Receive-Side Boundary Timing (with Elastic Store Disabled)           | 100 |

| Figure 18-3. Receive-Side 1.544MHz Boundary Timing (with Elastic Store Enabled)   | 101 |

| Figure 18-4. Receive-Side 2.048MHz Boundary Timing (with Elastic Store Enabled)   | 101 |

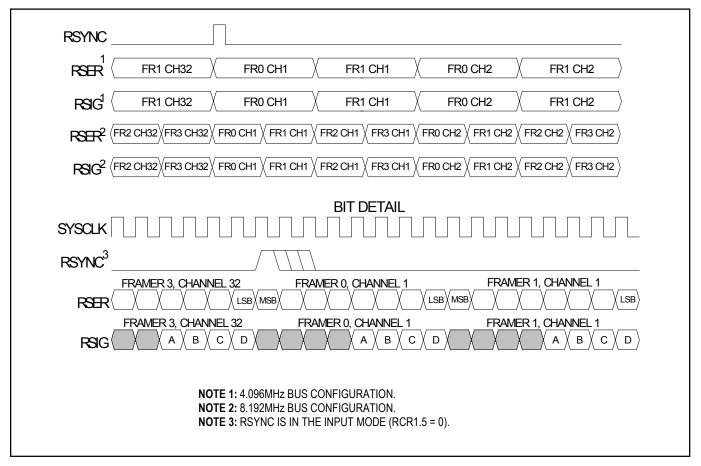

| Figure 18-5. Receive-Side Interleave Bus Operation, Byte Mode                     | 102 |

| Figure 18-6. Receive-Side Interleave Bus Operation, Frame Mode                    | 103 |

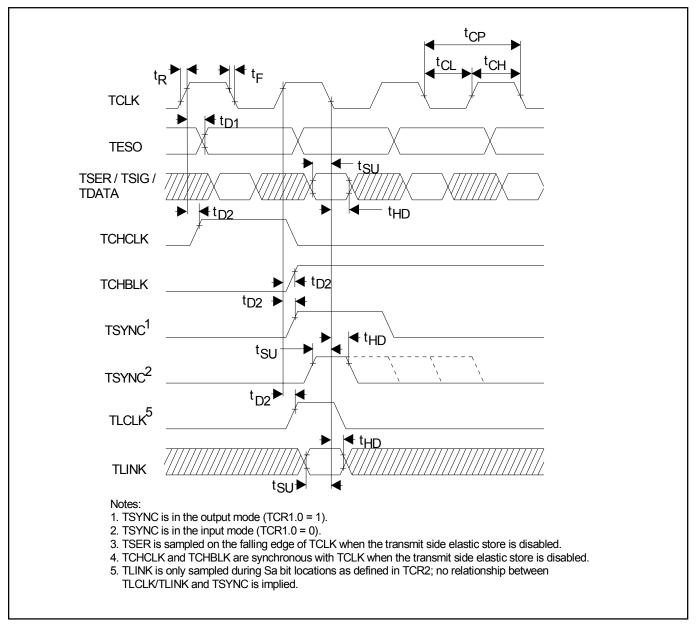

| Figure 18-7. Transmit-Side Timing                                                 | 104 |

| Figure 18-8. Transmit-Side Boundary Timing (with Elastic Store Disabled)          | 104 |

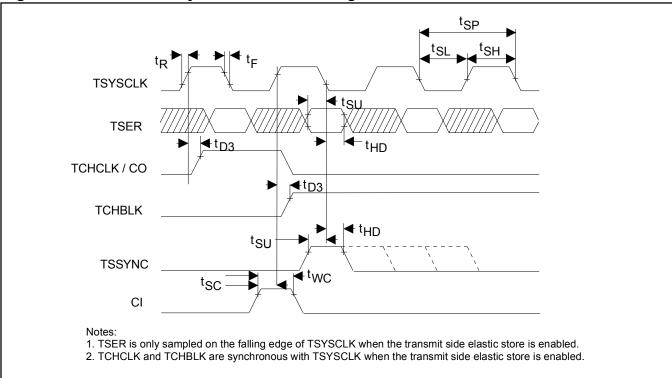

| Figure 18-9. Transmit-Side 1.544MHz Boundary Timing (with Elastic Store Enabled)  | 105 |

| Figure 18-10. Transmit-Side 2.048MHz Boundary Timing (with Elastic Store Enabled) | 105 |

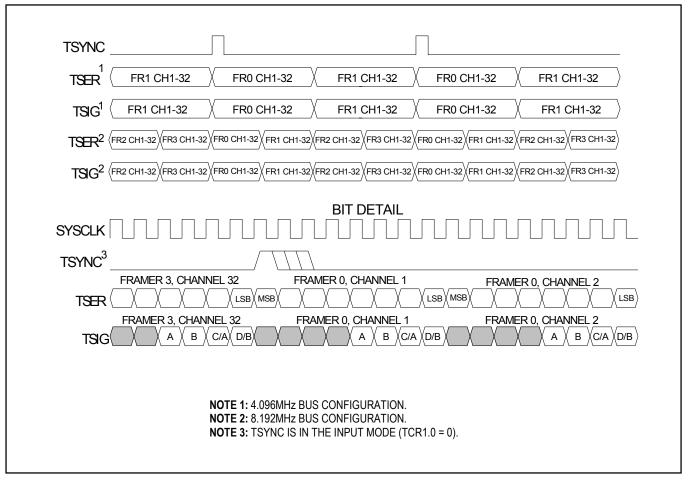

| Figure 18-11. Transmit-Side Interleave Bus Operation, Byte Mode                   | 106 |

| Figure 18-12. Transmit-Side Interleave Bus Operation, Frame Mode                  | 107 |

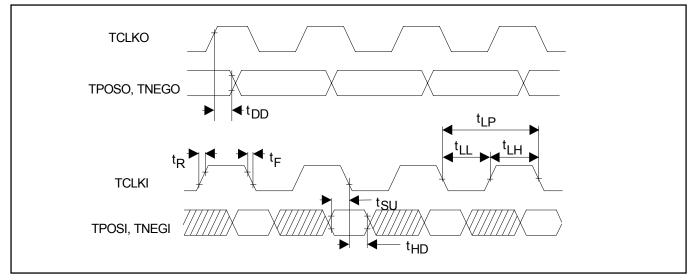

| Figure 18-13. G.802 Timing                                                        |     |

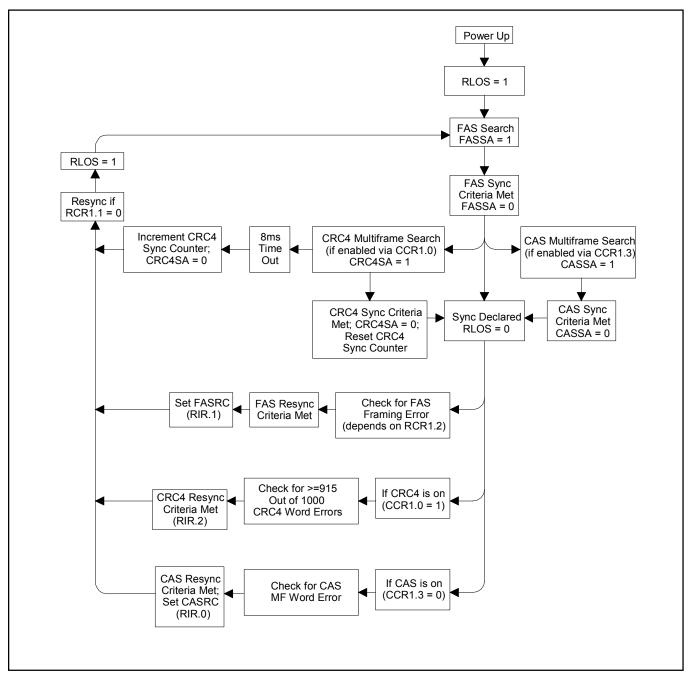

| Figure 18-14. DS21354/DS21554 Framer Synchronization Flowchart                    | 109 |

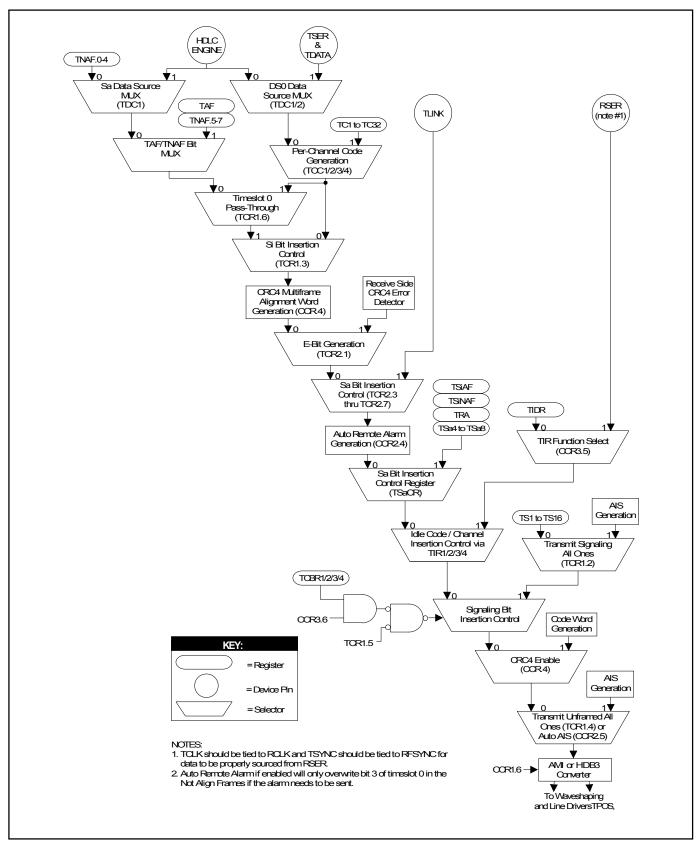

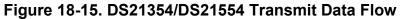

| Figure 18-15. DS21354/DS21554 Transmit Data Flow                                  |     |

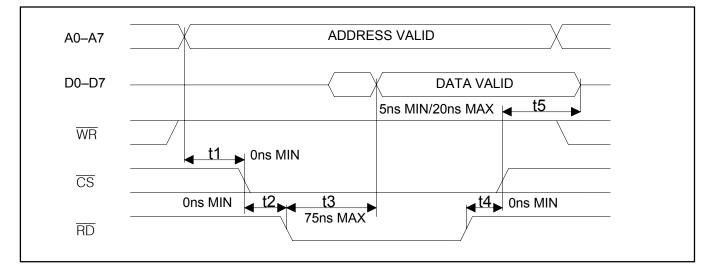

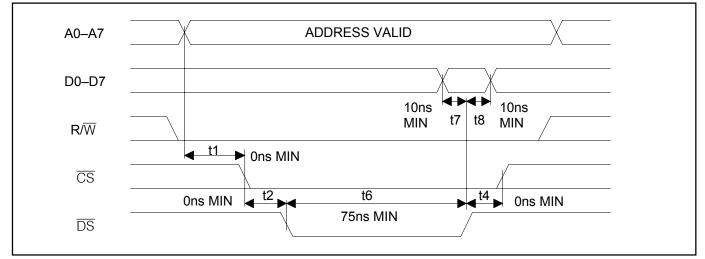

| Figure 20-1. Intel Bus Read Ac Timing (BTS = 0/MUX = 1)                           | 113 |

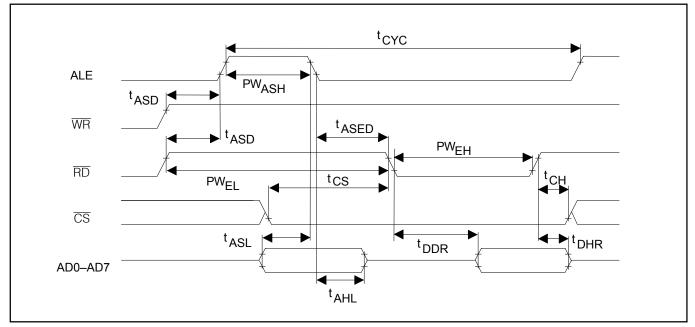

| Figure 20-2. Intel Bus Write Timing (BTS = 0/MUX = 1)                             | 113 |

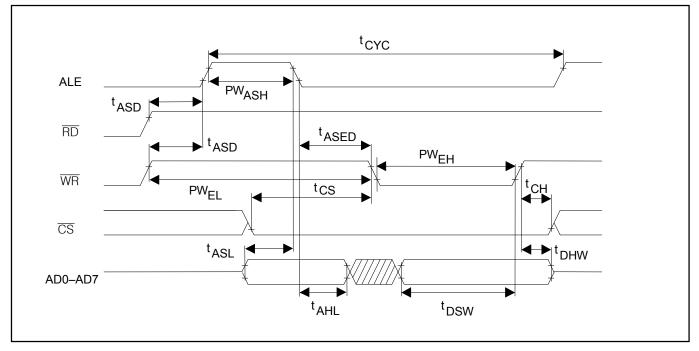

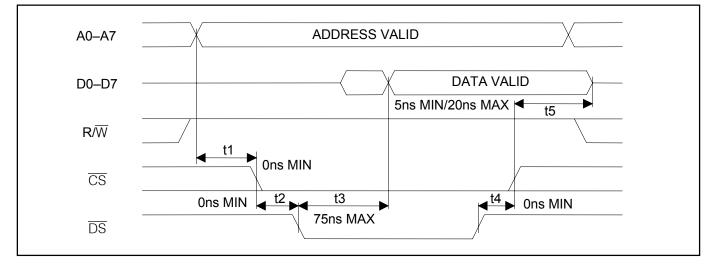

| Figure 20-3. Motorola Bus AC Timing (BTS = 1/MUX = 1)                             | 114 |

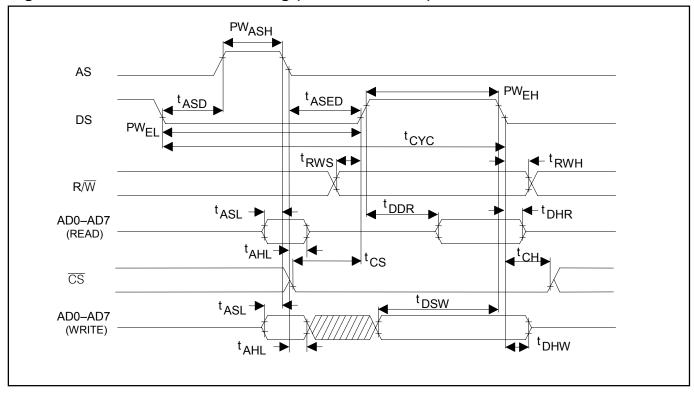

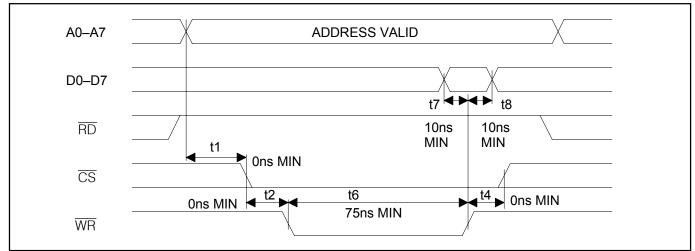

| Figure 20-4. Intel Bus Read AC Timing (BTS = 0/MUX = 0)                           |     |

| Figure 20-5. Intel Bus Write AC Timing (BTS = 0/MUX = 0)                          |     |

| Figure 20-6. Motorola Bus Read AC Timing (BTS = 1/MUX = 0)                        |     |

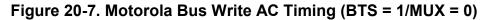

| Figure 20-7. Motorola Bus Write AC Timing (BTS = 1/MUX = 0)                       | 116 |

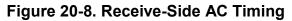

| Figure 20-8. Receive-Side AC Timing                                               | 118 |

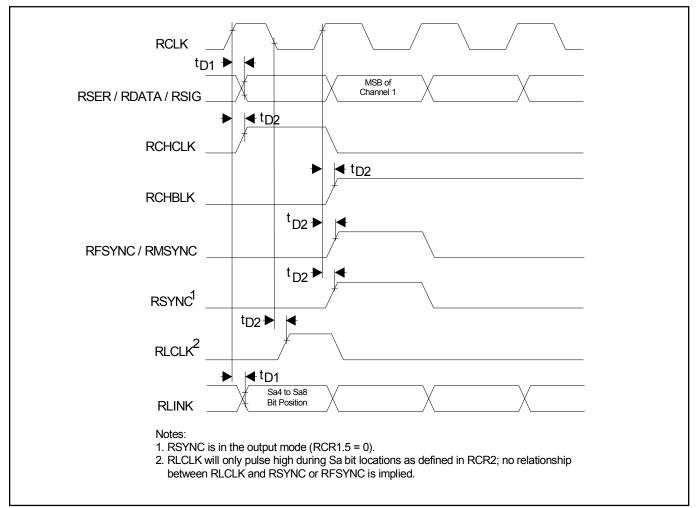

| Figure 20-9. Receive System Side AC Timing                                        | 119 |

| Figure 20-10. Receive Line Interface AC Timing                                    | 120 |

| Figure 20-11. Transmit-Side AC Timing                                             | 122 |

| Figure 20-12. Transmit System Side AC Timing                                      | 123 |

| Figure 20-13. Transmit Line Interface Side AC Timing                              | 123 |

## LIST OF TABLES

| Table 3-1. Pin Description Sorted by Pin Number            | 10 |

|------------------------------------------------------------|----|

| Table 3-2. Pin Description by Symbol                       | 12 |

| Table 4-1. Register Map Sorted by Address                  | 25 |

| Table 5-1. Device ID Bit Map                               | 30 |

| Table 5-2. SYNC/RESYNC Criteria                            |    |

| Table 6-1. Alarm Criteria                                  | 46 |

| Table 14-1. HDLC Controller Register List                  |    |

| Table 15-1. Line Build-Out Select in LICR for the DS21554  |    |

| Table 15-2. Line Build-Out Select in LICR for the DS21354  | 82 |

| Table 15-3. Transformer Specifications                     |    |

| Table 15-4. Receive Monitor Mode Gain                      |    |

| Table 16-1. Instruction Codes for IEEE 1149.1 Architecture | 95 |

| Table 16-2. ID Code Structure                              | 96 |

| Table 16-3. Device ID Codes                                |    |

| Table 16-4. Boundary Scan Control Bits                     | 97 |

| Table 17-1. IBO Master Device Select                       | 98 |

#### 1. INTRODUCTION

The DS21354/DS21554 are superset versions of the popular DS2153 and DS2154 SCTs offering the new features listed below. All the original features of the DS2153 and DS2154 have been retained, and the software created for the original devices is transferable into the DS21354/DS21554.

#### New Features in the DS21354 and DS21554

| FEATURE                                                              | SECTION                 |

|----------------------------------------------------------------------|-------------------------|

| HDLC controller with 64-Byte Buffers for Sa Bits or DS0s or Sub DS0s | <u>14</u>               |

| Interleaving PCM Bus Operation                                       | <u>17</u>               |

| IEEE 1149.1 JTAG-Boundary Scan Architecture                          | <u>16</u>               |

| 3.3V (DS21354 Only) Supply                                           | <u>1.1</u> and <u>2</u> |

| Line Interface Support for the G.703 2.048 Synchronization Interface | <u>15</u>               |

| Customer Disconnect Indication (101010) Generator                    | <u>5.6</u>              |

| Open-Drain Line Driver Option                                        | <u>5.6</u>              |

#### Additional Features in the DS21354 and DS21554

| FEATURE                                                                           | SECTION                    |

|-----------------------------------------------------------------------------------|----------------------------|

| Option for nonmultiplexed bus operation                                           | <u>1.1</u> and <u>20.2</u> |

| Crystal-less jitter attenuation                                                   | <u>15.3</u>                |

| Additional hardware signaling capability including:                               |                            |

| Receive signaling reinsertion to a backplane multiframe sync                      | 0                          |

| Availability of signaling in a separate PCM data stream                           | <u>9</u>                   |

| Signaling freezing Interrupt generated on change of signaling data                |                            |

| Improved receive sensitivity: 0 to -43dB                                          | <u>1.1</u>                 |

| Per-channel code insertion in both transmit and receive paths                     | <u>10</u>                  |

| Expanded access to Sa and Si bits                                                 | <u>13</u>                  |

| RCL, RLOS, RRA, and RAIS alarms now interrupt on change of state                  | <u>6</u>                   |

| 8.192MHz clock synthesizer                                                        | <u>1.1</u>                 |

| Per-channel loopback                                                              | <u>10</u>                  |

| Addition of hardware pins to indicate carrier loss and signaling freeze           | <u>1.1</u>                 |

| Line interface function can be completely decoupled from the framer/formatter to  |                            |

| allow:                                                                            |                            |

| Interface to optical, HDSL, and other NRZ interfaces                              | <u>1.1</u>                 |

| "tap" the transmit and receive bipolar data streams for monitoring purposes       |                            |

| Be able to corrupt data and insert framing errors, CRC errors, etc.               |                            |

| Transmit and receive elastic stores now have independent backplane clocks         | <u>1.1</u>                 |

| Ability to monitor one DS0 channel in both the transmit and receive paths         | <u>8</u>                   |

| Access to the data streams in between the framer/formatter and the elastic stores | <u>1.1</u>                 |

| AIS generation in the line interface that is independent of loopbacks             | <u>1.1</u> and <u>5</u>    |

| Transmit current limiter to meet the 50mA short circuit requirement               | <u>15</u>                  |

| Option to extend carrier loss criteria to a 1ms period as per ETS 300 233         | <u>5.4</u>                 |

| Automatic RAI generation to ETS 300 011 specifications                            | <u>5.4</u>                 |

#### 1.1. Functional Description

The analog AMI/HDB3 waveform off the E1 line is transformer coupled into the RRING and RTIP pins of the DS21354/554. The device recovers clock and data from the analog signal and passes it through the jitter attenuation mux to the receive-side framer where the digital serial stream is analyzed to locate the framing/multiframe pattern. The DS21354/DS21554 contain an active filter that reconstructs the analog-received signal for the nonlinear losses that occur in transmission. The devices have a usable receive sensitivity of 0 to -43dB, which allows the device to operate on cables over 2km in length. The receive-side framer locates FAS frame and CRC and CAS multiframe boundaries as well as detects incoming alarms including, carrier loss, loss of synchronization, AIS, and Remote Alarm. If needed, the receive-side elastic store can be enabled to absorb the phase and frequency differences between the recovered E1 data stream and an asynchronous backplane clock, which is provided at the RSYSCLK input. The clock applied at the RSYSCLK input can be either a 2.048MHz/4.096MHz/8.192MHz clock or a 1.544MHz clock.

The transmit-side framer is totally independent from the receive side in both the clock requirements and characteristics. Data off a backplane can be passed through a transmit-side elastic store if necessary. The transmit formatter provides the necessary frame/multiframe data overhead for E1 transmission.

**Reader's Note:** This data sheet assumes a particular nomenclature of the E1 operating environment. In each 125µs frame, there are 32 eight-bit time slots numbered 0 to 31. Time slot 0 is transmitted first and received first. These 32 time slots are also referred to as channels with a numbering scheme of 1 to 32. Time slot 0 is identical to channel 1, time slot 1 is identical to Channel 2, and so on. Each time slot (or channel) is made up of eight bits, which are numbered 1 to 8. Bit number 1 is the most significant bit (MSB) and is transmitted first. Bit number 8 is the least significant bit (LSB) and is transmitted last. The term "locked" refers to two clock signals that are phase or frequency locked, or derived from a common clock (i.e., a 1.544MHz clock may be locked to a 2.048MHz clock if they share the same 8kHz component). Throughout this data sheet, the following abbreviations are used:

| NAME  | FUNCTION                     |  |  |  |

|-------|------------------------------|--|--|--|

| FAS   | Frame-Alignment Signal       |  |  |  |

| CAS   | Channel-Associated Signaling |  |  |  |

| MF    | Multiframe                   |  |  |  |

| Si    | International Bits           |  |  |  |

| CRC4  | Cyclical Redundancy Check    |  |  |  |

| CCS   | Common-Channel Signaling     |  |  |  |

| Sa    | Additional Bits              |  |  |  |

| E-Bit | CRC4 Error Bits              |  |  |  |

## 1.2. Document Revision History

| REVISION | DESCRIPTION                                                                 |  |  |  |

|----------|-----------------------------------------------------------------------------|--|--|--|

| 012799   | Initial release                                                             |  |  |  |

| 012899   | Corrected TSYSCLK and RSYSCLK timing and added 4.096MHz and 8.192MHz timing |  |  |  |

| 020399   | Corrected definition and label of TUDR bit in the THIR register.            |  |  |  |

| 021199   | Corrected address of IBO register in text.                                  |  |  |  |

| 040199   | Added Receive Monitor Mode section                                          |  |  |  |

| 041599   | Added section on Protected Interfaces                                       |  |  |  |

| 050799   | Corrected pin number and description of FMS in JTAG section                 |  |  |  |

| 072999   | Added list of tables and figures                                            |  |  |  |

| 091499   | Added 10µF cap to interface examples                                        |  |  |  |

| 092399   | Corrected definition of $\overline{\text{DS}}$ in pin description.          |  |  |  |

| 072401   | Typo corrected in JTAG Test Access Port Pins.                               |  |  |  |

|          | Added note to the Receive Information Register, FAS Resync Criteria Met.    |  |  |  |

| 021004   | Corrected Figures 20-1, 20-2, 20-3 with respect to $\overline{CS}$ .        |  |  |  |

| 021004   | Corrected typo in Figure 18-14 (RCR1.1 reference corrected).                |  |  |  |

|          | Corrected formatting issues.                                                |  |  |  |

#### 2. BLOCK DIAGRAM

### 3. PIN DESCRIPTION

| PIN                            | NAME   | ТҮРЕ | FUNCTION                                           |  |

|--------------------------------|--------|------|----------------------------------------------------|--|

| 1                              | RCHBLK | 0    | Receive Channel Block                              |  |

| 2                              | JTMS   | Ι    | IEEE 1149.1 Test Mode Select                       |  |

| 3                              | 8MCLK  | 0    | 8.192 MHz Clock                                    |  |

| 4                              | JTCLK  | Ι    | IEEE 1149.1 Test Clock Signal                      |  |

| 5                              | JTRST  | Ι    | IEEE 1149.1 Test Reset, Active Low                 |  |

| 6                              | RCL    | 0    | Receive Carrier Loss                               |  |

| 7                              | JTDI   | Ι    | IEEE 1149.1 Test Data Input                        |  |

| 8, 9, 15,<br>23, 26, 27,<br>28 | N.C.   |      | No Connect. Do not connect any signal to this pin. |  |

| 10                             | JTDO   | 0    | IEEE 1149.1 Test Data Output                       |  |

| 11                             | BTS    | Ι    | Bus Type Select                                    |  |

| 12                             | LIUC   | Ι    | Line Interface Connect                             |  |

| 13                             | 8XCLK  | 0    | Eight Times Clock                                  |  |

| 14                             | TEST   | Ι    | Test                                               |  |

| 16                             | RTIP   | Ι    | Receive Analog Tip Input                           |  |

| 17                             | RRING  | Ι    | Receive Analog Ring Input                          |  |

| 18                             | RVDD   | —    | Receive Analog Positive Supply                     |  |

| 19, 20, 24                     | RVSS   | —    | Receive Analog Signal Ground                       |  |

| 21                             | MCLK   | Ι    | Master Clock Input                                 |  |

| 22                             | XTALD  | 0    | Quartz Crystal Driver                              |  |

| 25                             | ĪNT    | 0    | Interrupt, Active Low                              |  |

| 29                             | TTIP   | 0    | Transmit Analog Tip Output                         |  |

| 30                             | TVSS   | —    | Transmit Analog Signal Ground                      |  |

| 31                             | TVDD   | _    | Transmit Analog Positive Supply                    |  |

| 32                             | TRING  | 0    | Transmit Analog Ring Output                        |  |

| 33                             | TCHBLK | 0    | Transmit Channel Block                             |  |

| 34                             | TLCLK  | 0    | Transmit Link Clock                                |  |

| 35                             | TLINK  | Ι    | Transmit Link Data                                 |  |

| 36                             | CI     | Ι    | Carry In                                           |  |

| 37                             | TSYNC  | I/O  | Transmit Sync                                      |  |

| 38                             | TPOSI  | Ι    | Transmit Positive Data Input                       |  |

| 39                             | TNEGI  | Ι    | Transmit Negative Data Input                       |  |

| 40                             | TCLKI  | Ι    | Transmit Clock Input                               |  |

| 41                             | TCLKO  | 0    | Transmit Clock Output                              |  |

| 42                             | TNEGO  | 0    | Transmit Negative Data Output                      |  |

| 43                             | TPOSO  | 0    | Transmit Positive Data Output                      |  |

| 44, 61,<br>81,83               | DVDD   |      | Digital Positive Supply                            |  |

| 45, 60, 80,<br>84              | DVSS   | _    | Digital Signal Ground                              |  |

| 46                             | TCLK   | Ι    | Transmit Clock                                     |  |

| 47                             | TSER   | Ι    | Transmit Serial Data                               |  |

| 48                             | TSIG   | Ι    | Transmit Signaling Input                           |  |

Table 3-1. Pin Description Sorted by Pin Number

| PIN | NAME                                         | TYPE | FUNCTION                                     |  |

|-----|----------------------------------------------|------|----------------------------------------------|--|

| 49  | TESO                                         | 0    | Transmit Elastic Store Output                |  |

| 50  | TDATA                                        | Ι    | Transmit Data                                |  |

| 51  | TSYSCLK                                      | Ι    | Transmit System Clock                        |  |

| 52  | TSSYNC                                       | Ι    | Transmit System Sync                         |  |

| 53  | TCHCLK                                       | 0    | Transmit Channel Clock                       |  |

| 54  | СО                                           | 0    | Carry Out                                    |  |

| 55  | MUX                                          | Ι    | Bus Operation                                |  |

| 56  | D0/AD0                                       | I/O  | Data Bus Bit0/Address/Data Bus Bit 0         |  |

| 57  | D1/AD1                                       | I/O  | Data Bus Bit1/Address/Data Bus Bit 1         |  |

| 58  | D2/AD2                                       | I/O  | Data Bus Bit 2/Address/Data Bus 2            |  |

| 59  | D3/AD3                                       | I/O  | Data Bus Bit 3/Address/Data Bus Bit 3        |  |

| 62  | D4/AD4                                       | I/O  | Data Bus Bit4/Address/Data Bus Bit 4         |  |

| 63  | D5/AD5                                       | I/O  | Data Bus Bit 5/Address/Data Bus Bit 5        |  |

| 64  | D6/AD6                                       | I/O  | Data Bus Bit 6/Address/Data Bus Bit 6        |  |

| 65  | D7/AD7                                       | I/O  | Data Bus Bit 7/Address/Data Bus Bit 7        |  |

| 66  | A0                                           | Ι    | Address Bus Bit 0                            |  |

| 67  | A1                                           | Ι    | Address Bus Bit 1                            |  |

| 68  | A2                                           | Ι    | Address Bus Bit 2                            |  |

| 69  | A3                                           | Ι    | Address Bus Bit 3                            |  |

| 70  | A4                                           | Ι    | Address Bus Bit 4                            |  |

| 71  | A5                                           | Ι    | Address Bus Bit 5                            |  |

| 72  | A6                                           | Ι    | Address Bus Bit 6                            |  |

| 73  | ALE (AS)/A7                                  | Ι    | Address Latch Enable/Address Bus Bit 7       |  |

| 74  | $\overline{\text{RD}}(\overline{\text{DS}})$ | Ι    | Read Input (Data Strobe), Active Low         |  |

| 75  | $\overline{CS}$                              | Ι    | Chip Select, Active Low                      |  |

| 76  | FMS                                          | Ι    | Framer Mode Select                           |  |

| 77  | $\overline{WR}$ (R/ $\overline{W}$ )         | Ι    | Write Input (Read/Write), Active Low         |  |

| 78  | RLINK                                        | 0    | Receive Link Data                            |  |

| 79  | RLCLK                                        | 0    | Receive Link Clock                           |  |

| 82  | RCLK                                         | 0    | Receive Clock                                |  |

| 85  | RDATA                                        | 0    | Receive Data                                 |  |

| 86  | RPOSI                                        | Ι    | Receive Positive Data Input                  |  |

| 87  | RNEGI                                        | Ι    | Receive Negative Data Input                  |  |

| 88  | RCLKI                                        | Ι    | Receive Clock Input                          |  |

| 89  | RCLKO                                        | 0    | Receive Clock Output                         |  |

| 90  | RNEGO                                        | 0    | Receive Negative Data Output                 |  |

| 91  | RPOSO                                        | 0    | Receive Positive Data Output                 |  |

| 92  | RCHCLK                                       | 0    | Receive Channel Clock                        |  |

| 93  | RSIGF                                        | 0    | Receive Signaling Freeze Output              |  |

| 94  | RSIG                                         | 0    | Receive Signaling Output                     |  |

| 95  | RSER                                         | 0    | Receive Serial Data                          |  |

| 96  | RMSYNC                                       | 0    | Receive Multiframe Sync                      |  |

| 97  | RFSYNC                                       | 0    | Receive Frame Sync                           |  |

| 98  | RSYNC                                        | I/O  | Receive Sync                                 |  |

| 99  | RLOS/LOTC                                    | 0    | Receive Loss Of Sync/ Loss Of Transmit Clock |  |

| 100 | RSYSCLK                                      | Ι    | Receive System Clock                         |  |

| PIN                         | NAME                                                                                            | ТҮРЕ | FUNCTION                                           |

|-----------------------------|-------------------------------------------------------------------------------------------------|------|----------------------------------------------------|

| 3                           | 8MCLK                                                                                           | 0    | 8.192MHz Clock                                     |

| 13                          | 8XCLK                                                                                           | 0    | Eight-Times Clock                                  |

| 66                          | A0                                                                                              | Ι    | Address Bus Bit 0                                  |

| 67                          | A1                                                                                              | Ι    | Address Bus Bit 1                                  |

| 68                          | A2                                                                                              | Ι    | Address Bus Bit 2                                  |

| 69                          | A3                                                                                              | Ι    | Address Bus Bit 3                                  |

| 70                          | A4                                                                                              | Ι    | Address Bus Bit 4                                  |

| 71                          | A5                                                                                              | Ι    | Address Bus Bit 5                                  |

| 72                          | A6                                                                                              | Ι    | Address Bus Bit 6                                  |

| 73                          | ALE (AS)/A7                                                                                     | Ι    | Address Latch Enable/Address Bus Bit 7             |

| 11                          | BTS                                                                                             | Ι    | Bus Type Select                                    |

| 36                          | CI                                                                                              | Ι    | Carry In                                           |

| 54                          | СО                                                                                              | 0    | Carry Out                                          |

| 75                          | $\overline{CS}$                                                                                 | Ι    | Chip Select, Active Low                            |

| 56                          | D0/AD0                                                                                          | I/O  | Data Bus Bit0/ Address/Data Bus Bit 0              |

| 57                          | D1/AD1                                                                                          | I/O  | Data Bus Bit1/ Address/Data Bus Bit 1              |

| 58                          | D2/AD2                                                                                          | I/O  | Data Bus Bit 2/Address/Data Bus 2                  |

| 59                          | D3/AD3                                                                                          | I/O  | Data Bus Bit 3/Address/Data Bus Bit 3              |

| 62                          | D4/AD4                                                                                          | I/O  | Data Bus Bit4/Address/Data Bus Bit 4               |

| 63                          | D5/AD5                                                                                          | I/O  | Data Bus Bit 5/Address/Data Bus Bit 5              |

| 64                          | D6/AD6                                                                                          | I/O  | Data Bus Bit 6/Address/Data Bus Bit 6              |

| 65                          | D7/AD7                                                                                          | I/O  | Data Bus Bit 7/Address/Data Bus Bit 7              |

| 44, 61, 81, 83              | DVDD                                                                                            |      | Digital Positive Supply                            |

| 45, 60, 80, 84              | DVSS                                                                                            |      | Digital Signal Ground                              |

| 76                          | FMS                                                                                             | Ι    | Framer Mode Select                                 |

| 25                          | ĪNT                                                                                             | 0    | Interrupt                                          |

| 4                           | JTCLK                                                                                           | I    | IEEE 1149.1 Test Clock Signal                      |

| 7                           | JTDI                                                                                            | I    | IEEE 1149.1 Test Data Input                        |

| 10                          | JTDO                                                                                            | 0    | IEEE 1149.1 Test Data Output                       |

| 2                           | JTMS                                                                                            | I    | IEEE 1149.1 Test Mode Select                       |

| 5                           | JTRST                                                                                           | I    | IEEE 1149.1 Test Reset, Active Low                 |

| 12                          | LIUC                                                                                            | I    | Line Interface Connect                             |

| 21                          | MCLK                                                                                            | I    | Master Clock Input                                 |

| 55                          | MUX                                                                                             | I    | Bus Operation                                      |

| 8, 9, 15, 23, 26,<br>27, 28 | N.C.                                                                                            |      | No Connect. Do not connect any signal to this pin. |

| 1                           | RCHBLK                                                                                          | 0    | Receive Channel Block                              |

| 92                          | RCHELK                                                                                          | 0    | Receive Channel Block Receive Channel Clock        |

| 92<br>6                     | RCL                                                                                             | 0    | Receive Chamer Clock<br>Receive Carrier Loss       |

| 82                          | RCLK                                                                                            | 0    | Receive Clock                                      |

| 82<br>88                    | RCLKI                                                                                           | I    | Receive Clock Input                                |

| 89<br>89                    | RCLKO                                                                                           | 0    | Receive Clock Input<br>Receive Clock Output        |

| 74                          |                                                                                                 | I    | Read Input (Data Strobe), Active Low               |

|                             | $\frac{\overline{\text{RD}}(\overline{\text{DS}})}{\overline{\text{RD}} \overline{\text{ATA}}}$ |      |                                                    |

| 85                          | RDATA                                                                                           | 0    | Receive Data                                       |

| 97                          | RFSYNC                                                                                          | 0    | Receive Frame Sync                                 |

| 79                          | RLCLK                                                                                           | О    | Receive Link Clock                                 |

Table 3-2. Pin Description by Symbol

| PIN        | NAME                                                         | TYPE | FUNCTION                                    |

|------------|--------------------------------------------------------------|------|---------------------------------------------|

| 78         | RLINK                                                        | 0    | Receive Link Data                           |

| 99         | RLOS/LOTC                                                    | 0    | Receive Loss of Sync/Loss of Transmit Clock |

| 96         | RMSYNC                                                       | 0    | Receive Multiframe Sync                     |

| 87         | RNEGI                                                        | Ι    | Receive Negative Data Input                 |

| 90         | RNEGO                                                        | 0    | Receive Negative Data Output                |

| 86         | RPOSI                                                        | Ι    | Receive Positive Data Input                 |

| 91         | RPOSO                                                        | 0    | Receive Positive Data Output                |

| 17         | RRING                                                        | Ι    | Receive Analog Ring Input                   |

| 95         | RSER                                                         | 0    | Receive Serial Data                         |

| 94         | RSIG                                                         | 0    | Receive Signaling Output                    |

| 93         | RSIGF                                                        | 0    | Receive Signaling Freeze Output             |

| 98         | RSYNC                                                        | I/O  | Receive Sync                                |

| 100        | RSYSCLK                                                      | Ι    | Receive System Clock                        |

| 16         | RTIP                                                         | Ι    | Receive Analog Tip Input                    |

| 18         | RVDD                                                         |      | Receive Analog Positive Supply              |

| 19, 20, 24 | RVSS                                                         |      | Receive Analog Signal Ground                |

| 33         | TCHBLK                                                       | 0    | Transmit Channel Block                      |

| 53         | TCHCLK                                                       | 0    | Transmit Channel Clock                      |

| 46         | TCLK                                                         | Ι    | Transmit Clock                              |

| 40         | TCLKI                                                        | Ι    | Transmit Clock Input                        |

| 41         | TCLKO                                                        | 0    | Transmit Clock Output                       |

| 50         | TDATA                                                        | Ι    | Transmit Data                               |

| 49         | TESO                                                         | 0    | Transmit Elastic Store Output               |

| 14         | TEST                                                         | Ι    | Test                                        |

| 34         | TLCLK                                                        | 0    | Transmit Link Clock                         |

| 35         | TLINK                                                        | Ι    | Transmit Link Data                          |

| 39         | TNEGI                                                        | Ι    | Transmit Negative Data Input                |

| 42         | TNEGO                                                        | 0    | Transmit Negative Data Output               |

| 38         | TPOSI                                                        | Ι    | Transmit Positive Data Input                |

| 43         | TPOSO                                                        | 0    | Transmit Positive Data Output               |

| 32         | TRING                                                        | 0    | Transmit Analog Ring Output                 |

| 47         | TSER                                                         | Ι    | Transmit Serial Data                        |

| 48         | TSIG                                                         | Ι    | Transmit Signaling Input                    |

| 52         | TSSYNC                                                       | Ι    | Transmit System Sync                        |

| 37         | TSYNC                                                        | I/O  | Transmit Sync                               |

| 51         | TSYSCLK                                                      | Ι    | Transmit System Clock                       |

| 29         | TTIP                                                         | 0    | Transmit Analog Tip Output                  |

| 31         | TVDD                                                         |      | Transmit Analog Positive Supply             |

| 30         | TVSS                                                         | —    | Transmit Analog Signal Ground               |

| 77         | $\overline{\mathrm{WR}}  (\mathrm{R}/\overline{\mathrm{W}})$ | Ι    | Write Input (Read/Write), Active Low        |

| 22         | XTALD                                                        | 0    | Quartz Crystal Driver                       |

#### 3.1. Pin Function Description

#### 3.1.1. Transmit-Side Pins

Signal Name:TCLKSignal Description:Transmit ClockSignal Type:InputA 2.048MHz primary clock. Used to clock data through the transmit side formatter.

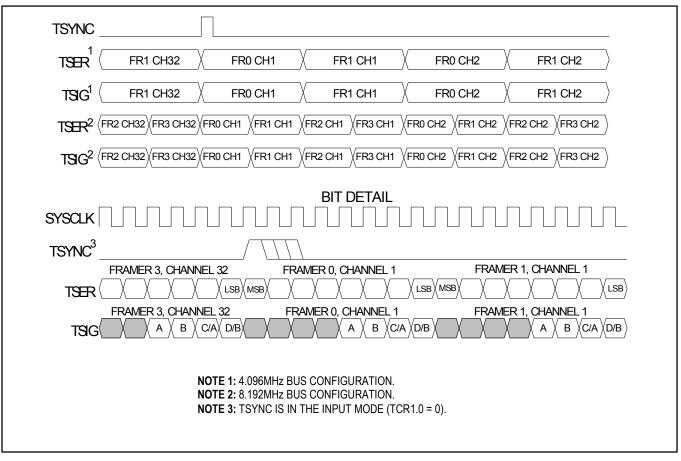

Signal Name:TSERSignal Description:Transmit Serial DataSignal Type:InputTransmit NRZ serial data.Sampled on the falling edge of TCLK when the transmit side elastic store isdisabled.Sampled on the falling edge of TSYSCLK when the transmit side elastic store is enabled.

| Signal Name:        | TCHCLK                        |

|---------------------|-------------------------------|

| Signal Description: | <b>Transmit Channel Clock</b> |

| Signal Type:        | Output                        |

| A 256kHz clock that | nulses high during the LSB    |

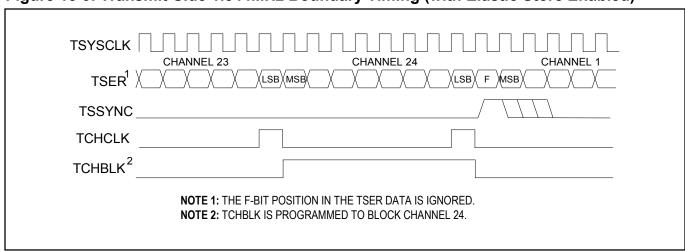

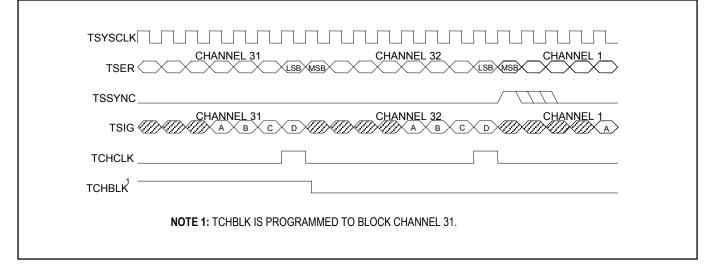

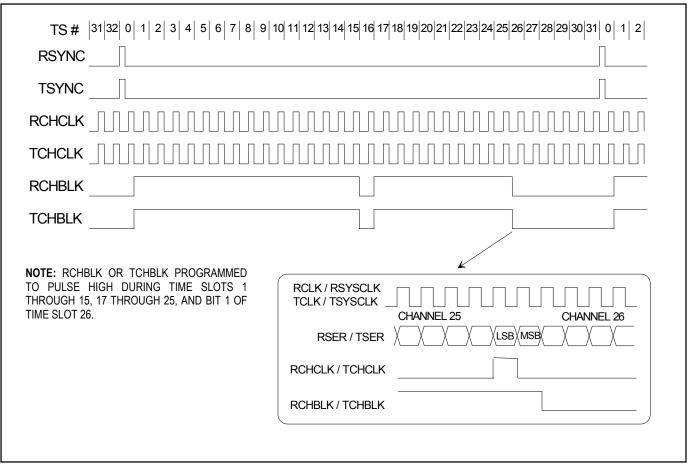

A 256kHz clock that pulses high during the LSB of each channel. Synchronous with TCLK when the transmit side elastic store is disabled. Synchronous with TSYSCLK when the transmit side elastic store is enabled. Useful for parallel to serial conversion of channel data.

| Signal Name:        | TCHBLK                 |

|---------------------|------------------------|

| Signal Description: | Transmit Channel Block |

| Signal Type:        | Output                 |

A user-programmable output that can be forced high or low during any of the 32 E1 channels. Synchronous with TCLK when the transmit side elastic store is disabled. Synchronous with TSYSCLK when the transmit-side elastic store is enabled. Useful for blocking clocks to a serial UART or LAPD controller in applications where not all E1 channels are used such as Fractional E1, 384kbps (H0), 768kbps, or ISDN–PRI. Also useful for locating individual channels in drop-and-insert applications, for external per-channel loopback, and for per-channel conditioning. See Section <u>12</u> for details.

Signal Name:TSYSCLKSignal Description:Transmit System ClockSignal Type:Input1.544MHz, 2.048MHz, 4.096MHz, or 8.192MHz clock. Only used when the transmit-side elastic storefunction is enabled. Should be tied low in applications that do not use the transmit-side elastic store. SeeSection 17 for details on 4.096MHz and 8.192MHz operation using the Interleave Bus Option.

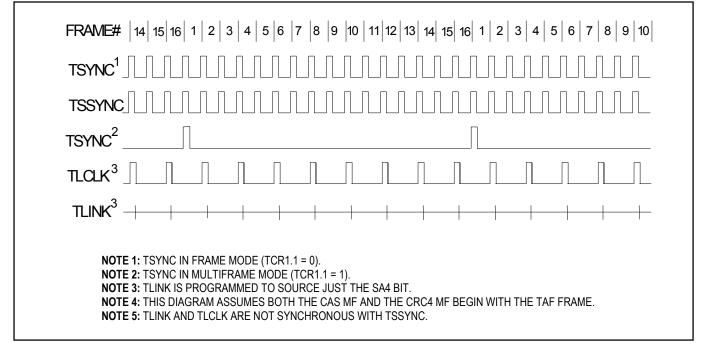

Signal Name:TLCLKSignal Description:Transmit Link ClockSignal Type:Output4kHz to 20kHz demand clock (Sa bits) for the TLINK input. See Section 17 for details.

Signal Name:TLINKSignal Description:Transmit Link DataSignal Type:InputIf enabled this pin will be sampled on the fallir

If enabled, this pin will be sampled on the falling edge of TCLK for data insertion into any combination of the Sa bit positions (Sa4 to Sa8). See Section 13 for details.

| Signal Name:        | TSYNC                |

|---------------------|----------------------|

| Signal Description: | <b>Transmit Sync</b> |

| Signal Type:        | Input/Output         |

A pulse at this pin will establish either frame or multiframe boundaries for the transmit side. Via TCR1.1, the DS21354/DS21554 can be programmed to output either a frame or multiframe pulse at this pin. This pin can also be configured as an input via TCR1.0. See Section <u>18</u> for details.

Signal Name:TSSYNCSignal Description:Transmit System SyncSignal Type:InputOnly used when the transmit-side elastic store is en

Only used when the transmit-side elastic store is enabled. A pulse at this pin will establish either frame or multiframe boundaries for the transmit side. Should be tied low in applications that do not use the transmit-side elastic store.

Signal Name:TSIGSignal Description:Transmit Signaling InputSignal Type:Input

When enabled, this input will sample signaling bits for insertion into outgoing PCM E1 data stream. Sampled on the falling edge of TCLK when the transmit-side elastic store is disabled. Sampled on the falling edge of TSYSCLK when the transmit-side elastic store is enabled.

Signal Name:TESOSignal Description:Transmit Elastic Store Data OutputSignal Type:OutputUpdated on the risingedge of TCLK with data out of the transmit-side elastic store whether the elasticstore is enabled or not.This pin is normally tied to TDATA.

Signal Name:TDATASignal Description:Transmit DataSignal Type:InputSampled on the falling edge of TCLK with data to be clocked through the transmit-side formatter. Thispin is normally tied to TESO.

Signal Name:**TPOSO**Signal Description:**Transmit Positive Data Output**Signal Type:**Output**Updated on the rising edge of TCLKO with the bipolar

Updated on the rising edge of TCLKO with the bipolar data out of the transmit-side formatter. Can be programmed to source NRZ data via the Output Data Format (TCR2.2) control bit. This pin is normally tied to TPOSI.

Signal Name:TNEGOSignal Description:Transmit Negative Data OutputSignal Type:OutputUpdated on the rising edge of TCLKO with the bipolar data out of the transmit-side formatter. This pin is<br/>normally tied to TNEGI.

Signal Name:TCLKOSignal Description:Transmit Clock OutputSignal Type:OutputBuffered output of signal that is clocking data through the transmit-side formatter. This pin is normallytied to TCLKI.

Signal Name:TPOSISignal Description:Transmit Positive Data InputSignal Type:InputSampled on the falling edge of TCLKI for data to be tr

Sampled on the falling edge of TCLKI for data to be transmitted out onto the T1 line. Can be internally connected to TPOSO by tying the LIUC pin high. TPOSI and TNEGI can be tied together in NRZ applications.

Signal Name:TNEGISignal Description:Transmit Negative Data InputSignal Type:InputSampled on the falling edge of TCLKI for data to be transmitted out onto the T1 line. Can be internally<br/>connected to TNEGO by tying the LIUC pin high. TPOSI and TNEGI can be tied together in NRZ<br/>applications.

Signal Name:TCLKISignal Description:Transmit Clock InputSignal Type:InputLine interface transmit clock. Can be internally connected to TCLKO by tying the LIUC pin high.

#### 3.1.2. Receive-Side Pins

Signal Name:RLINKSignal Description:Receive Link DataSignal Type:OutputUpdated with the fully recovered E1 data stream on the rising edge of RCLK.

Signal Name:RLCLKSignal Description:Receive Link ClockSignal Type:Output4kHz to 20kHz clock (Sa bits) for the RLINK output. See Section 13 for details.

Signal Name:RCLKSignal Description:Receive ClockSignal Type:Output2.048MHz clock that is used to clock data through the receive-side framer.

| Signal Name:        | RCHCLK                       |

|---------------------|------------------------------|

| Signal Description: | <b>Receive Channel Clock</b> |

| Signal Type:        | Output                       |

| A 05(111 1 1 1 1    |                              |

A 256kHz clock that pulses high during the LSB of each channel. Synchronous with RCLK when the receive-side elastic store is disabled. Synchronous with RSYSCLK when the receive-side elastic store is enabled. Useful for parallel to serial conversion of channel data.

| Signal Name:        | RCHBLK                       |

|---------------------|------------------------------|

| Signal Description: | <b>Receive Channel Block</b> |

| Signal Type:        | Output                       |

A user-programmable output that can be forced high or low during any of the 32 E1 channels. Synchronous with RCLK when the receive-side elastic store is disabled. Synchronous with RSYSCLK when the receive-side elastic store is enabled. Useful for blocking clocks to a serial UART or LAPD controller in applications where not all E1 channels are used such as Fractional E1, 384kbps service, 768kbps, or ISDN–PRI. Also useful for locating individual channels in drop-and-insert applications, for external per-channel loopback, and for per-channel conditioning. See Section <u>10</u> for details.

Signal Name:RSERSignal Description:Receive Serial DataSignal Type:OutputReceived NRZ serial data.Updated on rising edges of RCLK when the receive-side elastic store isdisabled.Updated on the rising edges of RSYSCLK when the receive-side elastic store is enabled.

Signal Name:RSYNCSignal Description:Receive SyncSignal Type:Input/Output

An extracted pulse, one RCLK wide, is output at this pin that identifies either frame or CAS/CRC multiframe boundaries. If the receive-side elastic store is enabled, then this pin can be enabled to be an input at which a frame or multiframe boundary pulse synchronous with RSYSCLK is applied.

Signal Name:RFSYNCSignal Description:Receive Frame SyncSignal Type:OutputAn extracted 8kHz pulse, one RCLK wide, is output at this pin that identifies frame boundaries.

Signal Name:RMSYNCSignal Description:Receive Multiframe SyncSignal Type:Output

If the receive-side elastic store is enabled, an extracted pulse, one RSYSCLK wide, is output at this pin that identifies multiframe boundaries. If the receive-side elastic store is disabled, then this output will output multiframe boundaries associated with RCLK.

Signal Name:RDATASignal Description:Receive DataSignal Type:OutputUpdated on the rising edge of RCLK with the data out of the receive-side framer.

Signal Name:RSYSCLKSignal Description:Receive System ClockSignal Type:Input1.544MHz, 2.048MHz, 4.096MHz, or 8.192MHz clock. Only used when the receive-side elastic storefunction is enabled. Should be tied low in applications that do not use the receive-side elastic store. SeeSection 17 for details on 4.096MHz and 8.192MHz operation using the Interleave Bus Option.

| Signal Name:            | RSIG                                                                               |

|-------------------------|------------------------------------------------------------------------------------|

| Signal Description:     | Receive Signaling Output                                                           |

| Signal Type:            | Output                                                                             |

| Outputs signaling bits  | in a PCM format. Updated on rising edges of RCLK when the receive-side elastic     |

| store is disabled. Upda | ted on the rising edges of RSYSCLK when the receive-side elastic store is enabled. |

Signal Name:RLOS/LOTCSignal Description:Receive Loss of Sync / Loss of Transmit ClockSignal Type:OutputA dual function output that is controlled by the TCR2 0 control bit. This pin

A dual function output that is controlled by the TCR2.0 control bit. This pin can be programmed to either toggle high when the synchronizer is searching for the frame and multiframe or to toggle high if the TCLK pin has not been toggled for  $5\mu$ s.

Signal Name:RCLSignal Description:Receive Carrier LossSignal Type:OutputSet high when the line interface detects a carrier loss.

Signal Name:RSIGFSignal Description:Receive Signaling FreezeSignal Type:Output

Set high when the signaling data is frozen via either automatic or manual intervention. Used to alert downstream equipment of the condition.

Signal Name:8MCLKSignal Description:8MHz ClockSignal Type:OutputAn 8.192MHz clock output that is referenced to the clock that is output at the RCLK pin.

Signal Name:RPOSOSignal Description:Receive Positive Data InputSignal Type:OutputUpdated on the rising edge of RCLKO with bipolar data out of the line interface. This pin is normally tiedto RPOSI.

Signal Name:RNEGOSignal Description:Receive Negative Data InputSignal Type:OutputUpdated on the rising edge of RCLKO with the bipolar data out of the line interface. This pin is normallytied to RNEGI.

Signal Name:RCLKOSignal Description:Receive Clock OutputSignal Type:OutputBuffered recovered clock from the T1 line. This pin is normally tied to RCLKI.

Signal Name:**RPOSI**Signal Description:**Receive Positive Data Input**Signal Type:**Input**Sampled on the falling edge of RCLKI for data to be clocked through the receive-side framer. RPOSI and<br/>RNEGI can be tied together for a NRZ interface. Can be internally connected to RPOSO by tying the<br/>LIUC pin high.

Signal Name:RNEGISignal Description:Receive Negative Data InputSignal Type:InputSampled on the falling edge of RCLKI for data to be clocked through the receive-side framer. RPOSI andRNEGI can be tied together for a NRZ interface. Can be internally connected to RNEGO by tying theLIUC pin high.

Signal Name:RCLKISignal Description:Receive Clock InputSignal Type:InputClock used to clock data through the receive-side

Clock used to clock data through the receive-side framer. This pin is normally tied to RCLKO. Can be internally connected to RCLKO by tying the LIUC pin high.

#### 3.1.3. Parallel Control Port Pins

| Signal Name:        | INT       |

|---------------------|-----------|

| Signal Description: | Interrupt |

| Signal Type:        | Output    |

Active-low, open-drain output that flags host controller during conditions and change of conditions defined in the Status Registers 1 and 2 and the HDLC Status Register.

| Signal Name:             | FMS                                                                                                          |

|--------------------------|--------------------------------------------------------------------------------------------------------------|

| Signal Description:      | Framer Mode Select                                                                                           |

| Signal Type:             | Input                                                                                                        |

| Selects the DS2154 m     | ode when high or the DS21354/DS21554 mode when low. If high, the JTRST is                                    |

| internally pulled low. I | f low, $\overline{\text{JTRST}}$ has normal JTAG functionality. This pin has a 10k $\Omega$ pullup resistor. |

Signal Name:

TEST

Signal Description:

Tri-State Control

Signal Type:

Input

Set high to tri-state all output and I/O pins (including the parallel control port). Set low for normal operation. Useful in board-level testing.

| Signal Name:                                                                                  | MUX           |  |

|-----------------------------------------------------------------------------------------------|---------------|--|

| Signal Description:                                                                           | Bus Operation |  |

| Signal Type:                                                                                  | Input         |  |

| Set low to select nonmultiplexed bus operation. Set high to select multiplexed bus operation. |               |  |

Signal Name:AD0 to AD7Signal Description:Data Bus [D0 to D7] or Address/Data BusSignal Type:InputIn nonmultiplexed bus operation (MUX = 0), serves as the data bus. In multiplexed bus operation (MUX = 1), serves as an 8-bit multiplexed address/data bus.

Signal Name:A0 to A6Signal Description:Address BusSignal Type:InputIn nonmultiplexed bus operation (MUX = 0), serves as the address bus. In multiplexed bus operation (MUX = 1), these pins are not used and should be tied low.

| Signal Name:                                        | BTS                                                                                                         |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Signal Description:                                 | Bus Type Select                                                                                             |

| Signal Type:                                        | Input                                                                                                       |

| Strap high to select M                              | otorola bus timing; strap low to select Intel bus timing. This pin controls the                             |

| function of the $\overline{RD}$ ( $\overline{DS}$ ) | ), ALE (AS), and $\overline{WR}$ (R/ $\overline{W}$ ) pins. If BTS = 1, then these pins assume the function |

| listed in parentheses ().                           |                                                                                                             |

Signal Name:

$\overline{RD}$  ( $\overline{DS}$ )

Signal Description:

Read Input—Data Strobe

Signal Type:

Input

In Intel Mode

$\overline{RD}$  determines when data is read from the device. In Motorola Mode,  $\overline{DS}$

In Intel Mode,  $\overline{RD}$  determines when data is read from the device. In Motorola Mode,  $\overline{DS}$  is used to write to the device. See the *Bus Timing Diagrams* section.

Signal Name: $\overline{CS}$ Signal Description:Chip SelectSignal Type:InputMust be low to read or write to the device. $\overline{CS}$  is an active-low signal.

Signal Name:ALE (AS)/A7Signal Description:Address Latch Enable (Address Strobe) or A7Signal Type:InputIn nonmultiplexed bus operation (MUX = 0), serves as the upper address bit. In multiplexed bus operation (MUX = 1), serves to demultiplex the bus on a positive-going edge.

Signal Name: $\overline{WR}$  (R/ $\overline{W}$ )Signal Description:Write Input (Read/Write)Signal Type:Input $\overline{WR}$  is an active-low signal.

#### 3.1.4. JTAG Test Access Port Pins

| Signal Name:        | JTRST                  |

|---------------------|------------------------|

| Signal Description: | IEEE 1149.1 Test Reset |

| Signal Type:        | Input                  |

This signal is used to asynchronously reset the test access port controller. At power up,  $\overline{\text{JTRST}}$  must be toggled from low to high. This action will set the device into JTAG DEVICE ID mode enabling the test access port features. This pin has a 10k $\Omega$  pullup resistor. When FMS = 1, this pin is tied low internally. Tie  $\overline{\text{JTRST}}$  low if JTAG is not used and the framer is in DS21354/DS21554 mode (FMS low).

Signal Name:JTMSSignal Description:IEEE 1149.1 Test Mode SelectSignal Type:InputThis pin is sampled on the rising edge of JTCLK and is used to place the test access port into the variousdefined IEEE 1149.1 states. This pin has a 10kΩ pullup resistor.

| Signal Name:              | JTCLK                                                                       |

|---------------------------|-----------------------------------------------------------------------------|

| Signal Description:       | IEEE 1149.1 Test Clock Signal                                               |

| Signal Type:              | Input                                                                       |

| This signal is used to sh | nift data into JTDI on the rising edge and out of JTDO on the falling edge. |

| Signal Name:          | JTDI                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------|

| Signal Description:   | IEEE 1149.1 Test Data Input                                                            |

| Signal Type:          | Input                                                                                  |

| Test instructions and | data are clocked into this pin on the rising edge of JTCLK. This pin has a $10k\Omega$ |

Test instructions and data are clocked into this pin on the rising edge of JTCLK. This pin has a  $10k\Omega$  pullup resistor.

| Signal Name:             | JTDO                                                                                |

|--------------------------|-------------------------------------------------------------------------------------|

| Signal Description:      | IEEE 1149.1 Test Data Output                                                        |

| Signal Type:             | Output                                                                              |

| Test instructions and d  | ata are clocked out of this pin on the falling edge of JTCLK. If not used, this pin |

| should be left unconnect | eted.                                                                               |

#### 3.1.5. Interleave Bus Operation Pins

| Signal Name:        | CI       |

|---------------------|----------|

| Signal Description: | Carry In |

| Signal Type:        | Input    |

A rising edge on this pin causes RSER and RSIG to come out of high-Z state and TSER and TSIG to start sampling on the next rising edge of RSYSCLK/TSYSCLK beginning an I/O sequence of 8 or 256 bits of data. This pin has a  $10k\Omega$  pullup resistor.

| Signal Name:            | CO                    |

|-------------------------|-----------------------|

| Signal Description:     | Carry Out             |

| Signal Type:            | Output                |

| An output that is set h | igh when the last hit |

An output that is set high when the last bit of the 8 or 256 IBO output sequence has occurred on RSER and RSIG.

#### 3.1.6. Line Interface Pins

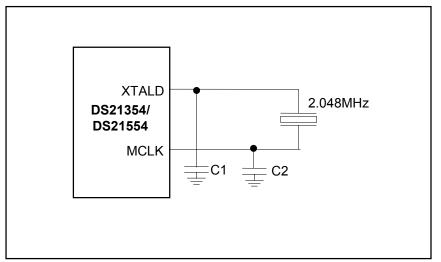

Signal Name:MCLKSignal Description:Master Clock InputSignal Type:Input

A 2.048MHz (±50ppm) clock source with TTL levels is applied at this pin. This clock is used internally for both clock/data recovery and for jitter attenuation. A quartz crystal of 2.048MHz may be applied across MCLK and XTALD instead of the TTL level clock source.

| Signal Name:            | XTALD                   |

|-------------------------|-------------------------|

| Signal Description:     | Quartz Crystal Driver   |

| Signal Type:            | Output                  |

| A quartz crystal of 2.0 | 48MHz may be applied ac |

A quartz crystal of 2.048MHz may be applied across MCLK and XTALD instead of a TTL level clock source at MCLK. Leave open circuited if a TTL clock source is applied at MCLK.

| Signal Name:        | 8XCLK                    |

|---------------------|--------------------------|

| Signal Description: | <b>Eight-Times</b> Clock |

| Signal Type:        | Output                   |

| A 16.384MHz clock   | that is frequency locked |

A 16.384MHz clock that is frequency locked to the 2.048MHz clock provided from the clock/data recovery block (if the jitter attenuator is enabled on the receive side) or from the TCLKI pin (if the jitter attenuator is enabled on the transmit side). Can be internally disabled via TEST2 register if not needed.

| Signal Name:          | LIUC                           |

|-----------------------|--------------------------------|

| Signal Description:   | Line Interface Connect         |

| Signal Type:          | Input                          |

| Tie low to separate t | the line interface circuitry f |

Tie low to separate the line interface circuitry from the framer/formatter circuitry and activate the TPOSI/TNEGI/TCLKI/RPOSI/RNEGI/RCLKI pins. Tie high to connect the line interface circuitry to the framer/formatter circuitry and deactivate the TPOSI/TNEGI/TCLKI/RPOSI/RNEGI/RCLKI pins. When LIUC is tied high, the TPOSI/TNEGI/TCLKI/ RPOSI/RNEGI/RCLKI pins should be tied low.

Signal Name:RTIP and RRINGSignal Description:Receive Tip and RingSignal Type:InputAnalog inputs for clock recovery circuitry. These pins connect via a 1:1 transformer to the E1 line. SeeSection 15 for details.

Signal Name:TTIP and TRINGSignal Description:Transmit Tip and RingSignal Type:OutputAnalog line-driver outputs. These pins connect via a step-up transformer to the E1 line. See Section 15for details

#### 3.1.7. Supply Pins

Signal Name:DVDDSignal Description:Digital Positive SupplySignal Type:Supply5.0V ±5% (DS21554) or 3.3V ±5% (DS21354). Should be tied to the RVDD and TVDD pins.