# System Basis Chip with LIN Transceiver

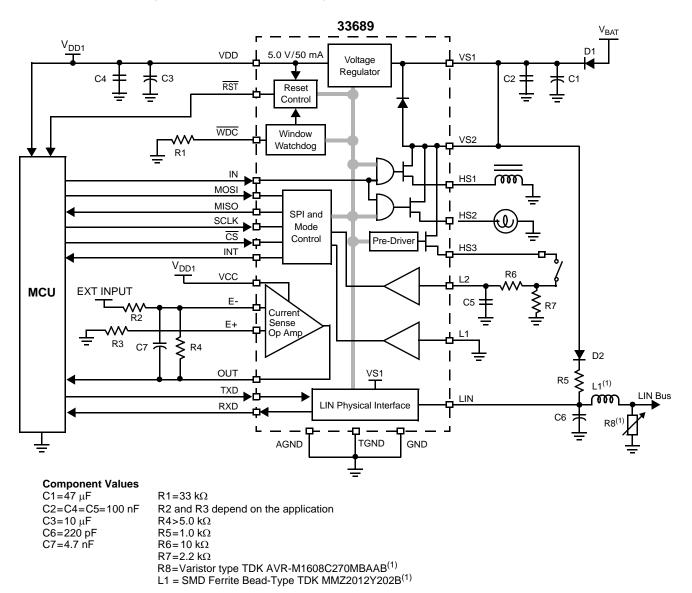

The 33689 is a serial peripheral interface (SPI) controlled system basis chip (SBC) that combines many frequently used functions in an MCU-based system plus a local interconnect network (LIN) transceiver. Applications include power window, mirror, and seat controls. The 33689 has a 5.0 V, 50 mA low dropout regulator with full protection and reporting features. The device provides full SPIreadable diagnostics and a selectable timing watchdog for detecting errant operation.

The LIN transceiver waveshaping circuitry can be disabled for higher data rates. One 50 mA and two 150 mA high side switches with output protection are available to drive inductive or resistive loads. The 150 mA switches can be pulse-width modulated (PWM).

Two high voltage inputs are available for contact monitoring or as external wake-up inputs. A current sense operational amplifier is available for load current monitoring.

The 33689 has three operational modes:

- Normal (all functions available)

- Sleep (VDD OFF, wake-up via LIN bus or wake-up inputs)

- Stop (VDD ON, wake-up via MCU, LIN bus, or wake-up inputs)

#### Features

- Full-duplex SPI Interface at frequencies up to 4.0 MHz

- LIN transceiver capable to 100 kbps with waveshaping capability

- 5.0 V low dropout regulator with full fault detection and protection

- One 50 mA and two 150 mA protected high side switches

- · Current sense operational amplifier

- · Compatible with LIN 2.0 specification package

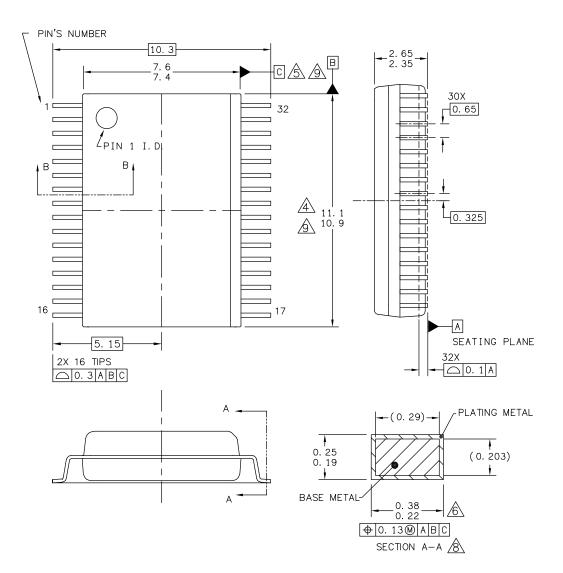

| ORDERING INFORMATION                                                                                   |                  |          |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|------------------|----------|--|--|--|--|

| Device         Temperature           (Add R2 Suffix for Tape and Reel)         Range (T <sub>A</sub> ) |                  | Package  |  |  |  |  |

| MC33689DPEW                                                                                            | -40 °C to 125 °C | 32 SOICW |  |  |  |  |

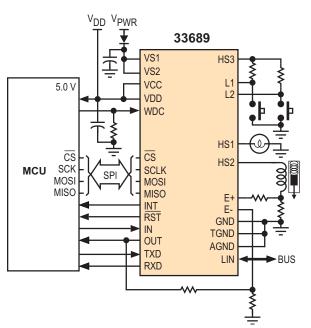

Figure 1. 33689 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products. © Freescale Semiconductor, Inc., 2006-2012. All rights reserved.

# 33689D

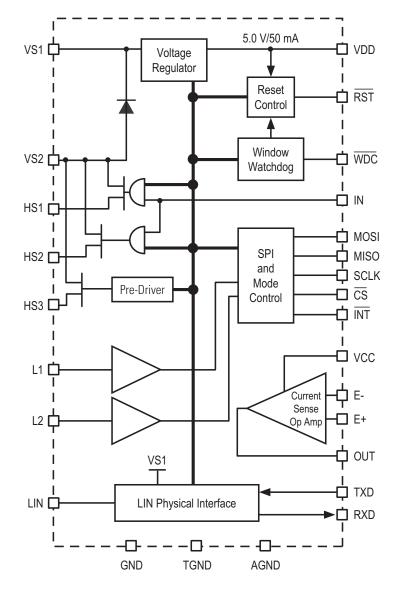

# **INTERNAL BLOCK DIAGRAM**

Figure 2. 33689 Simplified Internal Block Diagram

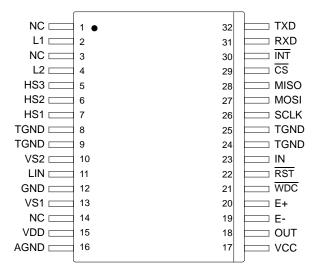

# **PIN CONNECTIONS**

## Table 1. 33689 32-SOICW Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 19.

| Pin          | Pin Name | Formal Name                               | Pin Function | Definition                                                                              |

|--------------|----------|-------------------------------------------|--------------|-----------------------------------------------------------------------------------------|

| 1, 3, 14     | NC       | No Connect                                | N/A          | No internal connection to these pins.                                                   |

| 2, 4         | L1, L2   | Level Inputs 1 and 2                      | Input        | Inputs from external switches or from logic circuitry.                                  |

| 5–7          | HS3-HS1  | High-Side Driver<br>Outputs 3 through 1   | Output       | High-side (HS) drive power outputs. SPI-controlled for driving system loads.            |

| 8, 9, 24, 25 | TGND     | Thermal Ground                            | N/A          | Thermal ground pins for the device.                                                     |

| 10           | VS2      | Voltage Supply 2                          | Input        | Supply pin for the high-side switches HS1, HS2, and HS3.                                |

| 11           | LIN      | LIN Bus                                   | Input/Output | Bidirectional pin that represents the single-wire bus transmitter and receiver.         |

| 12           | GND      | Ground                                    | N/A          | Electrical ground pin for the device.                                                   |

| 13           | VS1      | Voltage Supply 1                          | Input        | Supply pin for the 5.0 V regulator, the LIN physical interface, and the internal logic. |

| 15           | VDD      | 5.0 V Regulator<br>Output                 | Output       | Output of the 5.0 V regulator.                                                          |

| 16           | AGND     | Analog Ground                             | N/A          | Analog ground pin for voltage regulator and current sense operational amplifier.        |

| 17           | VCC      | Power Supply In                           | Input        | 5.0 V supply for the internal current sense operational amplifier.                      |

| 18           | OUT      | Amplifier Output                          | Output       | Output of the internal current sense operational amplifier.                             |

| 19           | E-       | Amplifier Inverted<br>Input               | Input        | Inverted input of the internal current sense operational amplifier.                     |

| 20           | E+       | Amplifier Non-Inverted<br>Input           | Input        | Non-inverted input of the internal current sense operational amplifier.                 |

| 21           | WDC      | Watchdog<br>Configuration<br>(Active Low) | Reference    | Configuration pin for the watchdog timer.                                               |

## Table 1. 33689 32-SOICW Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page <u>19</u>.

| Pin | Pin Name | Formal Name                      | Pin Function | Definition                                                                                               |

|-----|----------|----------------------------------|--------------|----------------------------------------------------------------------------------------------------------|

| 22  | RST      | Reset Output<br>(Active LOW)     | Output       | 5.0 V regulator and watchdog reset output pin.                                                           |

| 23  | IN       | PWM Input Control                | Input        | External input PWM control pin for high-side switches HS1 and HS2.                                       |

| 26  | SCLK     | Serial Data Clock                | Input        | Clock input for the SPI of the 33689.                                                                    |

| 27  | MOSI     | Master Out Slave In              | Input        | SPI data received by the 33689.                                                                          |

| 28  | MISO     | Master In Slave Out              | Output       | SPI data sent to the MCU by the 33689. When $\overline{CS}$ is HIGH, pin is in the high-impedance state. |

| 29  | CS       | Chip Select<br>(Active LOW)      | Input        | SPI control chip select input pin.                                                                       |

| 30  | INT      | Interrupt Output<br>(Active LOW) | Output       | This output pin reports faults to the MCU when an enabled interrupt condition occurs.                    |

| 31  | RXD      | Receiver Output                  | Output       | Receiver output of the LIN interface and reports the state of the bus voltage.                           |

| 32  | TXD      | Transmitter Input                | Input        | Transmitter input of the LIN interface and controls the state of the bus output.                         |

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                         | Symbol                           | Value                         | Unit |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------|------|

| ELECTRICAL RATINGS                                                                                                              |                                  |                               |      |

| V <sub>PWR</sub> Supply Voltage at VS1 and VS2                                                                                  |                                  |                               | V    |

| Continuous                                                                                                                      | V <sub>SUPDC</sub>               | -0.3 to 27                    |      |

| Transient (Load Dump)                                                                                                           | V <sub>SUPTR</sub>               | 40                            |      |

| Supply Voltage at VDD and VCC                                                                                                   | V <sub>DD</sub>                  | -0.3 to 5.5                   | V    |

| Output Current at VDD                                                                                                           | I <sub>DD</sub>                  | Internally Limited            | А    |

| Logic Input Voltage at MOSI, SCLK, CS, IN, and TXD                                                                              | V <sub>INLOG</sub>               | -0.3 to V <sub>DD</sub> +0.3  | V    |

| Logic Output Voltage at MISO, INT, RST, and RXD                                                                                 | V <sub>OUTLOG</sub>              | -0.3 to V <sub>DD</sub> +0.3  | V    |

| Input Voltage at E+ and E-                                                                                                      | $V_{E+}/V_{E-}$                  | -0.3 to 7.0                   | V    |

| Input Current at E+ and E-                                                                                                      | I <sub>E+</sub> /I <sub>E-</sub> | ±20                           | mA   |

| Output Voltage at OUT                                                                                                           | V <sub>OUT</sub>                 | -0.3 to V <sub>CC</sub> +0.33 | V    |

| Output Current at OUT                                                                                                           | I <sub>OUT</sub>                 | ±20                           | mA   |

| Input Voltage at L1 and L2                                                                                                      |                                  |                               | V    |

| DC Input with a 33 k $\Omega$ Resistor                                                                                          | V <sub>LXDC</sub>                | -18 to 40                     |      |

| Transient Input with External Component (per ISO7637 Specification) (See Figure 4, page 6)                                      | V <sub>LXTR</sub>                | ±100                          |      |

| Input/Output Voltage at LIN                                                                                                     |                                  |                               | V    |

| DC Voltage                                                                                                                      | V <sub>BUSDC</sub>               | -18 to 40                     |      |

| Transient Input Voltage with specified External Component (per ISO7637<br>Specification) (See <u>Figure 4</u> , page <u>6</u> ) | V <sub>BUSTR</sub>               | -150 to 100                   |      |

| DC Output Voltage at HS1 and HS2                                                                                                |                                  |                               | V    |

| Positive                                                                                                                        | V <sub>HS+</sub>                 | V <sub>VS2</sub> + 0.3        |      |

| Negative                                                                                                                        | V <sub>HS-</sub>                 | Internally Clamped            |      |

| DC Output Voltage at HS3                                                                                                        | V <sub>HS3</sub>                 | -0.3 to V <sub>VS2</sub> +0.3 | V    |

| ESD Voltage, Human Body Model <sup>(1)</sup>                                                                                    | V <sub>ESD1</sub>                |                               | V    |

| GND Configured as Ground. TGND and AGND Configured as I/O Pins                                                                  |                                  |                               |      |

| LIN, L1, and L2                                                                                                                 |                                  | . 1000                        |      |

| All Other Pins                                                                                                                  |                                  | ±4000<br>±2000                |      |

| ESD Voltage, Charge Device Model <sup>(1)</sup>                                                                                 | V <sub>ESD2</sub>                | TZUUU                         | V    |

|                                                                                                                                 | *ESD2                            | ±750                          | v    |

| Corner Pins (Pins 1, 16, 17, and 32)<br>All other Pins (Pins 2–15 and 18–31)                                                    |                                  | ±500                          |      |

Notes

1. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), ESD2 testing is performed in accordance with the Charge Device Model, Robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

## Table 2. Maximum Ratings(continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                               | Symbol              | Value      | Unit |

|-----------------------------------------------------------------------|---------------------|------------|------|

| THERMAL RATINGS                                                       | ·                   |            |      |

| Operating Temperature                                                 |                     |            | °C   |

| Ambient                                                               | T <sub>A</sub>      | -40 to 125 |      |

| Junction                                                              | Τ <sub>J</sub>      | -40 to 150 |      |

| Storage Temperature                                                   | T <sub>STG</sub>    | -55 to 165 | °C   |

| Thermal Resistance, Junction-to-Ambient                               | R <sub>0JA</sub>    | 80         | °C/W |

| Peak Package Reflow Temperature During Solder Mounting <sup>(2)</sup> | T <sub>SOLDER</sub> | 240        | °C   |

Notes

2. Pin soldering temperature is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause permanent damage to the device.

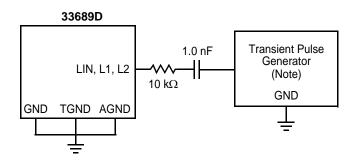

Note Waveform per ISO 7637-1. Test Pulses 1, 2, 3a, and 3b.

#### Figure 4. ISO 7637 Test Setup for LIN, L1, and L2 Pins

## STATIC ELECTRICAL CHARACTERISTICS

## Table 3. Static Electrical Characteristics

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                              | Symbol                 | Min  | Тур   | Max  | Unit     |

|---------------------------------------------------------------------------------------------|------------------------|------|-------|------|----------|

| /S1 AND VS2 INPUT PINS (DEVICE POWER SUPPLY)                                                | ·                      |      |       |      | <u>.</u> |

| Supply Input Voltage                                                                        |                        |      |       |      | V        |

| Nominal DC                                                                                  | V <sub>SUP</sub>       | 5.5  | —     | 18   |          |

| Load Dump                                                                                   | V <sub>SUPLD</sub>     | —    | —     | 40   |          |

| Jump Start <sup>(3)</sup>                                                                   | V <sub>SUPJS</sub>     | —    | —     | 27   |          |

| Supply Input Current <sup>(4)</sup>                                                         |                        |      |       |      |          |

| Normal Mode, I <sub>OUT</sub> at VDD = 10 mA, LIN Recessive State                           | I <sub>SUP(NORM)</sub> | —    | 5.0   | 8.0  | mA       |

| Sleep Mode, VDD OFF, $V_{SUP} \leq 13.5 \text{ V}$                                          | I <sub>SLEEP</sub>     | _    | 35    | 45   | μA       |

| Stop Mode, VDD ON with $I_{OUT}$ < 100 $\mu A,  V_{SUP}$ $\leq$ 13.5 V                      | ISTOP                  | —    | 60    | 75   | μA       |

| Input Threshold Voltage (Normal Mode, Interrupt Generated)                                  |                        |      |       |      | V        |

| Fall Early Warning, Bit VSUV Set                                                            | V <sub>SUVEW</sub>     | 5.7  | 6.1   | 6.6  |          |

| Overvoltage Warning, Bit VSOV Set                                                           | V <sub>SOVW</sub>      | 18   | 19.75 | 20.5 |          |

| Hysteresis <sup>(5)</sup>                                                                   | V <sub>HYS</sub>       |      |       |      |          |

| VSUV Flag                                                                                   |                        | —    | 1.0   | —    | V        |

| VSOV Flag                                                                                   |                        | —    | 220   | —    | mV       |

| /DD OUTPUT PIN (EXTERNAL 5.0 V OUTPUT FOR MCU USE) $^{(6)}$                                 | ·                      |      |       |      | <u>.</u> |

| Output Voltage                                                                              | V <sub>DDOUT</sub>     |      |       |      | V        |

| $I_{\mbox{\scriptsize DD}}$ from 2.0 mA to 50 mA, 5.5 V < V_{\mbox{\scriptsize SUP}} < 27 V |                        | 4.75 | 5.0   | 5.25 |          |

| Dropout Voltage <sup>(7)</sup>                                                              | V <sub>DDDROP</sub>    |      |       |      | V        |

| $I_{DD} = 50 \text{ mA}$                                                                    |                        | —    | 0.1   | 0.2  |          |

|                                                                                             |                        |      |       |      | +        |

| $I_{DD} = 50 \text{ mA}$                       |                  | _   | 0.1 | 0.2 |    |

|------------------------------------------------|------------------|-----|-----|-----|----|

| Output Current Limitation <sup>(8)</sup>       | I <sub>DD</sub>  | 50  | 120 | 200 | mA |

| Overtemperature Pre-warning (Junction)         | T <sub>PRE</sub> |     |     |     | °C |

| Normal Mode, Interrupt Generated, Bit VDDT Set |                  | 120 | 135 | 160 |    |

| Thermal Shutdown (Junction)                    | T <sub>SD</sub>  |     |     |     | °C |

| Normal Mode                                    |                  | 165 | 170 | _   |    |

Notes

3. Device is fully functional. All features are operating. An overtemperature fault may occur.

4. Total current ( $I_{VS1}$  +  $I_{VS2}$ ) at VS1 and VS2 pins is measured at the ground pins.

5. Parameter guaranteed by design; however, it is not production tested.

6. Specification with external capacitor 2.0  $\mu$ F < C < 10  $\mu$ F and 200 m $\Omega \le$  ESR  $\le$  10  $\Omega$ . Normal mode. Low ESR electrolytic capacitor values up to 47  $\mu$ F can be used.

7. Measured when the voltage has dropped 100 mV below its nominal value.

8. Internally limited. Total 5.0 V regulator current. A 5.0 mA current for the Current Sense Operational Amplifier operation is included. Digital outputs are supplied from VDD.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                     | Symbol              | Min                 | Тур  | Max                  | Unit |

|----------------------------------------------------------------------------------------------------|---------------------|---------------------|------|----------------------|------|

| VDD OUTPUT PIN (5.0 V OUTPUT FOR MCU USE) (CONTIN                                                  | UED) <sup>(9)</sup> | •                   |      |                      |      |

| Temperature Threshold Difference                                                                   | T <sub>DIFF</sub>   |                     |      |                      | °C   |

| Normal Mode (T <sub>SD</sub> - T <sub>PRE</sub> )                                                  |                     | 20                  | 30   | 40                   |      |

| V <sub>SUP</sub> Range for Reset Active                                                            | V <sub>SUPR</sub>   |                     |      |                      | V    |

| $0.5 \text{ V} < \text{V}_{\text{DD}} < \text{V}_{\text{DD}} (\text{V}_{\overline{\text{RSTTH}}})$ |                     | 4.0                 | —    | —                    |      |

| Line Regulation                                                                                    | V <sub>LR1</sub>    |                     |      |                      | mV   |

| 5.5 V < V <sub>SUP</sub> < 27 V, I <sub>DD</sub> = 10 mA                                           |                     | —                   | 20   | 150                  |      |

| Load Regulation                                                                                    | V <sub>LD1</sub>    |                     |      |                      | mV   |

| 1.0 mA < I <sub>DD</sub> < 50 mA                                                                   |                     | —                   | 10   | 150                  |      |

| VDD OUTPUT PIN IN STOP MODE                                                                        |                     | •                   |      |                      |      |

| Output Voltage <sup>(10)</sup>                                                                     | V <sub>DDS</sub>    |                     |      |                      | V    |

| $I_{DD} \le 2.0 \text{ mA}$                                                                        |                     | 4.75                | 5.0  | 5.25                 |      |

| Output Current Capability <sup>(11)</sup>                                                          | IDDS                | 4.0                 | 8.0  | 14                   | mA   |

| Line Regulation                                                                                    | V <sub>LRS</sub>    |                     |      |                      | mV   |

| $5.5 \text{ V} < \text{V}_{\text{SUP}} < 27 \text{ V}, \text{ I}_{\text{DD}} = 2.0 \text{ mA}$     |                     | —                   | 10   | 100                  |      |

| Load Regulation                                                                                    | V <sub>LDS</sub>    |                     |      |                      | mV   |

| 1.0 mA < I <sub>DD</sub> < 5.0 mA                                                                  |                     | —                   | 40   | 150                  |      |

| RST OUTPUT PIN IN NORMAL AND STOP MODES                                                            |                     |                     |      |                      |      |

| Reset Threshold Voltage                                                                            | VRSTTH              | 4.5                 | 4.7  | V <sub>DD</sub> -0.2 | V    |

| Low-Level Output Voltage                                                                           | V <sub>OL</sub>     |                     |      |                      | V    |

| $I_{O}$ = 1.5 mA, 4.5 V < V <sub>SUP</sub> < 27 V                                                  |                     | 0.0                 | —    | 0.9                  |      |

| High-Level Output Current                                                                          | I <sub>ОН</sub>     |                     |      |                      | μA   |

| 0.0 V < V <sub>OUT</sub> < 0.7 V <sub>DD</sub>                                                     |                     | —                   | -275 | —                    |      |

| Reset Pulldown Current                                                                             | I <sub>PDRST</sub>  |                     |      |                      | mA   |

| Internally Limited, $V_{DD}$ < 4.0 V, $V_{RST}$ = 4.6 V                                            |                     | 1.5                 | _    | 8.0                  |      |

| N INPUT PIN                                                                                        |                     |                     |      |                      |      |

| Low-Level Input Voltage                                                                            | V <sub>IL</sub>     | -0.3                | _    | 0.3 V <sub>DD</sub>  | V    |

| High-Level Input Voltage                                                                           | V <sub>IH</sub>     | 0.7 V <sub>DD</sub> | —    | V <sub>DD</sub> +0.3 | V    |

| Input Current                                                                                      | I <sub>IN</sub>     |                     |      |                      | μΑ   |

| $0.0 \text{ V} < \text{V}_{\text{IN}} < \text{V}_{\text{DD}}$                                      |                     | -10                 | —    | 10                   |      |

Notes

9. Specification with external capacitor 2.0  $\mu$ F < C < 10  $\mu$ F and 200 m $\Omega \le$  ESR  $\le$  10  $\Omega$ . Normal mode. Low ESR electrolytic capacitor values up to 47  $\mu$ F can be used.

10. When switching from Normal mode to Stop mode or from Stop mode to Normal mode, the voltage can vary within the output voltage specification.

11. When  $I_{\mbox{DD}}$  is above  $I_{\mbox{DDS}},$  the 33689 enters the Reset mode.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                  | Symbol              | Min                   | Тур | Max                  | Unit |

|-----------------------------------------------------------------|---------------------|-----------------------|-----|----------------------|------|

| MISO SPI OUTPUT PIN                                             |                     |                       |     |                      |      |

| Low-Level Output Voltage                                        | V <sub>OL</sub>     |                       |     |                      | V    |

| I <sub>OUT</sub> = 1.5 mA                                       |                     | 0.0                   | —   | 1.0                  |      |

| High-Level Output Voltage                                       | V <sub>OH</sub>     |                       |     |                      | V    |

| I <sub>OUT</sub> = 250 μA                                       |                     | V <sub>DD</sub> - 0.9 | —   | V <sub>DD</sub>      |      |

| Tri-Stated MISO Output Leakage Current                          | I <sub>HZ</sub>     |                       |     |                      | μΑ   |

| $0.0 \text{ V} < \text{V}_{\text{MISO}} < \text{V}_{\text{DD}}$ |                     | -2.0                  |     | 2.0                  |      |

| MOSI, SCLK, CS SPI INPUT PINS                                   |                     |                       |     |                      |      |

| Low-Level Input Voltage                                         | V <sub>IL</sub>     | -0.3                  | —   | 0.3 V <sub>DD</sub>  | V    |

| High-Level Input Voltage                                        | V <sub>IH</sub>     | 0.7 V <sub>DD</sub>   | —   | V <sub>DD</sub> +0.3 | V    |

| Pullup Input Current on CS                                      | I <sub>PU</sub> CS  |                       |     |                      | μA   |

| $V_{\overline{CS}} = 4.0 V$                                     |                     | -100                  | _   | -20                  |      |

| MOSI, SCLK Input Current                                        | I <sub>IN</sub>     |                       |     |                      | μA   |

| $0.0 \text{ V} < \text{V}_{\text{IN}} < \text{V}_{\text{DD}}$   |                     | -10                   | _   | 10                   |      |

| INT OUTPUT PIN                                                  |                     |                       |     |                      |      |

| Low-Level Output Voltage                                        | V <sub>OL</sub>     |                       |     |                      | V    |

| I <sub>O</sub> = 1.5 mA                                         |                     | 0.0                   | _   | 0.9                  |      |

| High-Level Output Voltage                                       | V <sub>OH</sub>     |                       |     |                      | V    |

| I <sub>O</sub> = -250 μA                                        |                     | V <sub>DD</sub> -0.9  | —   | V <sub>DD</sub>      |      |

| WDC PIN                                                         |                     |                       |     |                      |      |

| External Resistor Range                                         | R <sub>EXT</sub>    | 10                    |     | 100                  | kΩ   |

| HS1 AND HS2 HIGH-SIDE OUTPUT PINS                               |                     |                       |     | -                    |      |

| Output Clamp Voltage                                            | V <sub>CL</sub>     |                       |     |                      | V    |

| I <sub>OUT</sub> = -100 mA                                      |                     | -6.0                  | —   | —                    |      |

| Output Drain-to-Source ON Resistance                            | R <sub>DS(ON)</sub> |                       |     |                      | Ω    |

| T <sub>A</sub> = 25°C, I <sub>OUT</sub> -150 mA                 | (0.1)               |                       | 2.0 | 2.5                  |      |

| T <sub>A</sub> = 125°C, I <sub>OUT</sub> -150 mA                |                     | _                     | _   | 4.5                  |      |

| T <sub>A</sub> = 125°C, I <sub>OUT</sub> -120 mA                |                     | -                     | 3.0 | 4.0                  |      |

| Output Current Limitation                                       | I <sub>LIM</sub>    | 300                   | 430 | 600                  | mA   |

| Overtemperature Shutdown <sup>(12)</sup>                        | T <sub>OTSD</sub>   | 155                   | _   | 190                  | °C   |

| Output Leakage Current                                          | I <sub>LEAK</sub>   | _                     | _   | 10                   | μA   |

Notes

12. When overtemperature occurs, switch is turned off and latched off. Flag is set in SPI Register. Refer to description on page 26.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                   | Symbol              | Min  | Тур | Max                  | Unit |

|--------------------------------------------------|---------------------|------|-----|----------------------|------|

| 1S3 HIGH-SIDE OUTPUT PIN                         |                     |      |     |                      |      |

| Output Drain-to-Source ON Resistance             | R <sub>DS(ON)</sub> |      |     |                      | Ω    |

| T <sub>A</sub> = 25°C, I <sub>OUT</sub> -50 mA   |                     | _    | 5.5 | 7.0                  |      |

| T <sub>A</sub> = 125°C, I <sub>OUT</sub> -50 mA  |                     | -    | -   | 10                   |      |

| T <sub>A</sub> = 125°C, I <sub>OUT</sub> -30 mA  |                     | _    | 10  | 14                   |      |

| Output Current Limitation                        | I <sub>LIM</sub>    | 60   | 100 | 200                  | mA   |

| Overtemperature Shutdown <sup>(13)</sup>         | T <sub>OTSD</sub>   | 155  | —   | 190                  | °C   |

| Output Leakage Current                           | I <sub>LEAK</sub>   | —    | -   | 10                   | μA   |

| OUT, E+, AND E- PINS AT CURRENT SENSE OPERATIONA |                     |      | •   |                      |      |

| Input Voltage – Rail-to-Rail at E+ and E-        | V <sub>IMC</sub>    | -0.1 | _   | V <sub>CC</sub> +0.1 | V    |

| Output Voltage Range at OUT                      | V <sub>OUT</sub>    |      |     |                      | V    |

| With ±1.0 mA Output Load Current                 |                     | 0.1  | —   | V <sub>CC</sub> -0.1 |      |

| With ±5.0 mA Output Load Current                 |                     | 0.3  | _   | V <sub>CC</sub> -0.3 |      |

| Input Bias Current                               | Ι <sub>Β</sub>      | —    | -   | 250                  | nA   |

| Input Offset Voltage                             | V <sub>IO</sub>     | -15  | -   | 15                   | mV   |

| Input Offset Current                             | I <sub>O</sub>      | -100 | —   | 100                  | nA   |

| 1 AND L2 INPUT PINS                              |                     |      |     |                      |      |

| Low-Voltage Detection Input Threshold Voltage    | V <sub>THL</sub>    |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                 |                     | 2.0  | 2.5 | 3.0                  |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                  |                     | 2.5  | 3.0 | 3.5                  |      |

| 18 V < V <sub>SUP</sub> < 27 V                   |                     | 2.7  | 3.2 | 3.7                  |      |

| High-Voltage Detection Input Threshold Voltage   | V <sub>THH</sub>    |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                 |                     | 2.7  | 3.3 | 3.8                  |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                  |                     | 3.0  | 4.0 | 4.5                  |      |

| 18 V < V <sub>SUP</sub> < 27 V                   |                     | 3.5  | 4.2 | 4.7                  |      |

| Input Hysteresis                                 | V <sub>HYS</sub>    |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 27 V                  |                     | 0.5  | -   | 1.3                  |      |

| Input Current                                    | I <sub>IN</sub>     |      |     |                      | μA   |

| -0.2 V < V <sub>IN</sub> < 40 V                  |                     | -10  | _   | 10                   |      |

Notes

13. When overtemperature occurs, switch is turned off and latched off. Flag is set in SPI Register. Refer to description on page 26.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                    | Symbol              | Min                   | Тур | Max   | Unit             |

|-----------------------------------------------------------------------------------|---------------------|-----------------------|-----|-------|------------------|

| RXD OUTPUT PIN (LIN PHYSICAL LAYER)                                               |                     |                       |     |       |                  |

| Low-Level Output Voltage                                                          | V <sub>OL</sub>     |                       |     |       | V                |

| $I_{OUT} \le 1.5 \text{ mA}$                                                      |                     | 0.0                   | —   | 0.9   |                  |

| High-Level Output Voltage                                                         | V <sub>OH</sub>     |                       |     |       | V                |

| $I_{OUT} \le 250 \ \mu A$                                                         |                     | 3.75                  | —   | 5.25  |                  |

| TXD INPUT PIN (LIN PHYSICAL LAYER)                                                |                     |                       |     | 1     |                  |

| Low-Level Input Voltage                                                           | V <sub>IL</sub>     | —                     | _   | 1.5   | V                |

| High-Level Input Voltage                                                          | V <sub>IH</sub>     | 3.5                   | _   | _     | V                |

| Input Hysteresis                                                                  | VINHYS              | 50                    | 145 | 300   | mV               |

| Pullup Current Source                                                             | I <sub>PUTXD</sub>  |                       |     |       | μA               |

| 1.0 V < V <sub>TXD</sub> < 3.5 V                                                  |                     | -100                  | _   | -20   |                  |

| LIN PHYSICAL LAYER, TRANSCEIVER                                                   |                     |                       |     |       |                  |

| Transceiver Output Voltage                                                        |                     |                       |     |       | V                |

| Dominant State, TXD LOW, External Bus Pullup 500 $\Omega$                         | V <sub>LINDOM</sub> | _                     | _   | 1.4   |                  |

| Recessive State, TXD HIGH, $I_{OUT}$ = 1.0 $\mu$ A                                | V <sub>LINREC</sub> | V <sub>SUP</sub> -1.0 | —   | —     |                  |

| Pullup Resistor to VSUP                                                           | R <sub>PU</sub>     |                       |     |       | kΩ               |

| In Normal Mode and in Sleep and Stop Modes When Not Disabled by SPI               |                     | 20                    | 30  | 47    |                  |

| Pullup Current Source                                                             | I <sub>PULIN</sub>  |                       |     |       | μA               |

| In Sleep and Stop Modes When Pullup Disabled by SPI                               |                     | —                     | 1.3 | _     |                  |

| Output Current Shutdown Threshold                                                 | IOUTSD              | 50                    | 75  | 150   | mA               |

| Leakage Output Current to GND                                                     | IBUSLEAK            |                       |     |       |                  |

| VS1 and VS2 Disconnected, $V_{LIN} = 18 V$                                        |                     | _                     | 1.0 | 10    | μΑ               |

| Recessive State, 8.0 V < V <sub>SUP</sub> < 18 V, 8.0 V < V <sub>LIN</sub> < 18 V |                     | 0.0                   | 3.0 | 20    | μΑ               |

| GND Disconnected, $V_{GND} = V_{SUP}$ , $V_{LIN} = -18$ V                         |                     | -1.0                  | —   | 1.0   | mA               |

| LIN PHYSICAL LAYER, RECEIVER                                                      |                     |                       |     | 1     |                  |

| Receiver Input Threshold Voltage                                                  |                     |                       |     |       | V <sub>SUP</sub> |

| Dominant State, TXD HIGH, RXD LOW                                                 | V <sub>BUSDOM</sub> | 0.0                   | —   | 0.4   |                  |

| Recessive State, TXD HIGH, RXD HIGH                                               | V <sub>BUSREC</sub> | 0.6                   | _   | 1.0   |                  |

| Center (V <sub>BUSDOM</sub> -V <sub>BUSREC</sub> )/2                              | V <sub>BUSCNT</sub> | 0.475                 | 0.5 | 0.525 |                  |

| Hysteresis (V <sub>BUSDOM</sub> -V <sub>BUSREC</sub> )                            | V <sub>BUSHYS</sub> | -                     | —   | 0.175 |                  |

| Bus Wake-Up Threshold                                                             | V <sub>BUSWU</sub>  | _                     | 0.5 | —     | V <sub>SUP</sub> |

## DYNAMIC ELECTRICAL CHARACTERISTICS

## Table 4. Dynamic Electrical Characteristics

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                           | Symbol                                      | Min        | Тур | Max      | Unit |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-----|----------|------|--|--|

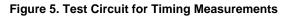

| SPI INTERFACE CHARACTERISTICS                                                                                                                            |                                             |            |     |          |      |  |  |

| SPI Operation Frequency                                                                                                                                  | f <sub>SPI</sub>                            | 0.25       | —   | 4.0      | MHz  |  |  |

| SCLK Clock Period                                                                                                                                        | t <sub>PSCLK</sub>                          | 250        | —   | N/A      | ns   |  |  |

| SCLK Clock High Time                                                                                                                                     | t <sub>WSCLKH</sub>                         | 125        | —   | N/A      | ns   |  |  |

| SCLK Clock Low Time                                                                                                                                      | t <sub>WSCLKL</sub>                         | 125        | —   | N/A      | ns   |  |  |

| Falling Edge of $\overline{CS}$ to Rising Edge of SCLK                                                                                                   | t <sub>LEAD</sub>                           | 100        | _   | N/A      | ns   |  |  |

| Falling Edge of SCLK to $\overline{CS}$ Rising Edge                                                                                                      | t <sub>LAG</sub>                            | 100        |     | N/A      | ns   |  |  |

| MOSI to Falling Edge of SCLK (Data Setup Time)                                                                                                           | t <sub>SI(SU)</sub>                         | 40         | —   | N/A      | ns   |  |  |

| Falling Edge of SCLK to MOSI (Data Hold Time)                                                                                                            | t <sub>SI(HOLD)</sub>                       | 40         | —   | N/A      | ns   |  |  |

| MISO Rise Time <sup>(14)</sup><br>C <sub>L</sub> = 220 pF                                                                                                | t <sub>RSO</sub>                            | _          | 25  | 50       | ns   |  |  |

| MISO Fall Time <sup>(14)</sup><br>C <sub>L</sub> = 220 pF                                                                                                | t <sub>FSO</sub>                            | _          | 25  | 50       | ns   |  |  |

| Time from Falling or Rising Edge of CS to: <sup>(14)</sup><br>MISO Low Impedance (Enable)<br>MISO High Impedance (Disable)                               | t <sub>SO(EN)</sub><br>t <sub>SO(DIS)</sub> | 0.0<br>0.0 | _   | 50<br>50 | ns   |  |  |

| Time from Rising Edge of SCLK to MISO Data Valid <sup>(14)</sup><br>0.2 V <sub>DD</sub> $\leq$ MISO $\geq$ 0.8 V <sub>DD</sub> , C <sub>L</sub> = 100 pF | t <sub>VALID</sub>                          | 0.0        | _   | 50       | ns   |  |  |

| RST OUTPUT PIN IN NORMAL AND STOP MODES                                                                                                                  |                                             |            |     |          |      |  |  |

| Reset Duration After VDD HIGH                                                                                                                            | t <sub>DUR</sub> RST                        | 0.65       | 1.0 | 1.35     | ms   |  |  |

|                                                                                                                                                          |                                             |            |     |          |      |  |  |

| Watchdog Period Accuracy Using an External Resistor (Excluding Resistor Tolerances) <sup>(15)</sup>                                                      | ACCWDC                                      | -15        | _   | 15       | %    |  |  |

| Tolerances) <sup>(15)</sup>                 | ACCWDC           | -15 |        | 15  | %  |

|---------------------------------------------|------------------|-----|--------|-----|----|

| Watchdog Time Period <sup>(15)</sup>        | t <sub>WDC</sub> |     |        |     | ms |

| 10 kΩ External Resistor                     |                  | —   | 10.558 | —   |    |

| 100 k $\Omega$ External Resistor            |                  | —   | 99.748 | —   |    |

| No External Resistor, WDC Open, Normal Mode |                  | 107 | 160    | 215 |    |

Notes

14. Parameter guaranteed by design; however, it is not production tested.

15. Watchdog time period calculation formula:  $t_{WDC} = 0.991 * R + 0.648$  (R in k $\Omega$  and  $t_{WDC}$  in ms).

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                    | Symbol                                  | Min      | Тур | Max       | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------|-----|-----------|------|

| CURRENT SENSE OPERATIONAL AMPLIFIER                                                                                                               |                                         |          |     |           |      |

| Supply Voltage Rejection Ratio (16)                                                                                                               | SVR                                     | 60       | -   | —         | dB   |

| Common Mode Rejection Ratio (16)                                                                                                                  | CMR                                     | 70       | —   | —         | dB   |

| Gain Bandwidth <sup>(16)</sup>                                                                                                                    | GBP                                     | 1.0      | —   | _         | MHz  |

| Output Slew Rate                                                                                                                                  | SR                                      | 0.5      | —   |           | V/µs |

| Phase Margin                                                                                                                                      | PHMO                                    | 40       | —   | —         | deg. |

| Open Loop Gain <sup>(16)</sup>                                                                                                                    | OLG                                     | -        | 85  | —         | dB   |

| L1 AND L2 INPUT PINS                                                                                                                              |                                         |          |     |           |      |

| Wake-Up Filter Time <sup>(16)</sup>                                                                                                               | t <sub>WUF</sub>                        | 8.0      | 20  | 38        | μS   |

| STATE MACHINE TIMING                                                                                                                              |                                         |          | 1   | 1         |      |

| Delay Between CS LOW-to-HIGH Transition (at End of SPI Stop Command)                                                                              | t <sub>STOP</sub>                       |          |     |           | μS   |

| and Stop Mode Activation <sup>(16)</sup><br>Minimum Watchdog Period                                                                               |                                         | 1.4      | —   | 5.0       |      |

| No Watchdog Selected                                                                                                                              |                                         | 6.0      | _   | 30        |      |

| Maximum Watchdog Period                                                                                                                           |                                         | 12       | —   | 50        |      |

| Interrupt Low-Level Duration                                                                                                                      | t <sub>INT</sub>                        | 7.0      | 10  | 13        | μs   |

| Internal Oscillator Frequency Accuracy (All Modes, for Information Only)                                                                          | fosc                                    | -35      | —   | 35        | %    |

| Normal Request Mode Time-Out (Normal Request Mode)                                                                                                | t <sub>NRTOUT</sub>                     | 97       | 150 | 205       | ms   |

| Delay Between SPI Command and HS1 or HS2 Turn On <sup>(17), (18)</sup><br>Normal Mode, $V_{SUP} > 9.0 V$ , $V_{HS} \ge 0.2 V_{VS2}$               | t <sub>SHSON</sub>                      | _        | _   | 20        | μs   |

| Delay Between SPI Command and HS1 or HS2 Turn Off <sup>(17)</sup> , <sup>(18)</sup><br>Normal Mode, $V_{SUP} > 9.0$ V, $V_{HS} \le 0.8$ $V_{VS2}$ | t <sub>SHSOFF</sub>                     |          | _   | 20        | μs   |

| Delay Between SPI Command and HS3 Turn On $^{(17),\ (19)}$ Normal Mode, $V_{SUP}$ > 9.0 V, $V_{HS} \ge 0.2 \ V_{VS2}$                             | t <sub>SHSON</sub>                      |          | _   | 20        | μs   |

| Delay Between SPI Command and HS3 Turn Off $^{(17),\ (19)}$ Normal Mode, V_{SUP} > 9.0 V, V_{HS} $\leq$ 0.8 V_{VS2}                               | t <sub>SHSOFF</sub>                     | _        | _   | 20        | μs   |

| Delay Between Normal Request and Normal Mode After a Watchdog Trigger Command (Normal Request Mode) <sup>(16)</sup>                               | t <sub>SNR2N</sub>                      | 7.0      | 15  | 30        | μs   |

| Delay Between CS Wake-Up (CS LOW to HIGH) in Stop Mode and:<br>Normal Request Mode, VDD ON and RST HIGH<br>First Accepted SPI Command             | t <sub>WUCS</sub><br>t <sub>WUSPI</sub> | 15<br>90 | 40  | 80<br>N/A | μs   |

| Delay Between Interrupt Pulse in Stop Mode After Wake-Up and First<br>Accepted SPI Command                                                        | t <sub>S1STSPI</sub>                    | 30       | —   | N/A       | μS   |

| Minimum Time Between Rising and Falling Edge on the $\overline{\text{CS}}$                                                                        | t <sub>2CS</sub>                        | 15       | _   | _         | μS   |

Notes

16. Parameter guaranteed by design; however, it is not production tested.

17. When IN input is set to HIGH, delay starts at falling edge of clock cycle #8 of the SPI command and start of device activation/deactivation. 30 mA load on high-side switches. Excluding rise or fall time due to external load.

18. When IN is used to control the high-side switches, delays are measured between IN and HS1 or HS2 ON/OFF. 30 mA load on high-side switches, excluding rise or fall time due to external load.

19. Delay between turn on or turn off command and HS ON or HS OFF, excluding rise or fall time due to external load.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                    | Symbol              | Min                    | Тур | Max | Unit |

|-----------------------------------------------------------------------------------|---------------------|------------------------|-----|-----|------|

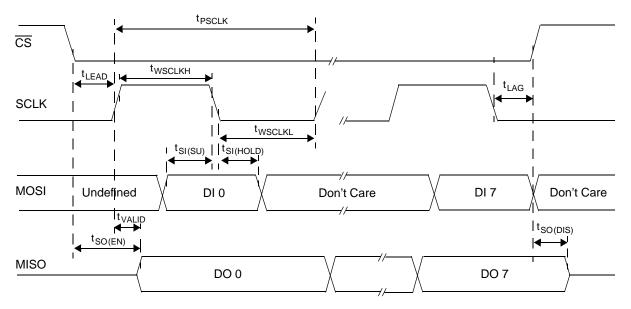

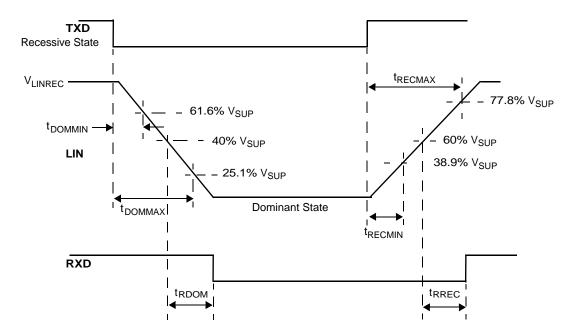

| LIN PHYSICAL LAYER: BUS DRIVER TIMING CHARACTERISTICS FOR                         | R NORMAL SLEW       | / RATE <sup>(20)</sup> |     |     |      |

| Propagation Delay TXD to LIN <sup>(21)</sup>                                      |                     |                        |     |     | μS   |

| Dominant State Minimum Threshold (50% TXD to 58.1% $V_{SUP}$ )                    | t <sub>DOMMIN</sub> | —                      | —   | 50  |      |

| Dominant State Maximum Threshold (50% TXD to 28.4% $V_{SUP})$                     | t <sub>DOMMAX</sub> | —                      | —   | 50  |      |

| Recessive State Minimum Threshold (50% TXD to 42.2% $\mathrm{V}_{\mathrm{SUP}}$ ) | t <sub>RECMIN</sub> | —                      | —   | 50  |      |

| Recessive State Maximum Threshold (50% TXD to 74.4% $\mathrm{V}_{\mathrm{SUP}}$ ) | t <sub>RECMAX</sub> | —                      | —   | 50  |      |

| Propagation Delay Symmetry                                                        |                     |                        |     |     | μS   |

| <sup>t</sup> DOMMIN <sup>- t</sup> RECMAX                                         | dt1s                | -10.44                 | —   | _   |      |

| tDOMMAX - tRECMIN                                                                 | dt2s                | —                      | —   | 11  |      |

| LIN PHYSICAL LAYER: BUS DRIVER TIMING CHARACTERISTICS FOR                         | R SLOW SLEW R       | ATE <sup>(20)</sup>    |     |     |      |

| Propagation Delay TXD to LIN <sup>(22)</sup>                                      |                     |                        |     |     | μS   |

| Dominant State Minimum Threshold (50% TXD to 61.6% $V_{SUP}$ )                    | t <sub>DOMMIN</sub> | —                      | —   | 100 |      |

| Dominant State Maximum Threshold (50% TXD to 25.1% $\mathrm{V}_{\mathrm{SUP}}$ )  | t <sub>DOMMAX</sub> | —                      | —   | 100 |      |

| Recessive State Minimum Threshold (50% TXD to 38.9% $\mathrm{V}_{\mathrm{SUP}}$ ) | t <sub>RECMIN</sub> | —                      | —   | 100 |      |

| Recessive State Maximum Threshold (50% TXD to 77.8% $\mathrm{V}_{\mathrm{SUP}})$  | t <sub>RECMAX</sub> | —                      | —   | 100 |      |

| Propagation Delay Symmetry                                                        |                     |                        |     |     | μS   |

| <sup>t</sup> DOMMIN <sup>- t</sup> RECMAX                                         | dt1s                | -22                    | —   | _   |      |

| <sup>t</sup> DOMMAX <sup>- t</sup> RECMIN                                         | dt2s                | —                      | —   | 23  |      |

| LIN PHYSICAL LAYER: BUS DRIVER FAST SLEW RATE                                     | ·                   | •                      | •   | •   | •    |

| LIN High Slew Rate (Programming Mode)                                             | dv/dt Fast          | _                      | 13  | _   | V/µs |

| LIN PHYSICAL LAYER, TRANSCEIVER                                                   |                     |                        |     |     | •    |

| Output Current Shutdown Delay <sup>(23)</sup>                                     | t <sub>OUTDLY</sub> | —                      | 10  | —   | μS   |

| Notes                                                                             |                     |                        |     |     |      |

Notes

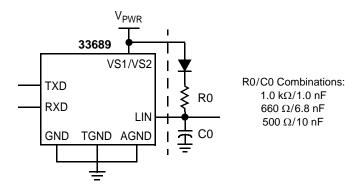

20. 7.0 V < V<sub>SUP</sub> < 18 V, bus load C0 and R0 1.0 nF/1.0 k $\Omega$ , 6.8 nF/660  $\Omega$ , 10 nF/500  $\Omega$ . 50% of TXD signal to LIN signal threshold. See Figure 5, page 16.

21. See Figure 7, page <u>17</u>.

22. See Figure 8, page 17.

23. Parameter guaranteed by design; however, it is not production tested.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                   | Symbol              | Min  | Тур | Max | Unit |  |  |  |  |

|------------------------------------------------------------------|---------------------|------|-----|-----|------|--|--|--|--|

| LIN PHYSICAL LAYER: RECEIVER CHARACTERISTICS AND WAKE-UP TIMINGS |                     |      |     |     |      |  |  |  |  |

| Propagation Delay LIN to RXD <sup>(24)</sup>                     |                     |      |     |     | μS   |  |  |  |  |

| Dominant State (LIN LOW to RXD LOW)                              | t <sub>RDOM</sub>   |      | 3.0 | 6.0 |      |  |  |  |  |

| Recessive State (LIN HIGH to RXD HIGH)                           | t <sub>RREC</sub>   | —    | 3.0 | 6.0 |      |  |  |  |  |

| Symmetry (t <sub>RDOM</sub> - t <sub>RREC</sub> )                | t <sub>RSYM</sub>   | -2.0 | —   | 2.0 |      |  |  |  |  |

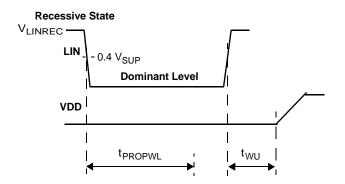

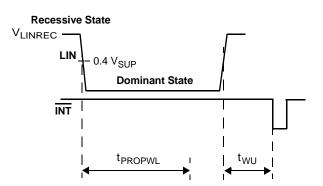

| Bus Wake-Up Deglitcher (Sleep and Stop Modes) <sup>(25)</sup>    | t <sub>PROPWL</sub> | 30   | 70  | 90  | μS   |  |  |  |  |

| Bus Wake-Up Event Reported                                       |                     |      |     |     | μS   |  |  |  |  |

| From Sleep Mode <sup>(26)</sup>                                  | t <sub>WU</sub>     | —    | 30  | —   |      |  |  |  |  |

| From Stop Mode <sup>(27)</sup>                                   | t <sub>WU</sub>     | —    | 20  | —   |      |  |  |  |  |

Notes

24. Measured between LIN signal threshold  $\rm V_{INL}$  or  $\rm V_{INH}$  and 50% of RXD signal.

25. See <u>Figures 9</u> and <u>10</u>, page <u>18</u>.

26. t<sub>WU</sub> is typically 2 internal clock cycles after a LIN rising edge is detected. In Sleep Mode, the measurement is done without a capacitor connected to the regulator. The delay is measured between the V<sub>SUP</sub>/2 rising edge of the LIN bus and when V<sub>DD</sub> reaches 3.0 V. The V<sub>DD</sub> rise time is strongly dependent upon the decoupling capacitor at V<sub>DD</sub> pin. See Figure 9, page 18.

t<sub>WU</sub> is typically 2 internal clock cycles after a LIN rising edge is detected. In Stop Mode, the delay is measured between the V<sub>SUP</sub>/2 rising edge of the LIN bus and the falling edge of the INT pin. See Figure 10, page 18.

## **TIMING DIAGRAMS**

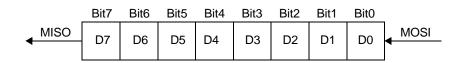

**Note** Incoming data at MOSI pin is sampled by the 33689 at SCLK falling edge. Outgoing data at MISO is set by the 33689 at SCLK rising edge (after  $t_{VALID}$  delay time).

## Figure 6. SPI Timing Characteristics

Figure 7. Timing Characteristics for Normal LIN Output Slew Rate

Figure 8. Timing Characteristics for Slow LIN Output Slew Rate

Figure 9. LIN Bus Wake-Up Behavior, Sleep Mode

Figure 10. LIN Bus Wake-Up Behavior, Stop Mode

# FUNCTIONAL DESCRIPTION

## **INTRODUCTION**

A System Basis Chip (SBC) is a monolithic IC combining many functions found in standard microcontroller-based systems; e.g., power management, communication interface, system protection, and diagnostics.

The 33689 is a SPI-controlled SBC combining many functions with a LIN transceiver for slave node applications. The 33689 has a 5.0 V, 50 mA regulator with undervoltage reset, output current limiting, overtemperature pre-warning, and thermal shutdown. An externally selectable timing Window Watchdog is also included.

The LIN transceiver has waveshaping that can be disabled when high data rates are warranted. A single 50 mA and two 150 mA fully protected high-side switches with output clamping are available for switching inductive or resistive loads. The 150 mA switches are PWM capable.

Two high-voltage inputs can be used to monitor switches or provide external wake-up. An internal current sense operational amplifier is available for load current monitoring.

## FUNCTIONAL PIN DESCRIPTION

## LEVEL 1 AND LEVEL 2 INPUT PINS (L1 AND L2)

These pins are used to sense external switches and to wake up the 33689 from Sleep or Stop mode. During Normal mode, the state of these pins can be read through the SPI Register. (Refer to the section entitled SPI Interface and Register Description on page 24 for information on the SPI Register.)

# HIGH-SIDE DRIVER OUTPUT PINS 1 AND 2 (HS1 AND HS2)

These two high-side switches are able to drive loads such as relays or lamps. They are protected against overcurrent and overtemperature and include internal clamp circuitry for inductive load protection. Switch control is done through selecting the correct bit in the SPI Register. HS1 and HS2 can be PWM-ed if required through the IN input pin. The internal circuitry that drives both high-side switches is an AND function between the SPI bit HS1 (or HS2) and the IN input pin.

If no PWM control is required, the IN pin must be connected to the VDD pin.

## **HIGH-SIDE DRIVER OUTPUT PIN 3 (HS3)**

This high-side switch can be used to drive small lamps, Hall sensors, or switch pullup resistors. Control is done through the SPI Register only.

No direct PWM control is possible on this pin.

This high-side switch features current limit to protect it against overcurrent and short circuit conditions. It is also protected against overtemperature.

## VOLTAGE SUPPLY PINS 1 AND 2 (VS1 AND VS2)

The 33689 is supplied from a battery line or other supply source through the VS1 and VS2 pins. An external diode is required to protect against negative transients and reverse

battery. The 33689 can operate from 4.5 V and under the jump start condition at 27 V DC. Device functionality is guaranteed down to 4.5 V at VS1 and VS2 pins. These pins sustain standard automotive voltage conditions such as load dump at 40 V.

## LIN BUS PIN (LIN)

The LIN pin represents the single-wire bus transmitter and receiver. It is suited for automotive bus systems and is based on the LIN bus specification.

## **VOLTAGE SOURCE PIN (VDD)**

The VDD pin is the 5.0 V supply pin for the MCU and the current sense operational amplifier.

## CURRENT SENSE OPERATIONAL AMPLIFIER PINS (E+, E-, VCC, AND OUT)

These are the pins of the single-supply current sense operational amplifier.

- The E+ and the E- input pins are the non-inverting and inverting inputs of the current sense operational amplifier, respectively.

- The OUT pin is the output pin of the current sense operational amplifier.

- The VCC pin is the +5.0 V single-supply connection for the current sense operational amplifier.

The current sense operational amplifier is enabled in Normal mode only.

## WATCHDOG CONFIGURATION PIN (WDC)

The WDC pin is the configuration pin for the internal watchdog. A resistor is connected to this pin. The resistor value defines the watchdog period. If the pin is left open, the watchdog period is fixed to its default value (150 ms typical). If no watchdog function is required, the WDC pin must be connected to GND.

33689

## **RESET OUTPUT PIN (RST)**

The  $\overline{\text{RST}}$  pin is the 5.0 V regulator and Watchdog reset output pin.

## **PWM INPUT CONTROL PIN (IN)**

The IN pin is the external PWM control pin for the HS1 and HS2 high-side switches.

## SERIAL DATA CLOCK PIN (SCLK)

The SCLK pin is the SPI clock input pin. MISO data changes on the negative transition of the SCLK. MOSI is sampled on the positive edge of the SCLK.

#### MASTER OUT SLAVE IN PIN (MOSI)

The MOSI pin receives SPI data from the MCU. This data input is sampled on the positive edge of SCLK.

## MASTER IN SLAVE OUT PIN (MISO)

The MISO pin sends data to an SPI-enabled MCU. Data on this output pin changes on the negative edge of the SCLK. When  $\overline{\text{CS}}$  is HIGH, this pin enters the high-impedance state.

## CHIP SELECT PIN (CS)

The  $\overline{CS}$  pin is the chip select input pin for SPI use. When this signal is high, SPI signals are ignored. Asserting this pin LOW starts an SPI transaction. The transaction is completed when this signal returns HIGH.

## INTERRUPT OUTPUT PIN (INT)

The  $\overline{\text{INT}}$  pin is used to report 33689 faults to the MCU. Interrupt pulses are generated for:

- Voltage regulator temperature pre-warning

- HS1, HS2, or HS3 thermal shutdown

- VS1 or VS2 overvoltage (20 V typical)

- VS1 or VS2 undervoltage (6.0 V typical)

If an interrupt is generated, then when the next SPI read operation is performed bit D7 in the SPI Register will be set to logic [1] and bits D6:D0 will report the interrupt source.

In cases of wake-up from the Stop mode,  $\overline{INT}$  is set LOW in order to signal to the MCU that a wake-up event from the L1, L2, or LIN bus pin has occurred.

#### **RECEIVER OUTPUT PIN (RXD)**

The RXD pin is the receiver output of the LIN interface and reports the state of the bus voltage (RXD LOW when LIN bus is dominant, RXD HIGH when LIN bus is recessive).

#### TRANSMITTER INPUT PIN (TXD)

The TXD pin is the transmitter input of the LIN interface and controls the state of the bus output (dominant when TXD is LOW, recessive when TXD is HIGH).

## **GROUND PINS (GND, TGND, AND AGND)**

The 33689 has three different types of ground pins.

- The GND pin is the electrical ground pin for the device.

- The AGND is the analog ground pin for the voltage regulator and current sense operational amplifier.

- The four TGND pins are the thermal ground pins for the device.

**Important** The GND, the AGND, and the four TGND pins must be connected together to a ground external to the 33689.

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

## WINDOW WATCHDOG

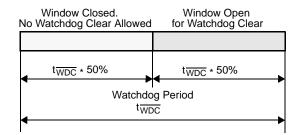

The window watchdog can be configured using an external resistor at WDC pin. The watchdog is cleared through MODE1 and MODE2 bit in the SPI Register (refer to <u>Table 2</u>, page <u>24</u>; also refer to the section entitled Functional Pin Description on page 19.

A watchdog clear is only allowed in the open window (see Figure 1). If the watchdog is cleared in the closed window or has not been cleared at the end of the open window, the watchdog will generate a reset on the RST pin and reset the whole device.

**Note** The watchdog clear in Normal request mode (150 ms) (first watchdog clear) has no window.

Figure 1. Window Watchdog Operation

#### Window Watchdog Configuration

If the  $\overline{\text{WDC}}$  pin is left open, the default watchdog period is selected (typ. 150 ms). If no watchdog function is required, the  $\overline{\text{WDC}}$  pin must be connected to GND.

The watchdog timer's period is calculated using the following formula:

$t_{WDC} = 0.991 * R + 0.648$  (with R in k $\Omega$  and  $t_{WDC}$  in ms).

#### VDD VOLTAGE REGULATOR

The 33689 chip contains a low-power, low dropout voltage regulator to provide internal power and external power for the MCU. The on-chip regulator consist of two elements, the main voltage regulator and the low-voltage reset circuit.

The VDD regulator accepts an unregulated input supply and provides a regulated  $V_{DD}$  supply to all digital sections of

the device. The output of the regulator is also connected to the VDD pin to provide the 5.0 V to the microcontroller.

#### **Current Limit (Overcurrent) Protection**

The voltage regulator has current limit to protect the device against overcurrent and short circuit conditions.

#### **Overtemperature Protection**

The voltage regulator also features overtemperature protection that has an overtemperature warning (Interrupt - VDDT) and an overtemperature shutdown.

#### Stop Mode

During Stop mode, the Stop mode regulator supplies a regulated output voltage. The Stop mode regulator has a limited output current capability.

#### Sleep Mode

In Sleep mode, the voltage regulator external VDD is turned off.

## VDD VOLTAGE REGULATOR TEMPERATURE PREWARNING

VDD voltage regulator temperature prewarning (VDDT) is generated if the voltage regulator temperature is above the  $T_{PRE}$  threshold. It will set the VDDT bit in the SPI Register and an interrupt will be initiated. The VDDT bit remains set as long as the error condition is present.

During Sleep and Stop modes the VDD voltage regulator temperature prewarning circuitry is disabled.

## HIGH-SIDE SWITCH THERMAL SHUTDOWN

The high-side switch thermal shutdown HSST is generated if one of the high-side switches HS1:HS3 is above the HSST threshold. It will shutdown all high-side switches and set the HSST flag in the SPI Register, and an interrupt will be initiated. The HSST bit remains set as long as the error condition is present. During Sleep and Stop modes the highside switch thermal shutdown circuitry is disabled.

21

## FUNCTIONAL DEVICE OPERATION

#### **OPERATIONAL MODES**

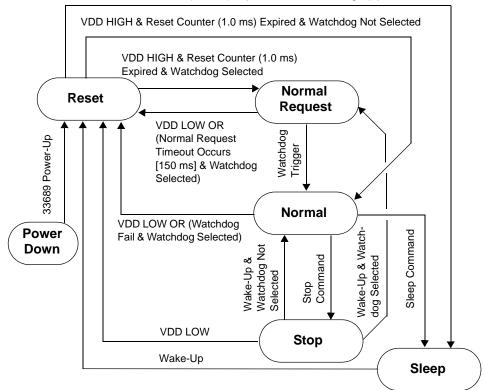

As described below and depicted in Figure 1 below and Table 1 on page 23, the 33689 has three operational modes: Normal, Sleep, and Stop. Operational modes are controlled by MODE1 and MODE2 bits in the SPI Register (refer to Logic Commands and Registers on page 24). In additional, there are two transitional modes: Reset and Normal Request.

#### **RESET MODE**

At power up, the 33689 switches automatically to Reset Mode for 1 ms if  $V_{DD}$  goes high. If  $V_{DD}$  stays low, after 150 ms the 33689 goes in Sleep Mode.

#### NORMAL REQUEST MODE

Before entering in Normal Request Mode, the 33689 stays for 1 ms in Reset Mode. In this mode, the LIN bus can transmit and receive information.

VDD LOW (150 ms) Expired & VSUV Bit = Logic [0]

#### Legend

Watchdog Selected: External resistor between WDC pin and GND or WDC pin open.

Watchdog Not Selected: WDC pin connected to GND.

Watchdog Fail: Watchdog trigger occurs in closed window or no SPI Watchdog trigger command. Stop Command: SPI stop command.

Sleep Command: SPI sleep request followed by SPI sleep command.

Wake-Up: L1 or L2 state change or LIN bus wake-up or CS rising edge.

Figure 1. 33689 Modes State Diagram

## NORMAL MODE

In Normal Mode, the 33689 has slew rate and timing compatible with the LIN protocol specification. The LIN bus can transmit and receive information. The  $V_{DD}$  regulator is ON and the watchdog function can be enabled.

## SLEEP AND STOP MODE

To safely enter Sleep or Stop modes and to ensure that these modes are not inadvertently entered due to noise issues during SPI transmission, a dedicated sequence must be sent twice: data with the bits controlling the LIN bus and the device mode.

#### **Entering Sleep Mode**

First and second SPI commands (with bit D6=1, D7=1, D5=0 or 1, D1=0, and D0=0) 11x00000 must be sent.

#### **Entering Stop Mode**

First and second SPI commands (with bit D6=1, D7=1, D5=0 or 1, D1=0, and D0=1) 11x00001 must be sent.

Sleep or Stop modes are entered after the second SPI command. Register bit D5 must be set accordingly.

| Device Mode       | VDD Voltage<br>Regulator                                                  | Wake-Up<br>Capabilities                    | RST Output                                                                                                              | Watchdog<br>Function                     | HS1, HS2, HS3 | LIN Interface                              | Operational<br>Amplifier |

|-------------------|---------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|--------------------------------------------|--------------------------|

| Reset             | VDD: ON                                                                   | N/A                                        | LOW for 1.0 ms<br>typical, then<br>HIGH (if VDD<br>above threshold)                                                     | Disabled                                 | OFF           | Recessive only                             | Not active               |

| Normal<br>Request | VDD: ON                                                                   | N/A                                        | HIGH.<br>Active LOW if<br>VDD<br>undervoltage<br>occurs and if<br>Normal Request<br>timeout (if<br>Watchdog<br>enabled) | 150 ms timeout<br>if Watchdog<br>enabled | ON or OFF     | Transmit and receive                       | Not active               |