# DALLAS JUX

# **XFP Laser Control and Digital Diagnostic IC**

### **General Description**

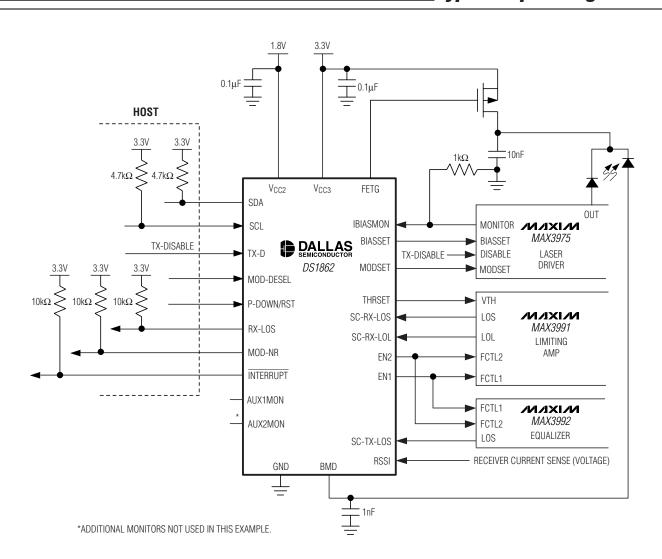

The DS1862 is a closed-loop laser-driver control IC with built-in digital diagnostics designed for XFP MSA. The laser control function incorporates automatic power control (APC) and allows extinction ratio control though a temperature-indexed lookup table (LUT). The DS1862 monitors up to seven analog inputs, including temperature and monitor diode (MD) current, which are used to regulate the laser bias current and extinction ratio. Warning and alarm thresholds can be programmed to generate an interrupt if monitored signals exceed tolerance. Calibration is also provided internally using independent gain and offset scaling registers for each of the monitored analog signals. Settings such as programmed calibration data are stored in password-protected EEPROM memory. Programming is accomplished through an I<sup>2</sup>C-compatible interface, which can also be used to access diagnostic functionality.

### **Applications**

Laser Control and Monitoring 10Gbps Optical Transceiver Modules (XFP)

Laser Control and Monitoring

Digital Diagnostics in Optical Transmission

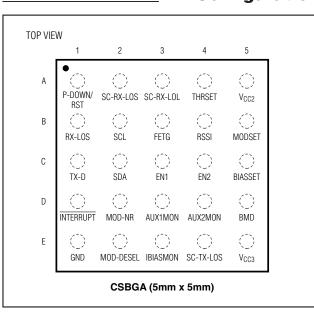

### **Pin Configuration**

### \_ Features

- Implements XFP MSA Requirements for Digital Diagnostics, Serial ID, and User Memory

- ♦ I<sup>2</sup>C-Compatible Serial Interface

- Automatic Power Control (APC)

- Extinction Ratio Control with Lookup Table

- Seven Monitored Channels for Digital Diagnostics (Five Basic Plus Two Auxiliary)

- Internal Calibration of Monitored Channels (Temp, V<sub>CC2/3</sub>, Bias Current, Transmitted, and Received Power)

- Programmable Quick-Trip Logic for Turning Off Laser for Eye Safety

- Access to Monitoring and ID Information

- Programmable Alarm and Warning Thresholds

- Operates from 3.3V or 5V Supply

- ♦ 25-Ball CSBGA, 5mm x 5mm Package

- Internal or External Temperature Sensor

- ♦ -40°C to +100°C Operating Temperature Range

- One 8-Bit Buffered DAC

### **Ordering Information**

Maxim Integrated Products 1

| PART     | TEMP RANGE      | PIN-PACKAGE |

|----------|-----------------|-------------|

| DS1862B  | -40°C to +100°C | 25 CSBGA    |

| DS1862B+ | -40°C to +100°C | 25 CSBGA    |

+Denotes a lead-free/RoHS-compliant package.

Typical Operating Circuit appears at end of data sheet.

\_\_\_\_\_

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

ABSOLUTE MAXIMUM RATINGS Voltage Range on Any Open-Drain Pin

| 0.5V to (VCC2 + 0.5V)*   |

|--------------------------|

| 40°C to +100°C           |

| Range0°C to +70°C        |

| 55°C to +125°C           |

| Refer to the IPC JEDEC   |

| J-STD-020 Specification. |

|                          |

\*Not to exceed +6.0V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

(V<sub>CC3</sub> = +2.9V to +5.5V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                             | SYMBOL           | CONDITIONS                                               | MIN                       | ΤΥΡ ΜΑ                 | x | UNITS |

|-----------------------------------------------------------------------|------------------|----------------------------------------------------------|---------------------------|------------------------|---|-------|

| Main Supply Voltage                                                   | V <sub>CC3</sub> | (Note 1)                                                 | +2.9                      | +5                     | 5 | V     |

| Secondary Supply Voltage                                              | V <sub>CC2</sub> | V <sub>CC2</sub> not to exceed V <sub>CC3</sub> (Note 2) | +1.6                      | +3                     | 6 | V     |

| High-Level Input Voltage<br>(SDA, SCL)                                | VIH              | I <sub>IH</sub> (max) = 10μA                             | 0.7 x<br>V <sub>CC3</sub> | V <sub>CC</sub><br>0.5 |   | V     |

| Low-Level Input Voltage<br>(SDA, SCL)                                 | VIL              | I <sub>IL</sub> (max) = -10µA                            | GND -<br>0.3              | 0.3<br>V <sub>C0</sub> |   | V     |

| High-Level Input Voltage<br>(TX-D, MOD-DESEL,<br>P-DOWN/RST) (Note 3) | VIH              | I <sub>IH</sub> (max) = 10μΑ                             | 2                         | Vcc:<br>0.3            |   | V     |

| Low-Level Input Voltage<br>(TX-D, MOD-DESEL,<br>P-DOWN/RST) (Note 3)  | VIL              | I <sub>IL</sub> (max) = -10µA                            | -0.3                      | +0                     | 8 | V     |

### DC ELECTRICAL CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                     | SYMBOL          | CONDITIONS                   | MIN                       | ТҮР | MAX | UNITS |

|---------------------------------------------------------------|-----------------|------------------------------|---------------------------|-----|-----|-------|

| Supply Current                                                | ICC3            | P-DOWN/RST = 1               |                           | 3   | 5   | mA    |

| High-Level Output Voltage<br>(FETG)                           | V <sub>OH</sub> | I <sub>OH</sub> (max) = -2mA | V <sub>CC3</sub> -<br>0.5 |     |     | V     |

| Low-Level Output Voltage<br>(MOD-NR, INTERRUPT, SDA,<br>FETG) | V <sub>OL</sub> | I <sub>OL</sub> (max) = 3mA  | 0                         |     | 0.4 | V     |

| Resistor (Pullup)                                             | R <sub>PU</sub> |                              | 9                         | 12  | 15  | kΩ    |

| I/O Capacitance                                               | CI/O            | (Note 4)                     |                           |     | 10  | pF    |

| Leakage Current                                               | ١L              |                              | -10                       |     | +10 | μA    |

| Leakage Current (SCL, SDA)                                    | ١L              |                              | -10                       |     | +10 | μA    |

| Digital Power-On Reset                                        | POD             |                              | 1.0                       |     | 2.2 | V     |

| Analog Power-On Reset                                         | POA             |                              | 2.0                       |     | 2.6 | V     |

### DC ELECTRICAL CHARACTERISTICS—INTERFACE SIGNALS TO SIGNAL CONDITIONERS

(V<sub>CC2</sub> = +1.6V to +3.6V, V<sub>CC3</sub> = +2.9V to +5.5V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                        | SYMBOL           | CONDITIONS                                              | MIN                       | ТҮР | МАХ                       | UNITS |

|------------------------------------------------------------------|------------------|---------------------------------------------------------|---------------------------|-----|---------------------------|-------|

| High-Level Input Voltage<br>(SC-RX-LOS, SC-RX-LOL,<br>SC-TX-LOS) | V <sub>IH</sub>  | I <sub>IH</sub> (max) = 100µA                           | 0.7 x<br>V <sub>CC2</sub> |     | V <sub>CC2</sub> + 0.1    | V     |

| Low-Level Input Voltage<br>(SC-RX-LOS, SC-RX-LOL,<br>SC-TX-LOS)  | VIL              | I <sub>IL</sub> (max) = -100μA                          | 0                         |     | 0.3 x<br>V <sub>CC2</sub> | V     |

|                                                                  | V <sub>OH</sub>  | I <sub>OH</sub> (max) = -0.7mA                          | V <sub>CC2</sub> -<br>0.2 |     |                           |       |

| High-Level Output Voltage<br>(EN1, EN2)                          | V <sub>OH2</sub> | $V_{CC2} = 2.5V$ to 3.6V, $I_{OH}$ (max) = -2mA         | V <sub>CC2</sub> - 0.4    |     |                           | V     |

|                                                                  | V <sub>OH3</sub> | V <sub>CC2</sub> = 1.6V, I <sub>OH</sub> (max) = -0.7mA | V <sub>CC2</sub> -<br>0.2 |     |                           |       |

| Low-Level Output Voltage                                         | VOL              | $I_{OL}(max) = 0.7mA$                                   |                           |     | 0.20                      | V     |

| (EN1, EN2, RX-LOS)                                               | Vol2             | $V_{CC2} = 2.5V$ to 3.6V, $I_{OL}$ (max) = 2mA          |                           |     | 0.40                      | v     |

| Leakage Current<br>(SC-RX-LOS, SC-RX-LOL,<br>SC-TX-LOS, RX-LOS)  | ١L               |                                                         | -10                       |     | +10                       | μA    |

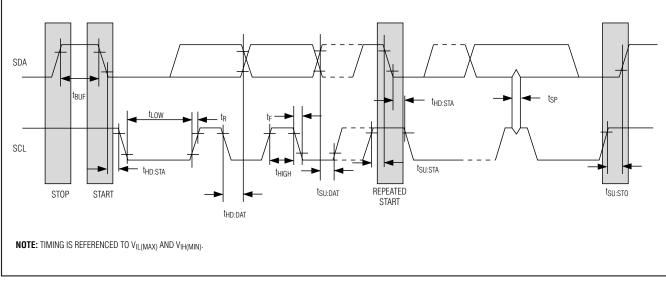

### I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                          | SYMBOL             | CONDITIONS                   | MIN TY                    | P MAX | UNITS |

|----------------------------------------------------|--------------------|------------------------------|---------------------------|-------|-------|

| SCL Clock Frequency                                | fsci               |                              | 0                         | 400   | kHz   |

| Clock Pulse-Width Low                              | tLOW               |                              | 1.3                       |       | μs    |

| Clock Pulse-Width High                             | thigh              |                              | 0.6                       |       | μs    |

| Bus Free Time Between STOP<br>and START Conditions | tBUF               |                              | 1.3                       |       | μs    |

| START Hold Time                                    | thd:SDA            |                              | 0.6                       |       | μs    |

| START Setup Time                                   | tsu:sda            |                              | 0.6                       |       | μs    |

| Data In Hold Time                                  | thd:dat            |                              | 0                         | 0.9   | μs    |

| Data In Setup Time                                 | tsu:dat            |                              | 100                       |       | ns    |

| Rise Time of Both SDA and SCL Signals              | t <sub>R</sub>     | (Note 5)                     | 20 +<br>0.1C <sub>B</sub> | 300   | ns    |

| Fall Time of Both SDA and SCL Signals              | tF                 | (Note 5)                     | 20 +<br>0.1C <sub>B</sub> | 300   | ns    |

| STOP Setup Time                                    | tsu:sto            |                              | 0.6                       |       | μs    |

| MOD-DESEL Setup Time                               | tHOST_SELECT_SETUP |                              | 2                         |       | ms    |

| MOD-DESEL Hold Time                                | tHOST_SELECT_HOLD  |                              | 10                        |       | μs    |

| Aborted Sequence Bus Release                       | tMOD-DESEL_ABORT   |                              |                           | 2     | ms    |

| Capacitive Load for Each Bus                       | CB                 | (Note 5)                     |                           | 400   | pF    |

| EEPROM Write Time                                  | tw                 | $\leq$ 4-byte write (Note 6) |                           | 16    | ms    |

### ANALOG OUTPUT CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                       | SYMBOL   | CONDITIONS                  | MIN  | ТҮР | МАХ  | UNITS |

|---------------------------------|----------|-----------------------------|------|-----|------|-------|

| IBIASSET                        | IBIASSET |                             | 0.01 |     | 1.50 | mA    |

| IBIASSET (Off-State Current)    | IBIASSET | Shutdown                    |      | ±10 | ±100 | nA    |

| IMODSET                         | IMODSET  |                             | 0.01 |     | 1.20 | mA    |

| IMODSET (Off-State Current)     | IMODSET  | Shutdown                    |      | ±10 | ±100 | nA    |

| Voltage on IBIASSET and IMODSET | VMAX     | (Note 7)                    | 0.7  |     | 3.0  | V     |

| VTHRSET                         | VTHRSET  | $I_{MAX} = 100 \mu A$       | 50   |     | 1000 | mV    |

| VTHRSET Drift                   |          | Across temperature (Note 8) | -5   |     | +5   | %     |

| VTHRSET Capacitance Load        | CTHRSET  |                             |      |     | 1    | nF    |

| APC Calibration Accuracy        |          | +25°C                       |      |     | 25   | μA    |

| APC Temp Drift                  |          | 0.200mA to 1.5mA            | -5   |     | +5   | %     |

|                                 |          | 50µA to 200µA               |      |     | 12   | μA    |

| IBMD DNL                        |          | Sink, SRC_SINK_B = 0        | -0.9 |     | +0.9 | LSB   |

|                                 |          | Source, SRC_SINK_B = 1      | -0.9 |     | +0.9 | LSD   |

| I <sub>BMD</sub> INL            |          | Sink, SRC_SINK_B = 0        | -4.0 |     | +4.0 | LSB   |

|                                 |          | Source, SRC_SINK_B = 1      | -4.0 |     | +4.0 | LOD   |

| IBMD Voltage Drift              |          |                             |      |     | 1.2  | %N    |

| I <sub>BMD</sub> FS Accuracy    |          |                             |      |     | 1.5  | %     |

DALLAS //////////

### ANALOG OUTPUT CHARACTERISTICS (continued)

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                         | SYMBOL | CONDITIONS                                   | MIN  | ТҮР | MAX  | UNITS |

|-----------------------------------|--------|----------------------------------------------|------|-----|------|-------|

| IMODSET Accuracy                  |        | +25°C, I <sub>MODSET</sub> = 0.04mA to 1.2mA | -1.5 |     | +1.5 | %     |

|                                   |        | 75µA range                                   | -0.9 |     | +0.9 |       |

|                                   |        | 150µA range                                  | -0.9 |     | +0.9 |       |

| IMODSET DNL                       |        | 300µA range                                  | -0.9 |     | +0.9 | LSB   |

|                                   |        | 600µA range                                  | -0.9 |     | +0.9 | ]     |

|                                   |        | 1200µA range                                 | -0.9 |     | +0.9 |       |

|                                   |        | 75µA range                                   | -1.5 |     | +1.5 |       |

|                                   |        | 150µA range                                  | -1.5 |     | +1.5 | ]     |

| I <sub>MODSET</sub> INL           |        | 300µA range                                  | -1.0 |     | +1.0 | LSB   |

|                                   |        | 600µA range                                  | -1.0 |     | +1.0 | ]     |

|                                   |        | 1200µA range                                 | -1.0 |     | +1.0 |       |

| IMODSET Temp Drift                |        |                                              |      |     | 5    | %     |

| I <sub>MODSET</sub> Voltage Drift |        |                                              |      |     | 1.2  | %N    |

| IMODSET FS Accuracy               |        |                                              |      |     | 1.5  | %     |

| APC Bandwidth                     |        | $I_{MD} / I_{APC} = 1$ (Note 4)              | 6    | 10  | 30   | kHz   |

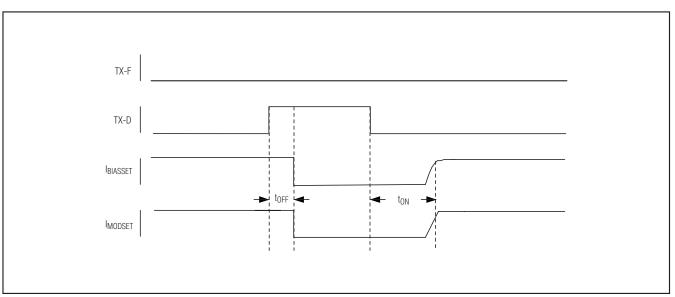

### AC ELECTRICAL CHARACTERISTICS—XFP CONTROLLER

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                | SYMBOL             | CONDITIONS                                                   | MIN | ТҮР | MAX | UNITS |

|--------------------------|--------------------|--------------------------------------------------------------|-----|-----|-----|-------|

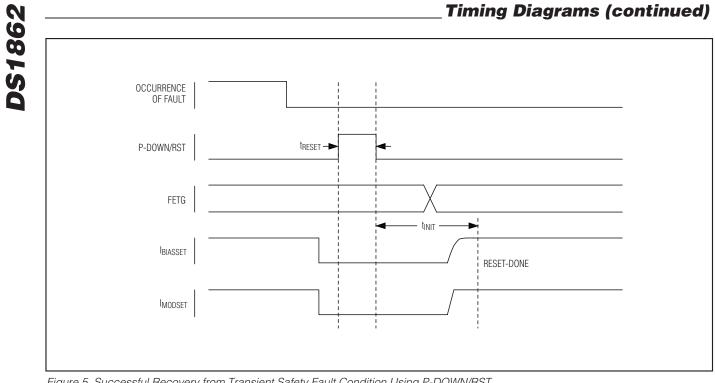

| Time to Initialize       | tinit              | V <sub>CC3</sub> within ±5% of nominal                       | 30  |     | 200 | ms    |

| TX-D Assert Time         | tOFF               | IBIAS and IMOD below 10% of nominal                          |     |     | 5   | μs    |

| TX-D Deassert Time       | ton                | IBIAS and IMOD above 90% of nominal                          |     |     | 1   | ms    |

| P-DOWN/RST Assert Time   | tpdr-on            | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal  |     |     | 100 | μs    |

| P-DOWN/RST Deassert Time | tPDR-OFF           | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal  |     |     | 200 | ms    |

| MOD-DESEL Deassert Time  | tMOD-DESEL         | Time until proper response to I <sup>2</sup> C communication |     |     | 2   | ms    |

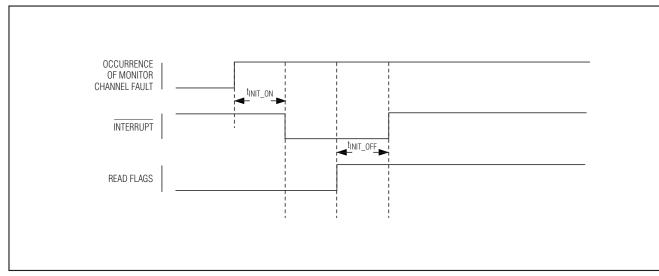

| INTERRUPT Assert Delay   | tinit_on           | Time from fault to interrupt assertion                       |     |     | 100 | ms    |

| INTERRUPT Deassert Delay | tinit_off          | Time from read (clear flags) to interrupt deassertion        |     |     | 500 | μs    |

| MOD-NR Assert Delay      | tmod-nr-on         | Time from fault to MOD-NR assertion                          |     |     | 0.5 | ms    |

| MOD-NR Deassert Delay    | tmod-NR-OFF        | Time from read (clear flags) to MOD-NR deassertion           |     |     | 0.5 | ms    |

| RX-LOS Assert Time       | tLOS-ON            | Time from SC-RX-LOS assertion to RX-LOS assertion            |     |     | 100 | ns    |

| RX-LOS Deassert Time     | tLOS-OFF           | Time from SC-RX-LOS deassertion to RX-LOS deassertion        |     |     | 100 | ns    |

| P-DOWN/RST Reset Time    | <sup>t</sup> RESET | Time from P-DOWN/RST assertion to initial reset              | 10  |     |     | μs    |

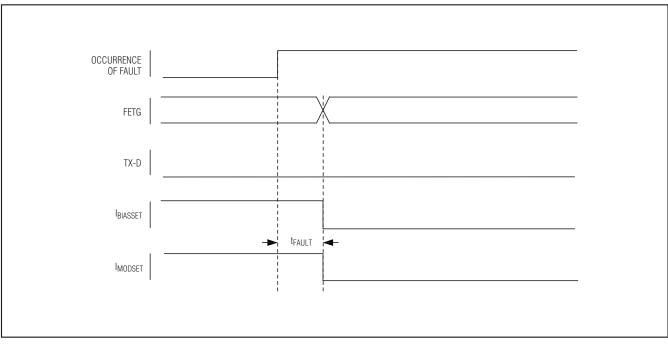

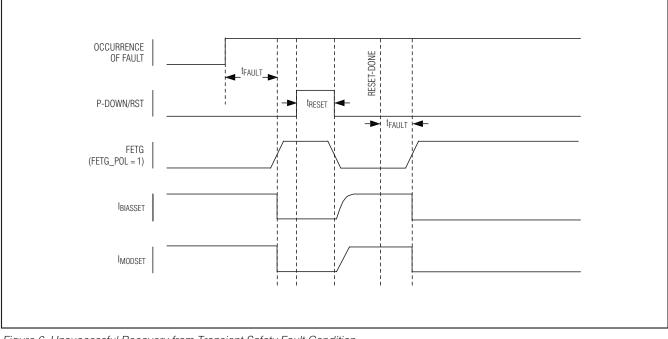

| Shutdown Time            | <b>t</b> FAULT     | Time from fault to IBIASSET, IMODSET,<br>and IBMD below 10%  |     |     | 30  | μs    |

**DS1862**

### AC ELECTRICAL CHARACTERISTICS—SOFT\* CONTROL AND STATUS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL                          | CONDITIONS                                                  | MIN | ТҮР | MAX | UNITS |

|------------------------------------------|---------------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| SOFT TX-D Assert Time                    | toff_soft                       | IBIAS and IMOD below 10% of nominal                         |     |     | 50  | ms    |

| SOFT TX-D Deassert Time                  | ton_soft                        | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal |     |     | 50  | ms    |

| SOFT P-DOWN/RST Assert Time              | tpdr-on_soft                    | I <sub>BIAS</sub> and I <sub>MOD</sub> below 10% of nominal |     |     | 50  | ms    |

| SOFT P-DOWN/RST Deassert Time            | tpdr-off_soft                   | I <sub>BIAS</sub> and I <sub>MOD</sub> above 90% of nominal |     |     | 200 | ms    |

| Soft MOD-NR Assert Delay                 | <sup>t</sup> MOD-NR-ON<br>_SOFT | Time from fault to MOD-NR assertion                         |     |     | 50  | ms    |

| Soft MOD-NR Deassert Delay               | t <sub>MOD-NR-OFF</sub> _SOFT   | Time from read (clear flags) to MOD-NR deassertion          |     |     | 50  | ms    |

| Soft RX_LOS Assert Time                  | tLOS-<br>ON_SOFT                | Time from SC-RX-LOS assertion to RX-LOS assertion           |     |     | 50  | ms    |

| Soft RX_LOS Deassert Time                | tLOS-<br>OFF_SOFT               | Time from SC-RX-LOS deassertion to RX-LOS deassertion       |     |     | 50  | ms    |

| Analog Parameter Data Ready<br>(DATA-NR) |                                 |                                                             |     |     | 500 | ms    |

\*All SOFT timing specifications are measured from the falling edge of STOP signal during I<sup>2</sup>C communication.

### **ANALOG INPUT CHARACTERISTICS**

(V<sub>CC3</sub> = +2.9V to +5.5V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                          | SYMBOL           | CONDITIONS MIN TYP MAX |                         |      |     | UNITS |    |

|----------------------------------------------------|------------------|------------------------|-------------------------|------|-----|-------|----|

| I <sub>BMD</sub> Configurable Source or Sink (+/-) |                  |                        |                         | 0.05 |     | 1.50  | mA |

|                                                    |                  | Source mode            | In the range O to 1 5mA |      | 2.0 |       | V  |

| I <sub>BMD</sub> Voltage (I <sub>BMD</sub> - 0µA)  | VBMD             | Sink mode              | IBMD range 0 to 1.5mA   |      | 1.2 |       |    |

| I <sub>BMD</sub> Input Resistance                  | R <sub>BMD</sub> |                        |                         | 400  | 550 | 700   | Ω  |

### A/D INPUT VOLTAGE MONITORING (IBIASMON, AUX2MON, AUX1MON, RSSI, BMD)

(V<sub>CC3</sub> = +2.9V to +5.5V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                                                    | SYMBOL             | CONDITIONS                     | MIN    | ТҮР    | MAX    | UNITS |

|------------------------------------------------------------------------------|--------------------|--------------------------------|--------|--------|--------|-------|

| Input Resolution                                                             | $\Delta V_{MON}$   |                                |        | 610    |        | μV    |

| Supply Resolution                                                            | $\Delta V_{CC2/3}$ |                                |        | 1.6    |        | mV    |

| Input/Supply Accuracy                                                        | Acc                | At factory setting             |        | 0.25   | 0.5    | %FS   |

| Update Rate                                                                  | tFRAME1            | AUX1MON and AUX2MON disabled   |        | 48     | 52     | m 0   |

|                                                                              | tFRAME2            | All channels enabled           |        | 64     | 75     | ms    |

| Input/Supply Offset                                                          | Vos                | (Note 4)                       |        | 0      | 5      | LSB   |

| Full-Scale Input (IBIASMON and RSSI)                                         |                    | At factory setting             | 2.4875 | 2.5    | 2.5125 | V     |

| Full-Scale Input (AUX1MON,<br>AUX2MON, V <sub>CC2</sub> , V <sub>CC3</sub> ) |                    | At factory setting<br>(Note 9) | 6.5208 | 6.5536 | 6.5864 | V     |

| BMD (Monitor) (TX-P)                                                         |                    | FS setting                     |        | 1.5    |        | mA    |

### FAST ALARMS AND V<sub>CC</sub> FAULT CHARACTERISTICS

(V<sub>CC3</sub> = +2.9V to +5.5V, V<sub>CC2</sub> = +1.6V to +3.6V,  $T_A$  = -40°C to +100°C, unless otherwise noted.)

| PARAMETER                                               | SYMBOL | CONDITIONS                        | MIN   | ТҮР   | MAX   | UNITS |

|---------------------------------------------------------|--------|-----------------------------------|-------|-------|-------|-------|

| HIGH BIAS and TX-P Threshold<br>FS                      |        | (Note 10)                         | 2.48  | 2.5   | 2.52  | mA    |

| V <sub>CC2/3</sub> Fault Asserted<br>Falling Edge Delay |        | ↓ V <sub>CC2/3</sub><br>(Note 11) |       |       | 75    | ms    |

| QT Temperature Coefficient                              |        |                                   | -3    |       | +3    | %     |

| QT Voltage Coefficient                                  |        |                                   |       |       | 0.5   | %/V   |

| QT FS Trim Accuracy (4.2V,<br>+25°C)                    |        |                                   | 2.480 | 2.500 | 2.520 | mA    |

| QT Accuracy (Trip) (INL)                                |        |                                   | -2    | 0     | +2    | LSB   |

| QT Voltco                                               |        |                                   |       |       | 0.5   | %N    |

| QT Tempco                                               |        |                                   |       | 1.5   | 3     | %     |

### NONVOLATILE MEMORY CHARACTERISTICS

$(V_{CC3} = +2.9V \text{ to } +5.5V, \text{ unless otherwise noted.})$

| PARAMETER               | SYMBOL | CONDITIONS | MIN  | ТҮР | MAX | UNITS  |

|-------------------------|--------|------------|------|-----|-----|--------|

| Endurance (Write Cycle) |        | +70°C      | 50k  |     |     | Cycles |

| Endurance (Write Cycle) |        | +25°C      | 200k |     |     | Cycles |

Note 1: All voltages are referenced to ground. Current into the IC is positive, and current out of the IC is negative.

**Note 2:** Secondary power supply is used to support optional variable power-supply feature of the XFP module. If V<sub>CC2</sub> is not used (i.e., signal conditioners using 3.3V supply), V<sub>CC2</sub> should be connected to the V<sub>CC3</sub>.

Note 3: Input signals (i.e., TX-D, MOD-DESEL, and P-DOWN/RST) have internal pullup resistors.

**Note 4:** Guaranteed by design. Simulated over process and  $50\mu A < I_{BMD} < 1500\mu A$ .

**Note 5:** C<sub>B</sub>—total capacitance of one bus line in picofarads.

**Note 6:** EEPROM write begins after a STOP condition occurs.

**Note 7:** This is the maximum and minimum voltage on the MODSET and BIASSET pins required to meet accuracy and drift specifications.

**Note 8:** For VTHRSET, offset may be as much as 10mV.

Note 9: This is the uncalibrated offset provided by the factory; offset adjustment is available on this channel.

Note 10: %FS refers to calibrated FS in case of internal calibration, and uncalibrated FS in the case of external calibration. Uncalibrated FS is set in the factory and specified in this data sheet as FS (factory). Calibrated FS is set by the user, allowing a change in any monitored channel scale.

Note 11: See the Monitor Channels section for more detail or V<sub>CC2</sub> and V<sub>CC3</sub> selection.

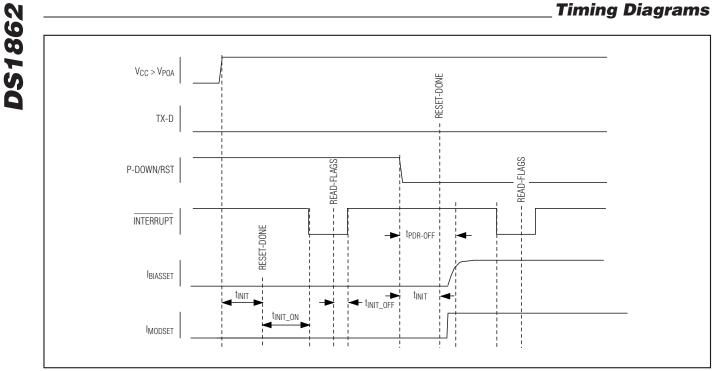

Figure 1. Power-On Initialization with P-DOWN/RST Asserted and TX-D/SOFT TX-D Not Asserted

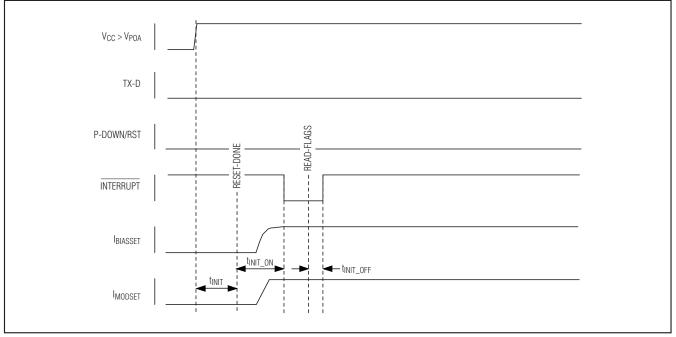

Figure 2. Power-On Initialization with P-DOWN/RST Not Asserted and TX-D/SOFT TX-D Not Asserted (Normal Operation)

DALLAS / XI/XI/VI

\_\_\_\_\_ Timing Diagrams (continued)

**DS1862**

Figure 3. TX-D Timing During Normal Operation

Figure 4. Detection of Safety Fault Condition

Figure 5. Successful Recovery from Transient Safety Fault Condition Using P-DOWN/RST

Figure 6. Unsuccessful Recovery from Transient Safety Fault Condition

### \_Timing Diagrams (continued)

Figure 7. Monitor Channel Fault Timing

**DS1862**

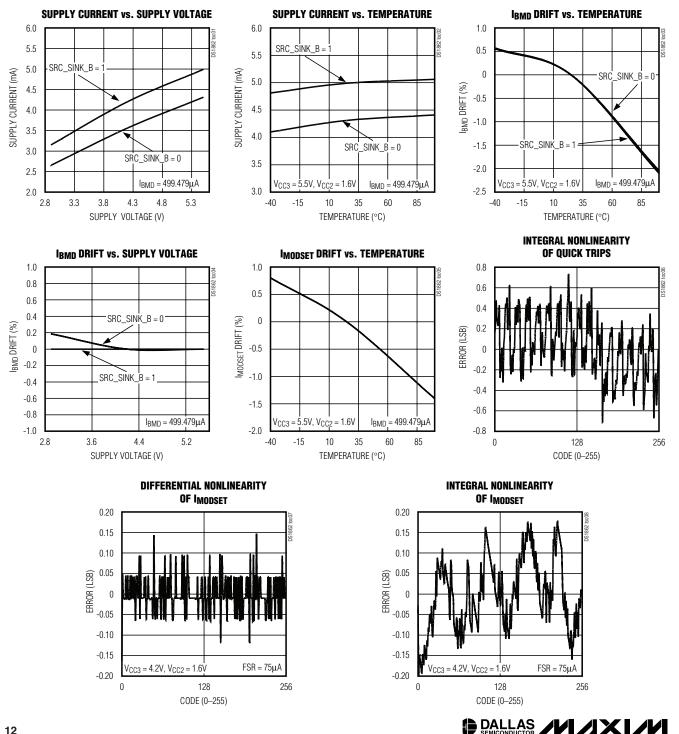

$(T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics**

**DS1862**

12

**Pin Description**

| NAME             | PIN | FUNCTION                                                                                                                                                 |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-DOWN/RST       | A1  | <b>Power-Down/Reset Input.</b> This multifunction pin is pulled high internally. See the <i>Power-Down/Reset Pin</i> section for additional information. |

| SC-RX-LOS        | A2  | Signal Conditioner Receiver Loss-of-Signal Input. This pin is an active-high input with LVCMOS/LVTTL voltage levels.                                     |

| SC-RX-LOL        | A3  | Signal Conditioner Receiver Loss-of-Lock Input. This pin is an active-high input with LVCMOS/LVTTL voltage levels.                                       |

| THRSET           | A4  | Threshold Set Output. This pin is a programmable voltage source that can be used for Rx signal conditioner.                                              |

| V <sub>CC2</sub> | A5  | 1.8V Power-Supply Input                                                                                                                                  |

| RX-LOS           | B1  | Receiver Loss of Signal. This open-drain output indicates when there is insufficient optical power.                                                      |

| SCL              | B2  | I <sup>2</sup> C Serial-Clock Input                                                                                                                      |

| FETG             | B3  | FET Gate Output. This pin can drive an external FET gate associated with safety fault disconnect.                                                        |

| RSSI             | B4  | Received Power Signal Input                                                                                                                              |

| MODSET           | B5  | Modulation Current Output. This pin is only capable of sinking current.                                                                                  |

| TX-D             | C1  | Transmit Disable Input. This pin has an internal pullup resistor.                                                                                        |

| SDA              | C2  | I <sup>2</sup> C Serial-Data Input/Output                                                                                                                |

| EN1              | C3  | Enable 1 Output. Functional control for signal conditioners.                                                                                             |

| EN2              | C4  | Enable 2 Output. Functional control for signal conditioners.                                                                                             |

| BIASSET          | C5  | Bias Current Output. This pin is only capable of sinking current.                                                                                        |

| INTERRUPT        | D1  | <b>Interrupt.</b> This open-drain output pin indicates a possible operational fault or critical status condition to the host.                            |

| MOD-NR           | D2  | Indicating Module Operational Fault. Open-drain output. This pin indicates the status of the MOD-NR flag.                                                |

| AUX1MON          | D3  | Aux1 Monitor Input. This pin can be used to measure any voltage quantity.                                                                                |

| AUX2MON          | D4  | Aux2 Monitor Input. This pin can be used to measure any voltage quantity or external temperature                                                         |

| BMD              | D5  | Monitor Diode Current Input. This pin is capable of sourcing or sinking current.                                                                         |

| GND              | E1  | Ground                                                                                                                                                   |

| MOD-DESEL        | E2  | <b>Module Deselect Input.</b> This pin must be pulled low to enable I <sup>2</sup> C communication. This pin is pulled high internally.                  |

| IBIASMON         | E3  | Bias Monitor Input. This pin can be used to monitor the voltage across the laser.                                                                        |

| SC-TX-LOS        | E4  | Signal Conditioner Transmitter Loss of Signal. This pin is an active-high input with LVCMOS/LVTTL voltage levels.                                        |

| V <sub>CC3</sub> | E5  | 3.3V or 5V Power-Supply Input                                                                                                                            |

14

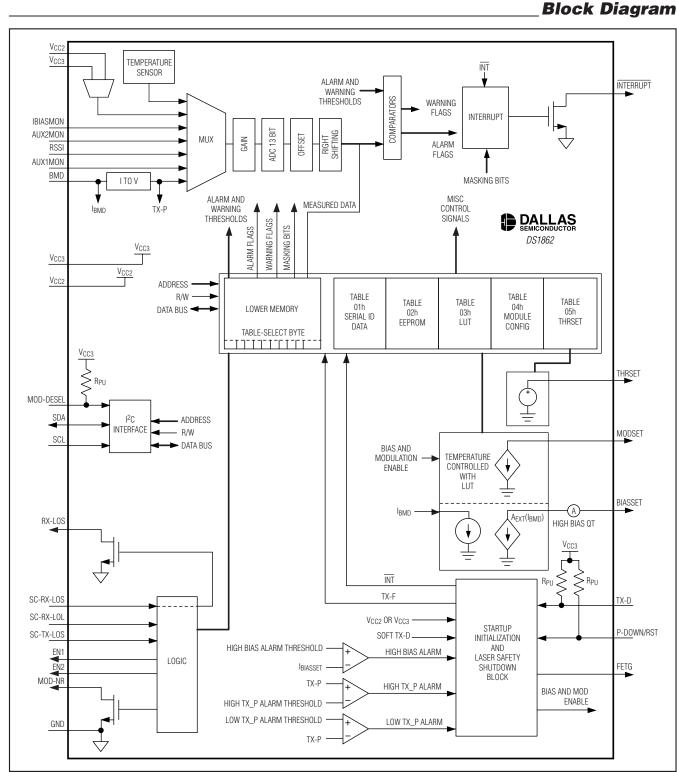

### **Detailed Description**

The DS1862's block diagram is described in detail within the following sections and memory map/memory description.

#### **Automatic Power Control (APC)**

The DS1862's APC is accomplished by closed-loop adjustment of the bias current (BIASSET) until the feedback current (BMD) from a photodiode matches the value determined by the APC registers. The relationship between the APC register and I<sub>BMD</sub> is given by:

> IBMD = 5.859µA x APC<sub>C</sub><7:0> + (1.464µA x APC<sub>F</sub><1:0>)

where  $APC_C < 7:0$  is the 8-bit value in Table 04h, Byte 84h that controls the coarse BMD current, and  $APC_F < 1:0$  is the 2-bit value that controls the fine BMD current.

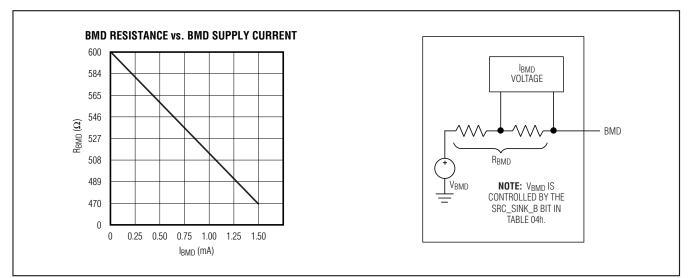

The BMD pin appears as a voltage source in series with two resistors. The overall equivalent resistance of the BMD input pin can be closely approximated by the plot in Figure 8. The voltage that appears on the BMD pin, assuming no external current load, is 1.2V if BMD is in sink-current mode (SRC\_SINK\_B = 0) or 2.0V if BMD is set to source current (SRC\_SINK\_B = 1). This allows the photodiode to be referenced to either V<sub>CC3</sub> or GND. When the control loop is at steady state, the BMD current setting matches the current that is measured by the I<sub>BMD</sub> voltage across the internal resistance. During a transient period, the DS1862 adjusts the current drive on the BIASSET pin to bring the loop into steady state. The DS1862 is designed to support loop gains of 1/20 to 10. On power-up, the BMD current ramps up to the previously saved current setting in EEPROM APC registers. While operating, the DS1862 monitors the BMD current. If it begins to deviate from the desired (set)  $I_{BMD}$  value, the current on the BIASSET pin is again adjusted to compensate.

#### Extinction Ratio Control Lookup Table (LUT)

The DS1862 uses a temperature indexed lookup table (LUT) to control the extinction ratio. The MODSET pin is capable of sinking current based on the 8-bit binary value that is controlling it. The DS1862 also features a user-configurable current range to increase extinction ratio resolution. Five current ranges, as described in Table 1, are available to control the current entering MODSET.

# Table 1. Selectable Current Ranges forMODSET

| LUT CURRENT RANGE<br>TABLE 04h, BYTE 86h<2:0> | CURRENT RANGE<br>(µA) |

|-----------------------------------------------|-----------------------|

| 000                                           | 0 to 75               |

| 001                                           | 0 to 150              |

| 010                                           | 0 to 300              |

| 011                                           | 0 to 600              |

| 100                                           | 0 to 1200             |

Figure 8. Approximate Model of the BMD Input

If the largest current range is selected, the maximum value of FFh (from LUT) corresponds to a 1200µA sink current. Regardless of the current range, the MODSET value always consists of 256 steps, including zero.

$\mathsf{I}_{\mathsf{MODSET}}$  can be controlled automatically with the temperature-based lookup table, or by three other manual methods.

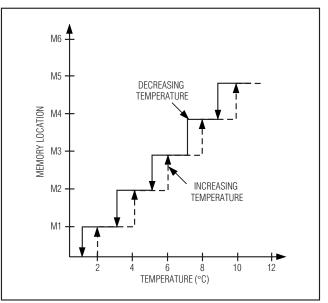

Automatic temperature addressed lookup is accomplished by an internal or external temperature sensor controlling an address pointer. This pointer indexes through 127 previously loaded 8-bit current values stored in the LUT. Each one of the 127 temperature slot locations corresponds to a 2°C increment over the -40°C to +102°C temperature range. Any temperature above or below these points causes the code in the first or last temperature slot to be indexed. Both the internal temperature sensor and an external sensor connected to AUX2MON are capable of providing a signal to control the extinction ratio automatically with an indexed LUT. Table 2 illustrates the relationship between the temperature and the memory locations in the LUT.

### Table 2. Temperature Lookup Table

| TEMPERATURE (°C) | CORRESPONDING LOOKUP<br>TABLE ADDRESS |

|------------------|---------------------------------------|

| < -40            | 80h                                   |

| -40              | 80h                                   |

| -38              | 81h                                   |

| -36              | 82h                                   |

|                  |                                       |

| +96              | C4h                                   |

| +98              | C5h                                   |

| +100             | C6h                                   |

| +102             | C7h                                   |

| > +102           | C7h                                   |

Automatic and manual control of MODSET is controlled by two bits, TEN and AEN, that reside in Table 04h, Byte B2h. By default (from factory) TEN and AEN are both set, causing complete automatic temperaturebased lookup. If TEN and/or AEN are altered, the DS1862 is set to one of the manual modes. Table 3 describes manual mode functionality.

### Table 3. Truth Table for TEN and AEN Bits

| TEN | AEN | DS1862 LUT FUNCTIONALITY                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Manual mode that allows users to write a<br>value directly to the LUT VALUE register<br>(Table 04h, Byte B1h) to drive MODSET. While<br>in this mode, the LUT INDEX POINTER register<br>is not being updated, and no longer drives the<br>LUT VALUE register.                                                                                                                                   |

| 0   | 1   | Manual mode that allows users to write a<br>value directly to the LUT VALUE register<br>(Table 04h, Byte B1h) to drive MODSET. While<br>in this mode, the LUT INDEX POINTER register<br>is still being updated; however, it no longer<br>drives the LUT VALUE register.                                                                                                                         |

| 1   | 0   | Manual mode that allows users to write a<br>value to the LUT INDEX POINTER register<br>(Table 04h, Byte B0), then the DS1862<br>updates the LUT VALUE register (Table 04h,<br>Byte B1h) based on the user's index pointer.                                                                                                                                                                      |

| 1   | 1   | Automatic mode (factory default). This mode<br>automatically indexes the LUT based on<br>temperature, placing the resulting LUT<br>address in the LUT INDEX POINTER register<br>(Table 04h, Byte B0h). Then the MODSET<br>setting is transferred from that LUT address to<br>the LUT VALUE register (Table 04h, Byte B1h).<br>Lastly, the I <sub>MODSET</sub> is set to the new MODSET<br>code. |

BALLAS ANALY

#### **Monitor Channels**

The DS1862 has seven monitored voltage signals that are polled in a round-robin multiplexed sequence and are updated with the frame rate, tFRAME. All channels are read as 16-bit values, but have 13-bit resolution, and with the exception of temperature measurements, all channels are stored as unsigned values. The resulting 16-bit value for all monitored channels, except internal temperature, is calculated by internally averaging the analog-to-digital result eight times. The resulting internal temperature monitor channel is averaged 16 times. See the *Internal Calibration* section for a complete description of each channel's method(s) of internal calibration.

The AUX1MON, AUX2MON, and  $V_{CC2/3}$  monitor channels are optional and can be disabled. This feature allows for shorter frame rate for the essential monitor channels. Channels that cannot be disabled are internal temperature, BMD, RSSI, and IBIASMON. A table of full-scale (FS) signal values (using factory internal calibration without right shifting) and the resulting FS code values for all seven channels is provided in Table 4.

#### Measuring Temperature—Internal or External

The DS1862 is capable of measuring temperature on three different monitor channels: internal temperature sensor, AUX1MON, and AUX2MON. Only the internal temperature and AUX2MON channels are capable of indexing the LUT to control the extinction ratio. To use an external temperature sensor on AUX2MON, the TEMP\_INT/EXT bit in Table 04h, Byte 8Bh, must be set. While AUX2MON controls the extinction ratio, the internal temperature sensor does not stop running; despite extinction ratio control by AUX2MON, it is this internal temperature signal that continues to control the status of temperature flags. Also, when TEMP\_INT/EXT = 1, the internal temperature clamps at -40°C and +103.9375°C, and when TEMP\_INT/EXT = 0 it clamps at -120°C and +127.984°C. AUX2MON, however, does have its own flag to indicate an out-of-tolerance condition and assert the **INTERRUPT** pin.

Both AUX1MON and AUX2MON can be used to measure temperature as a function of voltage on their respective pins. They can be enabled by selecting either 0h or 4h from Table 5. Internal (or external) calibration may be required to transmute the input voltage to the desired two's-complement digital code, readable from the result registers in lower memory, Bytes 6Ah, 6Bh, 6Ch, 6Dh.

#### Measuring VCC2/3

The DS1862 has the flexibility to internally measure either V<sub>CC2</sub> or V<sub>CC3</sub> to monitor supply voltage. V<sub>CC2</sub> or V<sub>CC3</sub> is user selectable by the V<sub>CC2/3</sub>\_SEL bit in Table 01h, Byte DCh. To remove V<sub>CC2/3</sub> from the round-robin monitor update scheme, despite having V<sub>CC2</sub> or V<sub>CC3</sub> selected to be monitored, the Reserve\_EN bit in Table 04h, Byte 8Bh can be programmed to a 0. The analog power-on-reset flag, POA, indicates the status of V<sub>CC3</sub> power supply. Even though POA seems to behave similarly to V<sub>CC2/3</sub> monitor channel, it is completely separate and has no connection.

| RESERVE_EN | V <sub>CC2/3</sub> _SEL | RESULT                                 |

|------------|-------------------------|----------------------------------------|

| 0          | 0                       | V <sub>CC2/3</sub> result not enabled. |

| 0          | 1                       | V <sub>CC2/3</sub> result not enabled. |

| 1          | 0                       | V <sub>CC3</sub> is being measured.    |

| 1          | 1                       | V <sub>CC2</sub> is being measured.    |

#### Measuring APC and Laser Parameters—BMD, IBIASMON, RSSI

BMD and BIASSET are used to control and monitor the laser functionality. Regardless of the set BMD current in the APC register, the DS1862 measures BMD pin current and uses this value not only to adjust the current on the BIASSET pin, but also to monitor TX-P as well. The IBIASMON pin is used to input a voltage signal to the DS1862 that can be used to monitor the bias current through the laser. This monitor channel does not drive the HIGH BIAS quick-trip (QT) alarms for safety

| SIGNAL             | +FS SIGNAL | +FS (hex) | -FS SIGNAL | -FS (hex) | LSB      |

|--------------------|------------|-----------|------------|-----------|----------|

| Temperature        | 127.984°C  | 7FF8      | -120°C     | 8800      | 0.0625°C |

| V <sub>CC2/3</sub> | 6.5528V    | FFF8      | OV         | 0000      | 100µV    |

| IBIASMON           | 2.4997V    | FFF8      | OV         | 0000      | 38.147µV |

| RSSI               | 2.4997V    | FFF8      | OV         | 0000      | 38.147µV |

| AUX1MON            | 6.5528V    | FFF8      | OV         | 0000      | 38.147µV |

| AUX2MON            | 6.5528V    | FFF8      | OV         | 0000      | 38.147µV |

| BMD (TX-P)         | 1.5mA      | FFF8      | 0mA        | 0000      | 22.888nA |

### Table 4. Monitor Channel FS and LSB Detail

fault functionality, current on the BIASSET pin is monitored by the DS1862 to control the HIGH BIAS quicktrip alarm. Similar to TX-P, the RSSI pin is used to measure the received power, RX-P.

### Measuring Voltage Quantities using AUX1MON and AUX2MON

AUX1MON and AUX2MON are auxiliary monitor inputs that may be used to measure additional parameters. AUX1/2MON feature a user-selectable register that determines the measured value's units (i.e., voltage, current, or temperature). In addition to indicating units, some of the 4-bit op codes, in Table 5, also place the part in special modes used for alarms and faults internally. Whichever units' scale is selected, the DS1862 is only capable of measuring a positive voltage quantity, therefore internal or external calibration may be

# Table 5. AUX1/2MON FunctionalitySelection (Unit Selection)

| VALUE | DESCRIPTION OF AUX1/2MON INTENDED USE<br>(UNITS OF MEASURE)                   |

|-------|-------------------------------------------------------------------------------|

| 0000b | Auxiliary monitoring not implemented                                          |

| 0001b | APD bias voltage (16-bit value is voltage in units of 10mV)                   |

| 0010b | Reserved                                                                      |

| 0011b | TEC current (mA) (16-bit value is current in units of 0.1mA)                  |

| 0100b | Laser temperature (same encoding as module temperature)                       |

| 0101b | Laser wavelength                                                              |

| 0110b | +5V supply voltage (encoded as primary voltage monitor)                       |

| 0111b | +3.3V supply voltage (encoded as primary voltage monitor)                     |

| 1000b | +1.8V supply voltage (encoded as primary voltage monitor) (V <sub>CC2</sub> ) |

| 1001b | -5.2V supply voltage (encoded as primary voltage monitor)                     |

| 1010b | +5V supply current (16-bit value is current in 0.1mA)                         |

| 1101b | +3.3V supply current (16-bit value is current in 0.1mA)                       |

| 1110b | +1.8V supply current (16-bit value is current in 0.1mA)                       |

| 1111b | -5.2V supply current (16-bit value is current in 0.1mA)                       |

required to get the binary value to match the measured quantity. A table of acceptable units and/or their corresponding user-programmable 4-bit op code is provided below.

#### Alarms and Warning Flags Based on Monitor Channels

All of the monitor channels feature alarm and warning flags that are asserted automatically as user-programmed thresholds are internally compared with monitor channel results. Flags may be set, which, if not masked, will generate an interrupt on the INTERRUPT pin or generate a safety fault. Whenever V<sub>CC2/3</sub>, AUX2MON, AUX1MON, RSSI, and internal temperature go beyond their threshold trip points and the corresponding mask bit is 0, an interrupt is generated on the INTERRUPT pin and a corresponding warning or alarm flag is set. Similarly, a safety fault occurs whenever BMD or BIASSET go beyond threshold trip points. When this happens, the FETG pin immediately asserts and BIASSET and MODSET currents are shut down.

#### **Monitor Channel Conversion Example**

Table 6 provides an example of how a 16-bit ADC code corresponds to a real life measured voltage using the factory-set calibration on either RSSI or IBIASMON. By factory default, the LSB is set to 38.147µV.

### Table 6. A/D Conversion Example

| MSB (BIN) | LSB (BIN) | VOLTAGE (V) |

|-----------|-----------|-------------|

| 11000000  | 00000000  | 1.875       |

| 1000000   | 1000000   | 1.255       |

To calculate V<sub>CC2</sub>, V<sub>CC3</sub>, AUX1MON, or AUX2MON, convert the unsigned 16-bit value to decimal and multiply by 100  $\mu$ V.

To calculate the temperature (internal), treat the two'scomplement value binary number as an unsigned binary number, then convert it to decimal and divide by 256. If the result is grater than or equal to 128, subtract 256 from the result.

Temperature: high byte = -128°C to +127°C signed; low byte = 1/256°C.

### **Table 7. Temperature Bit Weights**

| S   | 2 <sup>6</sup>  | 2 <sup>5</sup>  | 24  | 2 <sup>3</sup>  | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |

|-----|-----------------|-----------------|-----|-----------------|----------------|----------------|----------------|

| 2-1 | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2-4 | 2 <sup>-5</sup> | —              |                | _              |

# Table 8. Temperature ConversionExamples

| MSB (BIN) | LSB (BIN) | TEMPERATURE (°C) |

|-----------|-----------|------------------|

| 01000000  | 00000000  | +64              |

| 01000000  | 00001000  | +64.03215        |

| 01011111  | 00000000  | +95              |

| 11110110  | 00000000  | -10              |

| 11011000  | 00000000  | -40              |

#### **Internal Calibration**

The DS1862 has two means for scaling an analog input to a digital result. The two devices alter the gain and offset of the signal to be calibrated. All of the inputs except internal temperature have unique registers for both the gain and the offset that can be found in Table 04h. See the table below for a complete description of internal calibration capabilities including right-shifting for all monitor channels.

**Table 9. Internal Calibration Capabilities**

| SIGNAL             | INTERNAL<br>SCALING | INTERNAL<br>OFFSET | RIGHT-<br>SHIFTING |

|--------------------|---------------------|--------------------|--------------------|

| Temperature        |                     | х                  | _                  |

| V <sub>CC2/3</sub> | х                   | х                  | —                  |

| IBIASMON           | х                   | х                  | Х                  |

| RSSI (RX-P)        | х                   | х                  | х                  |

| AUX1MON            | х                   | х                  | Х                  |

| AUX2MON            | х                   | х                  | х                  |

| BMD (TX-P)         | х                   | х                  | х                  |

To scale a specific input's gain and offset, the relationship between the analog input and the expected digital result must be known. The input that would produce a corresponding digital result of all zeroes is the null value (normally this input is GND). The input that would produce a corresponding digital result of all ones is the full-scale (FS) value minus one LSB. The FS value is also found by multiplying an all ones digital value by the weighted LSB. For example, a digital reading is 16 bits long, assume that the LSB is known to be 50µV, then the FS value would be  $2^{16} \times 50$ µV = 3.2768V.

A binary search can be used to find the appropriate gain value to achieve the desired FS of the converter. Once the gain value is determined, then it can be loaded into the appropriate channels' Gain register. This requires forcing two known voltages on to the monitor input pin. For best results, one of the forced voltages should be the NULL input and the other should be 90% of FS. Since the LSB of the least significant byte in the digital reading register is known, the expected digital results are also known for both the null and FS value inputs. Figure 9 describes the hysteresis built into the DS1862's LUT functionality.

Figure 9. Lookup Table Hysteresis

With the exception of BMD, which can source or sink current, all monitored channels are high impedance and are only capable of directly measuring a voltage. If other measured quantities are desired, such as light, frequency, power, current, etc., they must be converted to a voltage. In this situation the user is not interested in voltage measurement on the monitored channel, but the measurement of the desired parameter. Only the relationship between the indirect measured quantity (light, frequency, power, current, etc.) to the expected digital result must be known.

An example of gain scaling using the recommended binary search procedure is provided with the following pseudo code.

To help will the computation, two integers need to be defined: count 1 and count 2. CNT1 = NULL / LSB and CNT2 = 90%FS / LSB. CLAMP is the largest result that can be accommodated.

DALLAS

DS1862

/\* Assume that the Null input is 0.5V. \*/

/\* In addition, the requirement for LSB is 50 $\mu V.$  \*/

FS = 65536 \* 50e-6; /\* 3.2768 \*/

CNT1 = 0.5 / 50e-6; /\* 10000 \*/

CNT2 = 0.90\*FS / 50e-6; /\* 58982 \*/

/\* Thus the NULL input of 0.5V and the 90% of FS input is 2.94912V. \*/

set the trim-offset-register to zero;

set Right-Shift register to zero (Typically zero. See the Right-Shifting section);

gain\_result = 0h;

CLAMP = FFF8h/2^(Right\_Shift\_Register);

For n = 15 down to 0

begin

$gain_result = gain_result + 2^n;$

Force the 90% FS input (2.94912V);

Meas2 = read the digital result from the part;

```

If Meas2 >= CLAMP then

```

$gain_result = gain_result - 2^n;$

Else

```

Force the NULL input (0.5V);

```

Meas1 = read the digital result from the part;

```

if (Meas2 - Meas1) > (CNT2 - CNT1) then

```

```

gain_result = gain_result - 2^n;

```

end;

Set the gain register to gain\_result;

The gain register is now set and the resolution of the conversion will best match the expected LSB. The next step is to calibrate the offset of the DS1862. With the correct gain value written to the gain register, again force the NULL input to the monitor pin. Read the digital result from the part (Meas1). The offset value is equal to negative value of Meas1.

OFFSET\_REGISTER =

$$\left[\frac{(-1)Meas1}{4}\right]$$

The calculated offset is now written to the DS1862 and the gain and offset-scaling procedure is complete.

#### Right-Shifting A/D Conversion Result (Scalable Dynamic Ranging)

Right-shifting is a digital method used to regain some of the lost ADC range of a calibrated system. If rightshifting is enabled, by simply loading a non-zero value into the appropriate Right-Shifting Register, then the DS1862 shifts the calibrated result just before it is stored into the monitor channels' register. If a system is calibrated so the maximum expected input results in a digital output value of less than 7FFFh (50% of FS), then it is a candidate for using the right-shifting method.

If the maximum desired digital output is less than 7FFFh, then the calibrated system is using less than 1/2 the ADC's range. Similarly, if the maximum desired digital output is less than 1FFFh, then the calibrated system is only using 1/8th the ADC's range. For example, if an applied maximum analog signal yields a maximum digital output less than 1FFCh, then only 1/8th of the ADC's range is used. Right-shifting improves the resolution of the measured signal as part of internal calibration. Without right-shifting, the 3 MS bits of the ADC will never be used. In this example, a value of 3 for the right-shifting maximizes the ADC range and a larger gain setting must be loaded to achieve optimal conversion. No resolution is lost since this is a 13-bit converter that is left justified. The value can be right-shifted 3 times without losing any resolution. The following table describes when the right-shifting method can be effectively used.

### Table 10. Right-Shifting Selection

| OUTPUT RANGE USED WITH<br>ZERO RIGHT-SHIFTS | NUMBER OF RIGHT-<br>SHIFTS NEEDED |

|---------------------------------------------|-----------------------------------|

| 0h FFFFh                                    | 0                                 |

| 0h 7FFFh                                    | 1                                 |

| 0h 3FFFh                                    | 2                                 |

| 0h 1FFFh                                    | 3                                 |

| 0h 0FFFh                                    | 4                                 |

#### Warning and Alarm Logic Based on AUX1/2MON, VCC2/3, Temp, RX-P, and IBIASMON

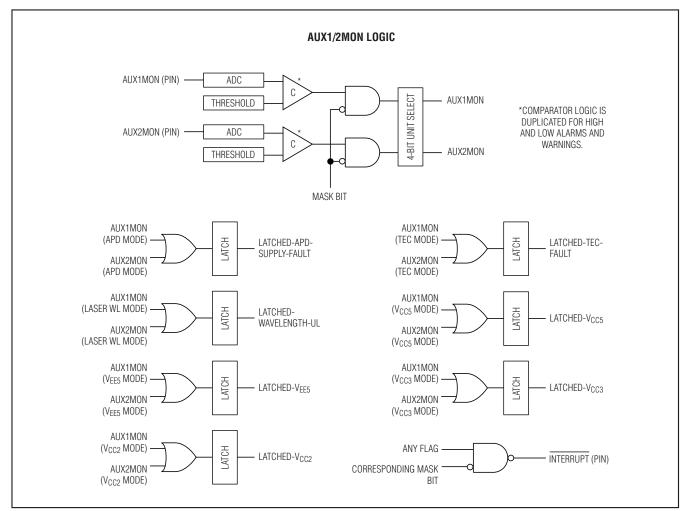

The DS1862 is capable of generating an alarm and/or warning whenever an analog monitored channel goes out of a user-defined tolerance. Temperature, bias current (based on IBIASMON), receive power (based on RSSI), AUX1MON, AUX2MON, and V<sub>CC2/3</sub>, are moni-

tored channels that generate latched flags. See the figure below for more detail pertaining to AUX1MON and AUX2MON. Flags are latched into a high state the first time a monitored channel goes out of the defined operating window and for each monitored signal there is a Mask bit that can be set to prevent the corresponding alarm or warning flag from being set. Once a flag is set, it is cleared by simply reading its memory location.

Figure 10. AUX1/2MON Monitor Logic

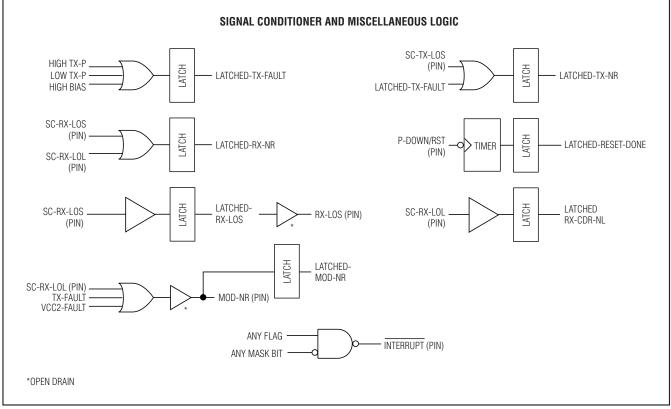

#### Warning and Alarm Logic Based on Signal Conditioners

The DS1862 also has flags that are set by certain logical conditions on signal conditioner (SC) pins: SC-RX-LOL, SC-RX-LOS, SC-TX-LOS. Similarly, for each latched signal conditioner flag there are also mask bits that are capable of preventing the alarm or warning flag from causing an INTERRUPT pin to assert. Again, flags are cleared automatically whenever their memory address is read. See Figure 11 for more detail.

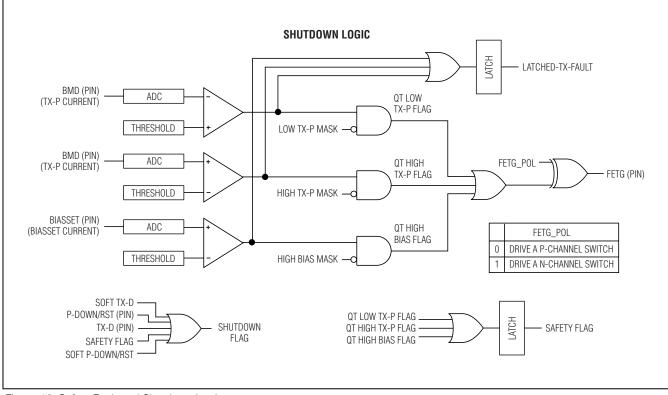

#### Quick-Trip Logic and FETG Shutdown Functionality

In addition to alarms and warnings, the DS1862 also has quick-trip (QT) functionality (sometimes referred to

as fast alarms) that is capable of shutting down the LASER with the FETG pin in conjunction with shutting down IMODSET and IBIASSET. IBMD and IBIASSET currents are measured and are compared with user-defined trip points to set the quick-trip flags: QT LOW TX-P, QT HIGH TX-P, and QT HIGH BIAS. These flags are also capable of being masked to prevent FETG from being asserted when an out-of-tolerance condition is detected. FETG is not asserted by setting the TX-D pin, SOFT TX-D, or P-DOWN/RST pin to a high state, however, IMODSET, and IBIASSET will shut down. See Figure 12 for more detail.

Figure 11. Signal Conditioner and Other Logic

**DS1862**

Figure 12. Safety Fault and Shutdown Logic

The polarity of the FETG pin can also be reversed by setting the FETG\_POL bit. Once a safety fault has occurred, the FETG pin and all of the attendant flags can only be reset by pulsing the P-DOWN/RST pin high for the reset time, tRESET, or by toggling the SOFT P-DOWN/RST bit in Byte 6Eh, bit 3. See the *Power-Down/Reset Pin* section for more details.

#### **Power-Down/Reset Pin**

The P-DOWN/RST pin is a multifunction input pin that resets and/or powers down the DS1862. Since the pin is internally pulled up, its normal state is released, which corresponds to power-down mode. If the P-DOWN/RST pin is released, or driven high, the DS1862 responds by shutting down the MODSET and BIASSET currents. Once the pin is pulled low, operation continues (if not inhibited by a safety fault). Besides powering down the DS1862, a high-going pulse with minimum reset time, tRESET, can be applied to the P-DOWN/RST pin. This is necessary to restart the DS1862, especially if it is in a safety shutdown condition and needs to be restarted

after the safety condition has been rectified. See the timing diagrams for proper pin timing.

#### **Power-Down Functionality**

During power-down mode IBIASSET and IMODSET drop below 10µA, effectively shutting down the laser. FETG is not asserted and safety faults do not occur during this period. During power-down, I<sup>2</sup>C communication is still active, but the signal conditioner pins EN1 and EN2 are noncontrollable and automatically change to the states: EN1 = 1 and EN2 = 0. Other internal flags/signals that are based on the signal conditioner inputs still reflect the status on the signal conditioner pins during power-down. For example, RX-LOS still reflects the status of SC-RX-LOS, and MOD-NR still reflects the logical states for the signal conditioner pins. Similarly, it is possible for FETG to be asserted, even though the BIASSET and MODSET currents are shut down. However, during power-down and a short period, tPDR-OFF, during powerup, TX-P Low flag is ignored (internally automatically masked out) and does not contribute to FETG's logic.

**DS1862**

During an asserted period of P-DOWN/RST (DS1862 in power-down), and V<sub>CC3</sub> is cycled, the DS1862 remains in power-down mode upon power-up. While in power-down mode the INTERRUPT pin does not assert. Once V<sub>CC3</sub> has returned, the reset done flag asserts after the interrupt assert delay,  $t_{INIT_ON}$ .

#### Reset Functionality

Besides powering down the DS1862, the P-DOWN/RST pin also functions to reset the DS1862. After a highgoing pulse of time tRESET, several events occur within the DS1862. First, MODSET and BIASSET currents shut down and are then reinstated. Second, between the rising edge of the reset pulse and the assertion of the reset-done flag (t<sub>INIT</sub>), the low TX-P flag is ignored and does not cause FETG to trip. After time t<sub>INIT</sub>, the low TX-P flag becomes functional. Also, at this time, the reset-done flag is asserted, causing an interrupt to be generated. If there are no faults before t<sub>INIT</sub>, then no interrupts are asserted on the INTERRUPT pin.

If V<sub>CC3</sub> is powered up while P-DOWN/RST is high, then the reset-done flag must be cleared twice. The first time the reset-done flag is generated by V<sub>CC3</sub> powering up, the second time reset-done is generated by a falling edge on P-DOWN/RST. If V<sub>CC3</sub> is continuously powered while P-DOWN/RST is low then only one resetdone flag needs to be cleared. See the timing diagrams for graphical detail.

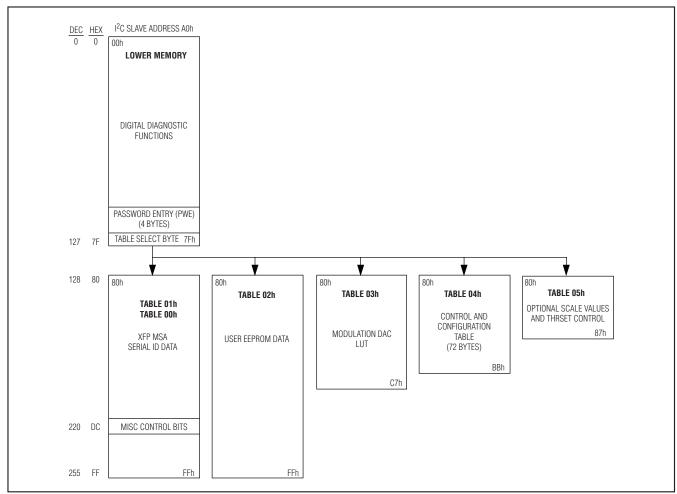

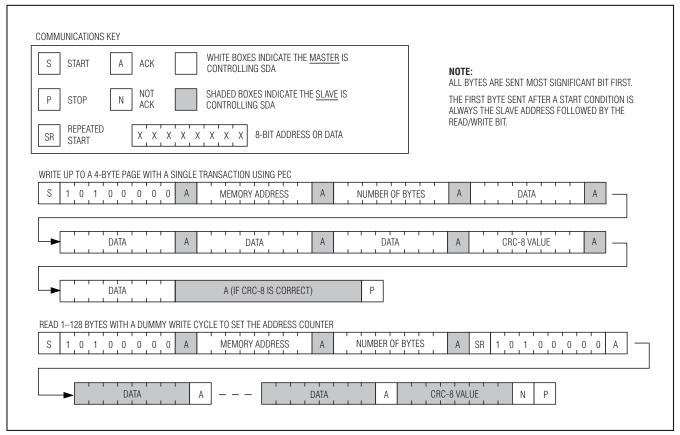

#### Memory Map

#### **Memory Organization**

The DS1862 features six separate memory tables that are internally organized into 4-word rows. The Lower Memory is addressed from 00h to 7Fh and contains alarm and warning thresholds, flags, masks, several control registers, password entry area (PE), and the

table select byte. Table 01h primarily contains user EEPROM as well as several control bytes for various functions. Table 02h is strictly user EEPROM that is protected by a host password. Table 03h is strictly used for controlling the extinction ratio with an LUT. Table 04h is a multifunction space that contains internal calibration values for monitored channels, LUT index pointers, and miscellaneous control bytes. Table 05h is factory programmed and stores SCALE values for use with suggested external temperature sensors. Also, one byte in Table 05h controls the THRSET voltage source and is completely accessible without any password protection. See the Detailed Register Description section for a more complete detail of each byte's function, as well as Table 11 for read/write permissions for each byte. Many nonvolatile memory locations are actually SRAM-shadowed EEPROM, which are controlled by the SEEB bit in Table 04h, Byte B2h.

The DS1862 incorporates SRAM-shadowed EEPROM memory locations for key memory addresses that may be rewritten many times. By default the shadowed-EEPROM bit, SEEB, is not set and these locations act as ordinary EEPROM. By setting SEEB, these locations begin to function like SRAM cells, which allow an infinite number of write cycles without concern of wearing out the EEPROM. This also eliminates the requirement for the EEPROM write time, twp. Because changes made with SEEB enabled do not affect the EEPROM, these changes are not retained through power cycles. The power-up value is the last value written with SEEB disabled. This function can be used to limit the number of EEPROM writes during calibration or to change the monitor thresholds periodically during normal operation helping to reduce the number of times EEPROM is written. The following information describes which locations are shadowed-EEPROM.

BALLAS ///X//

Figure 13. General View of DS1862 Memory Organization

| PERMISSION | READ                                                                           | WRITE               |

|------------|--------------------------------------------------------------------------------|---------------------|

| <0>        | At least one byte in thi<br>the rest of the bytes, s<br>separately for permiss | o look at each byte |

| <1>        | ALL                                                                            | ALL                 |

| <2>        | ALL                                                                            | MODULE              |

| <3>        | ALL                                                                            | HOST                |

| <4>        | MODULE                                                                         | MODULE              |

| <5>        | ALL                                                                            | FACTORY             |

| <6>        | NEVER                                                                          | HOST                |

| <7>        | NEVER                                                                          | MODULE              |

#### **Register Map** Table 11. Permission Table

25

**DS1862**

| N  |

|----|

| 0  |

| 00 |

|    |

| S  |

|    |

|         |                             |                    |                   | L                                   | OWEF              |                            | RY (00h     | –7Fh)            |                    |                           |                      |       |                                         |                    |                                       |                           |

|---------|-----------------------------|--------------------|-------------------|-------------------------------------|-------------------|----------------------------|-------------|------------------|--------------------|---------------------------|----------------------|-------|-----------------------------------------|--------------------|---------------------------------------|---------------------------|

| ADDRESS | WO                          | RD 0               |                   |                                     | WOF               | RD 1                       |             |                  | W                  | ORD 2                     |                      |       |                                         | WOR                | D 3                                   |                           |

| (hex)   | BYTE 0/8                    | BYTE               | 1/9               | BYTE                                | 2/A               | BYT                        | E 3/B       | BY               | FE 4/C             | B                         | /TE 5/D              |       | BYTE                                    | 6/E                | BYTE                                  | 5 7/F                     |

| 00<0,2> | USER EE                     | Signal C           | Cond*             | Te                                  | emp A             | larm Hi                    |             |                  | Temp               | Alarm                     | Lo                   |       | Т                                       | emp W              | arn Hi                                |                           |

| 08<2>   | Temp \                      | Varn Lo            |                   | Vc                                  | <sub>C3</sub> Ala | ırm Hi**                   |             |                  | V <sub>CC3</sub> A | larm L                    | _0**                 |       | V                                       | <sub>CC3</sub> Wa  | rn Hi**                               |                           |

| 10<2>   | V <sub>CC3</sub> W          | arn Lo**           |                   | E                                   | ias Al            | arm Hi                     |             |                  | Bias               | Alarm                     | Lo                   |       | E                                       | Bias Wa            | arn Hi                                |                           |

| 18<2>   | Bias V                      | /arn Lo            |                   | Т                                   | X-P AI            | arm Hi                     |             |                  | TX-P               | Alarm                     | Lo                   |       | -                                       | TX-P Wa            | arn Hi                                |                           |

| 20<2>   | TX-P V                      | /arn Lo            |                   | F                                   | X-P AI            | arm Hi                     |             |                  | RX-P               | Alarm                     | Lo                   |       | F                                       | RX-P W             | arn Hi                                |                           |

| 28<2>   | RX-P V                      | Varn Lo            |                   | A                                   | UX1 A             | larm Hi                    |             |                  | AUX1               | Alarm                     | Lo                   |       | A                                       | UX1 W              | arn Hi                                |                           |

| 30<2>   | AUX1 \                      | Varn Lo            |                   | A                                   | UX2 A             | larm Hi                    |             |                  | AUX2               | Alarm                     | Lo                   |       | Α                                       | UX2 W              | arn Hi                                |                           |

| 38<0,2> | AUX2 \                      | Varn Lo            |                   | USER E                              | E                 | USEF                       | REE         | Res              | served             | Re                        | eserved              |       | Reserv                                  | /ed                | Rese                                  | rved                      |

| 40<1>   | Reserved                    | Reser              | ved               | Reserv                              | ed                | Rese                       | rved        | Res              | served             | Re                        | eserved              | ι     | JSER SI                                 | RAM                | USER                                  | SRAM                      |

| 48<1>   | USER SRAM                   | USER S             | RAM               | USER SF                             | AM                | USER S                     | SRAM        | USEF             | R SRAM             | USE                       | R SRAM               | ι     | JSER SI                                 | RAM                | USER                                  | SRAM                      |

| 50<1>   | Temp/Res/Bias/<br>TxP Alarm | RxP/AUX1<br>Res Al |                   | Temp/Res,<br>TxP Wa                 |                   | RxP/A<br>AUX2/R€           |             | · ·              | x Misc<br>ags      |                           | od/Tec/<br>/Res Flag |       | /CC5/3/2<br>\larm F                     |                    | V <sub>CC5/3</sub><br>Warn            |                           |

| 58<1>   | Temp/Res/Bias/<br>TxP Mask  | RxP/AUX1<br>Res M  |                   | Temp/Res,<br>TxP Ma                 |                   | RxP/AUX1/<br>AUX2/Res Mask |             |                  |                    | Apd/Tec/Wave/<br>Res Mask |                      |       | V <sub>CC5/3/2/</sub> Vee<br>Alarm Mask |                    | V <sub>CC5/3/2</sub> /Ve<br>Warn Masł |                           |

| 60<1>   | Temp                        | Value              |                   | V                                   | CC2/3 V           | /alue**                    |             |                  | Bias               | s Value                   | Э                    |       |                                         | TX-P V             | alue                                  |                           |

| 68<1>   | RX-P                        | Value              |                   |                                     | AUX1              | Value                      |             |                  | AUX                | 2 Valu                    | е                    |       | GCS                                     | 1                  | GC                                    | S0                        |

| 70<0,1> | Reserved                    | Reser              | ved               | Reserv                              | ved               | Rese                       | erved       | F                | POA                | Re                        | eserved              |       | PEC_E                                   | EN                 | Host                                  | PW                        |

| 78<0,1> | Host PW                     | Host I             | PW                | Host F                              |                   |                            | PWE (       |                  |                    |                           | PW                   | E (LS | B)                                      | Table S            |                                       | Select                    |

|         |                             |                    |                   |                                     | EX                | PANDED                     | BYTE        | S                |                    |                           |                      |       |                                         |                    |                                       |                           |

| BYTE    | BYTE/WORD                   | Bit                |                   | Bit6*                               | _                 | Bit5                       | Bi          |                  | Bit                |                           | Bit2                 |       | -                                       | it1                |                                       | it0                       |

| (hex)   | NAME                        | -                  | bit <sub>14</sub> | bit <sub>13</sub> bit <sub>12</sub> |                   | -                          | bit9        | bit <sub>8</sub> | bit <sub>7</sub>   | bit <sub>6</sub>          |                      | bit4  | bit <sub>3</sub>                        | bit <sub>2</sub>   | bit <sub>1</sub>                      | bit <sub>0</sub>          |

| 01      | Signal Cond<1>*             | USEF               | REE               | USER EE                             | US                | SER EE                     | USEF        | REE              | USEF               | REE                       | EN2 Va               | lue   | EN1                                     | Value              | Lock-                                 | T1-221                    |