# FemtoClock<sup>®</sup> NG Universal Frequency Translator

# ICS849N212I

## DATA SHEET

## **General Description**

The ICS849N212I is a highly flexible FemtoClock® NG general purpose, low phase noise Frequency Translator / Synthesizer with alarm and monitoring functions suitable for networking and communications applications. It is able to generate any output frequency in the 1MHz - 250MHz range (see Table 3 for details). A wide range of input reference clocks and a range of low-cost fundamental mode crystal frequencies may be used as the source for the output frequency.

The ICS849N212I has three operating modes to support a very broad spectrum of applications:

- 1) Frequency Synthesizer

- Synthesizes output frequencies from a 16MHz 40MHz fundamental mode crystal.

- Fractional feedback division is used, so there are no requirements for any specific crystal frequency to produce the desired output frequency with a high degree of accuracy.

- 2) High-Bandwidth Frequency Translator

- Applications: PCI Express, Computing, General Purpose

- Translates any input clock in the 16MHz 710MHz frequency range into any supported output frequency.

- This mode has a high PLL loop bandwidth in order to track input reference changes, such as Spread-Spectrum Clock modulation, so it will not attenuate much jitter on the input reference.

- 3) Low-Bandwidth Frequency Translator

- Applications: Networking & Communications.

- Translates any input clock in the 8kHz 710MHz frequency range into any supported output frequency.

- This mode supports PLL loop bandwidths in the 10Hz 580Hz range and makes use of an external crystal to provide significant jitter attenuation.

This device provides two factory-programmed default power-up configurations burned into One-Time Programmable (OTP) memory. The configuration to be used is selected by the CONFIG pin. The two configurations are specified by the customer and are programmed by IDT during the final test phase from an on-hand stock of blank devices. The two configurations may be completely independent of one another.

One usage example might be to install the device on a line card with two optional daughter cards: an OC-3 option (configuration 0) requiring a 155.52MHz LVDS clock translated from a 19.44MHz input and a Gigabit Ethernet option (configuration 1) requiring a 125MHz LVPECL clock translated from the same 19.44MHz input reference.

To implement other configurations, these power-up default settings can be overwritten after power-up using the l<sup>2</sup>C interface and the device can be completely reconfigured. However, these settings would have to be re-written each time the device powers-up.

### Features

- Fourth generation FemtoClock® NG technology

- Universal Frequency Translator/Frequency Synthesizer

- Two outputs

- One programmable as LVPECL or LVDS

- One LVCMOS

- Both outputs may be set to use 2.5V or 3.3V output levels

- Programmable output frequency: 1.0MHz to 250MHz

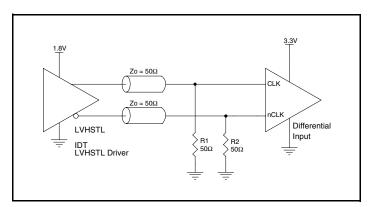

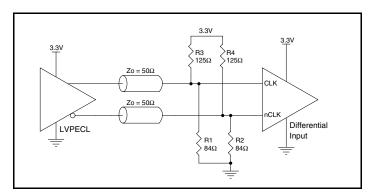

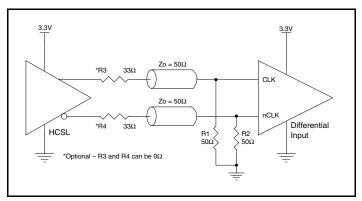

- Two differential inputs support the following input types: LVPECL, LVDS, LVHSTL, HCSL

- Input frequency range: 8kHz 710MHz

- Crystal input frequency range: 16MHz 40MHz

- Two factory-set register configurations for power-up default state

- Power-up default configuration pin or register selectable

- Configurations customized via One-Time Programmable ROM

- Settings may be overwritten after power-up via I<sup>2</sup>C

- I<sup>2</sup>C Serial interface for register programming

- RMS phase jitter at 125MHz, using a 40MHz crystal (12kHz - 20MHz): 558fs (typical), Low Bandwidth Mode (FracN)

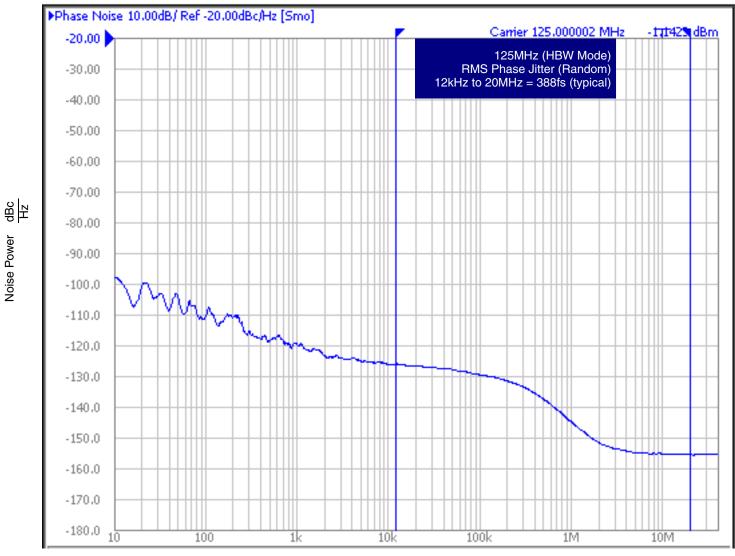

- RMS phase jitter at 125MHz, using a 100MHz input clock (12kHz - 20MHz): 388fs (typical), High Bandwidth Mode (Integer FB)

- Output supply voltage modes: V<sub>CC</sub>/V<sub>CCA</sub>/V<sub>CCO</sub> 3.3V/3.3V/3.3V

3.3V/3.3V/2.5V (LVPECL only) 2.5V/2.5V/2.5V

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

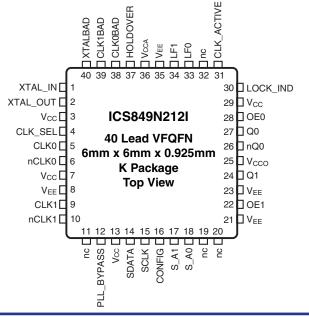

## **Pin Assignment**

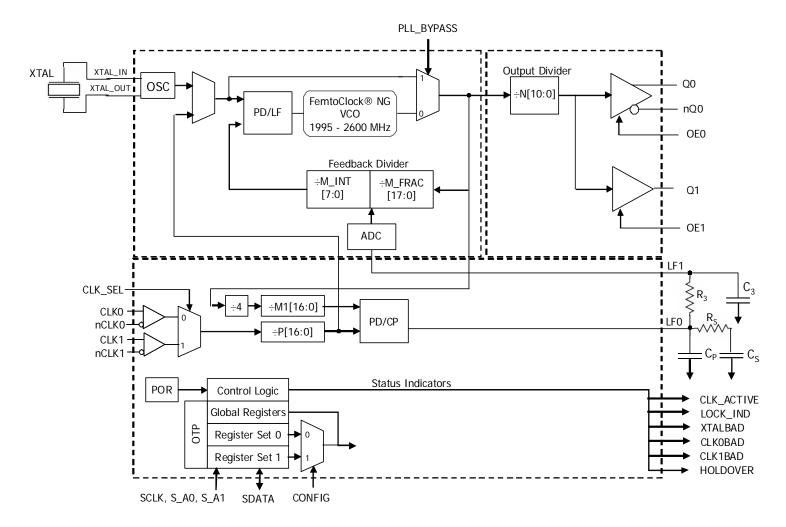

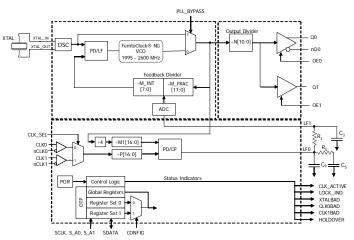

## **Complete Block Diagram**

# Table 1. Pin Descriptions

| Number            | Name                | Т      | уре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

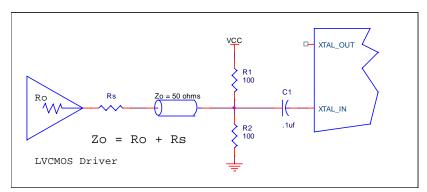

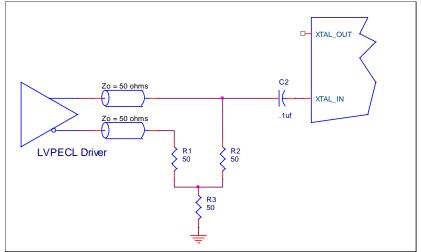

| 1<br>2            | XTAL_IN<br>XTAL_OUT | Input  |                     | Crystal oscillator interface designed for 12pF parallel resonant crystals.<br>XTAL_IN (pin 1) is the input and XTAL_OUT (pin 2) is the output.                                                                                                                                                                                                                                                                                                      |

| 3, 7, 13, 29      | V <sub>CC</sub>     | Power  |                     | Core supply pins. All must be either 3.3V or 2.5V.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4                 | CLK_SEL             | Input  | Pulldown            | Input clock select. Selects the active differential clock input. LVCMOS/LVTTL<br>Interface Levels.<br>0 = CLK0, nCLK0 (default)<br>1 = CLK1, nCLK1                                                                                                                                                                                                                                                                                                  |

| 5                 | CLK0                | Input  | Pulldown            | Non-inverting differential clock input.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6                 | nCLK0               | Input  | Pullup/<br>Pulldown | Inverting differential clock input. $V_{CC}/2$ default when left floating (set by the internal pullup and pulldown resistors).                                                                                                                                                                                                                                                                                                                      |

| 8, 21, 23, 35     | V <sub>EE</sub>     | Power  |                     | Negative supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9                 | CLK1                | Input  | Pulldown            | Non-inverting differential clock input.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10                | nCLK1               | Input  | Pullup/<br>Pulldown | Inverting differential clock input. $V_{CC}/2$ default when left floating (set by the internal pullup and pulldown resistors).                                                                                                                                                                                                                                                                                                                      |

| 11, 19,<br>20, 32 | nc                  | Unused |                     | No connect. These pins are to be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12                | PLL_BYPASS          | Input  | Pulldown            | Bypasses the VCXO PLL. In Bypass mode, outputs are clocked off the falling<br>edge of the input reference. LVCMOS/LVTTL Interface Levels.<br>0 = PLL mode (default)<br>1 = PLL Bypassed                                                                                                                                                                                                                                                             |

| 14                | SDATA               | I/O    | Pullup              | I <sup>2</sup> C Data Input/Output. Open drain.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                | SCLK                | Input  | Pullup              | I <sup>2</sup> C Clock Input. LVCMOS/LVTTL Interface Levels.                                                                                                                                                                                                                                                                                                                                                                                        |

| 16                | CONFIG              | Input  | Pulldown            | Configuration Pin. Selects between one of two factory programmable pre-set<br>power-up default configurations. The two configurations can have different<br>output/input frequency translation ratios, different PLL loop bandwidths, etc.<br>These default configurations can be overwritten after power-up via l <sup>2</sup> C if the<br>user so desires. LVCMOS/LVTTL Interface Levels.<br>0 = Configuration 0 (default)<br>1 = Configuration 1 |

| 17                | S_A1                | Input  | Pulldown            | I <sup>2</sup> C Address Bit 1. LVCMOS/LVTTL Interface Levels.                                                                                                                                                                                                                                                                                                                                                                                      |

| 18                | S_A0                | Input  | Pulldown            | I <sup>2</sup> C Address Bit 0. LVCMOS/LVTTL Interface Levels.                                                                                                                                                                                                                                                                                                                                                                                      |

| 22                | OE1                 | Input  | Pullup              | Active High Output Enable for Q1, nQ1. LVCMOS/LVTTL Interface Levels.<br>0 = Output pins high-impedance<br>1 = Output switching (default)                                                                                                                                                                                                                                                                                                           |

| 24                | Q1                  | Output |                     | Single-ended clock output. LVCMOS/LVTTL Interface Levels.                                                                                                                                                                                                                                                                                                                                                                                           |

| 25                | V <sub>CCO</sub>    | Power  |                     | Output supply pin for differential Q0, nQ0 and single-ended Q1 outputs.<br>Either 2.5V or 3.3V.                                                                                                                                                                                                                                                                                                                                                     |

| 26, 27            | nQ0, Q0             | Output |                     | Differential output pair. Output type is programmable to LVDS or LVPECL interface levels.                                                                                                                                                                                                                                                                                                                                                           |

| 28                | OE0                 | Input  | Pullup              | Active High Output Enable for Q0, nQ0. LVCMOS/LVTTL Interface Levels.<br>0 = Output pins high-impedance<br>1 = Output switching (default)                                                                                                                                                                                                                                                                                                           |

| 30                | LOCK_IND            | Output |                     | Lock Indicator - indicates that the PLL is in a locked condition. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                                                                                                                                                                    |

| 31                | CLK_ACTIVE          | Output |                     | Indicates which of the two differential clock inputs is currently selected.<br>LVCMOS/LVTTL Interface Levels.<br>0 - CLK0/nCLK0 differential input pair<br>1 - CLK1/nCLK1 differential input pair                                                                                                                                                                                                                                                   |

| Number | Name             | Туре          | Description                                                                                                                                                                                            |

|--------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33, 34 | LF0, LF1         | Analog<br>I/O | Loop filter connection node pins. LF0 is the output. LF1 is the input.                                                                                                                                 |

| 36     | V <sub>CCA</sub> | Power         | Analog supply voltage. See Applications section for details on how to connect this pin.                                                                                                                |

| 37     | HOLDOVER         | Output        | Alarm output reflecting if the device is in a holdover state. LVCMOS/LVTTL interface levels.<br>0 = Device is locked to a valid input reference<br>1 = Device is not locked to a valid input reference |

| 38     | CLK0BAD          | Output        | Alarm output reflecting the state of CLK0. LVCMOS/LVTTL interface levels.<br>0 = Input Clock 0 is switching within specifications<br>1 = Input Clock 0 is out of specification                         |

| 39     | CLK1BAD          | Output        | Alarm output reflecting the state of CLK1. LVCMOS/LVTTL interface levels.<br>0 = Input Clock 1 is switching within specifications<br>1 = Input Clock 1 is out of specification                         |

| 40     | XTALBAD          | Output        | Alarm output reflecting the state of XTAL. LVCMOS/LVTTL interface levels.<br>0 = crystal is switching within specifications<br>1 = crystal is out of specification                                     |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter           |                                                                 | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|---------------------|-----------------------------------------------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitar     | nce                                                             |                 |         | 4       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Re     | esistor                                                         |                 |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown      | Resistor                                                        |                 |         | 51      |         | kΩ    |

|                       |                     | Q1                                                              |                 |         | 15      |         | Ω     |

| R <sub>OUT</sub>      | Output<br>Impedance | CLK_ACTIVE, HOLDOVER,<br>XTALBAD, CLK0BAD,<br>CLK1BAD, LOCK_IND |                 |         | 25      |         | Ω     |

## **Functional Description**

The ICS849N212I is designed to provide two copies of almost any desired output frequency within its operating range (0.98 - 250MHz) from any input source in the operating range (8kHz - 710MHz). It is capable of synthesizing frequencies from a crystal or crystal oscillator source. The output frequency is generated regardless of the relationship to the input frequency. The output frequency will be exactly the required frequency in most cases. In most others, it will only differ from the desired frequency by a few ppb. IDT configuration software will indicate the frequency error, if any. The ICS849N212I can translate the desired output frequency from one of two input clocks. Again, no relationship is required between the input and output frequencies in order to translate to the output clock rate. In this frequency translation mode, a low-bandwidth, jitter attenuation option is available that makes use of an external fixed-frequency crystal or crystal oscillator to translate from a noisy input source. If the input clock is known to be fairly clean or if some modulation on the input needs to be tracked, then the high-bandwidth frequency translation mode can be used, without the need for the external crystal.

The input clock references and crystal input are monitored continuously and appropriate alarm outputs are raised both as register bits and hard-wired pins in the event of any out-of-specification conditions arising. Clock switching is supported in manual, revertive & non-revertive modes.

The ICS849N212I has two factory-programmed configurations that may be chosen from as the default operating state after reset. This is intended to allow the same device to be used in two different applications without any need for access to the I<sup>2</sup>C registers. These defaults may be over-written by I<sup>2</sup>C register access at any time, but those over-written settings will be lost on power-down. Please contact IDT if a specific set of power-up default settings is desired.

## **Configuration Selection**

The ICS849N212I comes with two factory-programmed default configurations. When the device comes out of power-up reset the selected configuration is loaded into operating registers. The ICS849N212I uses the state of the CONFIG pin or CONFIG register bit (controlled by the CFG\_PIN\_REG bit) to determine which configuration is active. When the output frequency is changed either via the CONFIG pin or via internal registers, the output behavior may not be predictable during the register writing and output settling periods. Devices sensitive to glitches or runt pulses may have to be reset once reconfiguration is complete.

Once the device is out of reset, the contents of the operating registers can be modified by write access from the I<sup>2</sup>C serial port. Users that have a custom configuration programmed may not require I<sup>2</sup>C access.

It is expected that the ICS849N212I will be used almost exclusively in a mode where the selected configuration will be used from device power-up without any changes during operation. For example, the device may be designed into a communications line card that supports different I/O modules such as a standard OC-3 module running at 155.52MHz or a (255/237) FEC rate OC-3 module running at 167.332MHz. The different I/O modules would result in a different level on the CONFIG pin which would select different divider ratios within the ICS849N212I for the two different card configurations. Access via I<sup>2</sup>C would not be necessary for operation using either of the internal configurations.

## **Operating Modes**

The ICS849N212I has three operating modes which are set by the MODE\_SEL[1:0] bits. There are two frequency translator modes - low bandwidth and high bandwidth and a frequency synthesizer mode. The device will operate in the same mode regardless of which configuration is active.

Please make use of IDT-provided configuration applications to determine the best operating settings for the desired configurations of the device.

### **Output Dividers & Supported Output Frequencies**

In all 3 operating modes, the output stage behaves the same way, but different operating frequencies can be specified in the two configurations.

The internal VCO is capable of operating in a range anywhere from 1.995GHz - 2.6GHz. It is necessary to choose an integer multiplier of the desired output frequency that results in a VCO operating frequency within that range. The output divider stage N[10:0] is limited to selection of even integers from 10 to 2046. Please refer to Table 3 for the values of N applicable to the desired output frequency.

| Table 3. Output Divider | r Settings & Frequency Ranges |  |

|-------------------------|-------------------------------|--|

|-------------------------|-------------------------------|--|

| Register<br>Setting        | Frequency<br>Divider | Minimum<br><sup>f</sup> ouт | Maximum<br><sup>f</sup> о∪т |

|----------------------------|----------------------|-----------------------------|-----------------------------|

| Nn[10:0]                   | N                    | (MHz)                       | (MHz)                       |

| 0000000000 -<br>000000100x | 2 - 8                | Not Su                      | upported                    |

| 000000101x                 | 10                   | 199.5                       | 260 (Note 1)                |

| 000000110x                 | 12                   | 166.3                       | 216.7                       |

| 000000111x                 | 14                   | 142.5                       | 185.7                       |

| 000001000x                 | 16                   | 124.7                       | 162.5                       |

| 000001001x                 | 18                   | 110.8                       | 144.4                       |

|                            | Even N               | 1995 / N                    | 2600 / N                    |

| 11111111111                | 2046                 | 0.98                        | 1.27                        |

Note 1: using a divider setting of N=0x00A or 0x00B with a high VCO frequency can result in the CMOS output running faster than its 250MHz maximum operating frequency.

#### **Frequency Synthesizer Mode**

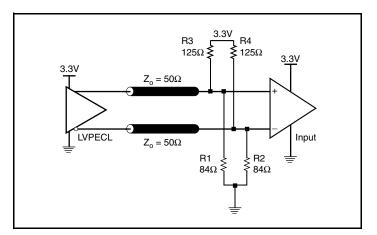

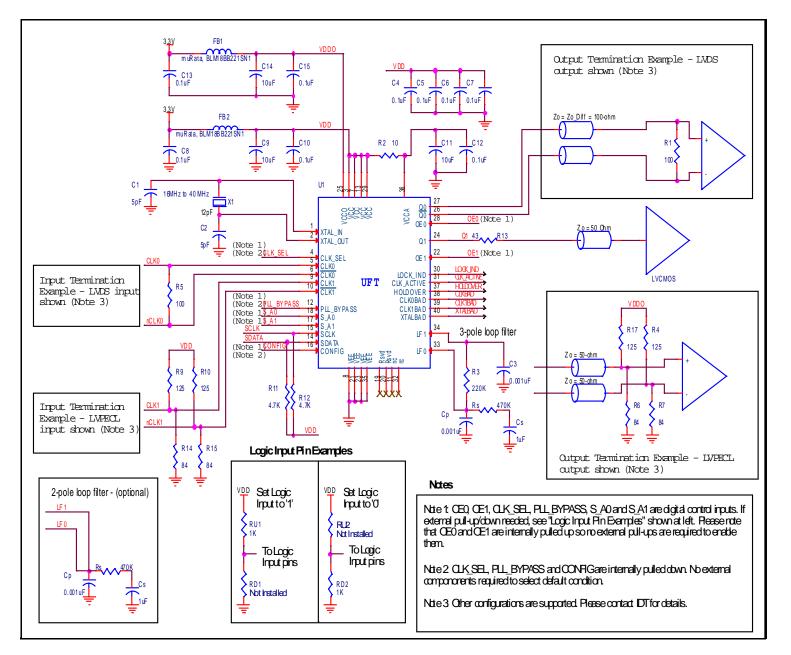

This mode of operation allows an arbitrary output frequency to be generated from a fundamental mode crystal input. As can be seen from the block diagram in Figure 1, only the upper feedback loop is used in this mode of operation.

The upper feedback loop supports a delta-sigma fractional feedback divider. This allows the VCO operating frequency to be a non-integer multiple of the crystal frequency. By using an integer multiple only, lower phase noise jitter on the output can be achieved, however the use of the delta-sigma divider logic will provide excellent performance on the output if a fractional divisor is used.

Figure 1. Frequency Synthesizer Mode Block Diagram

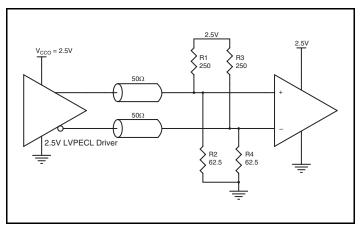

### **High-Bandwidth Frequency Translator Mode**

This mode of operation is used to translate one of two input clocks of the same nominal frequency into an output frequency with little jitter attenuation. As can be seen from the block diagram in *Figure 2*, similarly to the Frequency Synthesizer mode, only the upper feedback loop is used.

# Figure 2. High Bandwidth Frequency Translator Mode Block Diagram

The input reference frequency range is now extended up to 710MHz. A pre-divider stage P is needed to keep the operating frequencies at the phase detector within limits.

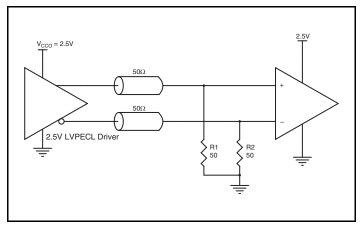

### Low-Bandwidth Frequency Translator Mode

As can seen from the block diagram in *Figure 3*, this mode involves two PLL loops. The lower loop with the large integer dividers is the low bandwidth loop and it sets the output-to-input frequency translation ratio. This loop drives the upper DCXO loop (digitally controlled crystal oscillator) via an analog-digital converter.

# Figure 3. Low Bandwidth Frequency Translator Mode Block Diagram

The phase detector of the lower loop is designed to work with frequencies in the 8kHz - 16kHz range. The pre-divider stage is used to scale down the input frequency by an integer value to achieve a frequency in this range. By dividing down the fed-back VCO operating frequency by the integer divider M1[18:0] to as close as possible to the same frequency, very accurate output frequency translations can be achieved.

## **Alarm Conditions & Status Bits**

The ICS849N212I monitors a number of conditions and reports their status via both output pins and register bits. All alarms will behave as indicated below in all modes of operation, but some of the conditions monitored have no valid meaning in some operating modes. For example, the status of CLK0BAD, CLK1BAD and CLK\_ACTIVE are not relevant in Frequency Synthesizer mode. The outputs will still be active and it is left to the user to determine which to monitor and how to respond to them based on the known operating mode.

CLK\_ACTIVE - indicates which input clock reference is being used to derive the output frequency.

LOCK\_IND - This status is asserted on the pin & register bit when the PLL is locked to the appropriate input reference for the chosen mode of operation. The status bit will not assert until frequency lock has been achieved, but will de-assert once lock is lost.

XTALBAD - indicates if valid edges are being received on the crystal input. Detection is performed by comparing the input to the feedback signal at the upper loop's Phase / Frequency Detector (PFD). If three edges are received on the feedback without an edge on the crystal input, the XTALBAD alarm is asserted on the pin & register bit. Once an edge is detected on the crystal input, the alarm is immediately deasserted. CLK0BAD - indicates if valid edges are being received on the CLK0 reference input. Detection is performed by comparing the input to the feedback signal at the appropriate Phase / Frequency Detector (PFD). When operating in high-bandwidth mode, the feedback at the upper PFD is used. In low-bandwidth mode, the feedback at the lower PFD is used. If three edges are received on the feedback without an edge on the divided down (÷P) CLK0 reference input, the CLK0BAD alarm is asserted on the pin & register bit. Once an edge is detected on the CLK0 reference input, the alarm is deasserted.

CLK1BAD - indicates if valid edges are being received on the CLK1 reference input. Behavior is as indicated for the CLK0BAD alarm, but with the CLK1 input being monitored and the CLK1BAD output pin & register bits being affected.

HOLDOVER - indicates that the device is not locked to a valid input reference clock. This can occur in Manual switchover mode if the selected reference input has gone bad, even if the other reference input is still good. In automatic mode, this will only assert if both input references are bad.

## Input Reference Selection and Switching

When operating in Frequency Synthesizer mode, the CLK0 and CLK1 inputs are not used and the contents of this section do not apply. Except as noted below, when operating in either High or Low Bandwidth Frequency Translator mode, the contents of this section apply equally when in either of those modes.

Both input references CLK0 and CLK1 must be the same nominal frequency. These may be driven by any type of clock source, including crystal oscillator modules. A difference in frequency may cause the PLL to lose lock when switching between input references. Please contact IDT for the exact limits for your situation.

The global control bits AUTO\_MAN[1:0] dictate the order of priority and switching mode to be used between the CLK0 and CLK1 inputs.

### Manual Switching Mode

When the AUTO\_MAN[1:0] field is set to Manual via Pin, then the ICS849N212I will use the CLK\_SEL input pin to determine which input to use as a reference. Similarly, if set to Manual via Register, then the device will use the CLK\_SEL register bit to determine the input reference. In either case, the PLL will lock to the selected reference if there is a valid clock present on that input.

If there is not a valid clock present on the selected input, the ICS849N212I will go into holdover (Low Bandwidth Frequency Translator mode) or free-run (High Bandwidth Frequency Translator mode) state. In either case, the HOLDOVER alarm will be raised. This will occur even if there is a valid clock on the non-selected reference input.

The device will recover from holdover / free-run state once a valid clock is re-established on the selected reference input.

The ICS849N212I will only switch input references on command from the user. The user must either change the CLK\_SEL register bit (if in Manual via Register) or CLK\_SEL input pin (if in Manual via Pin).

### Automatic Switching Mode

When the AUTO\_MAN[1:0] field is set to either of the automatic selection modes (Revertive or Non-Revertive), the ICS849N212I determines which input reference it prefers / starts from by the state of the CLK\_SEL register bit only. The CLK\_SEL input pin is not used in either Automatic switching mode.

When starting from an unlocked condition, the device will lock to the input reference indicated by the CLK\_SEL register bit. It will not pay attention to the non-selected input reference until a locked state has been achieved. This is necessary to prevent 'hunting' behavior during the locking phase.

Once the ICS849N212I has achieved a stable lock, it will remain locked to the preferred input reference as long as there is a valid clock on it. If at some point, that clock fails, then the device will automatically switch to the other input reference as long as there is a valid clock there. If there is not a valid clock on either input reference, the ICS849N212I will go into holdover (Low Bandwidth Frequency Translator mode) or free-run (High Bandwidth Frequency Translator mode) state. In either case, the HOLDOVER alarm will be raised.

The device will recover from holdover / free-run state once a valid clock is re-established on either reference input. If clocks are valid on both input references, the device will choose the reference indicated by the CLK\_SEL register bit.

If running from the non-preferred input reference and a valid clock returns, there is a difference in behavior between Revertive and Non-revertive modes. In Revertive mode, the device will switch back to the reference indicated by the CLK\_SEL register bit even if there is still a valid clock on the non-preferred reference input. In Non-revertive mode, the ICS849N212I will not switch back as long as the non-preferred input reference still has a valid clock on it.

### Switchover Behavior of the PLL

Even though the two input references have the same nominal frequency, there may be minor differences in frequency and potentially large differences in phase between them. The ICS849N212I will adjust its output to the new input reference. It will use Phase Slope Limiting to adjust the output phase at a fixed maximum rate until the output phase and frequency are now aligned to the new input reference. Phase will always be adjusted by extending the clock period of the output so that no unacceptably short clock periods are generated on the output ICS849N212I.

### Holdover / Free-run Behavior

When both input references have failed (Automatic mode) or the selected input has failed (Manual mode), the ICS849N212I will enter holdover (Low Bandwidth Frequency Translator mode) or free-run (High Bandwidth Frequency Translator mode) state. In both cases, once both input references are lost, the PLL will stop making adjustments to the output phase.

If operating in Low Bandwidth Frequency Translation mode, the PLL will continue to reference itself to the local oscillator and will hold its output phase and frequency in relation to that source. Output stability is determined by the stability of the local oscillator in this case.

However, if operating in High Bandwidth Frequency Translation mode, the PLL no longer has any frequency reference to use and output stability is now determined by the stability of the internal VCO.

If the device is programmed to perform Manual switching, once the selected input reference recovers, the ICS849N212I will switch back to that input reference. If programmed for either Automatic mode, the device will switch back to whichever input reference has a valid clock first.

The switchover that results from returning from holdover or free-run is handled in the same way as a switch between two valid input references as described in the previous section.

### **Output Configuration**

The two outputs of the ICS849N212I both provide the same clock frequency. Both must operate from the same output voltage level of 3.3V or 2.5V, although this output voltage may be less than or equal to the core voltage (3.3V or 2.5V) the rest of the device is operating from. The output voltage level used on the two outputs is supplied on the V<sub>CCO</sub> pin.

The Q0 output is selectable as LVDS or LVPECL output type via the Q0\_TYPEm register bits. This selection bit is provided in each configuration to allow different output type settings under each configuration.

The Q1 output is always an LVCMOS output.

The two outputs can be enabled individually also via both register control bits and input pins. When both the OEn register bit and OEn

### Table 4A. I<sup>2</sup>C Device Slave Address

Table 4B. Block Write Operation

| 1 1 0 | 0 1 | 1 | S_A1 | S_A0 | R/W |

|-------|-----|---|------|------|-----|

|-------|-----|---|------|------|-----|

pin are enabled, then the appropriate output is enabled. The OEn register bits default to enabled so that by default the outputs can be directly controlled by the input pins. Similarly, the input pins are provisioned with weak pull-ups so that if they are left unconnected, the output state can be directly controlled by the register bits. When the differential output is in the disabled state, it will show a high impedance condition.

### **Serial Interface Configuration Description**

The ICS849N212I has an I<sup>2</sup>C-compatible configuration interface to access any of the internal registers (Table 4D) for frequency and PLL parameter programming. The ICS849N212I acts as a slave device on the I<sup>2</sup>C bus and has the address 0b11011xx, where xx is set by the values on the S\_A0 & S\_A1 pins (see Table 4A for details). The interface accepts byte-oriented block write and block read operations. An address byte (P) specifies the register address (Table 4D) as the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first, see table 4B, 4C). Read and write block transfers can be stopped after any complete byte transfer. It is recommended to terminate I<sup>2</sup>C the read or write transfer after accessing byte #23.

For full electrical l<sup>2</sup>C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-up resistors have a size of  $50k\Omega$  typical.

Note: if a different device slave address is desired, please contact IDT.

| Bit           | 1     | 2:8              | 9     | 10  | 11:18               | 19  | 20:27            | 28  | 29-36              | 37  |               |  |

|---------------|-------|------------------|-------|-----|---------------------|-----|------------------|-----|--------------------|-----|---------------|--|

| Description   | START | Slave<br>Address | W (0) | ACK | Address<br>Byte (P) | ACK | Data Byte<br>(P) | ACK | Data Byte<br>(P+1) | ACK | Data Byte<br> |  |

| Length (bits) | 1     | 7                | 1     | 1   | 8                   | 1   | 8                | 1   | 8                  | 1   | 8             |  |

### Table 4C. Block Read Operation

| Bit          | 1     | 2:8              | 9        | 10    | 11:18               | 19          | 20                | 21:27            | 28       | 29          | 30:37            | 38          | 39-46              | 47          |               |             |      |

|--------------|-------|------------------|----------|-------|---------------------|-------------|-------------------|------------------|----------|-------------|------------------|-------------|--------------------|-------------|---------------|-------------|------|

| Description  | START | Slave<br>Address | W<br>(0) | A C K | Address<br>Byte (P) | A<br>C<br>K | Repeated<br>START | Slave<br>Address | R<br>(1) | A<br>C<br>K | Data Byte<br>(P) | A<br>C<br>K | Data Byte<br>(P+1) | A<br>C<br>K | Data Byte<br> | A<br>C<br>K | STOP |

| Length (bits | 1     | 7                | 1        | 1     | 8                   | 1           | 1                 | 7                | 1        | 1           | 8                | 1           | 8                  | 1           | 8             | 1           | 1    |

...

STOP

1

ACK

## **Register Descriptions**

Please consult IDT for configuration software and/or programming guides to assist in selection of optimal register settings for the desired configurations.

### Table 4D. I<sup>2</sup>C Register Map

| Regi | Binary              |             |             |             | Register    | Bit         |             |            |            |

|------|---------------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|

| ster | Register<br>Address | D7          | D6          | D5          | D4          | D3          | D2          | D1         | D0         |

| 0    | 00000               | MFRAC0[17]  | MFRAC0[16]  | MFRAC0[15]  | MFRAC0[14]  | MFRAC0[13]  | MFRAC0[12]  | MFRAC0[11] | MFRAC0[10] |

| 1    | 00001               | MFRAC1[17]  | MFRAC1[16]  | MFRAC1[15]  | MFRAC1[14]  | MFRAC1[13]  | MFRAC1[12]  | MFRAC1[11] | MFRAC1[10] |

| 2    | 00010               | MFRAC0[9]   | MFRAC0[8]   | MFRAC0[7]   | MFRAC0[6]   | MFRAC0[5]   | MFRAC0[4]   | MFRAC0[3]  | MFRAC0[2]  |

| 3    | 00011               | MFRAC1[9]   | MFRAC1[8]   | MFRAC1[7]   | MFRAC1[6]   | MFRAC1[5]   | MFRAC1[4]   | MFRAC1[3]  | MFRAC1[2]  |

| 4    | 00100               | MFRAC0[1]   | MFRAC0[0]   | MINT0[7]    | MINT0[6]    | MINT0[5]    | MINT0[4]    | MINT0[3]   | MINT0[2]   |

| 5    | 00101               | MFRAC1[1]   | MFRAC1[0]   | MINT1[7]    | MINT1[6]    | MINT1[5]    | MINT1[4]    | MINT1[3]   | MINT1[2]   |

| 6    | 00110               | MINT0[1]    | MINT0[0]    | P0[16]      | P0[15]      | P0[14]      | P0[13]      | P0[12]     | P0[11]     |

| 7    | 00111               | MINT1[1]    | MINT1[0]    | P1[16]      | P1[15]      | P1[14]      | P1[13]      | P1[12]     | P1[11]     |

| 8    | 01000               | P0[10]      | P0[9]       | P0[8]       | P0[7]       | P0[6]       | P0[5]       | P0[4]      | P0[3]      |

| 9    | 01001               | P1[10]      | P1[9]       | P1[8]       | P1[7]       | P1[6]       | P1[5]       | P1[4]      | P1[3]      |

| 10   | 01010               | P0[2]       | P0[1]       | P0[0]       | M1_0[16]    | M1_0[15]    | M1_0[14]    | M1_0[13]   | M1_0[12]   |

| 11   | 01011               | P1[2]       | P1[1]       | P1[0]       | M1_1[16]    | M1_1[15]    | M1_1[14]    | M1_1[13]   | M1_1[12]   |

| 12   | 01100               | M1_0[11]    | M1_0[10]    | M1_0[9]     | M1_0[8]     | M1_0[7]     | M1_0[6]     | M1_0[5]    | M1_0[4]    |

| 13   | 01101               | M1_1[11]    | M1_1[10]    | M1_1[9]     | M1_1[8]     | M1_1[7]     | M1_1[6]     | M1_1[5]    | M1_1[4]    |

| 14   | 01110               | M1_0[3]     | M1_0[2]     | M1_0[1]     | M1_0[0]     | N0[10]      | N0[9]       | N0[8]      | N0[7]      |

| 15   | 01111               | M1_1[3]     | M1_1[2]     | M1_1[1]     | M1_1[0]     | N1[10]      | N1[9]       | N1[8]      | N1[7]      |

| 16   | 10000               | N0[6]       | N0[5]       | N0[4]       | N0[3]       | N0[2]       | N0[1]       | N0[0]      | BW0[6]     |

| 17   | 10001               | N1[6]       | N1[5]       | N1[4]       | N1[3]       | N1[2]       | N1[1]       | N1[0]      | BW1[6]     |

| 18   | 10010               | BW0[5]      | BW0[4]      | BW0[3]      | BW0[2]      | BW0[1]      | BW0[0]      | Rsvd       | Q0_TYPE0   |

| 19   | 10011               | BW1[5]      | BW1[4]      | BW1[3]      | BW1[2]      | BW1[1]      | BW1[0]      | Rsvd       | Q0_TYPE1   |

| 20   | 10100               | MODE_SEL[1] | MODE_SEL[0] | CONFIG      | CFG_PIN_REG | OE1         | OE0         | Rsvd       | Rsvd       |

| 21   | 10101               | CLK_SEL     | AUTO_MAN[1] | AUTO_MAN[0] | 0           | ADC_RATE[1] | ADC_RATE[0] | LCK_WIN[1] | LCK_WIN[0] |

| 22   | 10110               | 1           | 0           | 1           | 0           | 0           | 0           | 0          | 0          |

| 23   | 10111               | CLK_ACTIVE  | HOLDOVER    | CLK1BAD     | CLK0BAD     | XTAL_BAD    | LOCK_IND    | Rsvd       | Rsvd       |

### **Register Bit Color Key**

| Configuration 0 Specific Bits |

|-------------------------------|

| Configuration 1 Specific Bits |

| Global Control & Status Bits  |

The register bits described in Table 4E are duplicated, with one set applying for Configuration 0 and the other for Configuration 1. The functions of the bits are identical, but only apply when the

configuration they apply to is enabled. Replace the lowercase n in the bit field description with 0 or 1 to find the field's location in the bitmap in Table 4D.

### Table 4E. Configuration-Specific Control Bits

| Register Bits | Function                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q0_TYPEn      | Determines the output type for output pair Q0, nQ0 for Configuration n.<br>0 = LVPECL<br>1 = LVDS                                                                                                                                                                                                                                                           |

| Pn[16:0]      | Reference Pre-Divider for Configuration n.                                                                                                                                                                                                                                                                                                                  |

| M1_n[16:0]    | Integer Feedback Divider in Lower Feedback Loop for Configuration n.                                                                                                                                                                                                                                                                                        |

| M_INTn[7:0]   | Feedback Divider, Integer Value in Upper Feedback Loop for Configuration n.                                                                                                                                                                                                                                                                                 |

| M_FRACn[17:0] | Feedback Divider, Fractional Value in Upper Feedback Loop for Configuration n.                                                                                                                                                                                                                                                                              |

| Nn[10:0]      | Output Divider for Configuration n.                                                                                                                                                                                                                                                                                                                         |

| BWn[6:0]      | Internal Operation Settings for Configuration n.<br>Please use IDT ICS849N212I Configuration Software to determine the correct settings for these bits for the specific configuration. Alternatively, please consult with IDT directly for further information on the functions of these bits. The function of these bits is explained in Tables 4J and 4K. |

### Table 4F. Global Control Bits

| Register Bits | Function                                                                                                                                                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE_SEL[1:0] | PLL Mode Select00 = Low Bandwidth Frequency Translator01 = Frequency Synthesizer10 = High Bandwidth Frequency Translator11 = High Bandwidth Frequency Translator                                                                        |

| CFG_PIN_REG   | Configuration Control. Selects whether the configuration selection function is under pin or register control.<br>0 = Pin Control<br>1 = Register Control                                                                                |

| CONFIG        | Configuration Selection. Selects whether the device uses the register configuration set 0 or 1. This bit only has an effect when the CFG_PIN_REG bit is set to 1 to enable register control.                                            |

| OE0           | Output Enable Control for Output 0. Both this register bit and the corresponding Output Enable pin OE0 must be asserted to enable the Q0, nQ0 output.<br>0 = Output Q0, nQ0 disabled<br>1 = Output Q0, nQ0 under control of the OE0 pin |

| OE1           | Output Enable Control for Output 1. Both this register bit and the corresponding Output Enable pin OE1 must be asserted to enable the Q1 output.<br>0 = Output Q1 disabled<br>1 = Output Q1 under control of the OE1 pin                |

| Rsvd          | Reserved bits - user should write a '0' to these bit positions if a write to these registers is needed                                                                                                                                  |

| AUTO_MAN[1:0] | Selects how input clock selection is performed.<br>00 = Manual Selection via pin only<br>01 = Automatic, non-revertive<br>10 = Automatic, revertive<br>11 = Manual Selection via register only                                          |

| CLK_SEL       | In manual clock selection via register mode, this bit will command which input clock is selected. In the automatic modes, this indicates the primary clock input. In manual selection via pin mode, this bit has no effect.<br>0 = CLK0<br>1 = CLK1 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_RATE[1:0] | Sets the ADC sampling rate in Low-Bandwidth Mode as a fraction of the crystal input frequency.<br>00 = Crystal Frequency / 16<br>01 = Crystal Frequency / 8<br>10 = Crystal Frequency / 4 (recommended)<br>11 = Crystal Frequency / 2               |

| LCK_WIN[1:0]  | Sets the width of the window in which a new reference edge must fall relative to the feedback edge: 00 = 2usec (recommended), 01 = 4usec, 10 = 8usec, 11 = 16usec                                                                                   |

### Table 4G. Global Status Bits

| Register Bits | Function                                                                                                                                                                                                                               |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0BAD       | Status Bit for input clock 0. This function is mirrored in the CLK0BAD pin.<br>0 = input 0 good<br>1 = input 0 bad. Self clears when input clock returns to good status                                                                |

| CLK1BAD       | Status Bit for input clock 1. This function is mirrored in the CLK1BAD pin.<br>0 = input 0 good<br>1 = input 0 bad. Self clears when input clock returns to good status                                                                |

| XTALBAD       | Status Bit. This function is mirrored on the XTALBAD pin.<br>0 = crystal input good<br>1 = crystal input bad. Self-clears when the XTAL clock returns to good status                                                                   |

| LOCK_IND      | Status bit. This function is mirrored on the LOCK_IND pin.<br>0 = PLL unlocked<br>1 = PLL locked                                                                                                                                       |

| HOLDOVER      | Status Bit. This function is mirrored on the HOLDOVER pin.<br>0 = Input to phase detector is within specifications and device is tracking to it<br>1 = Phase detector input not within specifications and DCXO is frozen at last value |

| CLK_ACTIVE    | Status Bit. Indicates which input clock is active. Automatically updates during fail-over switching. Status also indicated on CLK_ACTIVE pin.                                                                                          |

### Table 4J. BW[6:0] Bits

| Mode                | BW[6]       | BW[5]       | BW[4]       | BW[3]       | BW[2]      | BW[1]      | BW[0]        |

|---------------------|-------------|-------------|-------------|-------------|------------|------------|--------------|

| Synthesizer Mode    | PLL2_LF[1]  | PLL2_LF[0]  | DSM_ORD     | DSM_EN      | PLL2_CP[1] | PLL2_CP[0] | PLL2_LOW_ICP |

| High-Bandwidth Mode | PLL2_LF[1]  | PLL2_LF[0]  | DSM_ORD     | DSM_EN      | PLL2_CP[1] | PLL2_CP[0] | PLL2_LOW_ICP |

| Low-Bandwidth Mode  | ADC_GAIN[3] | ADC_GAIN[2] | ADC_GAIN[1] | ADC_GAIN[0] | PLL1_CP[1] | PLL1_CP[0] | PLL2_LOW_ICP |

### Table 4K. Functions of Fields in BW[6:0]

| Register Bits | Function                                                                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL2_LF[1:0]  | Sets loop filter values for upper loop PLL in Frequency Synthesizer & High-Bandwidth modes.<br>Defaults to setting of 00 when in Low Bandwidth Mode. See Table 4L for settings. |

| DSM_ORD       | Sets Delta-Sigma Modulation to 2nd (0) or 3rd order (1) operation.                                                                                                              |

| DSM_EN        | Enables Delta-Sigma Modulator.<br>0 = Disabled - feedback in integer mode only<br>1 = Enabled - feedback in fractional mode                                                     |

| PLL2_CP[1:0]  | Upper loop PLL charge pump current settings:<br>$00 = 173\mu A$ (defaults to this setting in Low Bandwidth Mode)<br>$01 = 346\mu A$<br>$10 = 692\mu A$<br>11 = reserved         |

| PLL2_LOW_ICP  | Reduces Charge Pump current by 1/3 <sup>RD</sup> to reduce bandwidth variations resulting from higher feedback register settings or high VCO operating frequency (>2.4GHz).     |

| ADC_GAIN[3:0] | Gain setting for ADC in Low Bandwidth Mode.                                                                                                                                     |

| PLL1_CP[1:0]  | Lower loop PLL charge pump current settings (lower loop is only used in Low Bandwidth Mode):<br>$00 = 800\mu A$<br>$01 = 400\mu A$<br>$10 = 200\mu A$<br>$11 = 100\mu A$        |

#### Table 4L. Upper Loop (PLL2) Bandwidth Settings

| Desired Bandwidth | PLL2_CP        | PLL2ICP        | PLL2_LF |

|-------------------|----------------|----------------|---------|

| Frequ             | ency Synthesiz | er Mode        |         |

| 200kHz            | 00             | 1              | 00      |

| 400kHz            | 01             | 1              | 01      |

| 800kHz            | 10             | 1              | 10      |

| 2MHz              | 10             | 1              | 11      |

| High Bandwid      | th Frequency   | Translator Mo  | de      |

| 200kHz            | 00             | 1              | 00      |

| 400kHz            | 01             | 1              | 01      |

| 800kHz            | 10             | 1              | 10      |

| 4MHz              | 10             | 0              | 11      |

| Low Bandwic       | Ith Frequency  | Franslator Mod | de      |

| 200kHz            | 00             |                | 00      |

NOTE: To achieve 4MHz bandwidth, reference to the phase detector should be 80MHz.

## **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                            | Rating                           |  |

|-------------------------------------------------|----------------------------------|--|

| Supply Voltage, V <sub>CC</sub>                 | 3.63V                            |  |

| Inputs, V <sub>I</sub>                          |                                  |  |

| XTAL_IN                                         | 0V to 2V                         |  |

| Other Input                                     | -0.5V to V <sub>CC</sub> + 0.5V  |  |

| Outputs, V <sub>O</sub> (LVCMOS)                | -0.5V to V <sub>CCO</sub> + 0.5V |  |

| Outputs, I <sub>O</sub> (LVPECL)                |                                  |  |

| Continuous Current                              | 50mA                             |  |

| Surge Current                                   | 100mA                            |  |

| Outputs, I <sub>O</sub> (LVDS)                  |                                  |  |

| Continuous Current                              | 10mA                             |  |

| Surge Current                                   | 15mA                             |  |

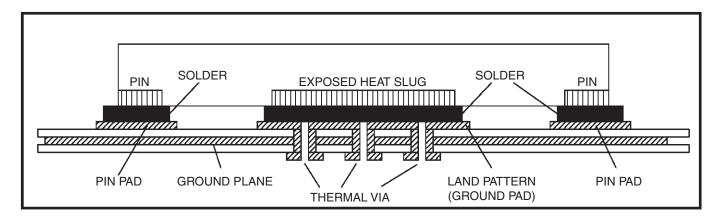

| Package Thermal Impedance, $\theta_{\text{JA}}$ | 32.4°C/W (0 mps)                 |  |

| Storage Temperature, T <sub>STG</sub>           | -65°C to 150°C                   |  |

## **DC Electrical Characteristics**

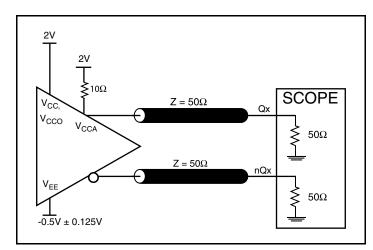

### Table 5A. LVPECL Power Supply DC Characteristics, $V_{CC} = V_{CCO} = 3.3V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol           | Parameter             | Test Conditions  | Minimum             | Typical | Maximum         | Units |

|------------------|-----------------------|------------------|---------------------|---------|-----------------|-------|

| V <sub>CC</sub>  | Core Supply Voltage   |                  | 3.135               | 3.3     | 3.465           | V     |

| V <sub>CCA</sub> | Analog Supply Voltage |                  | $V_{\rm CC} - 0.30$ | 3.3     | V <sub>CC</sub> | V     |

| V <sub>CCO</sub> | Output Supply Voltage |                  | 3.135               | 3.3     | 3.465           | V     |

| I <sub>EE</sub>  | Power Supply Current  | Outputs Unloaded |                     |         | 320             | mA    |

| I <sub>CCA</sub> | Analog Supply Current | Outputs Unloaded |                     |         | 30              | mA    |

### Table 5B. LVPECL Power Supply DC Characteristics, $V_{CC} = 3.3V \pm 5\%$ , $V_{CCO} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol           | Parameter             | Test Conditions  | Minimum                | Typical | Maximum         | Units |

|------------------|-----------------------|------------------|------------------------|---------|-----------------|-------|

| V <sub>CC</sub>  | Core Supply Voltage   |                  | 3.135                  | 3.3     | 3.465           | V     |

| V <sub>CCA</sub> | Analog Supply Voltage |                  | V <sub>CC</sub> - 0.30 | 3.3     | V <sub>CC</sub> | V     |

| V <sub>CCO</sub> | Output Supply Voltage |                  | 2.375                  | 2.5     | 2.625           | V     |

| I <sub>EE</sub>  | Power Supply Current  | Outputs Unloaded |                        |         | 319             | mA    |

| I <sub>CCA</sub> | Analog Supply Current | Outputs Unloaded |                        |         | 30              | mA    |

NOTE: Table only applies when output Q0, nQ0 is in LVPECL mode.

| Symbol           | Parameter             | Test Conditions  | Minimum                | Typical | Maximum         | Units |

|------------------|-----------------------|------------------|------------------------|---------|-----------------|-------|

| V <sub>CC</sub>  | Core Supply Voltage   |                  | 2.375                  | 2.5     | 2.625           | V     |

| V <sub>CCA</sub> | Analog Supply Voltage |                  | V <sub>CC</sub> – 0.26 | 2.5     | V <sub>CC</sub> | V     |

| V <sub>CCO</sub> | Output Supply Voltage |                  | 2.375                  | 2.5     | 2.625           | V     |

| I <sub>EE</sub>  | Power Supply Current  | Outputs Unloaded |                        |         | 304             | mA    |

| I <sub>CCA</sub> | Analog Supply Current | Outputs Unloaded |                        |         | 26              | mA    |

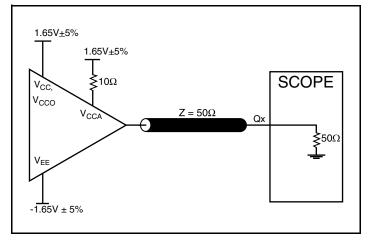

## Table 5C. LVPECLPower Supply DC Characteristics, $V_{CC} = V_{CCO} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

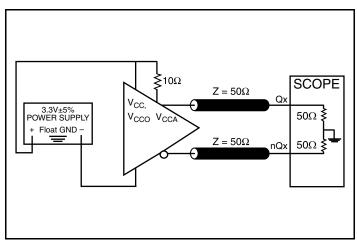

## Table 5D. LVDS Power Supply DC Characteristics, $V_{CC} = V_{CCO} = 3.3V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol           | Parameter             | Test Conditions  | Minimum                | Typical | Maximum         | Units |

|------------------|-----------------------|------------------|------------------------|---------|-----------------|-------|

| V <sub>CC</sub>  | Core Supply Voltage   |                  | 3.135                  | 3.3     | 3.465           | V     |

| V <sub>CCA</sub> | Analog Supply Voltage |                  | V <sub>CC</sub> - 0.30 | 3.3     | V <sub>CC</sub> | V     |

| V <sub>CCO</sub> | Output Supply Voltage |                  | 3.135                  | 3.3     | 3.465           | V     |

| I <sub>CC</sub>  | Power Supply Current  | Outputs Unloaded |                        |         | 280             | mA    |

| I <sub>CCA</sub> | Analog Supply Current | Outputs Unloaded |                        |         | 30              | mA    |

| I <sub>CCO</sub> | Output Supply Current | Outputs Unloaded |                        |         | 40              | mA    |

## Table 5E. LVDS Power Supply DC Characteristics, $V_{CC} = V_{CCO} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol           | Parameter             | Test Conditions  | Minimum                | Typical | Maximum         | Units |

|------------------|-----------------------|------------------|------------------------|---------|-----------------|-------|

| V <sub>CC</sub>  | Core Supply Voltage   |                  | 2.375                  | 2.5     | 2.625           | V     |

| V <sub>CCA</sub> | Analog Supply Voltage |                  | V <sub>CC</sub> – 0.26 | 2.5     | V <sub>CC</sub> | V     |

| V <sub>CCO</sub> | Output Supply Voltage |                  | 2.375                  | 2.5     | 2.625           | V     |

| I <sub>CC</sub>  | Power Supply Current  | Outputs Unloaded |                        |         | 275             | mA    |

| I <sub>CCA</sub> | Analog Supply Current | Outputs Unloaded |                        |         | 26              | mA    |

| I <sub>CCO</sub> | Output Supply Current | Outputs Unloaded |                        |         | 40              | mA    |

| Symbol          | Parameter              |                                                                           | Test Conditions                                               | Minimum                                           | Typical              | Maximum               | Units |   |

|-----------------|------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|----------------------|-----------------------|-------|---|

| V               | Input Lligh Volt       |                                                                           | $V_{CC} = 3.3V$                                               | 2                                                 |                      | V <sub>CC</sub> + 0.3 | V     |   |

| V <sub>IH</sub> | Input High Volt        | age                                                                       | V <sub>CC</sub> = 2.5V                                        | 1.7                                               |                      | V <sub>CC</sub> + 0.3 | V     |   |

| V               | Input Low Volt         |                                                                           | $V_{CC} = 3.3V$                                               | -0.3                                              |                      | 0.8                   | V     |   |

| V <sub>IL</sub> | Input Low Volt         | age                                                                       | V <sub>CC</sub> = 2.5V                                        | -0.3                                              | V <sub>CC</sub> + 0. | 0.7                   | V     |   |

|                 | Input                  | CLK_SEL, CONFIG,<br>PLL_BYPASS, S_A[0:1]                                  | $V_{CC} = V_{IN} = 3.465 V \text{ or } 2.625 V$               |                                                   |                      | 150                   | μΑ    |   |

| IIH             | High Current           | OE0, OE1,<br>SCLK, SDATA                                                  | $V_{CC} = V_{IN} = 3.465 V \text{ or } 2.625 V$               |                                                   |                      | 5                     | μΑ    |   |

|                 | Input                  | CLK_SEL, CONFIG,<br>PLL_BYPASS, S_A[0:1]                                  | $V_{CC} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$        | -5                                                |                      |                       | μA    |   |

| IIL             | Low Current            | OE0, OE1,<br>SCLK, SDATA                                                  | $V_{CC} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$        | -150                                              |                      |                       | μA    |   |

|                 |                        |                                                                           | HOLDOVER,                                                     | V <sub>CCO</sub> = 3.465V, I <sub>OH</sub> = -8mA | 2.6                  |                       |       | V |

| V <sub>OH</sub> | Output<br>High Voltage | CLK_ACTIVE, SDATA,<br>LOCK_IND, XTALBAD,<br>CLK0BAD, CLK1BAD              | V <sub>CCO</sub> = 2.625V, I <sub>OH</sub> = -8mA             | 1.8                                               |                      |                       | V     |   |

|                 | riigh volkago          | Q1                                                                        | V <sub>CCO</sub> = 3.465V, I <sub>OH</sub> = -12mA            | 2.6                                               |                      |                       | V     |   |

|                 |                        | QI                                                                        | V <sub>CCO</sub> = 2.625V, I <sub>OH</sub> = -12mA            | 1.8                                               |                      |                       | V     |   |

| V <sub>OL</sub> | Output<br>Low Voltage  | HOLDOVER,<br>CLK_ACTIVE, SDATA,<br>LOCK_IND, XTALBAD,<br>CLK0BAD, CLK1BAD | V <sub>CCO</sub> = 3.465V or 2.625V,<br>I <sub>OL</sub> = 8mA |                                                   |                      | 0.5                   | v     |   |

|                 |                        | Q1                                                                        | $V_{CCO} = 3.465V \text{ or } 2.625V,$<br>$I_{OL} = 12mA$     |                                                   |                      | 0.5                   | V     |   |

### Table 5F. LVCMOS/LVTTL DC Characteristics, $T_A$ = -40°C to 85°C

## Table 5G. Differential DC Characteristics, $V_{CC} = V_{CCO} = 3.3V \pm 5\%$ or 2.5V±5%, $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to 85°C

| Symbol           | Parameter                     |                             | Test Conditions                                                                              | Minimum               | Typical | Maximum               | Units    |

|------------------|-------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|-----------------------|---------|-----------------------|----------|

| I <sub>IH</sub>  | Input<br>High Current         | CLK0, nCLK0,<br>CLK1, nCLK1 | V <sub>CC</sub> = V <sub>IN</sub> = 3.465V or 2.625V                                         |                       |         | 150                   | μΑ       |

| IIL              | Input<br>Low Current          | CLK0, CLK1<br>nCLK0, nCLK1  | $V_{CC} = 3.465$ V or 2.625V, $V_{IN} = 0$ V<br>$V_{CC} = 3.465$ V or 2.625V, $V_{IN} = 0$ V | -5<br>-150            |         |                       | μΑ<br>μΑ |

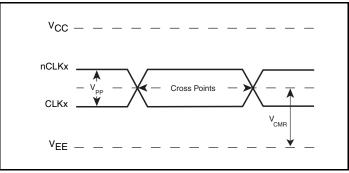

| V <sub>PP</sub>  | Peak-to-Peak Voltag           | ge; NOTE 1                  |                                                                                              | 0.15                  |         | 1.3                   | V        |

| V <sub>CMR</sub> | Common Mode Inpu<br>NOTE 1, 2 | ıt Voltage;                 |                                                                                              | V <sub>EE</sub> + 0.5 |         | V <sub>CC</sub> – 1.0 | V        |

NOTE 1:  $V_{IL}$  should not be less than -0.3V.

NOTE 2: Common mode voltage is defined as the crosspoint.

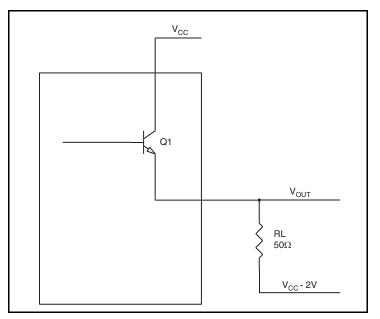

## Table 5H. LVPECL DC Characteristics, $V_{CC}$ = $V_{CCO}$ = 3.3V±5%, $V_{EE}$ = 0V, $T_A$ = -40°C to 85°C

| Symbol             | Parameter                         | Test Conditions | Minimum                | Typical | Maximum                | Units |

|--------------------|-----------------------------------|-----------------|------------------------|---------|------------------------|-------|

| V <sub>OH</sub>    | Output High Voltage; NOTE 1       |                 | V <sub>CCO</sub> – 1.1 |         | V <sub>CCO</sub> – 0.7 | V     |

| V <sub>OL</sub>    | Output Low Voltage NOTE 1         |                 | V <sub>CCO</sub> - 2.0 |         | V <sub>CCO</sub> – 1.5 | V     |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing |                 | 0.6                    |         | 1.0                    | V     |

### NOTE 1: Outputs terminated with 50 $\Omega$ to V\_{CCO} – 2V.

|                    |                                   |                 | ,0 =10 = = 7 7,        |         |                        |       |

|--------------------|-----------------------------------|-----------------|------------------------|---------|------------------------|-------|

| Symbol             | Parameter                         | Test Conditions | Minimum                | Typical | Maximum                | Units |

| V <sub>OH</sub>    | Output High Voltage; NOTE 1       |                 | V <sub>CCO</sub> – 1.1 |         | V <sub>CCO</sub> – 0.8 | V     |

| V <sub>OL</sub>    | Output Low Voltage NOTE 1         |                 | V <sub>CCO</sub> – 2.0 |         | V <sub>CCO</sub> – 1.5 | V     |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing |                 | 0.6                    |         | 1.0                    | V     |

### Table 5I. LVPECL DC Characteristics, $V_{CC} = 3.3V \pm 5\%$ or $2.5V \pm 5\%$ , $V_{CCO} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

NOTE 1: Outputs terminated with 50  $\Omega$  to V\_{CCO} – 2V.

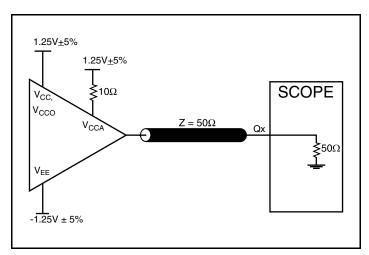

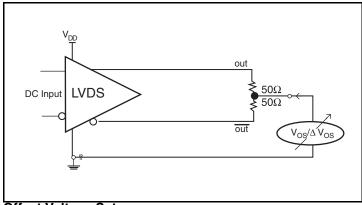

### Table 5J. LVDS DC Characteristics, $V_{CC} = V_{CCO} = 3.3V \pm 5\%$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol          | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub> | Differential Output Voltage      |                 | 247     |         | 454     | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |                 |         |         | 50      | mV    |

| V <sub>OS</sub> | Offset Voltage                   |                 | 1.125   |         | 1.375   | V     |

| $\Delta V_{OS}$ | V <sub>OS</sub> Magnitude Change |                 |         |         | 50      | mV    |

## Table 5K. LVDS DC Characteristics, $V_{CC} = V_{CCO} = 2.5V \pm 5\%$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol          | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub> | Differential Output Voltage      |                 | 247     |         | 454     | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |                 |         |         | 50      | mV    |

| V <sub>OS</sub> | Offset Voltage                   |                 | 1.125   |         | 1.375   | V     |

| $\Delta V_{OS}$ | V <sub>OS</sub> Magnitude Change |                 |         |         | 50      | mV    |

### Table 6. Input Frequency Characteristics, $V_{CC}$ = $V_{CCO}$ = 3.3V $\pm$ 5%, $T_{A}$ = -40°C to 85°C

| Symbol          | Parameter |                             | Test Conditions     | Minimum | Typical | Maximum | Units |

|-----------------|-----------|-----------------------------|---------------------|---------|---------|---------|-------|

|                 |           | XTAL_IN, XTAL_OUT<br>NOTE 1 |                     | 16      |         | 40      | MHz   |

| f <sub>IN</sub> | Input     | CLK0, nCLK0,                | High Bandwidth Mode | 16      |         | 710     | MHz   |

|                 | Frequency | CLK1, nCLK1                 | Low Bandwidth Mode  | 0.008   |         | 710     | MHz   |

|                 |           | SCLK                        |                     |         |         | 5       | MHz   |

NOTE 1: For the input crystal and CLKx, nCLKx frequency range, the M value must be set for the VCO to operate within the 1995MHz to 2600MHz range.

### Table 7. Crystal Characteristics

| Parameter                          | Test Conditions | Minimum | Typical    | Maximum | Units |

|------------------------------------|-----------------|---------|------------|---------|-------|

| Mode of Oscillation                |                 |         | Fundamenta | l       |       |

| Frequency                          |                 | 16      |            | 40      | MHz   |

| Equivalent Series Resistance (ESR) |                 |         |            | 100     | Ω     |

| Shunt Capacitance                  |                 |         |            | 7       | pF    |

| Load Capacitance (CL)              |                 |         | 12         |         | pF    |

## **AC Electrical Characteristics**

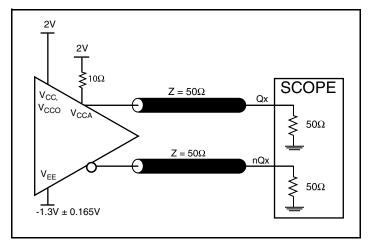

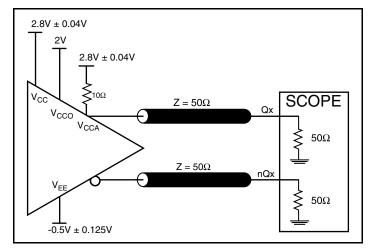

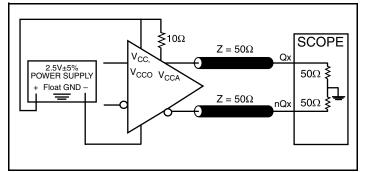

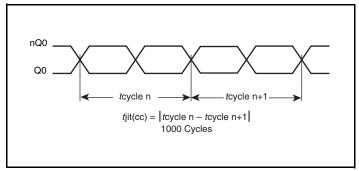

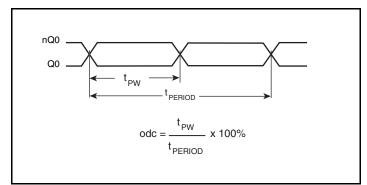

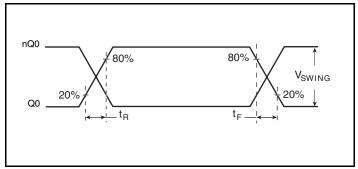

**Table 8. AC Characteristics,**  $V_{CC} = V_{CCO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ , or  $V_{CC} = 3.3V \pm 5\%$ ,  $V_{CCO} = 2.5V \pm 5\%$  (LVPECL only,  $V_{EE} = 0V$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

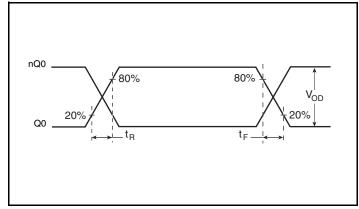

| Symbol                          | Parameter                     |                     | Test Conditions                                                                                                                | Minimum | Typical | Maximum | Units |

|---------------------------------|-------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| f <sub>OUT</sub>                | Output Frequency              |                     |                                                                                                                                | 0.98    |         | 250     | MHz   |