# ANALOG DEVICES

# 16-Bit 100 kSPS Sampling ADC

AD676

#### FEATURES

Autocalibrating On-Chip Sample-Hold Function Parallel Output Format 16 Bits No Missing Codes ±1 LSB INL –97 dB THD 90 dB S/(N+D) 1 MHz Full Power Bandwidth

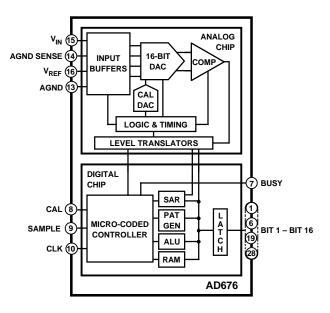

#### FUNCTIONAL BLOCK DIAGRAM

The AD676 operates from +5 V and ±12 V supplies and typically consumes 360 mW during conversion. The digital supply (V<sub>DD</sub>) is separated from the analog supplies (V<sub>CC</sub>, V<sub>EE</sub>) for reduced digital crosstalk. An analog ground sense is provided for the analog input. Separate analog and digital grounds are also provided.

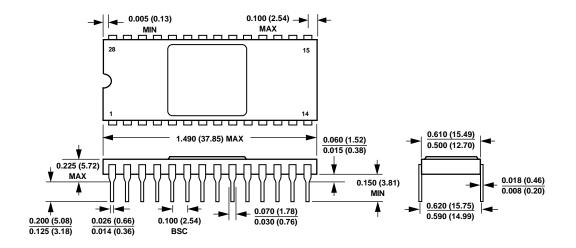

The AD676 is available in a 28-pin plastic DIP or 28-pin sidebrazed ceramic package. A serial-output version, the AD677, is available in a 16-pin 300 mil wide ceramic or plastic package.

#### **PRODUCT DESCRIPTION**

The AD676 is a multipurpose 16-bit parallel output analog-todigital converter which utilizes a switched-capacitor/charge redistribution architecture to achieve a 100 kSPS conversion rate (10  $\mu$ s total conversion time). Overall performance is optimized by digitally correcting internal nonlinearities through on-chip autocalibration.

The AD676 circuitry is segmented onto two monolithic chips a digital control chip fabricated on Analog Devices DSP CMOS process and an analog ADC chip fabricated on our BiMOS II process. Both chips are contained in a single package.

The AD676 is specified for ac (or "dynamic") parameters such as S/(N+D) Ratio, THD and IMD which are important in signal processing applications. In addition, dc parameters are specified which are important in measurement applications.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# AD676-SPECIFICATIONS

### **AC SPECIFICATIONS** $(T_{MIN} \text{ to } T_{MAX}, V_{CC} = +12 \text{ V} \pm 5\%, V_{EE} = -12 \text{ V} \pm 5\%, V_{DD} = +5 \text{ V} \pm 10\%)^{1}$

|                                                        |     | AD676J/A |       |     | AD676K/B |       |        |

|--------------------------------------------------------|-----|----------|-------|-----|----------|-------|--------|

| Parameter                                              | Min | Тур      | Max   | Min | Тур      | Max   | Units  |

| Total Harmonic Distortion (THD) <sup>2</sup>           |     |          |       |     |          |       |        |

| @ 83 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>        |     | -96      | -88   |     | -97      | -90   | dB     |

|                                                        |     | 0.0016   | 0.004 |     | 0.0014   | 0.003 | %      |

| @ 100 kSPS, +25°C                                      |     | -96      |       |     | -97      |       | dB     |

|                                                        |     | 0.0016   |       |     | 0.0014   |       | %      |

| @ 100 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>       |     | -92      |       |     | -92      |       | dB     |

|                                                        |     | 0.0025   |       |     | 0.0025   |       | %      |

| Signal-to-Noise and Distortion Ratio $(S/(N+D))^{2,3}$ |     |          |       |     |          |       |        |

| @ 83 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>        | 85  | 89       |       | 87  | 90       |       | dB     |

| @ 100 kSPS, +25°C                                      |     | 89       |       |     | 90       |       | dB     |

| @ 100 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>       |     | 86       |       |     | 86       |       | dB     |

| Peak Spurious or Peak Harmonic Component               |     | -98      |       |     | -98      |       | dB     |

| Intermodulation Distortion (IMD) <sup>4</sup>          |     |          |       |     |          |       |        |

| 2nd Order Products                                     |     | -102     |       |     | -102     |       | dB     |

| 3rd Order Products                                     |     | -98      |       |     | -98      |       | dB     |

| Full Power Bandwidth                                   |     | 1        |       |     | 1        |       | MHz    |

| Noise                                                  |     | 160      |       |     | 160      |       | μV rms |

# **DIGITAL SPECIFICATIONS** (for all grades T<sub>MIN</sub> to T<sub>MAX</sub>, $V_{CC} = +12 V \pm 5\%$ , $V_{EE} = -12 V \pm 5\%$ , $V_{DD} = +5 V \pm 10\%$ )

| Parame          | eter                      | Test Conditions           | Min                | Тур | Max            | Units |

|-----------------|---------------------------|---------------------------|--------------------|-----|----------------|-------|

| LOGIC           | INPUTS                    |                           |                    |     |                |       |

| $V_{\rm IH}$    | High Level Input Voltage  |                           | 2.4                |     | $V_{DD} + 0.3$ | V     |

| V <sub>IL</sub> | Low Level Input Voltage   |                           | -0.3               |     | 0.8            | V     |

| I <sub>IH</sub> | High Level Input Current  | $V_{IH} = V_{DD}$         | -10                |     | +10            | μA    |

| I <sub>IL</sub> | Low Level Input Current   | $V_{II} = 0 V$            | -10                |     | +10            | μA    |

| C <sub>IN</sub> | Input Capacitance         |                           |                    | 10  |                | pF    |

| LOGIC           | OUTPUTS                   |                           |                    |     |                |       |

| V <sub>OH</sub> | High Level Output Voltage | $I_{OH} = 0.1 \text{ mA}$ | V <sub>DD</sub> -1 | V   |                | V     |

|                 |                           | $I_{OH} = 0.5 \text{ mA}$ | 2.4                |     |                | V     |

| V <sub>OL</sub> | Low Level Output Voltage  | $I_{OL} = 1.6 \text{ mA}$ |                    |     | 0.4            | V     |

NOTES

$^{1}V_{REF}$  = 10.0 V, (Conversion Rate (fs) = 83 kSPS,  $f_{IN}$  = 1.0 kHz,  $V_{IN}$  = -0.05 dB, Bandwidth = fs/2 unless otherwise indicated. All measurements referred to a 0 dB (20 V p-p) input signal. Values are post-calibration.

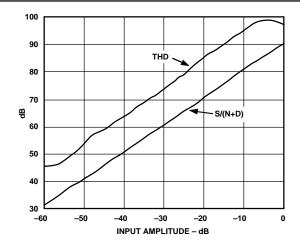

<sup>2</sup>For other input amplitudes, refer to Figure 13.

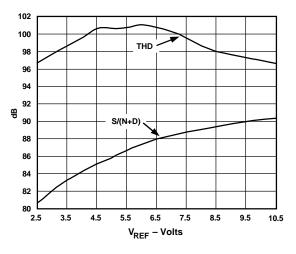

<sup>3</sup>For other input ranges/voltages reference values see Figure 12.

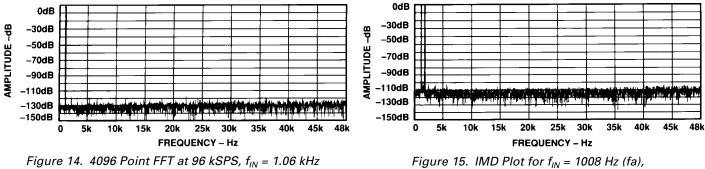

${}^{4}$ fa = 1008 Hz. fb = 1055 Hz. See Definition of Specifications section and Figure 15.

Specifications subject to change without notice.

# **DC SPECIFICATIONS** $(T_{MIN} \text{ to } T_{MAX}, V_{CC} = +12 \text{ V} \pm 5\%, V_{EE} = -12 \text{ V} \pm 5\%, V_{DD} = +5 \text{ V} \pm 10\%)^{1}$

|                                                               | AD676J/A |                 |               |     |                 |               |       |

|---------------------------------------------------------------|----------|-----------------|---------------|-----|-----------------|---------------|-------|

| Parameter                                                     | Min      | Тур             | Max           | Min | Тур             | Max           | Units |

| TEMPERATURE RANGE                                             |          |                 |               |     |                 |               |       |

| J, K Grades                                                   | 0        |                 | +70           | 0   |                 | +70           | °C    |

| A, B Grades                                                   | -40      |                 | +85           | -40 |                 | +85           | °C    |

| ACCURACY                                                      |          |                 |               |     |                 |               |       |

| Resolution                                                    | 16       |                 |               | 16  |                 |               | Bits  |

| Integral Nonlinearity (INL)                                   |          |                 |               |     |                 |               |       |

| (a) 83 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>             |          | $\pm 1$         |               |     | $\pm 1$         | ±1.5          | LSB   |

| (a) 100 kSPS, +25°C                                           |          | $\pm 1$         |               |     | $\pm 1$         |               | LSB   |

| (a) 100 kSPS, T <sub>MIN</sub> to T <sub>MAX</sub>            |          | $\pm 2$         |               |     | $\pm 2$         |               | LSB   |

| Differential Nonlinearity (DNL)–No Missing Codes              |          | 16              |               | 16  | ± 2             |               | Bits  |

| Bipolar Zero Error <sup>2</sup> (at Nominal Supplies)         |          | 0.005           |               | 10  | 0.005           |               | % FSR |

| Gain Error (at Nominal Supplies)                              |          | 0.005           |               |     | 0.005           |               |       |

| (a) 83 kSPS <sup>2</sup>                                      |          | 0.005           |               |     | 0.005           |               | % FSR |

| @ 100 kSPS, +25°C                                             |          | 0.005           |               |     | 0.005           |               | % FSR |

| $(a) 100 \text{ kSPS}^2$                                      |          | 0.005           |               |     | 0.005           |               | % FSR |

| Temperature Drift, Bipolar Zero <sup>3</sup>                  |          | 0.01            |               |     | 0.01            |               | % FSR |

| J, K Grades                                                   |          | 0.0015          |               |     | 0.0015          |               | % FSR |

|                                                               |          |                 |               |     |                 |               |       |

| A, B Grades                                                   |          | 0.003           |               |     | 0.003           |               | % FSR |

| Temperature Drift, Gain <sup>3</sup>                          |          | 0.0015          |               |     | 0.0015          |               | % FSR |

| J, K Grades                                                   |          | 0.0015          |               |     | 0.0015          |               |       |

| A, B Grades                                                   |          | 0.003           |               |     | 0.003           |               | % FSR |

| VOLTAGE REFERENCE INPUT RANGE <sup>4</sup> ( $V_{REF}$ )      | 5        |                 | 10            | 5   |                 | 10            | V     |

| ANALOG INPUT⁵                                                 |          |                 |               |     |                 |               |       |

| Input Range (V <sub>IN</sub> )                                |          |                 | $\pm V_{REF}$ |     |                 | $\pm V_{REF}$ | V     |

| Input Impedance                                               |          | *               | i deli        |     | *               |               |       |

| Input Settling Time                                           |          | 2               |               |     | 2               |               | μs    |

| Input Capacitance During Sample                               |          |                 | 50*           |     |                 | 50*           | pF    |

| Aperture Delay                                                |          | 6               |               |     | 6               |               | ns    |

| Aperture Jitter                                               |          | 100             |               |     | 100             |               | ps    |

| POWER SUPPLIES                                                |          |                 |               |     |                 |               |       |

| Power Supply Rejection                                        |          |                 |               |     |                 |               |       |

| $V_{CC} = +12 V \pm 5\%$                                      |          | ±1              |               |     | $\pm 1$         |               | LSB   |

| $V_{CC} = -12 V \pm 5\%$<br>$V_{EE} = -12 V \pm 5\%$          |          | $\pm 1$ $\pm 1$ |               |     | $\pm 1$ $\pm 1$ |               | LSB   |

| $V_{EE} = -12$ V $\pm$ 5%<br>V <sub>DD</sub> = +5 V $\pm$ 10% |          | $\pm 1$         |               |     | $\pm 1$         |               | LSB   |

| $v_{DD} - +5 v \pm 10\%$<br>Operating Current                 |          | ± 1             |               |     | ± 1             |               |       |

|                                                               |          | 145             | 10            |     | 14 5            | 10            |       |

| I <sub>CC</sub>                                               |          | 14.5            | 18            |     | 14.5            | 18            | mA    |

| I <sub>EE</sub>                                               |          | 14.5            | 18            |     | 14.5            | 18            | mA    |

|                                                               |          | 2               | 5             |     | 2               | 5             | mA    |

| Power Consumption                                             |          | 360             | 480           |     | 360             | 480           | mW    |

NOTES

$^{1}V_{REF}$  = 5.0 V, Conversion Rate = 83 kSPS unless otherwise noted. Values are post-calibration.

<sup>2</sup>Values shown apply to any temperature from  $T_{MIN}$  to  $T_{MAX}$  after calibration at that temperature. <sup>3</sup>Values shown are based upon calibration at +25°C with no additional calibration at temperature. Values shown are the worst case variation from the value at +25°C. <sup>4</sup>See "APPLICATIONS" section for recommended voltage reference circuit, and Figure 12 for dynamic performance with other reference voltage values. <sup>5</sup>See "APPLICATIONS" section for recommended input buffer circuit.

\*For explanation of input characteristics, see "ANALOG INPUT" section.

Specifications subject to change without notice.

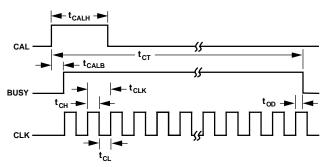

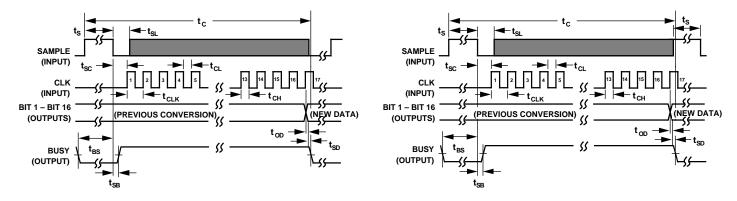

# AD676 TIMING SPECIFICATIONS(T<sub>MIN</sub> to T<sub>MAX</sub> V<sub>CC</sub> = +12 V ± 5%, V<sub>EE</sub> = -12 V ± 5%, V<sub>DD</sub> = +5 V ± 10%, V<sub>REF</sub> = 10.0 V)<sup>1</sup>

| Parameter                                   | Symbol            | Min | Тур | Max    | Units            |

|---------------------------------------------|-------------------|-----|-----|--------|------------------|

| Conversion Time <sup>2</sup>                | t <sub>C</sub>    | 10  |     | 1000   | μs               |

| CLK Period <sup>3</sup>                     | t <sub>CLK</sub>  | 480 |     |        | ns               |

| Calibration Time                            | t <sub>CT</sub>   |     |     | 85,530 | t <sub>CLK</sub> |

| Sampling Time (Included in t <sub>C</sub> ) | t <sub>S</sub>    | 2   |     |        | μs               |

| CAL to BUSY Delay                           | t <sub>CALB</sub> |     | 75  | 150    | ns               |

| BUSY to SAMPLE Delay                        | t <sub>BS</sub>   | 2   |     |        | μs               |

| SAMPLE to BUSY Delay                        | t <sub>SB</sub>   |     | 15  | 100    | ns               |

| CLK HIGH <sup>4</sup>                       | t <sub>CH</sub>   | 50  |     |        | ns               |

| $CLK LOW^4$                                 | t <sub>CL</sub>   | 50  |     |        | ns               |

| SAMPLE LOW to 1st CLK Delay                 | t <sub>SC</sub>   | 50  |     |        | ns               |

| SAMPLE LOW                                  | t <sub>SL</sub>   | 100 |     |        | ns               |

| Output Delay                                | t <sub>OD</sub>   |     | 125 | 200    | ns               |

| Status Delay                                | t <sub>SD</sub>   | 50  |     |        | ns               |

| CAL HIGH Time                               | t <sub>CALH</sub> | 50  |     |        | ns               |

#### NOTES

<sup>1</sup>See the "CONVERSION CONTROL" and "AUTOCALIBRATION" sections for detailed explanations of the above timing.

<sup>2</sup>Depends upon external clock frequency; includes acquisition time and conversion time. The maximum conversion time is specified to account for the droop of the internal sample/hold function. Longer conversion times may degrade performance. See "General Conversion Guidelines" for additional explanation of maximum conversion time.

<sup>3</sup>580 ns is recommended for optimal accuracy over temperature.

${}^{4}t_{CH} + t_{CL} = t_{CLK}$  and must be greater than 480 ns.

Figure 1. Calibration Timing

Figure 2a. General Conversion Timing

Figure 2b. Continuous Conversion Timing

| <b>ORDERING G</b> | UIDE |

|-------------------|------|

|-------------------|------|

| Model   | Temperature Range <sup>1</sup> | S/(N+D) | Max INL  | Package Description | Package<br>Option <sup>2</sup> |

|---------|--------------------------------|---------|----------|---------------------|--------------------------------|

| AD676JD | 0°C to +70°C                   | 85 dB   | ±1.5 LSB | Ceramic 28-Pin DIP  | D-28                           |

| AD676KD | 0°C to +70°C                   | 87 dB   |          | Ceramic 28-Pin DIP  | D-28                           |

| AD676AD | -40°C to +85°C                 | 85 dB   | ±1.5 LSB | Ceramic 28-Pin DIP  | D-28                           |

| AD676BD | -40°C to +85°C                 | 87 dB   |          | Ceramic 28-Pin DIP  | D-28                           |

NOTES

$^{1}$ For details on grade and package offerings screened in accordance with MIL-STD-883, refer to the AD676/883 data sheet.  $^{2}$ D = Ceramic DIP.

#### ABSOLUTE MAXIMUM RATINGS\*

| $V_{CC}$ to $V_{EE}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$ to DGND $\ldots$ $-0.3$ V to +7 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $V_{CC}$ to AGND $\hdots 0.00$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{EE}$ to AGND $\hfill \ldots \hfill \hfill \ldots \hfill \hfi$ |

| AGND to DGND ±0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Digital Inputs to DGND 0 V to +5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Analog Inputs, V <sub>REF</sub> to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $(V_{CC} + 0.3 \text{ V})$ to $(V_{EE} - 0.3 \text{ V})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Soldering +300°C, 10 sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *Stresses greater than those listed under "Absolute Maximum Ratings" may cause<br>permanent damage to the device. This is a stress rating only and functional<br>operation of the device at these or any other conditions above those indicated in<br>the operational section of this specification is not implied. Exposure to absolute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION

The AD676 features input protection circuitry consisting of large "distributed" diodes and polysilicon series resistors to dissipate both high energy discharges (Human Body Model) and fast, low energy pulses (Charged Device Model). Per Method 3015.2 of MIL-STD-883C, the AD676 has been classified as a Category 1 Device.

Proper ESD precautions are strongly recommended to avoid functional damage or performance degradation. Charges as high as 4000 volts readily accumulate on the human body and test equipment, and discharge without detection. Unused devices must be stored in conductive foam or shunts, and the foam discharged to the destination socket before devices are removed. For further information on ESD Precaution. Refer to Analog Devices' *ESD Prevention Manual*.

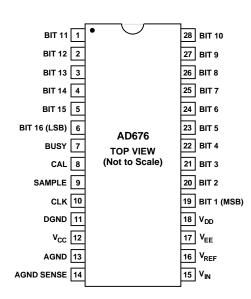

#### **PIN DESCRIPTION**

| Pin   | Name             | Туре | Description                                                                                                                                                                                                                                                                                                                                                     |

|-------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–6   | BIT 11-BIT 16    | DO   | BIT 11-BIT 16 represent the six LSBs of data.                                                                                                                                                                                                                                                                                                                   |

| 7     | BUSY             | DO   | Status Line for Converter. Active HIGH, indicating a conversion or calibration in progress.<br>BUSY should be buffered when capacitively loaded.                                                                                                                                                                                                                |

| 8     | CAL              | DI   | Calibration Control Pin (Asynchronous).                                                                                                                                                                                                                                                                                                                         |

| 9     | SAMPLE           | DI   | $V_{IN}$ Acquisition Control Pin. Active HIGH. During conversion, SAMPLE controls the state of the internal sample-hold amplifier and the falling edge initiates conversion (see "Conversion Control" paragraph). During calibration, SAMPLE should be held LOW. If HIGH during calibration, diagnostic information will appear on the two LSBs (Pins 5 and 6). |

| 10    | CLK              | DI   | Master Clock Input. The AD676 requires 17 clock cycles to execute a conversion.                                                                                                                                                                                                                                                                                 |

| 11    | DGND             | Р    | Digital Ground.                                                                                                                                                                                                                                                                                                                                                 |

| 12    | V <sub>CC</sub>  | Р    | +12 V Analog Supply Voltage.                                                                                                                                                                                                                                                                                                                                    |

| 13    | AGND             | P/AI | Analog Ground.                                                                                                                                                                                                                                                                                                                                                  |

| 14    | AGND SENSE       | AI   | Analog Ground Sense.                                                                                                                                                                                                                                                                                                                                            |

| 15    | V <sub>IN</sub>  | AI   | Analog Input Voltage.                                                                                                                                                                                                                                                                                                                                           |

| 16    | V <sub>REF</sub> | AI   | External Voltage Reference Input.                                                                                                                                                                                                                                                                                                                               |

| 17    | V <sub>EE</sub>  | Р    | $-12$ V Analog Supply Voltage. Note: the lid of the ceramic package is internally connected to $V_{\rm EE}$ .                                                                                                                                                                                                                                                   |

| 18    | V <sub>DD</sub>  | Р    | +5 V Logic Supply Voltage.                                                                                                                                                                                                                                                                                                                                      |

| 19–28 | BIT 1-BIT 10     | DO   | BIT 1-BIT 10 represent the ten MSB of data.                                                                                                                                                                                                                                                                                                                     |

Type: AI = Analog Input

DI = Digital Input DO = Digital Output

P = Power

ANALOG VIN CHIP AGND SENSE INPUT 16-BIT COMF DAC V<sub>REF</sub> BUFFERS AGND CAL DAC LOGIC & TIMING LEVEL TRANSLATORS DIGITAL CHIP 🧑 вusy SAR 1 6 9 19 20 20 CAL PAT L A T C H MICRO-CODED GEN SAMPLE (9 CONTROLLER ALU CLK 🔞 RAM AD676

Package Pinout

Functional Block Diagram

### NYQUIST FREQUENCY

An implication of the Nyquist sampling theorem, the "Nyquist frequency" of a converter is that input frequency which is one half the sampling frequency of the converter.

### TOTAL HARMONIC DISTORTION

Total harmonic distortion (THD) is the ratio of the rms sum of the harmonic components to the rms value of a full-scale input signal and is expressed in percent (%) or decibels (dB). For input signals or harmonics that are above the Nyquist frequency, the aliased components are used.

### SIGNAL-TO-NOISE PLUS DISTORTION RATIO

Signal-to-noise plus distortion is defined to be the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc.

#### GAIN ERROR

The last transition should occur at an analog value 1.5 LSB below the nominal full scale (4.99977 volts for a  $\pm 5$  V range). The gain error is the deviation of the actual difference between the first and last code transition from the ideal difference between the first and last code transition.

#### **BIPOLAR ZERO ERROR**

Bipolar zero error is the difference between the ideal midscale input voltage (0 V) and the actual voltage producing the midscale output code.

#### DIFFERENTIAL NONLINEARITY (DNL)

In an ideal ADC, code transitions are one LSB apart. Differential nonlinearity is the maximum deviation from this ideal value. It is often specified in terms of resolution for which no missing codes are guaranteed.

#### INTEGRAL NONLINEARITY (INL)

The ideal transfer function for an ADC is a straight line bisecting the center of each code drawn between "zero" and "full scale." The point used as "zero" occurs 1/2 LSB before the most negative code transition. "Full scale" is defined as a level 1.5 LSB beyond the most positive code transition. Integral nonlinearity is the worst-case deviation of a code center average from the straight line.

#### BANDWIDTH

The full-power bandwidth is that input frequency at which the amplitude of the reconstructed fundamental is reduced by 3 dB for a full-scale input.

#### INTERMODULATION DISTORTION (IMD)

With inputs consisting of sine waves at two frequencies, fa and fb, any device with nonlinearities will create distortion products, of order (m+n), at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3. . . . Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms are (fa + fb) and (fa - fb), and the third order terms are (2 fa + fb), (2 fa - fb), (fa + 2 fb) and (fa - 2 fb). The IMD products are expressed as the decibel ratio of the rms sum of the measured input signals to the rms sum of the distortion terms. The two signals applied to the converter are of equal amplitude, and the peak value of their sum is -0.5 dB from full scale. The IMD products are normalized to a 0 dB input signal.

#### APERTURE DELAY

Aperture delay is the time required after SAMPLE pin is taken LOW for the internal sample-hold of the AD676 to open, thus holding the value of  $V_{\rm lN}$ .

#### **APERTURE JITTER**

Aperture jitter is the variation in the aperture delay from sample to sample.

#### POWER SUPPLY REJECTION

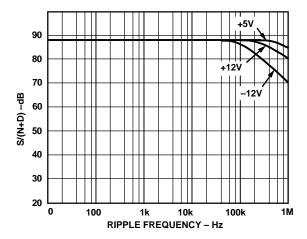

DC variations in the power supply voltage will affect the overall transfer function of the ADC, resulting in zero error and gain error changes. Power supply rejection is the maximum change in either the bipolar zero error or gain error value. Additionally, there is another power supply variation to consider. AC ripple on the power supplies can couple noise into the ADC, resulting in degradation of dynamic performance. This is displayed in Figure 16.

#### INPUT SETTLING TIME

Settling time is a function of the SHA's ability to track fast slewing signals. This is specified as the maximum time required in track mode after a full-scale step input to guarantee rated conversion accuracy.

#### FUNCTIONAL DESCRIPTION

The AD676 is a multipurpose 16-bit analog-to-digital converter and includes circuitry which performs an input sample/hold function, ground sense, and autocalibration. These functions are segmented onto two monolithic chips—an analog signal processor and a digital controller. Both chips are contained within the AD676 package.

The AD676 employs a successive-approximation technique to determine the value of the analog input voltage. However, instead of the traditional laser-trimmed resistor-ladder approach, this device uses a capacitor-array, charge redistribution technique. Binary-weighted capacitors subdivide the input sample to perform the actual analog-to-digital conversion. The capacitor array eliminates variation in the linearity of the device due to temperature-induced mismatches of resistor values. Since a capacitor array is used to perform the data conversions, the sample/hold function is included without the need for additional external circuitry.

Initial errors in capacitor matching are eliminated by an autocalibration circuit within the AD676. This circuit employs an on-chip microcontroller and a calibration DAC to measure and compensate capacitor mismatch errors. As each error is determined, its value is stored in on-chip memory (RAM). Subsequent conversions use these RAM values to improve conversion accuracy. The autocalibration routine may be invoked at any time. Autocalibration insures high performance while eliminating the need for any user adjustments and is described in detail below.

The microcontroller controls all of the various functions within the AD676. These include the actual successive approximation algorithm, the autocalibration routine, the sample/hold operation, and the internal output data latch.

#### **AUTOCALIBRATION**

The AD676 achieves rated performance without the need for user trims or adjustments. This is accomplished through the use of on-chip autocalibration.

In the autocalibration sequence, sample/hold offset is nulled by internally connecting the input circuit to the ground sense circuit. The resulting offset voltage is measured and stored in RAM for later use. Next, the capacitor representing the most significant bit (MSB) is charged to the reference voltage. This charge is then transferred to a capacitor of equal size (composed of the sum of the remaining lower weight bits). The difference in the voltage that results and the reference voltage represents the amount of capacitor mismatch. A calibration digital-to-analog converter (DAC) adds an appropriate value of error correction voltage to cancel this mismatch. This correction factor is also stored in RAM. This process is repeated for each of the capacitors representing the remaining top eight bits. The accumulated values in RAM are then used during subsequent conversions to adjust conversion results accordingly.

As shown in Figure 1, when CAL is taken HIGH the AD676 internal circuitry is reset, the BUSY pin is driven HIGH, and the ADC prepares for calibration. This is an asynchronous hardware reset and will interrupt any conversion or calibration currently in progress. Actual calibration begins when CAL is taken LOW and completes in 85,530 clock cycles, indicated by BUSY going LOW. During calibration, it is preferable for SAMPLE to be held LOW. If SAMPLE is HIGH, diagnostic data will appear on Pins 5 and 6. This data is of no value to the user.

The AD676 requires one clock cycle after BUSY goes LOW to complete the calibration cycle. If this clock cycle is not provided, it will be taken from the first conversion, likely resulting in first conversion error.

In most applications, it is sufficient to calibrate the AD676 only upon power-up, in which case care should be taken that the power supplies and voltage reference have stabilized first. If not calibrated, the AD676 accuracy may be as low as 10 bits.

#### **CONVERSION CONTROL**

The AD676 is controlled by two signals: SAMPLE and CLK, as shown in Figures 2a and 2b. It is assumed that the part has been calibrated and the digital I/O pins have the levels shown at the start of the timing diagram.

A conversion consists of an input acquisition followed by 17 clock pulses which execute the 16-bit internal successive approximation routine. The analog input is acquired by taking the SAMPLE line HIGH for a minimum sampling time of t<sub>s</sub>. The actual sample taken is the voltage present on V<sub>IN</sub> one aperture delay after the SAMPLE line is brought LOW, assuming the previous conversion has completed (signified by BUSY going LOW). Care should he taken to ensure that this negative edge is well defined and jitter free in ac applications to reduce the uncertainty (noise) in signal acquisition. With SAMPLE going LOW, the AD676 commits itself to the conversion-the input at V<sub>IN</sub> is disconnected from the internal capacitor array, BUSY goes HIGH, and the SAMPLE input will be ignored until the conversion is completed (when BUSY goes LOW). SAMPLE must be held LOW for a minimum period of time  $t_{SL}$ . A period of time t<sub>SC</sub> after bringing SAMPLE LOW, the 17 CLK cycles are applied; CLK pulses that start before this period of time are ignored. BUSY goes HIGH  $t_{SB}$  after SAMPLE goes LOW, signifying that a conversion is in process, and remains HIGH until the conversion is completed. BUSY goes LOW during the 17th CLK cycle at the point where the data outputs have changed and are valid. The AD676 will ignore CLK after BUSY has gone LOW and the output data will remain constant until a new conversion is completed. The data can, therefore, be read any time after BUSY goes LOW and before the 17th CLK of the next conversion (see Figures 2a and 2b). The section on Microprocessor Interfacing discusses how the AD676 can be interfaced to a 16-bit databus.

Typically BUSY would be used to latch the AD676 output data into buffers or to interrupt microprocessors or DSPs. It is recommended that the capacitive load on BUSY be minimized by driving no more than a single logic input. Higher capacitive loads such as cables or multiple gates may degrade conversion quality unless BUSY is buffered.

#### **CONTINUOUS CONVERSION**

For maximum throughput rate, the AD676 can be operated in a continuous convert mode (see Figure 2b). This is accomplished by utilizing the fact that SAMPLE will no longer be ignored after BUSY goes LOW, so an acquisition may be initiated even during the HIGH time of the 17th CLK pulse for maximum throughput rate while enabling full settling of the sample/hold circuitry. If SAMPLE is already HIGH when BUSY goes LOW at the end of a conversion, then an acquisition is immediately initiated and  $t_S$  and  $t_C$  start from that time. Data from the previous conversion may be latched up to  $t_{SD}$  before BUSY goes LOW or  $t_{OD}$  after the rising edge of the 17th clock pulse. However, it is preferred that latching occur on or after the falling edge of BUSY.

Care must he taken to adhere to the minimum/maximum timing requirements in order to preserve conversion accuracy.

#### **GENERAL CONVERSION GUIDELINES**

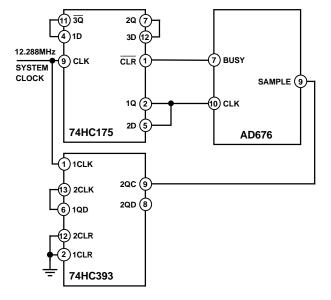

During signal acquisition and conversion, care should be taken with the logic inputs to avoid digital feedthrough noise. It is possible to run CLK continuously, even during the sample period. However, CLK edges during the sampling period, and especially when SAMPLE goes LOW, may inject noise into the sampling process. The AD676 is tested with no CLK cycles during the sampling period. The BUSY signal can be used to prevent the clock from running during acquisition, as illustrated in Figure 3. In this circuit BUSY is used to reset the circuitry which divides the system clock down to provide the AD676 CLK. This serves to interrupt the clock until after the input signal has been acquired, which has occurred when BUSY goes HIGH. When the conversion is completed and BUSY goes LOW, the circuit in Figure 3 truncates the 17th CLK pulse width which is tolerable because only its rising edge is critical.

Figure 3.

Figure 3 also illustrates the use of a counter (74HC393) to derive the AD676 SAMPLE command from the system clock when a continuous convert mode is desirable. Pin 9 (2QC) provides a 96 kHz sample rate for the AD676 when used with a 12.288 MHz system clock. Alternately, Pin 8 (2QD) could be used for a 48 kHz rate.

If a continuous clock is used, then the user must avoid CLK edges at the instant of disconnecting  $V_{\rm IN}$  which occurs at the falling edge of SAMPLE (see  $t_{\rm SC}$  specification). The duty cycle of CLK may vary, but both the HIGH ( $t_{\rm CH}$ ) and LOW ( $t_{\rm CL}$ ) phases must conform to those shown in the timing specifications. The internal comparator makes its decisions on the rising edge of CLK. To avoid a negative edge transition disturbing the comparator's settling,  $t_{\rm CL}$  should be at least half the value of  $t_{\rm CLK}$ . To also avoid transitions disturbing the internal comparator's settling, it is not recommended that the SAMPLE pin change state toward the end of a CLK cycle.

During a conversion, internal dc error terms such as comparator voltage offset are sampled, stored on internal capacitors and used to correct for their corresponding errors when needed. Because these voltages are stored on capacitors, they are subject to leakage decay and so require refreshing. For this reason there is a maximum conversion time  $t_C$  (1000 µs). From the time SAMPLE goes HIGH to the completion of the 17th CLK pulse, no more than 1000 µs should elapse for specified performance. However, there is no restriction to the maximum time between conversions.

Output coding for the AD676 is twos complement, as shown in Table I. By inverting the MSB, the coding can be converted to offset binary. The AD676 is designed to limit output coding in the event of out-of-range inputs.

| V <sub>IN</sub>     | Output Code |

|---------------------|-------------|

| >Full Scale         | 01111       |

| Full Scale          | 01111       |

| Full Scale – 1 LSB  | 011 10      |

| Midscale + 1 LSB    | 00001       |

| Midscale            | 00000       |

| Midscale – 1 LSB    | 111 11      |

| –Full Scale + 1 LSB | 100 01      |

| -Full Scale         | 100 00      |

| <-Full Scale        | 100 00      |

Table I. Output Coding

#### POWER SUPPLIES AND DECOUPLING

The AD676 has three power supply input pins.  $V_{CC}$  and  $V_{EE}$  provide the supply voltages to operate the analog portions of the AD676 including the ADC and sample-hold amplifier (SHA).  $V_{\rm DD}$  provides the supply voltage which operates the digital portions of the AD676 including the data output buffers and the autocalibration controller.

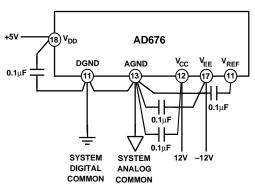

As with most high performance linear circuits, changes in the power supplies can produce undesired changes in the performance of the circuit. Optimally, well regulated power supplies with less than 1% ripple should be selected. The ac output impedance of a power supply is a complex function of frequency, and in general will increase with frequency. In other words, high frequency switching such as that encountered with digital circuitry requires fast transient currents which most power supplies cannot adequately provide. This results in voltage spikes on the supplies. If these spikes exceed the  $\pm 5\%$  tolerance of the  $\pm 12$  V supplies or the  $\pm 10\%$  limits of the +5 V supply, ADC performance will degrade. Additionally, spikes at frequencies higher than 100 kHz will also degrade performance. To compensate for the finite ac output impedance of the supplies, it is necessary to store "reserves" of charge in bypass capacitors. These capacitors can effectively lower the ac impedance presented to the AD676 power inputs which in turn will significantly reduce the magnitude of the voltage spikes. For bypassing to be effective, certain guidelines should be followed. Decoupling capacitors, typically 0.1 µF, should be placed as closely as possible to each power supply pin of the AD676. It is essential that these capacitors be placed physically close to the IC to minimize the inductance of the PCB trace between the capacitor and the supply pin. The logic supply (V<sub>DD</sub>) should be decoupled to digital common and the analog supplies (Vcc and V<sub>EE</sub>) to analog common. The reference input is also considered as a power supply pin in this regard and the same decoupling procedures apply. These points are displayed in Figure 4.

Figure 4. Grounding and Decoupling the AD676

Additionally, it is beneficial to have large capacitors (>47  $\mu$ F) located at the point where the power connects to the PCB with 10  $\mu$ F capacitors located in the vicinity of the ADC to further reduce low frequency ripple. In systems that will be subjected to particularly harsh environmental noise, additional decoupling may be necessary. RC-filtering on each power supply combined with dedicated voltage regulation can substantially decrease power supply ripple effects (this is further detailed in Figure 7).

#### **BOARD LAYOUT**

Designing with high resolution data converters requires careful attention to board layout. Trace impedance is a significant issue. A 1.22 mA current through a 0.5  $\Omega$  trace will develop a voltage drop of 0.6 mV, which is 4 LSBs at the 16-bit level for a 10 V full-scale span. In addition to ground drops, inductive and capacitive coupling need to be considered, especially when high accuracy analog signals share the same board with digital signals.

Analog and digital signals should not share a common return path. Each signal should have an appropriate analog or digital return routed close to it. Using this approach, signal loops enclose a small area, minimizing the inductive coupling of noise. Wide PC tracks, large gauge wire, and ground planes are highly recommended to provide low impedance signal paths. Separate analog and digital ground planes are also desirable, with a single interconnection point at the AD676 to minimize interference between analog and digital circuitry. Analog signals should be routed as far as possible from digital signals and should cross them, if at all, only at right angles. A solid analog ground plane around the AD676 will isolate it from large switching ground currents. For these reasons, the use of wire wrap circuit construction will not provide adequate performance; careful printed circuit board construction is preferred.

#### GROUNDING

The AD676 has three grounding pins, designated ANALOG GROUND (AGND), DIGITAL GROUND (DGND) and ANALOG GROUND SENSE (AGND SENSE). The analog ground pin is the "high quality" ground reference point for the device, and should be connected to the analog common point in the system.

AGND SENSE is intended to be connected to the input signal ground reference point. This allows for slight differences in level between the analog ground point in the system and the input signal ground point. However no more than 100 mV is recommended between the AGND and the AGND SENSE pins for specified performance. Using AGND SENSE to remotely sense the ground potential of the signal source can be useful if the signal has to be carried some distance to the A/D converter. Since all IC ground currents have to return to the power supply and no ground leads are free from resistance and inductance, there are always some voltage differences from one ground point in a system to another.

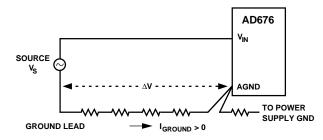

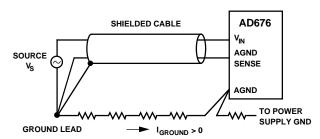

Over distance this voltage difference can easily amount to several LSBs (in a 10 V input span, 16-bit system each LSB is about 0.15 mV). This would directly corrupt the A/D input signal if the A/D measures its input with respect to power ground (AGND) as shown in Figure 5a. To solve this problem the AD676 offers an AGND SENSE pin. Figure 5b shows how the AGND SENSE can be used to eliminate the problem in Figure 5a. Figure 5b also shows how the signal wires should be shielded in a noisy environment to avoid capacitive coupling. If inductive (magnetic) coupling is expected to be dominant such as where motors are present, twisted-pair wires should be used instead.

The digital ground pin is the reference point for all of the digital signals that operate the AD676. This pin should be connected to the digital common point in the system. As Figure 4 illustrated, the analog and digital grounds should be connected together at one point in the system, preferably at the AD676.

Figure 5a. Input to the A/D Is Corrupted by IR Drop in Ground Leads:  $V_{IN} = V_S + \Delta V$

Figure 5b. AGND SENSE Eliminates the Problem in Figure 5a.

#### **VOLTAGE REFERENCE**

The AD676 requires the use of an external voltage reference. The input voltage range is determined by the value of the reference voltage; in general, a reference voltage of n volts allows an input range of  $\pm$ n volts. The AD676 is specified for both 10 V and 5.0 V references. A 10 V reference will typically require support circuitry operated from  $\pm$ 15 V supplies; a 5.0 V reference may be used with  $\pm$ 12 V supplies. Signal-to-noise performance is increased proportionately with input signal range. In the presence of a fixed amount of system noise, increasing the LSB size (which results from increasing the reference voltage) will increase the effective S/(N+D) performance. Figure 12 illustrates S/(N+D) as a function of reference voltage. In contrast, INL will be optimal at lower reference voltage values (such as 5 V) due to capacitor nonlinearity at higher voltage values.

During a conversion, the switched capacitor array of the AD676 presents a dynamically changing current load at the voltage reference as the successive-approximation algorithm cycles through various choices of capacitor weighting. (See the following section "Analog Input" for a detailed discussion of the  $V_{REF}$  input characteristics.) The output impedance of the reference circuitry must be low so that the output voltage will remain sufficiently constant as the current drive changes. In some applications, this may require that the output of the voltage reference be buffered by an amplifier with low impedance at relatively high frequencies. In choosing a voltage reference, consideration should be made for selecting one with low noise. A capacitor connected between REF IN and AGND will reduce the demands on the reference by decreasing the magnitude of high frequency components required to be sourced by the reference.

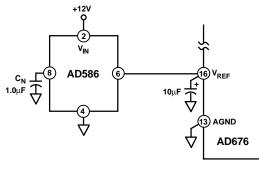

Figures 6 and 7 represent typical design approaches.

#### Figure 6.

Figure 6 shows a voltage reference circuit featuring the 5 V output AD586. The AD586 is a low cost reference which utilizes a buried Zener architecture to provide low noise and drift. Over the 0°C to +70°C range, the AD586L grade exhibits less than 2.25 mV output change from its initial value at +25°C. A noise-reduction capacitor,  $C_N$ , reduces the broadband noise of the

AD586 output, thereby optimizing the overall performance of the AD676. It is recommended that a 10  $\mu$ F to 47  $\mu$ F high quality tantalum capacitor be tied between the V<sub>REF</sub> input of the AD676 and ground to minimize the impedance on the reference.

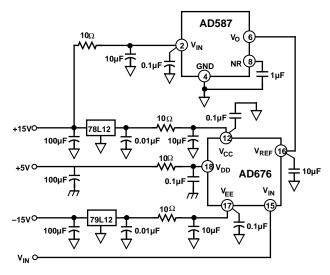

#### Figure 7.

Using the AD676 with  $\pm 10$  V input range (V<sub>REF</sub> = 10 V) typically requires  $\pm 15$  V supplies to drive op amps and the voltage reference. If  $\pm 12$  V is not available in the system, regulators such as 78L12 and 79L12 can be used to provide power for the AD676. This is also the recommended approach (for any input range) when the ADC system is subjected to harsh environments such as where the power supplies are noisy and where voltage spikes are present. Figure 7 shows an example of such a system based upon the 10 V AD587 reference, which provides a 300 µV LSB. Circuitry for additional protection against power supply disturbances has been shown. A 100 µF capacitor at each regulator prevents very large voltage spikes from entering the regulators. Any power line noise which the regulators cannot eliminate will be further filtered by an RC filter (10  $\Omega/10 \mu$ F) having a -3 dB point at 1.6 kHz. For best results the regulators should be within a few centimeters of the AD676.

#### ANALOG INPUT

As previously discussed, the analog input voltage range for the AD676 is  $\pm V_{REF}$ . For purposes of ground drop and common mode rejection, the  $V_{IN}$  and  $V_{REF}$  inputs each have their own ground.  $V_{REF}$  is referred to the local analog system ground (AGND), and  $V_{IN}$  is referred to the analog ground sense pin (AGND SENSE) which allows a remote ground sense for the input signal.

The AD676 analog inputs (V<sub>IN</sub>, V<sub>REF</sub> and AGND SENSE) exhibit dynamic characteristics. When a conversion cycle begins, each analog input is connected to an internal, discharged 50 pF capacitor which then charges to the voltage present at the corresponding pin. The capacitor is disconnected when SAMPLE is taken LOW, and the stored charge is used in the subsequent conversion. In order to limit the demands placed on the external source by this high initial charging current, an internal buffer amplifier is employed between the input and this capacitance for a few hundred nanoseconds. During this time the input pin exhibits typically 20 k $\Omega$  input resistance, 10 pF input capacitance and  $\pm 40 \ \mu$ A bias current. Next, the input is switched directly to the now precharged capacitor and allowed to fully settle. During this time the input sees only a 50 pF capacitor. Once the sample is taken, the input is internally floated so that the external input source sees a very high input resistance and a parasitic input capacitance of typically only 2 pF. As a result, the only dominant input characteristic which must be considered is the high current steps which occur when the internal buffers are switched in and out.

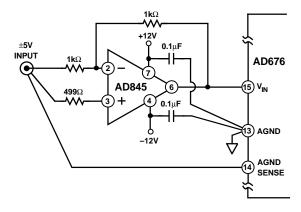

In most cases, these characteristics require the use of an external op amp to drive the input of the AD676. Care should he taken with op amp selection; even with modest loading conditions, most available op amps do not meet the low distortion requirements necessary to match the performance capabilities of the AD676. Figure 8 represents a circuit, based upon the AD845, recommended for low noise, low distortion ac applications.

For applications optimized more for low bias and low offset than speed or bandwidth, the AD845 of Figure 8 may be replaced by the OP27.

Figure 8.

#### AC PERFORMANCE

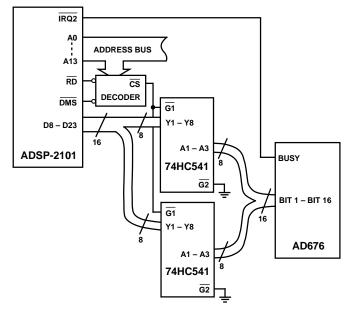

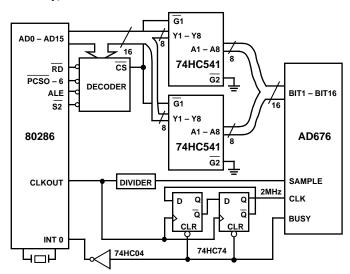

AC parameters, which include S/(N+D), THD, etc., reflect the AD676's effect on the spectral content of the analog input signal. Figures 12 through 16 provide information on the AD676's ac performance under a variety of conditions.

As a general rule, averaging the results from several conversions reduces the effects of noise, and therefore improves such parameters as S/(N+D). AD676 performance may be optimized by operating the device at its maximum sample rate of 100 kSPS and digitally filtering the resulting bit stream to the desired signal bandwidth. This succeeds in distributing noise over a wider frequency range, thus reducing the noise density in the frequency band of interest. This subject is discussed in the following section.

#### **OVERSAMPLING AND NOISE FILTERING**

The Nyquist rate for a converter is defined as one-half its sampling rate. This is established by the Nyquist theorem, which requires that a signal he sampled at a rate corresponding to at least twice its highest frequency component of interest in order to preserve the informational content. Oversampling is a conversion technique in which the sampling frequency is more than twice the frequency bandwidth of interest. In audio applications, the AD676 can operate at a  $2 \times F_S$  oversampling rate, where  $F_S = 48$  kHz.

In quantized systems, the informational content of the analog input is represented in the frequency spectrum from dc to the Nyquist rate of the converter. Within this same spectrum are higher frequency noise and signal components. Antialias, or low pass, filters are used at the input to the ADC to reduce these noise and signal components so that their aliased components do not corrupt the baseband spectrum. However, wideband noise contributed by the AD676 will not be reduced by the antialias filter. The AD676 quantization noise is evenly distributed from dc to the Nyquist rate, and this fact can be used to minimize its overall affect.