# 8031AH/8051AH 8032AH/8052AH MCS® 51

# NMOS SINGLE-CHIP 8-BIT MICROCONTROLLERS

Automotive

- High Performance HMOS Process

- Internal Timers/Event Counters

- 2-Level Interrupt Priority Structure

- 32 I/O Lines (Four 8-Bit Ports)

- 64K Program Memory Space

- Security Feature Protects EPROM Parts Against Software Piracy

- Bit-Addressable RAM

- Programmable Full Duplex Serial Channel

- 111 Instructions (64 Single-Cycle)

- 64K Data Memory Space

- Available in PLCC and DIP Packages

Boolean Processor

The MCS<sup>®</sup> 51 microcontroller products are optimized for control applications. Byte-processing and numerical operations on small data structures are facilitated by a variety of fast addressing modes for accessing the internal RAM. The instruction set provides a convenient menu of 8-bit arithmetic instructions, including multiply and divide instructions. Extensive on-chip support is provided for one-bit variables as a separate data type, allowing direct bit manipulation and testing in control and logic systems that require Boolean processing.

| Device | Internal Memory |             | Timers/        | Interrupts |  |

|--------|-----------------|-------------|----------------|------------|--|

| Bettee | Program         | Data        | Event Counters | monupto    |  |

| 8052AH | 8K x 8 ROM      | 256 x 8 RAM | 3 x 16-Bit     | 6          |  |

| 8051AH | 4K x 8 ROM      | 128 x 8 RAM | 2 x 16-Bit     | 5          |  |

| 8032AH | none            | 256 x 8 RAM | 3 x 16-Bit     | 6          |  |

| 8031AH | none            | 128 x 8 RAM | 2 x 16-Bit     | 5          |  |

### NOTICE:

This datasheet contains information on products in full production. Specifications within this datasheet are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1995 February 1995

# **PRODUCT OPTIONS**

Intel's extended and automotive temperature range products are designed to meet the needs of those applications whose operating requirements exceed commercial standards.

With the commercial standard temperature range, operational characteristics are guaranteed over the temperature range of 0°C to +70°C ambient. With

the extended temperature range option, operational characteristics are guaranteed over the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient. For the automotive temperature range option, operational characteristics are guaranteed over the temperature range of  $-40^{\circ}$ C to  $+110^{\circ}$ C ambient.

The automotive, extended, and commercial temperature versions of the MCS 51 microcontroller product families are available with or without burn-in options.

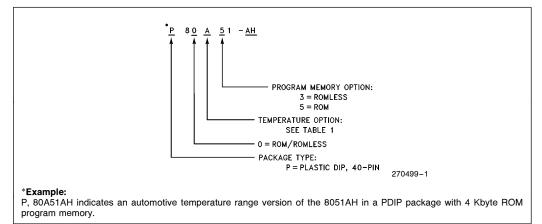

Figure 1. MCS® 51 Microcontroller Product Family Nomenclature

| Temperature<br>Classification | Temperature<br>Designation | Operating<br>Temperature<br>°C Ambient | Burn-In<br>Option |  |

|-------------------------------|----------------------------|----------------------------------------|-------------------|--|

| Extended                      | Т                          | -40 to +85                             | Standard          |  |

|                               | L                          | -40 to +85                             | Extended          |  |

| Automotive                    | А                          | -40 to +110                            | Standard          |  |

## Table 1. Temperature Options

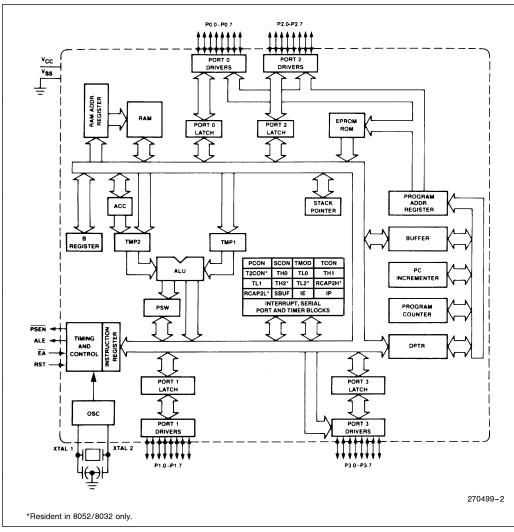

Figure 2. MCS® 51 Microcontroller Block Diagram

# **PIN DESCRIPTIONS**

# V<sub>CC</sub>

Supply voltage.

intel

# VSS

Circuit ground.

# Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink 8 LS TTL inputs.

Port 0 pins that have 1s written to them float, and in that state can be used as high-impedance inputs.

Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pullups when emitting 1s and can source and sink 8 LS TTL inputs.

Port 0 also outputs the code bytes during program verification of the ROM. External pullups are required.

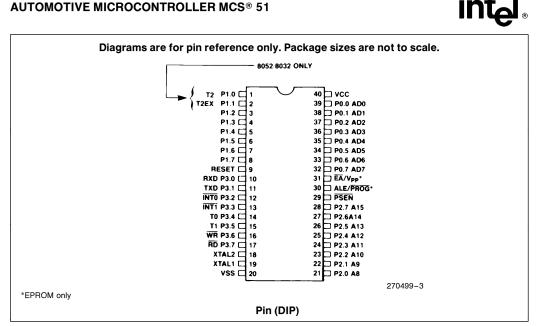

Figure 3. MCS<sup>®</sup> 51 Microcontroller Connections

## Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source 4 LS TTL inputs. Port 1 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current (IIL on the datasheet) because of the internal pullups.

Port 1 also receives the low-order address bytes during program verification of the ROM.

In the 8032AH and 8052AH, Port 1 pins P1.0 and P1.1 also serve the T2 and T2EX functions, respectively.

## Port 2

Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source 4 LS TTL inputs. Port 2 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current (IIL on the datasheet) because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external Program Memory and during accesses to external Data Memory that use 16-bit addresses (MOVX @DPTR). In this application it uses strong internal pullups when emitting 1s. During accesses to external Data Memory that use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits during program verification of the ROM.

### Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source 4 LS TTL inputs. Port 3 pins that have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current (III on the datasheet) because of the pullups.

Port 3 also serves the functions of various special features of the MCS 51 microcontroller family, as listed below:

| Port<br>Pin | Alternative Function                   |

|-------------|----------------------------------------|

| P3.0        | RXD (serial input port)                |

| P3.1        | TXD (serial output port)               |

| P3.2        | INTO (external interrupt 0)            |

| P3.3        | INT1 (external interrupt 1)            |

| P3.4        | T0 (Timer 0 external input)            |

| P3.5        | T1 (Timer 1 external input)            |

| P3.6        | WR (external data memory write strobe) |

| P3.7        | RD (external data memory read strobe)  |

# RESET

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

# ALE/PROG

Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory.

In normal operation ALE is emitted at a constant rate of  $\frac{1}{6}$  the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

# **PSEN**

Program Store Enable is the read strobe to external Program Memory.

When the device is executing code from external Program Memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external Data Memory.

# EA/V<sub>PP</sub>

External Access enable  $\overline{\text{EA}}$  must be strapped to V<sub>SS</sub> in order to enable any MCS 51 microcontroller device to fetch code from external Program memory locations 0 to 0FFFH (0 to 1FFFH, in the 8032AH and 8052AH).

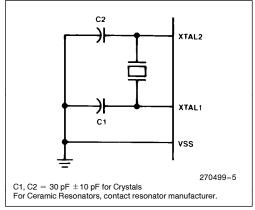

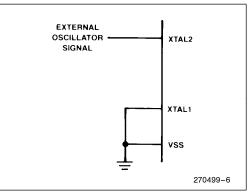

Figure 4. Oscillator Connections

# **AUTOMOTIVE MICROCONTROLLER MCS® 51**

# XTAL1

Input to the inverting oscillator amplifier.

# XTAL2

Output from the inverting oscillator amplifier.

# **OSCILLATOR CHARACTERISTICS**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 4. Either a quartz crystal or ceramic resonator may be used. More detailed information concerning the use of the on-chip oscillator is available in Application Note AP-155, "Oscillators for Microcontrollers."

To drive the device from an external clock source, XTAL1 should be grounded, while XTAL2 is driven, as shown in Figure 5. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the datasheet must be observed.

Figure 5. External Drive Configuration

# **ABSOLUTE MAXIMUM RATINGS\***

### Ambient Temperature

NOTICE: This is a production data sheet. The specifications are subject to change without notice. \*WARNING: Stressing the device beyond the "Absolute

Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### Maximum Case Temperature

Under Bias ......+ 125°C

## Typical Thermal Resistance Junction to Ambient ( $\theta_{JA}$ )

| Package     | $\theta_{JA}$ |

|-------------|---------------|

| Plastic DIP | 75°C/W        |

## DC CHARACTERISTICS $T_A = -40^{\circ}C$ to $+110^{\circ}C$ ; $V_{CC} = 5V \pm 10^{\circ}$ ; $V_{SS} = 0V$

| Symbol           | Parameter                                                                    | Min  | Max                   | Units          | Test Conditions                      |

|------------------|------------------------------------------------------------------------------|------|-----------------------|----------------|--------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                                            | -0.5 | 0.7                   | V              |                                      |

| V <sub>IH</sub>  | Input High Voltage (Except XTAL2, RST)                                       | 2.1  | V <sub>CC</sub> + 0.5 | V              |                                      |

| V <sub>IH1</sub> | Input High Voltage to XTAL2, RST                                             | 2.6  | $V_{CC} + 0.5$        | V              | $XTAL1 = V_{SS}$                     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3)*                                          |      | 0.45                  | V              | $I_{OL} = 1.6 \text{ mA}$            |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE, PSEN)*                                      |      | 0.45                  | V              | $I_{OL} = 3.2 \text{ mA}$            |

| V <sub>OH</sub>  | Output High Voltage (Ports 1, 2, 3, ALE, PSEN)                               | 2.4  |                       | V              | $I_{OH} = -80 \ \mu A$               |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in<br>External Bus Mode)                         | 2.4  |                       | V              | $I_{OH} = -400 \ \mu A$              |

| I <sub>IL</sub>  | Logical 0 Input Current (Ports 1, 2, 3,<br>RST) 8032AH, 8052AH<br>All Others |      | 800<br>500            | μΑ<br>μΑ       | $V_{IN} = 0.45V$<br>$V_{IN} = 0.45V$ |

| I <sub>IL2</sub> | Logical 0 Input Current (XTAL2)                                              |      | -4.0                  | mA             | $V_{IN} = 0.45V$                     |

| ILI              | Input Leakage Current (Port 0)                                               |      | ±10                   | μΑ             | $0.45 \leq V_{IN} \leq V_{CC}$       |

| l <sub>IH1</sub> | Input Current to RST to Activate Reset                                       |      | 500                   | μΑ             | $V_{\rm IN} < (V_{\rm CC} - 1.5V)$   |

| ICC              | Power Supply Current:<br>8031/8051<br>8031AH/8051AH<br>8032AH/8052AH         |      | 175<br>135<br>175     | mA<br>mA<br>mA | All Outputs<br>Disconnected;         |

| C <sub>IO</sub>  | Pin Capacitance                                                              |      | 10                    | pF             | Test freq = 1 MHz                    |

## \*NOTE:

Capacitive loading on Ports 0 and 2 may cause noise pulses to be superimposed on the VOLs of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE line may exceed 0.8V. In such cases it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

# **AUTOMOTIVE MICROCONTROLLER MCS® 51**

# AC CHARACTERISTICS $T_A = -40^\circ C \text{ to } +110^\circ C; V_{CC} = 5V \pm 10\%; V_{SS} = 0V;$ Load Capacitance for Port 0, ALE, and PSEN = 100 pF; Load Capacitance for All Other Outputs = 80 pF

| Symbol              | Parameter                                           | 12 MHz Oscillator |     | Variable                | Units                   |       |

|---------------------|-----------------------------------------------------|-------------------|-----|-------------------------|-------------------------|-------|

| Symbol              | Farameter                                           | Min               | Max | Min                     | Max                     | Units |

| 1/T <sub>CLCL</sub> | Oscillator Frequency                                |                   |     | 3.5                     | 12.0                    | MHz   |

| T <sub>LHLL</sub>   | ALE Pulse Width                                     | 127               |     | 2T <sub>CLCL</sub> -40  |                         | ns    |

| T <sub>AVLL</sub>   | Address Valid to ALE Low                            | 43                |     | T <sub>CLCL</sub> -40   |                         | ns    |

| T <sub>LLAX</sub>   | Address Hold after ALE Low                          | 48                |     | T <sub>CLCL</sub> -35   |                         | ns    |

| T <sub>LLIV</sub>   | ALE Low to Valid Instr In                           |                   | 233 |                         | 4T <sub>CLCL</sub> -100 | ns    |

| T <sub>LLPL</sub>   | ALE Low to PSEN Low                                 | 58                |     | T <sub>CLCL</sub> -25   |                         | ns    |

| T <sub>PLPH</sub>   | PSEN Pulse Width                                    | 215               |     | 3T <sub>CLCL</sub> -35  |                         | ns    |

| T <sub>PLIV</sub>   | PSEN Low to Valid Instr In                          |                   | 125 |                         | 3T <sub>CLCL</sub> -125 | ns    |

| T <sub>PXIX</sub>   | Input Instr Hold after PSEN                         | 0                 |     | 0                       |                         | ns    |

| T <sub>PXIZ</sub>   | Input Instr Float after PSEN                        |                   | 63  |                         | T <sub>CLCL</sub> -20   | ns    |

| T <sub>PXAV</sub>   | PSEN to Address Valid                               | 75                |     | T <sub>CLCL</sub> -8    |                         | ns    |

| T <sub>AVIV</sub>   | Address to Valid Instr In                           |                   | 302 |                         | 5T <sub>CLCL</sub> -115 | ns    |

| T <sub>PLAZ</sub>   | PSEN Low to Address Float                           |                   | 20  |                         | 20                      | ns    |

| T <sub>RLRH</sub>   | RD Pulse Width                                      | 400               |     | 6T <sub>CLCL</sub> -100 |                         | ns    |

| T <sub>WLWH</sub>   | WR Pulse Width                                      | 400               |     | 6T <sub>CLCL</sub> -100 |                         | ns    |

| T <sub>RLDV</sub>   | RD Low to Valid Data In                             |                   | 252 |                         | 5T <sub>CLCL</sub> -165 | ns    |

| T <sub>RHDX</sub>   | Data Hold after RD High                             | 0                 |     | 0                       |                         | ns    |

| T <sub>RHDZ</sub>   | Data Float after RD High                            |                   | 97  |                         | 2T <sub>CLCL</sub> -70  | ns    |

| T <sub>LLDV</sub>   | ALE Low to Valid Data In                            |                   | 517 |                         | 8T <sub>CLCL</sub> -150 | ns    |

| T <sub>AVDV</sub>   | Address to Valid Data In                            |                   | 585 |                         | 9T <sub>CLCL</sub> -165 | ns    |

| T <sub>LLWL</sub>   | ALE Low to $\overline{RD}$ or $\overline{WR}$ Low   | 200               | 300 | 3T <sub>CLCL</sub> -50  | 3T <sub>CLCL</sub> +50  | ns    |

| T <sub>AVWL</sub>   | Address to $\overline{RD}$ or $\overline{WR}$ Low   | 203               |     | 4T <sub>CLCL</sub> -130 |                         | ns    |

| T <sub>QVWX</sub>   | Data Valid to WR Transition                         | 23                |     | T <sub>CLCL</sub> -60   |                         | ns    |

| T <sub>QVWH</sub>   | Data Valid to WR High                               | 433               |     | 7T <sub>CLCL</sub> -150 |                         | ns    |

| T <sub>WHQX</sub>   | Data Hold after WR High                             | 33                |     | T <sub>CLCL</sub> -50   |                         | ns    |

| T <sub>RLAZ</sub>   | RD Low to Address Float                             |                   | 20  |                         | 20                      | ns    |

| T <sub>WHLH</sub>   | $\overline{RD}$ or $\overline{WR}$ High to ALE High | 43                | 123 | T <sub>CLCL</sub> -40   | T <sub>CLCL</sub> +40   | ns    |

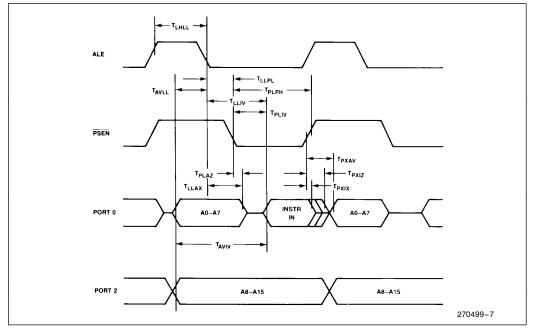

# EXTERNAL PROGRAM MEMORY READ CYCLE

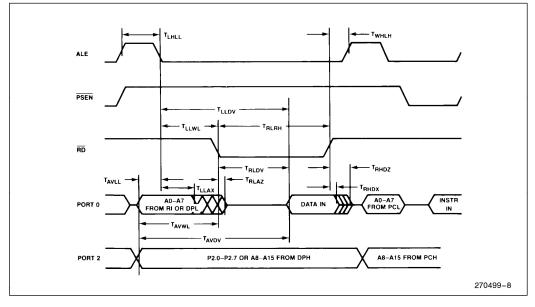

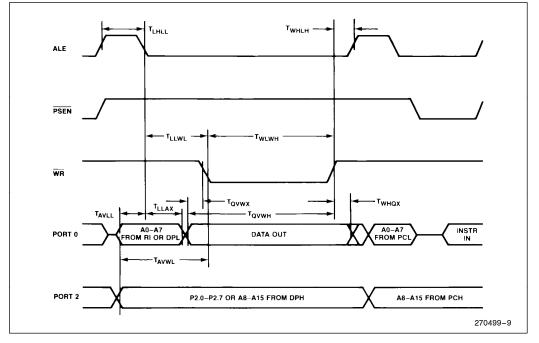

## EXTERNAL DATA MEMORY READ CYCLE

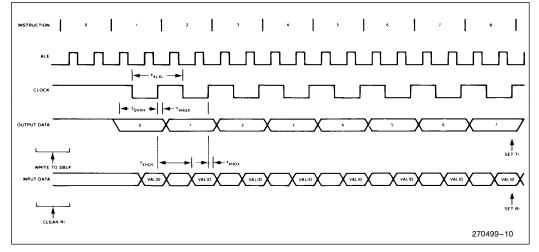

**SERIAL PORT TIMING—SHIFT REGISTER MODE** Test Conditions:  $T_A = -40^{\circ}C$  to  $+110^{\circ}C$ ;  $V_{CC} = 5V \pm 10\%$ ;  $V_{SS} = 0V$ ; Load Capacitance = 80 pF

| Symbol            | Parameter                                   | 12 MHz Oscillator |     | Variable Oscillator      |                          | Units |

|-------------------|---------------------------------------------|-------------------|-----|--------------------------|--------------------------|-------|

|                   | i arameter                                  | Min               | Max | Min                      | Max                      | Onits |

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time                | 1.0               |     | 12T <sub>CLCL</sub>      |                          | μs    |

| Τ <sub>QVXH</sub> | Output Data Setup to Clock Rising<br>Edge   | 700               |     | 10T <sub>CLCL</sub> -133 |                          | ns    |

| T <sub>XHQX</sub> | Output Data Hold after Clock<br>Rising Edge | 50                |     | 2T <sub>CLCL</sub> -117  |                          | ns    |

| T <sub>XHDX</sub> | Input Data Hold after Clock Rising<br>Edge  | 0                 |     | 0                        |                          | ns    |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data<br>Valid    |                   | 700 |                          | 10T <sub>CLCL</sub> -133 | ns    |

## SHIFT REGISTER TIMING WAVEFORMS

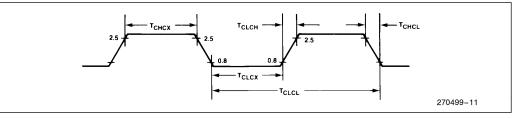

# EXTERNAL CLOCK DRIVE

| Symbol              | Parameter            | Min | Max | Units |

|---------------------|----------------------|-----|-----|-------|

| 1/T <sub>CLCL</sub> | Oscillator Frequency | 3.5 | 12  | MHz   |

| T <sub>CHCX</sub>   | High Time            | 20  |     | ns    |

| T <sub>CLCX</sub>   | Low Time             | 20  |     | ns    |

| T <sub>CLCH</sub>   | Rise Time            |     | 20  | ns    |

| T <sub>CHCL</sub>   | Fall Time            |     | 20  | ns    |

## EXTERNAL CLOCK DRIVE WAVEFORMS

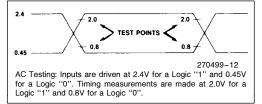

## AC TESTING INPUT, OUTPUT WAVEFORMS

# intel

# DATASHEET REVISION HISTORY

The following are key differences between this datasheet and the -005 version:

- 1. The "preliminary" status was dropped and replaced with production status (no label).

- 2. Trademarks were updated.

The following are key differences between the -005 and the -004 version of the datasheet:

- 1. Preliminary notice was placed on the title page.

- 2. Figure 2. MCS 51 Block Diagram was modified to include the note found at the bottom of the figure.

- 3. RST pin in Figure 3 was changed to RESET.

- 4. RST pin description was changed to RESET pin description.

- 5. Power dissipation note added below Power dissipation listing in Absolute Maximum Ratings.

- 6.  $V_{IH}$  and  $V_{IH1}$  were changed by 0.1V to reflect test conditions.

- 7. T<sub>PLPH</sub> was corrected to show test program timing.

The following are key differences between the -004 datasheet and the -003 version of the datasheet:

- The title was changed to 8031AH/8051AH, 8032AH/8052AH MCS 51 NMOS Single-Chip 8-Bit Microcontrollers.

- 2. "NC" pin labels changed to "Reserved" in Figure 3.

- 3. Capacitor value for ceramic resonators deleted in Figure 4.

The following are key differences between the -001 and the -002 version of the datasheet:

- 1. The title was changed to 8031/8051, 8031AH/8051AH, 8032AH/8052AH, 8751H MCS 51 NMOS Single-Chip 8-Bit Microcontrollers.

- 2. Removed 8751H-8 from the datasheet.

- 3. Removed reference to LCC package version.

- 4. Removed burn-in options from Table 1.

- 5. Added pin count to Figure 1.

- 6. Test conditions for  $I_{IL1}$  and  $I_{IH}$  specifications added to the DC Characteristics.

- 7. Datasheet revision history added.

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

# Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

# http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

# Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9