# L9780

## Wide range air fuel sensor control interface

- 2 channels available to connect compensation networks

- Short to battery diagnostic on functional ground (pin SR)

- Short to battery/ground diagnostic on voltage from reference cell (pin INRC)

- -5 V internal supply

- 4 MHz internal oscillator

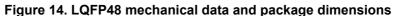

- Package: 48 pin LQFP

- Technology: BCD5s\_70 V

## Description

L9780 is an IC designed to interface a variety of wide range air fuel sensors.

The device manages the oxygen pump of the wide range air fuel sensor by means of a voltage controlled current source (VCCS). The reference for the VCCS is generated by a PI controller with external compensation network in order to adapt the device to different sensors. The user can choose between two different networks using the SPI interface. L9780 is fully compatible with most sensors on the market.

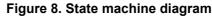

The internal timing state machine automatically manages all the operations needed for a right sequencing of the measurement process. All the main time values can be configured by SPI.

L9780 drives also an external FET used to control the sensor heater. The device protects the sensor and all the I/O against shorts and provides the diagnosis by SPI.

#### Table 1. Device summary

| Order code | Package | Packing       |

|------------|---------|---------------|

| L9780      | LQFP48  | Tray          |

| L9780TR    | LQFP48  | Tape and reel |

#### November 2014

DocID026356 Rev 3

This is information on a product in full production.

## Features

- Voltage controlled current source (VCCS) pump cell driver with selectable voltage clamp, offset compensation, diagnostic (short to battery) and 2 output channels

- Impedance measurement of reference cell

- 10-bit multiplexed A/D converter

- Scaling amplifier with sample & hold and offset compensation

- Control voltage amplifier with sample & hold and offset compensation

- Synchronous or asynchronous functionality selectable via SPI

- Heater FET driver with diagnostic (short to battery, short to ground, open circuit)

- 4 possible levels for clean current

- SPI with fault detection

- Digital input and outputs compatible with 5 V or 3.3 V voltage supply

1/56

## Contents

| 1 | Pin d | lescription                                                                        | 7    |

|---|-------|------------------------------------------------------------------------------------|------|

| 2 | Oper  | ating conditions                                                                   | 9    |

|   | 2.1   | Maximum ratings                                                                    | 9    |

|   | 2.2   | Absolute maximum ratings                                                           | 9    |

|   | 2.3   | Operating temperature range                                                        | . 10 |

| 3 | Bloc  | k diagram                                                                          | . 11 |

| 4 | Main  | functionalities                                                                    | . 12 |

|   | 4.1   | Power supplies                                                                     | . 12 |

|   | 4.2   | Pin protection                                                                     | . 12 |

|   | 4.3   | Internal references                                                                | . 12 |

|   | 4.4   | Power on reset                                                                     | . 13 |

|   | 4.5   | Pin INRC functionalities: INRC amplifier, clean currents, pull-down current        | 13   |

|   | 4.6   | Pin RCT1 – RCT2 functionalities: RCT2 amplifier, RCT1 switch, RCT1 band-gap switch | . 14 |

|   | 4.7   | Pin C1A, C2A, C1B, C2B, C3 functionalities: compensation network connection        | . 14 |

|   | 4.8   | Pin FV, FVOUT functionalities: FVOUT amplifier                                     | . 15 |

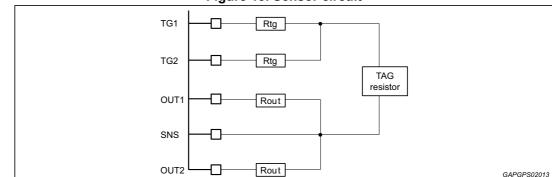

|   | 4.9   | Pin TG1, TG2, OUT1, OUT2, SNS functionalities: the VCCS                            | . 15 |

|   | 4.10  | Pin PG1, PG2, SR functionalities                                                   | . 20 |

|   | 4.11  | Analog to digital conversion                                                       | . 21 |

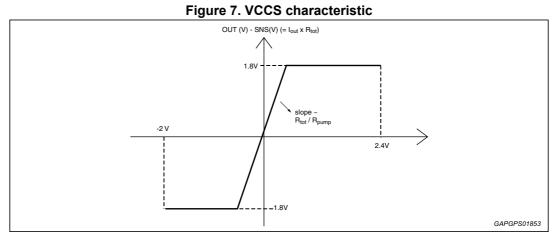

|   | 4.12  | Timing state machine                                                               | . 22 |

|   | 4.13  | Pin HD, HG functionalities: heater FET driver and diagnostic                       | . 25 |

| 5 | Diag  | nostic                                                                             | . 26 |

|   | 5.1   | Sensor short to battery                                                            | . 26 |

|   |       | Actions                                                                            |      |

|   | 5.2   | INRC pin short to ground                                                           |      |

|   |       | Actions                                                                            |      |

|   | 5.3   | SNS pin short to ground                                                            |      |

|   |       | Actions                                                                            |      |

|   | 5.4   | Application note                                                                   |      |

|   | 0.4   | 5.4.1   Heater short to battery                                                    |      |

|   |       | 0.4.1 FIEdler Shull to ballery                                                     | . 20 |

L9780

| L978 | 0 |

|------|---|

|------|---|

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                           |

|---|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   |       | 5.4.2    | Heater short to ground                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                                           |

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                           |

|   |       | 5.4.3    | Heater open circuit                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                           |

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                           |

|   | 5.5   | SPI dia  | agnostic                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                           |

|   |       | 5.5.1    | SPI data fault                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                           |

|   |       | 5.5.2    | SPI length fault                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                           |

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|   |       | 5.5.3    | SPI not valid command fault                                                                                                                                                                                                                                                                                                                                                                    | 30                                                                                           |

|   |       |          | Actions                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                           |

|   | 5.6   | Loss o   | of ground                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                           |

|   |       |          |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 6 | Digit | al inter | face description                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                           |

|   | 6.1   | CSN      |                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                                           |

|   | 6.2   | CLK      |                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                                           |

|   | 6.3   | SI       |                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                                           |

|   |       | 6.3.1    | SPI input register                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|   |       |          | Bit 63 – 60:                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|   |       |          | Bit 59: REG                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|   |       |          |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

|   |       |          | Bit 58: INRCPD.                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

|   |       |          |                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                                           |

|   |       |          | Bit 58: INRCPD                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|   |       |          | Bit 58: INRCPD<br>Bit 57: STGINRC                                                                                                                                                                                                                                                                                                                                                              | 33<br>33<br>33                                                                               |

|   |       |          | Bit 58: INRCPD<br>Bit 57: STGINRC<br>Bit 56: INRCGAIN                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.                                                                                                                                                                                                                                                        |                                                                                              |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD                                                                                                                                                                                                                                 | 33<br>33<br>33<br>33<br>33<br>34<br>34                                                       |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD.         Bit 51: COMPSEL.                                                                                                                                                                                                       | 33<br>33<br>33<br>33<br>33<br>34<br>34<br>34                                                 |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN                                                                                                                                                                                | 33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>35                                     |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN.         Bit 49: CLAMPCL                                                                                                                                                       | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>35<br>35                                     |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN         Bit 48: CLAMPSIM                                                                                                                                                       | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35                                     |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN.         Bit 49: CLAMPCL         Bit 47: CLEARFLT                                                                                                                              | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35                               |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN         Bit 49: CLAMPCL         Bit 48: CLAMPSIM         Bit 47: CLEARFLT         Bit 46 - 43: CCS[30]                                                                         | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>35                         |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN         Bit 49: CLAMPCL         Bit 48: CLAMPSIM         Bit 46 - 43: CCS[30]         Bit 42 - 40: SAMP[20].                                                                   | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>35<br>36<br>36             |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN         Bit 49: CLAMPCL         Bit 42: CLAMPSIM         Bit 42: CLAMPSIM         Bit 42: A0: SAMP[2.0]         Bit 39 - 34: VCCSCAP[50]                 | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>36<br>36<br>36             |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN         Bit 49: CLAMPCL         Bit 48: CLAMPSIM         Bit 46 - 43: CCS[30]         Bit 42 - 40: SAMP[20].                                                                   | 33<br>33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>36<br>36<br>36<br>36       |

|   |       |          | Bit 58: INRCPD.         Bit 57: STGINRC         Bit 56: INRCGAIN.         Bit 55: TGEN.         Bit 54: VCCSEN         Bit 53: VCCSOUT.         Bit 52: VCCSPD         Bit 51: COMPSEL.         Bit 50: CLAMPEN.         Bit 49: CLAMPCL         Bit 48: CLAMPSIM         Bit 46 - 43: CCS[3.0]         Bit 42 - 40: SAMP[2.0]         Bit 39 - 34: VCCSCAP[5.0]         Bit 33 - 32: MCP[1.0] | 33<br>33<br>33<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>35<br>36<br>36<br>36<br>36<br>37 |

|    |          |           | Bit 22 - 16: CBT[60]                           |    |

|----|----------|-----------|------------------------------------------------|----|

|    |          |           | Bit 15 - 14: CB[10]                            |    |

|    |          |           | Bit 13:                                        |    |

|    |          |           | Bit 12 - 11: STBHFT[10]                        |    |

|    |          |           | Bit 10 - 8: ISPT[20]                           |    |

|    |          |           | Bit 7: PG2EN                                   |    |

|    |          |           | Bit 6: PG1EN                                   |    |

|    |          |           | Bit 5 – 0:                                     |    |

|    | 6.4      | SO        |                                                | 39 |

|    |          | 6.4.1     | SPI output register (status configuration)     |    |

|    |          |           | Bit 63:                                        |    |

|    |          |           | Bit 59: REG                                    |    |

|    |          |           | Bit 58:                                        |    |

|    |          |           | Bit 57 - 48: RCAMP[90]                         |    |

|    |          |           | Bit 47 - 45: COUNT[20]                         |    |

|    |          |           | Bit 44 - 42: STBS[31]                          |    |

|    |          |           | Bit 41 - 32: FV[90]                            |    |

|    |          |           | Bit 31 - 30: CB[10]                            |    |

|    |          |           | Bit 29 - 28: SPIF[12]                          |    |

|    |          |           | Bit 27 - 26:                                   |    |

|    |          |           | Bit 25 - 16: RCIMP1_[90]                       |    |

|    |          |           | Bit 15: STGSNS                                 |    |

|    |          |           | Bit 14: CLAMP                                  |    |

|    |          |           | Bit 13: OCH                                    |    |

|    |          |           | Bit 12: STBH                                   |    |

|    |          |           | Bit 11: STGH.                                  |    |

|    |          |           | Bit 10: STGRC                                  | 41 |

|    |          |           | Bit 9 - 0: RCIMP2_[90]                         | 41 |

|    |          | 6.4.2     | SPI output register (input echo configuration) | 42 |

|    |          |           | Bit 63 – 0:                                    |    |

|    |          |           |                                                |    |

| 7  | Elec     | trical ch | haracteristics                                 | 43 |

|    | 7.1      | DC cha    | aracteristics                                  | 43 |

|    | 7.2      | AC cha    | aracteristics                                  | 49 |

| 0  | <b>A</b> |           |                                                | 50 |

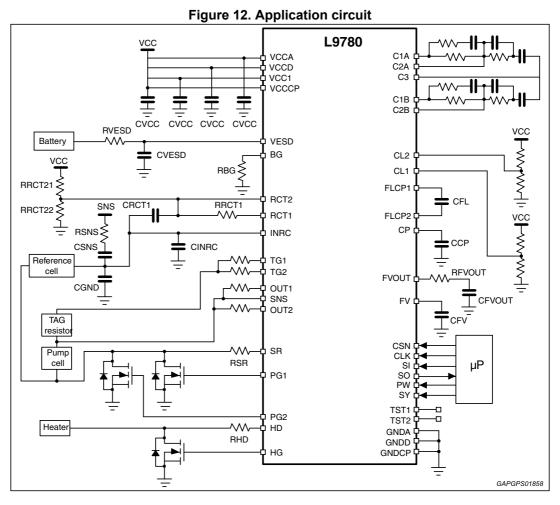

| 8  | App      | lication  |                                                |    |

|    |          |           | Sensors value:                                 |    |

| 9  | Pack     | kage inf  | formation                                      | 54 |

|    |          |           |                                                |    |

| 10 | Revi     | sion his  | story                                          | 55 |

|    |          |           |                                                |    |

|    |          |           |                                                |    |

DocID026356 Rev 3

7

8

9

# List of tables

| Device summary                                                                           | . 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin function                                                                             | . 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Maximum ratings.                                                                         | . 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Absolute maximum ratings                                                                 | . 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operating temperature range                                                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C <sub>int</sub> vs. possible R <sub>tot</sub> to guarantee phase margin and bandwidth   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Silicon version bits                                                                     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPI data fault                                                                           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Supplies and control inputs.                                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INRC, RCT2 and integrator amplifiers, RCT1, INRC and band-gap switches, clean currents 4 | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FVOUT, scaling amplifiers, A/D conversion, RFV resistor                                  | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCCS, PG1 (PG2) driver, Heater Fet driver                                                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Diagnostic                                                                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Leakage currents                                                                         | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AC parameters                                                                            | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Timing                                                                                   | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Diagnostic filter times                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

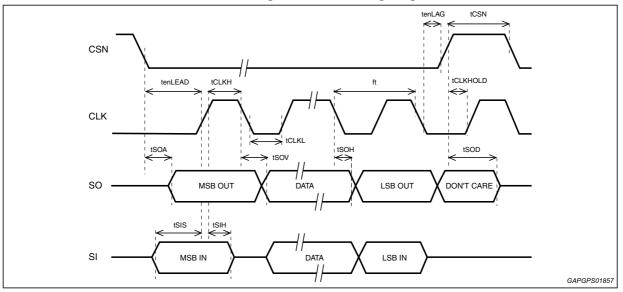

| Logic communications timing                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| External components value.                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Document revision history.                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                          | Device summary .<br>Pin function .<br>Maximum ratings .<br>Absolute maximum ratings .<br>Operating temperature range .<br>C <sub>int</sub> vs. possible R <sub>tot</sub> to guarantee phase margin and bandwidth .<br>Silicon version bits .<br>SPI data fault .<br>Supplies and control inputs.<br>INRC, RCT2 and integrator amplifiers, RCT1, INRC and band-gap switches, clean currents .<br>FVOUT, scaling amplifiers, A/D conversion, RFV resistor .<br>VCCS, PG1 (PG2) driver, Heater Fet driver .<br>Diagnostic .<br>Leakage currents .<br>AC parameters .<br>Timing .<br>Diagnostic filter times .<br>Logic communications timing .<br>External components value.<br>Document revision history. |

# List of figures

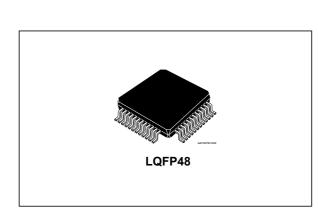

| Figure 1.  | Pin connection diagram (top view)              | . 7 |

|------------|------------------------------------------------|-----|

| Figure 2.  | Block diagram                                  |     |

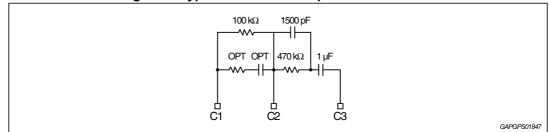

| Figure 3.  | Typical sensor D compensation network          |     |

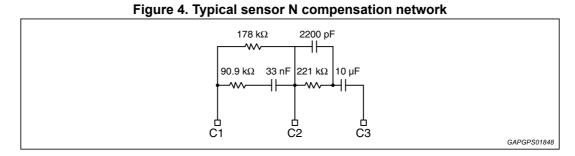

| Figure 4.  | Typical sensor N compensation network          | 15  |

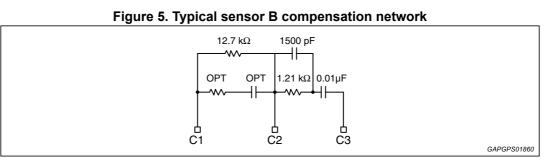

| Figure 5.  | Typical sensor B compensation network          | 15  |

| Figure 6.  | VCCS external resistance configuration         | 16  |

| Figure 7.  | VCCS characteristic                            | 17  |

| Figure 8.  | State machine diagram                          | 22  |

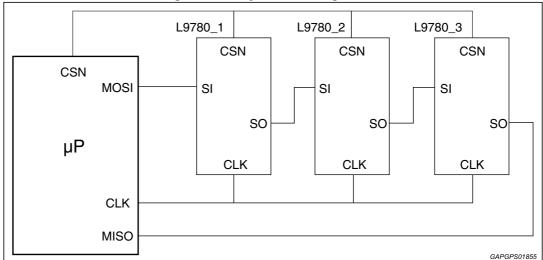

| Figure 9.  | Daisy chain configuration                      | 31  |

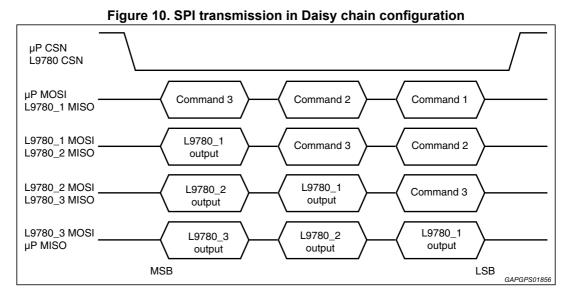

| Figure 10. | SPI transmission in Daisy chain configuration  | 31  |

| Figure 11. | SPI timing diagram                             | 51  |

| Figure 12. | Application circuit                            | 52  |

| Figure 13. | Sensor circuit                                 | 53  |

| Figure 14. | LQFP48 mechanical data and package dimensions. | 54  |

## 1 Pin description

Table 2. Pin function

| Pin number | Pin name | Pin description                      |

|------------|----------|--------------------------------------|

| 1          | TG1      | Switching TAG resistor pin channel 1 |

| 2          | SNS      | VCCS sense pin                       |

| 3          | TST1     | Test mode pin 1                      |

| 4          | INRC     | Reference cell input                 |

| 5          | RCT1     | Impedance test pin 1                 |

| 6          | RCT2     | Impedance test amplifier input       |

| 7          | SR       | Sensor return                        |

| 8          | PG1      | Protection fet gate channel 1        |

| 9          | PG2      | Protection fet gate channel 2        |

| 10         | HD       | Heater fet drain                     |

| 11         | TST2     | Test mode pin 2                      |

| 12         | HG       | Heater fet gate                      |

| 13         | SY       | Synchronous mode pin                 |

| 14         | PW       | Heater PWM input pin                 |

| 15         | SO       | Serial data output                   |

| 16         | CLK      | SPI clock                            |

| 17         | SI       | Serial data input                    |

DocID026356 Rev 3

| Table 2 | 2. Pin | function | (continued) |

|---------|--------|----------|-------------|

|---------|--------|----------|-------------|

| Iable 2. Pin function (continued)       Bin number     Bin name |          |                                      |  |  |

|-----------------------------------------------------------------|----------|--------------------------------------|--|--|

| Pin number                                                      | Pin name | Pin description                      |  |  |

| 18                                                              | CSN      | SPI chip select                      |  |  |

| 19                                                              | VCCI     | Digital transfer level supply        |  |  |

| 20                                                              | GNDD     | Digital ground                       |  |  |

| 21                                                              | VCCD     | Digital supply                       |  |  |

| 22                                                              | n.c.     | Not connected pin                    |  |  |

| 23                                                              | n.c.     | Not connected pin                    |  |  |

| 24                                                              | n.c.     | Not connected pin                    |  |  |

| 25                                                              | C1B      | Compensation network pin1, side B    |  |  |

| 26                                                              | C2B      | Compensation network pin2, side B    |  |  |

| 27                                                              | C3       | Compensation network common pin      |  |  |

| 28                                                              | C2A      | Compensation network pin2, side A    |  |  |

| 29                                                              | C1A      | Compensation network pin1, side A    |  |  |

| 30                                                              | FV       | VCCS filtered control voltage pin    |  |  |

| 31                                                              | FVOUT    | Analog output                        |  |  |

| 32                                                              | BG       | Bandgap voltage                      |  |  |

| 33                                                              | CL2      | VCCS voltage clamp channel 2         |  |  |

| 34                                                              | CL1      | VCCS voltage clamp channel 1         |  |  |

| 35                                                              | n.c.     | Not connected pin                    |  |  |

| 36                                                              | n.c.     | Not connected pin                    |  |  |

| 37                                                              | VCCCP    | Charge pump supply                   |  |  |

| 38                                                              | FLCP1    | Charge pump floating pin 1           |  |  |

| 39                                                              | FLCP2    | Charge pump floating pin 2           |  |  |

| 40                                                              | GNDCP    | Charge pump analog ground            |  |  |

| 41                                                              | СР       | -5V charge pump output               |  |  |

| 42                                                              | VESD     | ESD reference voltage                |  |  |

| 43                                                              | GNDA     | Analog ground                        |  |  |

| 44                                                              | VCCA     | Analog supply                        |  |  |

| 45                                                              | n.c.     | Not connected pin                    |  |  |

| 46                                                              | TG2      | Switching TAG resistor pin channel 2 |  |  |

| 47                                                              | OUT2     | Pump cell output pin channel 2       |  |  |

| 48                                                              | OUT1     | Pump cell output pin channel 1       |  |  |

# 2 Operating conditions

## 2.1 Maximum ratings

L9780 may not operate out of the maximum rating ranges. Once the correct situation is restored after one of the following conditions is not respected (but not exceeding the absolute maximum rating range) the part is still able to work with no damage.

| Symbol           | Parameter                                                                                                                                                                                                                                                                                  | Value                                         | Unit                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------|

| Vs               | Supply voltage:<br>VCCA, VCCD, VCCCP<br>VCCI                                                                                                                                                                                                                                               | 4.9 to 5.1<br>3.14 to 5.1                     | V                          |

| V <sub>ESD</sub> | ESD reference                                                                                                                                                                                                                                                                              | 40                                            | V                          |

| V <sub>in</sub>  | Input voltage<br>HD, RCT1, RCT2, INRC<br>SR, SNS<br>CSN, SI, CLK, PW, SY                                                                                                                                                                                                                   | 0 to 40<br>-VCCA to VCCA<br>0 to VCCA         | V                          |

| l <sub>in</sub>  | Input current<br>VESD<br>SR, RCT1, RCT2, SNS<br>INRC<br>HD<br>OUT1, OUT2, TG1, TG2<br>(leakage for maximum short to battery voltage)<br>SR, RCT1, RCT2, SNS, INRC, HD, OUT1, OUT2,<br>TG1, TG2<br>(when the voltage is driven below the normal<br>operating range)<br>CSN, SI, CLK, PW, SY | -20<br>10<br>50<br>150<br>350<br>-275<br>±275 | mA<br>μA<br>μA<br>μA<br>μA |

| Тj               | Junction temperature                                                                                                                                                                                                                                                                       | -40 to 150                                    | °C                         |

## 2.2 Absolute maximum ratings

The part can be irreparably damaged if the voltages out of the absolute maximum ratings ranges are applied to the pins. The part at these ratings could not work properly.

| Symbol           | Parameter                                  | Value        | Unit |

|------------------|--------------------------------------------|--------------|------|

| Vs               | Supply voltage:<br>VCCA, VCCD, VCCCP, VCCI | -0.3 to +6.5 | V    |

| V <sub>ESD</sub> | ESD reference                              | +53          | V    |

| Symbol           | Parameter                                                                                                                  | Value                       | Unit |

|------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|

|                  | Input voltage:                                                                                                             |                             |      |

|                  | HD                                                                                                                         | -0.3 to 53 <sup>(1)</sup>   |      |

|                  | RCT1, RCT2, INRC                                                                                                           | -0.3 to +40 <sup>(1)</sup>  |      |

|                  | SR, SNS, TGx, OUTx                                                                                                         | -VCCA to +40 <sup>(1)</sup> |      |

|                  | CSN, SI, CLK, PW, SY, SO                                                                                                   | -0.3 to VCCI+0.3            |      |

| V <sub>in</sub>  | C1B, C2B, C3, C2A, C1A, BG, CL2, CL1, FV,<br>FVOUT, PG1, PG2, HG                                                           | -0.3 to VCCA+0.3            | v    |

|                  | СР                                                                                                                         | -6.5 to +0.3                |      |

|                  | FLCP1                                                                                                                      | -0.3 to VCCCP+0.3           |      |

|                  | FLCP2                                                                                                                      | CP-0.3 to +0.3              |      |

|                  | TST1, TST2                                                                                                                 | -0.3 to 40 <sup>(1)</sup>   |      |

|                  | TGx – OUTx                                                                                                                 | +16                         |      |

|                  | Input current:                                                                                                             |                             |      |

|                  | VESD                                                                                                                       | -20                         | mA   |

|                  | SR, RCT1, RCT2, SNS                                                                                                        | 10                          | μA   |

|                  | INRC                                                                                                                       | 50                          | μA   |

|                  | HD                                                                                                                         | 150                         | μΑ   |

| l <sub>in</sub>  | OUT1, OUT2, TG1, TG2<br>(leakage for maximum short to battery voltage)                                                     | 500                         | μA   |

|                  | SR, RCT1, RCT2, SNS, INRC, HD, OUT1, OUT2,<br>TG1, TG2<br>(when the voltage is driven below the normal<br>operating range) | -500                        | μA   |

|                  | CSN, SI, CLK, PW, SY                                                                                                       | ±500                        | μA   |

| T <sub>stg</sub> | Storage temperature range                                                                                                  | -65 to +150                 | °C   |

| Тj               | Maximum junction temperature                                                                                               | +150                        | °C   |

Table 4. Absolute maximum ratings (continued)

1. Voltage at the pin cannot exceed V<sub>ESD</sub>+0.3 V.

## 2.3 Operating temperature range

#### Table 5. Operating temperature range

| Symbol           | Parameter                   | Value      | Unit |

|------------------|-----------------------------|------------|------|

| T <sub>amb</sub> | Operating temperature range | -40 to 125 | °C   |

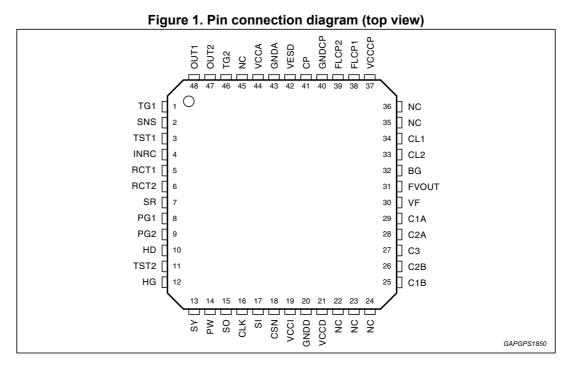

## 3 Block diagram

The following is L9780 block diagram; the description of each block and the definition of external components can be found in the next sections.

Figure 2. Block diagram

## 4 Main functionalities

## 4.1 **Power supplies**

4 different power supplies are present in the device: VCCA, VCCD, VCCCP, VCCI, respectively for analog part, digital part, charge pump, digital interfaces. Digital inputs are compatible with 2 different logic levels (5 V or 3.3 V, the possible levels for VCCI), and are converted to the range 0V-VCCD using internal level shifters connected to VCCD and VCCI. In the device a negative charge pump is also present and it is used to generate -5 V voltage level (on CP pin), to bias the substrate and to allow the excursion to the negative range to the output pins of VCCS. Charge pump clock frequency is 2 MHz.

3 different ground pins are also present in the device: GNDA, GNDD, GNDCP, respectively for analog, digital and charge pump circuitry.

Possible ranges for power supplies, currents consumption and input/output logic levels are specified in *Table 9*, *Table 12* and *Table 13*. External component values are specified in *Table 19*.

## 4.2 Pin protection

On the device a high ESD reference voltage pin (VESD) is available and is used as a protection for the pins externally connected to the sensor and for HD pin; this voltage must be the highest in the application and has to be always connected to the device, through the RC low pass filter shown in *Figure 12* (external component values are specified in *Table 19*). For pins compatible to negative voltages, the negative ESD reference voltage is the substrate (internally connected to CP pin, -5 V). All the other pins have a 5V positive ESD protection voltage level and GND as negative ESD protection voltage level.

## 4.3 Internal references

Into the device the following voltage references are present:

- a band-gap voltage (typical value 1.215 V) with 3 trimming bits dedicated;

- REF voltage; obtained as the band-gap multiplied by a factor of 1.555; typical value for this voltage is 1.89 V (possible range for this parameter is specified in *Table 10*.

- REF2 voltage; typical value is about VCCA/2 (possible range for this parameter is specified in *Table 11*).

All internal currents are generated from a reference current obtained by the band-gap (buffered on BG pin) applied on an external resistance; the possible BG pin voltage range is specified in *Table 9*, the value of external resistance is defined in *Table 19*.

All timing references are calculated as multiples of the period of the internal oscillator (TOSC); the typical oscillation frequency is 4 MHz, the possible range is specified in *Table 15*. Internal oscillator has 4 trimming bits dedicated.

### 4.4 **Power on reset**

A power on reset (POR) circuit is present into the device; this circuit monitors VCCA, VCCCP, VCCD, GNDA, GNDCP, GNDD voltage levels. If one of the supplies falls below (or one of the grounds exceeds) the defined POR threshold (defined in *Table 10*) all the outputs are driven in inactive state, all the registers are set at their default state and the time state machine and all the timers are fixed in the reset state. All these actions are applied after a typical filter time of 15  $\mu$ s (possible range is defined in *Table 15*). When the supply that has caused POR condition reaches POR value plus hysteresis (or the ground decreases under POR threshold) all the outputs are re-enabled.

During reset condition an internal switch connects the charge pump output voltage (CP pin) to GNDA.

## 4.5 Pin INRC functionalities: INRC amplifier, clean currents, pulldown current

Pin INRC in the application is connected to the sensor reference cell; the voltage generated by this cell and applied on L9780 INRC pin is a function of the  $\lambda$  parameter of the sensor and gives information about how much the  $\lambda$  parameter is far from the target value. The final purpose is to obtain  $\lambda = 1$ , that in terms of electrical parameters means to have 450 mV as output of the reference cell (and applied on INRC pin). In the device this pin is the input of an amplifier (INRC amplifier) with gain selectable via SPI (using bit INRCGAIN). The output of this amplifier is one of the multiplexed inputs of the A/D converter (in order to give the  $\mu$ P the estimation of the  $\lambda$  parameter of the sensor via SPI) and is also internally connected by a switch (INRC switch) to C1A or C1B pin and the external compensation network. The selection of channel A or B is possible using bit COMPSEL. Electrical parameters of INRC amplifier and INRC switches are specified in *Table 10*.

On INRC pin is present a diagnostic circuitry able to detect short to battery/ground conditions and communicate it via SPI (bits STBS2 and STGRC of SPI output register); short to battery detection is always enabled, while the short to ground detection is disabled by default; it can be enabled using bit STGINRC. INRC short to battery/ground thresholds typical values are 3.2 V and 200 mV (possible ranges are defined in *Table 13*). The consequences of the detection of each one of these faults are described in *Section 5.1* and *5.2*.

The INRC pin is connected to the clean current generator: it is a pull-up current source used to clean the air reference of the sensor; the generated current value is selectable via SPI (using bits CCS[3..0]). Possible clean current values are specified in *Table 10*.

On the same pin a 500  $\mu$ A pull-down current source is also available, used in order to prevent the presence of false short to battery detection due to capacitive commutations. The activation of this current is selectable via SPI (bit INRCPD); pull-down current range is specified in *Table 10*.

A detailed bit description is present in Section 6.3 and 6.4.

# 4.6 Pin RCT1 – RCT2 functionalities: RCT2 amplifier, RCT1 switch, RCT1 band-gap switch

RCT2 pin is the input of an amplifier with typical gain 4.2 (electrical characteristics of RCT2 amplifier are specified in *Table 10*). The output of this amplifier is evaluated during the impedance test and converted in order to communicate its value via SPI to the  $\mu$ P: the value of RCT2 amplifier output, measured in 2 different conditions (with RCT1 switch open and closed), can in fact give a feedback about the impedance of the reference cell, and consequently about the temperature of the sensor.

RCT1 pin is connected through a switch (RCT1 switch) to ground and through another switch (RCT1 band-gap switch) to the band-gap voltage; both these functions are used during the reference cell impedance test, in particular the second one is used to restore the correct charge of the reference cell after the impedance test (charge balance mechanism). RCT1 switches resistance range and RCT1 voltage during charge balance are specified in *Table 10*. For the time diagram of the sequence and the related description see *Section 4.12*. Values of external components connected to pins RCT1 and RCT2 are specified in *Table 19*.

# 4.7 Pin C1A, C2A, C1B, C2B, C3 functionalities: compensation network connection

These pins are used to connect externally the compensation network to the device; via SPI (using COMPSEL bit) it is possible to select the desired channel (A or B) and connect the external network to the pins C1(A or B), C2(A or B) and C3. The pins of the non selected channel are in high impedance state. C1 is internally connected to the output of INRC amplifier through the INRC switch (driven by the logic during the impedance test, for details see *Section 4.12*), while C2 and C3 are internally connected to the inverting input and the output of an integrator amplifier (C3 is also the VCCS control voltage pin). The non inverting input of the amplifier is connected to REF voltage (typ 1.89 V). The integrator amplifier and the VCCS create a loop (with the external compensation network) of a PI controller. When the loop reaches a stable condition ( $\lambda = 1$ ), on INRC pin there are 450 mV (if 4.2 gain for INRC amplifier is selected), while the inputs of integrator amplifier are both to 1.89 V (450 mV \* 4.2). In this condition there is no output current from the VCCS cell (2.5 V on C3 pin).

The values of the external components that must be used in compensation network depend on the sensor that will be driven by the device.

Two examples of possible compensation networks (with defined external components values) are shown below.

Figure 3. Typical sensor D compensation network

DocID026356 Rev 3

## 4.8 Pin FV, FVOUT functionalities: FVOUT amplifier

C3 pin voltage is the VCCS direct input control voltage. Thanks to the presence of the external capacitor on FV pin (CFV, specified in *Table 19*) and the internal resistance RFV (typical value 5 k $\Omega$  and possible range specified in *Table 11*), on FV pin the low pass filtered C3 voltage can be measured. FV voltage is the input of the FVOUT amplifier used to provide on FVOUT pin a signal range compatible with an external A/D converter, as follows:

FVOUT = REF2 + G \* (FV - REF2)

Where G is the gain of VOUT amplifier selectable via SPI (using bits SAMP[2..0]) among the following values: 1 - 1.5 - 2 - 3 - 4 - 6 - 8 - 12. A sample and hold circuitry and the offset compensation technique are used in the architecture of FVOUT amplifier; for this cell all the electrical parameters are specified in *Table 10* and *Table 15*.

## 4.9 Pin TG1, TG2, OUT1, OUT2, SNS functionalities: the VCCS

TG1, TG2, OUT1, OUT2, SNS are the interface pins between VCCS structure and the external pump cell. The pump cell allows to control the oxygen concentration by forcing an electric current through the cell itself; in other words it is possible to control the direction and the intensity of oxygen transport, because it is directly related to the direction and the intensity of the current. By controlling the amount of current through the pump cell, it is possible to control the amount of oxygen and consequently the  $\lambda$  parameter of the sensor; closing this mechanism into a loop, like in L9780, it is possible to regulate the pump cell current in order to obtain the target  $\lambda = 1$ . The best working condition for the sensor is the high temperature; in this condition the AC impedance of the pump cell can be assumed to be a large capacitance in series to with a resistor of about 20-30  $\Omega$ . When cold, the pump cell can be assumed to be an open circuit.

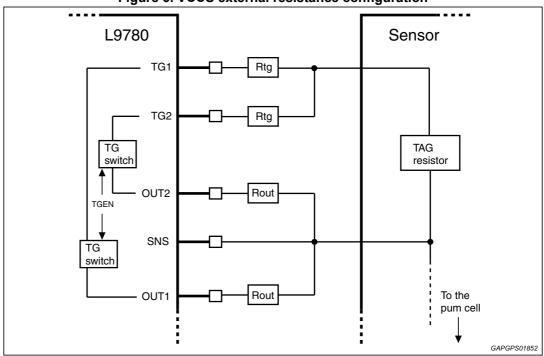

VCCS is a voltage controlled current source and is able to sink or source current from the pump cell, depending on its control voltage, that is the voltage present on C3 pin. Through TG and OUT pins there is the VCCS output current flow, while SNS is a sense pin. VCCS present in L9780 has 2 output channels (1 and 2), selectable via SPI (using bit VCCSOUT); TG and OUT pins of the non selected channel are in high impedance condition. In VCCS architecture there are 2 internal switches (TG switches) able to short OUT and TG pins of the selected channel (see *Figure 6*); the actuation of these switches can be selected via SPI (using bit TGEN).

If the switch is in off condition the TG pin of the selected channel is in high impedance state. If the TG switch is in on state the output current of VCCS structure can flow both through TG and OUT pins and can be described with the following expression:

$$I_{out} = - (C3 - REF2)/R_{tot}$$

where  $R_{tot}$  is the external total resistance, that can be obtained as a combination of all the external resistances connected to the VCCS pins. Referring to *Figure 6*,  $R_{tot}$  can be calculated as follows:

$$R_{tot} = R_{out} // (R_{tg} + TAG resistor)$$

where  $\mathsf{R}_{tg}$  and  $\mathsf{R}_{out}$  are the series resistances of the VCCS pins related to the selected channel.

Otherwise, if TG switch is in off state,  $R_{tot} = R_{out}$  and consequently the VCCS output current can be described with the following expression:

$$I_{out} = - (C3 - REF2)/R_{out}$$

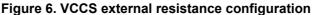

The VCCS characteristic is shown in *Figure* 7. In this figure the relationship between SNS voltage and the voltage on R<sub>tot</sub> resistance (that is equal to the difference between OUT voltage and SNS voltage) is defined; these two quantities are in agreement in sign as both

depend on the VCCS output current multiplied by a resistance value (the resistance of the pump cell in SNS voltage case and the R<sub>tot</sub> resistance in the voltage drop case); from the same figure it is evident that the maximum SNS voltage dynamic range compatible with L9780 VCCS architecture is -2 V < SNS < 2.4 V and the maximum drop allowed on R<sub>tot</sub> (or Rout if TG switch is off) is 1.8 V.

At the startup of the device, VCCS structure is disabled by default, that means that all its pins are in high impedance condition and the "parking functionality" is active; in other words, the parking amplifier is switched on and a voltage similar to REF2 is present on C3 pin (see block diagram in *Figure 2*). Besides, a pull-down resistor is internally connected by default from OUT1 pin to GNDA; this is done to avoid that a leakage current can increase the voltage value of VCCS pins until the short to battery condition. When VCCS is enabled or a sensor short to battery condition is detected, the pull-down resistor is automatically disconnected from OUT1 pin; when VCCS is disabled and no fault conditions are present, VCCS pull-down resistor can be re enabled via SPI (using bit VCCSPD).

If no sensor short to battery condition is present, VCCS structure can be enabled and the output channel selected with an SPI frame (using bits VCCSEN and VCCSOUT); in this case the "parking functionality" is disabled. When VCCS is enabled, it is also possible to activate/deactivate clamp functionality via SPI (using bit CLAMPEN), in order to protect the sensor; when the clamp functionality is activated, a voltage control is enabled on SNS pin and, if its value is going to exceed the voltage range defined by the user, the clamp circuit intervenes in order to modify the VCCS output current and make SNS pin reenter the clamp limits. The clamp limit range can be symmetric or asymmetric; the desired kind of range can be defined via SPI (bit CLAMPSIM). In case of symmetric range, if VCL is the clamp voltage defined by the user, the consequent range allowed for SNS voltage is:

-VCL < SNS < +VCL, with 0.75V<VCL<2V

In case of asymmetric range, if VCL is the clamp voltage defined by the user, the consequent range for SNS voltage is:

-0.8333\*VCL < SNS < +VCL, with 0.75 V < VCL < 2.4 V

If the clamp circuit is activated and intervenes while VCCS is working, it is visible also via SPI because CLAMP bit in SO register is kept = 1 until the clamp circuit is acting during VCCS activation. The clamp voltage VCL is defined by the user and is equal to the voltage applied on CL1 or CL2 pin; the input channel chosen to read the clamp voltage can be selected via SPI (bit CLAMPCL); the non selected pin can be left open.

DocID026356 Rev 3

On all VCCS pins a short to battery diagnostic is always active: a short to battery condition is detected if OUT or TG pins exceed VCCA voltage + 30 mV or if SNS pin exceed STBS3 threshold voltage (2.7 V typical value, possible range defined in ). The consequences of a

On SNS pin is also present a short to ground diagnostic circuitry, that is able to detect if SNS pin is into the range SNS\_NTH < SNS < SNS\_PTH (SNS\_NTH and SNS\_PTH are voltage thresholds specified in *Table 13*, their typical values are -200 mV and 200 mV). The consequences of a sensor short to ground detection are specified in *Section 5.3*.

short to battery fault detection are specified in Section 5.1.

VCCS is designed to respect specification of minimum bandwidth (100 kHz) for different R<sub>tot</sub> values and is able to guarantee in all conditions a minimum phase margin of 60°. This is possible thanks to the programmability of the VCCS internal compensation capacitances (C<sub>int</sub>). In SPI input frame, 6bit for capacitance configuration are present (VCCSCAP[5..0]); these bits allow to drive the connection of internal compensation capacitances, that in this way are selectable by the user. The higher is the value of capacitance selected and the higher is the phase margin of the structure, but the lower is the consequent bandwidth; with some simplifications the bandwidth of VCCS can be described with the following formula:

Ft = (Gm\_in \* Gm\_outDC \*  $R_{tot}$ )/ (2 $\pi$  \*  $C_{int}$ )