# Intel® Quark™ microcontroller D2000

**Datasheet**

---

*January 2016*

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting: <http://www.intel.com/design/literature.htm>

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at <http://www.intel.com/> or from the OEM or retailer.

No computer system can be absolutely secure.

Intel, Intel Quark, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2016, Intel Corporation. All rights reserved.

# Contents

|        |                                         |    |

|--------|-----------------------------------------|----|

| 1      | Introduction .....                      | 16 |

| 1.1    | Feature Overview .....                  | 17 |

| 1.1.1  | Clock Oscillators.....                  | 17 |

| 1.1.2  | Quark Processor Core .....              | 17 |

| 1.1.3  | Memory Subsystem .....                  | 17 |

| 1.1.4  | I <sup>2</sup> C .....                  | 17 |

| 1.1.5  | UART.....                               | 17 |

| 1.1.6  | SPI .....                               | 18 |

| 1.1.7  | DMA Controller .....                    | 18 |

| 1.1.8  | GPIO Controller.....                    | 18 |

| 1.1.9  | Timers.....                             | 18 |

| 1.1.10 | Pulse Width Modulation (PWM) .....      | 18 |

| 1.1.11 | Watchdog Timer.....                     | 19 |

| 1.1.12 | Real Time Clock (RTC) .....             | 19 |

| 1.1.13 | Analog to Digital Convertor (ADC).....  | 19 |

| 1.1.14 | Analog Comparators .....                | 19 |

| 1.1.15 | Interrupt Routing .....                 | 19 |

| 1.1.16 | Power Management .....                  | 20 |

| 1.1.17 | Package .....                           | 20 |

| 2      | Physical Interfaces .....               | 21 |

| 2.1    | Pin States Through Reset .....          | 21 |

| 2.2    | <i>External</i> Interface Signals.....  | 21 |

| 2.3    | GPIO Multiplexing.....                  | 26 |

| 3      | Ballout and Package Information .....   | 27 |

| 3.1    | SoC Attributes .....                    | 27 |

| 3.2    | Package Diagrams.....                   | 28 |

| 3.3    | Pin Multiplexing.....                   | 30 |

| 3.4    | Alphabetical Ball Listing .....         | 33 |

| 3.5    | Platform Requirements.....              | 35 |

| 3.5.1  | 3.5.1 Internal Voltage Regulator.....   | 35 |

| 3.5.2  | RTC Oscillator .....                    | 37 |

| 3.5.3  | Hybrid Oscillator .....                 | 38 |

| 3.5.4  | ADC .....                               | 39 |

| 4      | Electrical Characteristics .....        | 40 |

| 4.1    | Thermal Specifications .....            | 40 |

| 4.2    | Voltage and Current Specifications..... | 40 |

| 4.2.1  | Absolute Maximum Ratings.....           | 40 |

| 4.3    | Crystal Specifications .....            | 41 |

| 4.4    | DC Specifications .....                 | 43 |

| 4.4.1  | IO DC specifications.....               | 43 |

| 4.4.2  | Undershoot Voltage Support .....        | 45 |

| 4.4.3  | ADC IO DC characteristics .....         | 45 |

| 4.5    | System Power Consumption.....           | 46 |

| 4.6    | AC Specifications.....                  | 48 |

| 4.6.1  | SPI Master IO AC characteristics.....   | 48 |

| 4.6.2  | SPI Slave IO AC characteristics .....   | 49 |

|         |                                                           |    |

|---------|-----------------------------------------------------------|----|

| 4.6.3   | I <sup>2</sup> C Master/Slave IO AC characteristics ..... | 49 |

| 4.6.4   | General IO AC characteristics.....                        | 50 |

| 4.6.5   | JTAG Interface AC characteristics .....                   | 50 |

| 5       | Register Access Methods .....                             | 51 |

| 5.1     | Fixed Memory Mapped Register Access .....                 | 51 |

| 5.2     | Register Field Access Types .....                         | 51 |

| 6       | Mapping Address Spaces.....                               | 53 |

| 6.1     | Physical Address Space Mappings .....                     | 53 |

| 6.1.1   | SoC Memory Map .....                                      | 53 |

| 6.2     | SoC Fabric.....                                           | 55 |

| 7       | Clocking .....                                            | 57 |

| 7.1     | Signal Descriptions .....                                 | 57 |

| 7.2     | Features .....                                            | 57 |

| 7.2.1   | System Clock - Hybrid Oscillator.....                     | 58 |

| 7.2.2   | RTC Oscillator .....                                      | 58 |

| 7.2.3   | Root Clock Frequency Scaling.....                         | 59 |

| 7.2.4   | Frequency Scaling .....                                   | 59 |

| 7.2.4.1 | Peripheral DFS requirements .....                         | 59 |

| 7.2.4.2 | Flash DFS requirements.                                   | 60 |

| 7.2.5   | Dynamic Clock Gating .....                                | 60 |

| 7.2.5.1 | UART autonomous clock gating (ACG).....                   | 60 |

| 7.2.5.2 | SPI autonomous clock gating (ACG) .....                   | 60 |

| 8       | Power Management .....                                    | 61 |

| 8.1     | Component Power States .....                              | 62 |

| 8.1.1   | Voltage Regulator.....                                    | 62 |

| 8.1.2   | CPU.....                                                  | 63 |

| 8.1.3   | ADC .....                                                 | 64 |

| 8.1.4   | Comparator .....                                          | 65 |

| 8.1.5   | 32.768 kHz OSC.....                                       | 65 |

| 8.1.6   | 32 MHz OSC .....                                          | 66 |

| 8.1.7   | SRAM .....                                                | 66 |

| 8.1.8   | Peripherals .....                                         | 67 |

| 8.2     | System Power States .....                                 | 68 |

| 8.2.1   | System Power State Diagram.....                           | 68 |

| 8.2.2   | System Power State Definition .....                       | 69 |

| 8.2.3   | Power and Latency Requirements .....                      | 70 |

| 8.2.4   | Minimum Voltage Limits (Vmin).....                        | 71 |

| 8.3     | Power Architecture .....                                  | 72 |

| 8.4     | Power Management Unit (PMU) .....                         | 74 |

| 8.4.1   | Internal Voltage Regulator.....                           | 74 |

| 8.4.2   | External Voltage Regulator .....                          | 75 |

| 9       | Power Up and Reset Sequence .....                         | 76 |

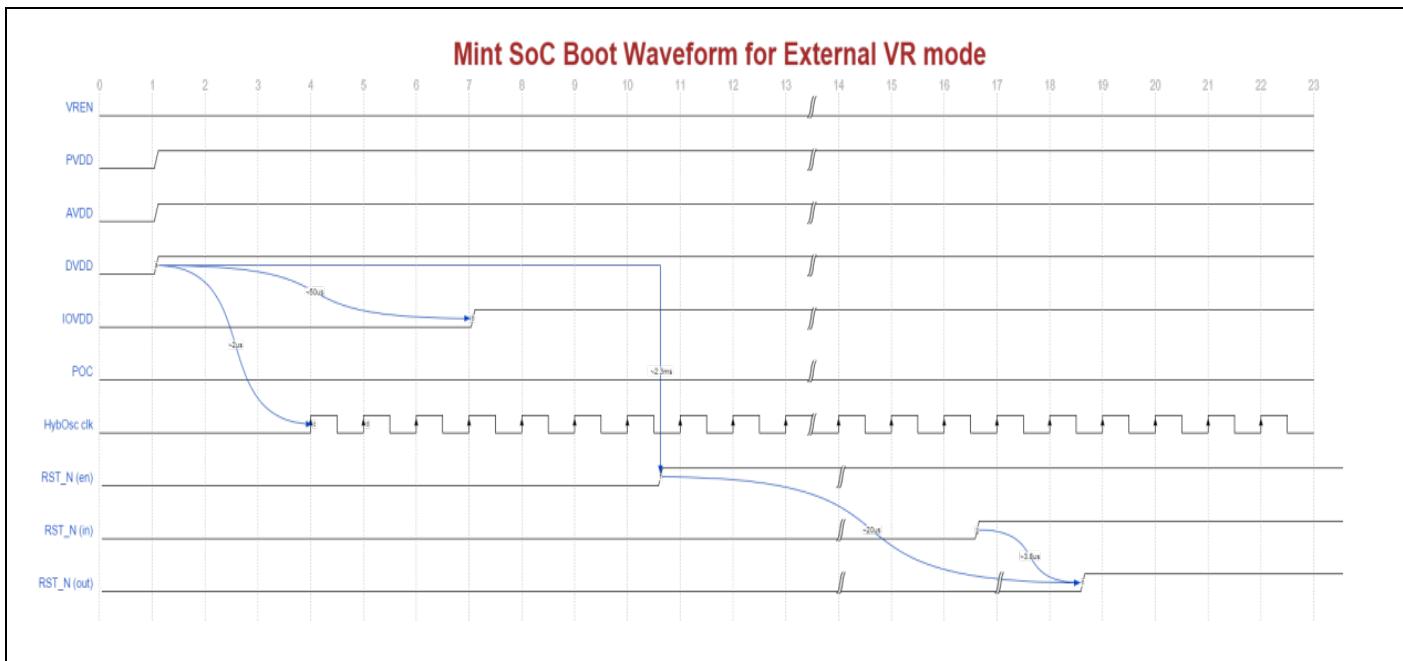

| 9.1     | Power Up Sequences .....                                  | 76 |

| 9.1.1   | RST_N Triggered Transition to ACTIVE state.....           | 76 |

| 9.1.2   | Low Power State to Active .....                           | 77 |

| 9.2     | Power Down Sequences .....                                | 78 |

| 9.2.1   | Active to Any Low Power State .....                       | 80 |

| 9.2.2   | Power Sequence Analog Characteristics .....               | 83 |

| 9.2.3   | Handling Power Failures .....                             | 83 |

|          |                                                                       |     |

|----------|-----------------------------------------------------------------------|-----|

| 9.3      | Reset Behavior.....                                                   | 83  |

| 9.3.1    | Power On Reset .....                                                  | 84  |

| 9.3.2    | Cold Reset.....                                                       | 85  |

| 9.3.3    | Warm Reset .....                                                      | 85  |

| 10       | Thermal Management .....                                              | 87  |

| 10.1     | Overview .....                                                        | 87  |

| 11       | Processor Core .....                                                  | 88  |

| 11.1     | Features .....                                                        | 88  |

| 11.2     | Processor Memory Map .....                                            | 90  |

| 11.3     | Main Fabric Bus Cycle Processing.....                                 | 92  |

| 11.3.1.1 | Code Reads .....                                                      | 92  |

| 11.3.1.2 | Memory Reads and Memory Writes.....                                   | 92  |

| 11.3.1.3 | IO Reads and IO Writes .....                                          | 93  |

| 11.3.1.4 | Interrupt Acknowledge .....                                           | 93  |

| 11.3.1.5 | Special Cycles .....                                                  | 93  |

| 11.3.1.6 | MSI .....                                                             | 95  |

| 11.3.1.7 | End of Interrupt .....                                                | 95  |

| 11.3.2   | Mapping FSB to AHB .....                                              | 95  |

| 11.3.2.1 | Byte Enables.....                                                     | 95  |

| 11.4     | Intel® Quark™ microcontroller D2000 Interrupt Controller (MVIC) ..... | 97  |

| 11.4.1   | MVIC Registers .....                                                  | 98  |

| 11.4.1.1 | TPR .....                                                             | 98  |

| 11.4.1.2 | PPR .....                                                             | 98  |

| 11.4.1.3 | EOI.....                                                              | 99  |

| 11.4.1.4 | SIVR.....                                                             | 99  |

| 11.4.1.5 | ISR.....                                                              | 99  |

| 11.4.1.6 | IRR.....                                                              | 100 |

| 11.4.1.7 | LVTTIMER.....                                                         | 100 |

| 11.4.1.8 | ICR.....                                                              | 101 |

| 11.4.1.9 | CCR.....                                                              | 101 |

| 11.4.2   | Programming Sequence .....                                            | 102 |

| 11.4.3   | Interrupt Latency Reduction.....                                      | 102 |

| 11.4.4   | Sample Code .....                                                     | 104 |

| 11.5     | CPUID .....                                                           | 105 |

| 12       | Memory Subsystem.....                                                 | 106 |

| 12.1     | Features .....                                                        | 106 |

| 12.1.1   | System Flash Controller Features.....                                 | 106 |

| 12.1.2   | OTP Features.....                                                     | 108 |

| 12.1.3   | Internal SRAM Features.....                                           | 109 |

| 12.2     | Error Handling .....                                                  | 111 |

| 12.3     | Memory Consistency Analysis.....                                      | 114 |

| 12.3.1   | Producer/Consumer Model Analysis of the Memory Subsystem.....         | 117 |

| 12.3.2   | Miscellaneous Memory Ordering related Scenarios.....                  | 119 |

| 12.4     | Memory Mapped IO Registers.....                                       | 120 |

| 12.4.1   | Flash Controller 0 Register Summary .....                             | 120 |

| 12.4.2   | Flash Controller 0 Register Detailed Description .....                | 121 |

| 12.4.2.1 | TMG_CTRL (TMG_CTRL) .....                                             | 121 |

| 12.4.2.2 | ROM_WR_CTRL (ROM_WR_CTRL) .....                                       | 122 |

| 12.4.2.3 | ROM_WR_DATA (ROM_WR_DATA) .....                                       | 123 |

| 12.4.2.4 | FLASH_WR_CTRL (FLASH_WR_CTRL) .....                                   | 124 |

| 12.4.2.5 | FLASH_WR_DATA (FLASH_WR_DATA) .....                                   | 125 |

|           |                                                                |     |

|-----------|----------------------------------------------------------------|-----|

| 12.4.2.6  | FLASH_STTS (FLASH_STTS) .....                                  | 125 |

| 12.4.2.7  | CTRL (CTRL) .....                                              | 126 |

| 12.4.2.8  | FPRO_RD_CFG (FPRO_RD_CFG) .....                                | 127 |

| 12.4.2.9  | FPR1_RD_CFG (FPR1_RD_CFG) .....                                | 128 |

| 12.4.2.10 | FPR2_RD_CFG (FPR2_RD_CFG) .....                                | 129 |

| 12.4.2.11 | FPR3_RD_CFG (FPR3_RD_CFG) .....                                | 130 |

| 12.4.2.12 | MPR_WR_CFG (MPR_WR_CFG) .....                                  | 131 |

| 12.4.2.13 | MPR_VSTS (MPR_VSTS) .....                                      | 132 |

| 12.4.2.14 | MPR_VDATA (MPR_VDATA) .....                                    | 133 |

| 12.4.3    | Internal SRAM Register Summary .....                           | 133 |

| 12.4.4    | Internal SRAM Register Detailed Description.....               | 134 |

| 12.4.4.1  | MPR_CFG (MPR0_CFG) .....                                       | 134 |

| 12.4.4.2  | MPR_CFG (MPR1_CFG) .....                                       | 135 |

| 12.4.4.3  | MPR_CFG (MPR2_CFG) .....                                       | 136 |

| 12.4.4.4  | MPR_CFG (MPR3_CFG) .....                                       | 138 |

| 12.4.4.5  | MPR_VDATA (MPR_VDATA) .....                                    | 139 |

| 12.4.4.6  | MPR_VSTS (MPR_VSTS) .....                                      | 139 |

| 13        | I <sup>2</sup> C.....                                          | 141 |

| 13.1      | Signal Descriptions .....                                      | 141 |

| 13.2      | Features .....                                                 | 141 |

| 13.3      | Memory Mapped IO Registers.....                                | 142 |

| 13.3.1.1  | Control Register (IC_CON) .....                                | 143 |

| 13.3.1.2  | Master Target Address (IC_TAR) .....                           | 146 |

| 13.3.1.3  | Slave Address (IC_SAR) .....                                   | 148 |

| 13.3.1.4  | High Speed Master ID (IC_HS_MADDR) .....                       | 149 |

| 13.3.1.5  | Data Buffer and Command (IC_DATA_CMD) .....                    | 149 |

| 13.3.1.6  | Standard Speed Clock SCL High Count<br>(IC_SS_SCL_HCNT) .....  | 152 |

| 13.3.1.7  | Standard Speed Clock SCL Low Count<br>(IC_SS_SCL_LCNT).....    | 153 |

| 13.3.1.8  | Fast Speed Clock SCL High Count (IC_FS_SCL_HCNT) ..            | 153 |

| 13.3.1.9  | Fast Speed I2C Clock SCL Low Count<br>(IC_FS_SCL_LCNT) .....   | 154 |

| 13.3.1.10 | High Speed I2C Clock SCL High Count<br>(IC_HS_SCL_HCNT) .....  | 155 |

| 13.3.1.11 | High Speed I2C Clock SCL Low Count<br>(IC_HS_SCL_LCNT) .....   | 155 |

| 13.3.1.12 | Interrupt Status (IC_INTR_STAT).....                           | 156 |

| 13.3.1.13 | Interrupt Mask (IC_INTR_MASK).....                             | 160 |

| 13.3.1.14 | Raw Interrupt Status (IC_RAW_INTR_STAT).....                   | 164 |

| 13.3.1.15 | Receive FIFO Threshold Level (IC_RX_TL) .....                  | 169 |

| 13.3.1.16 | Transmit FIFO Threshold Level (IC_TX_TL) .....                 | 169 |

| 13.3.1.17 | Clear Combined and Individual Interrupt<br>(IC_CLR_INTR) ..... | 170 |

| 13.3.1.18 | Clear RX_UNDER Interrupt (IC_CLR_RX_UNDER) .....               | 171 |

| 13.3.1.19 | Clear RX_OVER Interrupt (IC_CLR_RX_OVER).....                  | 171 |

| 13.3.1.20 | Clear TX_OVER Interrupt (IC_CLR_TX_OVER) .....                 | 171 |

| 13.3.1.21 | Clear RD_REQ Interrupt (IC_CLR_RD_REQ) .....                   | 172 |

| 13.3.1.22 | Clear TX_ABRT Interrupt (IC_CLR_TX_ABRT) .....                 | 172 |

| 13.3.1.23 | Clear RX_DONE Interrupt (IC_CLR_RX_DONE) .....                 | 173 |

| 13.3.1.24 | Clear ACTIVITY Interrupt (IC_CLR_ACTIVITY) .....               | 173 |

| 13.3.1.25 | Clear STOP_DET Interrupt (IC_CLR_STOP_DET) .....               | 174 |

| 13.3.1.26 | Clear START_DET Interrupt (IC_CLR_START_DET) .....             | 174 |

| 13.3.1.27 | Clear GEN_CALL Interrupt (IC_CLR_GEN_CALL) .....               | 175 |

|           |                                                                              |     |

|-----------|------------------------------------------------------------------------------|-----|

| 13.3.1.28 | Enable (IC_ENABLE) .....                                                     | 175 |

| 13.3.1.29 | Status (IC_STATUS).....                                                      | 177 |

| 13.3.1.30 | Transmit FIFO Level (IC_TXFLR) .....                                         | 179 |

| 13.3.1.31 | Receive FIFO Level (IC_RXFLR).....                                           | 179 |

| 13.3.1.32 | SDA Hold (IC_SDA_HOLD) .....                                                 | 180 |

| 13.3.1.33 | Transmit Abort Source (IC_TX_ABRT_SOURCE).....                               | 180 |

| 13.3.1.34 | SDA Setup (IC_DMA_CR).....                                                   | 184 |

| 13.3.1.35 | DMA Transmit Data Level Register (IC_DMA_TDLR) .....                         | 185 |

| 13.3.1.36 | I2C Receive Data Level Register (IC_DMA_RDLR) .....                          | 185 |

| 13.3.1.37 | SDA Setup (IC_SDA_SETUP) .....                                               | 186 |

| 13.3.1.38 | General Call Ack (IC_ACK_GENERAL_CALL) .....                                 | 187 |

| 13.3.1.39 | Enable Status (IC_ENABLE_STATUS) .....                                       | 187 |

| 13.3.1.40 | SS and FS Spike Suppression Limit (IC_FS_SPKLEN) .....                       | 189 |

| 13.3.1.41 | HS spike suppression limit (IC_HS_SPKLEN) .....                              | 190 |

| 13.3.1.42 | Clear the RESTART_DET interrupt<br>(IC_CLR_RESTART_DET) .....                | 191 |

| 13.3.1.43 | Configuration Parameters (IC_COMP_PARAM_1).....                              | 191 |

| 13.3.1.44 | Component Version (IC_COMP_VERSION) .....                                    | 191 |

| 13.3.1.45 | Component Type (IC_COMP_TYPE).....                                           | 192 |

| 14        | UART .....                                                                   | 193 |

| 14.1      | Signal Descriptions .....                                                    | 193 |

| 14.2      | Features .....                                                               | 194 |

| 14.3      | Memory Mapped IO Registers.....                                              | 195 |

| 14.3.1.1  | Receive Buffer / Transmit Holding / Divisor Latch Low<br>(RBR_THR_DLL) ..... | 196 |

| 14.3.1.2  | Interrupt Enable / Divisor Latch High (IER_DLH) .....                        | 198 |

| 14.3.1.3  | Interrupt Identification / FIFO Control (IIR_FCR) .....                      | 199 |

| 14.3.1.4  | Line Control (LCR) .....                                                     | 202 |

| 14.3.1.5  | MODEM Control (MCR).....                                                     | 204 |

| 14.3.1.6  | Line Status (LSR) .....                                                      | 206 |

| 14.3.1.7  | MODEM Status (MSR).....                                                      | 211 |

| 14.3.1.8  | Scratchpad (SCR) .....                                                       | 214 |

| 14.3.1.9  | UART Status (USR) .....                                                      | 215 |

| 14.3.1.10 | Halt Transmission (HTX) .....                                                | 216 |

| 14.3.1.11 | DMA Software Acknowledge (DMASA) .....                                       | 217 |

| 14.3.1.12 | Transceiver Control Register (TCR).....                                      | 217 |

| 14.3.1.13 | Driver Output Enable Register (DE_EN).....                                   | 219 |

| 14.3.1.14 | Receiver Output Enable Register (RE_EN).....                                 | 220 |

| 14.3.1.15 | Driver Output Enable Timing Register (DET) .....                             | 220 |

| 14.3.1.16 | TurnAround Timing Register (TAT) .....                                       | 221 |

| 14.3.1.17 | Divisor Latch Fraction (DLF) .....                                           | 222 |

| 14.3.1.18 | Receive Address Register (RAR) .....                                         | 222 |

| 14.3.1.19 | Transmit Address Register (TAR).....                                         | 223 |

| 14.3.1.20 | Line Extended Control Register (LCR_EXT) .....                               | 224 |

| 15        | SPI .....                                                                    | 227 |

| 15.1      | Signal Descriptions .....                                                    | 227 |

| 15.2      | Features .....                                                               | 228 |

| 15.3      | Memory Mapped IO Registers.....                                              | 229 |

| 15.3.1.1  | Control Register 0 (CTRLR0).....                                             | 231 |

| 15.3.1.2  | Control Register 1 (CTRLR1).....                                             | 235 |

| 15.3.1.3  | SSI Enable Register (SSIENR) .....                                           | 236 |

| 15.3.1.4  | Microwire Control Register (MWCR) .....                                      | 236 |

|           |                                                                |     |

|-----------|----------------------------------------------------------------|-----|

| 15.3.1.5  | Slave Enable Register (SER) .....                              | 238 |

| 15.3.1.6  | Baud Rate Select (BAUDR) .....                                 | 239 |

| 15.3.1.7  | Transmit FIFO Threshold Level (TXFTLR) .....                   | 240 |

| 15.3.1.8  | Receive FIFO Threshold Level (RXFTLR) .....                    | 240 |

| 15.3.1.9  | Transmit FIFO Level Register (TXFLR) .....                     | 241 |

| 15.3.1.10 | Receive FIFO Level Register (RXFLR) .....                      | 242 |

| 15.3.1.11 | Status Register (SR) .....                                     | 242 |

| 15.3.1.12 | Interrupt Mask Register (IMR) .....                            | 244 |

| 15.3.1.13 | Interrupt Status Register (ISR) .....                          | 245 |

| 15.3.1.14 | Raw Interrupt Status Register (RISR) .....                     | 246 |

| 15.3.1.15 | Transmit FIFO Overflow Interrupt Clear Register (TXOICR) ..... | 247 |

| 15.3.1.16 | Receive FIFO Overflow Interrupt Clear Register (RxoICR) .....  | 247 |

| 15.3.1.17 | Receive FIFO Underflow Interrupt Clear Register (RXUICR) ..... | 248 |

| 15.3.1.18 | Multi-Master Interrupt Clear Register (MSTICR) .....           | 248 |

| 15.3.1.19 | Interrupt Clear Register (ICR) .....                           | 249 |

| 15.3.1.20 | DMA Control Register (DMACR) .....                             | 249 |

| 15.3.1.21 | DMA Transmit Data Level (DMATDLR) .....                        | 250 |

| 15.3.1.22 | DMA Receive Data Level (DMARDLR) .....                         | 250 |

| 15.3.1.23 | Identification Register (IDR) .....                            | 251 |

| 15.3.1.24 | coreKit Version ID register (SSI_COMP_VERSION) .....           | 251 |

| 15.3.1.25 | Data Register (DR0) .....                                      | 252 |

| 15.3.1.26 | Data Register (DR1) .....                                      | 252 |

| 15.3.1.27 | Data Register (DR2) .....                                      | 253 |

| 15.3.1.28 | Data Register (DR3) .....                                      | 254 |

| 15.3.1.29 | Data Register (DR4) .....                                      | 254 |

| 15.3.1.30 | Data Register (DR5) .....                                      | 255 |

| 15.3.1.31 | Data Register (DR6) .....                                      | 256 |

| 15.3.1.32 | Data Register (DR7) .....                                      | 256 |

| 15.3.1.33 | Data Register (DR8) .....                                      | 257 |

| 15.3.1.34 | Data Register (DR9) .....                                      | 258 |

| 15.3.1.35 | Data Register (DR10) .....                                     | 258 |

| 15.3.1.36 | Data Register (DR11) .....                                     | 259 |

| 15.3.1.37 | Data Register (DR12) .....                                     | 260 |

| 15.3.1.38 | Data Register (DR13) .....                                     | 260 |

| 15.3.1.39 | Data Register (DR14) .....                                     | 261 |

| 15.3.1.40 | Data Register (DR15) .....                                     | 262 |

| 15.3.1.41 | Data Register (DR16) .....                                     | 263 |

| 15.3.1.42 | Data Register (DR17) .....                                     | 263 |

| 15.3.1.43 | Data Register (DR18) .....                                     | 264 |

| 15.3.1.44 | Data Register (DR19) .....                                     | 265 |

| 15.3.1.45 | Data Register (DR20) .....                                     | 265 |

| 15.3.1.46 | Data Register (DR21) .....                                     | 266 |

| 15.3.1.47 | Data Register (DR22) .....                                     | 267 |

| 15.3.1.48 | Data Register (DR23) .....                                     | 267 |

| 15.3.1.49 | Data Register (DR24) .....                                     | 268 |

| 15.3.1.50 | Data Register (DR25) .....                                     | 269 |

| 15.3.1.51 | Data Register (DR26) .....                                     | 269 |

| 15.3.1.52 | Data Register (DR27) .....                                     | 270 |

| 15.3.1.53 | Data Register (DR28) .....                                     | 271 |

| 15.3.1.54 | Data Register (DR29) .....                                     | 271 |

| 15.3.1.55 | Data Register (DR30) .....                                     | 272 |

| 15.3.1.56 | Data Register (DR31) .....                                     | 273 |

|           |                                                          |     |

|-----------|----------------------------------------------------------|-----|

| 15.3.1.57 | Data Register (DR32) .....                               | 273 |

| 15.3.1.58 | Data Register (DR33) .....                               | 274 |

| 15.3.1.59 | Data Register (DR34) .....                               | 275 |

| 15.3.1.60 | Data Register (DR35) .....                               | 275 |

| 15.3.1.61 | RX Sample Delay Register (RX_SAMPLE_DLY) .....           | 276 |

| 16        | DMA Controller .....                                     | 277 |

| 16.1      | Features .....                                           | 277 |

| 16.2      | Use .....                                                | 277 |

| 16.3      | Memory Mapped IO Registers .....                         | 279 |

| 16.3.1.1  | Channel0 Source Address (SAR0) .....                     | 281 |

| 16.3.1.2  | Channel0 Destination Address (DAR0) .....                | 281 |

| 16.3.1.3  | Channel0 Linked List Pointer (LLPO) .....                | 282 |

| 16.3.1.4  | Channel0 Control LOWER (CTL_LO) .....                    | 282 |

| 16.3.1.5  | Channel0 Control UPPER (CTL_U0) .....                    | 287 |

| 16.3.1.6  | Channel0 Source Status (SSTAT0) .....                    | 289 |

| 16.3.1.7  | Channel0 Destination Status (DSTAT0) .....               | 289 |

| 16.3.1.8  | Channel0 Source Status Address (SSTATAR0) .....          | 290 |

| 16.3.1.9  | Channel0 Destination Status Address (DSTATAR0) .....     | 290 |

| 16.3.1.10 | Channel0 Configuration LOWER (CFG_LO) .....              | 291 |

| 16.3.1.11 | Channel0 configuration UPPER (CFG_U0) .....              | 293 |

| 16.3.1.12 | Channel0 Source Gather (SGR0) .....                      | 296 |

| 16.3.1.13 | Channel0 Destination Scatter (DSR0) .....                | 297 |

| 16.3.1.14 | Channel1 Source Address (SAR1) .....                     | 298 |

| 16.3.1.15 | Channel1 Destination Address (DAR1) .....                | 298 |

| 16.3.1.16 | Channel1 Linked List Pointer (LLP1) .....                | 299 |

| 16.3.1.17 | Channel1 Control LOWER (CTL_L1) .....                    | 300 |

| 16.3.1.18 | Channel1 Control UPPER (CTL_U1) .....                    | 304 |

| 16.3.1.19 | Channel1 Source Status (SSTAT1) .....                    | 306 |

| 16.3.1.20 | Channel1 Destination Status (DSTAT1) .....               | 306 |

| 16.3.1.21 | Channel1 Source Status Address (SSTATAR1) .....          | 307 |

| 16.3.1.22 | Channel1 Destination Status Address (DSTATAR1) .....     | 307 |

| 16.3.1.23 | Channel1 Configuration LOWER (CFG_L1) .....              | 308 |

| 16.3.1.24 | Channel1 configuration UPPER (CFG_U1) .....              | 310 |

| 16.3.1.25 | Channel1 Source Gather (SGR1) .....                      | 313 |

| 16.3.1.26 | Channel1 Destination Scatter (DSR1) .....                | 314 |

| 16.3.1.27 | Raw Status for IntTfr Interrupt (RAW_TFR) .....          | 314 |

| 16.3.1.28 | Raw Status for IntBlock Interrupt (RAW_BLOCK) .....      | 315 |

| 16.3.1.29 | Raw Status for IntSrcTran Interrupt (RAW_SRC_TRAN) ..... | 316 |

| 16.3.1.30 | Raw Status for IntDstTran Interrupt (RAW_DST_TRAN) ..... | 316 |

| 16.3.1.31 | Raw Status for IntErr Interrupt (RAW_ERR) .....          | 317 |

| 16.3.1.32 | Status for IntTfr Interrupt (STATUS_TFR) .....           | 318 |

| 16.3.1.33 | Status for IntBlock Interrupt (STATUS_BLOCK) .....       | 318 |

| 16.3.1.34 | Status for IntSrcTran Interrupt (STATUS_SRC_TRAN) .....  | 319 |

| 16.3.1.35 | Status for IntDstTran Interrupt (STATUS_DST_TRAN) .....  | 319 |

| 16.3.1.36 | Status for IntErr Interrupt (STATUS_ERR) .....           | 320 |

| 16.3.1.37 | Mask for IntTfr Interrupt (MASK_TFR) .....               | 320 |

| 16.3.1.38 | Mask for IntBlock Interrupt (MASK_BLOCK) .....           | 321 |

| 16.3.1.39 | Mask for IntSrcTran Interrupt (MASK_SRC_TRAN) .....      | 322 |

|           | Mask for IntDstTran Interrupt (MASK_DST_TRAN) .....      | 323 |

| 16.3.1.40 | Mask for IntErr Interrupt (MASK_ERR) .....               | 323 |

| 16.3.1.41 | Clear for IntTfr Interrupt (CLEAR_TFR) .....             | 324 |

| 16.3.1.42 | Clear for IntBlock Interrupt (CLEAR_BLOCK) .....         | 325 |

| 16.3.1.43 | Clear for IntSrcTran Interrupt (CLEAR_SRC_TRAN) .....    | 325 |

| 16.3.1.44 | Clear for IntDstTran Interrupt (CLEAR_DST_TRAN) .....    | 326 |

|           |                                                                         |     |

|-----------|-------------------------------------------------------------------------|-----|

| 16.3.1.45 | Clear for IntErr Interrupt (CLEAR_ERR) .....                            | 326 |

| 16.3.1.46 | Combined Interrupt Status (STATUS_INT) .....                            | 327 |

| 16.3.1.47 | Source Software Transaction Request (REQ_SRC_REG) .....                 | 328 |

| 16.3.1.48 | Destination Software Transaction Request register (REQ_DST_REG) .....   | 328 |

| 16.3.1.49 | Source Single Transaction Request (SGL_REQ_SRC_REG) .....               | 329 |

| 16.3.1.50 | Destination Single Software Transaction Request (SGL_REQ_DST_REG) ..... | 330 |

| 16.3.1.51 | Source Last Transaction Request (LST_SRC_REG) .....                     | 331 |

| 16.3.1.52 | Destination Single Transaction Request (LST_DST_REG) .....              | 331 |

| 16.3.1.53 | DMA Configuration (DMA_CFG_REG) .....                                   | 332 |

| 16.3.1.54 | Channel Enable (CH_EN_REG) .....                                        | 332 |

| 16.3.1.55 | DMA ID (DMA_ID_REG) .....                                               | 333 |

| 16.3.1.56 | DMA Test (DMA_TEST_REG) .....                                           | 334 |

| 16.3.1.57 | DMA Component ID - LOWER (DMA_COMP_ID_L) .....                          | 334 |

| 16.3.1.58 | DMA Component ID - UPPER (DMA_COMP_ID_U) .....                          | 335 |

| 17        | General Purpose I/O (GPIO) .....                                        | 336 |

| 17.1      | Signal Descriptions .....                                               | 336 |

| 17.2      | Features .....                                                          | 336 |

| 17.3      | Memory Mapped IO Registers .....                                        | 336 |

| 17.3.1.1  | Port A Data (GPIO_SWPORTA_DR) .....                                     | 337 |

| 17.3.1.2  | Port A Data Direction (GPIO_SWPORTA_DDR) .....                          | 338 |

| 17.3.1.3  | Port A Data Source (GPIO_SWPORTA_CTL) .....                             | 339 |

| 17.3.1.4  | Interrupt Enable (GPIO_INTEN) .....                                     | 339 |

| 17.3.1.5  | Interrupt Mask (GPIO_INTMASK) .....                                     | 340 |

| 17.3.1.6  | Interrupt Type (GPIO_INTTYPE_LEVEL) .....                               | 341 |

| 17.3.1.7  | Interrupt Polarity (GPIO_INT_POLARITY) .....                            | 342 |

| 17.3.1.8  | Interrupt Status (GPIO_INTSTATUS) .....                                 | 342 |

| 17.3.1.9  | Raw Interrupt Status (GPIO_RAW_INTSTATUS) .....                         | 343 |

| 17.3.1.10 | Debounce Enable (GPIO_DEBOUNCE) .....                                   | 343 |

| 17.3.1.11 | Clear Interrupt (GPIO_PORTA_EOI) .....                                  | 344 |

| 17.3.1.12 | Port A External Port (GPIO_EXT_PORTA) .....                             | 345 |

| 17.3.1.13 | Synchronization Level (GPIO_LS_SYNC) .....                              | 345 |

| 17.3.1.14 | Interrupt both edge type (GPIO_INT_BOTHEDGE) .....                      | 346 |

| 17.3.1.15 | GPIO Configuration Register 2 (GPIO_CONFIG_REG2) .....                  | 347 |

| 17.3.1.16 | GPIO Configuration Register 1 (GPIO_CONFIG_REG1) .....                  | 347 |

| 18        | Timers and PWM .....                                                    | 348 |

| 18.1      | Signal Descriptions .....                                               | 348 |

| 18.2      | Features .....                                                          | 348 |

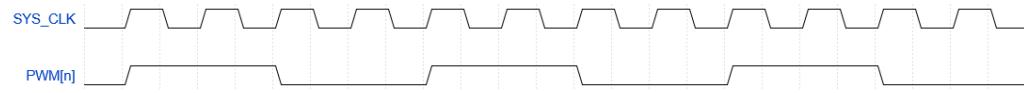

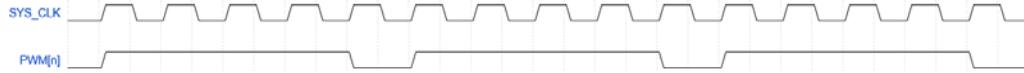

| 18.2.1    | PMW Signaling .....                                                     | 349 |

| 18.2.2    | Functional Operation .....                                              | 349 |

| 18.3      | Use .....                                                               | 350 |

| 18.3.1    | PWM Mode .....                                                          | 350 |

| 18.3.2    | Timer Mode .....                                                        | 351 |

| 18.4      | Memory Mapped IO Registers .....                                        | 351 |

| 18.4.1.1  | Timer 1 Load Count (Timer1LoadCount) .....                              | 352 |

| 18.4.1.2  | Timer 1 Current Value (Timer1CurrentValue) .....                        | 352 |

| 18.4.1.3  | Timer 1 Control (Timer1ControlReg) .....                                | 353 |

| 18.4.1.4  | Timer 1 End Of Interrupt (Timer1EOI) .....                              | 355 |

| 18.4.1.5  | Timer 1 Interrupt Status (Timer1IntStatus) .....                        | 355 |

|           |                                                                      |     |

|-----------|----------------------------------------------------------------------|-----|

| 18.4.1.6  | Timer 2 Load Count (Timer2LoadCount) .....                           | 356 |

| 18.4.1.7  | Timer 2 Current Value (Timer2CurrentValue) .....                     | 356 |

| 18.4.1.8  | Timer 2 Control (Timer2ControlReg) .....                             | 357 |

| 18.4.1.9  | Timer 2 End Of Interrupt (Timer2EOI) .....                           | 357 |

| 18.4.1.10 | Timer 2 Interrupt Status (Timer2IntStatus) .....                     | 358 |

| 18.4.1.11 | Timers Interrupt Status (TimersIntStatus) .....                      | 359 |

| 18.4.1.12 | Timers End Of Interrupt (TimersEOI) .....                            | 359 |

| 18.4.1.13 | Timers Raw (unmasked) Interrupt Status<br>(TimersRawIntStatus) ..... | 360 |

| 18.4.1.14 | Timers Component Version (TimersCompVersion).....                    | 360 |

| 18.4.1.15 | Timer 1 Load Count 2 (Timer1LoadCount2) .....                        | 361 |

| 18.4.1.16 | Timer 2 Load Count 2 (Timer2LoadCount2) .....                        | 361 |

| 19        | Watchdog Timer .....                                                 | 362 |

| 19.1      | Features .....                                                       | 362 |

| 19.1.1    | WDT Enable.....                                                      | 362 |

| 19.1.2    | WDT Timeout Capabilities .....                                       | 362 |

| 19.2      | Use .....                                                            | 363 |

| 19.3      | Memory Mapped IO Registers.....                                      | 363 |

| 19.3.1.1  | Control Register (WDT_CR) .....                                      | 364 |

| 19.3.1.2  | Timeout Range Register (WDT_TORR) .....                              | 365 |

| 19.3.1.3  | Current Counter Value Register (WDT_CCVR) .....                      | 366 |

| 19.3.1.4  | Current Restart Register (WDT_CRR) .....                             | 366 |

| 19.3.1.5  | Interrupt Status Register (WDT_STAT) .....                           | 366 |

| 19.3.1.6  | Interrupt Clear Register (WDT_EOI) .....                             | 367 |

| 19.3.1.7  | Component Parameters (WDT_COMP_PARAM_5) .....                        | 367 |

| 19.3.1.8  | Component Parameters (WDT_COMP_PARAM_4) .....                        | 367 |

| 19.3.1.9  | Component Parameters (WDT_COMP_PARAM_3) .....                        | 368 |

| 19.3.1.10 | Component Parameters (WDT_COMP_PARAM_2) .....                        | 368 |

| 19.3.1.11 | Component Parameters Register 1<br>(WDT_COMP_PARAM_1) .....          | 368 |

| 19.3.1.12 | Component Version Register (WDT_COMP_VERSION) ..                     | 369 |

| 19.3.1.13 | Component Type Register (WDT_COMP_TYPE) .....                        | 369 |

| 20        | Real Time Clock (RTC) .....                                          | 370 |

| 20.1      | Signal Descriptions .....                                            | 370 |

| 20.2      | Features .....                                                       | 370 |

| 20.2.1    | RTC Clock .....                                                      | 371 |

| 20.2.2    | Counter Functionality.....                                           | 371 |

| 20.3      | Use .....                                                            | 372 |

| 20.3.1    | Clock and Calendar.....                                              | 372 |

| 20.3.2    | Alarm .....                                                          | 373 |

| 20.3.3    | Wake Event .....                                                     | 373 |

| 20.4      | Memory Mapped IO Registers.....                                      | 374 |

| 20.4.1.1  | Current Counter Value Register (RTC_CCVR) .....                      | 374 |

| 20.4.1.2  | Current Match Register (RTC_CMR) .....                               | 376 |

| 20.4.1.3  | Counter Load Register (RTC_CLR) .....                                | 376 |

| 20.4.1.4  | Counter Control Register (RTC_CCR) .....                             | 377 |

| 20.4.1.5  | Interrupt Status Register (RTC_STAT) .....                           | 377 |

| 20.4.1.6  | Interrupt Raw Status Register (RTC_RSTAT) .....                      | 378 |

| 20.4.1.7  | End of Interrupt Register (RTC_EOI).....                             | 378 |

| 20.4.1.8  | End of Interrupt Register (RTC_COMP_VERSION) .....                   | 379 |

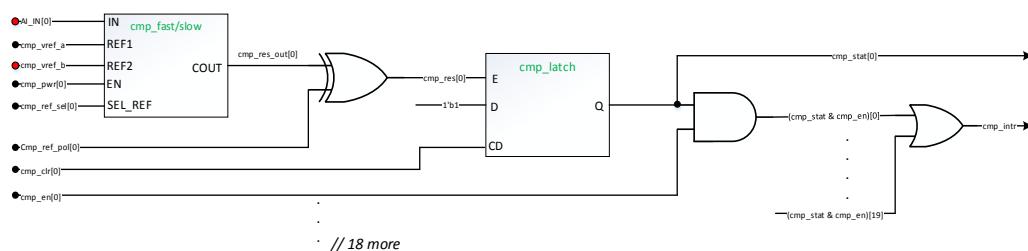

| 21        | Comparators .....                                                    | 380 |

|           |                                                                       |     |

|-----------|-----------------------------------------------------------------------|-----|

| 21.1      | Signal Descriptions .....                                             | 380 |

| 21.2      | Features .....                                                        | 381 |

| 21.3      | Use .....                                                             | 381 |

| 22        | Analog to Digital Convertor (ADC) .....                               | 383 |

| 22.1      | Signal Descriptions .....                                             | 383 |

| 22.2      | Features .....                                                        | 383 |

| 22.3      | Use .....                                                             | 384 |

| 22.4      | Memory Mapped IO Registers.....                                       | 386 |

| 22.4.1.1  | ADC Channel Sequence Table (ADC_SEQ [0..7]) .....                     | 386 |

| 22.4.1.2  | ADC Command Register (ADC_CMD) .....                                  | 388 |

| 22.4.1.3  | ADC Interrupt Status Register (ADC_INTR_STATUS) ....                  | 390 |

| 22.4.1.4  | ADC Interrupt Enable (ADC_INTR_ENABLE) .....                          | 391 |

| 22.4.1.5  | ADC Sample Register (ADC_SAMPLE) .....                                | 392 |

| 22.4.1.6  | ADC Calibraton Data Register (ADC_CALIBRATION) ....                   | 392 |

| 22.4.1.7  | ADC FIFO Count Register (ADC_FIFO_COUNT) .....                        | 393 |

| 22.4.1.8  | ADC Operating Mode Register (ADC_OP_MODE) .....                       | 393 |

| 23        | Interrupt Routing .....                                               | 395 |

| 23.1      | Interrupt Routing .....                                               | 395 |

| 23.1.1    | Host Processor Interrupts .....                                       | 395 |

| 23.1.2    | SoC Interrupts and Routing .....                                      | 396 |

| 24        | System Control Subsystem.....                                         | 398 |

| 24.1      | Features .....                                                        | 398 |

| 24.2      | Memory Mapped IO Registers.....                                       | 399 |

| 24.3      | Register Detailed Description .....                                   | 402 |

| 24.3.1.1  | Hybrid Oscillator Configuration 0 (OSCO_CFG0).....                    | 402 |

| 24.3.1.2  | Hybrid Oscillator status 1 (OSCO_STAT1) .....                         | 405 |

| 24.3.1.3  | Hybrid Oscillator configuration 1 (OSCO_CFG1) .....                   | 406 |

| 24.3.1.4  | RTC Oscillator status 0 (OSC1_STAT0) .....                            | 408 |

| 24.3.1.5  | RTC Oscillator Configuration 0 (OSC1_CFG0) .....                      | 409 |

| 24.3.1.6  | Peripheral Clock Gate Control<br>(CCU_PERIPH_CLK_GATE_CTL) .....      | 410 |

| 24.3.1.7  | Peripheral Clock Divider Control 0<br>(CCU_PERIPH_CLK_DIV_CTL0) ..... | 413 |

| 24.3.1.8  | Peripheral Clock Divider Control 1<br>(CCU_GPIO_DB_CLK_CTL) .....     | 414 |

| 24.3.1.9  | External Clock Control Register<br>(CCU_EXT_CLOCK_CTL) .....          | 415 |

| 24.3.1.10 | System Low Power Clock Control (CCU_LP_CLK_CTL) ..                    | 416 |

| 24.3.1.11 | Wake Mask register (WAKE_MASK) .....                                  | 418 |

| 24.3.1.12 | AHB Control Register (CCU_Mlayer_AHB_CTL) .....                       | 419 |

| 24.3.1.13 | System Clock Control Register (CCU_SYS_CLK_CTL)....                   | 420 |

| 24.3.1.14 | Clocks Lock Register (OSC_LOCK_0) .....                               | 421 |

| 24.3.1.15 | SoC Control Register (SOC_CTRL) .....                                 | 423 |

| 24.3.1.16 | SoC Control Register Lock (SOC_CTRL_LOCK).....                        | 424 |

| 24.3.1.17 | General Purpose Sticky Register 0 (GPS0) .....                        | 424 |

| 24.3.1.18 | General Purpose Sticky Register 1 (GPS1) .....                        | 425 |

| 24.3.1.19 | General Purpose Sticky Register 2 (GPS2) .....                        | 425 |

| 24.3.1.20 | General Purpose Sticky Register 3 (GPS3) .....                        | 425 |

| 24.3.1.21 | General Purpose Scratchpad Register 0 (GPO) .....                     | 426 |

| 24.3.1.22 | General Purpose Scratchpad Register 1 (GP1) .....                     | 426 |

| 24.3.1.23 | General Purpose Scratchpad Register 2 (GP2) .....                     | 426 |

|                                                                                           |     |

|-------------------------------------------------------------------------------------------|-----|

| 24.3.1.24 General Purpose Scratchpad Register 3 (GP3) .....                               | 427 |

| 24.3.1.25 Write-Once Scratchpad Register (WO_SP) .....                                    | 427 |

| 24.3.1.26 Write Once Sticky Register (WO_ST) .....                                        | 427 |

| 24.3.1.27 Comparator enable (CMP_EN).....                                                 | 428 |

| 24.3.1.28 Comparator reference select (CMP_REF_SEL).....                                  | 428 |

| 24.3.1.29 Comparator reference polarity select register (CMP_REF_POL) .....               | 429 |

| 24.3.1.30 Comparator power enable register (CMP_PWR) .....                                | 429 |

| 24.3.1.31 Comparator clear register (CMP_STAT_CLR) .....                                  | 430 |

| 24.3.1.32 Host Processor Interrupt Routing Mask 0 (INT_I2C_MST_0_MASK) .....              | 435 |

| 24.3.1.33 Host Processor Interrupt Routing Mask 2 (INT_SPI_MST_0_MASK) .....              | 436 |

| 24.3.1.34 Host Processor Interrupt Routing Mask 4 (INT_SPI_SLV_MASK) .....                | 437 |

| 24.3.1.35 Host Processor Interrupt Routing Mask 5 (INT_UART_0_MASK) .....                 | 437 |

| 24.3.1.36 Host Processor Interrupt Routing Mask 6 (INT_UART_1_MASK) .....                 | 438 |

| 24.3.1.37 Host Processor Interrupt Routing Mask 8 (INT_GPIO_MASK) .....                   | 439 |

| 24.3.1.38 Host Processor Interrupt Routing Mask 9 (INT_TIMER_MASK) .....                  | 440 |

| 24.3.1.39 Host Processor Interrupt Routing Mask 11 (INT_RTC_MASK) .....                   | 441 |

| 24.3.1.40 Host Processor Interrupt Routing Mask 12 (INT_WATCHDOG_MASK) .....              | 441 |

| 24.3.1.41 Host Processor Interrupt Routing Mask 13 (INT_DMA_CHANNEL_0_MASK) .....         | 442 |

| 24.3.1.42 Host Processor Interrupt Routing Mask 14 (INT_DMA_CHANNEL_1_MASK) .....         | 443 |

| 24.3.1.43 Host Processor Interrupt Routing Mask 23 (INT_COMPARATORS_HOST_HALT_MASK) ..... | 443 |

| 24.3.1.44 Host Processor Interrupt Routing Mask 25 (INT_COMPARATORS_HOST_MASK) .....      | 444 |

| 24.3.1.45 Host Processor Interrupt Routing Mask 26 (INT_HOST_BUS_ERR_MASK) .....          | 445 |

| 24.3.1.46 Host Processor Interrupt Routing Mask 27 (INT_DMA_ERROR_MASK) .....             | 445 |

| 24.3.1.47 Host Processor Interrupt Routing Mask 28 (INT_SRAM_CONTROLLER_MASK).....        | 446 |

| 24.3.1.48 Host Processor Interrupt Routing Mask 29 (INT_FLASH_CONTROLLER_0_MASK) .....    | 447 |

| 24.3.1.49 Host Processor Interrupt Routing Mask 31 (INT_AON_TIMER_MASK) .....             | 447 |

| 24.3.1.50 Host Processor Interrupt Routing Mask 32 (INT_ADC_PWR_MASK) .....               | 448 |

| 24.3.1.51 Host Processor Interrupt Routing Mask 33 (INT_ADC_CALIB_MASK) .....             | 449 |

| 24.3.1.52 Interrupt Mask Lock Register (LOCK_INT_MASK_REG) ..                             | 449 |

| 24.3.1.53 AON Voltage Regulator (AON_VR) .....                                            | 450 |

| 24.3.1.54 Power Management Wait (PM_WAIT) .....                                           | 452 |

| 24.3.1.55 Processor Status (P_STS) .....                                                  | 453 |

| 24.3.1.56 Reset Control (RSTC) .....                                                      | 454 |

| 24.3.1.57 Reset Status (RSTS) .....                                                       | 456 |

|           |                                                                   |     |

|-----------|-------------------------------------------------------------------|-----|

| 24.3.1.58 | Power Management Lock (PM_LOCK) .....                             | 457 |

| 24.3.1.59 | Always on counter register (AONC_CNT) .....                       | 458 |

| 24.3.1.60 | Always on counter enable (AONC_CFG) .....                         | 458 |

| 24.3.1.61 | Always on periodic timer (AONPT_CNT) .....                        | 459 |

| 24.3.1.62 | Always on periodic timer status register (AONPT_STAT) .....       | 459 |

| 24.3.1.63 | Always on periodic timer control (AONPT_CTRL) .....               | 460 |

| 24.3.1.64 | Always on periodic timer configuration register (AONPT_CFG) ..... | 461 |

| 24.3.1.65 | Peripheral Configuration (PERIPH_CFG0) .....                      | 461 |

| 24.3.1.66 | Configuration Lock (CFG_LOCK) .....                               | 462 |

| 24.3.1.67 | Pin Mux Pullup (PMUX_PULLUP) .....                                | 463 |

| 24.3.1.68 | Pin Mux Slew Rate (PMUX_SLEW) .....                               | 463 |

| 24.3.1.69 | Pin Mux Input Enable (PMUX_IN_EN) .....                           | 464 |

| 24.3.1.70 | Pin Mux Select (PMUX_SEL [0..1]) .....                            | 464 |

| 24.3.1.71 | Pin Mux Pullup Lock (PMUX_PULLUP_LOCK) .....                      | 467 |

| 24.3.1.72 | Pin Mux Slew Rate Lock (PMUX_SLEW_LOCK) .....                     | 467 |

| 24.3.1.73 | Pin Mux Select Lock 0 (PMUX_SEL_0_LOCK) .....                     | 468 |

| 24.3.1.74 | Pin Mux Slew Rate Lock (PMUX_IN_EN_LOCK) .....                    | 470 |

| 24.3.1.75 | Identification Register (ID) .....                                | 471 |

| 24.3.1.76 | Revision Register (REV) .....                                     | 471 |

| 24.3.1.77 | Flash Size Register (FS) .....                                    | 472 |

| 24.3.1.78 | RAM Size Register (RS) .....                                      | 472 |

| 24.3.1.79 | Code OTP Size Register (COTPS) .....                              | 473 |

| 24.3.1.80 | Data OTP Size Register (DOTPS) .....                              | 473 |

| 25        | AON Counters .....                                                | 474 |

| 25.1      | Features .....                                                    | 474 |

| 25.1.1    | AON Counter .....                                                 | 474 |

| 25.1.2    | AON Periodic Timer .....                                          | 474 |

## Revision History

---

| Date     | Revision | Description                       |

|----------|----------|-----------------------------------|

| Jan 2016 | 002      | Initial public release            |

| Dec 2015 | 001      | Internal release available by NDA |

§

# 1 Introduction

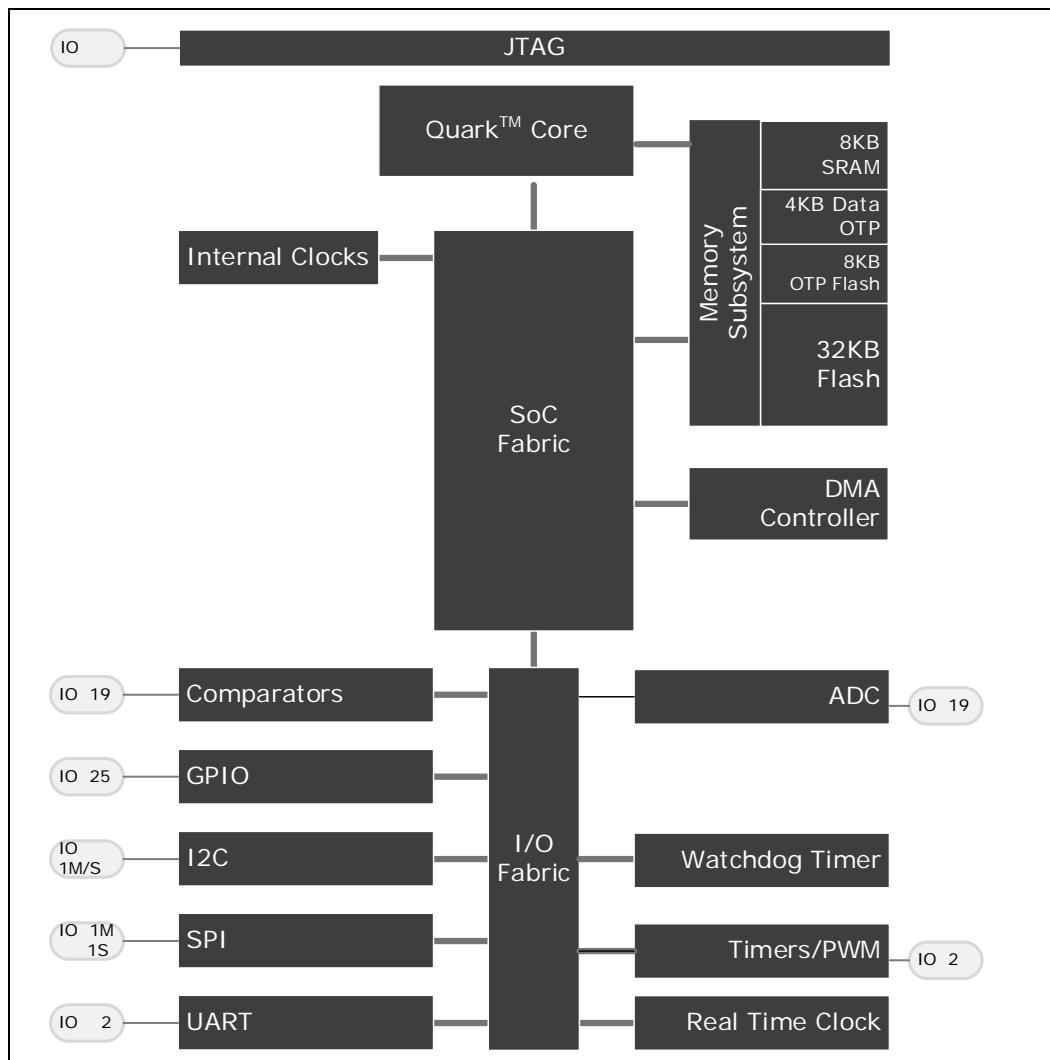

The Intel® Quark™ microcontroller D2000 is an ultra-low power Intel Architecture (IA) SoC that integrates an Intel® Quark processor core, Memory Subsystem with on-die volatile and non-volatile storage, and I/O interfaces into a single low-cost system-on-chip solution.

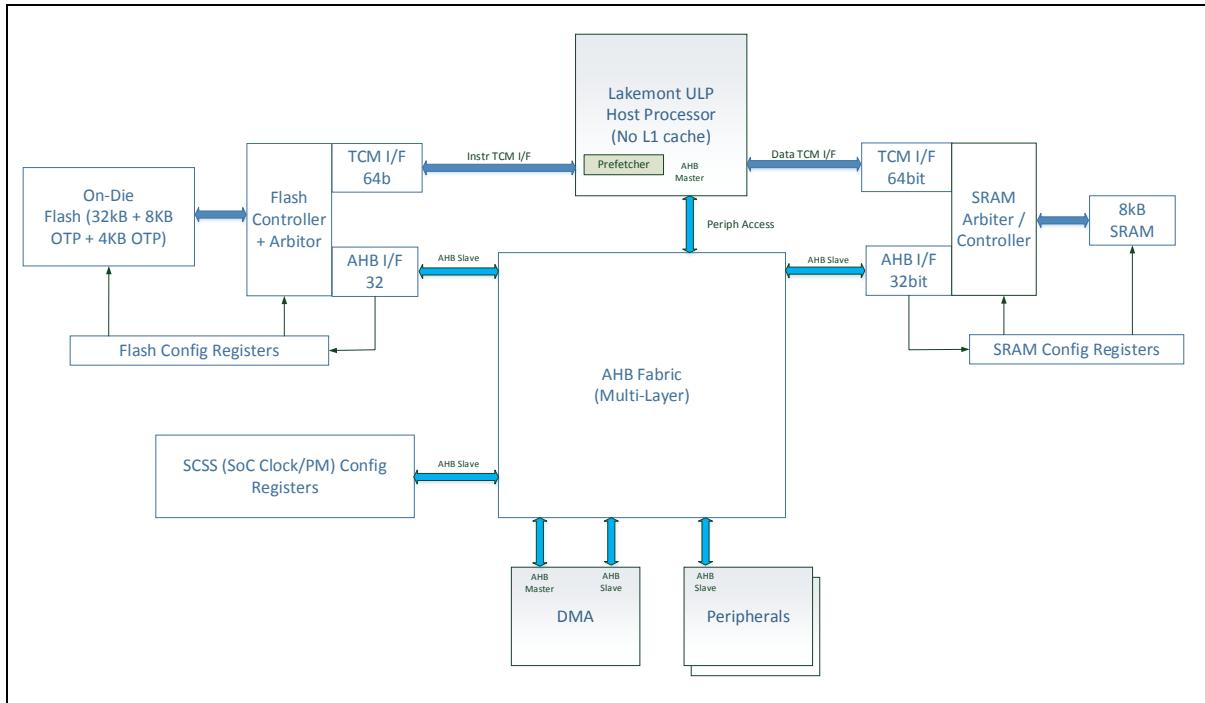

Figure 1 shows the system level block diagram of the SoC. Refer to the subsequent chapters for detailed information on the individual functional blocks.

**Figure 1. SoC Block Diagram**

## 1.1 Feature Overview

### 1.1.1 Clock Oscillators

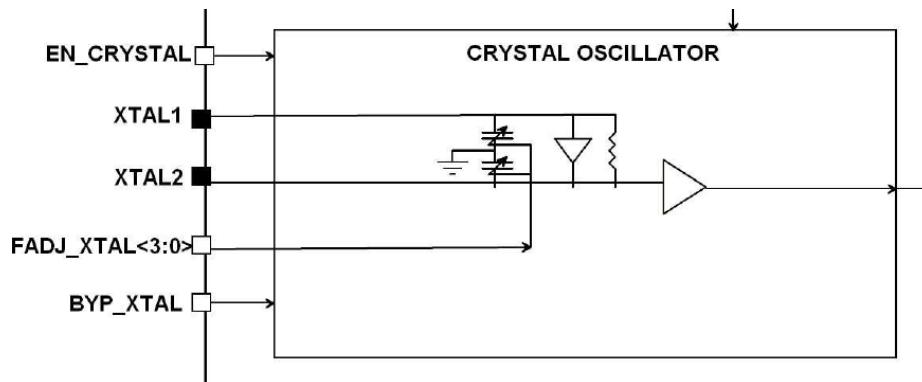

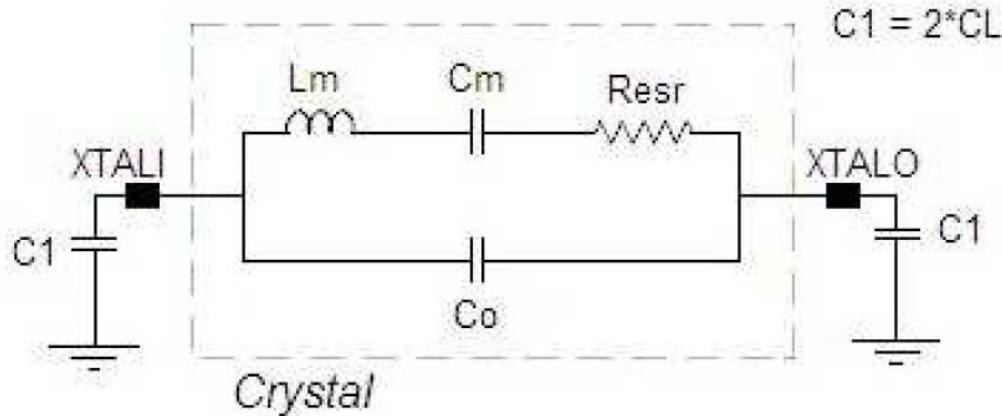

- 32 MHz Clock (system clock) generated by on-die Hybrid Oscillator which works in either:

- Silicon mode (external crystal not needed) (generates 4/8/16/32 MHz clock output as configured) or

- Crystal mode (external 32MHz crystal required).

- 32.768 kHz RTC Clock generated by on-die RTC Crystal oscillator (external 32.768kHz crystal required). SoC is designed to work without RTC clock, if there is no use-case for RTC clock.

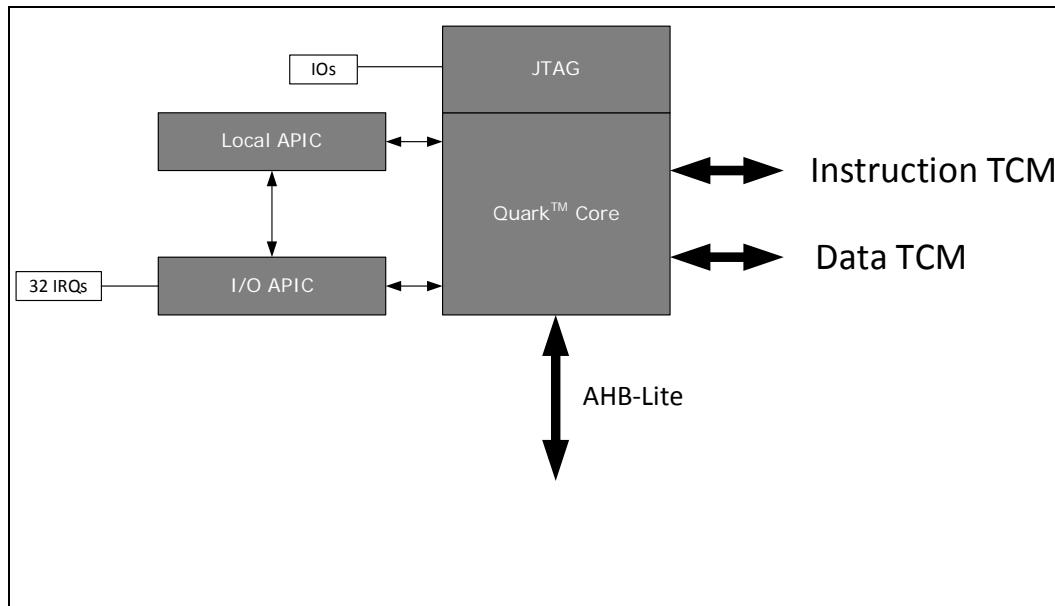

### 1.1.2 Quark Processor Core

- 32 MHz Clock Frequency

- 32-bit Address Bus

- Pentium 586 ISA Compatible without x87 Floating Point Unit

- Integrated Local APIC and I/O APIC

- 1 32-bit timer in Local APIC running with system/core clock

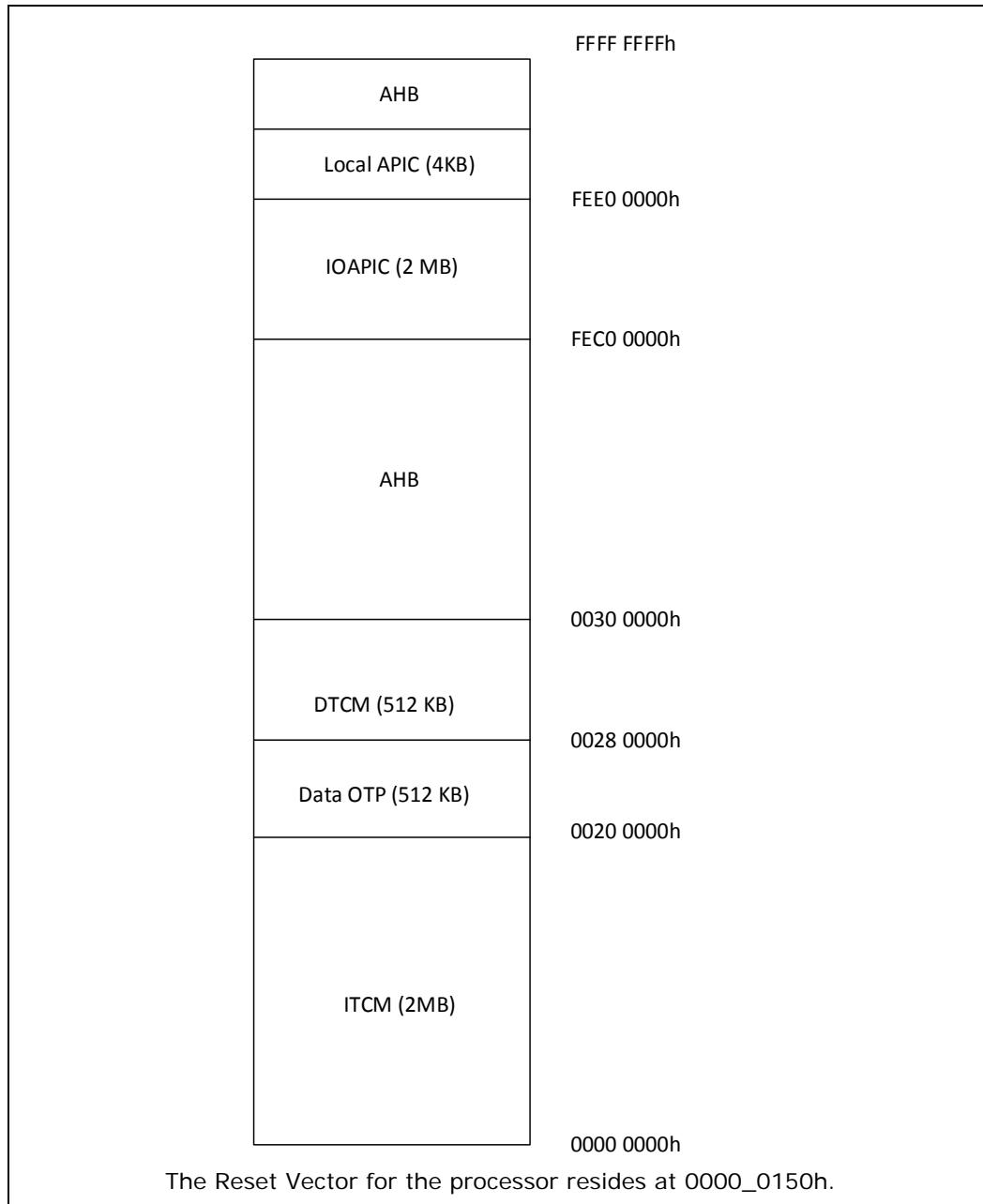

### 1.1.3 Memory Subsystem

- 32 KB of 64b wide on-die Flash

- Supports Page Erase and Program cycles

- Supports configurable wait states to allow Flash to run at various frequencies. At 32MHz, 2-wait-states are introduced for all accesses

- 4 configurable Protection regions for Flash access control

- 8 KB Code OTP with independent read-disable of the two 4KB regions

- 4 KB Data OTP (One-time-programmable) memory

- 8 KB of on-die SRAM with 64b interface with 0-wait state in case of no arbitration conflict

- 4 configurable Protection regions for SRAM access control

### 1.1.4 I<sup>2</sup>C

- One I<sup>2</sup>C Interface

- Three I<sup>2</sup>C speeds supported : Standard Mode (100 Kbps), Fast Mode (400 Kbps) and Fast Mode Plus (1 Mbps)

- 7-bit and 10-bit Addressing Modes Supported

- Supports Master or Slave operation

- FIFO mode support (16B TX and RX FIFO's)

- Supports HW DMA with configurable FIFO thresholds

### 1.1.5 UART

- Two 16550 compliant UART interfaces

- Supports baud rates from 300 to 2M with less than 2% frequency error

- Support for hardware and software flow control

- FIFO mode support (16B TX and RX FIFO's)

- Supports HW DMA with configurable FIFO thresholds

- Supports 9-bit serial operation mode

- Supports RS485

- Support for DTR/DCD/DSR/RI Modem Control Pins through GPIO pins controlled by Software

### 1.1.6 SPI

- One SPI Master Interfaces with support for SPI clock frequencies up to 16 MHz

- One SPI Slave Interface with support for SPI clock frequencies up to 3.2 MHz

- Support for 4-bit up to 32-bit Frame Size

- Up to four Slave Select pins per Master interface

- FIFO mode support (Independent 32B TX and RX FIFO's)

- Supports HW DMA with configurable FIFO thresholds

### 1.1.7 DMA Controller

- Provides 2 Unidirectional Channels

- Provides support for 16 HW Handshake Interfaces

- tx and rx channels of I<sup>2</sup>C controller, SPI Slave controller, SPI Master controller, two UART controllers use this interface

- Supports Memory to Memory, Peripheral to Memory, Memory to Peripheral and Peripheral to Peripheral transfers

- Dedicated Hardware Handshaking interfaces with peripherals plus Software Handshaking Support

- Supports Single and Multi-Block Transfers

### 1.1.8 GPIO Controller

- Provides 25 independently configurable GPIO

- All GPIOs are interrupt capable supporting level sensitive and edge triggered modes

- Debounce logic for interrupt source

- All 25 GPIOs are Always-on interrupt and wake capable

### 1.1.9 Timers

- Two 32-bit Timers running at system clock (running in timer mode or PWM mode)

- Supports an additional 32-bit Always-On Counter running with 32.768 kHz clock

- Supports an additional 32-bit Always-On Periodic Timer running with 32.768 kHz clock and with interrupt and wake capability

### 1.1.10 Pulse Width Modulation (PWM)

- Two 32-bit Timers running at system clock can be configured to generate two PWM outputs

### 1.1.11 Watchdog Timer

- Configurable Watchdog timer with support to trigger an interrupt and/or a system reset upon timeout

### 1.1.12 Real Time Clock (RTC)

- 32-bit Counter running from 1Hz up to 32.768 kHz

- Supports interrupt and wake event generation upon match of programmed value

- Only requires 32.768 kHz clock to be running to generate interrupt and wake events

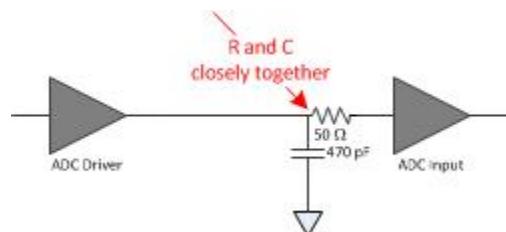

### 1.1.13 Analog to Digital Convertor (ADC)

- 19 Analog Input channels

- Selectable 6/8/10/12-bit resolution

- Supports maximum of 2.28 Mega Samples Per Second (MSps) at 12-bit resolution and 4 MSps at 6-bit resolution

- Differential Non-Linearity DNL of +/- 1.0 LSB

- Integral Non-Linearity INL of +/- 2.0 LSB

- SINAD of 68 dBFS

- Offset Error of +/- 2 LSB (calibration enabled), +/- 64 LSB (calibration disabled)

- Full-scale input range of 0 to AVDD.

### 1.1.14 Analog Comparators

- Provides 19 Analog Comparators

- Six high performance comparators

- 13 low power comparators

- Configurable polarity

- Interrupt and Wake Event capable

### 1.1.15 Interrupt Routing

- Configurable Routing of SoC Interrupts with capability to route to the Interrupt Controller of the Quark Processor.

- SoC events can be routed as: Interrupts to the Quark Processor, debug break events to the Quark Processor or SoC Warm Reset requests.

### 1.1.16 Power Management

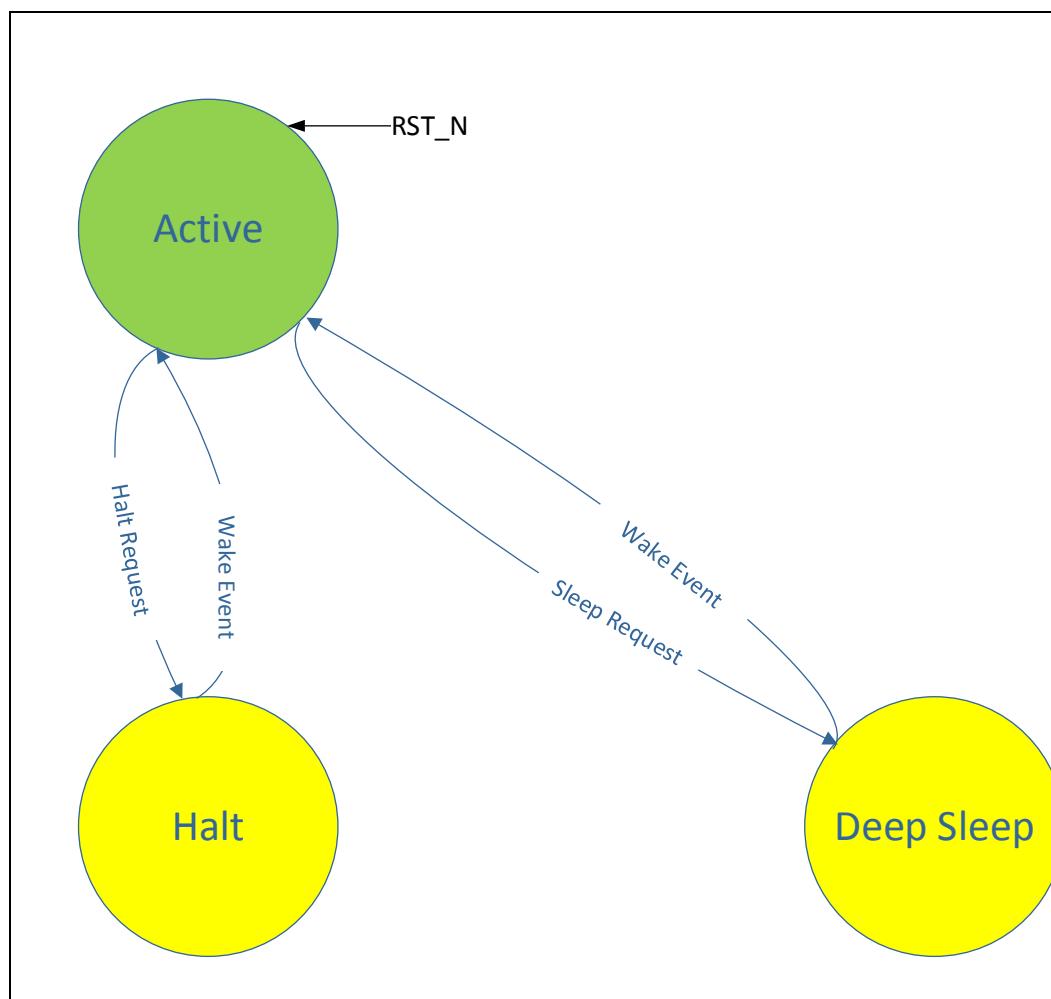

- SoC System States : RUN, Low Power Compute, HALT, Low Power Wait, Deep Sleep (RTC or NORTC) state.

- Processor States : C0 – C2

- Supports Coin-cell Battery source (2.0V to 3.6V range)

| Scenario                                                                                                                                                                                      | Max Current Draw |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Active/RUN state: All SoC components including ADC, Comparators, clock oscillators, peripheral enabled and core running at 32MHz                                                              | < 30 mA          |

| Idle/Sleep state: Most SoC components such as ADC, hybrid oscillator, RTC oscillator, peripherals are powered down or clock gated. Core halted. Only 1 low power-comparator enabled for wake. | < 3.5 $\mu$ A    |

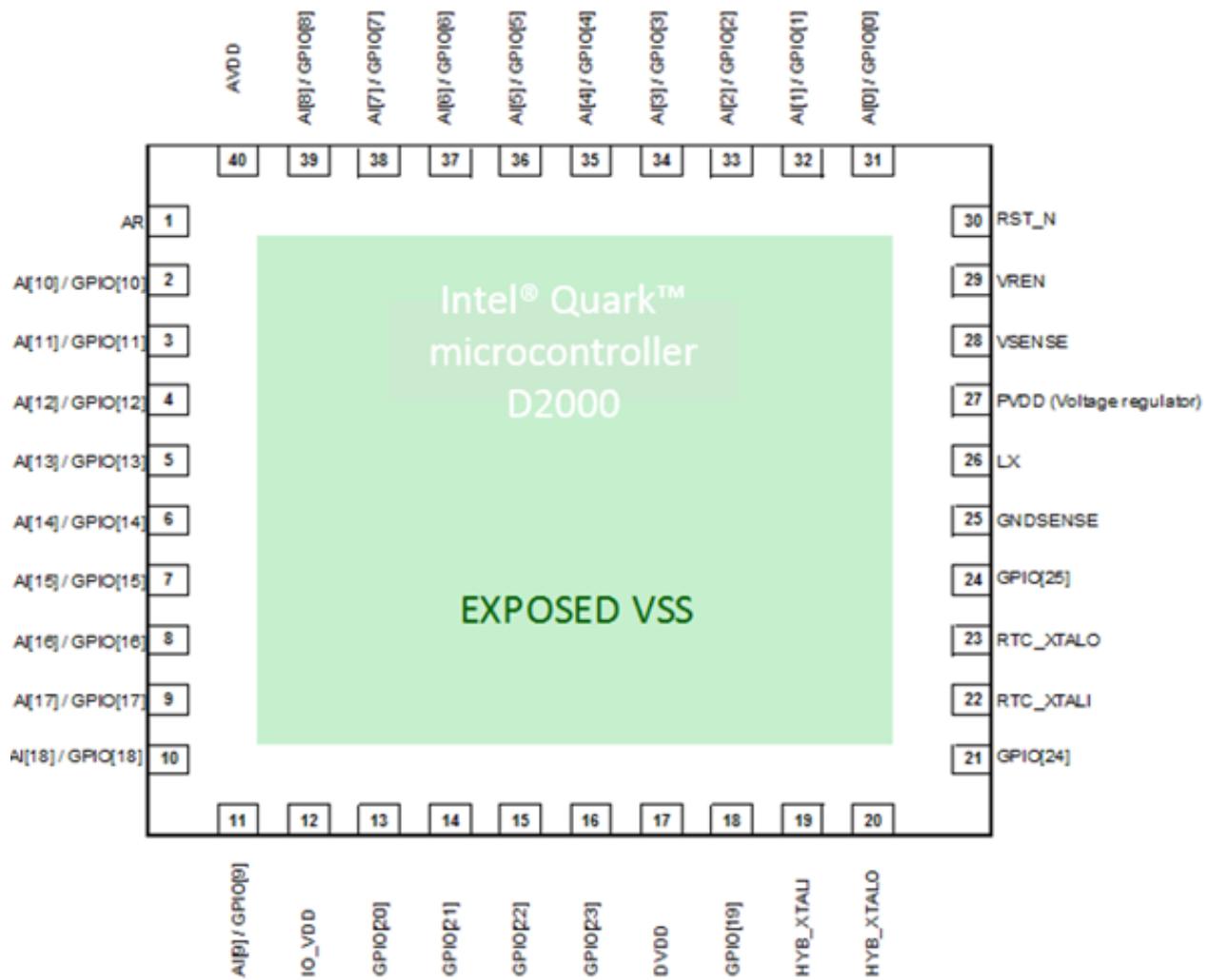

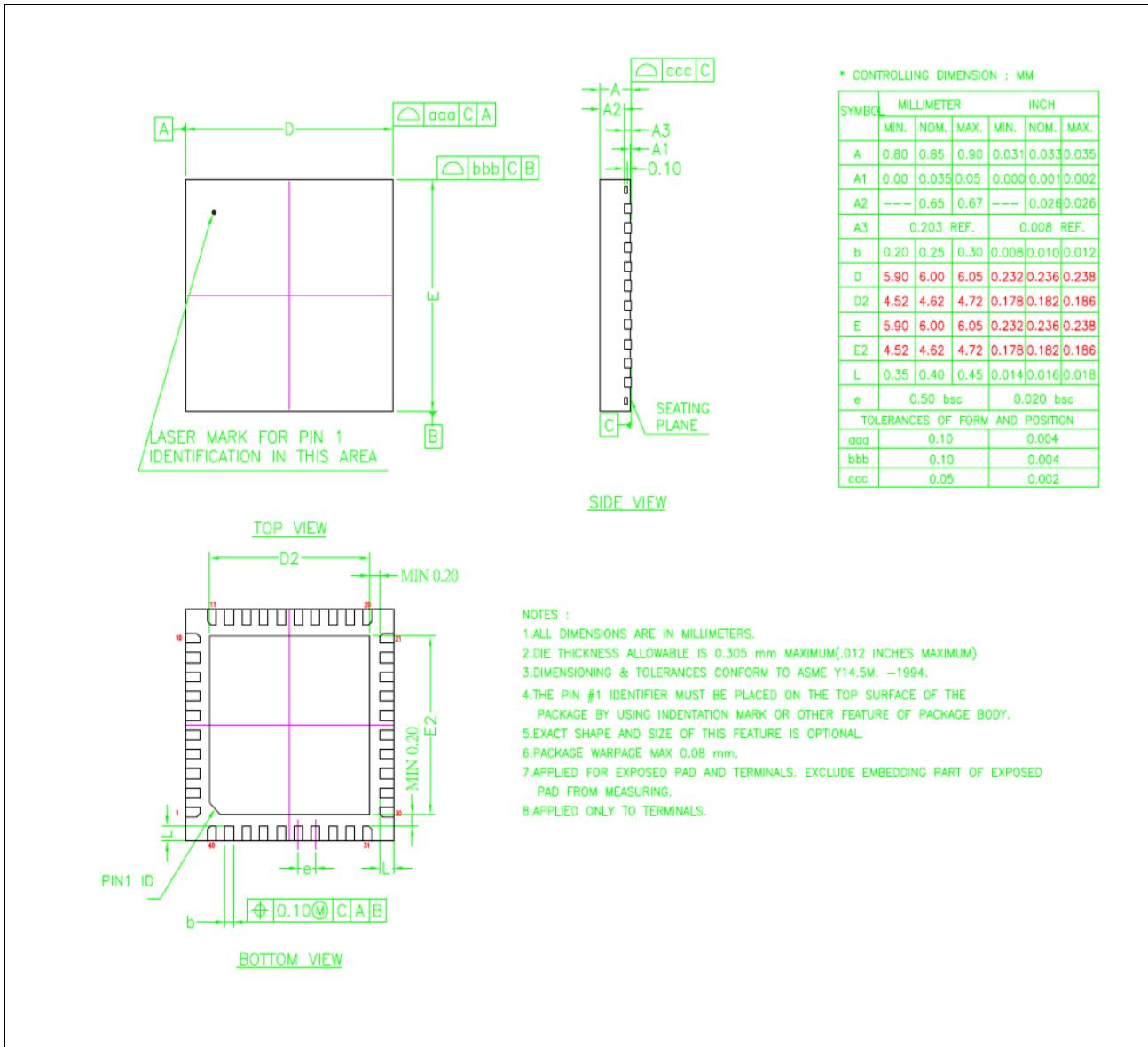

### 1.1.17 Package

40-pin Quad Flat No-Leads (QFN) package.

§

## 2 Physical Interfaces

### 2.1 Pin States Through Reset

All functional IOs will come up in input mode after reset except JTAG TDO output which is kept tristated.

All Digital IO include a configurable pullup (49K ohm typ; 34K-74Kohm range) with pull-up disabled by default, except for F\_20, F\_22, F\_23 pins (TRST\_N, TMS, TDI)) where pull-up is enabled by default.

The state of all IOs is retained whenever SoC goes into low power states.

### 2.2 External Interface Signals

The following table gives the definition of external interface signals of Intel® Quark™ microcontroller D2000. Not all interfaces are available simultaneously through external pins of Intel® Quark™ microcontroller D2000. For pin multiplexing options, refer to [Chapter 3](#).

**Table 1. List of User Mode External Interfaces**

| Interface | Pin Name | Type   | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power     | VSS      | Ground | QFN package ground plane                                                                                                                                                                                                                                                                                                                                                                                                        |

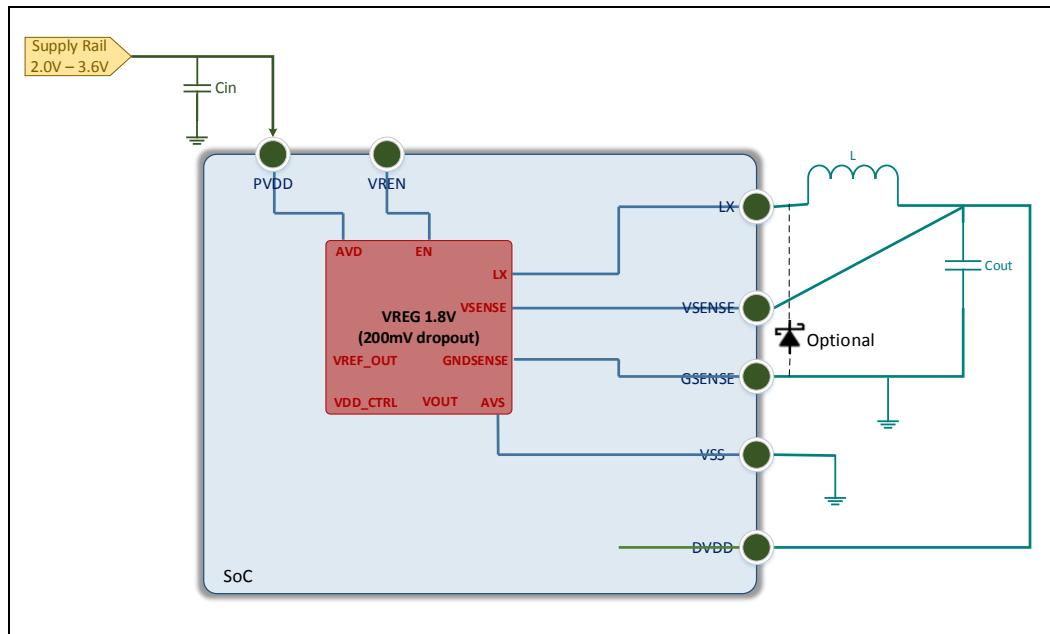

|           | PVDD     | Supply | 2.0-3.6 V unregulated battery supply rail input (can lower to 1.8V if analog comparators are not used). This rail is used only by internal voltage regulator. There is a mechanism to disable internal voltage regulator and feed IOVDD/AVDD/DVDD by platform directly. PVDD is to be supplied even if Internal voltage regulator is not enabled as internal VR is used to generate internal voltage reference for comparators. |

|           | AVDD     | Supply | 2.0-3.6V Analog Voltage Rail Input powering both ADC and Comparator - ADC supports 1.8V to 3.3V range, but Comparator only supports 2V to 3.3V. AVDD can be an AC isolated version of PVDD.                                                                                                                                                                                                                                     |

| Interface | Pin Name  | Type         | Description                                                                                                                                                                                          |

|-----------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | IOVDD     | Supply       | Analog (Driver) side Voltage Rail Input for IO ring (1.8V to 3.3V Nominal +/- 10%). All digital IO pads use IOVDD only. IOVDD can be an AC isolated version of PVDD but is not required.             |

|           | VSENSE    | Analog input | Voltage Regulator Voltage Sense Input - Feedback of Load side of inductor.                                                                                                                           |

|           | GSENSE    | Analog input | core power ground sense                                                                                                                                                                              |

|           | LX        | Supply       | Core voltage regulator output                                                                                                                                                                        |

|           | VREN      | Analog input | Internal Voltage regulator enable:<br>PVDD = enable<br>VSS/GND = disable<br>VREN cannot be dynamically changed. VREN has to be stable/static when PVDD becomes stable.                               |

|           | DVDD      | Supply       | 1.8 V (nominal) +/- 10% regulated core power supply. In Deep Sleep state, it can be configured to go to 1.35V (nominal) +/- 10% to reduce sleep/leakage power.                                       |

|           | DVDD_2    | Supply       | 1.8 V (nominal) +/- 10% regulated core power supply. Connected to same source as DVDD pin. In Deep Sleep state, it can be configured to go to 1.35V (nominal) +/- 10% to reduce sleep/leakage power. |

| Clocking  | HYB_XTALI | Logic input  | Crystal/oscillator input for System Clock. If no external XTAL is connected, keep these pins as no-connect.                                                                                          |

|           | HYB_XTALO | Logic output | Crystal output for System clock. If no external XTAL is connected, keep these pins as no-connect.                                                                                                    |

|           | RTC_XTALI | Logic input  | 32.768 kHz Crystal/oscillator input for RTC clock. If RTC XTAL is not connected, this pin has to be grounded (to 0).                                                                                 |

| Interface | Pin Name    | Type         | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | RTC_XTALO   | Logic output | Crystal output for RTC clock. If RTC XTAL is not connected, this pin has to be grounded (to 0).                                                                                                                                                                                                                                                                                                                                    |

|           | SYS_CLK_OUT | Logic Output | Divided (1:1, 1:2, 1:4) version of 32MHz system clock output                                                                                                                                                                                                                                                                                                                                                                       |

|           | RTC_CLK_OUT | Logic Output | 32.768 kHz RTC clock output                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reset     | RST_N       | Analog input | <p>Active Low reset input with Hysteresis. Tie to PVDD for internal power-on reset.</p> <p>&lt;0.788V = reset<br/>&gt;1.112V = not reset</p> <p>RST_N is connected to an internal comparator which compares RST_N voltage level to an internal reference to assert/deassert internal SOC reset. There is an internal mechanism to assert reset if PVDD is power recycled (power on reset) irrespective of RST_N voltage level.</p> |

| GPIO      | GPIO[24:0]  | Logic I/O    | General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                |

| I2C       | I2C_SCL     | Logic I/O    | Open drain clock                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | I2C_SDA     | Logic I/O    | Open drain data                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PWM       | PWM1        | Logic Output | PWM Output 1                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | PWM0        | Logic Output | PWM Output 0                                                                                                                                                                                                                                                                                                                                                                                                                       |

| UART      | UART_A_TXD  | Logic output | UART A single-ended Transmit data (RS232 or RS485). In RS485 mode, differential driver is outside SoC.                                                                                                                                                                                                                                                                                                                             |

|           | UART_A_RXD  | Logic input  | UART A single-ended Receive data (RS232 or RS485). In RS485 mode, differential receiver is outside SoC.                                                                                                                                                                                                                                                                                                                            |

|           | UART_A_RTS  | Logic output | UART A Request to send (RS232)                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | UART_A_CTS  | Logic input  | UART A Clear to send (RS232)                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | UART_A_DE   | Logic Output | UART A Driver Enable (RS485 mode). Used to control the differential driver of RS485 in platform/board. Polarity is configurable. This is multiplexed onto UART_A_RTS pin                                                                                                                                                                                                                                                           |

| Interface  | Pin Name      | Type         | Description                                                                                                                                                                                                                 |

|------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |               |              | depending on RS485 or RS232 mode of operation.                                                                                                                                                                              |

|            | UART_A_RXE    | Logic Output | UART B Receiver Enable (RS485 mode). Used to control the differential receiver of RS485 in platform/board. Polarity is configurable. This is multiplexed onto UART_B_CTS pin depending on RS485 or RS232 mode of operation. |

|            | UART_B_TXD    | Logic output | UART B single-ended Transmit data (RS232 or RS485). In RS485 mode, differential driver is outside SoC.                                                                                                                      |

|            | UART_B_RXD    | Logic input  | UART B single-ended Receive data (RS232 or RS485). In RS485 mode, differential receiver is outside SoC.                                                                                                                     |

|            | UART_B_RTS    | Logic output | UART B Request to send (RS232)                                                                                                                                                                                              |

|            | UART_B_CTS    | Logic input  | UART B Clear to send (RS232)                                                                                                                                                                                                |

|            | UART_B_DE     | Logic Output | UART B Driver Enable (RS485 mode). Used to control the differential driver of RS485 in platform/board. This is multiplexed onto UART_B_RTS pin depending on RS485 or RS232 mode of operation.                               |

|            | UART_B_RXE    | Logic Output | UART A Receiver Enable (RS485 mode). Used to control the differential receiver of RS485 in platform/board. This is multiplexed onto UART_B_CTS pin depending on RS485 or RS232 mode of operation.                           |

| Slave SPI  | SPI_S_SCLK    | Logic input  | Slave SPI Clock                                                                                                                                                                                                             |

|            | SPI_S_SDIN    | Logic input  | Slave SPI Receive data                                                                                                                                                                                                      |

|            | SPI_S_SCS     | Logic input  | Slave SPI Slave Chip Select                                                                                                                                                                                                 |

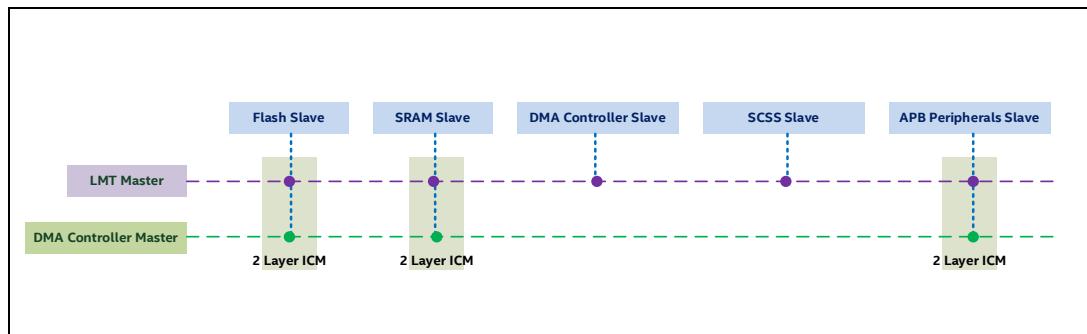

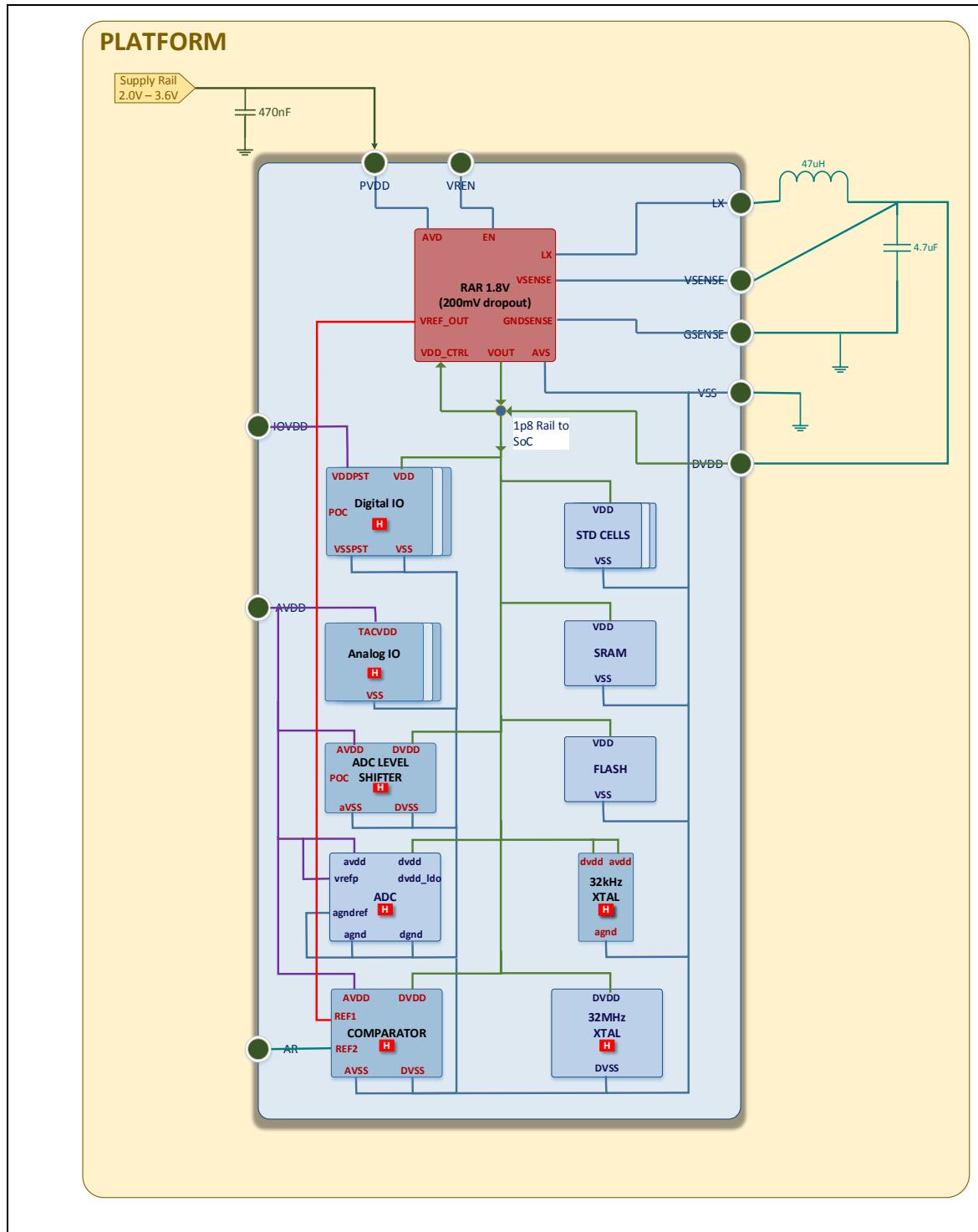

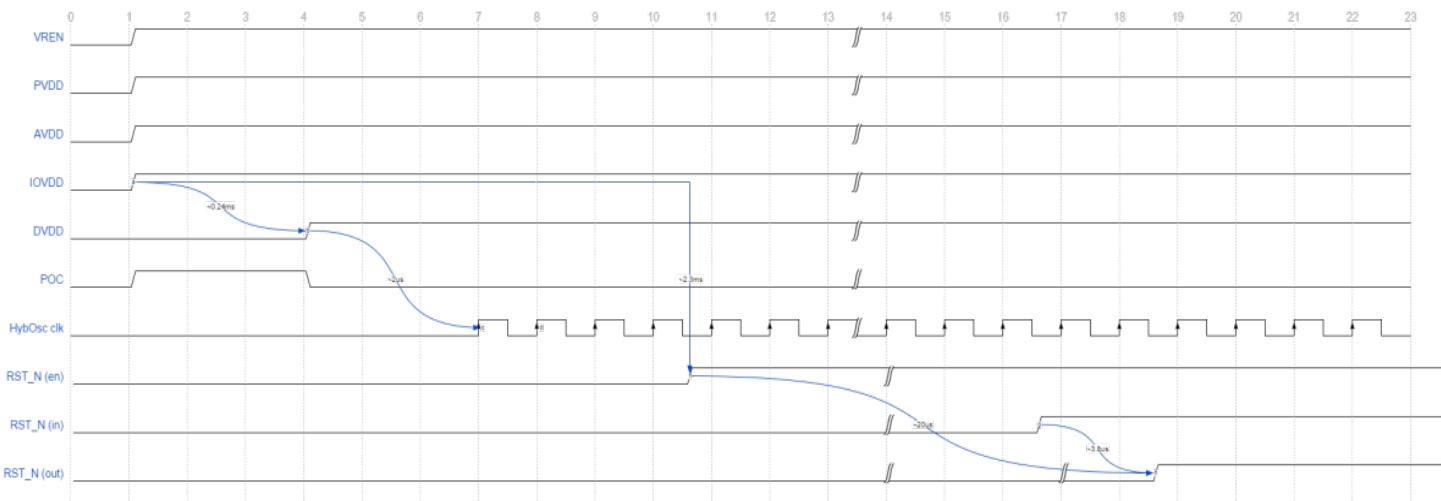

|            | SPI_S_SDOUT   | Logic output | Slave SPI Transmit data                                                                                                                                                                                                     |