# Quad Low Noise, Low Cost Variable Gain Amplifier

Data Sheet AD8335

#### **FEATURES**

Low noise preamplifier (PrA)

Voltage noise = 1.3 nV/ $\sqrt{\text{Hz}}$  typical

Current noise = 2.4 pA/ $\sqrt{\text{Hz}}$  typical

NF = 7 dB (R<sub>S</sub> = R<sub>IN</sub> = 50  $\Omega$ )

Single-ended input; V<sub>IN</sub> maximum = 625 mV p-p

Active input match

Input SNR (noise bandwidth = 20 MHz) = 92 dB

VGA

**Differential output**

$V_{\text{OUT}}$  maximum = 5 V p-p,  $R_{\text{L}}$  = 500  $\Omega$  differential

Gain range (8 dB output gain step)

-10 dB to +38 dB—low gain mode

-2 dB to +46 dB—high gain mode

Accurate linear-in-dB gain control

PrA + VGA performance

-3 dB bandwidth of 85 MHz

**Excellent overload performance**

Supply: 5 V

**Power consumption**

95 mW/channel (380 mW total)

65 mW/channel (PrA off; 260 mW total)

Power-down

#### **APPLICATIONS**

Medical imaging (ultrasound, gamma cameras)

Sonar

Test and measurement

Precise, stable wideband gain control

#### **GENERAL DESCRIPTION**

The AD8335 is a quad variable gain amplifier (VGA) with low noise preamplifier intended for cost and power sensitive applications. Each channel features a gain range of 48 dB, fully differential signal paths, active input preamplifier matching, and user-selectable maximum gains of 46 dB and 38 dB. Individual gain controls are provided for each channel.

The preamplifier (PrA) has a single-ended to differential gain of  $\times 8$  (18.06 dB) and accepts input signals  $\le 625$  mV p-p. PrA noise is 1.2 nV/ $\sqrt{\text{Hz}}$  and the combined input referred voltage noise of the PrA and VGA is 1.3 nV/ $\sqrt{\text{Hz}}$  at maximum gain.

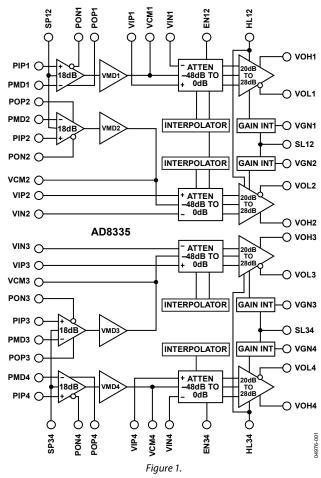

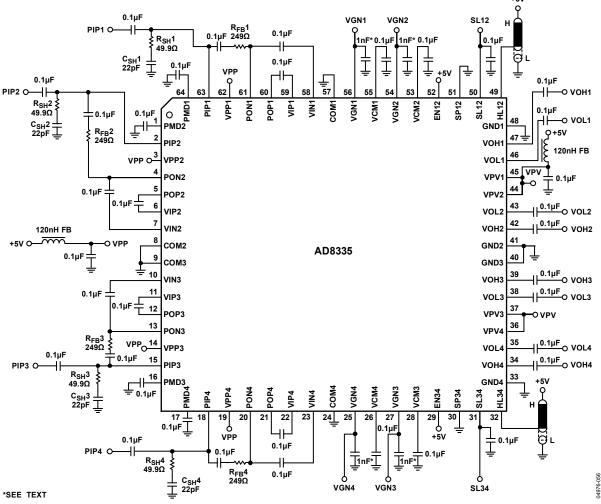

#### **FUNCTIONAL BLOCK DIAGRAM**

Assuming a 20 MHz noise bandwidth (NBW), the Nyquist frequency for a 40 MHz ADC, the input SNR is 92 dB. The HLxx pin optimizes the output SNR for 10-bit and 12-bit ADCs with 1 V p-p or 2 V p-p full-scale (FS) inputs.

Channel 1 and Channel 2 are enabled through the EN12 pin, and Channel 3 and Channel 4 are enabled through the EN34 pin. For VGA only applications, the PrAs can be powered down, significantly reducing power consumption.

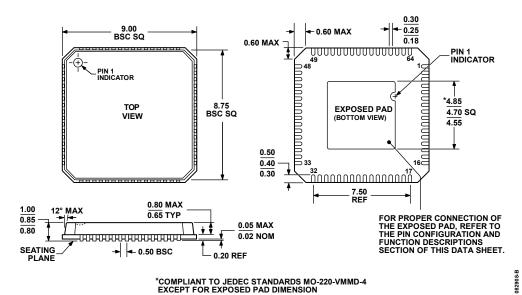

The AD8335 is available in a 64-lead lead frame chip scale package (9 mm  $\times$  9 mm) for the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Data Sheet

## **AD8335**

## **TABLE OF CONTENTS**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Absolute Maximum Ratings 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ESD Caution5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Configuration and Function Descriptions6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Test Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Enable Summary16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Preamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REVISION HISTORY<br>2/12—Rev. A to Rev. B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2/12—Rev. A to Rev. B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2/12—Rev. A to Rev. B Changes to Figure 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2/12—Rev. A to Rev. B Changes to Figure 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2/12—Rev. A to Rev. B Changes to Figure 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2/12—Rev. A to Rev. BChanges to Figure 11Added Exposed Pad Notation to Figure 2 and Table 36Changes to Figure 12 Caption11Deleted Measurement Setup Section23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2/12—Rev. A to Rev. B1Changes to Figure 11Added Exposed Pad Notation to Figure 2 and Table 36Changes to Figure 12 Caption11Deleted Measurement Setup Section23Changes to Figure 60 through Figure 6823Deleted Table 727                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A                                                                                                                                                                                                                                                                                            |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A         Changes to Features Section       1                                                                                                                                                                                                                                                |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A       2         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4                                                                                                                                                                             |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4         Changes to Theory of Operation Section       16                                                                                                                             |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A       1         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4         Changes to Theory of Operation Section       16         Changes to Figure 54       16                                                                               |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A       1         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4         Changes to Theory of Operation Section       16         Changes to Figure 54       16         Changes to Equation 4       18                                        |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A       27         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4         Changes to Theory of Operation Section       16         Changes to Figure 54       16         Changes to Equation 4       18         Changes to Figure 58       21 |

| 2/12—Rev. A to Rev. B         Changes to Figure 1       1         Added Exposed Pad Notation to Figure 2 and Table 3       6         Changes to Figure 12 Caption       11         Deleted Measurement Setup Section       23         Changes to Figure 60 through Figure 68       23         Deleted Table 7       27         8/08—Rev. 0 to Rev. A       1         Changes to Features Section       1         Changes to Table 1, Scale Factor Parameter       4         Changes to Theory of Operation Section       16         Changes to Figure 54       16         Changes to Equation 4       18                                        |

| VGA                      | 18 |

|--------------------------|----|

| Applications Information | 20 |

| Ultrasound               | 20 |

| Basic Connections        | 21 |

| Preamp Connections       | 21 |

| Input Overdrive          | 22 |

| Logic Inputs             | 22 |

| Common-Mode Pins         | 22 |

| Driving ADCs             | 22 |

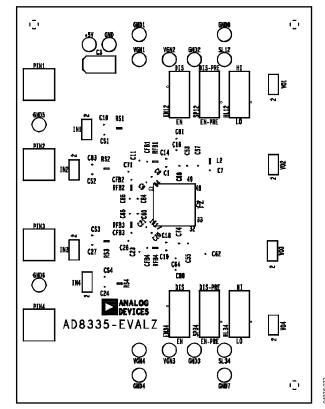

| Evaluation Board         | 23 |

| Board Layout             | 23 |

| Outline Dimensions       |    |

| Ordering Guide           | 28 |

#### 9/04—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_S=5~V,~T_A=25^{\circ}C,~R_L=500~\Omega,~f=5~MHz,~C_L=10~pF, low~gain~range~(-10~dB~to~+38~dB),~R_{FB}=249~\Omega~(PrA~R_{IN}=50~\Omega)~and~signal~voltage~specified~differential,~per~channel~performance,~dBm~(50~\Omega),~unless~otherwise~noted.$

Table 1.

| Parameter                        | Test Conditions/Comments                                             | Min | Тур               | Max | Unit       |

|----------------------------------|----------------------------------------------------------------------|-----|-------------------|-----|------------|

| Pra Characteristics              |                                                                      |     |                   |     |            |

| Gain                             | Single-ended input to differential output                            |     | 18                |     | dB         |

|                                  | Single-ended input to single-ended output                            |     | 12                |     | dB         |

| Input Voltage Range              | PrA output limited to 5 V p-p differential                           |     | 625               |     | mV p-r     |

| Input Resistance                 | $R_{FB} = 249 \Omega$                                                |     | 50                |     | Ω          |

| •                                | $R_{FB} = 374 \Omega$                                                |     | 75                |     | Ω          |

|                                  | $R_{FB} = 499 \Omega$                                                |     | 100               |     | Ω          |

|                                  | $R_{FB} = \infty$ , low frequency value into PIPx                    |     | 14.7              |     | kΩ         |

| Input Capacitance                | PIPx (Pin 2, Pin 15, Pin 18, Pin 63)                                 |     | 1.5               |     | pF         |

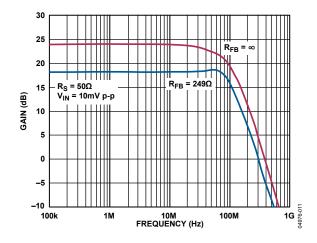

| –3 dB Small Signal Bandwidth     | With $R_{FB} = 249 \Omega$                                           |     | 110               |     | MHz        |

| Input Voltage Noise              | $R_S = 0 \Omega$ , $R_{FB} = \infty$                                 |     | 1.15              |     | nV/√H      |

| Input Current Noise              | 113 - 0 12, 11 <sub>FB</sub> - 11                                    |     | 2.4               |     | pA/√H      |

| Noise Figure                     |                                                                      |     | 2.4               |     | P/V VII    |

| Active Termination Match         | $R_S = R_{IN} = 50 \Omega$ , $R_{FB} = 249 \Omega$                   |     | 7                 |     | dB         |

| Unterminated                     | $R_S = 50 \Omega, R_{FB} = \infty$                                   |     | 4.4               |     | dВ         |

| PrA + VGA CHARACTERISTICS        | 112 – 20 77' IV-R – ~                                                |     | 4.4               | +   | ub         |

|                                  | Haterminated D. — FO.O. D.                                           |     | 70                |     | NAL 1-     |

| –3 dB Small Signal Bandwidth     | Unterminated: $R_S = 50 \Omega$ , $R_{FB} = \infty$                  |     | 70<br>85          |     | MHz<br>MHz |

| CL D                             | Matched: $R_S = R_{IN} = 50 \Omega$                                  |     |                   |     |            |

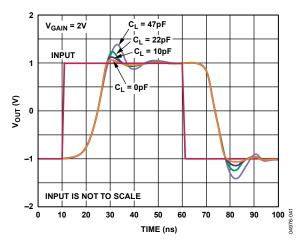

| Slew Rate                        | Low gain, VGN = 3 V, V <sub>OUT</sub> = 2 V p-p                      |     | 250               |     | V/µs       |

|                                  | High gain, VGN = 3 V, V <sub>OUT</sub> = 2 V p-p                     |     | 350               |     | V/µs       |

| Input Voltage Noise              | VGNx pins = 3 V, $R_S = 0 \Omega$ , $R_{FB} = \infty$                |     | 1.3               |     | nV/√H      |

| Noise Figure                     | VGNx pins = $3 \text{ V}$ , f = $1 \text{ MHz}$ to $10 \text{ MHz}$  |     |                   |     |            |

| Active Termination Match         | $R_S = R_{IN} = 50 \Omega$                                           |     | 7                 |     | dB         |

|                                  | $R_S = R_{IN} = 100 \Omega$                                          |     | 4.5               |     | dB         |

| Unterminated                     | $R_S = 50 \Omega$ , $R_{FB} = \infty$                                |     | 5.0               |     | dB         |

|                                  | $R_S = 500 \Omega$ , $R_{FB} = \infty$                               |     | 1.3               |     | dB         |

| Output Referred Noise            | Low gain; VGN < 2 V                                                  |     | 33                |     | nV/√H      |

|                                  | High gain; VGN < 2 V                                                 |     | 80                |     | nV/√H      |

| Peak Output Voltage              | Differential, $R_L \ge 500 \Omega$                                   |     | 5                 |     | V p-p      |

| Output Resistance                | f < 1 MHz, VOHx, VOLx pins                                           |     | 1.2               |     | Ω          |

| Common-Mode Level                | Set to midsupply for PrA and VGA                                     |     | V <sub>S</sub> /2 |     | V          |

| Output Offset Voltage            |                                                                      |     |                   |     |            |

| Differential                     | Between VOHx pins and VOLx pins, full gain range                     | -25 | +5                | +35 | mV         |

| Common-Mode                      | Between VOHx pins and VCMx pins, and between VOLx pins and VCMx pins | -20 | +0                | +20 | mV         |

| Harmonic Distortion              | $V_{OUT} = 1 \text{ V p-p, low gain, VGN} = 2 \text{ V}$             |     |                   |     |            |

| HD2                              | f=1 MHz                                                              |     | -69               |     | dBc        |

| HD3                              | f=1 MHz                                                              |     | -57               |     | dBc        |

| HD2                              | f = 10 MHz                                                           |     | -57               |     | dBc        |

| HD3                              | f = 10 MHz                                                           |     | -55               |     | dBc        |

| Harmonic Distortion              | $V_{OUT} = 1 \text{ V p-p, high gain, VGN} = 2 \text{ V}$            |     |                   |     |            |

| HD2                              | f = 1 MHz                                                            |     | -58               |     | dBc        |

| HD3                              | f = 1 MHz                                                            |     | -70               |     | dBc        |

| HD2                              | f = 10 MHz                                                           |     | -55               |     | dBc        |

| HD3                              | f = 10 MHz                                                           |     | -55               |     | dBc        |

| Output 1 dB Compression (OP1dB)  | VGN = 3 V                                                            |     | 18                |     | dBm        |

| Output 1 ub Compression (OP 10b) |                                                                      |     |                   |     |            |

|                                  | VGN = 3 V                                                            |     | 8                 |     | dB\        |

| Parameter                                                    | Test Conditions/Comments                                                         | Min   | Тур       | Max   | Unit |

|--------------------------------------------------------------|----------------------------------------------------------------------------------|-------|-----------|-------|------|

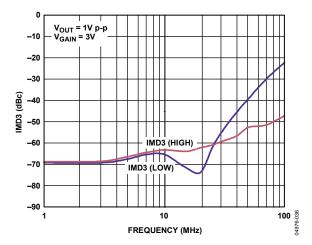

| Two-Tone IMD3 Distortion                                     | V <sub>OUT</sub> = 1 V p-p, VGN = 3 V                                            |       |           |       |      |

|                                                              | $f_1 = 1 \text{ MHz}, f_2 = 1.05 \text{ MHz}$                                    |       | -69       |       | dBc  |

|                                                              | $f_1 = 10 \text{ MHz}, f_2 = 10.05 \text{ MHz}$                                  |       | -65       |       | dBc  |

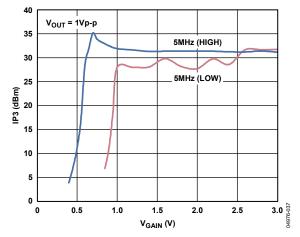

| Output IP3 (OIP3)                                            | $V_{OUT} = 1 \text{ V p-p, VGN} = 3 \text{ V}$                                   |       |           |       |      |

|                                                              | f = 1 MHz                                                                        |       | 33        |       | dBm  |

|                                                              | f = 10 MHz                                                                       |       | 31        |       | dBm  |

| Channel-to-Channel Crosstalk                                 | $V_{OUT} = 1 \text{ V p-p, f} = 1 \text{ to } 10 \text{ MHz}$                    |       | -80       |       | dBc  |

| Overload Recovery                                            | PrA or VGA                                                                       |       | 10        |       | ns   |

| Group Delay Variation                                        | Full gain range, f = 1 MHz to 10 MHz                                             |       | 3.0       |       | ns   |

| GAIN CONTROL INTERFACE                                       | VGNx pins                                                                        |       |           |       |      |

| Normal Operating Range                                       |                                                                                  | 0     |           | 3     | V    |

| Maximum Range                                                | No gain foldover                                                                 | 0     |           | $V_S$ | V    |

| Gain Range                                                   | Low gain mode; (HLxx pins = 0 V)                                                 | _     | -10 to +3 | 8     | dB   |

|                                                              | High gain mode; (HLxx pins = $V_s$ )                                             | -     | -2 to +4  | 5     | dB   |

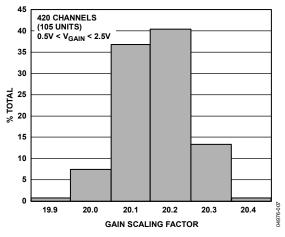

| Scale Factor                                                 | Nominal (Pin SL12 and Pin SL34 = 2.5 V)                                          | 19.1  | 20.1      | 21.1  | dB/V |

| Bias Current                                                 |                                                                                  |       | -0.3      |       | μΑ   |

| Response Bandwidth                                           |                                                                                  |       | 5         |       | MHz  |

| Response Time                                                | 48 dB gain change                                                                |       | 350       |       | ns   |

| GAIN ACCURACY                                                | VGNx pins                                                                        |       |           |       |      |

| Absolute Gain Error                                          | 0 ≤ VGN ≤ 0.4 V                                                                  | 1.25  |           | 7.5   | dB   |

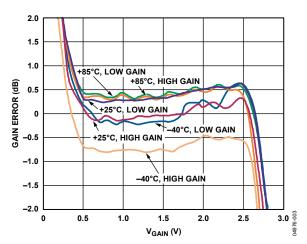

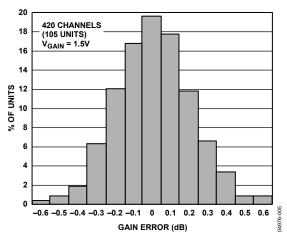

|                                                              | $0.4 \le VGN \le 2.6 \text{ V}, 1\sigma$                                         | -1.25 | ±0.2      | +1.25 | dB   |

|                                                              | 2.6 ≤ VGN ≤ 3 V                                                                  | -7.5  |           | -1.25 | dB   |

| Gain Law Conformance Over Temperature                        | $0.4 \le VGN \le 2.6 \text{ V}; -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ |       | ±0.75     |       | dB   |

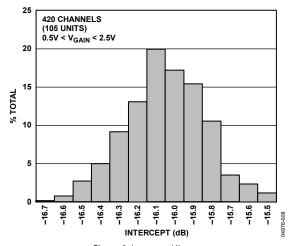

| Intercept                                                    | Low gain mode; PrA matched to 50 Ω                                               |       | -16.1     |       | dB   |

| ·                                                            | High gain mode; PrA matched to $50 \Omega$                                       |       | -8.1      |       | dB   |

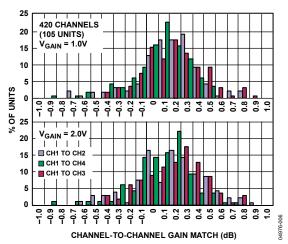

| Channel-to-Channel Matching                                  | $0.4 \le V_{GN} \le 2.6 \text{ V}$                                               |       | 0.15      |       | dB   |

| LOGIC LEVEL—HIGH/LOW, SHUTDOWN PREAMP, and ENABLE INTERFACES | HLxx, SPxx, and ENxx pins                                                        |       |           |       |      |

| Logic High                                                   |                                                                                  | 2.75  |           | 5     | V    |

| Logic Low                                                    |                                                                                  | 0     |           | 1     | V    |

| BIAS CURRENT—HIGH/LOW, ENABLE                                |                                                                                  |       |           |       |      |

| Logic High                                                   |                                                                                  |       | 80        |       | μΑ   |

| Logic Low                                                    |                                                                                  |       | -12       |       | μA   |

| NPUT RESISTANCE—HIGH/LOW, ENABLE                             |                                                                                  |       | 50        |       | kΩ   |

| BIAS CURRENT— SHUTDOWN PREAMP                                |                                                                                  |       |           |       |      |

| Logic High                                                   |                                                                                  |       | 20        |       | μΑ   |

| Logic Low                                                    |                                                                                  |       | 0         |       | μA   |

| NPUT RESISTANCE—SHUTDOWN PREAMP                              |                                                                                  |       | 500       |       | kΩ   |

| High/Low Response Time                                       |                                                                                  |       | 0.6       |       | μs   |

| Enable Response Time                                         |                                                                                  |       | 100       |       | μs   |

| POWER SUPPLY                                                 | VPPx and VPVx pins                                                               |       |           |       |      |

| Supply Voltage                                               | ·                                                                                | 4.5   | 5         | 5.5   | V    |

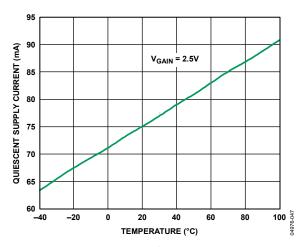

| Quiescent Current                                            | Each channel—PrA and VGA enabled                                                 |       | 19        |       | mA   |

|                                                              | Each channel—PrA disabled, VGA enabled                                           |       | 13        |       | mA   |

|                                                              | All channels enabled                                                             |       | 76        |       | mA   |

| Over Temperature                                             | -40°C < T <sub>A</sub> < +85°C                                                   | 16    | -         | 22.8  | mA   |

| Quiescent Power                                              | Each channel—PrA and VGA enabled                                                 |       | 95        |       | mW   |

| 2                                                            | Each channel—PrA disabled, VGA enabled                                           |       | 65        |       | mW   |

| Disable Current                                              | All channels disabled                                                            |       | 0.8       |       | mA   |

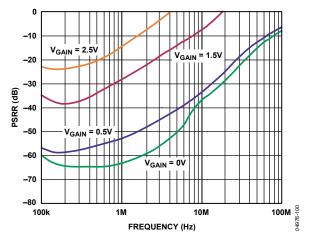

| PSRR                                                         | $V_{GN} = 0 \text{ V}$ , all bypass capacitors removed, 1 MHz                    | 1     | -60       |       | dB   |

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                           | Rating          |

|-----------------------------------------------------|-----------------|

| Voltage                                             |                 |

| Supply V <sub>5</sub>                               | 6 V             |

| Preamp Input                                        | Vs              |

| VGA Inputs                                          | Vs              |

| Enable, Shutdown Preamp, and<br>High/Low Interfaces | Vs              |

| Gain                                                | Vs              |

| Power Dissipation (4-Layer JEDEC Board (2s2p))      | 2.46 W          |

| $	heta_{JA}$                                        | 26.4°C/W        |

| θις                                                 | 6.8°C/W         |

| Operating Temperature Range                         | −40°C to +85°C  |

| Storage Temperature Range                           | −65°C to +150°C |

| Lead Temperature (Soldering 60 sec)                 | 300°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

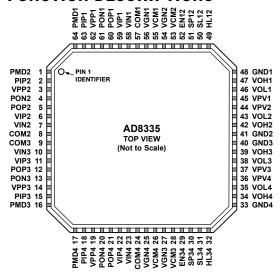

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

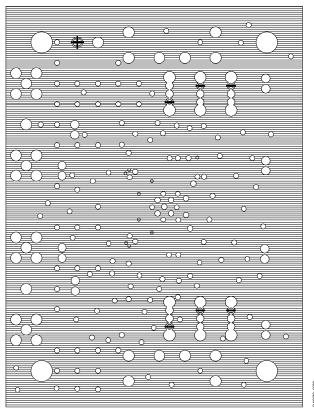

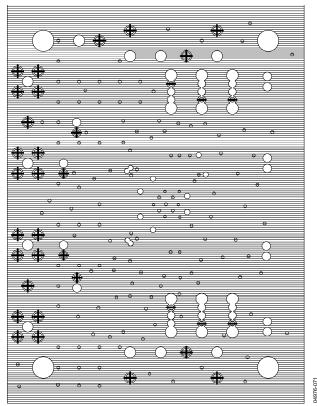

NOTES

1. THE EXPOSED PADDLE MUST BE SOLDERED TO THE PCB GROUND TO ENSURE PROPER HEAT DISSIPATION, NOISE, AND MECHANICAL STRENGTH BENEFITS.

Figure 2. Pin Configuration

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| -       | riii ruiictioii | -                                |         |          | T                                      |

|---------|-----------------|----------------------------------|---------|----------|----------------------------------------|

| Pin No. | Mnemonic        | Description                      | Pin No. | Mnemonic | Description                            |

| 1       | PMD2            | Preamp Input Common—CH2          | 35      | VOL4     | VGA Output Negative—CH4                |

| 2       | PIP2            | Preamp Input—CH2                 | 36      | VPV4     | Positive Supply VGA—CH4                |

| 3       | VPP2            | Positive Supply Preamp—CH2       | 37      | VPV3     | Positive Supply VGA—CH3                |

| 4       | PON2            | Preamp Output Negative—CH2       | 38      | VOL3     | VGA Output Negative—CH3                |

| 5       | POP2            | Preamp Output Positive—CH2       | 39      | VOH3     | VGA Output Positive—CH3                |

| 6       | VIP2            | VGA Input Positive—CH2           | 40      | GND3     | Ground VGA—CH3                         |

| 7       | VIN2            | VGA Input Negative—CH2           | 41      | GND2     | Ground VGA—CH2                         |

| 8       | COM2            | Ground Preamp—CH2                | 42      | VOH2     | VGA Output Positive—CH2                |

| 9       | COM3            | Ground Preamp—CH3                | 43      | VOL2     | VGA Output Negative—CH2                |

| 10      | VIN3            | VGA Input Negative—CH3           | 44      | VPV2     | Positive Supply VGA—CH2                |

| 11      | VIP3            | VGA Input Positive—CH3           | 45      | VPV1     | Positive Supply VGA—CH1                |

| 12      | POP3            | Preamp Output Positive—CH3       | 46      | VOL1     | VGA Output Negative—CH1                |

| 13      | PON3            | Preamp Output Negative—CH3       | 47      | VOH1     | VGA Output Positive—CH1                |

| 14      | VPP3            | Positive Supply Preamp—CH3       | 48      | GND1     | Ground VGA—CH1                         |

| 15      | PIP3            | Preamp Input—CH3                 | 49      | HL12     | High/Low Pin—CH1 and CH2               |

| 16      | PMD3            | Preamp Input Common—CH3          | 50      | SL12     | Slope Decoupling Pin—CH1 and CH2       |

| 17      | PMD4            | Preamp Input Common—CH4          | 51      | SP12     | Shutdown—Preamp 1 and Preamp 2         |

| 18      | PIP4            | Preamp Input—CH4                 | 52      | EN12     | Enable—CH1 and CH2                     |

| 19      | VPP4            | Positive Supply Preamp—CH4       | 53      | VCM2     | Common-Mode Decoupling Pin—CH2         |

| 20      | PON4            | Preamp Output Negative—CH4       | 54      | VGN2     | Gain Control—CH2                       |

| 21      | POP4            | Preamp Output Positive—CH4       | 55      | VCM1     | Common-Mode Decoupling Pin—CH1         |

| 22      | VIP4            | VGA Input Positive—CH4           | 56      | VGN1     | Gain Control—CH1                       |

| 23      | VIN4            | VGA Input Negative—CH4           | 57      | COM1     | Ground Preamp—CH1                      |

| 24      | COM4            | Ground Preamp—CH4                | 58      | VIN1     | VGA Input Negative—CH1                 |

| 25      | VGN4            | Gain Control—CH4                 | 59      | VIP1     | VGA Input Positive—CH1                 |

| 26      | VCM4            | Common-Mode Decoupling Pin—CH4   | 60      | POP1     | Preamp Output Positive—CH1             |

| 27      | VGN3            | Gain Control—CH3                 | 61      | PON1     | Preamp Output Negative—CH1             |

| 28      | VCM3            | Common-Mode Decoupling Pin—CH3   | 62      | VPP1     | Positive Supply Preamp—CH1             |

| 29      | EN34            | Enable—CH3 and CH4               | 63      | PIP1     | Preamp Input—CH1                       |

| 30      | SP34            | Shutdown—Preamp 3 and Preamp 4   | 64      | PMD1     | Preamp Input Common—CH1                |

| 31      | SL34            | Slope Decoupling Pin—CH3 and CH4 |         | EPAD     | The exposed paddle must be soldered to |

| 32      | HL34            | High/Low Pin—CH3 and CH4         |         |          | the PCB ground to ensure proper heat   |

| 33      | GND4            | Ground VGA—CH4                   |         |          | dissipation, noise, and mechanical     |

| 34      | VOH4            | VGA Output Positive—CH4          |         |          | strength benefits.                     |

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_S = 5$  V,  $T_A = 25$ °C,  $R_L = 500$   $\Omega$ , f = 5 MHz,  $C_L = 10$  pF, low gain range (-10 dB to +38 dB),  $R_{FB} = 249$   $\Omega$  (PrA  $R_{IN} = 50$   $\Omega$ ) and signal voltage specified differential, per channel performance, unless otherwise noted.

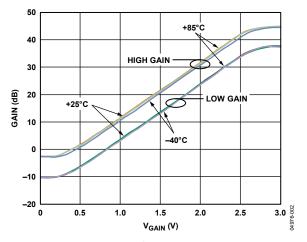

Figure 3. Gain vs. V<sub>GAIN</sub> at Three Temperatures (See Figure 49)

Figure 4. Gain Error vs. V<sub>GAIN</sub> at Three Temperatures (See Figure 49)

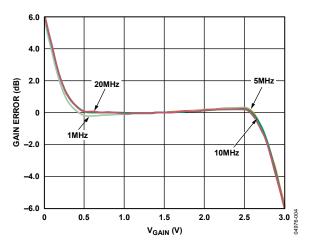

Figure 5. Gain Error vs. V<sub>GAIN</sub> at Various Frequencies (See Figure 49)

Figure 6. Gain Error Histogram

Figure 7. Gain Match Histogram for  $V_{GAIN} = 1 V$  and 2 V

Figure 8. Gain Scaling Factor Histogram for 0.5  $V < V_{GAIN} < 2.5 V$

Figure 9. Intercept Histogram

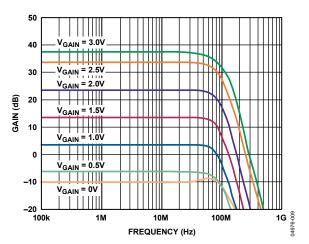

Figure 10. Frequency Response for Various Values of V<sub>GAIN</sub> (See Figure 49)

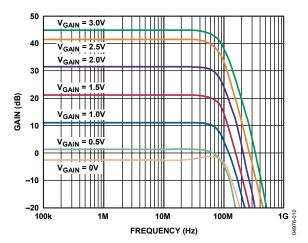

Figure 11. Frequency Response vs. Frequency for Various Values of  $V_{\text{GAIN}}$ , HLxx = High (See Figure 49)

Figure 12. Preamp Frequency Response for a Terminated and Unterminated 50  $\Omega$  Source (See Figure 49)

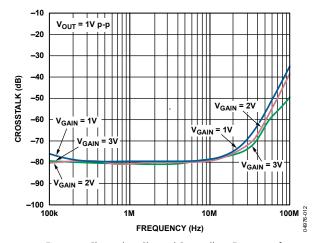

Figure 13. Channel-to-Channel Crosstalk vs. Frequency for Various Values of V<sub>GAIN</sub>

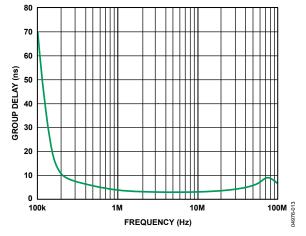

Figure 14. Group Delay vs. Frequency

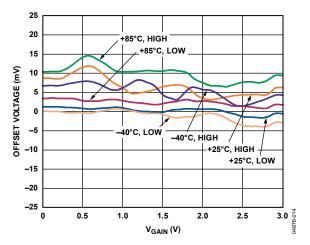

Figure 15. Differential Output Offset Voltage vs. V<sub>GAIN</sub> at Three Temperatures

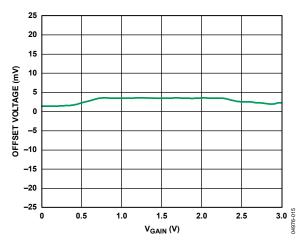

Figure 16. Absolute Offset vs. V<sub>GAIN</sub> at VOHx and VOLx Pins Relative to VCMx Pins

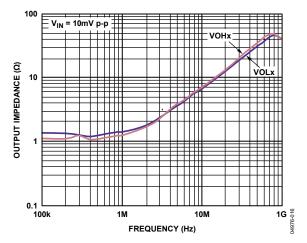

Figure 17. Output Resistance at VOHx and VOLx Pins vs. Frequency

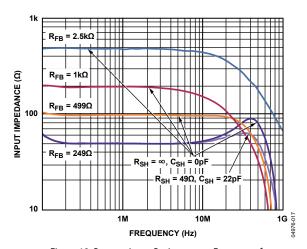

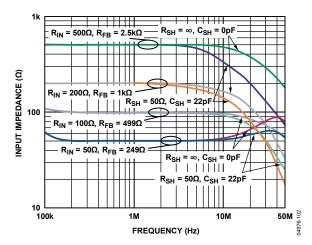

Figure 18. Preamp Input Resistance vs. Frequency for Various Values of  $R_{FB}$

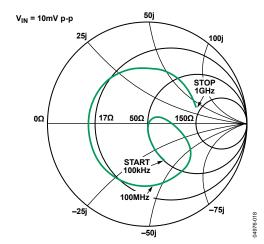

Figure 19. Smith Chart S11 vs. Frequency, 100 kHz to 1 GHz

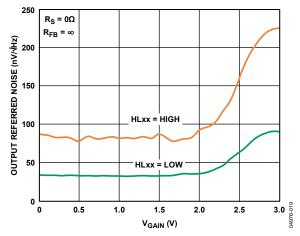

Figure 20. Output Referred Noise vs. V<sub>GAIN</sub> (See Figure 50)

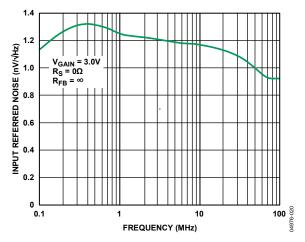

Figure 21. Short-Circuit Input Referred Noise vs. Frequency at Maximum Gain (See Figure 50)

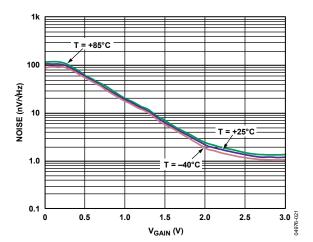

Figure 22. Input Referred Noise vs.  $V_{GAIN}$  at Three Temperatures (See Figure 50)

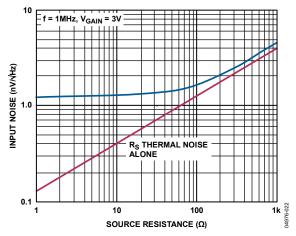

Figure 23. Input Referred Noise vs. Rs

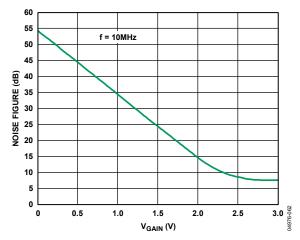

Figure 24. Noise Figure vs.  $V_{GAIN}$  for  $R_S = R_{IN} = 50 \Omega$

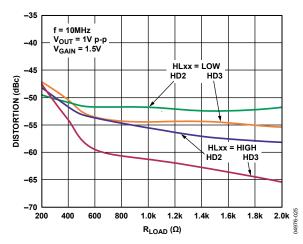

Figure 25. Harmonic Distortion vs. R<sub>LOAD</sub> (See Figure 53)

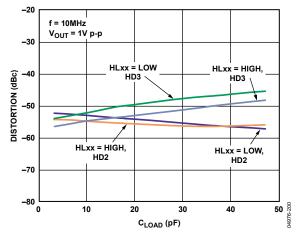

Figure 26. Harmonic Distortion vs.  $C_{LOAD}$  (See Figure 53)

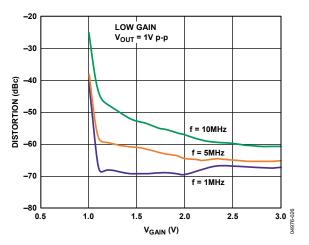

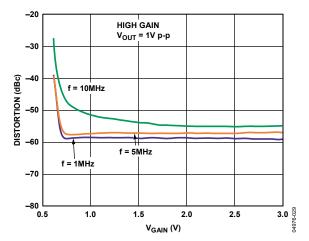

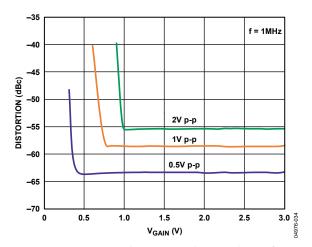

Figure 27. HD2 vs. V<sub>GAIN</sub> at Three Frequencies, Low Gain (See Figure 53)

Figure 28. HD3 vs. V<sub>GAIN</sub> at Three Frequencies, Low Gain (See Figure 53)

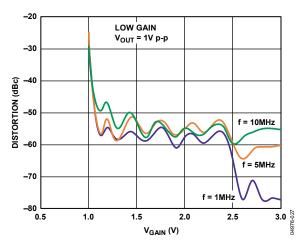

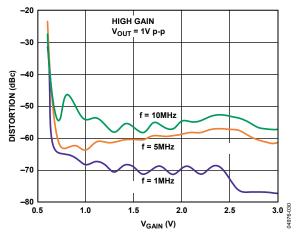

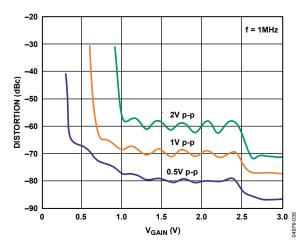

Figure 29. HD2 vs. V<sub>GAIN</sub> at Three Frequencies, High Gain (See Figure 53)

Figure 30. HD3 vs. V<sub>GAIN</sub> at Three Frequencies, High Gain (See Figure 53)

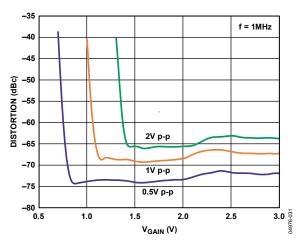

Figure 31. HD2 vs. V<sub>GAIN</sub> at Three Output Voltages, Low Gain (See Figure 53)

Figure 32. HD3 vs. V<sub>GAIN</sub>, at Three Output Voltages, Low Gain (See Figure 53)

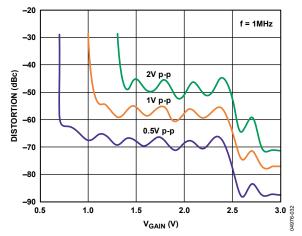

Figure 33. HD2 vs.  $V_{GAIN}$  at Three Output Voltages, High Gain, f = 1 MHz (See Figure 53)

Figure 34. HD3 vs. V<sub>GAIN</sub> at Three Output Voltages, High Gain (See Figure 53)

Figure 35. IMD3 vs. Frequency

Figure 36. Output Referred IP3 (OIP3) vs. V<sub>GAIN</sub>

Figure 37. Input P1dB (IP1dB) vs. V<sub>GAIN</sub>

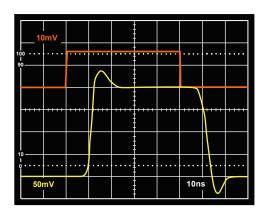

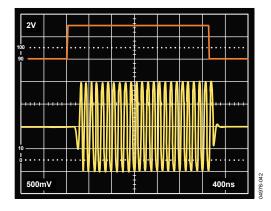

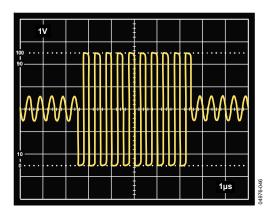

Figure 38. Small Signal Pulse Response, Low Gain (See Figure 51)

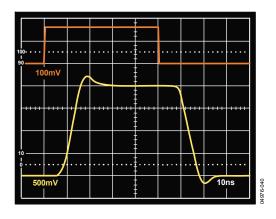

Figure 39. Large Signal Pulse Response, Low Gain (See Figure 51)

Figure 40. Large Signal Pulse Response for Various Capacitive Loads,  $C_L = 0$  pF, 10 pF, 20 pF, 47 pF Each Output (See Figure 51)

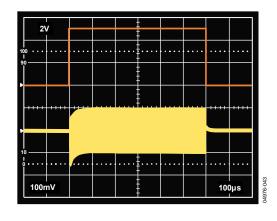

Figure 41. Gain Response,  $V_{GAIN}$  Stepped from 0 V to 3 V,  $V_{OUT} = 2 V p-p$  (See Figure 51)

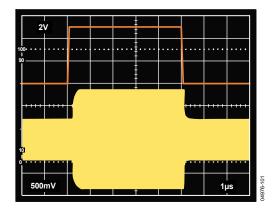

Figure 42. Small Signal Enable Response (See Figure 51)

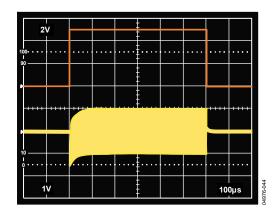

Figure 43. Large Signal Enable Response (See Figure 51)

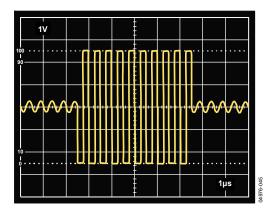

Figure 44. Preamp Overdrive Recovery, 50 mV p-p to 1.5 V p-p at Preamp Input (Measured at Preamp Output)

Figure 45. VGA Overdrive Recovery, 40 mV to 500 mV Input,  $V_{GAIN} = 2.5 \text{ V}$

Figure 46. PSRR vs. Frequency (All Bypass Capacitors Removed)

Figure 47. Quiescent Supply Current vs. Temperature

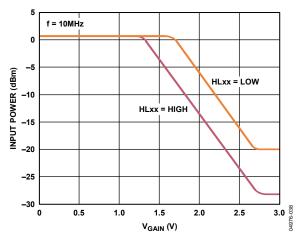

Figure 48 High/Low Response Time

## **TEST CIRCUITS**

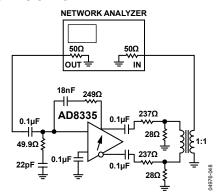

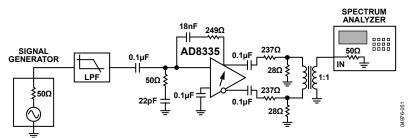

Figure 49. Test Circuit for Gain and Bandwidth Measurements

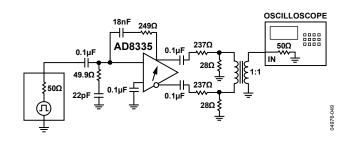

Figure 51. Test Circuit for Transient Measurements

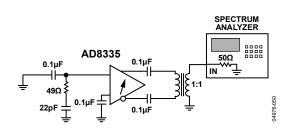

Figure 50. Test Circuit for Noise Measurements

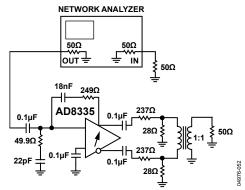

Figure 52. Test Circuit for S11 Measurements

Figure 53. Test Circuit Used for Distortion Measurements

## THEORY OF OPERATION

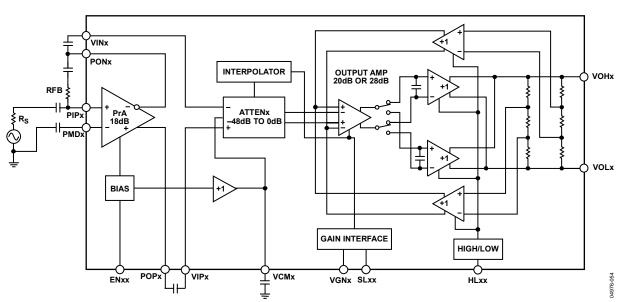

Figure 54 is a simplified block diagram of a single channel. Each channel consists of a low noise preamplifier (PrA) followed by a VGA with a user-selectable gain of 20 dB or 28 dB. Channels are enabled in pairs, Channel 1 and Channel 2, and Channel 3 and Channel 4. The preamps are enabled by grounding the SPxx pins and powered down by connecting them to the positive supply. The ENxx pins are connected to the positive supply to enable the VGAs and the overall channel. HLxx configures VGA for a fixed gain of 20 dB or 28 dB, with 0 V or 5 V applied to the HLxx pins, respectively. Channel 1 and Channel 2 share Pin HL12, and Channel 3 and Channel 4 share Pin HL34. The HLxx pins are typically hardwired to adjust the VGA gain according to an ADC resolution of 12 bits for low gain and 10 bits for high gain.

The signal path is fully differential throughout to maximize signal swing and reduce even-order distortion; however, the preamplifiers are designed to be driven from a single-ended signal source. Gain values are referenced from the single-ended PrA input to the differential output of either the PrA or the VGA. Again referring to Figure 54, the system gain is distributed as listed in Table 4.

In the remainder of this document, the gain values are rounded to -10~dB to +38~dB for low gain mode and to -2~dB to +46~dB for high gain mode. If desired, Equation 1 can be used to calculate the gain at a value of  $V_{\rm GAIN}$ .

$$Gain[dB] = 20.1 \frac{dB}{V} VGN + ICPT$$

(1)

where ICPT = -16.1 dB for low gain mode -8.1 dB for high gain mode.

Power consumption is 95 mW/channel from a 5 V supply, or 380 mW for all four channels. Power is distributed 35% for the PrA, and 65% for the remainder of the circuit. The preamps can be shut down via the SP12 and SP34 pins if a user wants to use the VGAs only. However, to avoid feedthrough around the preamp, feedback resistors should not be installed.

**Table 4. Channel Gain Distribution**

| Section    | Low Nominal Gain<br>(dB) | High Nominal Gain<br>(dB) |

|------------|--------------------------|---------------------------|

| PrA        | 18.06                    | 18.06                     |

| Attenuator | 0 to -48.16              | 0 to -48.16               |

| Output Amp | 20                       | 27.96                     |

| Aggregate  | -10.1 to +38.6           | -2.14 to +46.02           |

#### **ENABLE SUMMARY**

Table 5summarizes the enable/shutdown logic and resulting supply current.

Table 5. Control Pin Logic and Power Consumption

| EN12 | SP12 | EN34 | SP34 | PrA1/PrA2 | VGA1/VGA2 | PrA3/PrA4 | VGA3/VGA4 | Is     |

|------|------|------|------|-----------|-----------|-----------|-----------|--------|

| High | Low  | High | Low  | On        | On        | On        | On        | 76 mA  |

| High | High | High | High | Off       | On        | Off       | On        | 52 mA  |

| Low  | Low  | Low  | Low  | Off       | Off       | Off       | Off       | 0.8 mA |

| Low  | High | Low  | High | Off       | Off       | Off       | Off       | 0.8 mA |

Figure 54. Simplified Block Diagram of Single Channel

#### **PREAMP**

Although the preamp signal path is fully differential, the design is optimized for single-ended input drive and signal source resistance matching. Thus, the negative input to the differential preamplifier PMDx pins must be ac-grounded to provide a balanced differential signal at the PrA outputs. Detailed information regarding the preamplifier architecture is found in the LNA section of the AD8331/AD8332 data sheet.

The preamplifier consists of a fixed gain amplifier with differential outputs. With the negative output available and a fixed gain of 8 (18.06 dB), an active input termination is synthesized by connecting a feedback resistor between the negative output and the positive input, Pin PIPx. This technique is well known and results in the input resistance shown in Equation 2.

$$R_{IN} = \frac{R_{FB}}{(1 + A/2)} \tag{2}$$

where A/2 is the single-ended gain, or the gain from the PIPx inputs to the PONx outputs. Since the amplifier has a gain of ×8 from its input to its differential output, it is important to note that the gain A/2 is the gain from Pin PIPx to Pin PONx, which is 6 dB lower, or 12.04 dB (×4). The input resistance is reduced by an internal bias resistor of 14.7 k $\Omega$  in parallel with the source resistance connected to Pin PIPx, with Pin PMDx ac-grounded. Equation 3 can be used to calculate the needed R<sub>FB</sub> for a desired R<sub>IN</sub>, and is used for higher values of R<sub>IN</sub>.

$$R_{IN} = \frac{R_{FB}}{(1+4)} || 14.7 \,\mathrm{k}\Omega$$

(3)

For example, to set  $R_{\rm IN} = 200~\Omega$ , the value of  $R_{\rm FB}$  is  $1.013~{\rm k}\Omega$ . If the simplified Equation 2 is used to calculate  $R_{\rm IN}$ , the value is 197  $\Omega$ , resulting in a less than 0.1 dB gain error. Factors such as a widely varying source resistance might influence the absolute gain accuracy more significantly. At higher frequencies, the input capacitance of the PrA needs to be considered. The user must determine the level of matching accuracy and adjust  $R_{\rm FB}$  accordingly.

The bandwidths (BW) of the preamplifier and VGA are approximately 110 MHz each, resulting in a cascaded BW of approximately 80 MHz. Ultimately the BW of the PrA limits the accuracy of the synthesized  $R_{\rm IN}.$  For  $R_{\rm IN}=R_{\rm S}$  up to approximately 200  $\Omega,$  the best match is between 100 kHz and 10 MHz, where the lower frequency limit is determined by the size of the ac coupling capacitors, and the upper limit is determined by the preamplifier BW. Furthermore, the input capacitance and  $R_{\rm S}$  limits the BW at higher frequencies.

Figure 55.  $R_{IN}$  vs. Frequency for Various Values of  $R_{FB}$ ; Effects of  $R_{SH}$  and  $C_{SH}$  are also shown.

Figure 55 shows  $R_{IN}$  vs. frequency for various values of  $R_{FB}$ . Note that at the lowest value, 50  $\Omega$ ,  $R_{IN}$  peaks at frequencies greater than 10 MHz. This is due to the BW roll-off of the PrA as mentioned earlier. The  $R_{SH}$  and  $C_{SH}$  network shown in Figure 58 reduces this peaking.

However, as can be seen for larger  $R_{\rm IN}$  values, parasitic capacitance starts rolling off the signal BW before the PrA can produce peaking and the  $R_{\rm SH}/C_{\rm SH}$  network further degrades the match. Therefore,  $R_{\rm SH}$  and  $C_{\rm SH}$  should not be used for values of  $R_{\rm IN}$  greater than 50  $\Omega.$

#### Noise

The total input referred noise (IRN) is approximately  $1.3 \text{ nV/}\sqrt{\text{Hz}}$ . Allowing for a gain of  $\times 8$  in the preamp, the VGA noise is  $0.46 \text{ nV/}\sqrt{\text{Hz}}$  referred to the PrA input. The preamp noise is  $1.2 \text{ nV/}\sqrt{\text{Hz}}$ . It is important to note that these noise values include all amplifier noise sources, including the VGA and the preamplifier gain resistors. Frequently, manufacturer noise specifications exclude gain setting resistors, and the voltage noise spectral density of an op amp might be presented as  $1 \text{ nV/}\sqrt{\text{Hz}}$ . Including the gain resistors results in a much higher noise specification.

Figure 56 shows the simulated noise figure (NF) vs. source resistance, and various values of preamplifier  $R_{\rm IN}$  from 50  $\Omega$  to 14.7 k $\Omega$ , the value seen looking into the PIPx pins when  $R_{\rm FB}=\infty$ . As shown in the figure, the minimum NF for  $R_{\rm IN}=50~\Omega$  is slightly less than 7 dB. Note that, for this preamplifier, the NF is optimized for the  $R_{\rm IN}$  from 50  $\Omega$  to 200  $\Omega$ ; for  $R_{\rm FB}=\infty$ , the minimum NF is at approximately 480  $\Omega$ . This optimum noise resistance can also be calculated by dividing the input referred voltage noise by the current noise.

Figure 56. Simulated Noise Figure vs. R<sub>S</sub> for Various Fixed Values of R<sub>IN</sub>, Actively Matched

#### **VGA**

As seen in Figure 54, the basic architecture, an X-AMP\*, consists of a ladder attenuator, followed by a fixed gain amplifier with selectable input stages. Earlier examples of this architecture are to be found in the AD60x series, AD8331/AD8332, andAD8367 VGAs. Through a proprietary, temperature-compensated interpolator design, the bias currents to the input g<sub>m</sub> stages are continuously steered from right to left (decreasing attenuation) resulting in increasing gain.

The HLxx gain pins (HL12 and HL34) select one of two output amplifier networks consisting of the feedback resistors, amplifier stages, and buffers.

#### **Optimizing the System Dynamic Range**

The VGA output gain switch of 8 dB (×2.5) optimizes the VGA noise floor for a 10-bit or 12-bit ADC, assuming a full-scale ADC input voltage of 1 V p-p.

At low gain, the ADC SNR should limit the system noise performance, whereas at high gains, the noise is defined by the source and preamplifier. The maximum voltage swing is bounded by the full-scale, peak-to-peak ADC input voltage (typically 1 V p-p to 2 V p-p). The noise performance is optimized by adjusting the noise floor of the VGA according to the ADC resolution. The SNR of a 12-bit converter is theoretically 12 dB better than a 10-bit; however, approximately 8 dB is typical in practice, accounting for the 8 dB gain option of the AD8335. The IRN and the power consumption of the VGA are unaffected by either gain setting; therefore, only the output referred noise (ORN) changes (by 8 dB) without affecting any other parameters.

#### Attenuator

The attenuator is an 8-stage differential R-2R ladder with a total attenuation of 48.16 dB or 6.02 dB per tap. The effective input resistance per side is 320  $\Omega$  nominal for a total differential resistance of 640  $\Omega$ . The common-mode voltage of the attenuator and the VGA is controlled by an amplifier that uses the same midsupply voltage derived in the preamplifier, permitting dc coupling of the PrA to the VGA without introducing large offsets due to common-mode differences. However, when dc coupling between the PrA and VGA, any offset from the PrA is amplified as the gain is increased, producing an exponentially increasing VGA output offset. When the PrA and the VGA are ac-coupled, the output offset is unchanged with changes in gain (see Figure 15). As a result, ac coupling is recommended for most applications. As can be seen from Figure 54, The VCMx pins connect to the respective midpoints on each channel and are used to ac decouple the common-mode node at high frequencies. It is very important that at least a 0.1 µF capacitor be used, with better decoupling at higher frequencies when another smaller capacitor (10 nF) is connected in parallel. The internal +1 buffer provides correct common-mode bias levels and any dynamic currents have to be absorbed by the external decoupling capacitors.

#### **Gain Control**

The gain control interface has two inputs,  $V_{\rm GAIN}$  (VGNx pins) and VSLP (SLxx pins). The slope input is intended only as a decoupling pin, and the only guaranteed gain slope is the 20 dB/V default. However, if a voltage is applied to the VSLP inputs, the gain slope can be increased by reducing the slope voltage. For example, if a voltage of 1.67 V is applied to the SLxx pins, the gain slope changes to 30 dB/V. Use Equation 4 to calculate the gain slope.

$$VSLP = \frac{2.5 \text{ V} \times 20.1 \text{ dB/V}}{Slope} \tag{4}$$

$V_{\rm GAIN}$  varies the gain of the VGA through the interpolator by selecting the appropriate input stages connected to the input attenuator. The nominal  $V_{\rm GAIN}$  range for 20 dB/V is 0 V to 3 V, with the best gain linearity from approximately 0.5 V to 2.5 V, where the error is typically less than  $\pm 0.2$  dB. For  $V_{\rm GAIN}$  voltages above 2.5 V and less than 0.5 V, the error increases (see Figure 4). The value of the  $V_{\rm GAIN}$  voltage can be increased to that of the supply voltage, without gain foldover.

Each channel has separate gain control pins that can be connected to a common voltage source such as found in most ultrasound applications. For control of individual channels, connect the appropriate gain control signal to each channel.

#### **Output Stage**

Duplicate output stages of the VGA provide an 8 dB ( $\times 2.5$ ) gain switch. The gain switch is intended to optimize the output noise floor for either a 10-bit or a 12-bit ADC. The VGA gain is 20 dB ( $\times 10$ ) in low gain mode and 28 dB ( $\times 25$ ) in high gain mode. The logic setting of the HLxx pins selects between output amplifiers including the gain resistors and feedback buffers.

100 MHz bandwidth is maintained between the amplifiers by changing the compensation capacitance as the gain switches gain settings. Power consumption is the same for either level of gain.

In certain applications, power consumption can be reduced by lowering the supply voltage as much as possible; however, the output dynamic range is affected by the more limited swing. The fully differential signal path of the AD8335 restores 6 dB of dynamic range, and the common-mode level is maintained automatically at half the supply voltage for maximum signal swing. The differential signal has the added benefit of suppressing the even order harmonics.

The output amplifier is designed to drive a nominal differential load of 500  $\Omega$  or greater; the signal swing can be as large as 5 V p-p differential before clipping occurs. However, that distortion increases before reaching the clipping level. Distortion is shown in Figure 25 through Figure 34 for typical values of 1 V p-p or 2 V p-p (full-scale inputs for many ADCs). The output is accoupled to a differential antialias filter driving a differential ADC. Most modern ADCs have differential inputs and achieve optimum performance when driven differentially. For more information, see the Applications Information section.

#### **VGA** Noise

As with all X-AMPs, the output noise of the VGA is constant with gain. This causes the input referred noise to increase as the gain is decreased. This characteristic is desirable in receiver applications where wide dynamic range input signals are compressed with a fixed ceiling and noise floor into an ADC. The VGA output noise is approximately 33 nV/ $\sqrt{\rm Hz}$  in low gain mode and 2.5 times higher than this, 83 nV/ $\sqrt{\rm Hz}$ , in high gain mode. As the gain increases, the noise of the preamplifier prevails and, at the maximum VGA gain, the output noise is approximately 90 nV/ $\sqrt{\rm Hz}$  and 225 nV/ $\sqrt{\rm Hz}$  for low and high gain modes, respectively.

The output SNR is determined by the noise floor and the largest signal level, typically limited by the FS of the ADC. Modulation noise, essentially the noise introduced by the gain control input, can be troublesome. Normally one tends to look at the main amplifier signal path for noise, but a VGA is really a multiplier with the following function:

$$V_{OUT} = \frac{V_{GAIN} \times V_{IN}}{V_{DEE}} \tag{5}$$

where  $V_{REF}$  (bias) and  $V_{GAIN}$  (gain control interface) are both noise contributors under certain conditions. It is therefore important that the gain control signals be kept clean, especially at higher gain control slopes.

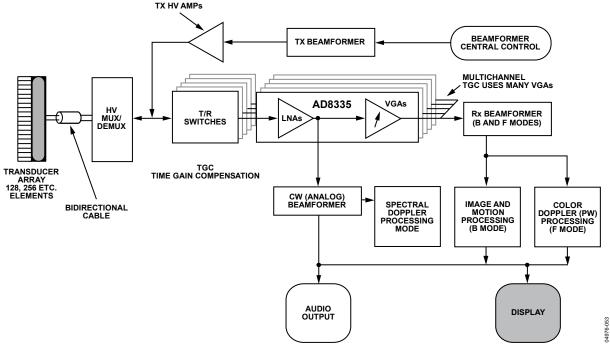

## APPLICATIONS INFORMATION ULTRASOUND

The primary application for the AD8335 is medical ultrasound. Figure 57 shows a simplified block diagram of an ultrasound system. The most critical function of an ultrasound system is the time gain control (TGC) compensation for physiological signal attenuation. Because the attenuation of ultrasound signals is exponential with respect to distance (time), a linear-in-dB VGA is the optimal solution.

Key requirements in an ultrasound signal chain are very low noise, active input termination, fast overload recovery, low power, and differential drive to an ADC. Because ultrasound machines use beamforming techniques requiring large binary weighted numbers (for example, 32 to 512) of channels, the lowest power at the lowest possible noise is of key importance.

Most modern machines use digital beamforming. In this technique, the signal is converted to digital format immediately following the TGC amplifier; beamforming is done digitally.

Typical ADC resolution in general purpose machines is 10 bits with sampling rates greater than 40 MSPS, and high-end systems use 12 bits.

Power consumption and low cost are of primary importance in low-end and portable ultrasound machines, and the AD8335 is designed for these criteria.

For additional information regarding ultrasound systems, refer to "How Ultrasound System Considerations Influence Front-End Component Choice", Analog Dialogue, Vol. 36, No. 3, May–July 2003. (www.analog.com/library/analogDialogue/archives/36-03/ultrasound/index.html)

Figure 57. Simplified Ultrasound System Block Diagram

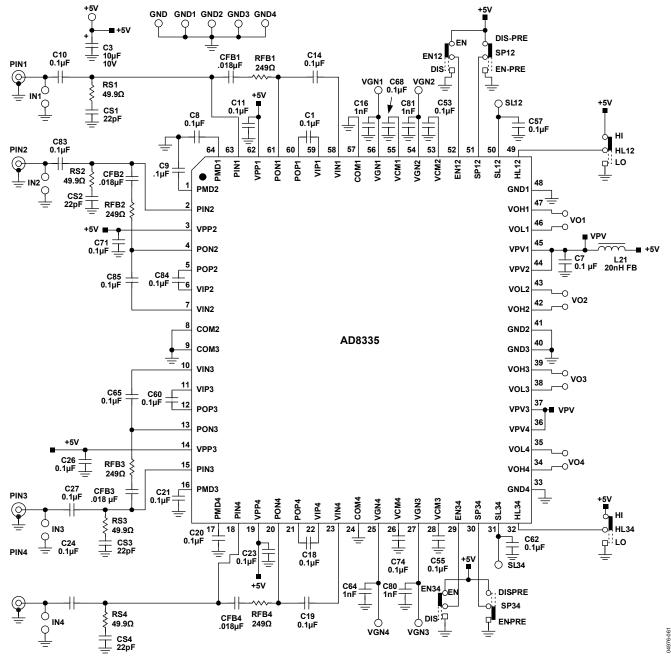

#### **BASIC CONNECTIONS**

Figure 58 shows the basic connections for the AD8335. Input signals enter from the left and output signals exit from the right, providing straight line signal paths. Of course, a device with four differential VGAs such as this requires a multilayer printed circuit board. Power supply isolation is shown for the preamps, and for the VGA sections. If components are mounted to both sides of the board, those in the signal path should be located on the top, with power-supply decoupling components on the wiring side.

#### **PREAMP CONNECTIONS**

To configure the AD8335 for input matching, a feedback resistor (R<sub>FB</sub>) is ac-coupled between Pin PONx and Pin PIPx. AC coupling accommodates dissimilar common-mode voltages at the input and output ports. For values of R<sub>SOURCE</sub> between 50  $\Omega$  and 200  $\Omega$ , R<sub>FB</sub> is simply 5 × R<sub>SOURCE</sub>. Table 6 lists a few larger values of source

resistor (or  $R_{IN}$ ), along with the exact value and nearest standard 1% feedback resistor. For values other those than listed in Table 6,  $R_{FB}$  can be calculated using Equation 6. For values larger than 1 k $\Omega$ , it may be advantageous to simply remove  $R_{FB}$ .

**Table 6. Feedback Resistor Values for Various Input Resistances**

| R <sub>IN</sub> (Ω) | Exact R <sub>FB</sub> Value (Ω) | Nearest Standard 1% Value (Ω) |

|---------------------|---------------------------------|-------------------------------|

| 200                 | 1014                            | 1.02 k                        |

| 500                 | 2588                            | 2.61 k                        |

| 1000                | 5365                            | 5.36 k                        |

$$R_{FB}(\Omega) = \frac{5 \times R_{IN}}{1 - \frac{R_{IN}}{14.7 \,\mathrm{k}}} \tag{6}$$

Figure 58. Basic Connections for  $R_{IN} = 50 \Omega$

The preamp PMD pins must be capacitively coupled to ground. Although the preamplifier is a differential design, the PMD pins are the internal input bias nodes and are made available for bypassing only. Do not use these pins as signal inputs.

The PIPx inputs must be capacitively coupled from the signal source because they have a nominal dc level of more than half the supply voltage. AC coupling capacitors throughout the circuit should be as large as possible for the application. Although 0.1  $\mu F$  capacitors are shown in Figure 58 (and used in most positions in the evaluation board), values of these capacitors should be determined by the application. Capacitors used for coupling PMDx and PIPx pins should be the same value.

When synthesizing low values of  $R_{IN}$ , the bandwidth of the preamplifier produces some peaking at the high end of the frequency response. The optional series  $R_{SHX}/C_{SHX}$  network shown in Figure 58 flattens the response (see Figure 55). With a 50  $\Omega$  source, the resistor and capacitor values should be 49.9  $\Omega$  and 22 pF. For  $R_S$  values greater than 100  $\Omega$ , the network is not needed. The circuit is stable in either scenario.

The starred capacitors in Figure 58 (\*) on the VGNx pins can be removed when faster gain control signals are required.

#### INPUT OVERDRIVE

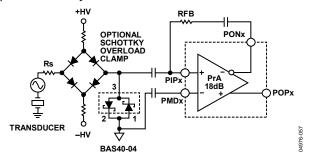

Excellent overload behavior is of primary importance in ultrasound. Both the preamplifier and VGA have built-in overdrive protection and quickly recover after an overload event.

#### **Input Overload Protection**

As with any amplifier, voltage clamping prior to the inputs is highly recommended if the application is subject to high transient voltages.

A block diagram of a simplified ultrasound transducer interface is shown in Figure 59. A common transducer element serves the dual functions of transmit and receive of ultrasound energy. During the transmit phase, high voltage pulses are applied to the ceramic elements. A typical T/R (transmit/receive) switch may consist of four high voltage diodes in a bridge configuration. Although they ideally block transmit pulses from the sensitive receiver input, diode characteristics are not ideal, and resulting leakage transients impinging on the PIPx inputs can be problematic.

Because ultrasound is a pulse system, and time-of-flight is used to determine depth, quick recovery from input overloads is essential. Overload can occur in the preamp and the VGA. Immediately following a transmit pulse, the typical VGA gains are low, and the PrA is subject to overload from T/R switch leakage. With increasing gain, the VGA can become overloaded from strong echoes that occur with near field echoes and acoustically dense materials, such as bone.

Figure 59 illustrates an external overload protection scheme. A pair of back-to-back Schottky diodes is installed prior to installing the ac-coupling capacitors. Although the BAS40 is shown, many types are available and merit investigation by the user. With such

diodes, clamping levels of  $\pm 0.5$  V or less greatly enhance the system overload performance.

Figure 59. Input Overload Protection

#### **LOGIC INPUTS**

The EN12 and EN34 enable pins, the SP12 and SP34 preamp shutdown pins, and the HL12 and HL34 high/low pins are all logic inputs of the AD8335. The enable inputs turn on and off each of the corresponding pairs of channels; the preamp shutdown pins do the same for the preamplifiers only; inputs HL12 and HL34 set the high/low gain for Channel 1 and Channel 2, and Channel 3 and Channel 4, respectively.

Shutting down the preamplifiers allows use of the VGAs alone, while reducing power consumption. The VGAs cannot be shut down independently. The SPxx (shutdown preamp) pins are logic high; thus, the pins are grounded to enable the preamplifiers.

The pins can be enabled by connecting to the supply or to ground for fixed enable or disable, or to the output of a logic device. Be sure to check the data sheet of the device for voltage and current requirements.

#### **COMMON-MODE PINS**

The common-mode VCMx pins are provided for bypassing the internal common-mode reference for each channel to ground. They require a capacitor at each of the four pins and can neither be connected together nor driven by an external source.

#### **DRIVING ADCs**

The AD8335 VGA is designed to drive 10-bit and 12-bit ADCs with minimal extra components. Because the AD8335 is a single supply 5 V part and many of the newest ADCs operate from a 3 V supply, dissimilar common-mode voltages exist between the VGA output and the ADC input. This level shift is most easily accommodated by ac coupling, especially if the signal is filtered, as is the case in most ultrasound and communications applications.

When an antialiasing filter (AAF) is called for, it is advantageous to implement a differential configuration. A fully differential AAF requires approximately 1.5 times the number of components than a single-ended filter, because the components that in the single-ended case are tied to ground, now connect across the differential signal path. Although the series components double, the component count for the differential filter is more economical when compared to simply building a pair of single-ended filters requiring twice as many components.

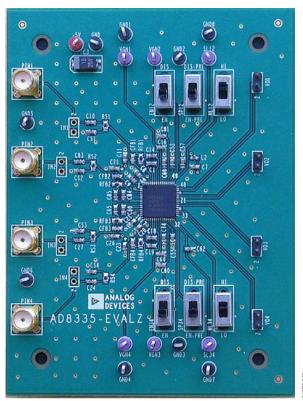

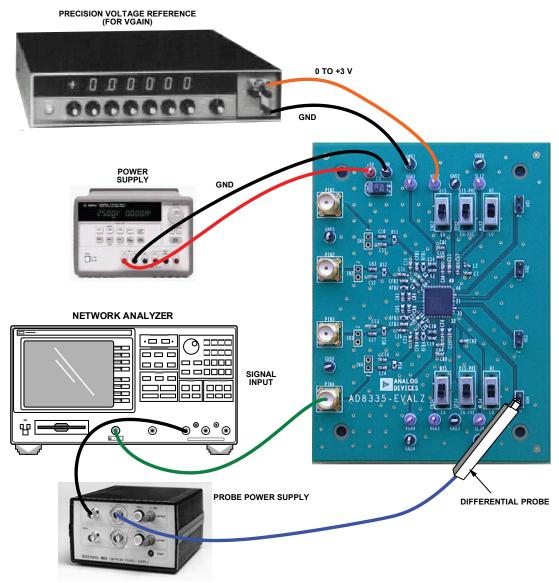

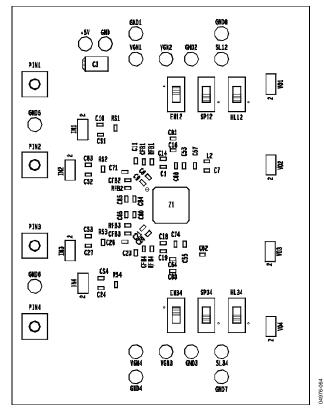

## **EVALUATION BOARD**

The AD8335 evaluation board is a convenient way to experiment with the operation and features of the AD8335 quad VGA. Switches connect or disconnect the low noise preamp and VGA channels and the two gain ranges. Just connect a 5 V/200 mA power supply to the red and black test loop and a differential probe (or two single-ended scope probes) to the output 2-pin headers to observe the output voltage. Test loops are also provided for the gain voltage inputs, which are typically dc bias voltages between 0 V and 3 V. The LNA and VGA channels are enabled independently. All channels are tested functionally before shipment. The low noise preamp active input matching is configured for 50  $\Omega$  to terminate a corresponding signal generator or network

analyzer. Input impedances up to  $14.7 \, k\Omega$  are possible by adjusting  $R_{FB}^{-1}$  through  $R_{FB}^{4}$  using the resistor values listed in Table 6. All passive components are 0603 size surface-mount components. A low noise voltage source (be careful of noise at the switching supply terminals) is recommended for gain control voltage (VGN1, VGN2, VGN3, and VGN4) inputs.

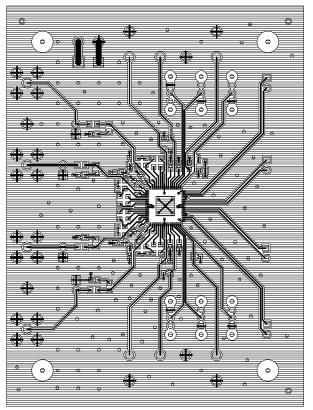

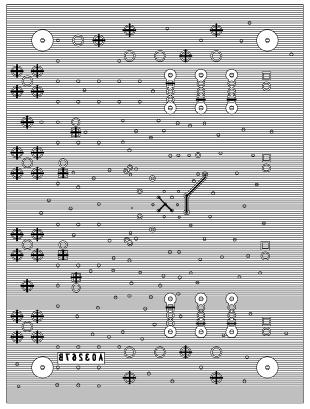

#### **BOARD LAYOUT**