### **General Description**

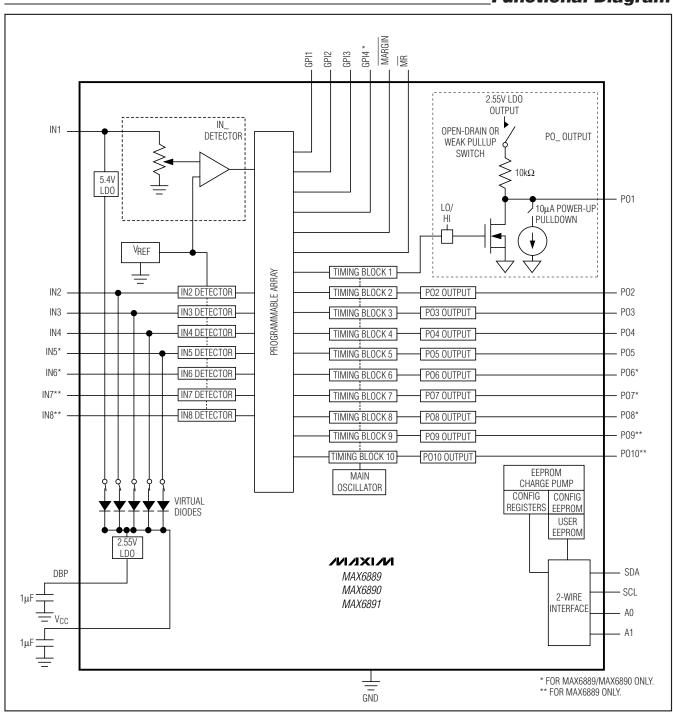

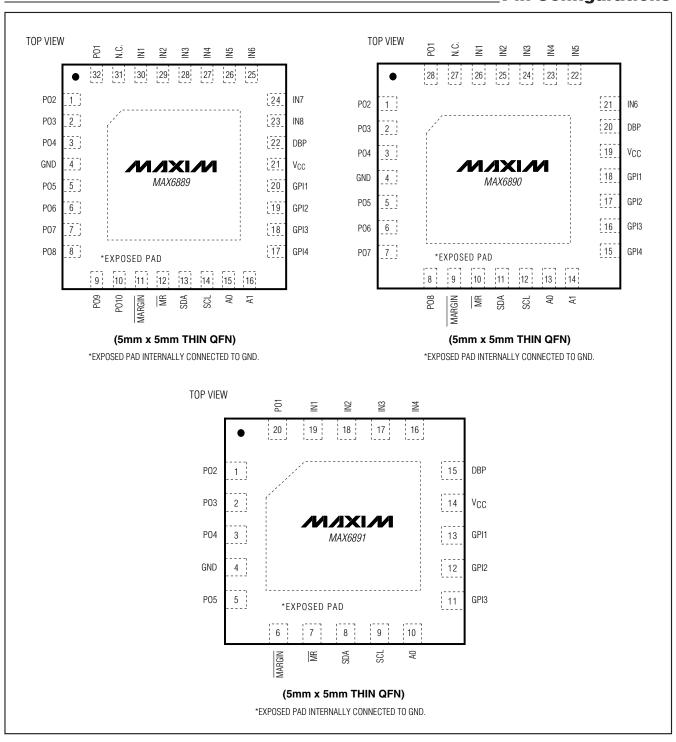

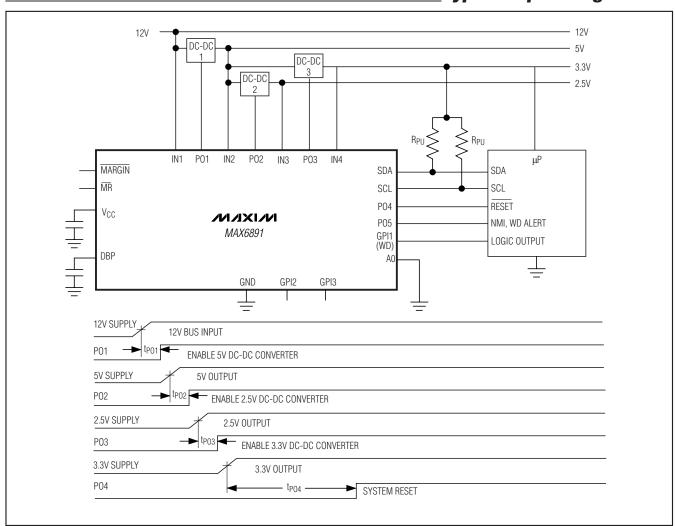

The MAX6889/MAX6890/MAX6891 EEPROM-configurable, multivoltage supply sequencers/supervisors monitor several voltage detector inputs and generalpurpose logic inputs and feature programmable outputs for highly configurable power-supply sequencing applications. The MAX6889 features eight voltage detector inputs and ten programmable outputs. The MAX6890 features six voltage detector inputs and eight programmable outputs, while the MAX6891 features four voltage detector inputs and five programmable outputs. Manual reset and margin disable inputs offer additional flexibility.

All voltage detectors offer a configurable threshold for undervoltage detection. High-voltage input IN1 monitors voltages from 2.5V to 13.2V in 50mV increments, or from 1.25V to 7.625V in 25mV increments. Inputs IN2-IN7 monitor voltages from 1V to 5.5V in 20mV increments or from 0.5V to 3.05V in 10mV increments. High-voltage input IN8 monitors voltages from 2.5V to 15.25V in 50mV increments, or from 1.25V to 7.625V in 25mV increments.

Programmable output stages control power-supply sequencing or system resets/interrupts. Programmable output options include: active-high, active-low, open drain, and weak pullup. Programmable timing delay blocks configure each output to wait between 25µs and 1600ms before deasserting.

The MAX6889/MAX6890/MAX6891 feature a watchdog timer for added flexibility. Program the watchdog timer to assert one or more programmable outputs. The initial and normal watchdog timeout periods are independently programmable from 6.25ms to 102.4s.

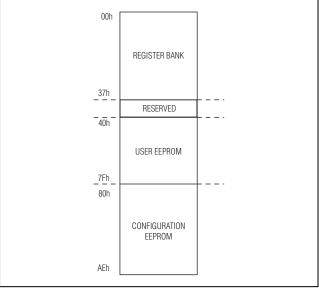

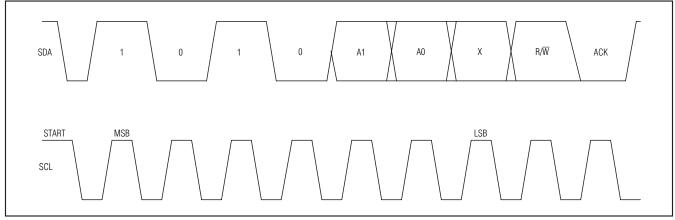

An SMBus™/I<sup>2</sup>C-compatible, 2-wire serial data interface programs and communicates with the configuration EEPROM, the configuration registers, and the internal 512-bit user EEPROM.

The MAX6889/MAX6890/MAX6891 are available in 5mm x 5mm x 0.8mm thin QFN packages and are specified to operate over the extended temperature range (-40°C to +85°C).

### **Applications**

Telecommunication/Central Office Systems

**Networking Systems**

Servers/Workstations

**Base Stations**

Storage Equipment

Multi-Microprocessor/Voltage Systems

**Features**

- ♦ Eight (MAX6889), Six (MAX6890), or Four (MAX6891) Configurable Input Voltage Detectors High-Voltage Input (1.25V to 7.625V or 2.5V to 13.2V)

- Six (MAX6889), Five (MAX6890), or Three (MAX6891) Voltage Inputs (0.5V to 3.05V or 1V to 5.5V)

- Additional (MAX6889) High-Voltage Input (1.25V to 7.625V or 2.5V to 15.25V)

- **♦** Four (MAX6889/MAX6890) or Three (MAX6891) General-Purpose Logic Inputs

- **♦ Configurable Watchdog Timer**

- **♦** Ten (MAX6889), Eight (MAX6890), or Five (MAX6891) Programmable Outputs Active-High, Active-Low, Open Drain, Weak **Pullup**

- Timing Delays from 25µs to 1600ms

- ♦ Margining Disable and Manual Reset Controls

- ♦ 512-Bit Internal User EEPROM Endurance: 100,000 Erase/Write Cycles **Data Retention: 10 Years**

- **♦** I<sup>2</sup>C/SMBus-Compatible Serial **Configuration/Communication Interface**

- ♦ ±1% Threshold Accuracy

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX6889ETJ | -40°C to +85°C | 32 Thin QFN-EP* |

| MAX6890ETI | -40°C to +85°C | 28 Thin QFN-EP* |

| MAX6891ETP | -40°C to +85°C | 20 Thin QFN-EP* |

<sup>\*</sup>EP = Exposed pad.

Pin Configurations and Typical Operating Circuit appear at end of data sheet.

SMBus is a trademark of Intel Corp.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.) IN2-IN7, V <sub>CC</sub> , SDA, SCL, A0, A1, GPI_ |              |

|-------------------------------------------------------------------------------------|--------------|

| MR, MARGIN                                                                          | 0.3V to +6V  |

| IN1, PO                                                                             |              |

| IN8                                                                                 | 0.3V to +20V |

| DBP                                                                                 | 0.3V to +3V  |

| Input/Output Current (all pins)                                                     | ±20mA        |

| Continuous Power Dissipation ( $T_A = +70$ °C)                                      |              |

| 20-Pin Thin QFN (derate 21.3mW/°C                                                   |              |

| above +70°C)                                                                        | 1702mW       |

| 28-Pin Thin QFN (derate 21.3mW/°C |        |

|-----------------------------------|--------|

| above +70°C)                      | 1702mW |

| 32-Pin Thin QFN (derate 21.3mW/°C |        |

| above +70°C)                      | 1702mW |

| Operating Temperature Range       |        |

| Maximum Junction Temperature      | +150°C |

| Storage Temperature Range         |        |

| Lead Temperature (soldering, 10s) | +300°C |

|                                   |        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1}=6.5V\ to\ 13.2V,\ V_{IN2}-V_{IN7}=2.7V\ to\ 5.5V,\ V_{IN8}=10V,\ GPI_=GND,\ \overline{MARGIN}=\overline{MR}=DBP,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C$ .) (Notes 1, 2, 3)

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                            | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Opposition Valtage Flance           | V <sub>IN1</sub>  | Voltage on IN1 to ensure the device is fully operational, IN2–IN8 = GND                               | 4.0   |      | 13.2  |       |

| Operating Voltage Range<br>(Note 4) |                   | Voltage on any one of IN2-IN5 or V <sub>CC</sub> to ensure the device is fully operational, IN1 = GND | 2.7   |      | 5.5   | V     |

| IN1 Supply Voltage (Note 4)         | V <sub>IN1P</sub> | Minimum voltage on IN1 to guarantee that the device is powered through IN1                            |       |      | 6.5   | V     |

| Undervoltage Lockout                | V <sub>UVLO</sub> | Minimum voltage on one of IN2–IN5 to guarantee the device is EEPROM configured                        |       |      | 2.5   | V     |

| Digital Bypass Voltage              | $V_{DBP}$         | No load                                                                                               | 2.48  | 2.55 | 2.67  | V     |

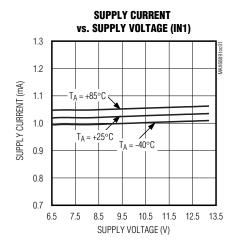

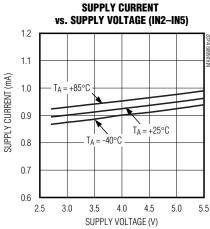

|                                     | lcc               | V <sub>IN1</sub> = 13.2V, IN2–IN8 = GND, no load                                                      |       | 1    | 1.2   | mA    |

| Supply Current                      |                   | Writing to configuration registers or EEPROM, no load                                                 |       | 1.1  | 1.5   | mA    |

|                                     |                   | V <sub>IN1</sub> (50mV increments)                                                                    | 2.5   |      | 13.2  |       |

|                                     |                   | V <sub>IN1</sub> (25mV increments)                                                                    | 1.25  |      | 7.625 |       |

|                                     |                   | V <sub>IN2</sub> -V <sub>IN7</sub> (20mV increments)                                                  | 1.0   |      | 5.5   |       |

| Threshold Voltage Range             | \/                | V <sub>IN2</sub> -V <sub>IN7</sub> (10mV increments)                                                  | 0.50  |      | 3.05  | V     |

| Tilleshold Voltage halige           | V <sub>TH</sub>   | V <sub>IN8</sub> (50mV increments)                                                                    | 2.50  |      | 15.25 | V     |

|                                     |                   | V <sub>IN8</sub> (25mV increments)                                                                    | 1.250 |      | 7.625 |       |

|                                     |                   | V <sub>IN2</sub> –V <sub>IN8</sub> (high-Z mode in 3.3mV increments)                                  | 0.167 |      | 1.017 |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1}=6.5V \text{ to } 13.2V, V_{IN2}-V_{IN7}=2.7V \text{ to } 5.5V, V_{IN8}=10V, \text{GPI}\_=\text{GND}, \overline{\text{MARGIN}}=\overline{\text{MR}}=\text{DBP}, T_A=-40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}\text{C}$ .) (Notes 1, 2, 3)

| PARAMETER                  | SYMBOL                | CONDITIONS                                                 |                                                                                      | MIN    | TYP | MAX    | UNITS             |

|----------------------------|-----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|--------|-----|--------|-------------------|

|                            |                       |                                                            | V <sub>IN</sub> _ = 2.5V to 5.5V (20mV increments)                                   | -1     |     | +1     | %                 |

|                            |                       | $T_A = +25^{\circ}C$ to $+85^{\circ}C$                     | V <sub>IN</sub> _ = 1V to 2.5V<br>(20mV increments)                                  | -25    |     | +25    | mV                |

|                            |                       | (V <sub>IN</sub> _ falling)                                | V <sub>IN</sub> _ = 1.25V to 3.05V<br>(10mV increments)                              | -1     |     | +1     | %                 |

| IN2-IN7 Threshold Accuracy |                       |                                                            | V <sub>IN</sub> _ = 0.5V to 1.25V (10mV increments)                                  | -12.5  |     | +12.5  | mV                |

| ,                          |                       |                                                            | V <sub>IN</sub> _ = 2.5V to 5.5V<br>(20mV increments)                                | -2     |     | +2     | %                 |

|                            |                       | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                     | V <sub>IN</sub> _ = 1V to 2.5V<br>(20mV increments)                                  | -50    |     | +50    | mV                |

|                            |                       | (V <sub>IN</sub> _ falling)                                | V <sub>IN</sub> _ = 1.25V to 3.05V (10mV increments)                                 | -2     |     | +2     | %                 |

|                            |                       |                                                            | V <sub>IN</sub> _ = 0.5V to 1.25V (10mV increments)                                  | -25    |     | +25    | mV                |

|                            |                       | $T_A = +25^{\circ}C$ to $+85^{\circ}C$ ( $V_{IN}$ falling) | V <sub>IN</sub> _ = 6.25V to 13.2V<br>(6.25V to 15.25V for IN8)<br>(50mV increments) | -1     |     | +1     | %                 |

|                            |                       |                                                            | V <sub>IN</sub> _ = 2.5V to 6.25V (50mV increments)                                  | -62.5  |     | +62.5  | mV                |

|                            |                       |                                                            | V <sub>IN</sub> _ = 3.125V to 7.625V (25mV increments)                               | -1     |     | +1     | %                 |

| IN1/IN8 Threshold Accuracy |                       |                                                            | V <sub>IN</sub> _ = 1.25V to 3.125V<br>(25mV increments)                             | -31.25 |     | +31.25 | mV                |

| INT/INO THESHOID ACCURACY  |                       |                                                            | V <sub>IN</sub> _ = 6.25V to 13.2V<br>(6.25V to 15.25V for IN8)<br>(50mV increments) | -2     |     | +2     | %                 |

|                            |                       | $T_A = -40^{\circ}C$ to +85°C                              | V <sub>IN</sub> _ = 2.5V to 6.25V (50mV increments)                                  | -125   |     | +125   | mV                |

|                            |                       | (V <sub>IN</sub> _ falling)                                | V <sub>IN</sub> _ = 3.125V to 7.625V (25mV increments)                               | -2     |     | +2     | %                 |

|                            |                       |                                                            | V <sub>IN</sub> _ = 1.25V to 3.125V (25mV increments)                                | -62.5  |     | +62.5  | mV                |

|                            |                       | IN_ = 0.6V in high                                         | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C$                                        | -1     |     | +1     | 0/                |

| IN_ Threshold Accuracy     |                       | mode (V <sub>IN</sub> _falling                             |                                                                                      | -2     |     | +2     | %                 |

| Threshold Hysteresis       | V <sub>TH-H</sub> yst |                                                            |                                                                                      |        | 0.3 |        | % V <sub>TH</sub> |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1}=6.5V\ to\ 13.2V,\ V_{IN2}-V_{IN7}=2.7V\ to\ 5.5V,\ V_{IN8}=10V,\ GPI\_=GND,\ \overline{MARGIN}=\overline{MR}=DBP,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C$ .) (Notes 1, 2, 3)

| PARAMETER                                   | SYMBOL                               | CONDITIONS                          |                                           | MIN   | TYP    | MAX   | UNITS  |

|---------------------------------------------|--------------------------------------|-------------------------------------|-------------------------------------------|-------|--------|-------|--------|

| Reset-Threshold Temperature Coefficient     | ΔV <sub>TH</sub> /°C                 |                                     |                                           |       | 10     |       | ppm/°C |

| Threshold-Voltage Differential Nonlinearity | V <sub>TH</sub> DNL                  |                                     |                                           | -1    |        | +1    | LSB    |

| IN1 Input Leakage Current                   | I <sub>LIN1</sub>                    | For V <sub>IN1</sub> < the high     | est of V <sub>IN2</sub> -V <sub>IN5</sub> |       | 100    | 140   | μΑ     |

| IN2-IN7 Input Impedance                     | R <sub>IN2</sub> to R <sub>IN7</sub> | V <sub>IN1</sub> > 6.5V             |                                           | 290   | 400    | 555   | kΩ     |

| IN8 Input Impedance                         | R <sub>IN8</sub>                     |                                     |                                           | 730   | 1000   | 1400  | kΩ     |

| IN2-IN8 Input Leakage Current               | I <sub>LIN2-LIN8</sub>               | IN2-IN8 in high-Z r                 | mode, V <sub>IN</sub> _ = 1.017V          | -50   |        | +50   | nA     |

| Power-Up Delay                              | tpu                                  | Vcc ≥ Vuvlo                         |                                           |       |        | 3     | ms     |

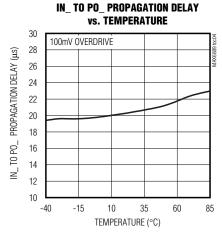

| IN_ to PO_ Delay                            | t <sub>DPO</sub>                     | V <sub>IN</sub> _ falling or rising | g, 100mV overdrive                        |       | 20     |       | μs     |

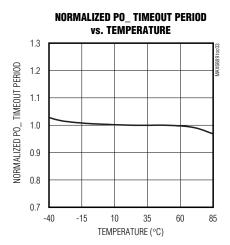

|                                             |                                      |                                     | 000                                       | 8     | 25     | 80    | μs     |

|                                             |                                      |                                     | 001                                       | 1.406 | 1.5625 | 1.719 |        |

|                                             |                                      |                                     | 010                                       | 5.625 | 6.25   | 6.875 |        |

| DO Time and David                           |                                      | Register contents                   | 011                                       | 22.5  | 25     | 27.5  | ms     |

| PO_ Timeout Period                          | t <sub>RP</sub>                      | (Table 19)                          | 100                                       | 45    | 50     | 55    |        |

|                                             |                                      |                                     | 101                                       | 180   | 200    | 220   |        |

|                                             |                                      |                                     | 110                                       | 360   | 400    | 440   |        |

|                                             |                                      |                                     | 111                                       | 1440  | 1600   | 1760  |        |

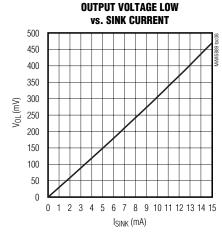

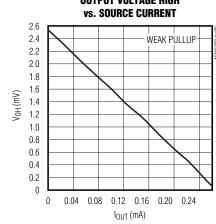

| PO_ Output Low                              | V <sub>OL</sub>                      | I <sub>SINK</sub> = 4mA, outpu      | ıt asserted                               |       |        | 0.4   | V      |

| PO_ Output Initial Pulldown<br>Current      | I <sub>PD</sub>                      | VCC ≤ VUVLO, VPO                    | = 0.8V                                    |       | 10     | 40    | μА     |

| PO_ Output Open-Drain Leakage<br>Current    | ILKG                                 | Output high imped                   | ance                                      | -1    |        | +1    | μА     |

| PO_ Output Pullup Resistance                | R <sub>PU</sub>                      | V <sub>PO</sub> _ = 2V              |                                           | 6.6   | 10     | 15.0  | kΩ     |

| MD MADOIN ODL based Valtage                 | V <sub>IL</sub>                      |                                     |                                           |       |        | 0.6   | V      |

| MR, MARGIN, GPI_ Input Voltage              | VIH                                  |                                     |                                           | 1.4   |        |       | ]      |

| MR Input Pulse Width                        | t <sub>MR</sub>                      |                                     |                                           | 1     |        |       | μs     |

| MR Glitch Rejection                         |                                      |                                     |                                           |       | 100    |       | ns     |

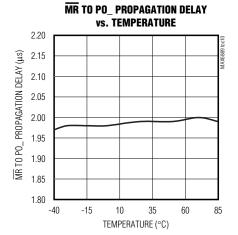

| MR to PO_ Delay                             | t <sub>DMR</sub>                     |                                     |                                           |       | 2      |       | μs     |

| MR to DBP Pullup Current                    | I <sub>MR</sub>                      | V <sub>MR</sub> = 1.4V              |                                           | 5     | 10     | 15    | μΑ     |

| MARGIN to DBP Pullup Current                | IMARGIN                              | V <sub>MARGIN</sub> = 1.4V          |                                           | 5     | 10     | 15    | μΑ     |

| GPI_ Input Hysteresis                       |                                      |                                     |                                           |       | 100    |       | mV     |

| GPI_ to PO_ Delay                           | tDGPI_                               |                                     |                                           |       | 200    |       | ns     |

| GPI_ Pulldown Current                       | I <sub>GPI</sub> _                   | V <sub>GPI</sub> _ = 0.6V           |                                           | 5     | 10     | 15    | μΑ     |

| Watchdog Input Pulse Width                  | twDI                                 | GPI_ configured as                  | a watchdog input                          | 50    |        |       | ns     |

· \_\_\_\_\_\_\_/////

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1}=6.5V \text{ to } 13.2V, V_{IN2}-V_{IN7}=2.7V \text{ to } 5.5V, V_{IN8}=10V, \text{GPI}\_=\text{GND}, \overline{\text{MARGIN}}=\overline{\text{MR}}=\text{DBP}, T_{A}=-40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_{A}=+25^{\circ}\text{C}$ .) (Notes 1, 2, 3)

| PARAMETER                   | SYMBOL           | COI                     | NDITIONS | MIN   | TYP    | MAX    | UNITS |

|-----------------------------|------------------|-------------------------|----------|-------|--------|--------|-------|

|                             |                  |                         | 000      | 5.625 | 6.25   | 6.875  |       |

|                             |                  |                         | 001      | 22.5  | 25     | 27.5   | ma    |

|                             |                  |                         | 010      | 90    | 100    | 110    | ms    |

| Watahdag Timagut Dariad     | *· · ·-          | Register contents       | 011      | 360   | 400    | 440    |       |

| Watchdog Timeout Period     | t <sub>WD</sub>  | (Table 21)              | 100      | 1.44  | 1.60   | 1.76   | s     |

|                             |                  |                         | 101      | 5.76  | 6.40   | 7.04   |       |

|                             |                  |                         | 110      | 23.04 | 25.60  | 28.16  |       |

|                             |                  |                         | 111      | 92.16 | 102.40 | 112.64 |       |

| SERIAL INTERFACE LOGIC (SDA | , SCL, A0, A     | 1)                      |          |       |        |        |       |

| Logic-Input Low Voltage     | VIL              |                         |          |       |        | 8.0    | V     |

| Logic-Input High Voltage    | VIH              |                         |          | 2.0   |        |        | V     |

| Input Leakage Current       | I <sub>LKG</sub> |                         |          | -1    |        | +1     | μΑ    |

| Output Low Voltage          | V <sub>OL</sub>  | I <sub>SINK</sub> = 3mA |          |       | •      | 0.4    | V     |

| Input/Output Capacitance    | C <sub>I/O</sub> |                         |          |       | 10     |        | pF    |

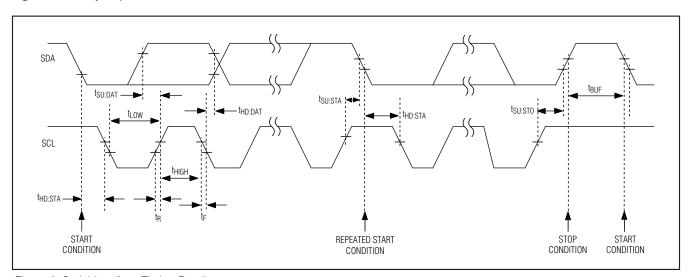

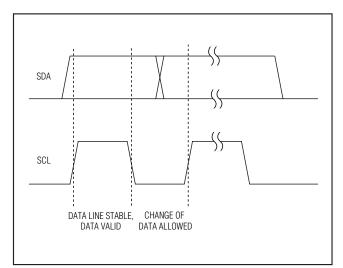

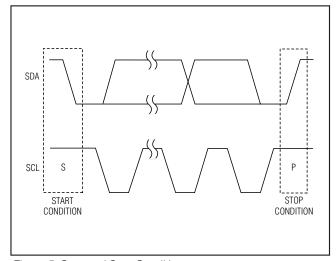

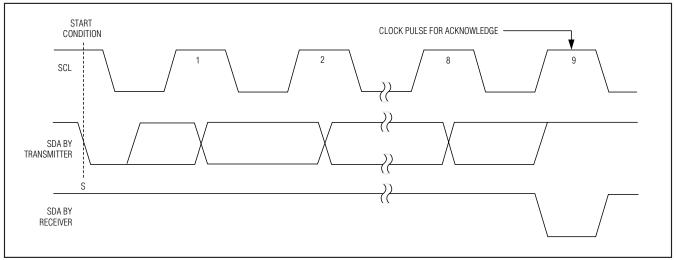

### **SERIAL INTERFACE TIMING CHARACTERISTICS (Figure 3)**

(IN1 = GND,  $V_{IN2}$ – $V_{IN7}$  = 2.7V to 5.5V,  $V_{IN8}$  = 10V,  $GPI_{-}$  = GND,  $\overline{MARGIN}$  =  $\overline{MR}$  = DBP,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.) (Notes 1, 2, 3)

| PARAMETER                            | SYMBOL  | CONDITIONS               | MIN                            | TYP                            | MAX | UNITS |

|--------------------------------------|---------|--------------------------|--------------------------------|--------------------------------|-----|-------|

| Serial Clock Frequency               | fscl    |                          |                                |                                | 400 | kHz   |

| Clock Low Period                     | tLOW    |                          | 1.3                            |                                |     | μs    |

| Clock High Period                    | thigh   |                          | 0.6                            |                                |     | μs    |

| Bus-Free Time                        | tBUF    |                          | 1.3                            |                                |     | μs    |

| START Setup Time                     | tsu:sta |                          | 0.6                            |                                |     | μs    |

| START Hold Time                      | thd:sta |                          | 0.6                            |                                |     | μs    |

| STOP Setup Time                      | tsu:sto |                          | 0.6                            |                                |     | μs    |

| Data In Setup Time                   | tsu:dat |                          | 100                            |                                |     | ns    |

| Data In Hold Time                    | thd:dat |                          | 30                             |                                | 900 | ns    |

| Receive SCL/SDA Minimum<br>Rise Time | tR      | (Note 5)                 |                                | 20 + 0.1<br>x C <sub>BUS</sub> |     | ns    |

| Receive SCL/SDA Maximum<br>Rise Time | tR      | (Note 5)                 |                                | 300                            |     | ns    |

| Receive SCL/SDA Minimum Fall Time    | tF      | (Note 5)                 | 20 + 0.1<br>× C <sub>BUS</sub> |                                | ns  |       |

| Receive SCL/SDA Maximum Fall Time    | tF      | (Note 5)                 |                                | 300                            | _   | ns    |

| Transmit SDA Fall Time               | tF      | C <sub>BUS</sub> = 400pF | 20 + 0.0<br>x C <sub>BUS</sub> |                                | 300 | ns    |

### **SERIAL INTERFACE TIMING CHARACTERISTICS (Figure 3) (continued)**

(IN1 = GND,  $V_{IN2}$ – $V_{IN7}$  = 2.7V to 5.5V,  $V_{IN8}$  = 10V,  $GPI_{-}$  = GND,  $\overline{MARGIN}$  =  $\overline{MR}$  = DBP,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.) (Notes 1, 2, 3)

| PARAMETER                       | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------|--------|------------|-----|-----|-----|-------|

| Pulse Width of Spike Suppressed | tsp    | (Note 6)   |     | 50  |     | ns    |

| EEPROM Byte Write Cycle Time    | twR    | (Note 7)   |     |     | 11  | ms    |

Note 1: 100% production tested at  $T_A = +25$ °C and  $T_A = +85$ °C. Specifications at  $T_A = -40$ °C are guaranteed by design.

**Note 2:** Specifications are guaranteed for the stated global conditions. The device also meets the parameters specified when  $0 < V_{IN1} < 6.5V$  and at least one of  $V_{IN2}$ – $V_{IN5}$  is between 2.7V and 5.5V, while the remaining  $V_{IN2}$ – $V_{IN5}$  are between 0 and 5.5V. Specifications are also guaranteed if  $V_{CC}$  is externally supplied.

Note 3: Device may be supplied from any one of IN1 to IN5, or V<sub>CC</sub> (see the *Powering the MAX6889/MAX6890/MAX6891* section).

**Note 4:** The internal supply voltage, measured at  $V_{CC}$ , equals the maximum of IN2 to IN5 if  $V_{IN1} = 0V$ , or equals 5.4V if  $V_{IN1} > 6.5V$ . For  $4V < V_{IN1} < 6.5V$  and  $V_{IN2} - V_{IN5} > 2.7V$ , the input that powers the device cannot be determined.

Note 5: CBUS = total capacitance of one bus line in pF. Rise and fall times are measured between 0.1 x VBUS and 0.9 x VBUS.

Note 6: Input filters on SDA, SCL, A0, and A1 suppress noise spikes < 50ns.

Note 7: An additional cycle is required when writing to configuration memory for the first time.

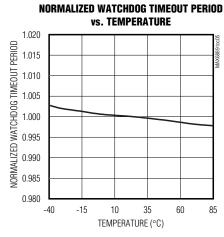

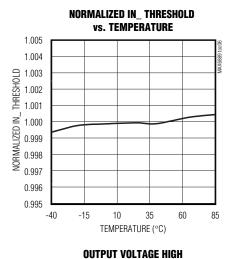

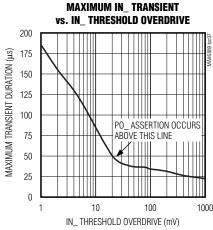

### **Typical Operating Characteristics**

$(V_{IN1} = 6.5V \text{ to } 13.2V, V_{IN8} = 10V, V_{IN} = 2.7V \text{ to } 5.5V, \\ GPI_{-} = GND, \\ \overline{MARGIN} = \overline{MR} = DBP, \\ T_{A} = +25^{\circ}C, \\ unless \text{ otherwise noted.})$

### Typical Operating Characteristics (continued)

$(V_{IN1}=6.5V \text{ to } 13.2V, V_{IN8}=10V, V_{IN}=2.7V \text{ to } 5.5V, \text{GPI}_=\text{GND}, \overline{\text{MARGIN}}=\overline{\text{MR}}=\text{DBP}, T_{A}=+25^{\circ}\text{C}, \text{ unless otherwise noted.})$

### **Pin Description**

|         | PIN     |         | PIN    |                                                                                                                                                                                                                                                                                                                             |  |  |

|---------|---------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX6889 | MAX6890 | MAX6891 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                    |  |  |

| 1       | 1       | 1       | PO2    | Programmable Output 2. Configurable, active-high, active-low, open-drain, or weak pullup output. PO2 pulls low with a 10μA internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO2 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V.       |  |  |

| 2       | 2       | 2       | PO3    | Programmable Output 3. Configurable, active-high, active-low, open-drain, or weak pullup output. PO3 pulls low with a 10μA internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO3 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V.       |  |  |

| 3       | 3       | 3       | PO4    | Programmable Output 4. Configurable, active-high, active-low, open-drain, or weak pullup output. PO4 pulls low with a 10 $\mu$ A internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO4 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V. |  |  |

| 4       | 4       | 4       | GND    | Ground                                                                                                                                                                                                                                                                                                                      |  |  |

| 5       | 5       | 5       | PO5    | Programmable Output 5. Configurable, active-high, active-low, open-drain, or weak pullup output. PO5 pulls low with a 10µA internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO5 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V.       |  |  |

| 6       | 6       | _       | PO6    | Programmable Output 6. Configurable, active-high, active-low, open-drain, or weak pullup output. PO6 pulls low with a 10 $\mu$ A internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO6 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V. |  |  |

| 7       | 7       | _       | P07    | Programmable Output 7. Configurable, active-high, active-low, open-drain, or weak pullup output. PO7 pulls low with a 10 $\mu$ A internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO7 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V. |  |  |

| 8       | 8       | _       | PO8    | Programmable Output 8. Configurable, active-high, active-low, open-drain, or weak pullup output. PO8 pulls low with a 10 $\mu$ A internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO8 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V. |  |  |

| 9       | _       | _       | PO9    | Programmable Output 9. Configurable, active-high, active-low, open-drain, or weak pullup output. PO9 pulls low with a 10µA internal current sink for +1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO9 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V.      |  |  |

| 10      | _       | _       | PO10   | Programmable Output 10. Configurable, active-high, active-low, open-drain, or weak pullup output. PO10 pulls low with a 10µA internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO10 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V.    |  |  |

| 11      | 9       | 6       | MARGIN | Margin Input. MARGIN holds PO_ in its existing state when MARGIN is driven low. Leave MARGIN unconnected or connect to DBP if unused. MARGIN overrides MR if both assert at the same time. MARGIN is internally pulled up to DBP through a 10µA current source.                                                             |  |  |

### Pin Description (continued)

| PIN     |         | NI 4    | FUNCTION |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6889 | MAX6890 | MAX6891 | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12      | 10      | 7       | MR       | Manual Reset Input. MR is configurable to either assert PO_ into a programmed state or to have no effect on PO_ when driving MR low (see Table 6). Leave MR unconnected or connect to DBP if unused. MR is internally pulled up to DBP through a 10μA current source.                                                                                                                                                |

| 13      | 11      | 8       | SDA      | Serial Data Input/Output (Open Drain). SDA requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                     |

| 14      | 12      | 9       | SCL      | Serial Clock Input. SCL requires an external pullup resistor.                                                                                                                                                                                                                                                                                                                                                        |

| 15      | 13      | 10      | AO       | Address Input 0. Address inputs allow up to four (MAX6889/MAX6890) or two (MAX6891) connections on one common bus. Connect A0 to GND or to the serial-interface power supply.                                                                                                                                                                                                                                        |

| 16      | 14      | _       | A1       | Address Input 1. Address inputs allow up to four MAX6889/MAX6890 connections on one common bus. Connect A1 to GND or to the serial-interface power supply.                                                                                                                                                                                                                                                           |

| 17      | 15      | _       | GPI4     | General-Purpose Logic Input 4. An internal 10µA current source pulls GPI4 to GND. Configure GPI4 to control watchdog timer functions or the programmable outputs.                                                                                                                                                                                                                                                    |

| 18      | 16      | 11      | GPI3     | General-Purpose Logic Input 3. An internal 10µA current source pulls GPI3 to GND. Configure GPI3 to control watchdog timer functions or the programmable outputs.                                                                                                                                                                                                                                                    |

| 19      | 17      | 12      | GPI2     | General-Purpose Logic Input 2. An internal 10µA current source pulls GPI2 to GND. Configure GPI2 to control watchdog timer functions or the programmable outputs.                                                                                                                                                                                                                                                    |

| 20      | 18      | 13      | GPI1     | General-Purpose Logic Input 1. An internal 10µA current source pulls GPI1 to GND. Configure GPI1 to control watchdog timer functions or the programmable outputs.                                                                                                                                                                                                                                                    |

| 21      | 19      | 14      | Vcc      | Internal Power-Supply Voltage. Bypass V <sub>CC</sub> to GND with a 1µF ceramic capacitor. V <sub>CC</sub> supplies power to the internal circuitry. V <sub>CC</sub> is internally powered from the highest of the monitored IN1–IN5 voltages. Do not use V <sub>CC</sub> to supply power to external circuitry. To externally supply V <sub>CC</sub> , see the <i>Powering the MAX6889/MAX6890/MAX6891</i> section. |

| 22      | 20      | 15      | DBP      | Internal Digital Power-Supply Voltage. Bypass DBP to GND with a 1µF ceramic capacitor. DBP supplies power to the EEPROM memory, the internal logic circuitry, and the programmable outputs. Do not use DBP to supply power to external circuitry.                                                                                                                                                                    |

| 23      | _       | _       | IN8      | High-Voltage Input 8. Configure IN8 to detect voltage thresholds from 2.5V to 15.25V in 50mV increments, or 1.25V to 7.625V in 25mV increments. For improved noise immunity, bypass IN8 to GND with a 0.1µF capacitor installed as close to the device as possible.                                                                                                                                                  |

| 24      | _       | _       | IN7      | Voltage Input 7. Configure IN7 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN7 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                                                                                                                   |

### Pin Description (continued)

|         | PIN     |         | PIN  |                                                                                                                                                                                                                                                                                                                             |  | FUNCTION |

|---------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|

| MAX6889 | MAX6890 | MAX6891 | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                    |  |          |

| 25      | 21      | _       | IN6  | Voltage Input 6. Configure IN6 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN6 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                          |  |          |

| 26      | 22      | _       | IN5  | Voltage Input 5. Configure IN5 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN5 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                          |  |          |

| 27      | 23      | 16      | IN4  | Voltage Input 4. Configure IN4 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN4 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                          |  |          |

| 28      | 24      | 17      | IN3  | Voltage Input 3. Configure IN3 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN3 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                          |  |          |

| 29      | 25      | 18      | IN2  | Voltage Input 2. Configure IN2 to detect voltage thresholds between 1V and 5.5V in 20mV increments, or 0.5V to 3.05V in 10mV increments. For improved noise immunity, bypass IN2 to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible.                                                          |  |          |

| 30      | 26      | 19      | IN1  | High-Voltage Input 1. Configure IN1 to detect voltage thresholds from 2.5V to 13.2V in 50mV increments, or 1.25V to 7.625V in 25mV increments. For improved noise immunity, bypass IN1 to GND with a 0.1µF capacitor installed as close to the device as possible.                                                          |  |          |

| 31      | 27      | _       | N.C. | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                    |  |          |

| 32      | 28      | 20      | PO1  | Programmable Output 1. Configurable, active-high, active-low, open-drain, or weak pullup output. PO1 pulls low with a 10 $\mu$ A internal current sink for 1V < V <sub>CC</sub> < V <sub>UVLO</sub> . PO1 assumes its programmed conditional output state when V <sub>CC</sub> exceeds undervoltage lockout (UVLO) of 2.5V. |  |          |

| EP      | EP      | EP      | GND  | Exposed Paddle. Internally connected to GND. Connect exposed paddle to GND or leave floating.                                                                                                                                                                                                                               |  |          |

### Functional Diagram

Figure 1. Top-Level Block Diagram

### **Detailed Description**

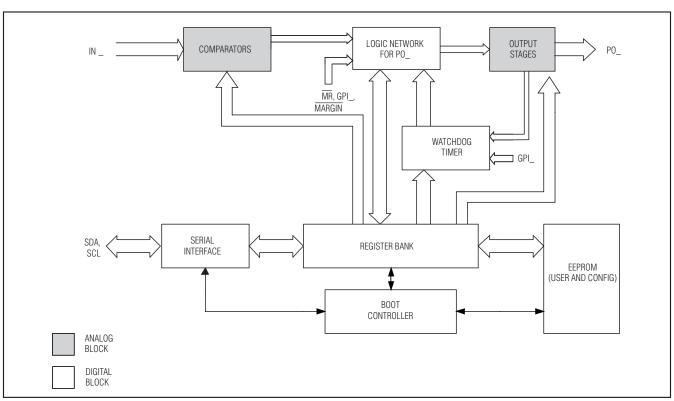

The MAX6889/MAX6890/MAX6891 EEPROM-configurable, multivoltage supply sequencers/supervisors monitor several voltage detector inputs and general-purpose logic inputs, and feature programmable outputs for highly-configurable power-supply sequencing applications. The MAX6889 features eight voltage detector inputs and ten programmable outputs. The MAX6890 features six voltage detector inputs and eight programmable outputs, while the MAX6891 features four voltage detector inputs and five programmable outputs. Manual reset and margin disable inputs simplify board-level testing during the manufacturing process.

All voltage detectors provide configurable thresholds for undervoltage detection. The high-voltage input (IN1) monitors voltages from 1.25V to 7.625V in 25mV increments, or 2.5V to 13.2V in 50mV increments. Inputs (IN2-IN7) monitor voltages from 0.5V to 3.05V in 10mV increments, or 1.0V to 5.5V in 20mV increments. An additional high-voltage input (IN8, MAX6889 only) monitors voltages from 1.25V to 7.625V in 25mV increments, or 2.5V to 15.25V in 50mV increments. To

monitor thresholds from 0.1667V to 1.0167V in 3.3mV increments, the respective input voltage detector must be programmed for high impedance (high-Z) and an external voltage-divider must be connected.

The host controller communicates with the MAX6889/MAX6890/MAX6891s' internal 512-bit user EEPROM, configuration EEPROM, and configuration registers through an SMBus/I<sup>2</sup>C-compatible serial interface (see Figure 1).

Programmable output options include active-high, active-low, open drain, and weak pullup. Program each output to assert on any voltage detector input, general-purpose logic input, watchdog timer, or manual reset. Programmable timing delay blocks configure each output to wait between 25µs and 1600ms before deasserting.

The MAX6889/MAX6890/MAX6891 feature a watchdog timer for added flexibility. Program the watchdog timer to assert one or more programmable outputs. Program the watchdog timer to clear on a combination of one GPI\_input and one programmable output, one of the GPI\_inputs only, or one of the programmable outputs only. The initial and normal watchdog timeout periods are independently programmable from 6.25ms to 102.4s.

\_ /N/XI/N

**Table 1. Programmable Features**

| FEATURE                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Voltage Input IN1                                                                 | <ul> <li>2.5V to 13.2V threshold in 50mV increments.</li> <li>1.25V to 7.625V threshold in 25mV increments.</li> </ul>                                                                                                                                                                                                                                                                               |

| Positive Voltage Input<br>IN2-IN7 (MAX6889)<br>IN2-IN6 (MAX6890)<br>IN2-IN4 (MAX6891)  | <ul> <li>1V to 5.5V threshold in 20mV increments.</li> <li>0.5V to 3.05V threshold in 10mV increments.</li> <li>0.1667V to 1.0167V threshold in 3.3mV increments in high-Z mode.</li> </ul>                                                                                                                                                                                                          |

| High-Voltage Input IN8 (MAX6889)                                                       | <ul> <li>2.5V to 15.25V threshold in 50mV increments.</li> <li>1.25V to 7.625V threshold in 25mV increments.</li> <li>0.1667V to 1.0167V threshold in 3.3mV increments in high-Z mode.</li> </ul>                                                                                                                                                                                                    |

| Programmable Outputs<br>PO1-PO10 (MAX6889)<br>PO1-PO8 (MAX6890)<br>PO1-PO5 (MAX6891)   | <ul> <li>Active-high or active-low.</li> <li>Open-drain or weak pullup output.</li> <li>Dependent on MR, MARGIN, IN_, GPI_, and WD.</li> <li>Programmable reset timeout periods of 25µs, 1.5625ms, 6.25ms, 25ms, 50ms, 200ms, 400ms, or 1.6s.</li> </ul>                                                                                                                                             |

| General-Purpose Logic Inputs:<br>GPI1-GPI4<br>(MAX6889-MAX6890)<br>GPI1-GPI3 (MAX6891) | <ul> <li>Active-high or active-low logic levels.</li> <li>Configure GPI_ as inputs to the watchdog timer or the programmable output stages.</li> </ul>                                                                                                                                                                                                                                               |

| Watchdog Timer                                                                         | <ul> <li>Clear dependent on any combination of one GPI_ input and one programmable output, a GPI_ input only, or a programmable output only.</li> <li>Initial watchdog timeout period of 6.25ms, 25ms, 100ms, 400ms, 1.6s, 6.4s, 25.6s, or 102.4s.</li> <li>Normal watchdog timeout period of 6.25ms, 25ms, 100ms, 400ms, 1.6s, 6.4s, 25.6s, or 102.4s.</li> <li>Watchdog enable/disable.</li> </ul> |

| Manual Reset Input (MR)                                                                | <ul> <li>Forces PO_ into the active output state when MR = GND.</li> <li>PO_ deassert after MR releases high and the PO_ timeout period expires.</li> </ul>                                                                                                                                                                                                                                          |

| V <sub>CC</sub> Power Mode                                                             | Programs whether the device is powered from the highest IN_ input or from an external supply connected to V <sub>CC</sub> .                                                                                                                                                                                                                                                                          |

| Write Disable                                                                          | Locks user EEPROM based on PO                                                                                                                                                                                                                                                                                                                                                                        |

| Configuration Lock                                                                     | Locks configuration registers and EEPROM.                                                                                                                                                                                                                                                                                                                                                            |

### Powering the MAX6889/MAX6890/MAX6891

The MAX6889/MAX6890/MAX6891 derive power from the voltage detector inputs: IN1-IN5 (MAX6889/MAX6890), IN1-IN4 (MAX6891), or an external VCC supply. A virtual diode-ORing scheme selects the positive input that supplies power to the device (see the Functional Diagram). IN1 must be at least 4V, or one of IN2-IN5 (MAX6889/MAX6890)/IN2-IN4 (MAX6891) must be at least 2.7V to ensure device operation. An internal LDO regulates IN1 down to 5.4V.

The highest input voltage on IN2-IN5 (MAX6889/ MAX6890)/IN2-IN4 (MAX6891) supplies power to the device, unless  $V_{\rm IN1}$  > 6.5V, in which case IN1 supplies power to the device. For 4V <  $V_{\rm IN1}$  < 6.5V and one of

$V_{IN2}$ – $V_{IN5}$  > 2.7V, the input power source cannot be determined due to the dropout voltage of the LDO. Internal hysteresis ensures that the supply input that initially powered the device continues to power the device when multiple input voltages are within 50mV of each other.

VCC powers the analog circuitry. Bypass VCC to GND with a 1 $\mu$ F ceramic capacitor installed as close to the device as possible. The internal supply voltage, measured at VCC, equals the maximum of IN2–IN5 if V<sub>IN1</sub> = 0V, or equals 5.4V when V<sub>IN1</sub> > 6.5V. Do not use the internally generated VCC to provide power to external circuitry. Power cannot be supplied through high-impedance voltage detector inputs. To externally supply power through VCC:

- 1) Apply a voltage between 2.7V and 5.5V to one of VCC or IN2-IN5.

- 2) Program the internal/external V<sub>CC</sub> power EEPROM at AEh, Bit[2] = 1 (see Table 22).

- 3) Power down the device.

Subsequent power-ups and software reboots require an externally supplied V<sub>CC</sub> to ensure the device is fully operational.

The MAX6889/MAX6890/MAX6891 also generate a digital supply voltage (DBP) for the internal logic circuitry and the EEPROM. Bypass DBP to GND with a  $1\mu F$  ceramic capacitor installed as close to the device as possible. The nominal DBP output voltage is 2.55V. Do not use DBP to provide power to external circuitry.

#### Inputs

The MAX6889/MAX6890/MAX6891 contain multiple logic and voltage detector inputs. Each voltage detector input is monitored for undervoltage thresholds. Table 1 summarizes these various inputs. Set the threshold voltage for each voltage detector input with registers 00h–07h. Each threshold voltage is an undervoltage threshold. Set the threshold range for each voltage detector with register 08h.

#### High-Voltage Input (IN1)

IN1 offers threshold voltages of 2.5V to 13.2V in 50mV increments, or 1.25V to 7.625V in 25mV increments. Use the following equations to set the threshold voltages for IN1:

$$x = \frac{V_{TH} - 2.5V}{0.05V} \text{ for 2.5V to 13.2V range}$$

$$x = \frac{V_{TH} - 1.25V}{0.025V} \text{ for 1.25V to 7.625V range}$$

where  $V_{TH}$  is the desired threshold voltage and x is the decimal code for the desired threshold (Table 2). For the 2.5V to 13.2V range, x must equal 214 or less; oth-

erwise the threshold exceeds the maximum operating voltage of IN1.

#### IN2-IN7

The IN2-IN7 positive voltage detectors monitor voltages from 1V to 5.5V in 20mV increments, 0.5V to 3.05V in 10mV increments, or 0.1667V to 1.0167V in 3.3mV increments in high-Z mode. Use the following equations to set the threshold voltages for IN\_:

$$x = \frac{V_{TH} - 1V}{0.02V} \text{ for 1V to 5.5V range}$$

$$x = \frac{V_{TH} - 0.5V}{0.1V} \text{ for 0.5V to 3.05V range}$$

$$x = \frac{V_{TH} - 0.1667V}{0.0033V} \text{ for 0.1667V to 1.0167V high-Z range}$$

where  $V_{TH}$  is the desired threshold voltage and x is the decimal code for the desired threshold (Table 3). For the 1V to 5.5V range, x must equal 225 or less; otherwise the threshold exceeds the maximum operating voltage of IN2–IN7.

#### High-Voltage Input (IN8)

Configure IN8 to detect positive thresholds from 2.5V to 15.25V in 50mV increments, 1.25V to 7.625V in 25mV increments, or 0.1667V to 1.0167V in 3.3mV increments in high-Z mode. Use the following equations to set the threshold voltages for IN8:

$$x = \frac{V_{TH} - 2.5V}{0.05V} \text{ for } 2.5V \text{ to } 15.25V \text{ range}$$

$$x = \frac{V_{TH} - 1.25V}{0.025V} \text{ for } 1.25V \text{ to } 7.625V \text{ range}$$

$$x = \frac{V_{TH} - 0.1667V}{0.0033V} \text{ for } 0.1667V \text{ to } 1.0167V \text{ high-} Z \text{ range}$$

where  $V_{TH}$  is the desired threshold voltage and x is the decimal code for the desired threshold (Table 4).

**Table 2. IN1 Threshold Settings**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                                                                    |

|---------------------|-----------------------------|--------------|----------------------------------------------------------------------------------------------------------------|

| 00h                 | 80h                         | [7:0]        | IN1 undervoltage detector threshold (V1) (see equations in the <i>Inputs</i> section)                          |

| 08h                 | 88h                         | [0]          | IN1 range selection. 0 = 2.5V to 13.2V range in 50mV increments. 1 = 1.25V to 7.625V range in 25mV increments. |

| 09h                 | 89h                         | [0]          | Must be set to "0" for normal operation                                                                        |

Table 3. IN2-IN7 Threshold Settings

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                                                                                         |

|---------------------|-----------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 01h                 | 81h                         | [7:0]        | IN2 undervoltage detector threshold (V2) (see equations in the <i>Inputs</i> section)                                               |

| 02h                 | 82h                         | [7:0]        | IN3 undervoltage detector threshold (V3) (see equations in the <i>Inputs</i> section)                                               |

| 03h                 | 83h                         | [7:0]        | IN4 undervoltage detector threshold (V4) (see equations in the <i>Inputs</i> section)                                               |

| 04h                 | 84h                         | [7:0]        | IN5 (MAX6889/MAX6890 only) undervoltage detector threshold (V5) (see equations in the <i>Inputs</i> section)                        |

| 05h                 | 85h                         | [7:0]        | IN6 (MAX6889/MAX6890 only) undervoltage detector threshold (V6) (see equations in the <i>Inputs</i> section)                        |

| 06h                 | 86h                         | [7:0]        | IN7 (MAX6889 only) undervoltage detector threshold (V7) (see equations in the <i>Inputs</i> section)                                |

|                     |                             | [1]          | IN2 range selection, 0 = 1V to 5.5V range in 20mV increments, 1 = 0.5V to 3.05V range in 10mV increments                            |

|                     |                             | [2]          | IN3 range selection, 0 = 1V to 5.5V range in 20mV increments, 1 = 0.5V to 3.05V range in 10mV increments                            |

|                     |                             | [3]          | IN4 range selection, 0 = 1V to 5.5V range in 20mV increments, 1 = 0.5V to 3.05V range in 10mV increments                            |

| 08h                 | 88h                         | [4]          | IN5 (MAX6889/MAX6890 only) range selection, $0 = 1V$ to 5.5V range in 20mV increments, $1 = 0.5V$ to 3.05V range in 10mV increments |

|                     |                             | [5]          | IN6 (MAX6889/MAX6890 only) range selection, 0 = 1V to 5.5V range in 20mV increments, 1 = 0.5V to 3.05V range in 10mV increments     |

|                     |                             | [6]          | IN7 (MAX6889 only) range selection, 0 = 1V to 5.5V range in 20mV increments, 1 = 0.5V to 3.05V range in 10mV increments             |

|                     |                             | [7]          | Not used                                                                                                                            |

|                     | 89h                         | [1]          | IN2 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

|                     |                             | [2]          | IN3 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

| 09h                 |                             | [3]          | IN4 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

|                     |                             | [4]          | IN5 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

|                     |                             | [5]          | IN6 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

|                     |                             | [6]          | IN7 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.                         |

#### GPI1-GPI4

The GPI1–GPI4 (General-Purpose Input) programmable logic inputs control power-supply sequencing (programmable outputs), reset/interrupt signaling, and watchdog functions (see the *Configuring the Watchdog Timer* section). Configure GPI1–GPI4 for active-low or active-high logic (Table 5). GPI1–GPI4 internally pull down to GND through a 10µA current sink.

The manual reset  $(\overline{MR})$  input initiates a reset condition. See Table 6 to program the PO\_ outputs to assert when  $\overline{MR}$  is low. All affected programmable outputs remain asserted (see the *Programmable Outputs* section) for their PO\_ timeout periods after  $\overline{MR}$  releases high. An internal 10µA current source pulls  $\overline{MR}$  to DBP. Leave  $\overline{MR}$  unconnected or connect to DBP if unused.

MIXIM

### **Table 4. IN8 Threshold Settings**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                                                                       |

|---------------------|-----------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| 07h                 | 87h                         | [7:0]        | IN8 undervoltage detector threshold (V8) (see equations in the <i>Inputs</i> section)                             |

| 08h                 | 88h                         | [7]          | IN8 range selection.  0 = 2.5V to 15.25V range in 50mV increments.  1 = 1.25V to 7.625V range in 25mV increments. |

| 09h                 | 89h                         | [7]          | IN8 input impedance. 0 = normal mode. 1 = high-Z mode, with a 0.1667V to 1.0167V range in 3.3mV increments.       |

### Table 5. GPI1-GPI4 Active Logic States

| REGISTER<br>ADDRESS | EEPROM<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                   |

|---------------------|-------------------|--------------|---------------------------------------------------------------|

|                     |                   | [0]          | GPI1. 0 = active-low, 1 = active-high.                        |

| 28h                 | A8h               | [1]          | GPI2. 0 = active-low, 1 = active-high.                        |

| 2011                | Aon               | [2]          | GPI3. 0 = active-low, 1 = active-high.                        |

|                     |                   | [3]          | GPI4 (MAX6889/MAX6890 only). 0 = active-low, 1 = active-high. |

#### MARGIN

MARGIN allows system-level testing while power supplies exceed the normal ranges. Driving MARGIN low forces the programmable outputs to hold the last state while system-level testing occurs. Leave MARGIN unconnected or connect to DBP if unused. An internal 10μA current source pulls MARGIN to DBP. The state of each programmable output does not change while MARGIN = GND. MARGIN overrides MR if both assert at the same time.

#### **Programmable Outputs**

The MAX6889 features ten programmable outputs, the MAX6890 features eight programmable outputs, and the MAX6891 features five programmable outputs. Selectable output stage configurations include: active-low or active-high, open drain, or weak pullup. During power-up, the programmable outputs pull to GND with an internal 10µA current sink for 1V < VCC < VUVLO. The programmable outputs remain in their active states until their respective PO timeout period expires, and all of the programmed conditions are met for each output. Any output programmed to depend on no condition always remains in its active state (Table 17). An output

configured as active-high is considered asserted when that output is logic-high.

The voltage monitors generate fault signals (logical 0) to the MAX6889/MAX6890/MAX6891s' logic array when an input voltage is below the programmed undervoltage threshold. For example, the PO3 (Table 9) programmable output may depend on the IN1 undervoltage threshold, and the state of GPI1. Write "1"s to R10h[0] and R11h[1] to configure as indicated. IN1 must be above the undervoltage threshold (Table 2) and GPI1 must be inactive (Table 5) to be a logic "1," then PO3 deasserts. The logic state of PO3, in this example, is equivalent to the logical statement: "V1 · GPI1."

Registers 0Ah through 27h configure each of the programmable outputs. Programmable timing blocks set the PO\_ timeout period from 25µs to 1600ms for each programmable output. See Table 17 to set the active state (active-high or active-low) for each programmable output and Tables 18 and 19 to select the output stage types, and PO\_ timeout periods for each output. Each programmable output allows a different set of conditions to assert each output as shown in Tables 7–16.

Table 6. Programmable Output Behavior and MR

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                                                                      |

|---------------------|-----------------------------|--------------|------------------------------------------------------------------------------------------------------------------|

| 0Bh                 | 8Bh                         | [5]          | PO1. 0 = PO1 independent of $\overline{MR}$ , 1 = PO1 asserts when $\overline{MR}$ = low.                        |

| 0Eh                 | 8Eh                         | [5]          | PO2. 0 = PO2 independent of $\overline{MR}$ , 1 = PO2 asserts when $\overline{MR}$ = low.                        |

| 11h                 | 91h                         | [5]          | PO3. 0 = PO3 independent of $\overline{MR}$ , 1 = PO3 asserts when $\overline{MR}$ = low.                        |

| 14h                 | 94h                         | [5]          | PO4. 0 = PO4/PO2 independent of $\overline{MR}$ , 1 = PO4 asserts when $\overline{MR}$ = low.                    |

| 17h                 | 97h                         | [5]          | PO5. 0 = PO5 independent of $\overline{MR}$ , 1 = PO5 asserts when $\overline{MR}$ = low.                        |

| 1Ah                 | 9Ah                         | [5]          | PO6 (MAX6889/MAX6890 only). 0 = PO6 independent of $\overline{MR}$ , 1 = PO6 asserts when $\overline{MR}$ = low. |

| 1Dh                 | 9Dh                         | [5]          | PO7 (MAX6889/MAX6890 only). 0 = PO7 independent of $\overline{MR}$ , 1 = PO7 asserts when $\overline{MR}$ = low. |

| 20h                 | A0h                         | [5]          | PO8 (MAX6889/MAX6890 only). 0 = PO8 independent of $\overline{MR}$ , 1 = PO8 asserts when $\overline{MR}$ = low. |

| 23h                 | A3h                         | [5]          | PO9 (MAX6889 only). $0 = PO9$ independent of $\overline{MR}$ , $1 = PO9$ asserts when $\overline{MR} = low$ .    |

| 26h                 | A6h                         | [5]          | PO10 (MAX6889 only). $0 = PO10$ independent of $\overline{MR}$ , $1 = PO10$ asserts when $\overline{MR} = low$ . |

**Table 7. PO1 Output Dependency**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT   | OUTPUT ASSERTION CONDITIONS                                                              |

|---------------------|-----------------------------|-------|------------------------------------------------------------------------------------------|

|                     |                             | [0]   | 1 = PO1 assertion depends on IN1 undervoltage threshold (Table 2)                        |

|                     |                             | [1]   | 1 = PO1 assertion depends on IN2 undervoltage threshold (Table 3)                        |

|                     |                             | [2]   | 1 = PO1 assertion depends on IN3 undervoltage threshold (Table 3)                        |

|                     |                             | [3]   | 1 = PO1 assertion depends on IN4 undervoltage threshold (Table 3)                        |

| 0Ah                 | 8Ah                         | [4]   | 1 = PO1 assertion depends on IN5 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [5]   | 1 = PO1 assertion depends on IN6 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [6]   | 1 = PO1 assertion depends on IN7 (MAX6890 only) undervoltage threshold (Table 3)         |

|                     |                             | [7]   | 1 = PO1 assertion depends on IN8 (MAX6890 only) undervoltage threshold (Table 4)         |

|                     |                             | [0]   | 1 = PO1 assertion depends on watchdog (Table 20)                                         |

|                     |                             | [1]   | 1 = PO1 assertion depends on GPI1 (Table 5)                                              |

|                     |                             | [2]   | 1 = PO1 assertion depends on GPI2 (Table 5)                                              |

| 0Bh                 | 8Bh                         | [3]   | 1 = PO1 assertion depends on GPI3 (Table 5)                                              |

|                     |                             | [4]   | 1 = PO1 assertion depends on GPI4 (MAX6889/MAX6890 only) (Table 5)                       |

|                     |                             | [5]   | 1 = PO1 asserts when MR = low (Table 6)                                                  |

|                     |                             | [7:6] | Not used                                                                                 |

**Note:** Table 7 only applies to PO1. Write a "0" to a bit to make the PO1 output independent of the respective signal (IN\_ thresholds, WD, GPI\_, or  $\overline{\text{MR}}$ ).

**Table 8. PO2 Output Dependency**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT   | OUTPUT ASSERTION CONDITIONS                                                              |

|---------------------|-----------------------------|-------|------------------------------------------------------------------------------------------|

|                     |                             | [0]   | 1 = PO2 assertion depends on IN1 undervoltage threshold (Table 2)                        |

|                     |                             | [1]   | 1 = PO2 assertion depends on IN2 undervoltage threshold (Table 3)                        |

|                     |                             | [2]   | 1 = PO2 assertion depends on IN3 undervoltage threshold (Table 3)                        |

|                     |                             | [3]   | 1 = PO2 assertion depends on IN4 undervoltage threshold (Table 3)                        |

| 0Dh                 | 8Dh                         | [4]   | 1 = PO2 assertion depends on IN5 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [5]   | 1 = PO2 assertion depends on IN6 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [6]   | 1 = PO2 assertion depends on IN7 (MAX6890 only) undervoltage threshold (Table 3)         |

|                     |                             | [7]   | 1 = PO2 assertion depends on IN8 (MAX6890 only) undervoltage threshold (Table 4)         |

|                     |                             | [0]   | 1 = PO2 assertion depends on watchdog (Table 20)                                         |

|                     |                             | [1]   | 1 = PO2 assertion depends on GPI1 (Table 5)                                              |

|                     |                             | [2]   | 1 = PO2 assertion depends on GPI2 (Table 5)                                              |

| 0Eh                 | 8Eh                         | [3]   | 1 = PO2 assertion depends on GPI3 (Table 5)                                              |

|                     |                             | [4]   | 1 = PO2 assertion depends on GPI4 (MAX6889/MAX6890 only) (Table 5)                       |

|                     |                             | [5]   | 1 = PO2 asserts when MR = low (Table 6)                                                  |

|                     |                             | [7:6] | Not used                                                                                 |

**Note:** Table 8 only applies to PO2. Write a "0" to a bit to make the PO2 output independent of the respective signal (IN\_ thresholds, WD, GPI\_, or MR).

**Table 9. PO3 Output Dependency**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | ВІТ   | OUTPUT ASSERTION CONDITIONS                                                              |

|---------------------|-----------------------------|-------|------------------------------------------------------------------------------------------|

|                     |                             | [0]   | 1 = PO3 assertion depends on IN1 undervoltage threshold (Table 2)                        |

|                     |                             | [1]   | 1 = PO3 assertion depends on IN2 undervoltage threshold (Table 3)                        |

|                     |                             | [2]   | 1 = PO3 assertion depends on IN3 undervoltage threshold (Table 3)                        |

|                     |                             | [3]   | 1 = PO3 assertion depends on IN4 undervoltage threshold (Table 3)                        |

| 10h                 | 90h                         | [4]   | 1 = PO3 assertion depends on IN5 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [5]   | 1 = PO3 assertion depends on IN6 (MAX6889/MAX6890 only) undervoltage threshold (Table 3) |

|                     |                             | [6]   | 1 = PO3 assertion depends on IN7 (MAX6890 only) undervoltage threshold (Table 3)         |