# RENESAS

# DATASHEET

### ISL6617

PWM Doubler with Phase Shedding Function and Output Monitoring Feature

FN7564 Rev 0.00 February 4, 2010

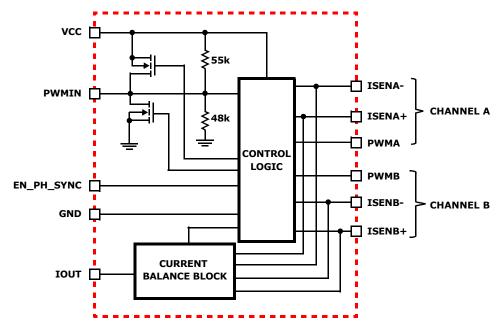

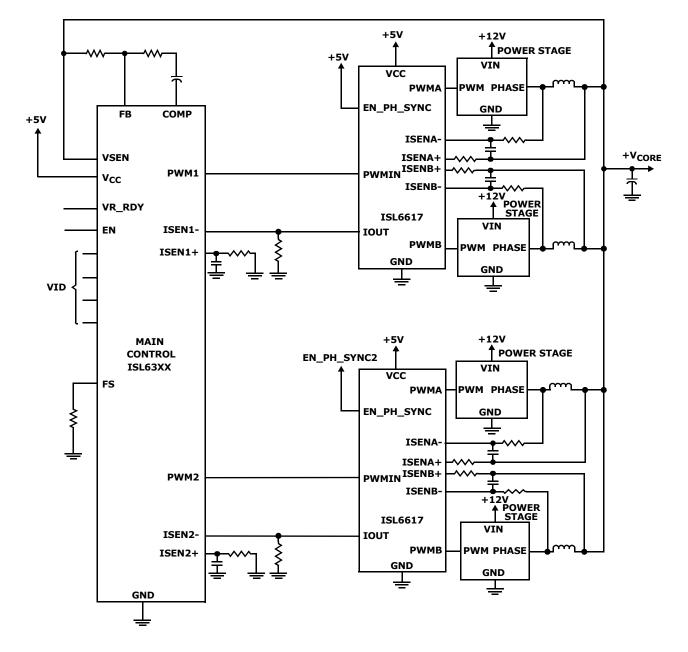

The ISL6617 utilizes Intersil's proprietary Phase Doubler scheme to modulate two-phase power trains with single PWM input. It doubles the number of phases that Intersil's multi-phase controllers ISL63xx can support. When the enable pin (EN\_PH\_SYNC) is pulled low, the PWM input is pulled high. This simplifies the phase shedding implementation for some Intersil controllers (VR10, VR11, VR11.1, and VR12 family) that can disable the respective and higher phase(s) by pulling the respective PWM line high.

The ISL6617 is designed to minimize the number of analog signals that interface between the controller and drivers in high phase count scalable applications. The common COMP signal, which is usually seen in conventional cascaded configuration, is not required; this improves noise immunity and simplifies the layout. Furthermore, the ISL6617 provides low part count and low cost advantage over the conventional cascaded technique.

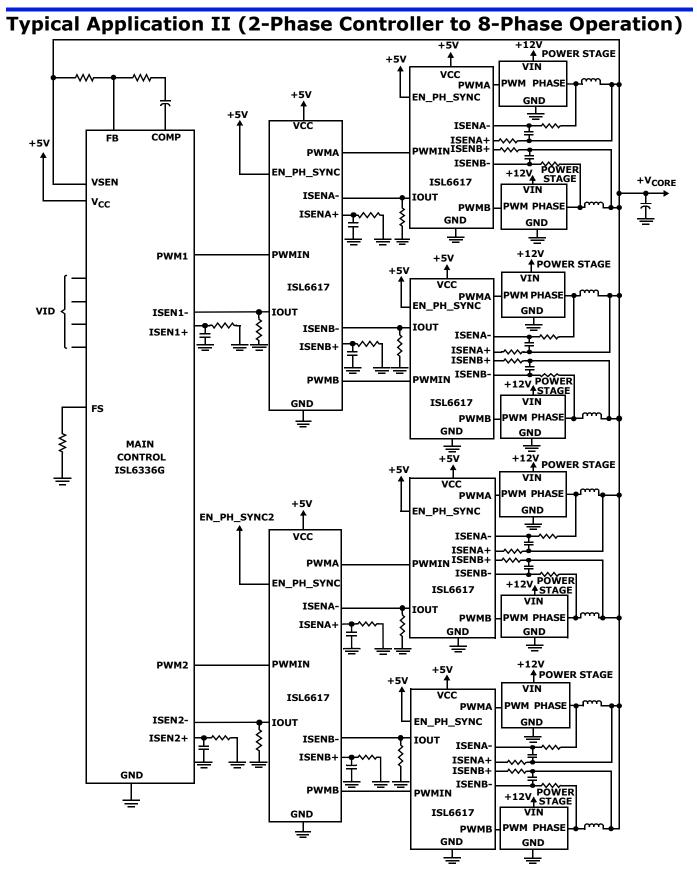

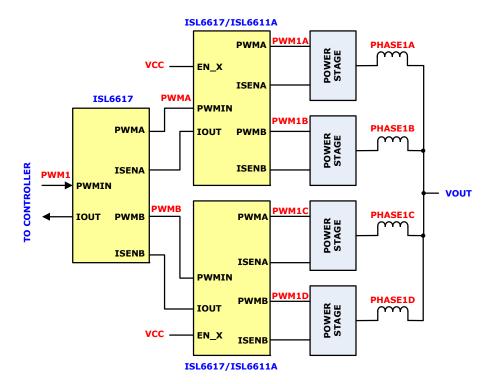

By cascading the ISL6617 with another ISL6617 or ISL6611A, it can quadruple the number of phases that Intersil's multi-phase controllers ISL63xx can support.

The ISL6617 also features Tri-State input and outputs that recognize a high-impedance state, working together with Intersil multiphase PWM controllers and driver stages to prevent negative transients on the controlled output voltage when operation is suspended. This feature eliminates the need for the schottky diode that may be utilized in a power system to protect the load from excessive negative output voltage damage.

## Applications

- High Current Low Voltage DC/DC Converters

- High Frequency and High Efficiency VRM and VRD

- High Phase Count and Phase Shedding Applications

- 5V PWM Input Integrated Power Stage or DrMOS

### Features

- Proprietary Phase Doubler scheme with Phase Shedding Function *(Patent Pending)*

- Enhanced Light to Full Load Efficiency

- Double or Quadruple Phase Count

- Patented Current Balancing with DCR Current Sensing and Adjustable Gain

- Current Monitoring Output (IOUT) to Simplify System Interface and Layout

- Triple-Level Enable Input for Mode Selection

- Dual PWM Output Drives for Two Synchronous Rectified Bridges with Single PWM Input

- Channel Synchronization and Two Interleaving Options

- Tri-State PWM Input and Outputs for Output Stage Shutdown

- Phase Enable Input and PWM Forced High Output to Interface with Intersil's Controller for Phase Shedding

- Overvoltage Protection

- Dual Flat No-Lead (DFN) Package

- Near Chip-Scale Package Footprint; Improves PCB Utilization, Thinner Profile

- Pb-Free (RoHS Compliant)

### **Related Literature**

Technical Brief <u>TB363</u> "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

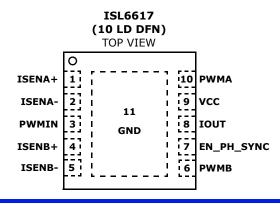

# **Pin Configuration**

RENESAS

FN7564 Rev 0.00 February 4, 2010

# **Functional Pin Descriptions**

| PIN # | PIN SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ISENA+     | Output of the differential amplifier for Channel A. Connect a resistor on this pin to the negative rail of the sensed voltage to set the current gain.                                                                                                                                                                                                   |

| 2     | ISENA-     | Input of the differential amplifier for Channel A. Typically, the positive rail of sensed voltage via DCR sensing network connects to this node.                                                                                                                                                                                                         |

| 3     | PWMIN      | The PWM input signal triggers the J-K flip flop and alternates its input to channel A and B. Both channels are effectively modulated. The PWM signal can enter three distinct states during operation, see Operation section for further details. Connect this pin to the PWM output of the controller. The pin is pulled to VCC when EN_PH_SYNC is low. |

| 4     | ISENB+     | Output of the differential amplifier for Channel B. Connect a resistor on this pin to the negative rail of the sensed voltage to set the current gain.                                                                                                                                                                                                   |

| 5     | ISENB-     | Input of the differential amplifier for Channel B. Typically, the positive rail of sensed voltage via DCR sensing network connects to this node.                                                                                                                                                                                                         |

| 6     | PWMB       | PWM output of Channel B with Tri-state feature.                                                                                                                                                                                                                                                                                                          |

| 7     | EN_PH_SYNC | Driver Enable and Mode Selection Input. See Enable and Mode Operation for more details.                                                                                                                                                                                                                                                                  |

| 8     | IOUT       | Current monitoring Output. It sources out the average current of both Channel A and B.                                                                                                                                                                                                                                                                   |

| 9     | VCC        | Connect this pin to a $+5V$ bias supply. It supplies power to internal analog circuits. Place a high quality low ESR ceramic capacitor from this pin to GND.                                                                                                                                                                                             |

| 10    | PWMA       | PWM output of Channel A with Tri-state feature.                                                                                                                                                                                                                                                                                                          |

| 11    | GND        | Bias and reference ground. All signals are referenced to this node. Place a high quality low ESR ceramic capacitor from this pin to VCC. Connect this pad to the power ground plane (GND) via thermally enhanced connection.                                                                                                                             |

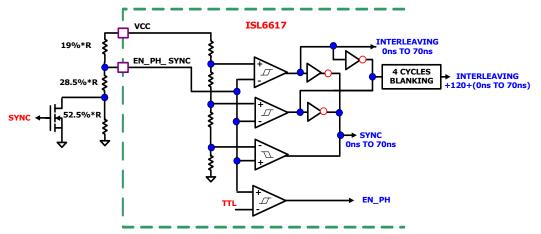

# **Block Diagram**

# Typical Application (2 Phase Controller for 4 Phase Operation)

RENESAS

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|---------------------|----------------------|----------------|

| ISL6617CRZ                     | 617C            | 0 to +70            | 10 Ld 3x3 DFN        | L10.3x3        |

| ISL6617IRZ                     | 617I            | -40 to +85          | 10 Ld 3x3 DFN        | L10.3x3        |

NOTES:

1. Add "-T\*" suffix for tape and reel. Please refer to  $\underline{\text{TB347}}$  for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL6617</u>. For more information on MSL, please see Technical Brief <u>TB363</u>.

#### Absolute Maximum Ratings

| Human Body Model (JEDEC Class 2) 2kV      |

|-------------------------------------------|

| Machine Model (JEDEC Class B)             |

| Charged Device Model (JEDEC Class IV) 2kV |

| Latch Up (JEDEC Class II) +85°C           |

#### **Thermal Information**

| Thermal Resistance (Typical)       | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------|------------------------|------------------------|

| 10 Ld DFN (Notes 4, 5)             | . 48                   | 7                      |

| Maximum Junction Temperature       |                        | +150°C                 |

| Maximum Storage Temperature Rang   | e65°                   | C to +150°C            |

| Pb-Free Reflow Profile             | S                      | ee link below          |

| http://www.intersil.com/pbfree/Pb- | FreeReflow.            | <u>asp</u>             |

#### **Recommended Operating Conditions**

| ISL6617CRZ0°C to +70°C                        |

|-----------------------------------------------|

| ISL6617IRZ40°C to +85°C                       |

| Maximum Operating Junction Temperature +125°C |

| Supply Voltage, VCC                           |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 4.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features.

- 5.  $\theta_{JC}$ , "case temperature" location is at the center of the package underside exposed pad. See Tech Brief TB379 for details.

# **Electrical Specifications** These specifications apply for recommended ambient temperature, unless otherwise noted. **Boldface limits apply over the operating temperature range.**

| PARAMETER                     | SYMBOL           | TEST CONDITIONS                                                 | MIN<br>(Note 6) | ТҮР | MAX<br>(Note 6) | UNITS |

|-------------------------------|------------------|-----------------------------------------------------------------|-----------------|-----|-----------------|-------|

| SUPPLY CURRENT                |                  |                                                                 |                 | 1   |                 |       |

| Bias Supply Current           | IVCC             | PWM pin floating, $V_{VCC} = 5V$ , EN_PH = 5V                   |                 | 5   | 6.5             | mA    |

|                               |                  | PWM pin floating, $V_{VCC} = 5V$ , EN_PH = 0V                   |                 | 5   | 6.5             | mA    |

|                               |                  | $F_{PWM} = 600 \text{kHz}, V_{VCC} = 5V,$<br>EN_PH_SYNC = 5V    |                 | 6   | 7.5             | mA    |

|                               |                  | $F_{PWM} = 600 \text{kHz}, V_{VCC} = 5V,$<br>EN_PH_SYNC = 4.25V |                 | 6   | 7.5             | mA    |

|                               |                  | $F_{PWM}$ = 300kHz, $V_{VCC}$ = 5V,<br>EN_PH_SYNC = 3.25V       |                 | 6   | 7.5             | mA    |

| POWER-ON RESET                |                  | 1                                                               |                 | 1   |                 |       |

| POR Rising                    |                  |                                                                 |                 | 3.4 | 4.2             | V     |

| POR Falling                   |                  |                                                                 | 2.3             | 3.0 |                 | V     |

| Hysteresis                    |                  |                                                                 |                 | 350 |                 | mV    |

| EN_PH_SYNC INPUT              |                  |                                                                 |                 |     |                 |       |

| ENx Minimum LOW Threshold     | V <sub>ENx</sub> |                                                                 |                 |     | 0.8             | V     |

| ENx Maximum HIGH Threshold    | V <sub>ENx</sub> |                                                                 | 2.0             |     |                 | V     |

| SYNC AND INTERLEAVING MODI    |                  | •                                                               | •               |     | •               |       |

| Interleaving Mode 1 Window    | V <sub>ENx</sub> |                                                                 | 97%             |     |                 | VCC   |

| Interleaving Mode 2 Window    | V <sub>ENx</sub> |                                                                 | 78%             |     | 85%             | VCC   |

| Synchronous Mode Window       | V <sub>ENx</sub> |                                                                 | 54%             |     | 64%             | VCC   |

| Typical Threshold Hysteresis  |                  |                                                                 |                 | -5% |                 | VCC   |

| Minimum SYNC Pulse            |                  |                                                                 |                 |     | 40              | ns    |

| Maximum Synchronization Delay |                  |                                                                 | 50              |     |                 | ns    |

| Interleaving Mode Phase Shift |                  | SYNC = 5V, PWM = 300kHz, 10% Width                              |                 | 180 |                 | 0     |

# **Electrical Specifications** These specifications apply for recommended ambient temperature, unless otherwise noted. **Boldface limits apply over the operating temperature range. (Continued)**

| PARAMETER                                     | SYMBOL                                                                             | TEST CONDITIONS                                                              | MIN<br>(Note 6) | түр  | MAX<br>(Note 6) | UNITS |

|-----------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| Synchronization Mode Phase Shift              |                                                                                    | SYNC = 0V, PWM = 300kHz, 10% Width                                           |                 | 0    |                 | 0     |

| PWM INPUT (PWMIN)                             |                                                                                    |                                                                              |                 |      |                 |       |

| Sinking Impedance                             | R <sub>PWM_SNK</sub>                                                               |                                                                              |                 | 55   |                 | kΩ    |

| Source Impedance                              | R <sub>PWM_SRC</sub>                                                               |                                                                              |                 | 48   |                 | kΩ    |

| Minimum Pull-Up Current                       | I <sub>PWM_SRC</sub>                                                               | EN_PH_SYNC = LOW                                                             | 40              |      |                 | mA    |

| Tri-State Rising Threshold                    |                                                                                    | V <sub>VCC</sub> = 5V (250mV Hysteresis)                                     | 0.95            | 1.20 | 1.45            | V     |

| Tri-State Falling Threshold                   |                                                                                    | V <sub>VCC</sub> = 5V (300mV Hysteresis)                                     | 3.00            | 3.40 | 3.7             | V     |

| PWM Pulled High Threshold                     |                                                                                    | EN_PH = LOW, Ramping PWM low                                                 |                 | 3.4  |                 | V     |

| CURRENT SENSE (ISENA±, ISENB                  | ±, IOUT) A                                                                         | ND PROTECTION (IOUT)                                                         |                 |      | 1               |       |

| Sensed Current Tolerance                      | I <sub>OUT</sub>                                                                   | ISENA = ISENB = 0µA                                                          | -6              | 0    | 6               | μA    |

|                                               |                                                                                    | ISENA = ISENB = 20µA                                                         | 14              | 20   | 26              | μA    |

|                                               |                                                                                    | ISENA = ISENB = 50µA                                                         | 43              | 50   | 57              | μA    |

|                                               |                                                                                    | ISENA = ISENB = 100µA                                                        | 90              | 100  | 110             | μA    |

| Un-Tri State Trip For OVP                     | I <sub>OUT</sub>                                                                   | ENx = LOW TO HIGH, PWM = LOW                                                 | 40              | 60   | 90              | μA    |

| PWM OUTPUT (PWMA AND PWMB                     | 5)                                                                                 |                                                                              | I               |      | 1               |       |

| Sourcing Impedance                            | R <sub>PWM_SRC</sub>                                                               | VCC = 5V                                                                     | 45              | 100  | 200             | Ω     |

| Sink Impedance                                | R <sub>PWM_SNK</sub>                                                               | VCC = 5V                                                                     | 45              | 100  | 125             | Ω     |

| Tri-State Level                               | V <sub>PWMA/B</sub>                                                                | VCC = 5V, EN_PH = LOW                                                        | 1.65            | 2.00 | 2.6             | V     |

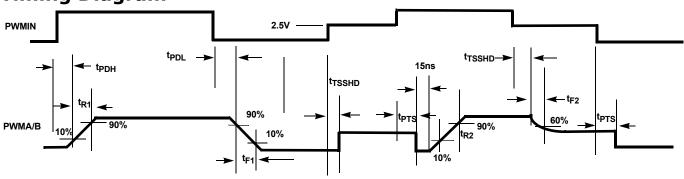

| SWITCHING TIME (See Figure 1 on               | Page 8)                                                                            |                                                                              | I               |      | 1               |       |

| PWMA/B Low to High Rise Time                  | t <sub>R1</sub>                                                                    | Unloaded, 10% to 90%                                                         |                 | 4.5  |                 | ns    |

| PWMA/B Tri-State to High Rise Time            | t <sub>R2</sub>                                                                    | Unloaded, 10% to 90%                                                         |                 | 4.5  |                 | ns    |

| PWMA/B High to Low Fall Time                  | t <sub>F1</sub>                                                                    | Unloaded, 90% to 10%                                                         |                 | 4.0  |                 | ns    |

| PWMA/B High to Tri-State Fall Time            | t <sub>F2</sub>                                                                    | 100% to 60% (3V), Assume Equavilent Loading of RC = $50k\Omega*10pF = 500ns$ |                 | 255  |                 | ns    |

| PWMA/B Turn-On Propagation Delay              | t <sub>PDH</sub>                                                                   | Outputs Unloaded                                                             |                 | 35   |                 | ns    |

| PWMA/B Turn-Off Propagation Delay             | t <sub>PDL</sub>                                                                   | Outputs Unloaded, excluding extension                                        |                 | 35   |                 | ns    |

| PWMA/B Extension                              | t <sub>EXT</sub>                                                                   | $ENx = VCC, I_{PWMA} > I_{PWMB}$                                             |                 | 70   |                 | ns    |

|                                               |                                                                                    | $ENx = VCC, I_{PWMA} < I_{PWMB}$                                             |                 | 70   |                 | ns    |

|                                               |                                                                                    | ENx = 80%*VCC, I <sub>PWMA</sub> > I <sub>PWMB</sub>                         |                 | 190  |                 | ns    |

|                                               |                                                                                    | ENx = 80%*VCC, I <sub>PWMA</sub> < I <sub>PWMB</sub>                         |                 | 190  |                 | ns    |

| Tri-State to High or Low Propagation<br>Delay | State to High or Low Propagation t <sub>PTS</sub> Outputs Unloaded, excluding exte |                                                                              |                 | 10   |                 | ns    |

| Tri-State Shutdown Holdoff Time               | t <sub>TSSHD</sub>                                                                 | Including Propagation Delay                                                  |                 | 65   |                 | ns    |

NOTE:

6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

### **Timing Diagram**

#### Operation

Designed for high phase count and phase shedding applications, the ISL6617 driverless phase doubler is meant to double or quadruple (cascaded option using two ISL6617s) the number of phases that Intersil's multi-phase controllers ISL63xx can support. Further, the PWM line can be pulled high to disable the respective phase and higher phase(s) when the enable pin (EN\_PH\_SYNC) is pulled low. This simplifies the phase shedding implementation for the controller that can disable the respective and higher phase(s) by pulling the respective PWM input high.

A rising transition on PWMIN initiates the turn-on of the PWMA/B (see Figure 1). After a short propagation delay  $[t_{PDH}]$ , the PWMA/B begins to rise. Typical rise times  $[t_{R1}]$  are provided in the "Electrical Specifications" table on page 7.

A falling transition on PWMIN indicates the turn-off of the PWMA/B. The PWMA/B begins to fall  $[t_{F1}]$  after a propagation delay  $[t_{PDL}]$ , which is modulated by the current balance circuits.

When the PWMIN stays in the tri-state window for longer than [ $t_{TSSHD}$ ], both PWMA/B will pull to ~2V so that the cascaded 5V PWM input MOSFET driver or integrated power stage can recognize tri-state.

#### **EN\_PH\_SYNC** Operation

The EN\_PH\_SYNC pin features multiple functions. It is the enable input of the device and the input to select various operational modes.

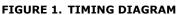

#### A. ENABLE OPERATION

As shown in Figure 2, the ISL6617 disables the doubler operation when the EN\_PH\_SYNC pin is pulled to ground, while the PWMIN pin is pulled to VCC. With the PWM line pulled high, some Intersil controllers such as VR10, VR11, VR11.1 and VR12 family can disable the respective and higher phase(s). When the EN PH SYNC returns high, the phase doubler will pull the PWM line into tri-state window, and then will be enabled only at the leading edge of PWM input. Prior to the first PWMin rising edge, both the PWMA and PWMB output will remain in tri-state unless an overvoltage fault is detected. This fault is defined as when a phase is detected to have more than 60% of the maximum I<sub>OUT</sub> current. This provides additonal protection to the load if the upper MOSFET experiences a short while the doubler is enabled.

The EN\_PH\_SYNC pin should remain high if driving the PWM line high is prohibited for the associated controller. For proper system interface, please refer to the device data sheets.

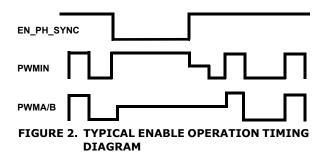

#### **B. SYNCHRONOUS OPERATION**

The ISL6617 can be set in interleaving mode or synchronous mode by pulling the EN\_PH\_SYNC pin to the respective level, shown in Table 1. A synchronous pulse can be sent to the phase doubler during the load application to improve the voltage droop and current balance while still maintaining interleaving operation at DC load conditions. However, excessive ringback can occur; hence, the synchronous mode operation should be carefully investigated. Figure 3 shows how to generate a synchronous pulse when a transient load is applied. The comparator should be a fast comparator with a minimum delay.

#### C. VARIOUS OPERATIONAL MODES

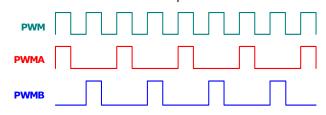

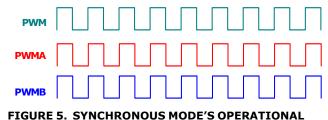

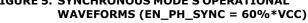

The ISL6617 has three distinct operating modes depending upon the voltage level of the EN PH SYNC pin. To ensure that the ISL6617 is in operation, the pin must be above 2V. When the EN\_PH\_SYNC pin is set to above 97% of  $V_{CC_{1}}$  the ISL6617 will operate in interleaving mode with a maximum extension of 70ns. When  $V_{CC}$  is between 78% and 85% of  $V_{CC}$ , the ISL6617 operates in interleaving mode with a fixed extension of 120ns and a variable extension of up to 70ns. This results in a minimum extension of 120ns and a max of 190ns. To enter this 2nd interleaving mode, the pin must remain in the 78% to 85% range for at least 4 cycles. Between 54% and 64% of  $V_{CC}$ , the device operates in synchronous mode. Figures 4 and 5 show simplified synchronous and interleaving modes' operational waveforms, respectively.

| TABLE 1. ISL6617 OPERATIONAL MODES |

|------------------------------------|

|------------------------------------|

| MODE           | MIN                                                      | ТҮР     | MAX     | EXTENSION                |  |

|----------------|----------------------------------------------------------|---------|---------|--------------------------|--|

| Enable Low     |                                                          |         | 0.8V    |                          |  |

| Enable High    | 2V                                                       |         |         |                          |  |

| Interleaving#1 | 97%*VCC                                                  |         | VCC     | Ons to 70ns              |  |

| Interleaving#2 | 78%*VCC                                                  | 81%*VCC | 85%*VCC | 120ns + (0ns<br>to 70ns) |  |

| Synchronous    | 54%*VCC                                                  | 60%*VCC | 64%*VCC | 0ns to 70ns              |  |

| Not Used       | From 0.8V to 2V or 54% of VCC is not recommended Region. |         |         |                          |  |

To transition between two different modes, the EN\_PH\_SYNC pin voltage level needs to be set accordingly. Figures 6 and 7 show an example of external circuits for mode transition between synchronous mode and interleaving #1 or #2 mode, respectively. The R should be less than  $50k\Omega$  to improve transition time.

FIGURE 4. INTERLEAVING MODE'S OPERATIONAL WAVEFORMS (ENx = VCC, OR 81%\*VCC)

FIGURE 6. CONFIGURATION FOR TRANSITION BETWEEN SYNCHRONOUS AND INTERLEAVING #1 MODES

FIGURE 7. CONFIGURATION FOR TRANSITION BETWEEN SYNCHRONOUS AND INTERLEAVING #2 MODES

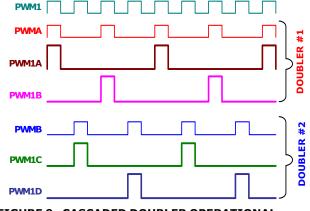

The ISL6617 can further be cascaded with itself or ISL6611A (phase doubler with integrated 5V drivers), as shown in Figure 8. This can quadruple the number of phase each PWM line can support. Figure 9 shows the operational waveforms of the cascaded doublers. The PWMIN pin will be pulled to VCC when the doubler is disabled (EN\_x = Low). To avoid driving the PWM outputs of the 1st stage ISL6617 by the 2nd stage's PWMIN, the 2nd stage doubler's enable input should remain high, i.e, tied to VCC, as shown in Figure 8.

To operate each phase at the switching frequency of  $F_{SW}$ , the operational frequency of the controller needs to be scaled accordingly for different modes, as shown in Table 2.

#### TABLE 2. CONTROLLER FREQUENCY AND MAXIMUM DUTY CYCLE

| OPERATIONAL<br>MODES     | FCONTROLLER         | ISL6617<br>MAXIMUM<br>DUTY CYCLE<br>PER PHASE | D <sub>MAX</sub><br>WITH<br>ISL6336G |

|--------------------------|---------------------|-----------------------------------------------|--------------------------------------|

| Interleaving             | 2 x F <sub>SW</sub> | 50%                                           | 45%                                  |

| Synchronous              | Fsw                 | 100%                                          | 90%                                  |

| Cascaded<br>Interleaving | 4 x Fsw             | 25%                                           | 22.5%                                |

When the doubler operates in interleaving mode, the PWM controller frequency should be set at two times the desired phase frequency (F<sub>SW</sub>). Since the input PWM pulse is divided into half to feed into each phase of the doubler, the operational duty cycle of each phase should be less than 50%. In synchronous mode, the PWM controller should be operated at the same frequency as the desired phase frequency. In this mode, the allowable duty cycle is up to 100%. For cascaded interleaving, the controller switching frequency needs to be set at four times the phase frequency. During cascaded operation, the maximum allowable duty cycle will be less than 25%. All of the maximum allowable duty cycle numbers referenced assume that the PWM controller can send out a 100% duty cycle pulse. In many cases, this is not achievable because the controller needs time to reset it's internal sawtooth ramp or internal max duty limit. However, the fixed 120ns extension of interleaving mode 2 helps recover the typical 1% duty cycle loss associated with the ramp reset time. In addition, Intersil has developed a dedicated controller, the ISL6336G with 90% duty cycle, to work with the ISL6617 for high-phase count and overclocking applications.

#### FIGURE 9. CASCADED DOUBLER OPERATIONAL WAVEFORMS

To properly compensate the system that uses phase doublers, the effective system sawtooth to calculate the modulator gain should factor in the duty cycle limitation ( $D_{MAX}$ ) as Equation 1. For instance, when using ISL6336G and ISL6617s in cascaded interleaving mode, the effective sawtooth amplitude should be scaled as 3V/22.5% = 13.33V.

$$V_{RAMP\_EFFECTIVE} = \frac{V_{RAMP}}{D_{MAX}}$$

(EQ. 1)

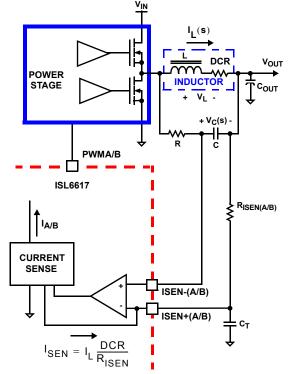

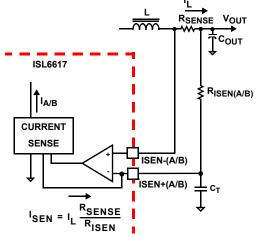

#### **Current Sensing**

The ISL6617 senses current continuously for fast response. The ISL6617 supports inductor DCR sensing, or resistive sensing techniques. The associated channel current sense amplifier uses the ISEN inputs to reproduce a signal proportional to the inductor current, I<sub>L</sub>. The sensed current, I<sub>SEN</sub>, is proportional to the inductor current. The sensed current is used for current balance and load-line regulation.

The internal circuitry, shown in Figures 10 and 11, represents one channel. This circuitry is repeated for each channel in the doubler. The input bias current of the current sensing amplifier is typically 60nA; less than  $5k\Omega$  input impedance is preferred to minimize the offset error. In addition, the common mode input voltage to the amplifier should be less than VCC-3V.

#### A. INDUCTOR DCR SENSING

An inductor's winding is characteristic of a distributed resistance, as measured by the DCR (Direct Current Resistance) parameter. Consider the inductor DCR as a separate lumped quantity, as shown in Figure 10.

#### FIGURE 10. DCR SENSING CONFIGURATION

The channel current  $I_L$ , flowing through the inductor, will also pass through the DCR. Equation 2 shows the s-domain equivalent voltage across the inductor  $V_L.$

$$V_{L}(s) = I_{L} \cdot (s \cdot L + DCR)$$

(EQ. 2)

A simple R-C network across the inductor extracts the DCR voltage, as shown in Figure 10.

The voltage on the capacitor  $V_C$ , can be shown to be proportional to the channel current  $I_L$ . See Equation 3.

$$V_{C}(s) = \frac{\left(s \cdot \frac{L}{DCR} + 1\right) \cdot (DCR \cdot I_{L})}{(s \cdot RC + 1)}$$

(EQ. 3)

If the R-C network components are selected such that the RC time constant matches the inductor time constant (RC = L/DCR), the voltage across the capacitor V<sub>C</sub> is equal to the voltage drop across the DCR, i.e., proportional to the channel current.

With the internal low-offset current amplifier, the capacitor voltage  $V_{\rm C}$  is replicated across the sense

resistor  $R_{\mbox{\rm ISEN}}.$  Therefore, the current out of  $\mbox{\rm ISEN}+\mbox{\rm pin},$   $I_{\mbox{\rm SEN}},$  is proportional to the inductor current.

Because of the internal filter at ISEN- pin, one capacitor,  $C_T$ , is needed to match the time delay between the ISENand ISEN+ signals. Select the proper  $C_T$  to keep the time constant of  $R_{ISEN}$  and  $C_T$  ( $R_{ISEN} \times C_T$ ) close to 27ns.

Equation 4 shows that the ratio of the channel current to the sensed current,  $\rm I_{SEN},$  is driven by the value of the sense resistor and the DCR of the inductor.

$$I_{\text{SEN}} = I_{\text{L}} \cdot \frac{\text{DCR}}{\text{R}_{\text{ISEN}}}$$

(EQ. 4)

#### **B. RESISTIVE SENSING**

For more accurate current sensing, a dedicated resistor  $R_{SENSE}$  in series with each output inductor can serve as the current sense element (see Figure 11). This technique reduces overall converter efficiency due to the additional power loss on the current sense element  $R_{SENSE}$ .

FIGURE 11. SENSE RESISTOR IN SERIES WITH INDUCTORS

The same capacitor  $C_T$  is needed to match the time delay between ISEN- and ISEN+ signals. Select the proper  $C_T$  to keep the time constant of  $R_{ISEN}$  and  $C_T$  ( $R_{ISEN} \times C_T$ ) close to 27ns.

Equation 5 shows the ratio of the channel current to the sensed current  $\mathrm{I}_{\mbox{SEN}}.$

| R <sub>SENSE</sub> |         |

|--------------------|---------|

|                    | (EQ. 5) |

| SEN L' RISEN       |         |

#### **Current Balance and Current Monitoring**

The sensed currents  $I_A$  and  $I_B$  from each respective channel are summed together and divided by 2. The resulting average current  $I_{AVG}$  provides a measure of the total load current. Channel current balance is achieved by comparing the sensed current of each channel to the average current to make an appropriate adjustment to the PWMA and PWMB duty cycle with Intersil's patented current-balance method.

Channel current balance is essential in achieving the thermal advantage of multiphase operation. With good

current balance, the power loss is equally dissipated over multiple devices and a greater area.

The resulting average current  $I_{AVG}$  also goes out from the IOUT pin for current monitoring and can also be fed back to the controller's ISEN lines for current balance, load-line regulation, and overcurrent protection. For fast response to the current information, the IOUT pin should have minimum decoupling; no more than 50ns filter is recommended. The full scale of IOUT is  $100\mu$ A; it typically should set resistor gain around  $50\mu$ A to  $80\mu$ A at the full load to ensure that it will not hit the full scale prior to the overcurrent trip point. At the same time, the current signal accuracy is maximized.

#### **Benefits of a High Phase Count System**

At heavy load condition, efficiency can be improved by spreading the load across many phases. This is primarily because the resistive loss becomes the dominant component of total loss budget at high current levels.

Since the load is carried by more phases, each power device handles less current. In addition, the devices are likely to be spread over a larger area on the Printed Circuit Board (PCB). Both these factors result in improved heat dissipation for higher phase count systems. By reducing the system's operating temperature, components reliability is improved.

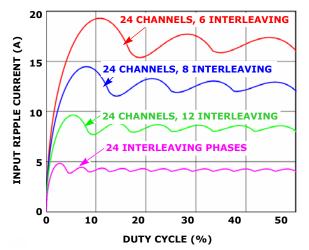

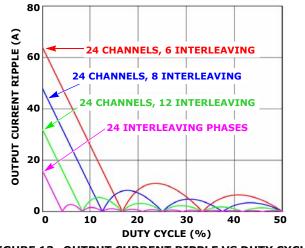

Furthermore, increasing the phase count also reduces the size of ripple on both the input and output currents. It reduces EMI and improves the efficiency. Figures 12 and 13 show the ripple values for a 24-Phase voltage regulator with the following parameters:

- Input voltage: 12V

- Output voltage: 1.6V

- Duty cycle: 13.3%

- Load current: 200A

- Output Phase Inductor: 500nH

- Phase switching frequency: 200kHz

In this example, the 24-phase voltage regulator (VR) can run in 6-phase, 8-phase, 12-phase, 24-phase interleaving mode. In 6-phase interleaving mode, every 4 phases runs synchronously, which yields 18.73A and 12.93A input and output ripple currents, respectively. The 24-phase interleaving regulator significantly drops these values to 4.05A and 0.78A, respectively. As shown in Table 3, both input and output ripple currents are reduced when more phases are running in interleaving mode. Note that the 8-phase VR has lower output ripple current than the 12-phase VR since the 8-phase VR has better output ripple cancellation factor close to the duty cycle of 1/8.

|  | TABLE 3. | RIPPLE | CURRENT | (UNIT: | A) |

|--|----------|--------|---------|--------|----|

|--|----------|--------|---------|--------|----|

| INTERLEAVED PHASES    | 6     | 8     | 12   | 24   |

|-----------------------|-------|-------|------|------|

| Input Ripple Current  | 18.73 | 11.64 | 8.79 | 4.05 |

| Output Ripple Current | 12.93 | 2.70  | 4.83 | 0.78 |

#### ISL6617

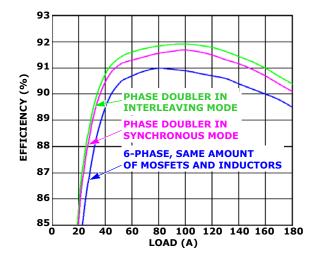

Figure 14 shows the efficiency of a 12-phase VR design, which runs the doubler in interleaving and synchronous modes. For comparison, a 6-phase VR with the same number of MOSFETs and inductors is also plotted, clearly demonstrating the efficiency improvement of a high-phase count system and interleaving mode over synchronous mode resulting from the better ripple cancellation.

FIGURE 12. INPUT CURRENT RIPPLE VS DUTY CYCLE, PHASE COUNT

FIGURE 13. OUTPUT CURRENT RIPPLE VS DUTY CYCLE, PHASE COUNT

FIGURE 14. EFFICIENCY COMPARISON IN 12-PHASE DESIGN

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

|   | DATE   | REVISION | CHANGE           |

|---|--------|----------|------------------|

|   | 2/4/10 | FN7564.0 | Initial release. |

| L |        |          | 4                |

## Products

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <u>ISL6617</u>

To report errors or suggestions for this datasheet, please go to: www.intersil.com/askourstaff

FITs are available from our website at: http://rel.intersil.com/reports/sear

© Copyright Intersil Americas LLC 2010. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7564 Rev 0.00 February 4, 2010

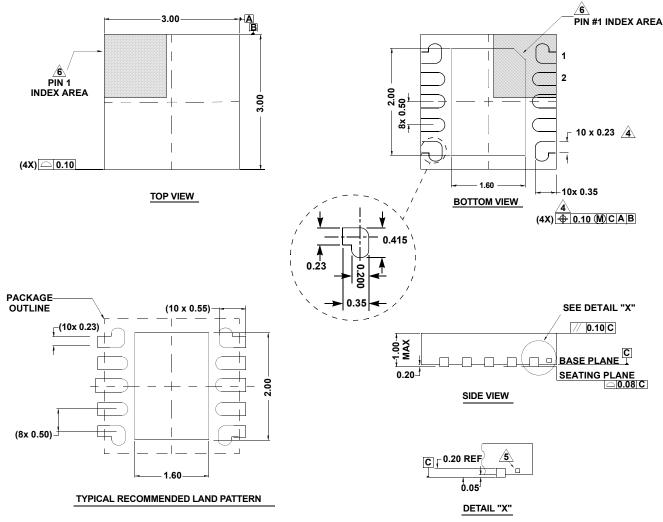

## Package Outline Drawing

L10.3x3

10 LEAD DUAL FLAT PACKAGE (DFN) Rev 6, 09/09

NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Lead width applies to the metallized terminal and is measured between 0.18mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

#### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9