# Features

- 8-bit Microcontroller Compatible with MCS<sup>®</sup>51 Products

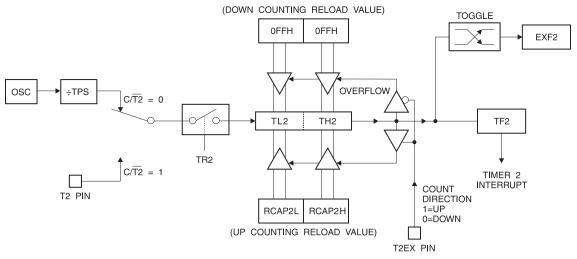

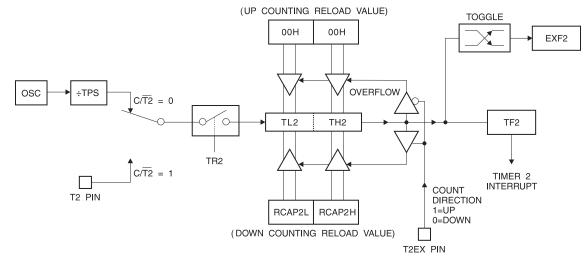

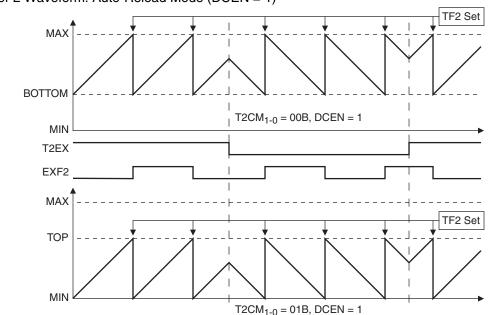

- Enhanced 8051 Architecture

- Single-clock Cycle per Byte Fetch

- Up to 20 MIPS Throughput at 20 MHz Clock Frequency

- Fully Static Operation: 0 Hz to 20 MHz

- On-chip 2-cycle Hardware Multiplier

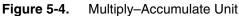

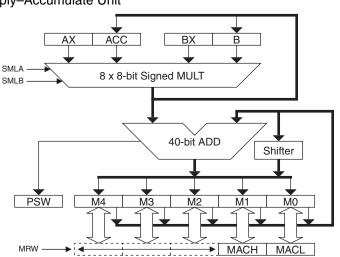

- 16x16 Multiply–Accumulate Unit

- 256x8 Internal RAM

- 4096x8 Internal Extra RAM

- Up to 4KB Extended Stack in Extra RAM

- Dual Data Pointers

- 4-level Interrupt Priority

- Nonvolatile Program and Data Memory

- 32K/64K Bytes of In-System Programmable (ISP) Flash Program Memory

- 8K Bytes of Flash Data Memory

- Endurance: Minimum 100,000 Write/Erase Cycles

- Serial Interface for Program Downloading

- 64-byte Fast Page Programming Mode

- 256-Byte User Signature Array

- 2-level Program Memory Lock for Software Security

- In-Application Programming of Program Memory

- Peripheral Features

- Three 16-bit Enhanced Timer/Counters

- Two 8-bit PWM Outputs

- 4-Channel 16-bit Compare/Capture/PWM Array

- Enhanced UART with Automatic Address Recognition and Framing Error Detection

- Enhanced Master/Slave SPI with Double-buffered Send/Receive

- Master/Slave Two-Wire Serial Interface

- Programmable Watchdog Timer with Software Reset

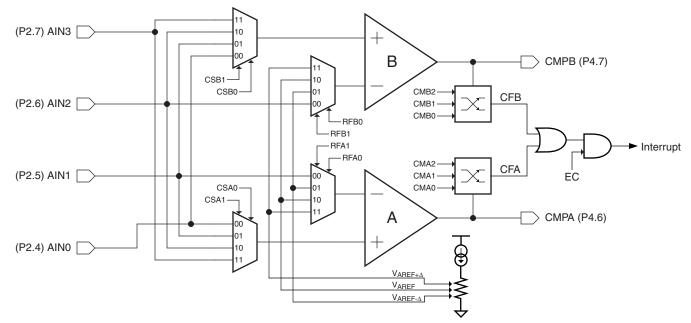

- Dual Analog Comparators with Selectable Interrupts and Debouncing

- 8-channel 10-bit ADC/DAC

- 8 General-purpose Interrupt Pins

- Special Microcontroller Features

- Two-wire On-chip Debug Interface

- Brown-out Detection and Power-on Reset with Power-off Flag

- Active-low External Reset Pin

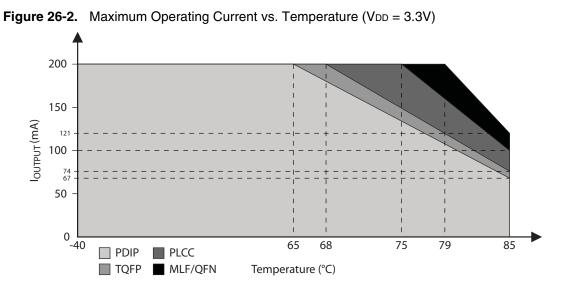

- Internal RC Oscillator

- Low Power Idle and Power-down Modes

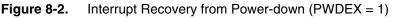

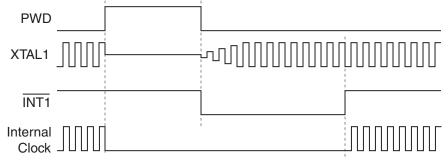

- Interrupt Recovery from Power-down Mode

- I/O and Packages

- Up to 38 Programmable I/O Lines

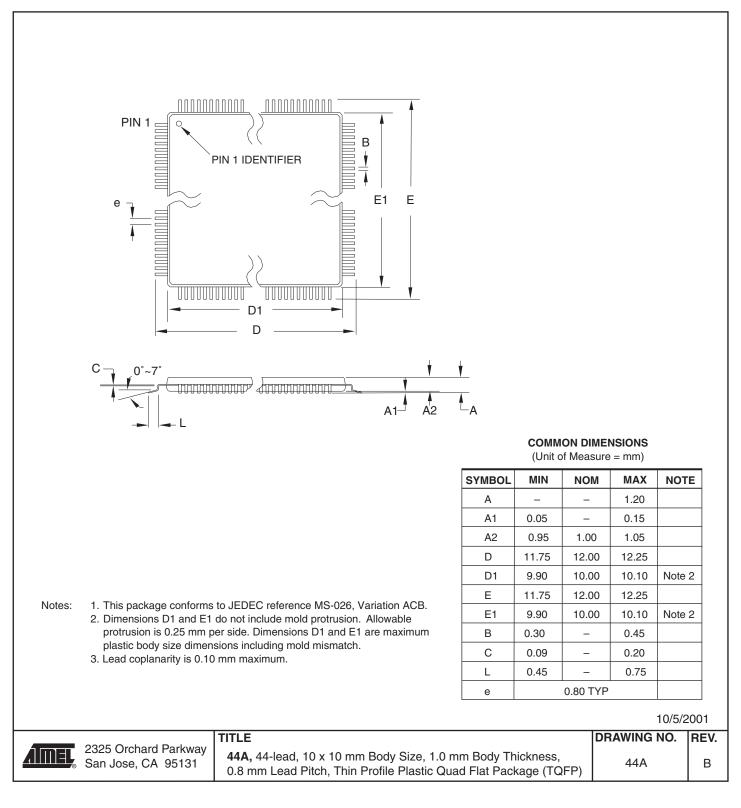

- 40-lead PDIP or 44-lead TQFP/PLCC or 44-pad VQFN/MLF

- Configurable I/O Modes

- Quasi-bidirectional (80C51 Style)

- Input-Only (Tristate)

- Push-pull CMOS Output

- Open-drain

- Operating Conditions

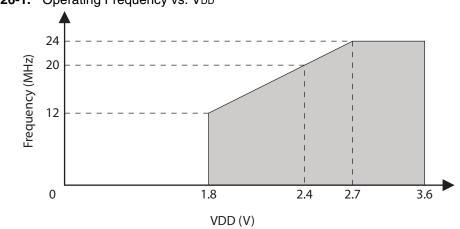

- 2.4V to 3.6V V<sub>DD</sub> Voltage Range

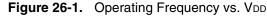

- -40° C to 85°C Temperature Range

- 0 to 20 MHz @ 2.4-3.6V

8-bit Microcontroller with 32K/64K Bytes In-System Programmable Flash

AT89LP3240 AT89LP6440

3706C-MICRO-2/11

# 1. Pin Configurations

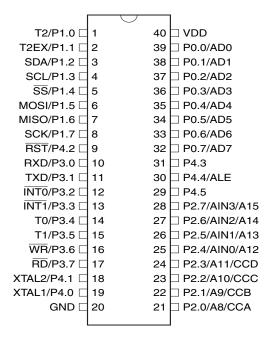

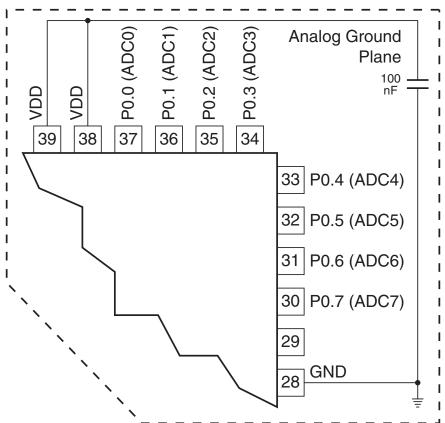

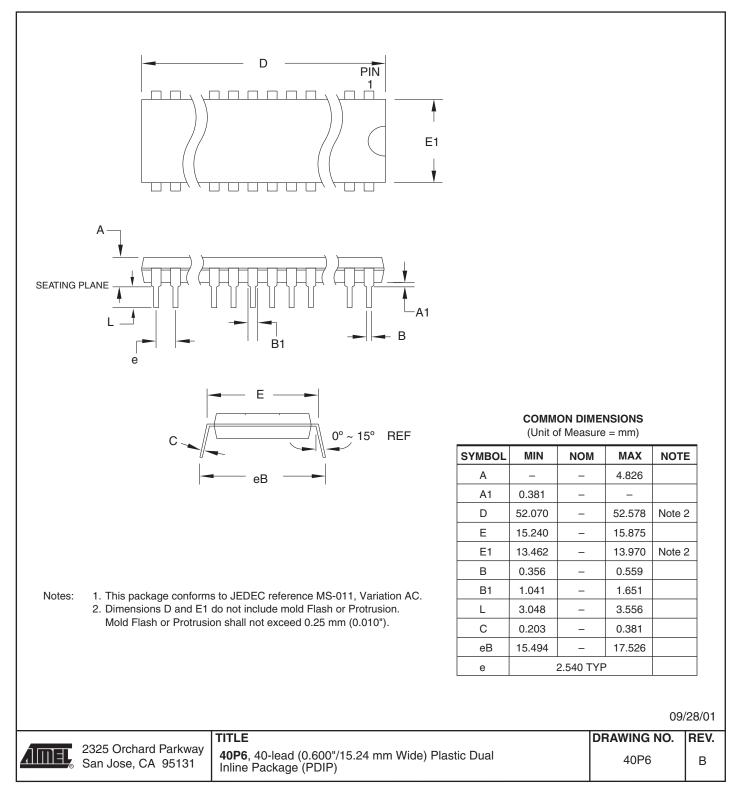

# 1.1 40P6: 40-lead PDIP

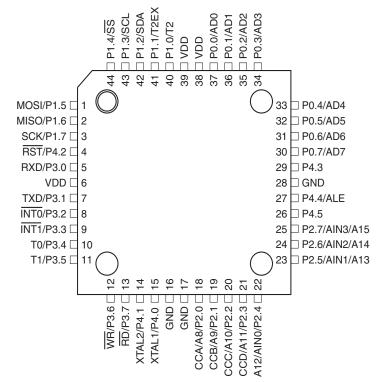

# 1.2 44A: 44-lead TQFP (Top View)

# AT89LP3240/6440

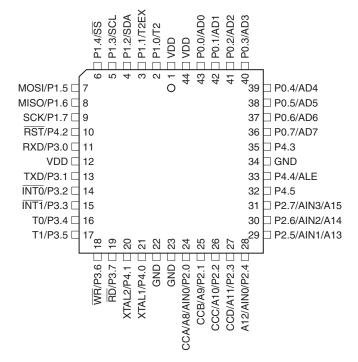

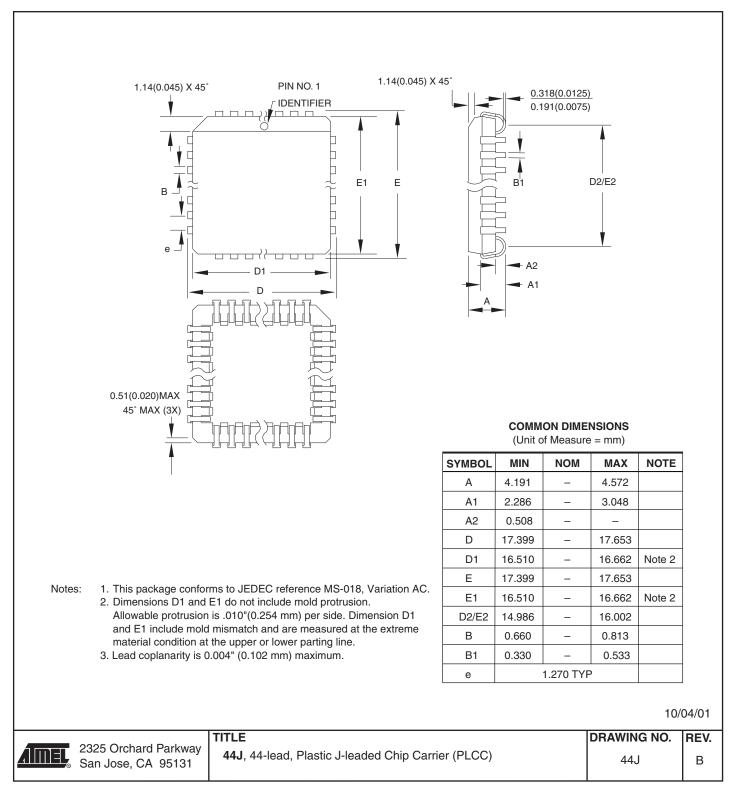

## 1.3 44J: 44-lead PLCC

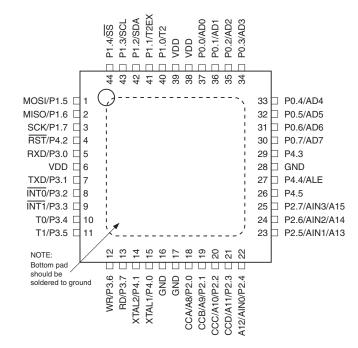

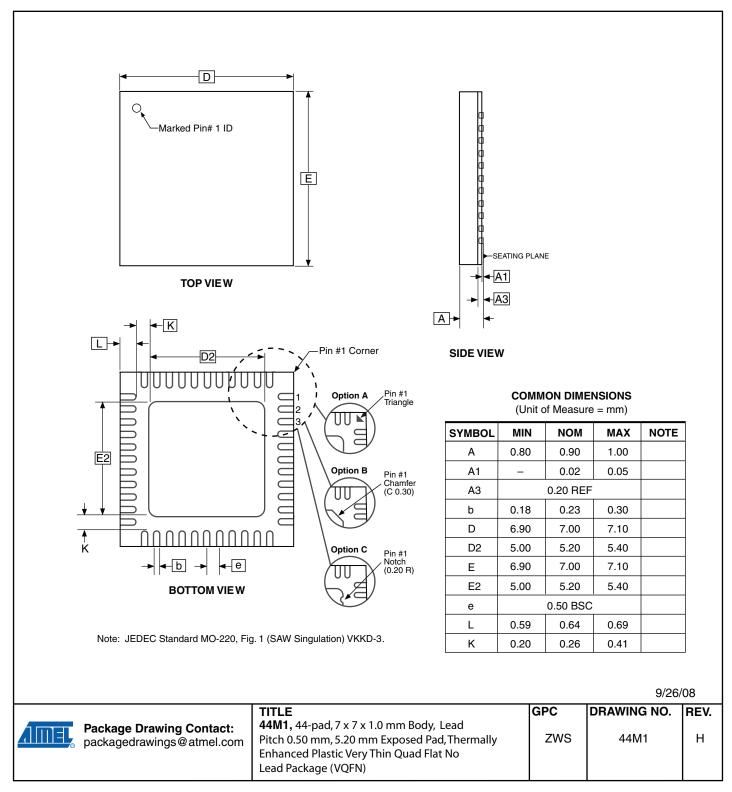

# 1.4 44M1: 44-pad VQFN/MLF

# 1.5 Pin Description

| Table 1-1.AT89LP3240/6440 Pin Description |

|-------------------------------------------|

|-------------------------------------------|

|      | Pin Number |      |      |        |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------|------------|------|------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFP | PLCC       | PDIP | VQFN | Symbol | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1    | 7          | 6    | 1    | P1.5   | I/O<br>I/O<br>I | <ul> <li>P1.5: User-configurable I/O Port 1 bit 5.</li> <li>MOSI: SPI master-out/slave-in. When configured as master, this pin is an output.</li> <li>When configured as slave, this pin is an input.</li> <li>GPI5: General-purpose Interrupt input 5.</li> </ul>                                                                                                                                                                                                                                            |  |  |  |

| 2    | 8          | 7    | 2    | P1.6   | I/O<br>I/O<br>I | <ul> <li>P1.6: User-configurable I/O Port 1 bit 6.</li> <li>MISO: SPI master-in/slave-out. When configured as master, this pin is an input. Whe configured as slave, this pin is an output.</li> <li>GPI6: General-purpose Interrupt input 6.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |

| 3    | 9          | 8    | 3    | P1.7   | I/O<br>I/O<br>I | <ul> <li>P1.7: User-configurable I/O Port 1 bit 7.</li> <li>SCK: SPI Clock. When configured as master, this pin is an output. When configure as slave, this pin is an input.</li> <li>GPI7: General-purpose Interrupt input 7.</li> </ul>                                                                                                                                                                                                                                                                     |  |  |  |

| 4    | 10         | 9    | 4    | P4.2   | I/O<br>I<br>I   | <ul> <li>P4.2: User-configurable I/O Port 4 bit 2 (if Reset Fuse is disabled).</li> <li>RST: External Active-Low Reset input (if Reset Fuse is enabled. See "External Reset" on page 35.).</li> <li>DCL: Serial Clock input for On-Chip Debug Interface when OCD is enabled.</li> </ul>                                                                                                                                                                                                                       |  |  |  |

| 5    | 11         | 10   | 5    | P3.0   | I/O<br>I        | P3.0: User-configurable I/O Port 3 bit 0.<br>RXD: Serial Port Receiver Input.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 6    | 12         |      | 6    | VDD    | I               | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 7    | 13         | 11   | 7    | P3.1   | I/O<br>O        | <b>P3.1</b> : User-configurable I/O Port 3 bit 1.<br><b>TXD</b> : Serial Port Transmitter Output.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 8    | 14         | 12   | 8    | P3.2   | I/O<br>I        | <b>P3.2</b> : User-configurable I/O Port 3 bit 2.<br>INT0: External Interrupt 0 Input or Timer 0 Gate Input.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 9    | 15         | 13   | 9    | P3.3   | I/O<br>I        | <b>P3.3</b> : User-configurable I/O Port 3 bit 3.<br><b>INT1</b> : External Interrupt 1 Input or Timer 1 Gate Input                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 10   | 16         | 14   | 10   | P3.4   | I/O<br>I/O      | P3.4: User-configurable I/O Port 3 bit 4.<br>T1: Timer/Counter 0 External input or PWM output.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 11   | 17         | 15   | 11   | P3.5   | I/O<br>I/O      | P3.5: User-configurable I/O Port 3 bit 5.<br>T1: Timer/Counter 1 External input or PWM output.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 12   | 18         | 16   | 12   | P3.6   | I/O<br>O        | <b>P3.6</b> : User-configurable I/O Port 3 bit 6.<br><b>WR</b> : External memory interface Write Strobe (active-low).                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 13   | 19         | 17   | 13   | P3.7   | I/O<br>O        | <b>P3.7</b> : User-configurable I/O Port 3 bit 7.<br><b>RD</b> : External memory interface Read Strobe (active-low).                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

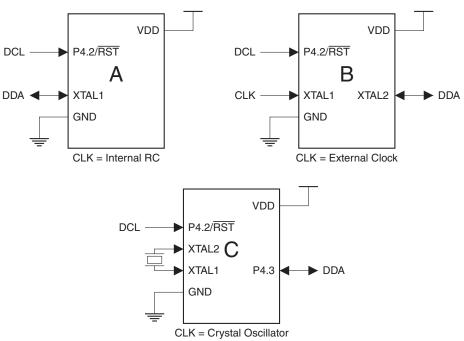

| 14   | 20         | 18   | 14   | P4.1   | I/O<br>O<br>I/O | <ul> <li>P4.1: User-configurable I/O Port 4 bit 1.</li> <li>XTAL2: Output from inverting oscillator amplifier. It may be used as a port pin if the internal RC oscillator is selected as the clock source.</li> <li>CLKOUT: When the internal RC oscillator is selected as the clock source, may be used to output the internal clock divided by 2.</li> <li>DDA: Serial Data input/output for On-Chip Debug Interface when OCD is enabled and the external clock is selected as the clock source.</li> </ul> |  |  |  |

| 15   | 21         | 19   | 15   | P4.0   | I/O<br>I<br>I/O | <ul> <li>P4.0: User-configurable I/O Port 4 bit 0.</li> <li>XTAL1: Input to the inverting oscillator amplifier and internal clock generation circuits. It may be used as a port pin if the internal RC oscillator is selected as the clock source.</li> <li>DDA: Serial Data input/output for On-Chip Debug Interface when OCD is enabled and the internal RC oscillator is selected as the clock source.</li> </ul>                                                                                          |  |  |  |

| 16   | 22         | N/A  | 16   | GND    | I               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

#### Table 1-1.AT89LP3240/6440 Pin Description

|      | Pin N | umber |      |        |                      |                                                                                                                                                                                                                                        |  |  |  |

|------|-------|-------|------|--------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFP | PLCC  | PDIP  | VQFN | Symbol | Туре                 | Description                                                                                                                                                                                                                            |  |  |  |

| 17   | 23    | 20    | 17   | GND    | I                    | Ground                                                                                                                                                                                                                                 |  |  |  |

| 18   | 24    | 21    | 18   | P2.0   | I/O<br>I/O<br>O      | <ul> <li>P2.0: User-configurable I/O Port 2 bit 0.</li> <li>CCA: Timer 2 Channel A Compare Output or Capture Input.</li> <li>A8: External memory interface Address bit 8.</li> </ul>                                                   |  |  |  |

| 19   | 25    | 22    | 19   | P2.1   | I/O<br>I/O<br>O      | <ul> <li>P2.1: User-configurable I/O Port 2 bit 1.</li> <li>CCB: Timer 2 Channel B Compare Output or Capture Input.</li> <li>A9: External memory interface Address bit 9.</li> </ul>                                                   |  |  |  |

| 20   | 26    | 23    | 20   | P2.1   | I/O<br>I/O<br>O<br>O | <ul> <li>P2.2: User-configurable I/O Port 2 bit 2.</li> <li>CCC: Timer 2 Channel C Compare Output or Capture Input.</li> <li>A10: External memory interface Address bit 10.</li> <li>DA-: DAC negative differential output.</li> </ul> |  |  |  |

| 21   | 27    | 24    | 21   | P2.3   | I/O<br>I/O<br>O<br>O | <ul> <li>P2.3: User-configurable I/O Port 2 bit 3.</li> <li>CCD: Timer 2 Channel D Compare Output or Capture Input.</li> <li>A11: External memory interface Address bit 11.</li> <li>D+-: DAC positive differential output.</li> </ul> |  |  |  |

| 22   | 28    | 25    | 22   | P2.4   | I/O<br>I<br>O        | <ul><li>P2.4: User-configurable I/O Port 2 bit 5.</li><li>AIN0: Analog Comparator Input 0.</li><li>A12: External memory interface Address bit 12.</li></ul>                                                                            |  |  |  |

| 23   | 29    | 26    | 23   | P2.5   | I/O<br>I<br>O        | <ul> <li>P2.5: User-configurable I/O Port 2 bit 5.</li> <li>AIN1: Analog Comparator Input 1.</li> <li>A13: External memory interface Address bit 13.</li> </ul>                                                                        |  |  |  |

| 24   | 30    | 27    | 24   | P2.6   | I/O<br>I<br>O        | <ul><li>P2.6: User-configurable I/O Port 2 bit 6.</li><li>AIN2: Analog Comparator Input 2.</li><li>A14: External memory interface Address bit 14.</li></ul>                                                                            |  |  |  |

| 25   | 31    | 28    | 25   | P2.7   | I/O<br>I<br>O        | <ul><li>P2.7: User-configurable I/O Port 2 bit 7.</li><li>AIN3: Analog Comparator Input 3.</li><li>A15: External memory interface Address bit 15.</li></ul>                                                                            |  |  |  |

| 26   | 32    | 29    | 26   | P4.5   | I/O                  | P4.5: User-configurable I/O Port 4 bit 5.                                                                                                                                                                                              |  |  |  |

| 27   | 33    | 30    | 27   | P4.4   | I/O<br>O             | <b>P4.4</b> : User-configurable I/O Port 4 bit 4.<br><b>ALE</b> : External memory interface Address Latch Enable.                                                                                                                      |  |  |  |

| 28   | 34    |       | 28   | GND    | I                    | Ground                                                                                                                                                                                                                                 |  |  |  |

| 29   | 35    | 31    | 29   | P4.3   | I/O<br>I/O           | <b>P4.3</b> : User-configurable I/O Port 4 bit 3.<br><b>DDA</b> : Serial Data input/output for On-Chip Debug Interface when OCD is enabled and the Crystal oscillator is selected as the clock source.                                 |  |  |  |

| 30   | 36    | 32    | 30   | P0.7   | I/O<br>O<br>I        | <b>P0.7</b> : User-configurable I/O Port 0 bit 7.<br><b>AD7</b> : External memory interface Address/Data bit 7.<br><b>ADC7</b> : ADC analog input 7.                                                                                   |  |  |  |

| 31   | 37    | 33    | 31   | P0.6   | I/O<br>O<br>I        | P0.6: User-configurable I/O Port 0 bit 6.<br>AD6: External memory interface Address/Data bit 6.<br>ADC6: ADC analog input 6.                                                                                                           |  |  |  |

| 32   | 38    | 34    | 32   | P0.5   | I/O<br>O<br>I        | <b>P0.5</b> : User-configurable I/O Port 0 bit 5.<br><b>AD5</b> : External memory interface Address/Data bit 5.<br><b>ADC5</b> : ADC analog input 5.                                                                                   |  |  |  |

| 33   | 39    | 35    | 33   | P0.4   | I/O<br>O<br>I        | <ul> <li>P0.4: User-configurable I/O Port 0 bit 4.</li> <li>AD4: External memory interface Address/Data bit 4.</li> <li>ADC4: ADC analog input 4.</li> </ul>                                                                           |  |  |  |

| 34   | 40    | 36    | 34   | P0.3   | I/O<br>O<br>I        | <b>P0.3</b> : User-configurable I/O Port 0 bit 3.<br><b>AD3</b> : External memory interface Address/Data bit 3.<br><b>ADC3</b> : ADC analog input 3.                                                                                   |  |  |  |

|      | Pin N | umber |      |        |                 |                                                                                                                                                                      |  |  |  |

|------|-------|-------|------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFP | PLCC  | PDIP  | VQFN | Symbol | Туре            | Description                                                                                                                                                          |  |  |  |

| 35   | 41    | 37    | 35   | P0.2   | I/O<br>O<br>I   | <ul> <li>P0.2: User-configurable I/O Port 0 bit 2.</li> <li>AD2: External memory interface Address/Data bit 2.</li> <li>ADC2: ADC analog input 2.</li> </ul>         |  |  |  |

| 36   | 42    | 38    | 36   | P0.1   | I/O<br>O<br>I   | <b>P0.1</b> : User-configurable I/O Port 0 bit 1.<br><b>AD1</b> : External memory interface Address/Data bit 1.<br><b>ADC1</b> : ADC analog input 1.                 |  |  |  |

| 37   | 43    | 39    | 37   | P0.0   | I/O<br>O<br>I   | <ul> <li>P0.0: User-configurable I/O Port 0 bit 0.</li> <li>AD0: External memory interface Address/Data bit 0.</li> <li>ADC0: ADC analog input 0.</li> </ul>         |  |  |  |

| 38   | 44    | 40    | 38   | VDD    | Ι               | Supply Voltage                                                                                                                                                       |  |  |  |

| 39   | 1     |       | 39   | VDD    | Ι               | Supply Voltage                                                                                                                                                       |  |  |  |

| 40   | 2     | 1     | 40   | P1.0   | I/O<br>I/O<br>I | <ul> <li>P1.0: User-configurable I/O Port 1 bit 0.</li> <li>T2: Timer 2 External Input or Clock Output.</li> <li>GPI0: General-purpose Interrupt input 0.</li> </ul> |  |  |  |

| 41   | 3     | 2     | 41   | P1.1   | I/O<br>I<br>I   | P1.1: User-configurable I/O Port 1 bit 1.<br>T2EX: Timer 2 External Capture/Reload Input.<br>GPI1: General-purpose Interrupt input 1                                 |  |  |  |

| 42   | 4     | 3     | 42   | P1.2   | I/O<br>I        | P1.2: User-configurable I/O Port 1 bit 2.<br>GPI2: General-purpose Interrupt input 2.                                                                                |  |  |  |

| 43   | 5     | 4     | 43   | P1.3   | I/O<br>I        | P1.3: User-configurable I/O Port 1 bit 3.<br>GPI3: General-purpose Interrupt input 3.                                                                                |  |  |  |

| 44   | 6     | 5     | 44   | P1.4   | I/O<br>I<br>I   | P1.4: User-configurable I/O Port 1 bit 4.<br>SS: SPI Slave-Select.<br>GPI6: General-purpose Interrupt input 4.                                                       |  |  |  |

Table 1-1. AT89LP3240/6440 Pin Description

# 2. Overview

The AT89LP3240/6440 is a low-power, high-performance CMOS 8-bit microcontroller with 32K/64K bytes of In-System Programmable Flash program memory and 8K bytes of Flash data memory. The device is manufactured using Atmel<sup>®</sup>'s high-density nonvolatile memory technology and is compatible with the industry-standard 8051 instruction set. The AT89LP3240/6440 is built around an enhanced CPU core that can fetch a single byte from memory every clock cycle. In the classic 8051 architecture, each fetch requires 6 clock cycles, forcing instructions need only 1 to 4 clock cycles providing 6 to 12 times more throughput than the standard 8051. Seventy percent of instructions need only as many clock cycles as they have bytes to execute, and most of the remaining instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current consumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a much lower speed and thereby greatly reducing power consumption and EMI.

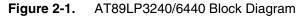

The AT89LP3240/6440 provides the following standard features: 32K/64K bytes of In-System Programmable Flash program memory, 8K bytes of Flash data memory, 4352 bytes of RAM, up to 38 I/O lines, three 16-bit timer/counters, up to six PWM outputs, a programmable watchdog timer, two analog comparators, a 10-bit ADC/DAC with 8 input channels, a full-duplex serial port, a serial peripheral interface, a two-wire serial interface, an internal RC oscillator, on-chip crystal oscillator, and a four-level, twelve-vector interrupt system. A block diagram is shown in Figure 2-1.

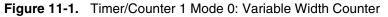

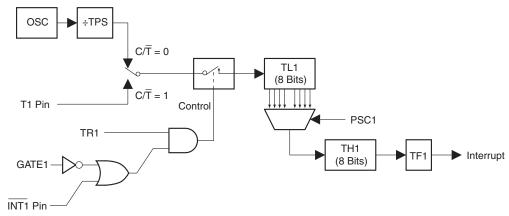

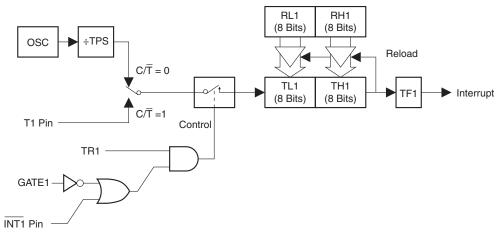

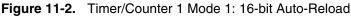

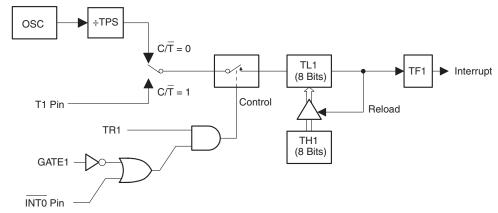

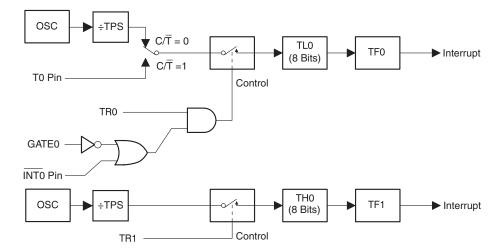

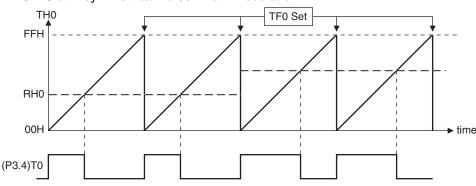

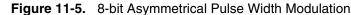

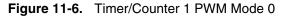

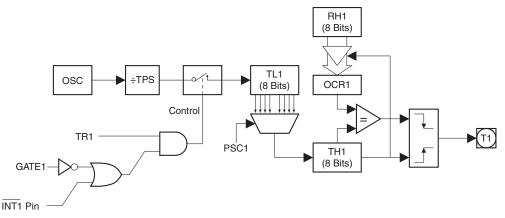

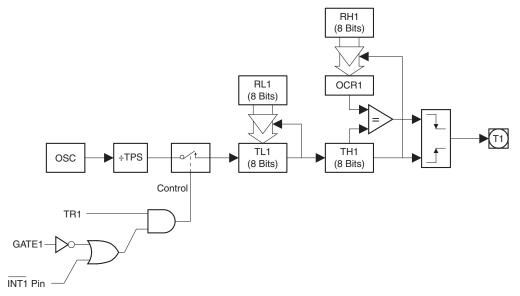

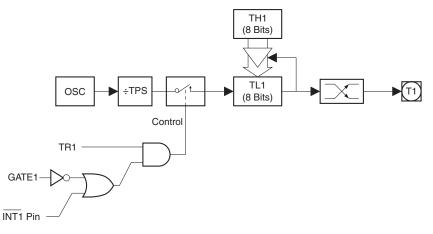

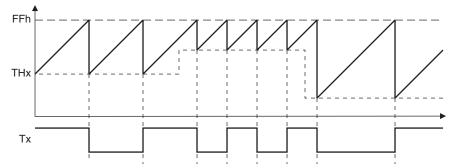

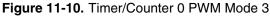

Timer 0 and Timer 1 in the AT89LP3240/6440 are enhanced with two new modes. Mode 0 can be configured as a variable 9- to 16-bit timer/counter and Mode 1 can be configured as a 16-bit auto-reload timer/counter. In addition, the timer/counters may each independently drive an 8-bit precision pulse width modulation output.

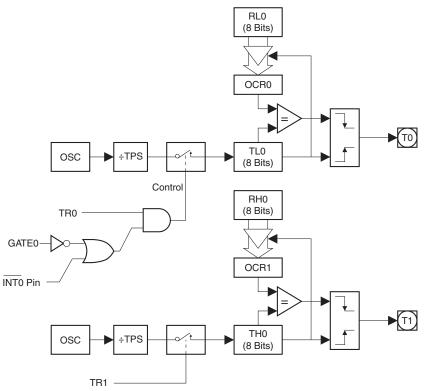

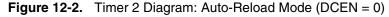

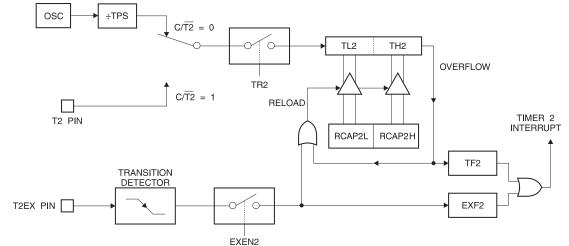

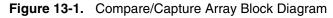

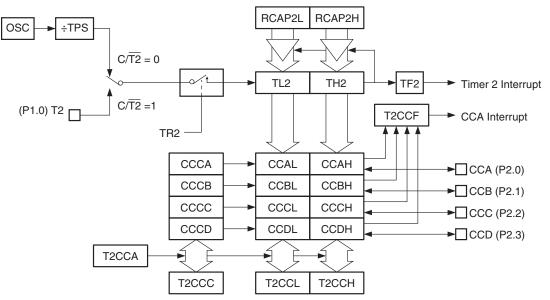

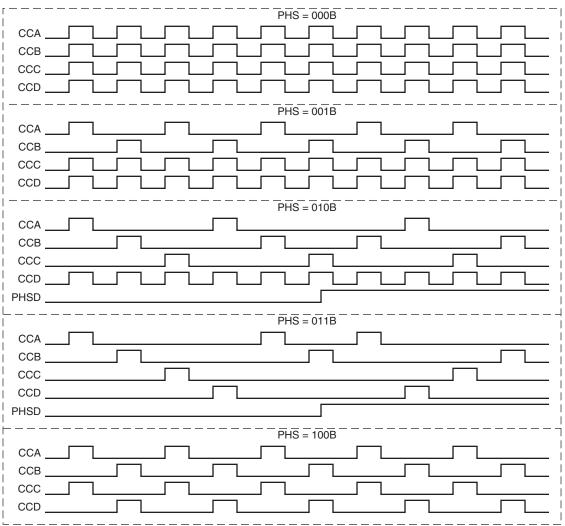

Timer 2 on the AT89LP3240/6440 serves as a 16-bit time base for a 4-channel Compare/Capture Array with up to four multi-phasic, variable precision (up to 16-bit) PWM outputs.

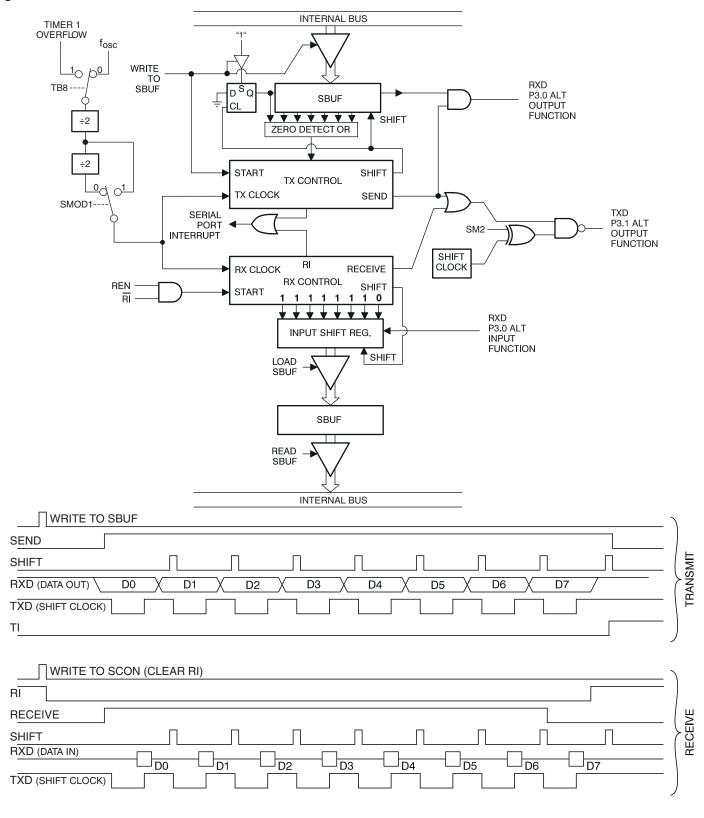

The enhanced UART of the AT89LP3240/6440 includes Framing Error Detection and Automatic Address Recognition. In addition, enhancements to Mode 0 allow hardware accelerated emulation of half-duplex SPI or Two Wire interfaces.

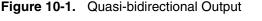

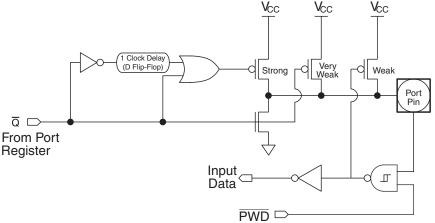

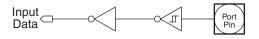

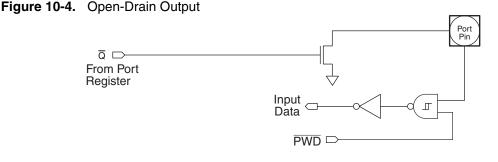

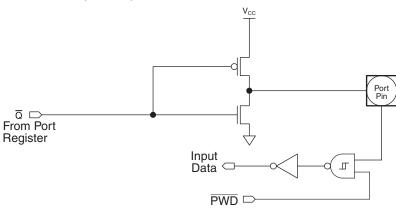

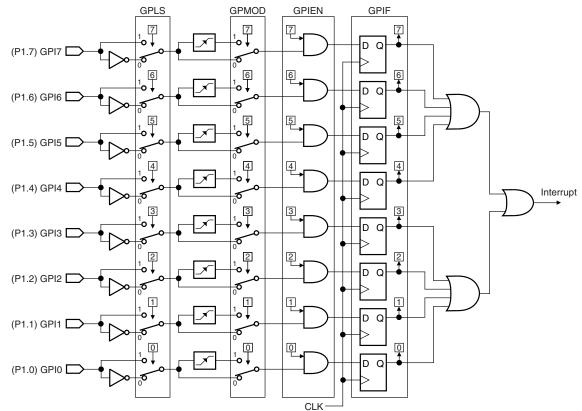

The I/O ports of the AT89LP3240/6440 can be independently configured in one of four operating modes. In quasi-bidirectional mode, the ports operate as in the classic 8051. In input-only mode, the ports are tristated. Push-pull output mode provides full CMOS drivers and open-drain mode provides just a pull-down. In addition, all 8 pins of Port 1 can be configured to generate an interrupt using the general-purpose interrupt interface.

# 2.1 Block Diagram

# 2.2 System Configuration

The AT89LP3240/6440 supports several system configuration options. Nonvolatile options are set through user fuses that must be programmed through the flash programming interface. Volatile options are controlled by software through individual bits of special function registers (SFRs). The AT89LP3240/6440 must be properly configured before correct operation can occur.

#### 2.2.1 Fuse Options

Table 2-1 lists the fusable options for the AT89LP3240/6440. These options maintain their state even when the device is powered off, but can only be changed with an external device programmer. For more information, see Section 25.7 "User Configuration Fuses" on page 164.

| Fuse Name                         | Description                                                                                                                                                   |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Clock Source                      | Selects between the High Speed Crystal Oscillator, Low Speed Crystal Oscillator, External Clock or Internal RC Oscillator for the source of the system clock. |  |  |  |  |

| Start-up Time                     | Selects time-out delay for the POR/BOD/PWD wake-up period.                                                                                                    |  |  |  |  |

| Reset Pin Enable                  | Configures the $\overline{\text{RST}}$ pin as a reset input or general purpose I/O                                                                            |  |  |  |  |

| Brown-Out Detector Enable         | Enables or disables the Brown-out Detector                                                                                                                    |  |  |  |  |

| On-Chip Debug Enable              | Enables or disables On-Chip Debug. OCD must be enabled prior to using an in-circuit debugger with the device.                                                 |  |  |  |  |

| In-System Programming Enable      | Enables or disables In-System Programming.                                                                                                                    |  |  |  |  |

| User Signature Programming Enable | Enables or disables programming of User Signature array.                                                                                                      |  |  |  |  |

| Default Port State                | Configures the default port state as input-only mode (tristated) or quasi-bidirectional mode (weakly pulled high).                                            |  |  |  |  |

| In-Application Programming Enable | Enables or disabled In-Application (self) Programming                                                                                                         |  |  |  |  |

| Table 2-1. | User Configuration Fuses |

|------------|--------------------------|

|------------|--------------------------|

#### 2.2.2 Software Options

Table 2-2 lists some important software configuration bits that affect operation at the system

level. These can be changed by the application software but are set to their default values upon

any reset. Most peripherals also have multipe configuration bits that are not listed here.

Table 2-2.

Important Software Configuration Bits

| Bit(s)             | SFR Location                                                     | Description                                                                                                                                                                                |  |  |  |  |  |

|--------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PxM0.y<br>PxM1.y   | P0M0, P0M1, P1M0, P1M1,<br>P2M0, P2M1, P3M0, P3M1,<br>P4M0, P4M1 | Configures the I/O mode of Port x Pin y to be one of input-only, quasi bidirectional, push-pull output or open-drain. The default state is controlled by the Default Port State fuse above |  |  |  |  |  |

| CDV <sub>2-0</sub> | CLKREG.3-1                                                       | Selects the division ratio between the oscillator and the system clock                                                                                                                     |  |  |  |  |  |

| TPS <sub>3-0</sub> | CLKREG.7-4                                                       | Selects the division ratio between the system clock and the timers                                                                                                                         |  |  |  |  |  |

| ALES               | AUXR.0                                                           | Enables/disables toggling of ALE                                                                                                                                                           |  |  |  |  |  |

| EXRAM              | AUXR.1                                                           | Enables/disables access to on-chip memories that are mapped to the external data memory address space                                                                                      |  |  |  |  |  |

| WS <sub>1-0</sub>  | AUXR.3-2                                                         | Selects the number of wait states when accessing external data memory                                                                                                                      |  |  |  |  |  |

| XSTK               | AUXR.4                                                           | Congifures the hardware stack to be in RAM or extra RAM                                                                                                                                    |  |  |  |  |  |

| DMEN               | MEMCON.3                                                         | Enables/disables access to the on-chip flash data memory                                                                                                                                   |  |  |  |  |  |

| IAP                | MEMCON.7                                                         | Enbles/disables the self programming feature when the fuse allows                                                                                                                          |  |  |  |  |  |

# 2.3 Comparison to Standard 8051

The AT89LP3240/6440 is part of a family of devices with enhanced features that are fully binary compatible with the 8051 instruction set. In addition, most SFR addresses, bit assignments, and pin alternate functions are identical to Atmel's existing standard 8051 products. However, due to the high performance nature of the device, some system behaviors are different from those of Atmel's standard 8051 products such as AT89S52 or AT89C2051. The major differences from the standard 8051 are outlined in the following paragraphs and may be useful to users migrating to the AT89LP3240/6440 from older devices.

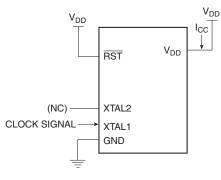

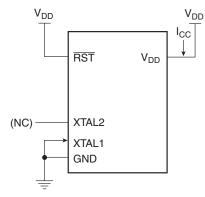

#### 2.3.1 System Clock

The maximum CPU clock frequency equals the externally supplied XTAL1 frequency. The oscillator is not divided by 2 to provide the internal clock and X2 mode is not supported. The System Clock Divider can scale the CPU clock versus the oscillator source (See Section 6.5 on page 32).

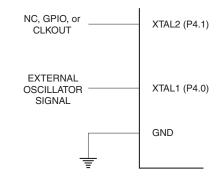

#### 2.3.2 Reset

The  $\overline{\text{RST}}$  pin of the AT89LP3240/6440 is **active-LOW** as compared with the active-high reset in the standard 8051. In addition, the  $\overline{\text{RST}}$  pin is sampled every clock cycle and must be held low for a minimum of two clock cycles, instead of 24 clock cycles, to be recognized as a valid reset.

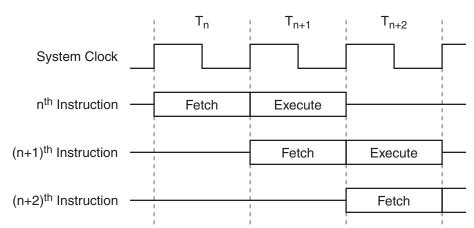

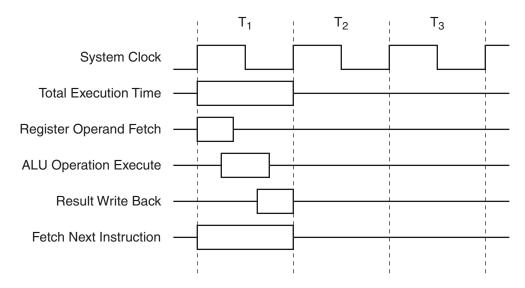

#### 2.3.3 Instruction Execution with Single-cycle Fetch

The CPU fetches one code byte from memory every clock cycle instead of every six clock cycles. This greatly increases the throughput of the CPU. As a consequence, the CPU no longer executes instructions in 12, 24 or 48 clock cycles. Each standard instruction executes in only 1 to 4 clock cycles. See "Instruction Set Summary" on page 143 for more details. Any software delay loops or instruction-based timing operations may need to be retuned to achieve the desired results.

#### 2.3.4 Interrupt Handling

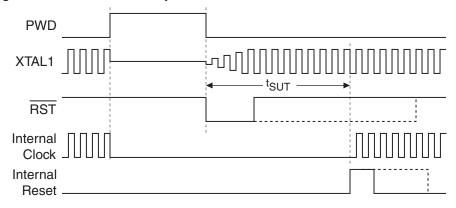

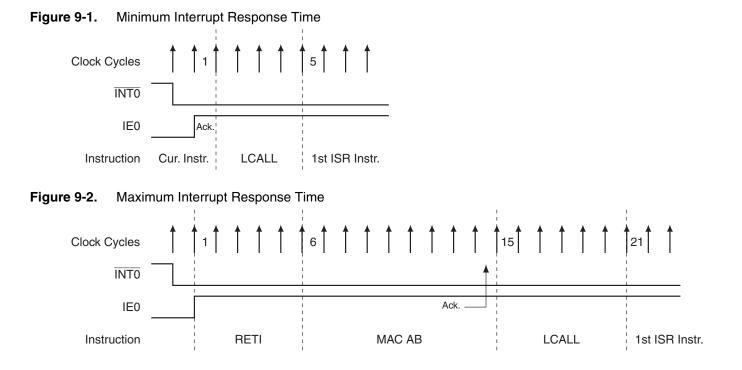

The interrupt controller polls the interrupt flags during the last clock cycle of any instruction. In order for an interrupt to be serviced at the end of an instruction, its flag needs to have been latched as active during the next to last clock cycle of the instruction, or in the last clock cycle of the previous instruction if the current instruction executes in only a single clock cycle.

The external interrupt pins, INTO and INT1, are sampled at every clock cycle instead of once every 12 clock cycles. Coupled with the shorter instruction timing and faster interrupt response, this leads to a higher maximum rate of incidence for the external interrupts.

The Serial Peripheral Interface (SPI) has a dedicated interrupt vector. The SPI no longer shares its interrupt with the Serial Port and the ESPI (IE2.2) bit replaces SPIE (SPCR.7).

### 2.3.5 Timer/Counters

By default Timer0, Timer 1 and Timer 2 are incremented at a rate of once per clock cycle. This compares to once every 12 clocks in the standard 8051. A common prescaler is available to divide the time base for all timers and reduce the increment rate. The TPS<sub>3-0</sub> bits in the CLKREG SFR control the prescaler (Table 6-2 on page 33). Setting TPS<sub>3-0</sub> = 1011B will cause the timers to count once every 12 clocks.

The external Timer/Counter pins, T0, T1, T2 and T2EX, are sampled at every clock cycle instead of once every 12 clock cycles. This increases the maximum rate at which the Counter modules may function.

There is no difference in counting rate between Timer 2's Auto-Reload/Capture and Baud Rate/Clock Out modes. All modes increment the timer once per clock cycle. Timer 2 in Auto-Reload/Capture mode increments at 12 times the rate of standard 8051s. Setting  $TPS_{3-0} = 1101B$  will force Timer 2 to count every twelve clocks. Timer 2 in Baud Rate or Clock Out mode increments at twice the rate of standard 8051s. Setting  $TPS_{3-0} = 0001B$  will force Timer 2 to count every two clocks.

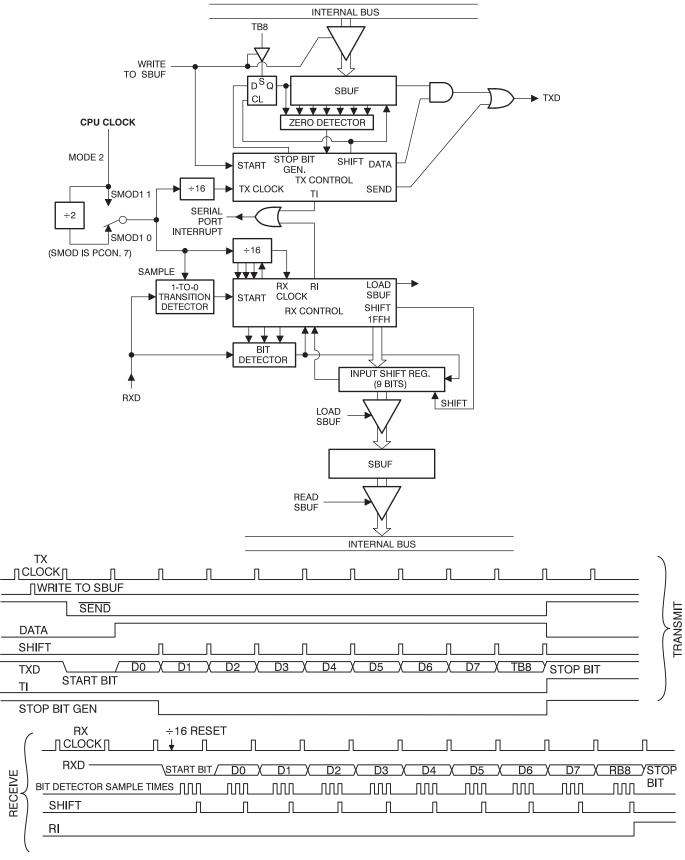

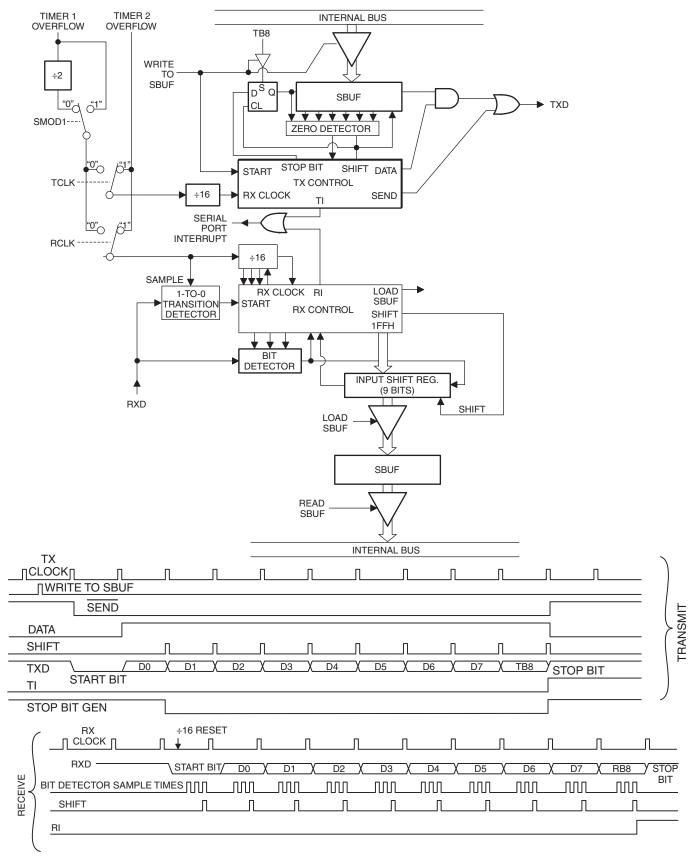

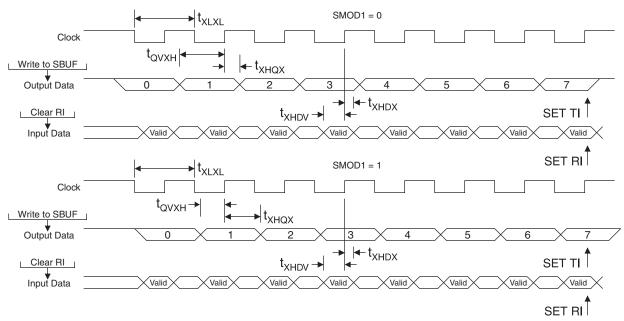

#### 2.3.6 Serial Port

The baud rate of the UART in Mode 0 defaults to 1/4 the clock frequency, compared to 1/12 the clock frequency in the standard 8051. In should also be noted that when using Timer 1 to generate the baud rate in UART Modes 1 or 3, the timer counts at the clock frequency and not at 1/12 the clock frequency. To maintain the same baud rate in the AT89LP3240/6440 while running at the same frequency as a standard 8051, the time-out period must be 12 times longer. Mode 1 of Timer 1 supports 16-bit auto-reload to facilitate longer time-out periods for generating low baud rates.

Timer 2 generated baud rates are twice as fast in the AT89LP3240/6440 than on standard 8051s when operating at the same frequency. The Timer Prescaler can also scale the baud rate to match an existing application.

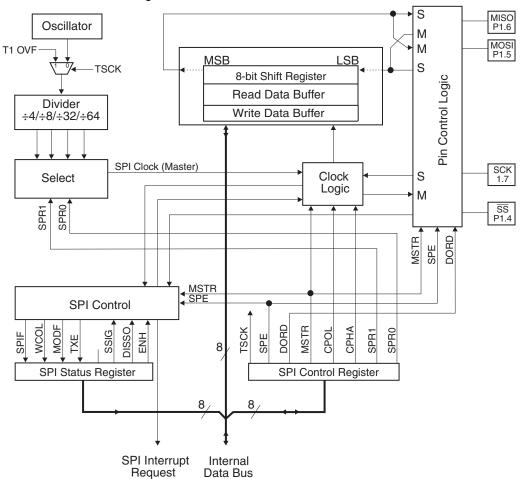

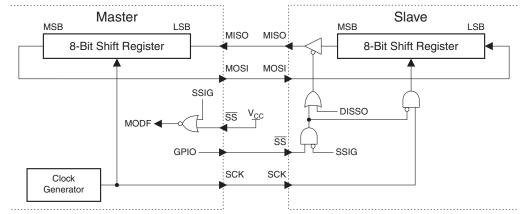

#### 2.3.7 SPI

The Serial Peripheral Interface (SPI) has a dedicated interrupt vector. The ESPI (IE2.2) bit replaces SPIE (SPCR.7). SPCR.7 (TSCK) now enables timer-generated baud rate.

The SPI includes Mode Fault detection. If multiple-master capabilities are not required, SSIG (SPSR.2) must be set to one for master mode to function correctly when  $\overline{SS}$  (P1.4) is a general purpose I/O.

#### 2.3.8 Watchdog Timer

The Watchdog Timer in AT89LP3240/6440 counts at a rate of once per clock cycle. This compares to once every 12 clocks in the standard 8051. A common prescaler is available to divide the time base for all timers and reduce the counting rate.

#### 2.3.9 I/O Ports

The I/O ports of the AT89LP3240/6440 may be configured in four different modes. By default all the I/O ports revert to input-only (tristated) mode at power-up or reset. In the standard 8051, all ports are weakly pulled high during power-up or reset. To enable 8051-like ports, the ports must be put into quasi-bidirectional mode by clearing the P1M0, P2M0, P3M0 and P4M0 SFRs. The user can also configure the ports to start in quasi-bidirectional mode by disabling the Tristate-Port User Fuse. When this fuse is disabled, P1M0, P2M0, P3M0 and P4M0 will reset to 00h instead of FFh and the ports will be weakly pulled high. Port 0 and the upper nibble of Port 2 always power up tristated regardless of the fuse setting due to their analog functions.

#### 2.3.10 External Memory Interface

The AT89LP3240/6440 does not support external program memory. The  $\overrightarrow{PSEN}$  and  $\overrightarrow{EA}$  functions are not supported and those pins are replaced with general purpose I/O. The ALE strobe does not toggle continuously and cannot be used as a board-level clock.

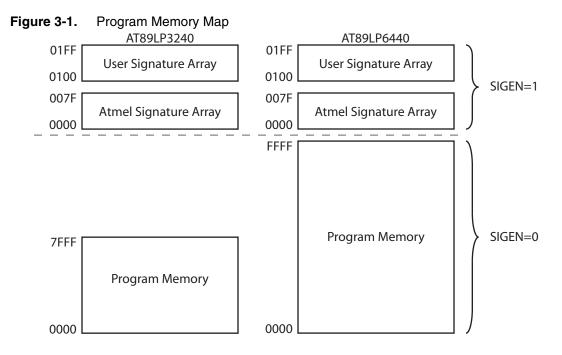

# 3. Memory Organization

The AT89LP3240/6440 uses a Harvard Architecture with separate address spaces for program and data memory. The program memory has a regular linear address space with support for 64K bytes of directly addressable application code. The data memory has 256 bytes of internal RAM and 128 bytes of Special Function Register I/O space. The AT89LP3240/6440 supports external data memory with portions of the external data memory space implemented on chip as Extra RAM and nonvolatile Flash data memory. External program memory is not supported. The memory address spaces of the AT89LP3240/6440 are listed in Table 3-1.

| Name  | Description                                           | Range       |

|-------|-------------------------------------------------------|-------------|

| DATA  | Directly addressable internal RAM                     | 00H–7FH     |

| IDATA | Indirectly addressable internal RAM and stack space   | 00H–FFH     |

| SFR   | Directly addressable I/O register space               | 80H–FFH     |

| EDATA | On-chip Extra RAM and extended stack space            | 0000H-0FFFH |

| FDATA | On-chip nonvolatile Flash data memory                 | 1000H–2FFFH |

| XDATA | External data memory                                  | 3000H-FFFFH |

| CODE  | On-chip nonvolatile Flash program memory (AT89LP3240) | 0000H-7FFFH |

| CODE  | On-chip nonvolatile Flash program memory (AT89LP6440) | 0000H-FFFFH |

| SIG   | On-chip nonvolatile Flash signature array             | 0000H-01FFH |

Table 3-1.

AT89LP3240/6440 Memory Address Spaces

## 3.1 Program Memory

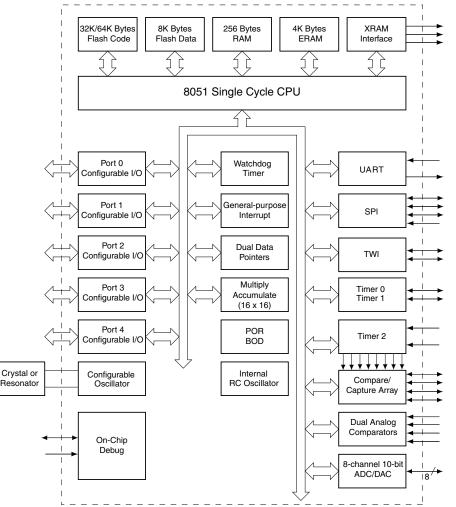

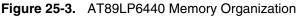

The AT89LP3240/6440 contains 32K/64K bytes of on-chip In-System Programmable Flash memory for program storage. The Flash memory has an endurance of at least 100,000 write/erase cycles and a minimum data retention time of 10 years. The reset and interrupt vectors are located within the first 83 bytes of program memory (refer to Table 9-1 on page 41). Constant tables can be allocated within the entire 32K/64K program memory address space for access by the MOVC instruction. The AT89LP3240/6440 does not support external program memory. A map of the AT89LP3240/6440 program memory is shown in Figure 3-1.

### 3.1.1 SIG

In addition to the 64K code space, the AT89LP3240/6440 also supports a 256-byte User Signature Array and a 128-byte Atmel Signature Array that are accessible by the CPU. The Atmel Signature Array is initialized with the Device ID in the factory. The second page of the User Signature Array (0180H–01FFH) is initialized with analog configuration data including the Internal RC Oscillator calibration byte. The User Signature Array is available for user identification codes or constant parameter data. Data stored in the signature array is not secure. Security bits will disable writes to the array; however, reads by an external device programmer are always allowed.

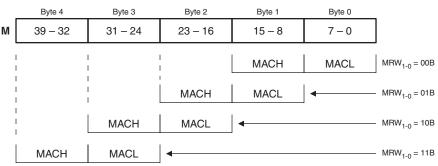

In order to read from the signature arrays, the SIGEN bit (DPCF.3) must be set (See Table 5-5 on page 28). While SIGEN is one, MOVC A, @A+DPTR will access the signature arrays. The User Signature Array is mapped from addresses 0100h to 01FFh and the Atmel Signature Array is mapped from addresses 0000h to 007Fh. SIGEN must be cleared before using MOVC to access the code memory. The User Signature Array may also be modified by the In-Application Programming interface. When IAP = 1 and SIGEN = 1, MOVX @DPTR instructions will access the array (See Section 3.5 on page 21).

## 3.2 Internal Data Memory

The AT89LP3240/6440 contains 256 bytes of general SRAM data memory plus 128 bytes of I/O memory mapped into a single 8-bit address space. Access to the internal data memory does not require any configuration. The internal data memory has three address spaces: DATA, IDATA and SFR; as shown in Figure 3-2. Some portions of external data memory are also implemented internally. See "External Data Memory" below for more information.

#### Figure 3-2. Internal Data Memory Map

#### 3.2.1 DATA

The first 128 bytes of RAM are directly addressable by an 8-bit address (00H–7FH) included in the instruction. The lowest 32 bytes of DATA memory are grouped into 4 banks of 8 registers each. The RS0 and RS1 bits (PSW.3 and PSW.4) select which register bank is in use. Instructions using register addressing will only access the currently specified bank. The lower 128 bit addresses are also mapped into DATA addresses 20H–2FH.

# 3.2.2 IDATA

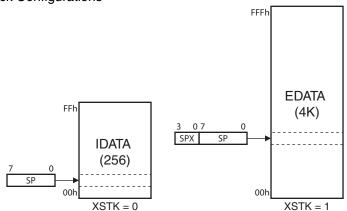

The full 256 byte internal RAM can be indirectly addressed using the 8-bit pointers R0 and R1. The first 128 bytes of IDATA include the DATA space. The hardware stack is also located in the IDATA space when XSTK = 0.

#### 3.2.3 SFR

The upper 128 direct addresses (80H–FFH) access the I/O registers. I/O registers on AT89LP devices are referred to as Special Function Registers. The SFRs can only be accessed through direct addressing. All SFR locations are not implemented. See Section 4. for a listed of available SFRs.

# 3.3 External Data Memory

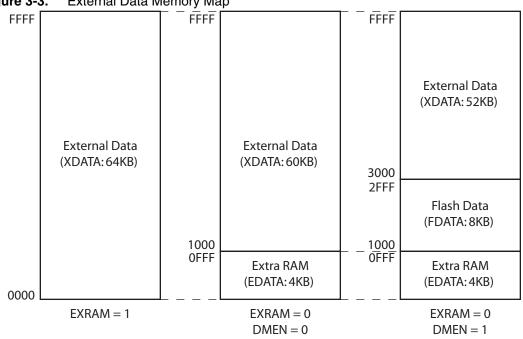

AT89LP microcontrollers support a 16-bit external memory address space for up to 64K bytes of external data memory (XDATA). The external memory space is accessed with the MOVX instructions. Some internal data memory resources are mapped into portions of the external address space as shown in Figure 3-3. These memory spaces may require configuration before the CPU can access them. The AT89LP3240/6440 includes 4K bytes of on-chip Extra RAM (EDATA) and 8K bytes of nonvolatile Flash data memory (FDATA).

#### 3.3.1 XDATA

The external data memory space can accommodate up to 64KB of external memory. The AT89LP3240/6440 uses the standard 8051 external memory interface with the upper address byte on Port 2, the lower address byte and data in/out multiplexed on Port 0, and the ALE,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes. MOVX instructions targeted to XDATA require a minimum of 4 clock cycles. XDATA can be accessed with both 16-bit (MOVX @DPTR) and 8-bit (MOVX @Ri) addresses. See Section 3.3.4 on page 17 for more details of the external memory interface.

Some internal data memory spaces are mapped into portions of the XDATA address space. In this case the lower address ranges will access internal resources instead of external memory. Addresses above the range implemented internally will default to XDATA. The AT89LP3240/6440 supports up to 52K or 60K bytes of external memory when using the internally mapped memories. Setting the EXRAM bit (AUXR.1) to one will force all MOVX instructions to access the entire 64KB XDATA regardless of their address (See "AUXR – Auxiliary Control Register" on page 18).

#### 3.3.2 EDATA

The Extra RAM is a portion of the external memory space implemented as an internal 4K byte auxiliary RAM. The Extra RAM is mapped into the EDATA space at the bottom of the external memory address space, from 0000H to 0FFFH. MOVX instructions to this address range will access the internal Extra RAM. EDATA can be accessed with both 16-bit (MOVX @DPTR) and 8-bit (MOVX @Ri) addresses. When 8-bit addresses are used, the PAGE register (086H) supplies the upper address bits. The PAGE register breaks EDATA into sixteen 256-byte pages. A page cannot be specified independently for MOVX @R0 and MOVX @R1. Setting PAGE above 0FH enables XDATA access, but does not change the value of Port 2. When 16-bit addresses are used (DPTR), the IAP bit (MEMCON.7) must be zero to access EDATA. MOVX instructions to EDATA require a minimum of 2 clock cycles.

**Table 3-2.**PAGE – EDATA Page Register

| PAGE = 86H Reset Value = 0000 000 |               |                                                                                                                                                                                                              |        |        |        |        |        |        |  |  |

|-----------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| Not Bit                           | t Addressable |                                                                                                                                                                                                              |        |        |        |        |        |        |  |  |

|                                   | PAGE.7        | PAGE.6                                                                                                                                                                                                       | PAGE.5 | PAGE.4 | PAGE.3 | PAGE.2 | PAGE.1 | PAGE.0 |  |  |

| Bit                               | 7             | 6                                                                                                                                                                                                            | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

| Symbol                            | Function      |                                                                                                                                                                                                              |        |        |        |        |        |        |  |  |

| PAGE <sub>7-0</sub>               |               | Selects which 256-byte page of EDATA is currently accessible by MOVX @Ri instructions when PAGE < 10H. Any PAGE value between 10H and FFH will selected XDATA; however, this value will not be output on P2. |        |        |        |        |        |        |  |  |

#### 3.3.3 FDATA

The Flash Data Memory is a portion of the external memory space implemented as an internal nonvolatile data memory. Flash Data Memory is enabled by setting the DMEN bit (MEMCON.3) to one. When IAP = 0 and DMEN = 1, the Flash Data Memory is mapped into the FDATA space, directly above the EDATA space near the bottom of the external memory address space, from 1000H to 2FFFH. (See Figure 3-3). MOVX instructions to this address range will access the internal nonvolatile memory. FDATA is not accessible while DMEN = 0. FDATA can be accessed only by 16-bit (MOVX @DPTR) addresses. MOVX @Ri instructions to the FDATA address range will access external memory. Addresses above the FDATA range are mapped to XDATA. MOVX instructions to FDATA require a minimum of 4 clock cycles.

#### 3.3.3.1 Write Protocol

The FDATA address space accesses an internal nonvolatile data memory. This address space can be read just like EDATA by issuing a MOVX A, @DPTR; however, writes to FDATA require a more complex protocol and take several milliseconds to complete. The AT89LP3240/6440 uses an *idle-while-write* architecture where the CPU is placed in an idle state while the write occurs. When the write completes, the CPU will continue executing with the instruction after the MOVX @DPTR,A instruction that started the write. All peripherals will continue to function during the write cycle; however, interrupts will not be serviced until the write completes.

# 14 **AT89LP3240/6440**

To enable write access to the nonvolatile data memory, the MWEN bit (MEMCON.4) must be set to one. When MWEN = 1 and DMEN = 1, MOVX @DPTR,A may be used to write to FDATA. FDATA uses flash memory with a page-based programming model. Flash data memory differs from traditional EEPROM data memory in the method of writing data. EEPROM generally can update a single byte with any value. Flash memory splits programming into write and erase operations. A Flash write can only program zeroes, i.e change ones into zeroes ( $1 \rightarrow 0$ ). Any ones in the write data are ignored. A Flash erase sets an entire page of data to ones so that all bytes become FFH. Therefore after an erase, each byte in the page can be written only once with any possible value. Bytes can not be overwritten once they are changed from the erased state without possibility of corrupting the data. Therefore, if even a single byte needs updating; then the contents of the page must first be saved, the entire page must be erased and the zero bits in all bytes (old and new data combined) must be written. Avoiding unnecessary page erases greatly improves the endurance of the memory.

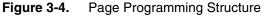

The AT89LP3240/6440 includes 64 data pages of 128 bytes each. One or more bytes in a page may be written at one time. The AT89LP3240/6440 includes a temporary page buffer of 64 bytes, or half of a page. Because the page buffer is 64 bytes long, the maximum number of bytes written at one time is 64. Therefore, two write cycles are required to fill the entire 128-byte page, one for the low half page (00H–3FH) and one for the high half page (40H–7FH) as shown in Figure 3-4.

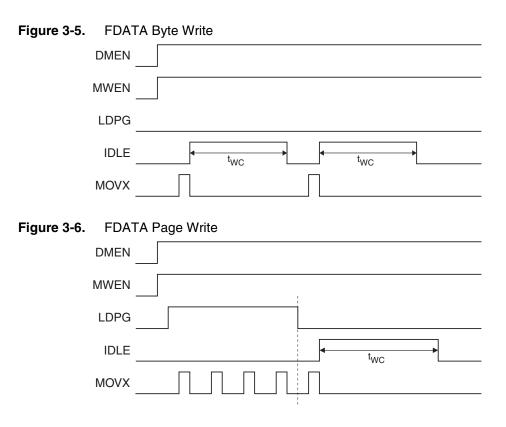

The LDPG bit (MEMCON.5) allows multiple data bytes to be loaded to the temporary page buffer. While LDPG = 1, MOVX @DPTR,A instructions will load data to the page buffer, but will not start a write sequence. Note that a previously loaded byte must not be reloaded prior to the write sequence. To write the half page into the memory, LDPG must first be cleared and then a MOVX @DPTR,A with the final data byte is issued. The address of the final MOVX determines which half page will be written. If a MOVX @DPTR,A instruction is issued while LDPG = 0 without loading any previous bytes, only a single byte will be written. The page buffer is reset after each write operation. Figures 3-5 and Figure 3-6 on page 16 show the difference between byte writes and page writes.

The auto-erase bit AERS (MEMCON.6) can be set to one to perform a page erase automatically at the beginning of any write sequence. The page erase will erase the entire page, i.e. both the low and high half pages. However, the write operation paired with the auto-erase can only program one of the half pages. A second write cycle without auto-erase is required to update the other half page.

Frequently just a few bytes within a page must be updated while maintaining the state of the other bytes. There are two options for handling this situation that allow the Flash Data memory to emulate a traditional EEPROM memory. The simplest method is to copy the entire page into a buffer allocated in RAM, modify the desired byte locations in the RAM buffer, and then load and write back first the low half page (with auto-erase) and then the high half page to the Flash memory. This option requires that at least one page size of RAM is available as a temporary buffer. The second option is to store only one half page in RAM. The unmodified bytes of the other page are loaded directly into the Flash memory's temporary load buffer before loading the updated values of the modified bytes. For example, if just the low half page needs modification, the user must first store the high half page to RAM, followed by reading and loading the unaffected bytes of the low half page into the page buffer. Then the modified bytes of the low half page are stored to the page buffer before starting the auto-erase sequence. The stored value of the high half page must be written without auto-erase after the programming of the low half page completes. This method reduces the amount of RAM required; however, more software overhead is needed because the read-and-load-back routine must skip those bytes in the page that need to be updated in order to prevent those locations in the buffer from being loaded with the previous data, as this will block the new data from being loaded correctly.

A write sequence will not occur if the Brown-out Detector is active, even if the BOD reset has been disabled. In cases where the BOD reset is disabled, the user should check the BOD status by reading the WRTINH bit in MEMCON. If a write currently in progress is interrupted by the BOD due to a low voltage condition, the ERR flag will be set. FDATA can always be read regardless of the BOD state.

For more details on using the Flash Data Memory, see the application note titled "AT89LP Flash Data Memory". FDATA may also be programmed by an external device programmer (See Section 25. on page 157).

#### Table 3-3. MEMCON – Memory Control Register

| MEMC   | CON = 96H                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                        |      |      |      |     | Reset Value | = 0000 00XXB |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----|-------------|--------------|--|--|

| Not Bi | t Addressable                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

|        | IAP                                                                                                                                                                                                                                                                                     | AERS                                                                                                                                                                                                   | LDPG | MWEN | DMEN | ERR | _           | WRTINH       |  |  |

| Bit    | 7                                                                                                                                                                                                                                                                                       | 6                                                                                                                                                                                                      | 5    | 4    | 3    | 2   | 1           | 0            |  |  |

| Symbol | Function                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| IAP    | In-Application Programming Enable. When IAP = 1 and the IAP Fuse is enabled, programming of the CODE/SIG space is enabled and MOVX @DPTR instructions will access CODE/SIG instead of EDATA or FDATA. Clear IAP to disable programming of CODE/SIG and allow access to EDATA and FDATA. |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| AERS   | Auto-Erase Enable. Set to perform an auto-erase of a Flash memory page (CODE, SIG or FDATA) during the next write sequence. Clear to perform write without erase.                                                                                                                       |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| LDPG   | Load Page Enable. Set to this bit to load multiple bytes to the temporary page buffer. Byte locations may not be loaded more than once before a write. LDPG must be cleared before writing.                                                                                             |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| MWEN   | Memory Write Enable. Set to enable programming of a nonvolatile memory location (CODE, SIG or FDATA). Clear to disable programming of all nonvolatile memories.                                                                                                                         |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| DMEN   | Data Memory Enable. Set to enable nonvolatile data memory and map it into the FDATA space. Clear to disable nonvolatile data memory.                                                                                                                                                    |                                                                                                                                                                                                        |      |      |      |     |             |              |  |  |

| ERR    |                                                                                                                                                                                                                                                                                         | Error Flag. Set by hardware if an error occurred during the last programming sequence due to a brownout condition (low voltage on VDD). Must be cleared by software.                                   |      |      |      |     |             |              |  |  |

| WRTINH |                                                                                                                                                                                                                                                                                         | Write Inhibit Flag. Cleared by hardware when the voltage on VDD has fallen below the minimum programming voltage.<br>Set by hardware when the voltage on VDD is above the minimum programming voltage. |      |      |      |     |             |              |  |  |

#### 3.3.4 External Memory Interface

The AT89LP3240/6440 uses the standard 8051 external memory interface with the upper address on Port 2, the lower address and data in/out multiplexed on Port 0, and the ALE,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes. The interface may be used in two different configurations depending on which type of MOVX instruction is used to access XDATA.

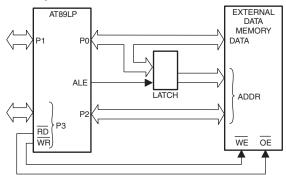

Figure 3-7 shows a hardware configuration for accessing up to 64K bytes of external RAM using a 16-bit linear address. Port 0 serves as a multiplexed address/data bus to the RAM. The Address Latch Enable strobe (ALE) is used to latch the lower address byte into an external register so that Port 0 can be freed for data input/output. Port 2 provides the upper address byte throughout the operation. The MOVX @DPTR instructions use Linear Address mode

### Figure 3-7. External Memory 16-bit Linear Address Mode

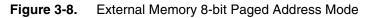

Figure 3-8 shows a hardware configuration for accessing 256-byte blocks of external RAM using an 8-bit paged address. Port 0 serves as a multiplexed address/data bus to the RAM. The ALE strobe is used to latch the address byte into an external register so that Port 0 can be freed for data input/output. The Port 2 I/O lines (or other ports) can provide control lines to page the memory; however, this operation is not handled automatically by hardware. The software application must change the Port 2 register when appropriate to access different pages. The MOVX @Ri instructions use Paged Address mode.

| Table 3-4. | AUXR – Auxiliary Control Register |

|------------|-----------------------------------|

|------------|-----------------------------------|

| AUXR =  | AUXR = 8EH Reset Value = xxx0 0000B |   |   |      |     |     |       |      |  |  |  |

|---------|-------------------------------------|---|---|------|-----|-----|-------|------|--|--|--|

| Not Bit | Addressable                         |   |   |      |     |     |       |      |  |  |  |

|         | -                                   | - | _ | XSTK | WS1 | WS0 | EXRAM | ALES |  |  |  |

| Bit     | 7                                   | 6 | 5 | 4    | 3   | 2   | 1     | 0    |  |  |  |

| Symbol  | Functio                                                                                                                                                                                                                                                                                                   | n                                                                                                                                                                                                                                                                                                   |             |                      |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|--|--|--|

| XSTK    | the stac                                                                                                                                                                                                                                                                                                  | Extended Stack Enable. When XSTK = 0 the stack resides in IDATA and is limited to 256 bytes. Set XSTK = 1 to place the stack in EDATA for up to 4K bytes of extended stack space. All PUSH, POP, CALL and RET instructions will incur a one or two cycle penalty when accessing the extended stack. |             |                      |  |  |  |

| WS[1-0] | Wait Sta                                                                                                                                                                                                                                                                                                  | Wait State Select. Determines the number of wait states inserted into external memory accesses.                                                                                                                                                                                                     |             |                      |  |  |  |

|         | <u>WS1</u>                                                                                                                                                                                                                                                                                                | <u>WS0</u>                                                                                                                                                                                                                                                                                          | Wait States | RD / WR Strobe Width |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   | 0           | 1 x t <sub>CYC</sub> |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   | 1           | 2 x t <sub>CYC</sub> |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                   | 2           | 3 x t <sub>CYC</sub> |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                   | 3           | 4 x t <sub>CYC</sub> |  |  |  |

| EXRAM   | External RAM Enable. When EXRAM = 0, MOVX instructions can access the internally mapped portions of the address space. Accesses to addresses above internally mapped memory will access external memory. Set EXRAM = 1 to bypass the internal memory and map the entire address space to external memory. |                                                                                                                                                                                                                                                                                                     |             |                      |  |  |  |

| ALES    |                                                                                                                                                                                                                                                                                                           | ALE Idle State. When ALES = 0 the idle polarity of ALE is high (active). When ALES = 1 the idle polarity of ALE is low (inactive). The ALE strobe pulse is always active high. ALES must be zero in order to use P4.4 as a general I/O.                                                             |             |                      |  |  |  |

Note that prior to using the external memory interface, Port 2,  $\overline{WR}$  (P3.6),  $\overline{RD}$  (P3.7) and ALE (P4.4) must be configured as outputs. See Section 10.1 "Port Configuration" on page 45. Port 0 is configured automatically to push-pull output mode when outputting address or data and is

automatically tristated when inputting data regardless of the Port 0 configuration. The Port 0 configuration will determine the idle state of Port 0 when not accessing the external memory.

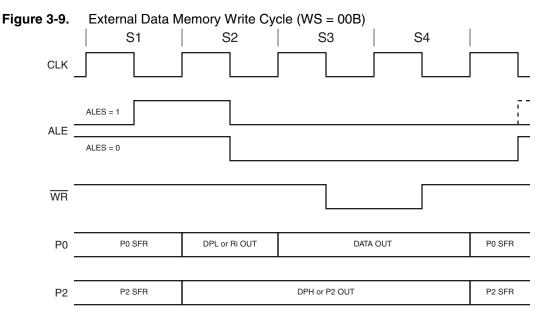

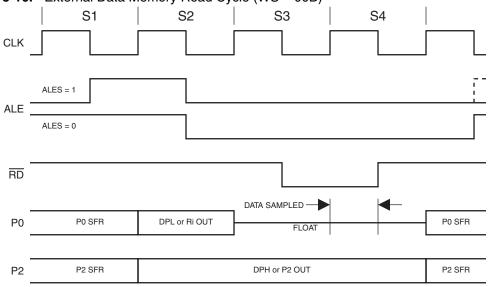

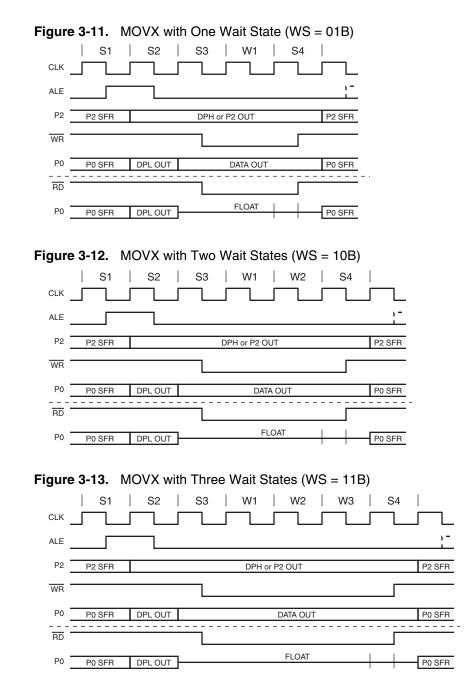

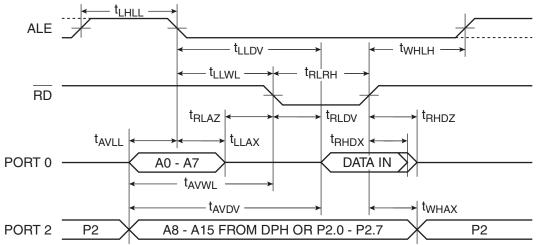

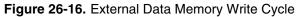

Figure 3-9 and Figure 3-10 show examples of external data memory write and read cycles, respectively. The address on P0 and P2 is stable at the falling edge of ALE. The idle polarity of ALE is controlled by ALES (AUXR.0). When ALES = 0 the idle polarity of ALE is high (active). When ALES = 1 the idle polarity of ALE is low (inactive). The ALE strobe pulse is always active high. Unlike standard 8051s, ALE will not toggle continuously when not accessing external memory. ALES must be zero in order to use P4.4 as a general-purpose I/O. The WS bits in AUXR can extended the  $\overline{RD}$  and  $\overline{WR}$  strobes by 1, 2 or 3 cycles as shown in Figures 3-11, 3-12 and 3-13. If a longer strobe is required, the application can scale the system clock with the clock divider to meet the requirements (See Section 6.5 on page 32).

Figure 3-10. External Data Memory Read Cycle (WS = 00B)

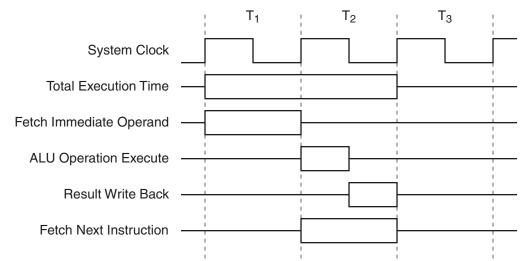

### 3.4 Extended Stack

The AT89LP3240/6440 provides an extended stack space for applications requiring additional stack memory. By default the stack is located in the 256-byte IDATA space of internal data memory. The IDATA stack is referenced solely by the 8-bit Stack Pointer (SP: 81H). Setting the XSTK bit in AUXR enables the extended stack. The extended stack resides in the EDATA space for up to 4KB of stack memory. The extended stack is referenced by a 12-bit pointer formed from SP and the four LSBs of the Extended Stack Pointer (SPX: 9EH) as shown in Figure 3-14. SP is shared between both stacks. Note that the standard IDATA stack will not overflow to the EDATA stack or vice versa. The stack and extended stack are mutually exclusive and SPX is ignored when XTSK = 0. An application choosing to switch between stacks by toggling XSTK must main-

# <sup>20</sup> **AT89LP3240/6440**

tain separate copies of SP for use with each stack space. Interrupts should be disabled while swapping copies of SP in such an application to prevent illegal stack accesses.

All interrupt calls and PUSH, POP, ACALL, LCALL, RET and RETI instructions will incur a one or two-cycle penalty while the extended stack is enabled, depending on the number of stack access in each instruction. The extended stack may only exist within the internal EDATA space; it cannot be placed in XDATA. The stack will continue to use EDATA even if EDATA is disabled by setting EXRAM = 1.

# 3.5 In-Application Programming (IAP)

The AT89LP3240/6440 supports In-Application Programming (IAP), allowing the program memory to be modified during execution. IAP can be used to modify the user application on the fly or to use program memory for nonvolatile data storage. The same page structure write protocol for FDATA also applies to IAP (See Section 3.3.3.1 "Write Protocol" on page 14). The CPU is always placed in idle while modifying the program memory. When the write completes, the CPU will continue executing with the instruction after the MOVX @DPTR,A instruction that started the write.

To enable access to the program memory, the IAP bit (MEMCON.7) must be set to one and the IAP User Fuse must be enabled. The IAP User Fuse can disable all IAP operations. When this fuse is disabled, the IAP bit will be forced to 0. While IAP is enabled, all MOVX @DPTR instructions will access the CODE space instead of EDATA/FDATA/XDATA. IAP also allows reprogramming of the User Signature Array when SIGEN = 1. The IAP access settings are summarized in Table 3-5.

| IAP | SIGEN | DMEN | MOVX @DPTR         | MOVC @DPTR        |

|-----|-------|------|--------------------|-------------------|

| 0   | 0     | 0    | EDATA (0000–0FFFH) | CODE (0000-FFFFH) |

| 0   | 0     | 1    | FDATA (1000–2FFFH) | CODE (0000–FFFFH) |

| 0   | 1     | 0    | EDATA (0000–0FFFH) | SIG (0000–01FFH)  |

| 0   | 1     | 1    | FDATA (1000–2FFFH) | SIG (0000–01FFH)  |

| 1   | 0     | Х    | CODE (0000-FFFFH)  | CODE (0000-FFFFH) |

| 1   | 1     | Х    | SIG (0000–01FFH)   | SIG (0000–01FFH)  |

Table 3-5.IAP Access Settings

# 4. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 4-1. See also "Register Index" on page 153.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect. User software should not write to these unlisted locations, since they may be used in future products to invoke new features.

Table 4-1.

AT89LP3240/6440 SFR Map and Reset Values

|      | 8                  | 9                  | Α                   | В                   | С                   | D                  | E                      | F                   |      |

|------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|------------------------|---------------------|------|

| 0F8H |                    |                    |                     |                     |                     |                    |                        |                     | 0FFH |

| 0F0H | B<br>0000 0000     |                    |                     |                     |                     |                    |                        | BX<br>0000 0000     | 0F7H |

| 0E8H | SPSR<br>000x x000  | SPCR<br>0000 0000  | SPDR<br>xxxx xxxx   |                     |                     |                    |                        |                     | 0EFH |

| 0E0H | ACC<br>0000 0000   | AX<br>0000 0000    | DSPR<br>0000 0000   | FIRD<br>0000 0000   | MACL<br>0000 0000   | MACH<br>0000 0000  |                        |                     | 0E7H |

| 0D8H |                    | DADC<br>0000 0000  | DADI<br>0000 0000   |                     | DADL<br>0000 0000   | DADH<br>0000 0000  |                        |                     | 0DFH |

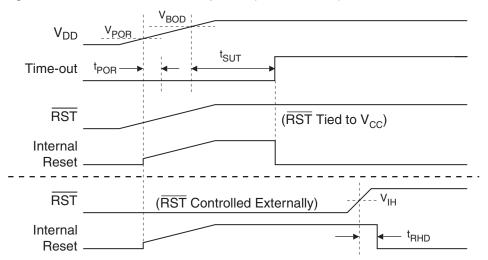

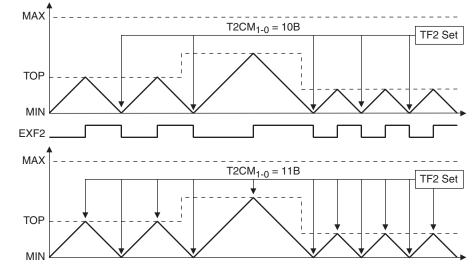

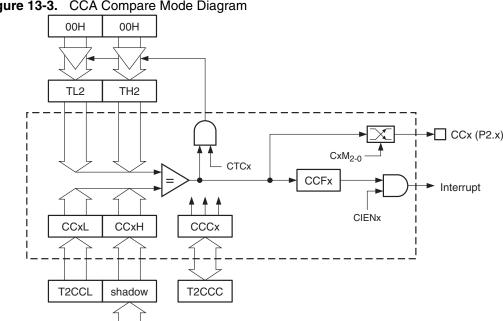

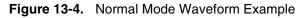

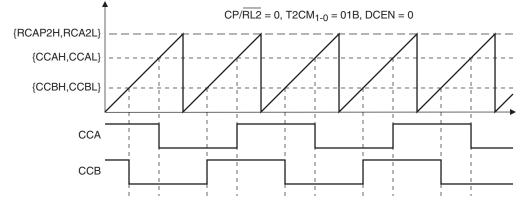

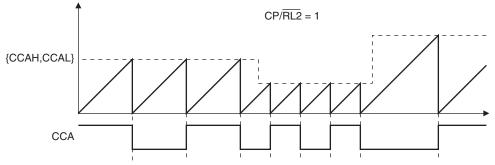

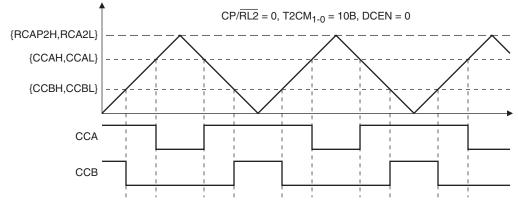

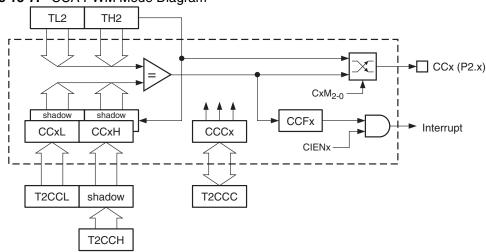

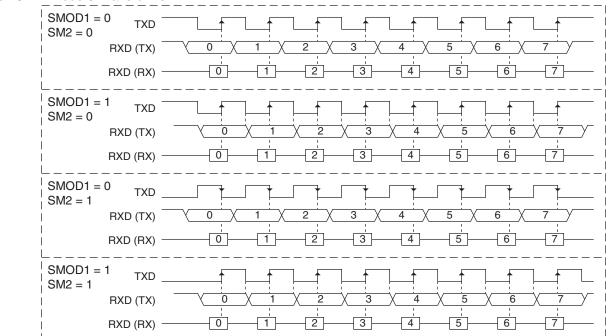

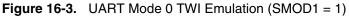

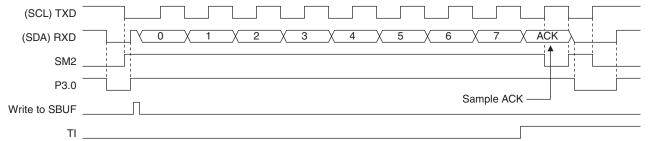

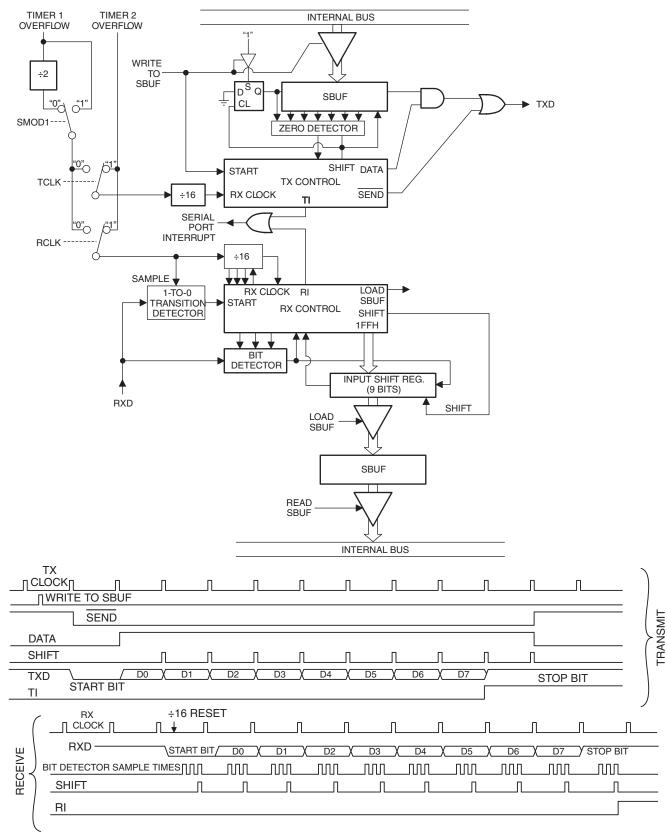

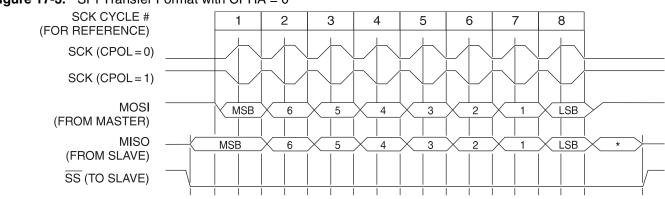

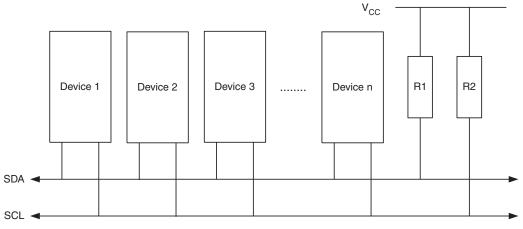

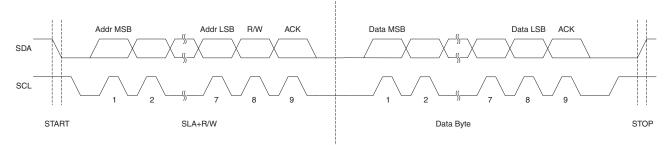

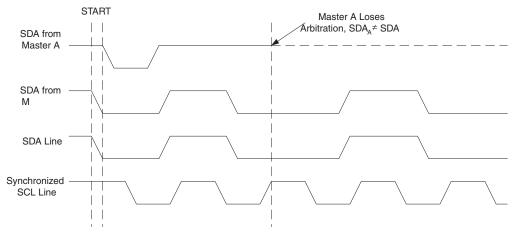

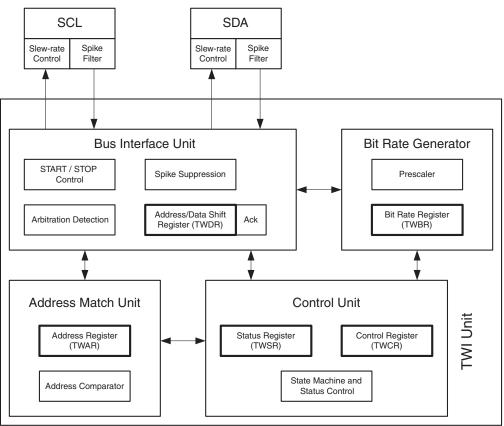

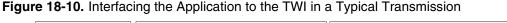

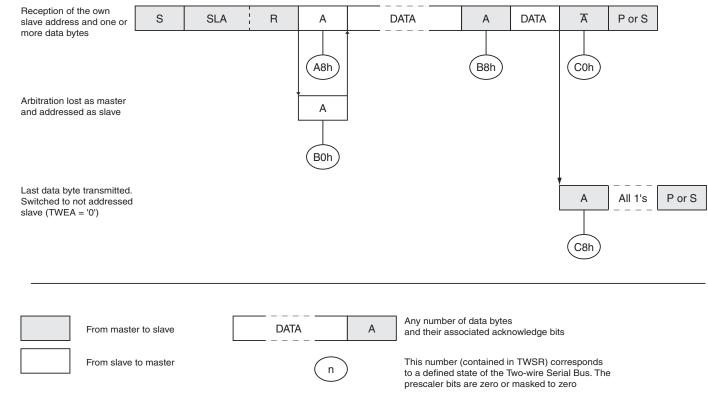

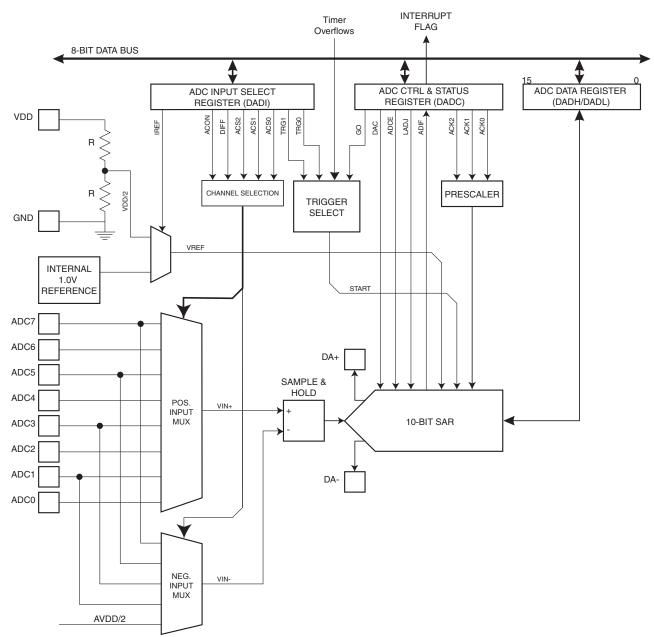

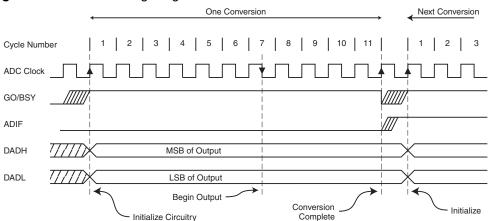

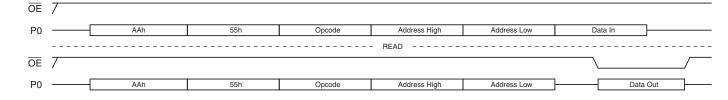

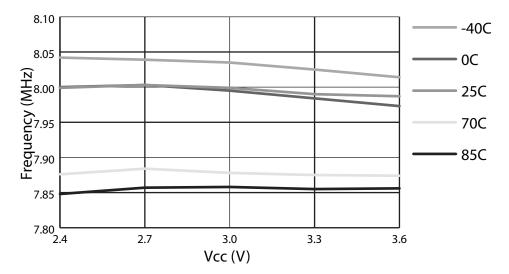

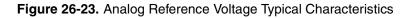

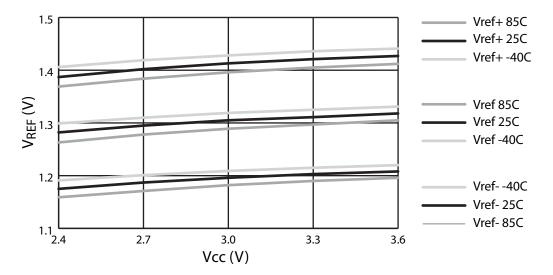

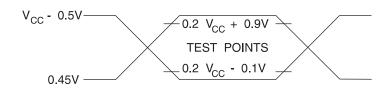

| 0D0H | PSW<br>0000 0000   | T2CCA<br>0000 0000 | T2CCL<br>0000 0000  | T2CCH<br>0000 0000  | T2CCC<br>0000 0000  | T2CCF<br>0000 0000 |                        |                     | 0D7H |