### **General Description**

The MAX5934/MAX5934A are fully integrated hot-swap controllers for +9V to +80V (MAX5934A) positive supply rails. The MAX5934 is optimized for +33V to +80V power-supply rails. These devices allow for the safe insertion and removal of circuit cards into a live backplane without causing glitches on the backplane power-supply rail. The MAX5934/MAX5934A feature a programmable analog foldback current limit, programmable undervoltage lockout, and programmable output-voltage slew rate through an external n-channel MOSFET. In addition, if these devices remain in current limit for more than a programmable time, the external n-channel MOSFET latches off.

The MAX5934/MAX5934A feature pin-selectable PWRGD\_ assertion polarity (active low or active high) and pin-selectable fault management (latched or autoretry). Other features include automatic restart after a circuit-breaker fault, selectable duty-cycle (DC) options, and thermal-shutdown mode for overtemperature protection.

The MAX5934/MAX5934A operate in the extended (-40°C to +85°C) temperature range and are available in a 16-pin QSOP package.

#### **Applications**

Hot Board Insertion Electronic Circuit Breakers Industrial High-Side Switch/Circuit Breakers Network Routers and Switches 24V/48V Industrial/Alarm Systems

Typical Application Circuit appears at end of data sheet.

#### **Features**

- ♦ Provides Safe Hot Swap for +9V to +80V Power Supplies (MAX5934A)

- ♦ Safe Board Insertion and Removal from a Live Backplane

- ♦ Pin-Selectable Active-Low or Active-High Power-**Good Output**

- ♦ Pin-Selectable Latched or Autoretry Fault Management

- Programmable Foldback Current Limiting

- ♦ High-Side Drive for an External N-Channel MOSFET

- ♦ Built-In Thermal Shutdown

- ♦ Undervoltage Lockout (UVLO)

- ♦ Pin-Selectable Duty-Cycle Options (0.94%, 1.88%, 3.75%)

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX5934EEE  | -40°C to +85°C | 16 QSOP     |

| MAX5934AEEE | -40°C to +85°C | 16 QSOP     |

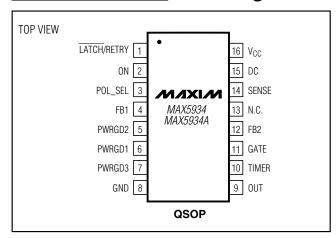

### **Pin Configuration**

#### Selector Guide

| PART     | DEFAULT UVLO<br>(V) | SUPPLY VOLTAGE RANGE (V)  LATCHED/ AUTORETRY FAULT PROTECTION |                | DUTY CYCLE     | PWRGD_<br>OUTPUT LOGIC |  |

|----------|---------------------|---------------------------------------------------------------|----------------|----------------|------------------------|--|

| MAX5934  | 31                  | +33 to +80                                                    | Pin-selectable | Pin-selectable | Pin-selectable         |  |

| MAX5934A | 8.3                 | +9 to +80                                                     | Pin-selectable | Pin-selectable | Pin-selectable         |  |

Maxim Integrated Products 1

#### ABSOLUTE MAXIMUM RATINGS

| (Voltages referenced to GND.)  VCC0.3V to +85V  SENSE, FB_, ON0.3V to (VCC + 0.3V)  TIMER, PWRGD_, DC, LATCH/RETRY, POL_SEL0.3V to +85V  GATE0.3V to +95V  OUT(VGATE - 14V) to the lower of (VGATE + 0.3V) and (VCC + 0.3V)  Maximum GATE Current50mA +150mA | Continuous Power Dissipation (T <sub>A</sub> = +70°C)  16-Pin QSOP (derate 8.3mW/°C above +70°C)667mW Operating Temperature Range40°C to +85°C Maximum Junction Temperature+150°C Storage Temperature Range60°C to +150°C ESD Rating (Human Body Model)2000V Lead Temperature (soldering, 10s)+300°C |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum GATE Current50mA, +150mA                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                      |

| ·                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                      |

| Maximum Current into Any Other Pin±50mA                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +24V \text{ (MAX5934A)}, V_{CC} = +48V \text{ (MAX5934)}, GND = 0V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                          | SYMBOL               | CONDITIONS                                                         |                                  | MIN   | TYP       | MAX         | UNITS |

|----------------------------------------------------|----------------------|--------------------------------------------------------------------|----------------------------------|-------|-----------|-------------|-------|

| Cupply Valtage Dange                               | Mari                 | MAX5934A                                                           |                                  | 9     |           | 80          | V     |

| Supply Voltage Range                               | Vcc                  | MAX5934                                                            |                                  | 33    |           | 80          | V     |

| Supply Current                                     | Icc                  | $V_{ON} = 3V, V_{CC} = 8$                                          | 0V                               |       | 1.4       | 3.5         | mA    |

| V <sub>CC</sub> Undervoltage Lockout               | V <sub>LKO</sub>     | V <sub>CC</sub> low-to-high transition                             | 90 9                             |       | 8.3<br>31 | 8.8<br>32.5 | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Hysteresis | VLKOHYST             | MAX5934A<br>MAX5934                                                |                                  |       | 0.4       |             | V     |

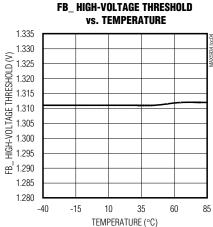

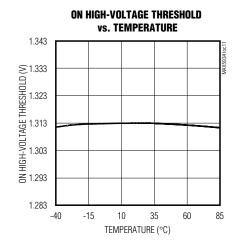

| FB1 High-Voltage Threshold                         | V <sub>FB1H</sub>    | FB1 low-to-high tra                                                | nsition                          | 1.280 | 1.313     | 1.345       | V     |

| FB2 High-Voltage Threshold                         | V <sub>FB2H</sub>    | FB2 low-to-high tra                                                | nsition                          | 1.280 | 1.313     | 1.345       | V     |

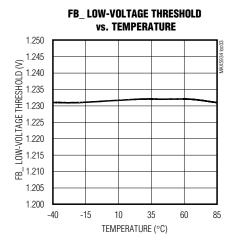

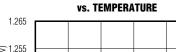

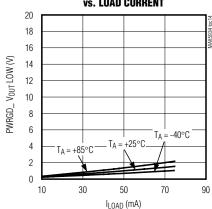

| FB1 Low-Voltage Threshold                          | V <sub>FB1L</sub>    | FB1 high-to-low tra                                                | nsition                          | 1.221 | 1.233     | 1.245       | V     |

| FB2 Low-Voltage Threshold                          | V <sub>FB2L</sub>    | FB2 high-to-low transition                                         |                                  | 1.202 |           | 1.264       | V     |

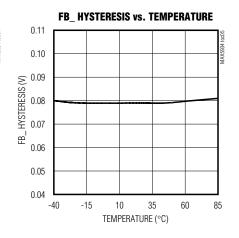

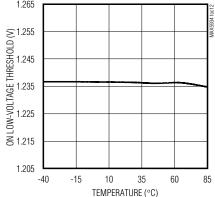

| FB_ Hysteresis                                     | V <sub>FBH</sub> YST |                                                                    |                                  |       | 80        |             | mV    |

| FB_ Input Bias Current                             | I <sub>INFB</sub>    | V <sub>FB</sub> _ = 0V                                             |                                  | -1    |           | +1          | μΑ    |

| FB1 Threshold Line Regulation                      | ΔV <sub>FB1</sub>    | V <sub>CC(MIN)</sub> ≤ V <sub>CC</sub> ≤ 80V, MAX5934A,<br>ON = 0V |                                  |       |           | 0.05        | mV/V  |

| FB2 Threshold Line Regulation                      | ΔV <sub>FB2</sub>    | V <sub>CC(MIN)</sub> ≤ V <sub>CC</sub> ≤ 80V, MAX5934A,<br>ON = 0V |                                  |       |           | 0.05        | mV/V  |

| SENSE Trip Voltage                                 | Ma                   | $V_{FB} = 0V$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$               |                                  | 8     | 12        | 17          | >/    |

| (VCC - VSENSE)                                     | VSENSETRIP           | V <sub>FB</sub> _ = 1V, T <sub>A</sub> = 0°0                       | C to +70°C                       | 39    | 47        | 55          | mV    |

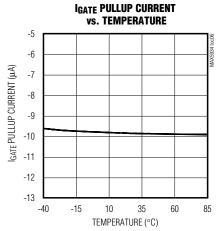

| GATE Pullup Current                                | IGATEUP              | Charge pump on, V <sub>GATE</sub> = 7V                             |                                  | -5    | -10       | -20         | μΑ    |

| GATE Pulldown Current                              | IGATEDN              | Any fault condition, VGATE = 2V                                    |                                  | 35    | 70        | 100         | mA    |

| (VGATE - VCC) at PWRGD3<br>Assertion               | ΔVGATEPWRGD3         | VGATE - VCC, low-to-high transition                                |                                  | 3.8   | 4.3       | 5           | V     |

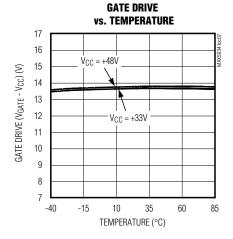

|                                                    | ΔVGATE               | V <sub>GATE</sub> - V <sub>CC</sub> , MAX5934                      |                                  | 10    | 13.6      | 18          |       |

| External N-Channel Gate Drive                      |                      | VGATE - VCC,                                                       | $V_{CC} = 10.8V \text{ to } 20V$ | 4.5   | 13.6      | 18.0        | V     |

|                                                    |                      | MAX5934A                                                           | V <sub>CC</sub> = 20V to 80V     | 10    | 13.6      | 18          |       |

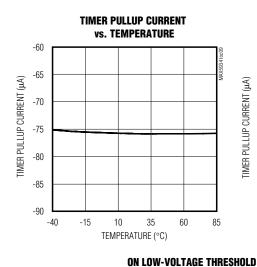

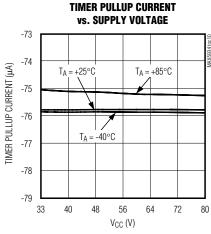

| TIMER Pullup Current                               | ITIMERUP             | V <sub>TIMER</sub> = 0V                                            |                                  | -24   | -75       | -120        | μΑ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +24V \text{ (MAX5934A)}, V_{CC} = +48V \text{ (MAX5934)}, \text{ GND} = 0V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                      | SYMBOL                                         | CONDITIONS                                |                            | MIN       | TYP   | MAX   | UNITS |

|------------------------------------------------|------------------------------------------------|-------------------------------------------|----------------------------|-----------|-------|-------|-------|

|                                                |                                                |                                           | DC = 3.75%, DC = floating  | 1.5       | 3     | 4.5   |       |

| TIMER Pulldown Current                         | ITIMERON                                       | V <sub>TIMER</sub> = 1V                   | DC = 1.88%, DC = high      | 0.75      | 1.5   | 2.25  | μΑ    |

|                                                |                                                |                                           | DC = 0.94%, DC = low       | 0.37      | 0.75  | 1.12  |       |

| ON High Threshold                              | Vonh                                           | ON low-to-high                            | n transition               | 1.280     | 1.313 | 1.355 | V     |

| ON Low Threshold                               | Vonl                                           | ON high-to-lov                            | v transition               | 1.221     | 1.233 | 1.245 | V     |

| ON Hysteresis                                  | Vonhyst                                        |                                           |                            |           | 80    |       | mV    |

| ON Input Bias Current                          | IINON                                          | $V_{ON} = 0V$                             |                            | -1        |       | +1    | μΑ    |

| LATCH/RETRY and POL_SEL Low-Voltage Threshold  | V <sub>LRIL</sub> ,<br>Vpos_sel_il             |                                           |                            | 0.4       |       |       | V     |

| LATCH/RETRY and POL_SEL High-Voltage Threshold | V <sub>LRIH</sub> ,<br>V <sub>POS_SEL_IH</sub> |                                           |                            |           |       | 3.2   | V     |

| LATCH/RETRY and POL_SEL                        | I <sub>LR_IN</sub> ,                           | V <sub>POL_SEL</sub> = 80                 | )V                         |           | 4.5   |       | μA    |

| Input Current                                  | IPOS_SEL_IN                                    | V <sub>POL_SEL</sub> = 0\                 | 1                          |           | -37   |       | μΑ    |

| Source GATE Clamp Voltage                      | V <sub>SGZ</sub>                               | VGATE - VOUT                              |                            | 15        | 16.4  | 19    | V     |

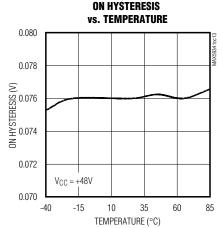

| PWRGD_ Output Low Voltage                      | Vol                                            | I <sub>O</sub> = 2mA                      |                            |           |       | 0.4   | V     |

| FWNGD_ Output Low Voltage                      | VoL                                            | $I_O = 4mA$                               |                            |           |       | 2.5   | V     |

| PWRGD_ Leakage Current                         | ЮН                                             | V <sub>PWRGD_</sub> = 80V                 |                            |           |       | 10    | μΑ    |

| Thermal Shutdown                               |                                                | Temperature rising                        |                            |           | +150  |       | °C    |

| Thermal-Shutdown Hysteresis                    |                                                |                                           |                            |           | 20    |       | °C    |

| SENSE Input Bias Current                       | ISENSE                                         | V <sub>SENSE</sub> = 0 to V <sub>CC</sub> |                            | -1        |       | +3    | μΑ    |

| DC High-Voltage Threshold 1                    | VDCHTH                                         | Rising edge, Di<br>1.88%                  | C transition from 3.75% to | 2.150     | 2.600 | 2.850 | V     |

| DC High-Voltage Threshold 2                    | V <sub>DCLTH</sub>                             | Rising edge, Di<br>3.75%                  | C transition from 0.94% to | 1.075     | 1.250 | 1.425 | V     |

| DC High-Voltage Threshold 1<br>Hysteresis      | VDCLHYS                                        |                                           |                            |           | 45    |       | mV    |

| DC High-Voltage Threshold 2<br>Hysteresis      | VDCLHYS                                        |                                           |                            |           | 45    |       | mV    |

| DC Input Open-Circuit Voltage                  | $V_{DCOC}$                                     |                                           |                            |           | 1.9   |       | V     |

| DC Input Impedance                             | R <sub>DC_IN</sub>                             |                                           |                            |           | 57    |       | kΩ    |

| DC Input Current                               | IDC_IN                                         | V_DC = 80V                                |                            | 50<br>-34 |       | μΑ    |       |

| DO INPUL GUITEIIL                              |                                                | V_DC = 0V                                 |                            |           |       |       |       |

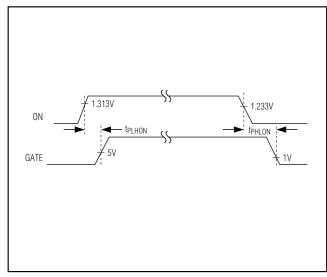

| ON Low-to-GATE Low<br>Propagation Delay        | <sup>t</sup> PHLON                             | C <sub>GATE</sub> = 0, Figures 1 and 2    |                            |           | 6     |       | μs    |

| ON High-to-GATE High<br>Propagation Delay      | <sup>t</sup> PLHON                             | C <sub>GATE</sub> = 0, Figures 1 and 2    |                            |           | 1.7   |       | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +24V \text{ (MAX5934A)}, V_{CC} = +48V \text{ (MAX5934)}, GND = 0V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                                     | SYMBOL                | CONDITIONS                                                     | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|-------|

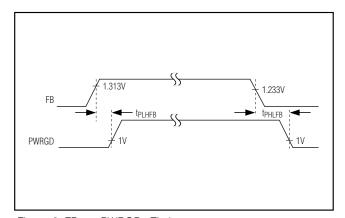

| FB_ Low-to-PWRGD_ Low<br>Propagation Delay                                    | tpHLFB_               | Figures 1, 3                                                   |     | 3.2 |     | μs    |

| FB_ High-to-PWRGD_ High<br>Propagation Delay                                  | tpLHFB_               | Figures 1, 3                                                   |     | 1.5 |     | μs    |

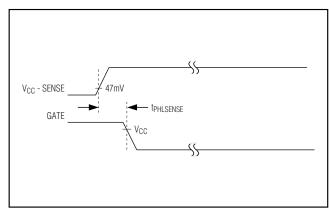

| (V <sub>CC</sub> - V <sub>SENSE</sub> ) High-to-GATE<br>Low Propagation Delay | <sup>t</sup> PHLSENSE | T <sub>A</sub> = +25°C, C <sub>GATE</sub> = 0, Figures 1 and 4 | 0.5 | 1.8 | 2.5 | μs    |

**Note 1:** All currents into the device are positive and all currents out of the device are negative. All voltages are referenced to ground, unless noted otherwise.

### **Test Circuit and Timing Diagrams**

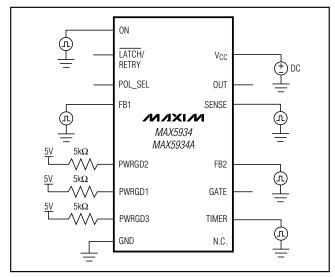

Figure 1. Test Circuit

Figure 2. ON-to-GATE Timing

Figure 3. FB\_-to-PWRGD\_ Timing

Figure 4. SENSE-to-GATE Timing

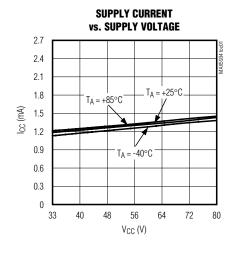

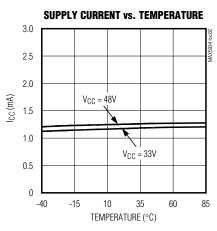

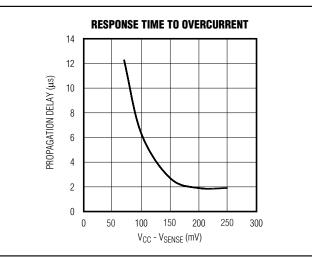

### Typical Operating Characteristics

$(V_{CC} = +48V, T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{CC} = +48V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### **PWRGD OUTPUT VOLTAGE LOW** vs. LOAD CURRENT

# Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                         |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LATCH/<br>RETRY | Circuit-Breaker Fault-Management Select Input. Connect LATCH/RETRY to GND to latch off after a circuit-breaker fault. Leave LATCH/RETRY open or drive to logic-high voltage for automatic restart after a circuit-breaker fault.                                 |

| 2   | ON              | On/Off Control Input. ON implements the undervoltage-lockout threshold and resets the part after a fault latch (see the Fault Management (LATCH/RETRY) section).                                                                                                 |

| 3   | POL_SEL         | PWRGD_ Polarity Select Input. Leave POL_SEL open or drive to logic-high voltage for PWRGD_ asserted high. Connect POL_SEL to GND for PWRGD_ asserted low.                                                                                                        |

| 4   | FB1             | Power-Good Comparator Input. Connect a resistive divider between output, FB1, and GND to monitor the output voltage (see the <i>Power-Good (PWRGD_ ) Detection</i> section). FB1 is also used as feedback for the current-limit foldback function.               |

| 5   | PWRGD2          | Open-Drain Power-Good Output. POL_SEL determines the output polarity of PWRGD2. PWRGD2 is asserted when FB2 is higher than V <sub>FB2H</sub> . PWRGD2 deasserts when FB2 is lower than V <sub>FB2L</sub> (see the <i>Power-Good (PWRGD_) Detection</i> section). |

| 6   | PWRGD1          | Open-Drain Power-Good Output. POL_SEL determines the output polarity of PWRGD1. PWRGD1 is asserted when FB1 is higher than V <sub>FB1H</sub> . PWRGD1 deasserts when FB1 is lower than V <sub>FB1L</sub> (see the <i>Power-Good (PWRGD_) Detection</i> section). |

| 7   | PWRGD3          | Open-Drain Power-Good Output. POL_SEL determines the output polarity of PWRGD3. PWRGD3 asserts when GATE is at maximum voltage. PWRGD3 deasserts after the timeout following an overcurrent event (see the <i>Power-Good (PWRGD_) Detection</i> section).        |

| 8   | GND             | Ground                                                                                                                                                                                                                                                           |

| 9   | OUT             | Output Voltage. OUT is used as the return path for the internal GATE protection clamping circuitry.                                                                                                                                                              |

| 10  | TIMER           | Timing Input. Connect a capacitor from TIMER to GND to program the maximum time the part is allowed to remain in current limit (see the <i>TIMER</i> section).                                                                                                   |

| 11  | GATE            | Gate-Drive Output. The high-side gate drive for the external n-channel MOSFET (see the <i>GATE</i> section).                                                                                                                                                     |

| 12  | FB2             | Noninverting Comparator Input. FB2 is used to monitor any other voltage in the system. When FB2 rises higher than V <sub>FB2H</sub> , PWRGD2 asserts. When FB2 drops below V <sub>FB2L</sub> , PWRGD2 deasserts.                                                 |

| 13  | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                         |

| 14  | SENSE           | Current-Sense Input. Connect a sense resistor from V <sub>CC</sub> to SENSE and the drain of the external n-channel MOSFET.                                                                                                                                      |

| 15  | DC              | Duty-Cycle Select. When DC is floating, the default duty cycle is 3.75%. Connect DC to V <sub>CC</sub> to set the duty cycle to 1.88%. Connect DC to GND to set the duty cycle to 0.94%.                                                                         |

| 16  | Vcc             | Power-Supply Input. Bypass V <sub>CC</sub> to GND with a 0.1µF capacitor. The input voltage range is from +9V to +80V for the MAX5934A and +33V to +80V for the MAX5934.                                                                                         |

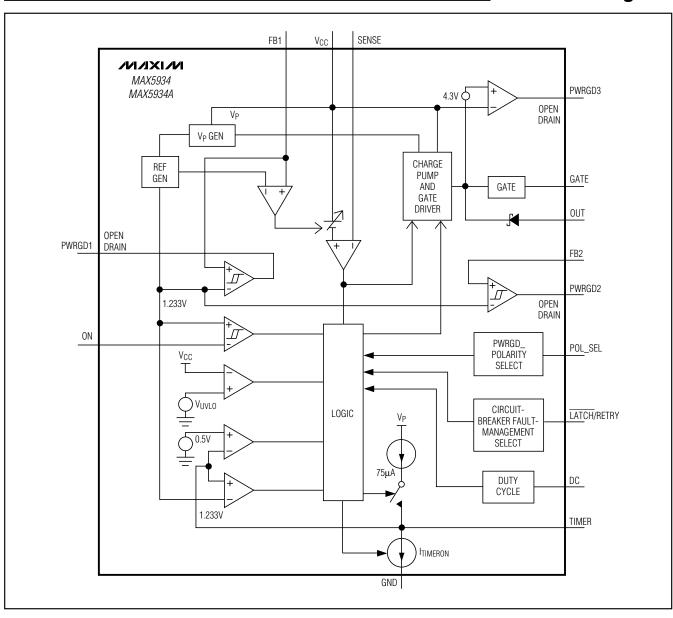

## **Functional Diagram**

### **Detailed Description**

The MAX5934/MAX5934A are fully integrated hot-swap controllers for positive supply rails. These devices allow for the safe insertion and removal of circuit cards into live backplanes without causing glitches on the backplane power-supply rail. During startup, the MAX5934/MAX5934A act as current regulators using an external sense resistor and MOSFET to limit the amount of current drawn by the load.

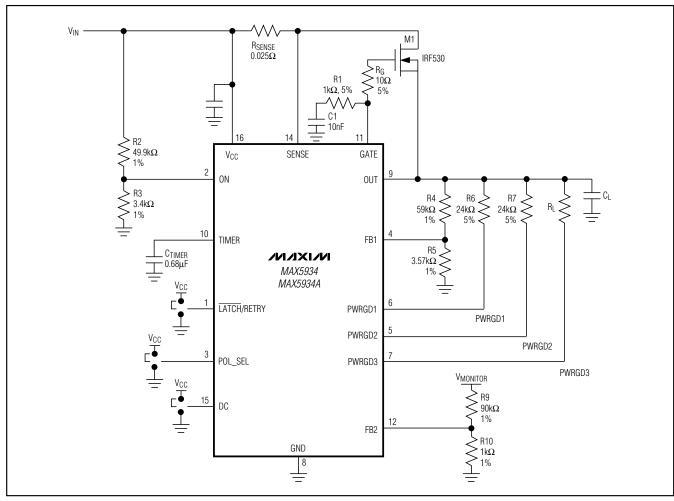

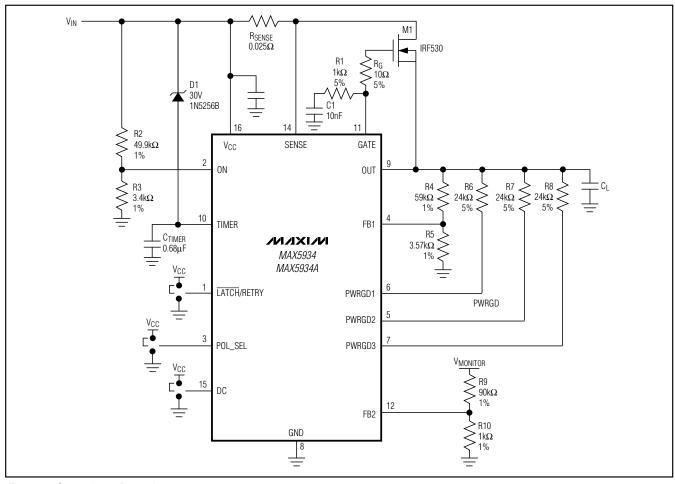

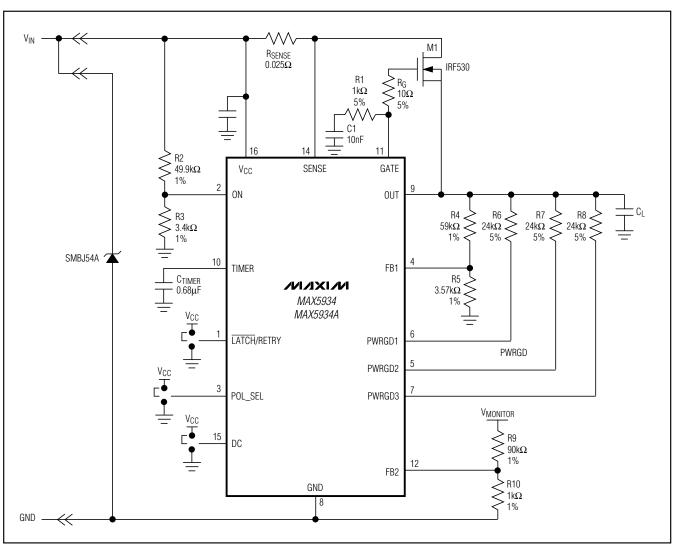

The MAX5934A operates from a +9V to +80V supply voltage range and has a default UVLO set to +8.3V. The MAX5934 operates from a +33V to +80V supply voltage range and has a default UVLO set to +31V. The UVLO threshold is adjustable using a resistive divider connected from  $V_{CC}$  to ON to GND (see R2 and R3 in Figure 5).

The MAX5934/MAX5934A monitor input voltage, output voltage, output current, and die temperature. These devices feature three power-good outputs (PWRGD\_) to indicate status by monitoring the voltage at FB1, FB2, and GATE (see the *Power-Good (PWRGD\_) Detection* section). PWRGD1 indicates an output-voltage status, PWRGD2 can be used to indicate an over-voltage condition on the main power-supply rail, and PWRGD3 asserts when GATE voltage has charged to 4.3V above the supply rail. PWRGD3 deasserts when the TIMER voltage exceeds a 1.233V threshold in response to an extended fault condition.

The MAX5934/MAX5934A control gate voltage on the external MOSFET to limit load current at startup and at overload to a value determined as:

Figure 5. Application Circuit

$$I_{LOAD} = \frac{V_{SENSETRIP}}{R_{SENSE}}$$

where:

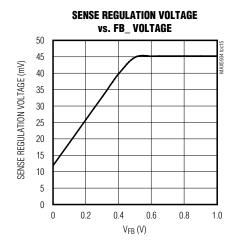

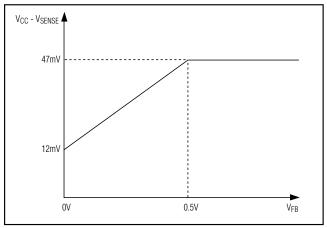

VSENSETRIP = VIN - VSENSE

VSENSETRIP varies from a low of 12mV when the voltage at FB1 = 0V and increases to 47mV as the voltage at FB1 increases to 0.5V and beyond (see Figure 6). Thus, the current limit is low at a low output voltage, and increases as the output voltage reaches its final value. This gradually increases the limiting load current at startup and creates a foldback current limit under overload or short-circuit conditions. See Figure 5 for FB1 and RSENSE connections.

#### **Power-Up Mode**

During power-up, the MAX5934/MAX5934A gradually turn on the external n-channel MOSFETs. The MAX5934/MAX5934A monitor and provide current-limit protection to the load at all times. The current limit is programmable using an external current-sense resistor connected from VCC to SENSE. The MAX5934/MAX5934A feature current-limit foldback and duty-cycle limit to ensure robust operation during load-fault and short-circuit conditions (see the *Detailed Description* and *Overcurrent Protection* sections).

#### **TIMER**

Connect an external capacitor from TIMER to ground to set the maximum overcurrent timeout limit. When the voltage at TIMER reaches 1.233V, GATE goes low and the 75µA pullup current turns off (see the *Functional Diagram*). As a result, a preset pulldown current (ITIMERON) discharges the capacitor. To reset the internal fault latch, these two conditions must be met:

Figure 6. Current-Limit Sense Voltage vs. Feedback Voltage

- 1) TIMER's voltage goes below 0.5V

- 2) ON goes low

When the current limit is not active, TIMER goes low by the ITIMERON current source. After the current limit becomes active, the ITIMEROFF pullup current source is connected to TIMER and the voltage rises with a slope of 75µA/CTIMER as long as the current limit remains active. A capacitor from TIMER to GND (CTIMER) sets the desired current-limit timeout:

$$T_{LIMIT} = (C_{TIMER} / 75\mu A) \times 1.233V$$

#### GATE

GATE provides a high-side gate drive for the external n-channel MOSFET. An internal charge-pump circuit guarantees at least 10V of gate drive for supply voltages higher than 20V (MAX5934A) and a 4.5V gate drive for supply voltages between 10.8V and 20V (MAX5934A) (for the MAX5934, see the *Electrical Characteristics* table). Connect an external capacitor from GATE to ground to set the rising slope of the voltage at GATE.

The voltage at GATE is adjusted to maintain a constant voltage across RSENSE when the current limit is reached while the TIMER capacitor starts to charge. When the voltage at TIMER exceeds 1.233V, the voltage at GATE goes low.

The MAX5934/MAX5934A monitor voltages at ON, V<sub>CC</sub>, and TIMER. GATE is pulled to GND whenever ON goes low, or the V<sub>CC</sub> supply voltage decreases below the UVLO threshold, or TIMER increases above the 1.233V threshold.

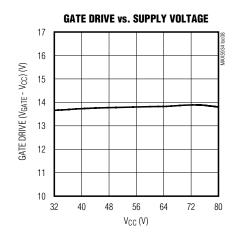

#### Gate Voltage

The Gate Drive vs. Supply Voltage graph in the *Typical Operating Characteristics* illustrates that GATE clamps to a maximum of 18V above the input voltage. The MAX5934 minimum gate-drive voltage is 10V at a minimum input-supply voltage of 33V. The MAX5934A minimum gate-drive voltage is 4.5V at a minimum supply of 10.8V. Therefore, a logic-level MOSFET must be used if the input supply is below 20V.

#### Fault Management (LATCH/RETRY)

The MAX5934/MAX5934A feature either latched-off or autoretry fault management configurable by the LATCH/RETRY input. To select automatic restart after a circuit-breaker fault, drive LATCH/RETRY high (above VLRIH) or leave it floating (see Figure 5).

In latch mode, the MAX5934/MAX5934A turn the MOSFET off and keep it off after an overcurrent fault. After the fault condition goes away and TIMER falls below 0.5V, recycle the power supplies or toggle ON low and high again to unlatch the device.

In autoretry mode, the MAX5934/MAX5934A turn the MOSFET off after an overcurrent fault occurs. After the fault condition is removed, the device waits for TIMER to fall below 0.5V and then automatically restarts. If the fault is due to an overtemperature condition, the MAX5934/MAX5934A wait for the die temperature to cool down below the +130°C threshold before restarting.

#### Power-Good (PWRGD\_ ) Detection

The MAX5934/MAX5934A feature three power-good outputs (PWRGD\_) to indicate the status of three separate voltages. PWRGD\_ asserts if the device detects an error condition.

PWRGD\_ is true when FB\_ voltages exceed the low-to-high threshold voltage (VFB\_H). PWRGD\_ is false when FB\_ voltages go lower than the high-to-low threshold voltage (VFB\_L).

Connect external pullup resistors between PWRGD\_ and OUT to pull up the PWRGD\_ voltages to Vout.

PWRGD2 can be used to indicate an overvoltage condition on the main power-supply rail.

PWRGD3 asserts when GATE voltage has charged to 4.3V above the supply rail. PWRGD3 deasserts when the TIMER voltage exceeds 1.233V threshold in response to an extended fault condition.

The output polarity of PWRGD\_ is determined by POL\_SEL. Drive POL\_SEL high or leave it floating to select PWRGD\_ active high. Connect POL\_SEL to GND for PWRGD\_ active low.

#### **Undervoltage Lockout (UVLO)**

The MAX5934A operates from a +9V to +80V supply voltage range and has a default UVLO set at +8.3V. The MAX5934 operates from a +33V to +80V supply voltage range and has a default UVLO set at +31V. The UVLO thresholds are adjustable using a resistive divider connected to VCC (see R2 and R3 in Figure 5). When the input voltage (or VCC) is below the UVLO threshold, the MOSFET is held off. When the input voltage (or VCC) is above the UVLO threshold, the MAX5934/MAX5934A go into normal operation (or begin to turn on the external MOSFET).

To adjust the UVLO threshold, connect an external resistive divider from  $V_{IN}$  (or  $V_{CC}$ ) to ON and then from ON to GND. The following equation is used to calculate the new UVLO threshold:

$V_{UVLO\_TH} = V_{REF} (1 + (R2 / R3))$  where  $V_{REF}$  is typically 1.233V.

### Applications Information

#### **Hot-Circuit Insertion**

The supply bypass capacitors on a circuit board can draw high peak currents from the backplane power bus as they charge when the circuit boards are inserted into a live backplane. This can cause permanent damage to the connector pins and glitch the system supply causing other boards in the system to reset.

The MAX5934/MAX5934A are capable of controlling a board's power-supply voltage allowing for the safe insertion or removal of a board from a live backplane. These devices provide undervoltage and overcurrent protection and power-good output signals (PWRGD\_).

#### **Overcurrent Protection**

The MAX5934/MAX5934A provide sophisticated overcurrent protection to ensure robust operation under output-current-transient and overcurrent fault conditions. The current-protection circuit employs a foldback current limit and a short-circuit or excessive output-current protection.

The MAX5934/MAX5934A offer a current foldback feature where the current folds back as a function of the output voltage that is sensed at FB1. As Figure 6 illustrates, the voltage across R<sub>SENSE</sub> decreases linearly when FB1 drops below 0.5V and stops at 12mV when  $V_{FB1} = 0V$ . The maximum current-limit equation is:

ILIMIT = 47mV / RSENSE

For RSENSE =  $0.025\Omega$ , the current limit is set to 1.88A and goes down to 480mA at short circuit (output shorted to GND).

In addition, the MAX5934/MAX5934A feature an adjustable overcurrent response time. The required time to regulate the MOSFET current depends on the input capacitance of the MOSFET, GATE capacitor (C1), compensation resistor (R1), and the internal delay from SENSE to GATE. Figure 7 shows the propagation delay from a voltage step at SENSE until GATE starts to fall, as a function of overdrive.

Figure 7. Response Time to Overcurrent

#### **Undervoltage and Overvoltage Detection**

An undervoltage fault is detected when  $V_{ON}$  goes below the trip point ( $V_{ONL} = 1.233V$ ). When this occurs, GATE pulls low and stays low until  $V_{ON}$  rises above ( $V_{ONH} = 1.313V$ ).

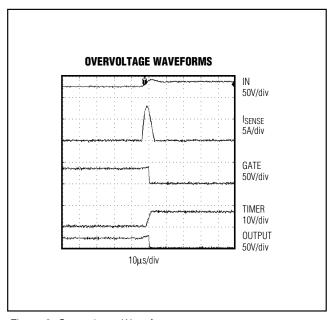

An example of overvoltage protection is shown in Figure 8. Zener diode D1 turns on when V<sub>IN</sub> exceeds the diode's breakdown voltage and begins to pull TIMER high. When V<sub>TIMER</sub> goes higher than 1.233V, a fault is detected and GATE pulls low. As a result, Q1 turns off. Figure 9 shows overvoltage waveforms for V<sub>IN</sub> (see the *Fault Management (LATCH/RETRY)* section for restart conditions).

#### **Supply Transient Protection**

The MAX5934/MAX5934A are guaranteed to be safe from damage with supply voltages of up to 85V. Spikes at voltages above 85V may damage the part. Instantaneous short-circuit conditions, can cause large

Figure 8. Overvoltage Detection

Figure 9. Overvoltage Waveforms

changes in currents flowing through the power-supply traces. This can cause inductive voltage spikes that could exceed 85V. Use wider traces or heavier trace plating and connect a  $0.1\mu F$  capacitor between  $V_{CC}$  and GND to minimize these inductive spikes. Use a transient voltage suppressor (TVS) at the input to prevent damage from voltage surges. An SMBJ54A is recommended.

#### **Power-Up Sequence**

At power-up, transistor Q1 (see the *Typical Application Circuit*) is off until these three conditions are met:

- Von exceeds the turn-on threshold voltage

- VCC exceeds the UVLO threshold

- VTIMER stays below 1.233V

The voltage at GATE increases with a slope of  $10\mu\text{A/C1}$  (where C1 is shown in the *Typical Application Circuit*) and I<sub>INRUSH</sub> = C<sub>L</sub> x  $10\mu\text{A}$  / C1. When the voltage across RSENSE goes too high, the inrush current is limited by the internal current-limit circuitry that adjusts the GATE voltage to keep a constant voltage across RSENSE.

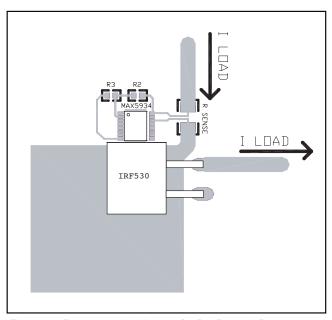

Figure 10. Recommended Layout for R2, R3, and RSENSE

### Thermal Shutdown

If the MAX5934/MAX5934A die temperature reaches +150°C, an overtemperature fault is generated. As a result, GATE goes low and turns the external MOSFET off. The MAX5934/MAX5934A die temperature must cool down below +120°C before the overtemperature fault condition is removed.

#### **Board Layout and Bypassing**

Kelvin connections are recommended for accurate current sensing. Make sure the minimum trace width for 2oz copper is 1.5mm per amp. A width of 4mm per amp is recommended.

Connect a resistive divider from  $V_{CC}$  to ON as close as possible to ON and have short traces from  $V_{CC}$  and GND. To decrease induced noise connect a  $0.1\mu F$  capacitor between ON and GND (see Figure 10).

The external MOSFET must be thermally coupled to the MAX5934/MAX5934A to ensure proper thermal shutdown operation.

## **Typical Application Circuit**

\_Chip Information

TRANSISTOR COUNT: 1573

PROCESS: BiCMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru 4 moschip.ru 9