# Three-Channel, Closed-Loop, Switch Mode LED Drive IC

#### **Features**

- Switch mode controller for single-switch converters

- · Closed loop control of output current

- Buck

- Boost

- SEPIC

- · High PWM dimming ratio

- · Internal 40V linear regulator

- · Constant frequency operation

- · Programmable slope compensation

- · Linear and PWM dimming

- +0.2A/-0.4A gate drives for the switching FETs

- · Output short circuit protection

- · Output over voltage protection

- · Hiccup-mode protection

- · Analog control of PWM dimming

#### **Applications**

- · RGB backlight applications

- · Multiple string, white-LED driver applications

#### Description

HV9982 is a three-channel, closed loop, peak-current mode PWM controller designed to drive a constant output current. It can be used for driving either RGB LEDs or multiple channels of white LEDs.

HV9982 includes a 40V linear regulator which provides an 8.0V supply to power the IC. The switching frequencies of the three converters are controlled by an external clock signal. The channels operate at a switching frequency of 1/12th of the external clock frequency and are positioned 120° out-of-phase to reduce the input current ripple. Each converter is driven by a peak current mode controller with output current feedback.

The three output currents can be individually dimmed using either linear or PWM dimming. The IC also includes three disconnect FET drivers, which enable high PWM-dimming ratios and also help to disconnect the input in case of an output short-circuit condition. HV9982 includes a Hiccup-mode protection for both open LED and short-circuit condition with automatic recovery when the fault clears.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### Pin Diagram

#### **Typical Application Circuit**

# 1.0 ELECTRICAL CHARACTERISTICS

#### **ABSOLUTE MAXIMUM RATINGS †**

| V <sub>IN</sub> to GND                             | 0.5V to +45V              |

|----------------------------------------------------|---------------------------|

| V <sub>DD</sub> to GND, V <sub>DD</sub> 1-3 to GND | 0.3V to +10V              |

| All other pins to GND                              | 0.3V to $(V_{DD} + 0.3V)$ |

| Operating temperature                              | 40°C to +125°C            |

| Storage temperature                                | 65°C to +150°C            |

| Continuous power dissipation (T <sub>A</sub> =     | +25°C)5000 mW             |

† Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operational listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 1.1 ELECTRICAL SPECIFICATIONS

TABLE 1-1: ELECTRICAL CHARACTERISTICS (SHEET 1 OF 3)<sup>1</sup>

| TABLE 1-1. ELECTRICAL CHARACTERISTICS (CHEET 1 OF 3) |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |                                                                                                                                                                                                                                                                    |                         |                         |                                                                                                  |  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter                                            | Note                                                                                                                                                                                                                                                                                                                                                                                                                | Min                                                                    | Тур                                                                                                                                                                                                                                                                | Max                     | Units                   | Conditions                                                                                       |  |  |  |  |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |                                                                                                                                                                                                                                                                    |                         |                         |                                                                                                  |  |  |  |  |

| Input DC supply voltage                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                                     | -                                                                                                                                                                                                                                                                  | 40                      | V                       | DC input voltage                                                                                 |  |  |  |  |

| Shut-down mode supply current                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | -                                                                                                                                                                                                                                                                  | 500                     | μA                      | EN ≤ 0.8V                                                                                        |  |  |  |  |

| Supply current                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | -                                                                                                                                                                                                                                                                  | 4.5                     | mA                      | EN ≥ 2.0V; PWMD1 = PWMD2<br>= PWMD3 = GND                                                        |  |  |  |  |

| Pull-down resistor                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                                     | 130                                                                                                                                                                                                                                                                | 160                     | kΩ                      | V <sub>EN</sub> = 5.0V                                                                           |  |  |  |  |

| gulator                                              |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |                                                                                                                                                                                                                                                                    |                         |                         |                                                                                                  |  |  |  |  |

| Internally regulated voltage                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | 7.25                                                                   | 7.75                                                                                                                                                                                                                                                               | 8.25                    | V                       | V <sub>IN</sub> = 12-40V; EN = HIGH;<br>PWMD1-3 = V <sub>DD</sub> ; GATE1-3 =<br>1nF; CLK = 6MHz |  |  |  |  |

| V <sub>DD</sub> under voltage lockout threshold      | -                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.0                                                                    | -                                                                                                                                                                                                                                                                  | 6.5                     | V                       | V <sub>DD</sub> falling                                                                          |  |  |  |  |

| V <sub>DD</sub> under voltage hysteresis             | -                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | 500                                                                                                                                                                                                                                                                | -                       | mV                      | V <sub>DD</sub> rising                                                                           |  |  |  |  |

| ing (PWMD1, PWMD2 and P\                             | VMD3)                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |                                                                                                                                                                                                                                                                    |                         |                         |                                                                                                  |  |  |  |  |

| PWMD input low voltage                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | -                                                                                                                                                                                                                                                                  | 0.8                     | V                       |                                                                                                  |  |  |  |  |

| PWMD input high voltage                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.0                                                                    | -                                                                                                                                                                                                                                                                  | -                       | V                       |                                                                                                  |  |  |  |  |

| PWMD pull down resistor                              | •                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                                     | 130                                                                                                                                                                                                                                                                | 160                     | kΩ                      | V <sub>PWMD</sub> = 5.0V                                                                         |  |  |  |  |

| 1, GATE2 and GATE3)                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |                                                                                                                                                                                                                                                                    |                         |                         |                                                                                                  |  |  |  |  |

| Gate short circuit current, sourcing                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.2                                                                    | -                                                                                                                                                                                                                                                                  | -                       | Α                       | V <sub>GATE</sub> = 0V                                                                           |  |  |  |  |

| Gate sinking current                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.4                                                                    | -                                                                                                                                                                                                                                                                  | -                       | Α                       | V <sub>GATE</sub> = VDD                                                                          |  |  |  |  |

| Gate output rise time                                | -                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | -                                                                                                                                                                                                                                                                  | 85                      | ns                      | C <sub>GATE</sub> = 1.0nF                                                                        |  |  |  |  |

| Gate output fall time                                | -                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | -                                                                                                                                                                                                                                                                  | 45                      | ns                      | C <sub>GATE</sub> = 1.0nF                                                                        |  |  |  |  |

| Maximum duty cycle                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                      | 91.7                                                                                                                                                                                                                                                               | -                       | %                       |                                                                                                  |  |  |  |  |

|                                                      | Input DC supply voltage Shut-down mode supply current Supply current Pull-down resistor Internally regulated voltage  V <sub>DD</sub> under voltage lockout threshold V <sub>DD</sub> under voltage hysteresis Ing (PWMD1, PWMD2 and PV PWMD input low voltage PWMD input high voltage PWMD pull down resistor 1, GATE2 and GATE3) Gate short circuit current, sourcing Gate output rise time Gate output fall time | Input DC supply voltage  Shut-down mode supply current  Supply current | Input DC supply voltage 1 10 Shut-down mode supply current Supply current  Pull-down resistor - 75  Internally regulated voltage 1 7.25  VDD under voltage lockout threshold  VDD under voltage hysteresis  Ing (PWMD1, PWMD2 and PWMD3)  PWMD input low voltage 1 | Input DC supply voltage | Input DC supply voltage | Input DC supply voltage                                                                          |  |  |  |  |

**Note 1:** Applies over the full operating ambient temperature range of  $0^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$ .

<sup>2:</sup> For design guidance only.

TABLE 1-1: ELECTRICAL CHARACTERISTICS (CONTINUED) (SHEET 2 OF 3)<sup>1</sup>

| Symbol                  | Parameter                                                  | Note                 | Min                  | Тур  | Max      | Units | Conditions                           |

|-------------------------|------------------------------------------------------------|----------------------|----------------------|------|----------|-------|--------------------------------------|

| Over-voltag             | e Protection (OVP1, OVP2 ar                                | nd OVP3              | 3)                   | I    |          |       |                                      |

| V <sub>OVP,rising</sub> | Over voltage rising trip point                             | 1                    | 4.5                  | 5.0  | 5.5      | V     | OVP rising                           |

| V <sub>OVP,HYST</sub>   | Over voltage hysteresis                                    | -                    | -                    | 0.5  | -        | V     | OVP falling                          |

| Current Sen             | ise (CS1, CS2 and CS3)                                     |                      |                      |      | •        | •     |                                      |

| T <sub>BLANK</sub>      | Leading edge blanking                                      | 1                    | 100                  | _    | 250      | ns    |                                      |

| T <sub>DELAY</sub>      | Delay to output of gate                                    | 1                    | -                    | -    | 200      | ns    | 100mV overdrive to the current sense |

| R <sub>DIS</sub>        | Discharge resistance for slope compensation                | 1                    | -                    | -    | 650      | Ω     | Gate = Low                           |

| Internal Tra            | nsconductance Opamp (G <sub>m1</sub>                       | , G <sub>m2</sub> ar | nd G <sub>m3</sub> ) |      |          |       |                                      |

| GB                      | Gain bandwidth product                                     | 2                    | -                    | 1.0  | -        | MHz   | 75pF capacitance at COMP pir         |

| A <sub>V</sub>          | Open loop DC gain                                          | -                    | 65                   | -    | -        | dB    | Output open                          |

| V <sub>CM</sub>         | Input common-mode range                                    | 2                    | -0.3                 | -    | 3.0      | V     |                                      |

| Vo                      | Output voltage range                                       | 2                    | 0.7                  | -    | $V_{DD}$ | V     |                                      |

| G <sub>m</sub>          | Transconductance                                           |                      | 500                  | 600  | 700      | μA/V  |                                      |

| V <sub>OFFSET</sub>     | Input offset voltage                                       | -                    | -5.0                 | -    | 5.0      | mV    |                                      |

| I <sub>BIAS</sub>       | Input bias current                                         | 2                    | -                    | 0.5  | 1.0      | nA    |                                      |

| Oscillator (0           | CLOCK)                                                     |                      |                      |      |          |       |                                      |

| f <sub>OSC1</sub>       | Oscillator frequency                                       | -                    | -                    | 500  | -        | kHz   | F <sub>CLOCK</sub> = 6.0MHz          |

| K <sub>SW</sub>         | Oscillator divider ratio                                   | 2                    | -                    | 12   | -        | -     |                                      |

| Phi1                    | GATE1 - GATE2 phase delay                                  | 2                    | -                    | 120  | -        | 0     |                                      |

| Phi1                    | GATE1 - GATE3 phase delay                                  | 2                    | -                    | 240  | -        | 0     |                                      |

| T <sub>OFF</sub>        | CLOCK low time                                             | 2                    | 50                   | -    | -        | ns    |                                      |

| $T_{ON}$                | CLOCK high time                                            | 2                    | 50                   | -    | -        | ns    |                                      |

| $V_{CLOCK,HI}$          | CLOCK input high                                           | 1                    | 2.0                  | -    | -        | V     |                                      |

| $V_{CLOCK,LO}$          | CLOCK input low                                            | 1                    | -                    | -    | 8.0      | V     |                                      |

| Disconnect              | Driver (FLT1, FLT2 and FLT3                                | )                    |                      |      |          |       |                                      |

| T <sub>RISE,FAULT</sub> | Fault output rise time                                     | -                    | -                    | -    | 450      | ns    | 330pF capacitor at FAULT pin         |

| T <sub>FALL,FAULT</sub> | Fault output fall time                                     | -                    | -                    | -    | 200      | ns    | 330pF capacitor at FAULT pin         |

| ·                       | it Protection (all three chann                             | els)                 |                      |      | •        | •     |                                      |

| T <sub>BLANK,SC</sub>   | Blanking time                                              | 1                    | 400                  | -    | 700      | ns    |                                      |

| G <sub>SC</sub>         | Gain for short circuit comparator                          | -                    | 1.85                 | 2.00 | 2.15     | -     |                                      |

| V <sub>omin</sub>       | Minimum current limit threshold                            | 2                    | 0.15                 | -    | 0.25     | V     | REF = GND                            |

| T <sub>OFF</sub>        | Propagation time for short circuit detection               | -                    | -                    | -    | 250      | ns    | FDBK = 2 • REF + 0.1V                |

| HICCUP tim              | er                                                         |                      |                      | •    |          |       | •                                    |

| I <sub>HC,SOURCE</sub>  | Current source at SKIP pin used for hiccup mode protection | -                    | -                    | 10   | -        | μA    |                                      |

**Note 1:** Applies over the full operating ambient temperature range of  $0^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$ .

**<sup>2:</sup>** For design guidance only.

### TABLE 1-1: ELECTRICAL CHARACTERISTICS (CONTINUED) (SHEET 3 OF 3)<sup>1</sup>

| Symbol                  | Parameter                                           | Note | Min | Тур  | Max | Units | Conditions                |

|-------------------------|-----------------------------------------------------|------|-----|------|-----|-------|---------------------------|

| V <sub>TH(H)</sub>      | High threshold at SKIP pin                          | 2    | -   | 5.0  | -   | V     |                           |

| $V_{TH(L)}$             | Low threshold at SKIP pin                           | 2    | 1   | 0.1  | 1   | V     |                           |

| C <sub>RAMP</sub> for A | C <sub>RAMP</sub> for Analog Control of PWM Dimming |      |     |      |     |       |                           |

| F <sub>RAMP,min</sub>   | Minimum frequency                                   | -    | -   | 110  | -   | Hz    | C <sub>RAMP</sub> = 10nF  |

| F <sub>RAMP,max</sub>   | Maximum frequency                                   | -    | -   | 1250 | -   | Hz    | C <sub>RAMP</sub> = 1.0nF |

**Note 1:** Applies over the full operating ambient temperature range of  $0^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$ .

#### TABLE 1-2: THERMAL RESISTANCE

| Package     | θја    |

|-------------|--------|

| 40-Lead QFN | 24°C/W |

<sup>2:</sup> For design guidance only.

#### 2.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN DESCRIPTION (SHEET 1 OF 2)

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDD1  | Power supply pin for channel 1. It can either be connected to the VDD pin or supplied with an external power supply. It must be bypassed with a low ESR capacitor to GND1 (at least 0.1 $\mu$ F). All VDD pins (VDD, VDD1-3) must be connected together externally. An external supply (7.0-9.0V) can be connected to these pins to power the IC if the internal regulator is not used. |

| 2     | FLT1  | Used to drive an external disconnect switch. The disconnect switch is used to protect the LEDs in case of fault conditions and also help to provide excellent PWM dimming response by disconnecting and reconnecting the LEDs from the output capacitor during PWM dimming.                                                                                                             |

| 3     | CS1   | Used to sense the source current of the external power FET used with channel 1. It includes a built-in 100 ns (min) blanking timer. An R-C network at this pin programs the slope compensation. Refer to the Slope Compensation section for additional information.                                                                                                                     |

| 4     | COMP1 | Stable closed loop control for channel 1 can be accomplished by connecting a compensation network between each COMP1 pin and GND1.                                                                                                                                                                                                                                                      |

| 5     | FDBK1 | Output current feedback input for channel 1. It receives a voltage signal from an external sense resistor.                                                                                                                                                                                                                                                                              |

| 6     | REF1  | The voltage at this pin sets the output current level for channel 1. Recommended voltage range for this pin is 0-1.25V.                                                                                                                                                                                                                                                                 |

| 7     | OVP1  | Provides the over-voltage protection for the channel 1. When the voltage at this pin exceeds 5.0V, the HV9982 is turned off and the fault timer starts. Upon completion of the fault timer the IC attempts to restart.                                                                                                                                                                  |

| 8     | VIN   | Input of the internal 40V linear regulator.                                                                                                                                                                                                                                                                                                                                             |

| 9     | VDD   | Output of the linear regulator. It maintains a regulated 7.75V as long as the voltage of the VIN pin is between 10 and 40V. It must be bypassed with a low ESR capacitor to GND (at least $0.1  \mu\text{F}$ ). Can be used as a power supply for the three channels.                                                                                                                   |

| 10    | EN    | When pin is pulled below 0.8V, the IC goes into a standby mode and draws minimal current.                                                                                                                                                                                                                                                                                               |

| 11    | GND   | Ground connection for the common circuitry in the HV9982.                                                                                                                                                                                                                                                                                                                               |

| 12    | COMP2 | Stable closed loop control for channel 2 can be accomplished by connecting a compensation network between each COMP2 pin and GND2.                                                                                                                                                                                                                                                      |

| 13    | REF2  | The voltage at this pin sets the output current level for channel 2. Recommended voltage range for this pin is 0-1.25V.                                                                                                                                                                                                                                                                 |

| 14    | OVP2  | Provides the over voltage protection for the channel 2. When the voltage at this pin exceeds 5.0V, the HV9982 is turned off and the fault timer starts. Upon completion of the fault timer the IC attempts to restart.                                                                                                                                                                  |

| 15    | SKIP  | Programs the hiccup timer for fault conditions. A capacitor to GND programs the hiccup time.                                                                                                                                                                                                                                                                                            |

| 16    | RAMP  | Provides a ramp signal which is used while dimming the channels with pulse-width modulation with an analog input. A capacitor to GND programs the PWM-dimming frequency.                                                                                                                                                                                                                |

| 17    | PWMD1 | PWM dimming of the three channels is accomplished by using the PWMD pins. If S1 is                                                                                                                                                                                                                                                                                                      |

| 18    | PWMD2 | LOW, then the three pins directly control the PWM dimming of the three channels and a                                                                                                                                                                                                                                                                                                   |

| 19    | PWMD3 | square wave input should be applied at these pins. If S1 is high, then a 0-2.0V analog signal should be applied at these pins. The PWM dimming is then done by comparing the analog voltage to the voltage at the RAMP pin.                                                                                                                                                             |

| 20    | S1    | Digital input pins which select the operating mode of the PWMD inputs. Refer to the                                                                                                                                                                                                                                                                                                     |

| 21    | S2    | PWM dimming section for additional information.                                                                                                                                                                                                                                                                                                                                         |

| 22    | NC    | No connect.                                                                                                                                                                                                                                                                                                                                                                             |

# HV9982

TABLE 2-1: PIN DESCRIPTION (CONTINUED) (SHEET 2 OF 2)

| Pin# | Name  | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23   | CLK   | Clock input for the HV9982. The input to the CLK pin should be a TTL compatible square wave signal. The three channels will switch at 1/12th the switching frequency of the signal applied at the CLK pin.                                                                                                                                                                              |

| 24   | OVP3  | Provides the over voltage protection for the channel 3. When the voltage at this pin exceeds 5.0V, the HV9982 is turned off and the fault timer starts. Upon completion of the fault timer the IC attempts to restart.                                                                                                                                                                  |

| 25   | REF3  | The voltage at this pin sets the output current level for channel 3. Recommended voltage range for this pin is 0-1.25V.                                                                                                                                                                                                                                                                 |

| 26   | FDBK3 | Output current feedback input for channel 3. It receives a voltage signal from an external sense resistor.                                                                                                                                                                                                                                                                              |

| 27   | COMP3 | Stable closed loop control for channel 3 can be accomplished by connecting a compensation network between each COMP3 pin and GND3.                                                                                                                                                                                                                                                      |

| 28   | CS3   | Used to sense the source current of the external power FET used with channel 3. It includes a built-in 100 ns (min) blanking timer. An R-C network at this pin programs the slope compensation. Refer to the Slope Compensation section for additional information.                                                                                                                     |

| 29   | FLT3  | Used to drive an external disconnect switch. The disconnect switch is used to protect the LEDs in case of fault conditions and also help to provide excellent PWM-dimming response by disconnecting and reconnecting the LEDs from the output capacitor during PWM dimming.                                                                                                             |

| 30   | VDD3  | Power supply pin for channel 3. It can either be connected to the VDD pin or supplied with an external power supply. It must be bypassed with a low ESR capacitor to GND3 (at least 0.1 $\mu$ F). All VDD pins (VDD, VDD1-3) must be connected together externally. An external supply (7.0-9.0V) can be connected to these pins to power the IC if the internal regulator is not used. |

| 31   | GATE3 | Output gate drive for an external N-channel power MOSFET.                                                                                                                                                                                                                                                                                                                               |

| 32   | GND3  | Ground return for channel 3. It is recommended that all the GNDs of the IC be connected together in a STAR connection at the input GND terminal to ensure best performance.                                                                                                                                                                                                             |

| 33   | VDD2  | Power supply pin for channel 2. It can either be connected to the VDD pin or supplied with an external power supply. It must be bypassed with a low ESR capacitor to GND2 (at least 0.1 $\mu$ F). All VDD pins (VDD, VDD1-3) must be connected together externally. An external supply (7.0-9.0V) can be connected to these pins to power the IC if the internal regulator is not used. |

| 34   | GND2  | Ground return for channel 2. It is recommended that all the GNDs of the IC be connected together in a STAR connection at the input GND terminal to ensure best performance.                                                                                                                                                                                                             |

| 35   | GATE2 | Output gate drive for an external N-channel power MOSFET.                                                                                                                                                                                                                                                                                                                               |

| 36   | FLT2  | Used to drive an external disconnect switch. The disconnect switch is used to protect the LEDs in case of fault conditions and also help to provide excellent PWM-dimming response by disconnecting and reconnecting the LEDs from the output capacitor during PWM dimming.                                                                                                             |

| 37   | CS2   | Used to sense the source current of the external power FET used with channel 2. It includes a built-in 100 ns (min) blanking timer. An R-C network at this pin programs the slope compensation. Refer to the Slope Compensation section for additional information.                                                                                                                     |

| 38   | FDBK2 | Output current feedback input for channel 2. It receives a voltage signal from an external sense resistor.                                                                                                                                                                                                                                                                              |

| 39   | GND1  | Ground return for channel 1. It is recommended that all the GNDs of the IC be connected together in a STAR connection at the input GND terminal to ensure best performance.                                                                                                                                                                                                             |

| 40   | GATE1 | Output gate drive for an external N-channel power MOSFET.                                                                                                                                                                                                                                                                                                                               |

#### 3.0 FUNCTIONAL DESCRIPTION

#### 3.1 Power Topology

HV9982 is a three-channel, switch-mode converter LED driver designed to control a continuous conduction mode buck, boost or SEPIC converter in a constant frequency mode. The IC includes an internal linear regulator, which operates from input voltages 10V to 40V. The IC can also be powered directly using the VDD pins and bypassing the internal linear regulator. The IC includes features typically required in LED drivers such as open LED protection, output short circuit protection, linear and PWM dimming, programmable input current limiting, and accurate control of the LED current. A high current gate drive output enables the controller to be used in high power converters. The IC is ideally suited for backlight application using either RGB or multichannel white LED configurations.

# 3.2 Power Supply to the IC (VIN, VDD, VDD1-3)

HV9982 can be powered directly from its VIN pin which withstands a voltage up to 40V. When a voltage is applied at the VIN pin, the HV9982 tries to maintain a constant 7.75V (typ) at the VDD pin. The regulator also has a built in under-voltage lockout, which shuts off the IC if the voltage at the VDD pin falls below the UVLO threshold. By connecting this VDD pin to pins VDD1-3 of the other three channels, the internal regulator can be used to power all three channels in the IC.

If the internal regulator is not utilized, an external power supply (7.0-9.0V) can be used to power the IC. In this case, the power supply is directly connected to the VDD1-3 pins and the VIN pin is left unconnected.

All four VDD pins must by bypassed by a low ESR capacitor ( $\geq 0.1 \, \mu$ F) to provide a low impedance path for the high frequency current of the output gate driver. These capacitors must be referenced to the individual grounds for proper noise rejection (see 3.13 "Layout Considerations"). Also, in all cases, the four VDD pins must be connected together externally.

The input current drawn from the external power supply (or VIN pin) is a sum of the 4.5 mA (max) current drawn by all the internal circuitry and the current drawn by the gate drivers (which in turn depends on the switching frequency and the gate charge of the external FET).

$$I_{1N}$$

= 4.5mA +  $(Q_{g1} + Q_{g2} + Q_{g3}) \cdot f_s$

In the above equation,  $f_S$  is the switching frequency of the converters and  $Q_{g1-3}$  are the gate charges of the external FETs (which can be obtained from the FET data sheets).

The EN pin is a TTL-compatible input used to disable the IC. Pulling the EN pin to GND will shut down the IC and reduce the quiescent current drawn by the IC to be less than 500  $\mu$ A. If the enable function is not required, the EN pin can be connected to VDD.

#### 3.3 Clock Input (CLK)

The switching frequency of the converters is set by using a TTL-compatible square wave input at the CLK pin. The switching frequencies of the three converters will be 1/12<sup>TH</sup> the frequency of the external clock.

#### 3.4 Current Sense (CS1-3)

The current sense input is used to sense the source current of the switching FET. Each CS input of the HV9982 includes a built-in, 100 ns (minimum) blanking time to prevent spurious turn off due to the initial current spike when the FET turns on.

The IC includes an internal, resistor-divider network, which steps down the voltage at the COMP pins by a factor of 13. This voltage is used as the reference for the current sense comparators. Since the maximum voltage of the COMP pin is  $(V_{DD}-1.0V)$ , this voltage determines the maximum reference current for the current sense comparator, and thus the maximum inductor current.

The current sense resistor,  $R_{CS}$ , should be chosen so that the input inductor current is kept below the saturation current level of the input inductor. For discontinuous conduction mode of operation, no slope compensation is necessary. In this case, the current sense resistor is chosen as:

$$R_{CS} = \frac{V_{DD} - 1.0V}{13 \cdot I_{IN,pk}}$$

where I<sub>IN.pk</sub> is the maximum desired peak input current.

For continuous conduction mode converters operating in the constant frequency mode, slope compensation becomes necessary to ensure stability of the peak current mode controller, if the operating duty cycle is greater than 0.5. This factor must also be accounted for when determining  $R_{CS}$  (see 3.5 "Slope Compensation").

#### 3.5 Slope Compensation

Choosing a slope compensation, which is one half of the down slope of the inductor current, ensures that the converter will be stable for all duty cycles.

Slope compensation in the HV9982 can be programmed by two external components, see Figure 3-1. A resistor for  $V_{DD}$  sets a current, which is almost constant since the  $V_{DD}$  voltage is much larger than the voltage at the CS pin. This current flows into the capacitor and produces a ramp voltage across the capacitor. The voltage at the CS pin is then the sum of the voltage

across the capacitor and the voltage across the current sense resistor. The voltage across the capacitor provides the required slope compensation. When the GATE turns off, an internal pull down FET discharges the capacitor. The  $650\Omega$  resistance of the internal FET will prevent the voltage at the CS pin from going all the way to zero.

FIGURE 3-1: SLOPE COMPENSATION

The minimum value of the voltage will instead be:

$$V_{CS, MIN} = \frac{V_{DD}}{R_{SC}} \bullet 650\Omega$$

The slope compensation capacitor is chosen so that it can be completely discharged by the internal  $650\Omega$  FET at the CS pin during the time the FET is off. Assuming the worst case switch duty cycle of 92%,

$$C_{SC} = \frac{0.08}{3 \cdot 650 \Omega \cdot f_S}$$

Assuming a down slope of DS (A/ms) for the inductor current, the current sense resistor and the slope compensation resistor can be computed as:

$$R_{CS} = \frac{V_{DD} - 1}{13} \bullet \frac{1}{\left(\frac{DS \bullet 10^{6} \bullet 0.92}{2 \bullet f_{s}}\right) + I_{IN, pk}}$$

$$R_{SC} = \frac{2 \cdot V_{DD}}{DS \cdot 10^6 \cdot C_{SC} \cdot R_{CS}}$$

#### 3.6 Control of the LED Current

The LED currents in the HV9982 are controlled in a closed-loop manner. The current references which set the three LED currents are provided at the REF pins (REF1-3). This reference voltage is compared to the voltage at the FDBK1-3 pins which sense the LED currents in the three channels using current sense resistors. HV9982 includes three 1 MHz transconductance amplifiers with tri-state output, which are used to close the feedback loops and provide accurate current control. The compensation networks are connected at the COMP pins (COMP1-3).

The output of the op-amps are buffered and connected to the current sense comparators using a 12R:1R resistor divider. The outputs of the op-amps are controlled by the signal applied to the PWMD pins (PWMD1-3). When PWMD is high, the output of the op-amp is connected to the COMP pin. When PWMD is low, the output is left open. This enables the integrating capacitor to hold the charge when the PWMD signal has turned off the gate drive. When the IC is enabled, the voltage on the integrating capacitor will force the converter into steady state almost instantaneously.

#### 3.7 Linear Dimming

Linear Dimming can be accomplished in the HV9982 by varying the voltages at the REF pins. Note that since the HV9982 is a peak current mode controller, it has a minimum on-time for the GATE outputs. This minimum on-time will prevent the converters from completely turning off even when the REF pins are pulled to GND. Thus, linear dimming cannot accomplish true zero LED current. To get zero LED current, PWM dimming has to be used. Different signals can be connected to the three REF pins if desired and they need not be connected together.

Due to the offset voltage of the short circuit comparator as well as the non-linearity of the X2 gain stage, pulling the REF pin very close to GND would cause the internal short circuit comparator to trigger and shut down the IC. To overcome this, the output of the gain stage is limited to 125 mV (minimum), allowing the REF pin to be pulled all the way to 0V without triggering the short circuit comparator.

#### 3.8 PWM Dimming

PWM dimming in the HV9982 can be accomplished in one of two ways: true PWM dimming using TTL-compatible square wave sources at the PWMD pins (PWMD1-3), or an analog control of PWM dimming by applying a 0-2.0V linear signal to the PWMD pins. The analog control of PWM dimming helps the HV9982 to be backward compatible with CCFL controllers. All three channels can be individually PWM dimmed as desired.

The mode of PWM dimming is set using control pins S1 and S2. The truth table for S1 and S2 control is given in Table 3-1. It is recommended that the pins be connected to either VDD or GND and not left unconnected.

TABLE 3-1: S1 AND S2 CONTROL

| S1 | S2 | PWMD Output                                              |

|----|----|----------------------------------------------------------|

| 0  | 0  | The output will follow PWMD input signal                 |

| 0  | 1  | The output will follow PWMD input signal                 |

| 1  | 0  | Input DC zero volt corresponds to 100% duty cycle output |

| 1  | 1  | Input DC two volt corresponds to 100% duty cycle output  |

When S1 is high and the HV9982 is operating in the analog control of PWM dimming mode, the PWM dimming frequency is set by a capacitor connected at the RAMP pin. The RAMP frequency range is 100Hz-1.0kHz and the capacitor can be selected as:

$$f(H_Z) = \frac{1.0 \mu s}{C_{RAMP}}$$

Note:

In the following description of the PWMdimming performance the PWMD signals refer to the internal PWM dimming signal and not to the signal applied at the PWMD pins

When the PWM signal is high, the GATE and FLT pins are enabled and the output of the transconductance op-amp is connected to the external compensation network. Thus, the internal amplifier controls the output current. When the PWMD signal goes low, the output of the transconductance amplifier is disconnected from the compensation network. Thus, the integrating capacitor maintains the voltage across it. The GATE is disabled, so the converter stops switching and the FLT pin goes low, turning off the disconnect switch.

The output capacitor of the converter determines the PWM-dimming response of the converter, because it is charged and discharged whenever the PWMD signal goes high or low. In the case of a buck converter, since the inductor current is continuous, a very small capacitor is used across the LEDs. This minimizes the effect of the capacitor on the PWM-dimming response of the converter. However, in the case of a boost converter. the output current is discontinuous and a very large output capacitor is required to reduce the ripple in the LED current. Thus, this capacitor will have a significant impact on the PWM-dimming response. By turning off the disconnect switch when PWMD goes low, the output capacitor is prevented from being discharged and thus the PWM-dimming response of the boost converter Improves dramatically.

Disconnecting the LED load during PWM dimming causes the energy stored in the inductor to be dumped into the output capacitor. The filter capacitor should be chosen large enough so that it can absorb the inductor energy without significant change to the voltage across it.

#### 3.9 Fault Conditions

The HV9982 is a robust controller which can protect the LEDs and the LED driver in case of fault conditions. The HV9982 includes both open LED protection and output short circuit protection. In both cases, the HV9982 shuts down and attempts a restart. The hiccup time can be programmed by a single external capacitor at the SKIP pin.

During start-up, or when a fault condition is detected, both GATE and FLT outputs are disabled, the COMP pins and SKIP pins are pulled to GND. Once the volt-

age at the SKIP pin falls below 0.1V and the fault condition(s) have disappeared, the capacitor at the SKIP pin is released and is charged slowly by a 10 $\mu$ A current source. When the capacitor is charged to 5.0V, the COMP pins are released and GATE and FLT pins are allowed to turn on. If the hiccup time is long enough, it will ensure that the compensation networks are all completely discharged and that the converters start at minimum duty cycle.

The hiccup timing capacitor can be programmed as:

$$C_{RAMP} = \frac{10\,\mu\text{A} \bullet t_{\text{HICCUP}}}{4.9V}$$

#### 3.10 Short Circuit Protection

When a short circuit condition is detected (output current becomes higher than twice the steady state current), the GATE and FLT outputs are pulled low. As soon as the disconnect FET is turned off, the output current goes to zero and the short circuit condition disappears. At this time, the hiccup timer is started (Fig. 3). Once the timing is complete, the converter attempts to restart. If the fault condition still persists, the converter shuts down and goes through the cycle again. If the fault condition is cleared, due to a momentary output short, the converter will start regulating the output current normally. This allows the LED driver to recover from accidental shorts without having to reset the IC.

During short circuit conditions, there are two conditions that determine the hiccup time.

The first condition is the time required to discharge the compensation capacitors. Assuming a pole-zero R-C network at the COMP pin (series combination of  $R_Z$  and  $C_Z$  in parallel with  $C_C$ ),

$$t_{COMP,n} = 3 \cdot R_{Zn} \cdot C_{Zn}$$

where n refers to the channel number.

If the compensation networks are only type 1 (single capacitor), then:

$$t_{COMP,n} = 3 \cdot 650\Omega \cdot C_{Zn}$$

Thus, the maximum compensation time required can be computed as:

$$t_{COMP.max} = max(t_{COMP1}, t_{COMP2}, t_{COMP3})$$

The second condition is the time required for the inductors to completely discharge following a short circuit. This time can be computed as:

$$t_{\text{IND, N}} = \frac{\pi}{4} \sqrt{L_{\text{N}} \cdot C_{\text{ON}}}$$

where L and  $C_{\rm O}$  are the input inductor and output capacitor of each power stage.

Thus, the maximum time required to discharge the inductors can be computed as:

$$t_{IND, MAX} = max(t_{IND1}, t_{IND2}, t_{IND3})$$

The hiccup time is then chosen as:

$$t_{\text{HICCUP}} > \max(t_{\text{COMP, MAX}}, t_{\text{IND, MAX}})$$

# 3.11 False Triggering of the Short Circuit Comparator During PWM Dimming

During PWM dimming, the parasitic capacitance of the LED string causes a spike in the output current when the disconnect FET is turned on. If this spike is detected by the short circuit comparator, it will cause the IC to falsely detect an over current condition and shut down.

In the HV9982, to prevent these false triggers, there is a built in 500 ns blanking network for the short circuit comparator. This blanking network activates when the PWMD input goes high. Thus, the short circuit comparator will not see the spike in the LED current during the PWM Dimming turn-on transition. Once the blanking timer is completed, the short circuit comparator will start monitoring the output current. Thus, the total delay time for detecting a short circuit will depend on the condition of the PWMD input.

If the output short circuit exists before the PWM-dimming signal goes high, the total detection time will be:

$$t_{DETECT1} = t_{BLANK} + t_{DELAY} \approx 950 \text{ns}(\text{max})$$

If the short circuit occurs when the PWM dimming signal is already high, the time to detect will be:

$$t_{\text{DETECT1}} = t_{\text{DELAY}} \approx 250 \text{ns}(\text{max})$$

#### 3.12 Over-voltage Protection

The HV9982 provides hysteretic over voltage protection allowing the IC to recover in case the LED load is momentarily disconnected.

When the load is disconnected in a boost converter, the output voltage rises as the output capacitor starts charging. When the output voltage reaches the OVP rising threshold, the HV9982 detects an over voltage condition and turns off the converter. The converter is turned back on only when the output voltage falls below the falling OVP threshold (which is 10% lower than the rising threshold). This time is mostly dictated by the R-C time constant of the output capacitor CO and the resistor network used to sense over voltage (ROVP1+ ROVP2). In

case of a persistent open circuit condition, this cycle keeps repeating maintaining the output voltage within a 10% band.

In most designs, the lower threshold voltage of the over voltage protection ( $V_{OVP}-10\%$ ) at which point the HV9982 attempts to restart will be more than the LED string voltage. Thus, when the LED load is reconnected to the output of the converter, the voltage differential between the actual output voltage and the LED string voltage will cause a spike in the output current. This causes a short circuit to be detected and the HV9982 will trigger short circuit protection. This behavior continues till the output voltage becomes lower than the LED string voltage at which point, no fault will be detected and normal operation of the circuit will commence.

#### 3.13 Layout Considerations

For multi-channel peak current mode controller IC to work properly with minimum interference between the channels, it is important to have a good PCB layout which minimizes noise. Following the layout rules stated below will help to ensure proper performance of all three channels.

#### 1. GND connection

The IC has four separate ground connections – one for each of the three channels and one analog ground for the common circuitry. It is recommended that four separate ground planes be used in the PCB and all the GND planes be connected together at the return terminal of the input power lines.

#### 2. VDD Connection

Each VDD pin should be by passed with a low ESR capacitor to its OWN ground (i.e. VDD1 is bypassed to GND1 and so on). The common VDD pin can be bypassed to the common GND.

#### 3. REF Connection

If all the references are going to be driven from a single voltage source, it is recommended to have a small R-C low pass filter (1.0k, 1.0 nF) at each REF pin with the filter being referenced to the appropriate channel's ground (as in the case of the VDD pins). If the REF pins are driven with three individual voltage sources, then just a small capacitor (1.0 nF) at each pin would suffice.

#### 4. GATE and CS connection

The connection from GATE output to the gate of the external FET as well as the connection from the CS pin to the external sense resistor made as short as possible to avoid false triggering.

#### OVP protection

Typically, the OVP resistor dividers would be located away from the IC. To prevent false triggering of the IC due to noise at the OVP pin, a small bypass capacitor (1.0nF) right at the OVP pin is recommended.

FIGURE 3-2: **LAYOUT GUIDELINES** VDD Connection Input Return Terminal GND3 GND1 GND2 VDD2 VDD1 VDD3 Star Connection of GND HV9982 REF3 Reference REF1 RÉF Connection **GND Tab** Connection ≥

FIGURE 3-3: INTERNAL BLOCK DIAGRAM

#### 4.0 PACKAGING INFORMATION

#### 4.1 Package Marking Information

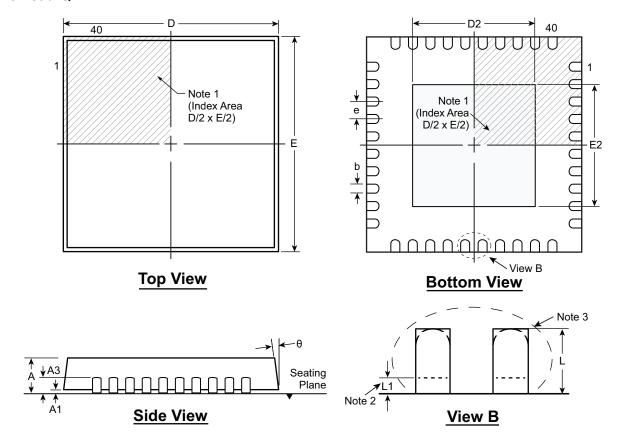

40-Lead QFN

Example

**Legend:** XX...X Product Code or Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

#### 40 Lead QFN

#### Notes:

- **1:** A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/ identifier; an embedded metal marker; or a printed indicator.

- 2: Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- **3:** The inner tip of the lead may be either rounded or square.

- **4:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Symb      | ol  | Α    | A1   | A3          | b    | D     | D2   | Е     | E2   | е           | L     | L1   | θ° |

|-----------|-----|------|------|-------------|------|-------|------|-------|------|-------------|-------|------|----|

| Dimension | MIN | 0.80 | 0.00 | 0.00        | 0.18 | 5.85* | 1.05 | 5.85* | 1.05 | 0.50        | 0.30† | 0.00 | 0  |

|           | NOM | 0.90 | 0.02 | 0.20<br>REF | 0.25 | 6.00  | -    | 6.00  | -    | 0.50<br>BSC | 0.40† | -    | -  |

| (mm)      | MAX | 1.00 | 0.05 | 11          | 0.30 | 6.15* | 4.45 | 6.15* | 4.45 | 550         | 0.50† | 0.15 | 14 |

JEDEC Registration MO-220, Variation VJJD-6, Issue K, June 2006.

Drawings not to scale.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.

#### **APPENDIX A: REVISION HISTORY**

#### Revision A (May 2014)

• Original Release of this Document.

#### **Revision B (September 2014)**

- Updated template to the Microchip template

- Updated the package marking information

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### PRODUCT IDENTIFICATION SYSTEM

$\underline{\text{To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.}\\$

| Device Pac    | ( <u>X</u> - <u>X</u> - <u>X</u><br>     <br>kage Environmental Reel<br>tions | a) | amples:<br>HV9982K6-G: | 40-lead QFN package,<br>490/Tray. |

|---------------|-------------------------------------------------------------------------------|----|------------------------|-----------------------------------|

|               |                                                                               | b) | HV9982K6-G-M935:       | 40-lead QFN package, 2000/Reel.   |

| Device:       | HV9982 = Three-Channel, Closed-Loop, Switch Mod<br>LED Drive IC               | le |                        |                                   |

| Package:      | K6 = 40-lead (6x6) QFN                                                        |    |                        |                                   |

| Environmental | G = Lead (Pb)-free/ROHS-compliant package                                     |    |                        |                                   |

| Reel:         | (nothing) = Tray                                                              |    |                        |                                   |

|               | M935 = Reel                                                                   |    |                        |                                   |