## DATASHEET

## FOUR CHANNEL HD AUDIO CODECS

#### **DUAL CAPLESS HEADPHONE AMPLIFIERS**

#### DESCRIPTION

The 92HD66B is a low power optimized, high fidelity, 4-channel audio codec compatible with Intel's High Definition (HD) Audio Interface.

The 92HD66B provides high quality, HD Audio capability to notebook and desktop PC applications.

#### **FEATURES**

- 4 Channels (2 stereo ADCs) with 24-bit resolution

- Full HDA015-B and EuP low power support

- Audio inactivity transitions codec from D0 to D3 low power mode

- Resume from D3 to D0 with audio activity in < 10 msec</li>

- D3 to D0 transition with < -65dB pop/click</li>

- Port presence detect in D3 with or without bit clock

- PC beep wake up in D3

- · Additional vendor specific modes for even lower power

- Microsoft WLP premium logo compliant

- 4 or 5 analog ports with port presence detect\*

- 3 integrated headphone amplifiers

- 2 Capless headphone amplifiers

- 3 or 4 ports support adjustable microphone bias\*

- Dual SPDIF outputs for WLP compliant support of simultaneous HDMI and SPDIF output

- SPDIF Input

- Two digital microphone inputs (mono, stereo or quad)

- High performance analog mixer

- Support for 1.5V and 3.3V HDA signaling

- Integrated AVDD LDO for improved PSRR

- +5V or +3.3V analog power supply

- Digital and Analog PC Beep to all outputs

- 48-pin or 40-pin QFN RoHS packages

## 92HD66B

#### SOFTWARE SUPPORT

- Intuitive TSI HD Sound graphical user interface that allows configurability and preference settings

- 12 band fully parametric equalizer

- Constant, system-level effects tuned to optimize a particular platform can be combined with user-mode "presets" tailored for specific acoustical environments and applications

- System-level effects automatically disabled when external audio connections made

#### Dynamics Processing

- · Enables improved voice articulation

- Compressor/limiter allows higher average volume level without resonances or damage to speakers.

#### TSI Vista APO wrapper

- Enables multiple APOs to be used with the TSI Driver

- Microphone Beam Forming, Acoustic Echo Cancellation, and Noise Suppression

- Dynamic Stream Switching

- Improved multi-streaming user experience with less support calls

- Broad 3<sup>rd</sup> party branded software including Creative, Dolby, DTS, and SRS

#### DEVICE OPTIONS

- 4 Channel, 48-pin QFN package

- 4 Channel, 40-pin QFN package

- \*40-pin package removes

- Port E and related VREF\_Out

- Mono Out

- GPIO 4

#### TABLE OF CONTENTS

#### **DESCRIPTION 10**

Overview 10

Orderable Part Numbers 10

#### **DETAILED DESCRIPTION 11**

Port Functionality 11

Port Characteristics 11

Vref Out 12

Jack Detect 12

SPDIF Output 13

SPDIF Input 15

Mono Output 16

Analog Mixer 16

**ADC Multiplexers 16**

Power Management 17

AFG D0 18

AFG D1 18

AFG D2 18

AFG D3 18

AFG D3cold 18

Vendor Specific Function Group Power States D4/D5 19

Vendor Specific Function Group Power State "D5 Kill" 19

Low-voltage HDA Signaling 19

Multi-channel capture 19

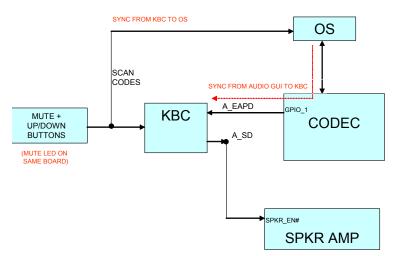

EAPD 21

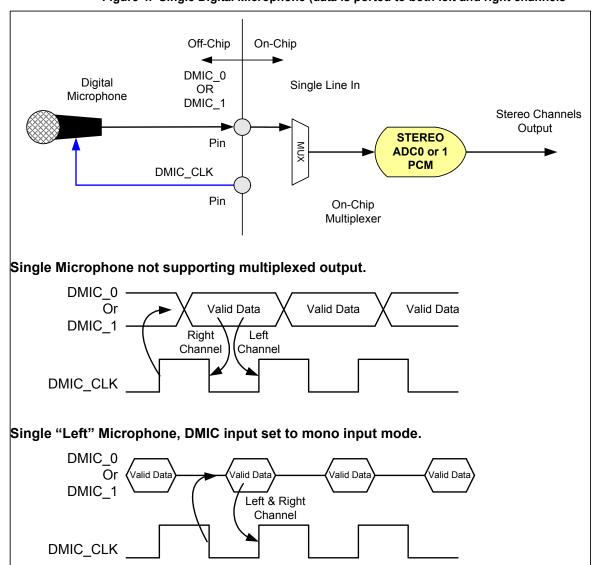

Digital Microphone Support 24

Analog PC-Beep 28

PC Beep Activity Monitor 29

Digital PC-Beep 31

Headphone Drivers 32

GPIO 32

GPIO Pin mapping and shared functions 32

Digital Microphone/GPIO Selection 32

SPDIF\_OUT/GPIO/DMIC Selection 33

HD Audio ECR 15b support 33

Digital Core Voltage Regulator 34

Analog Core Voltage Regulator 34

Combo Jack 34

#### **CHARACTERISTICS 35**

Audio Fidelity 35

Electrical Specifications 35

Absolute Maximum Ratings 35

**Recommended Operating Conditions 35**

92HD66B Analog Performance Characteristics 36

Capless Headphone Supply Characteristics 41

AC Timing Specs 41

HD Audio Bus Timing 41

SPDIF Timing 42

Digital Microphone Timing 42

**GPIO Characteristics 42**

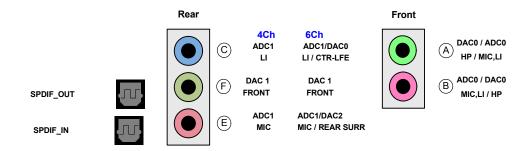

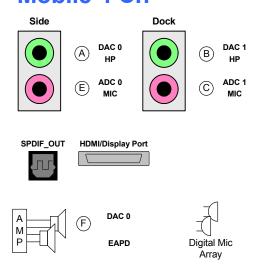

## **COMMON PORT CONFIGURATIONS 43**

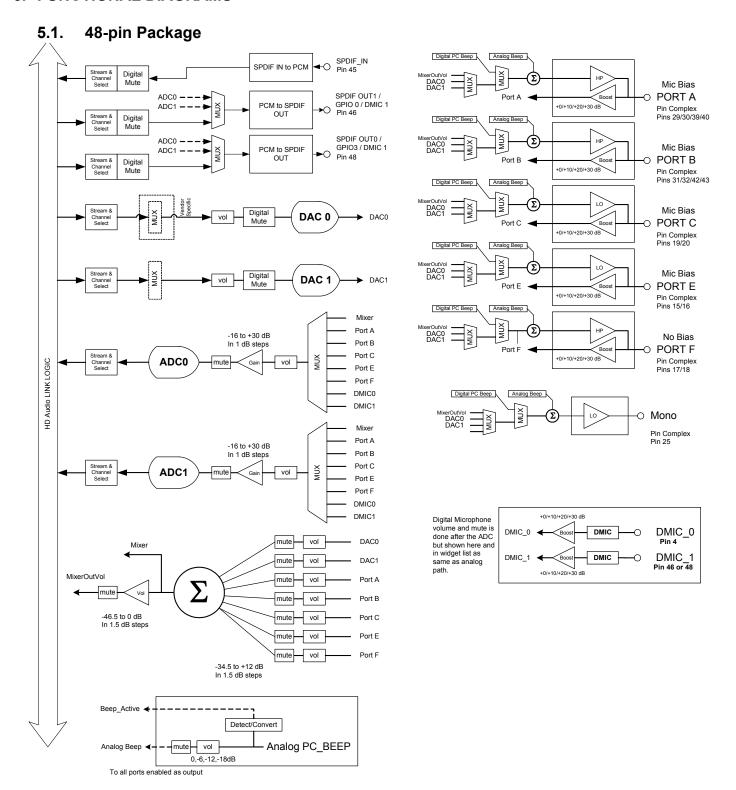

#### **FUNCTIONAL DIAGRAMS 44**

48-pin Package 44

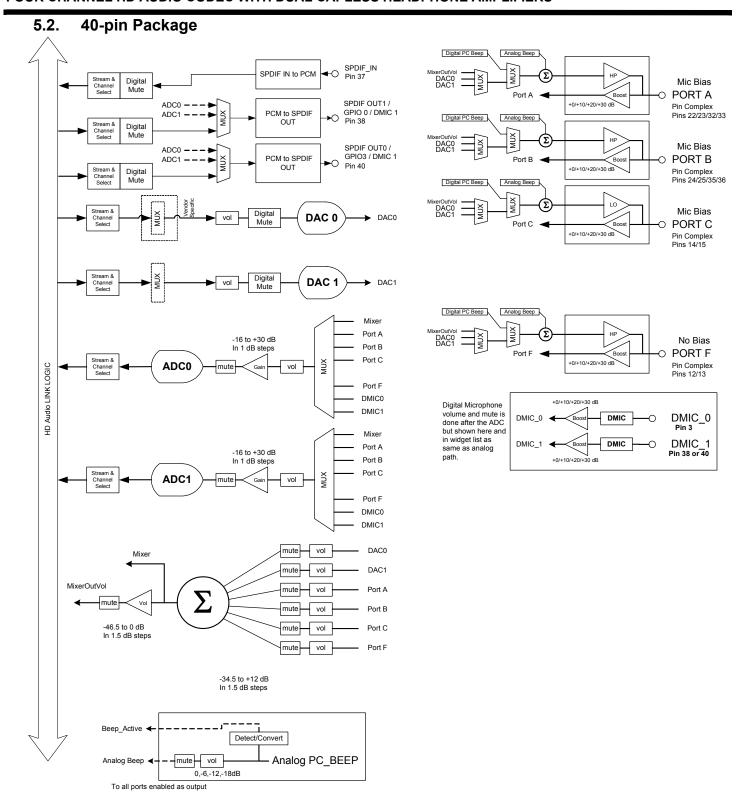

40-pin Package 45

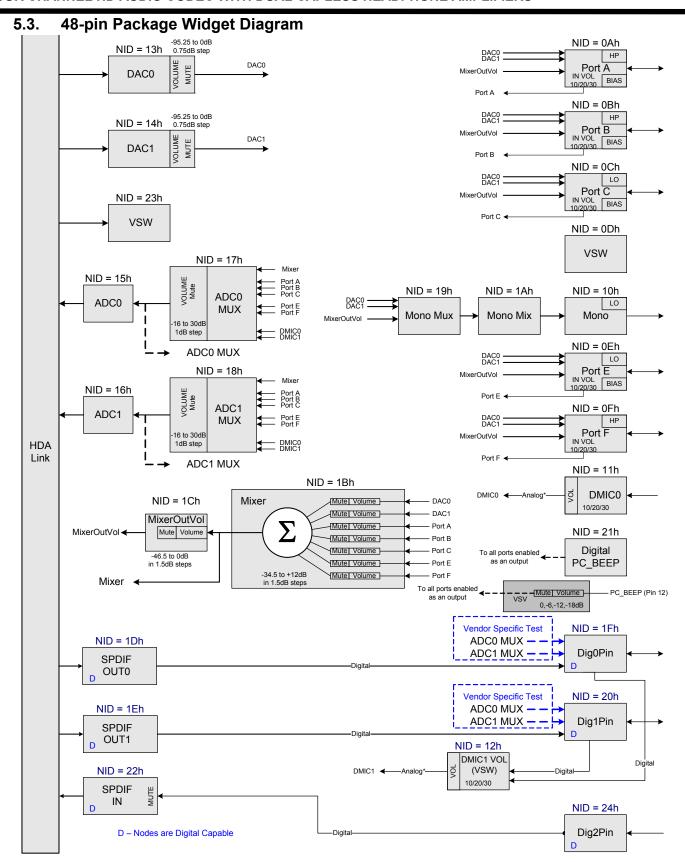

48-pin Package Widget Diagram 46

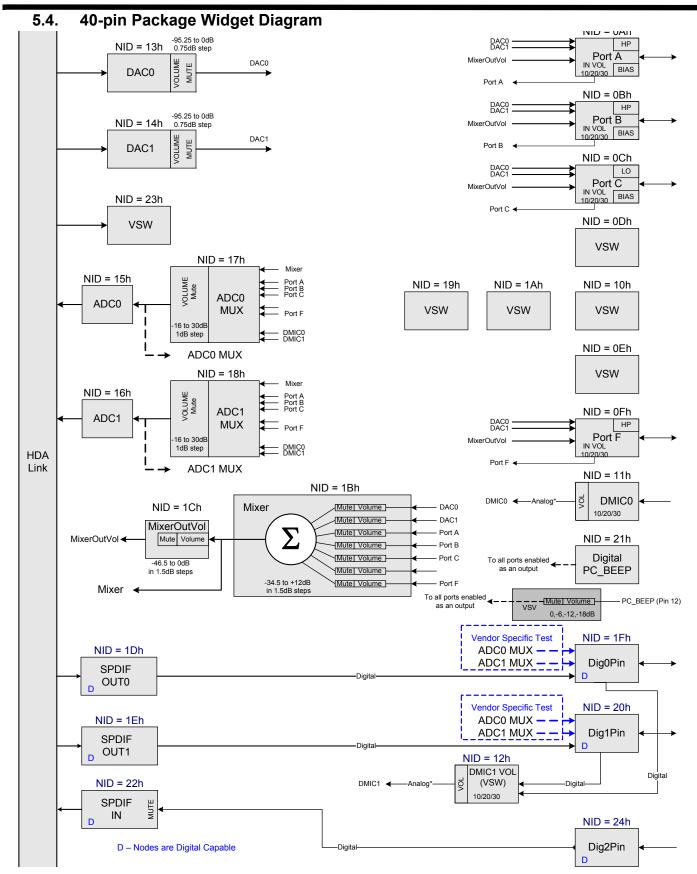

40-pin Package Widget Diagram 47

48-Pin Configuration Default Register Settings 48

40-Pin Configuration Default Register Settings 49

#### **WIDGET INFORMATION 50**

Widget List 50 Widget Descriptions 51 Widget Details 51 Device IDs 51 Reset Key 52 Root (NID = 00h): VendorID 52 Root (NID = 00h): RevID 53 Root (NID = 00h): NodeInfo 53 AFG (NID = 01h): NodeInfo 54 AFG (NID = 01h): FGType 54 AFG (NID = 01h): AFGCap 55 AFG (NID = 01h): PCMCap 56 AFG (NID = 01h): StreamCap 57 AFG (NID = 01h): InAmpCap 58 AFG (NID = 01h): PwrStateCap 59 AFG (NID = 01h): GPIOCnt 60 AFG (NID = 01h): OutAmpCap 60 AFG (NID = 01h): PwrState 61 AFG (NID = 01h): UnsolResp 62 AFG (NID = 01h): GPIO 62 AFG (NID = 01h): GPIOEn 63 AFG (NID = 01h): GPIODir 64 AFG (NID = 01h): GPIOWakeEn 65 AFG (NID = 01h): GPIOUnsol 66 AFG (NID = 01h): GPIOSticky 67 AFG (NID = 01h): SubID 67 AFG (NID = 01h): GPIOPIrty 68 AFG (NID = 01h): GPIODrive 69 AFG (NID = 01h): DMic 70 AFG (NID = 01h): DACMode 71 AFG (NID = 01h): ADCMode 72 AFG (NID = 01h): PortUse 73 AFG (NID = 01h): ComJack 74 AFG (NID = 01h): ComJackTime 75 AFG (NID = 01h): VSPwrState 77 AFG (NID = 01h): AnaPort 77 AFG (NID = 01h): AnaBeep 79 AFG (NID = 01h): AnaCapless 79 AFG (NID = 01h): Reset 82 PortA (NID = 0Ah): WCap 83 PortA (NID = 0Ah): PinCap 84 PortA (NID = 0Ah): ConLst 85 PortA (NID = 0Ah): ConLstEntry0 86 PortA (NID = 0Ah): InAmpLeft 86 PortA (NID = 0Ah): InAmpRight 87 PortA (NID = 0Ah): ConSelectCtrl 87 PortA (NID = 0Ah): PwrState 88 PortA (NID = 0Ah): PinWCntrl 88 PortA (NID = 0Ah): UnsolResp 89 PortA (NID = 0Ah): ChSense 90 PortA (NID = 0Ah): EAPDBTLLR 90 PortA (NID = 0Ah): ConfigDefault 91 PortB (NID = 0Bh): WCap 93 PortB (NID = 0Bh): PinCap 95 PortB (NID = 0Bh): ConLst 96 PortB (NID = 0Bh): ConLstEntry0 97 PortB (NID = 0Bh): InAmpLeft 97

PortB (NID = 0Bh): InAmpRight 98

```

PortB (NID = 0Bh): ConSelectCtrl 98

PortB (NID = 0Bh): PwrState 98

PortB (NID = 0Bh): PinWCntrl 99

PortB (NID = 0Bh): UnsolResp 100

PortB (NID = 0Bh): ChSense 101

PortB (NID = 0Bh): EAPDBTLLR 101

PortB (NID = 0Bh): ConfigDefault 101

PortC (NID = 0Ch): WCap 104

PortC (NID = 0Ch): PinCap 105

PortC (NID = 0Ch): ConLst 106

PortC (NID = 0Ch): ConLstEntry0 107

PortC (NID = 0Ch): InAmpLeft 107

PortC (NID = 0Ch): InAmpRight 108

PortC (NID = 0Ch): ConSelectCtrl 108

PortC (NID = 0Ch): PwrState 109

PortC (NID = 0Ch): PinWCntrl 109

PortC (NID = 0Ch): UnsolResp 110

PortC (NID = 0Ch): ChSense 111

PortC (NID = 0Ch): EAPDBTLLR 111

PortC (NID = 0Ch): ConfigDefault 112

NID = 0Dh Reserved 114

PortE (NID = 0Eh): WCap (Available only on 48-pin versions) 114

PortE (NID = 0Eh): PinCap (Available only on 48-pin versions) 116

PortE (NID = 0Eh): ConLst (Available only on 48-pin versions) 117

PortE (NID = 0Eh): ConLstEntry0 (Available only on 48-pin versions) 118

PortE (NID = 0Eh): InAmpLeft (Available only on 48-pin versions) 118

PortE (NID = 0Eh): InAmpRight (Available only on 48-pin versions) 118

PortE (NID = 0Eh): ConSelectCtrl (Available only on 48-pin versions) 119

PortE (NID = 0Eh): PwrState (Available only on 48-pin versions) 119

PortE (NID = 0Eh): PinWCntrl (Available only on 48-pin versions) 120

PortE (NID = 0Eh): UnsolResp (Available only on 48-pin versions) 121

PortE (NID = 0Eh): ChSense (Available only on 48-pin versions) 121

PortE (NID = 0Eh): EAPDBTLLR (Available only on 48-pin versions) 122

PortE (NID = 0Eh): ConfigDefault (Available only on 48-pin versions) 122

PortF (NID = 0Fh): WCap 125

PortF (NID = 0Fh): PinCap 126

PortF (NID = 0Fh): ConLst 127

PortF (NID = 0Fh): ConLstEntry0 128

PortF (NID = 0Fh): InAmpLeft 128

PortF (NID = 0Fh): InAmpRight 129

PortF (NID = 0Fh): ConSelectCtrl 129

PortF (NID = 0Fh): PwrState 130

PortF (NID = 0Fh): PinWCntrl 130

PortF (NID = 0Fh): UnsolResp 131

PortF (NID = 0Fh): ChSense 132

PortF (NID = 0Fh): EAPDBTLLR 132

PortF (NID = 0Fh): ConfigDefault 132

MonoOut (NID = 10h): WCap (Available only on 48-pin versions) 135

MonoOut (NID = 10h): PinCap (Available only on 48-pin versions) 136

MonoOut (NID = 10h): ConLst (Available only on 48-pin versions) 137

MonoOut (NID = 10h): ConLstEntry0 (Available only on 48-pin versions) 138

MonoOut (NID = 10h): PwrState (Available only on 48-pin versions) 138

MonoOut (NID = 10h): PinWCntrl (Available only on 48-pin versions) 139

MonoOut (NID = 10h): UnsolResp (Available only on 48-pin versions) 140

MonoOut (NID = 10h): ChSense (Available only on 48-pin versions) 140

MonoOut (NID = 10h): ConfigDefault (Available only on 48-pin versions) 141

DMic0 (NID = 11h): WCap 143

DMic0 (NID = 11h): PinCap 145

DMic0 (NID = 11h): InAmpLeft 146

```

```

DMic0 (NID = 11h): InAmpRight 146

DMic0 (NID = 11h): PwrState 147

DMic0 (NID = 11h): PinWCntrl 148

DMic0 (NID = 11h): ConfigDefault 148

DMic1Vol (NID = 12h): WCap 151

DMic1Vol (NID = 12h): ConLst 152

DMic1Vol (NID = 12h): ConLstEntry0 153

DMic1Vol (NID = 12h): InAmpLeft 153

DMic1Vol (NID = 12h): InAmpRight 153

DMic1Vol (NID = 12h): ConSelectCtrl 154

DMic1Vol (NID = 12h): PwrState 154

DAC0 (NID = 13h): WCap 155

DAC0 (NID = 13h): Cnvtr 157

DAC0 (NID = 13h): OutAmpLeft 158

DAC0 (NID = 13h): OutAmpRight 158

DAC0 (NID = 13h): PwrState 159

DAC0 (NID = 13h): CnvtrID 160

DAC0 (NID = 13h): EAPDBTLLR 160

DAC1 (NID = 14h): WCap 161

DAC1 (NID = 14h): Cnvtr 162

DAC1 (NID = 14h): OutAmpLeft 163

DAC1 (NID = 14h): OutAmpRight 164

DAC1 (NID = 14h): PwrState 164

DAC1 (NID = 14h): CnvtrID 165

DAC1 (NID = 14h): EAPDBTLLR 166

ADC0 (NID = 15h): WCap 166

ADC0 (NID = 15h): ConLst 168

ADC0 (NID = 15h): ConLstEntrv0 168

ADC0 (NID = 15h): Cnvtr 169

ADC0 (NID = 15h): ProcState 170

ADC0 (NID = 15h): PwrState 170

ADC0 (NID = 15h): CnvtrID 171

ADC1 (NID = 1Bh): WCap 172

ADC1 (NID = 1Bh): ConLst 173

ADC1 (NID = 1Bh): ConLstEntry0 174

ADC1 (NID = 1Bh): Cnvtr 174

ADC1 (NID = 1Bh): ProcState 176

ADC1 (NID = 1Bh): PwrState 176

ADC1 (NID = 1Bh): CnvtrlD 177

ADC0Mux (NID = 17h): WCap 177

ADC0Mux (NID = 17h): ConLst 179

ADC0Mux (NID = 17h): ConLstEntry4 179

ADC0Mux (NID = 17h): ConLstEntry0 180

ADC0Mux (NID = 17h): OutAmpCap 180

ADC0Mux (NID = 17h): OutAmpLeft 181

ADC0Mux (NID = 17h): OutAmpRight 182

ADC0Mux (NID = 17h): ConSelectCtrl 182

ADC0Mux (NID = 17h): PwrState 183

ADC0Mux (NID = 17h): EAPDBTLLR 183

ADC1Mux (NID = 18h): WCap 184

ADC1Mux (NID = 18h): ConLst 185

ADC1Mux (NID = 18h): ConLstEntrv4 186

ADC1Mux (NID = 18h): ConLstEntry0 186

ADC1Mux (NID = 18h): OutAmpCap 187

ADC1Mux (NID = 18h): OutAmpLeft 188

ADC1Mux (NID = 18h): OutAmpRight 188

ADC1Mux (NID = 18h): ConSelectCtrl 189

ADC1Mux (NID = 18h): PwrState 189

```

ADC1Mux (NID = 18h): EAPDBTLLR 190

```

MonoMux (NID = 19h): WCap (Available only on 48-pin versions) 190

MonoMux (NID = 19h): ConLst (Available only on 48-pin versions) 192

MonoMux (NID = 19h): ConLstEntry0 (Available only on 48-pin versions) 192

MonoMux (NID = 19h); ConSelectCtrl (Available only on 48-pin versions) 193

MonoMux (NID = 19h): PwrState (Available only on 48-pin versions) 193

MonoMix (NID = 1Ah): WCap (Available only on 48-pin versions) 194

MonoMix (NID = 1Ah): ConLst (Available only on 48-pin versions) 196

MonoMix (NID = 1Ah): ConLstEntry0 (Available only on 48-pin versions) 196

MonoMix (NID = 1Ah): PwrState (Available only on 48-pin versions) 197

Mixer (NID = 1Bh): WCap 198

Mixer (NID = 1Bh): InAmpCap 199

Mixer (NID = 1Bh): ConLst 200

Mixer (NID = 1Bh): ConLstEntry4 201

Mixer (NID = 1Bh): ConLstEntry0 201

Mixer (NID = 1Bh): InAmpLeft0 202

Mixer (NID = 1Bh): InAmpRight0 202

Mixer (NID = 1Bh): InAmpLeft1 203

Mixer (NID = 1Bh): InAmpRight1 203

Mixer (NID = 1Bh): InAmpLeft2 204

Mixer (NID = 1Bh): InAmpRight2 204

Mixer (NID = 1Bh): InAmpLeft3 205

Mixer (NID = 1Bh): InAmpRight3 205

Mixer (NID = 1Bh): InAmpLeft4 206

Mixer (NID = 1Bh): InAmpRight4 206

Mixer (NID = 1Bh): InAmpLeft5 207

Mixer (NID = 1Bh): InAmpRight5 207

Mixer (NID = 1Bh): InAmpLeft6 208

Mixer (NID = 1Bh): InAmpRight6 209

Mixer (NID = 1Bh): InAmpLeft7 209

Mixer (NID = 1Bh): InAmpRight7 210

Mixer (NID = 1Bh): PwrState 210

MixerOutVol (NID = 1Ch): WCap 211

MixerOutVol (NID = 1Ch): ConLst 212

MixerOutVol (NID = 1Ch): ConLstEntry0 213

MixerOutVol (NID = 1Ch): OutAmpCap 213

MixerOutVol (NID = 1Ch): OutAmpLeft 214

MixerOutVol (NID = 1Ch): OutAmpRight 215

MixerOutVol (NID = 1Ch): PwrState 215

SPDIFOut0 (NID = 1Dh): WCap 216

SPDIFOut0 (NID = 1Dh): PCMCap 218

SPDIFOut0 (NID = 1Dh): StreamCap 220

SPDIFOut0 (NID = 1Dh): OutAmpCap 220

SPDIFOut0 (NID = 1Dh): Cnvtr 221

SPDIFOut0 (NID = 1Dh): OutAmpLeft 222

SPDIFOut0 (NID = 1Dh): OutAmpRight 223

SPDIFOut0 (NID = 1Dh): PwrState 223

SPDIFOut0 (NID = 1Dh): CnvtrID 224

SPDIFOut0 (NID = 1Dh): DigCnvtr 224

SPDIFOut1 (NID = 1Eh): WCap 225

SPDIFOut1 (NID = 1Eh): PCMCap 227

SPDIFOut1 (NID = 1Eh): StreamCap 229

SPDIFOut1 (NID = 1Eh): OutAmpCap 229

SPDIFOut1 (NID = 1Eh): Cnvtr 230

SPDIFOut1 (NID = 1Eh): OutAmpLeft 231

SPDIFOut1 (NID = 1Eh): OutAmpRight 232

SPDIFOut1 (NID = 1Eh): PwrState 232

SPDIFOut1 (NID = 1Eh): CnvtrlD 233

SPDIFOut1 (NID = 1Eh): DigCnvtr 234

```

Dig0Pin (NID = 1Fh): WCap 235

```

Dig0Pin (NID = 1Fh): PinCap 236

Dig0Pin (NID = 1Fh): ConLst 237

Dig0Pin (NID = 1Fh): ConLstEntry0 238

DigOPin (NID = 1Fh): PwrState 238

Dig0Pin (NID = 1Fh): PinWCntrl 239

Dig0Pin (NID = 1Fh): UnsolResp 240

Dig0Pin (NID = 1Fh): ChSense 240

Dig0Pin (NID = 1Fh): ConfigDefault 241

Dig1Pin (NID = 20h): WCap 243

Dig1Pin (NID = 20h): PinCap 245

Dig1Pin (NID = 20h): ConLst 246

Dig1Pin (NID = 20h): ConLstEntry0 247

Dig1Pin (NID = 20h): PwrState 247

Dig1Pin (NID = 20h): PinWCntrl 248

Dig1Pin (NID = 20h): UnsolResp 249

Dia1Pin (NID = 20h): ChSense 249

Dig1Pin (NID = 20h): ConfigDefault 249

DigBeep (NID = 21h): WCap 252

DigBeep (NID = 21h): OutAmpCap 253

DigBeep (NID = 21h): OutAmpLeft 253

DigBeep (NID = 21h): PwrState 254

DigBeep (NID = 21h): Gen 255

SPDIFIn (NID = 22h): WCap 255

SPDIFIn (NID = 22h): Cnvtr 258

SPDIFIn (NID = 22h): PCMCap 259

SPDIFIn (NID = 22h): StreamCap 260

SPDIFIn (NID = 22h): ConLst 261

SPDIFIn (NID = 22h): ConLstEntrv0 261

SPDIFIn (NID = 22h): PwrState 262

SPDIFIn (NID = 22h): CnvtrID 263

SPDIFIn (NID = 22h): DigCnvtr 263

SPDIFIn (NID = 22h): InAmpCap 264

SPDIFIn (NID = 22h): InAmpLeft 265

SPDIFIn (NID = 22h): InAmpRight 265

SPDIFIn (NID = 22h): VS 266

SPDIFIn (NID = 22h): Status 266

NID = 23h Reserved 269

Dig2Pin (NID = 24h): WCap 270

Dig2Pin (NID = 24h): PinCap 271

Dig2Pin (NID = 24h): PwrState 272

Dig2Pin (NID = 24h): UnsolResp 274

Dig2Pin (NID = 24h): ChSense 274

Dig2Pin (NID = 24h): ConfigDefault 275

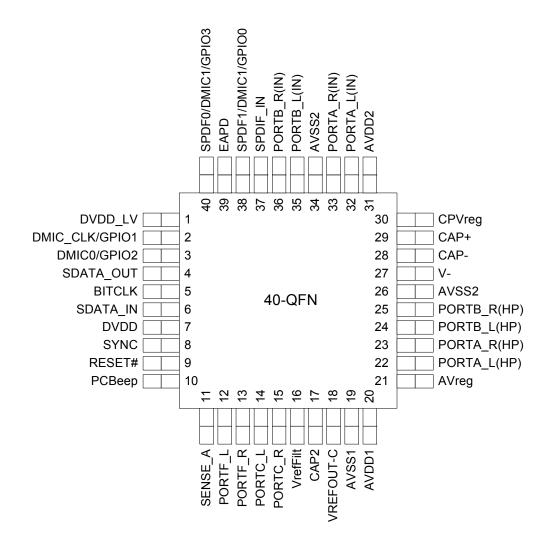

PINOUTS AND PACKAGE INFORMATION 278

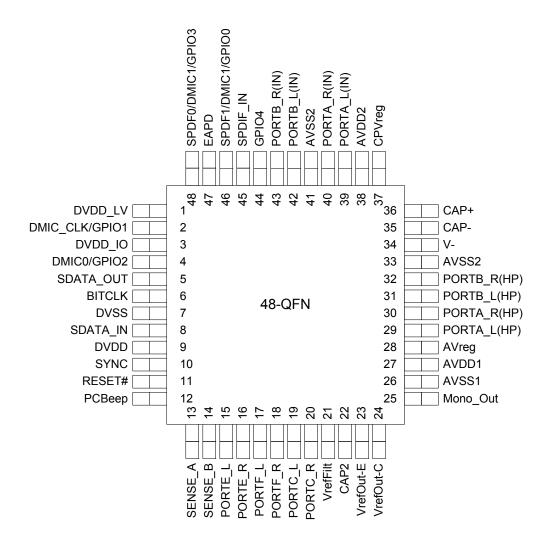

48-Pin Pinout 278

40-Pin Pinout 279

Pin Table for 48-Pin 280

Pin Table for 40-Pin 281

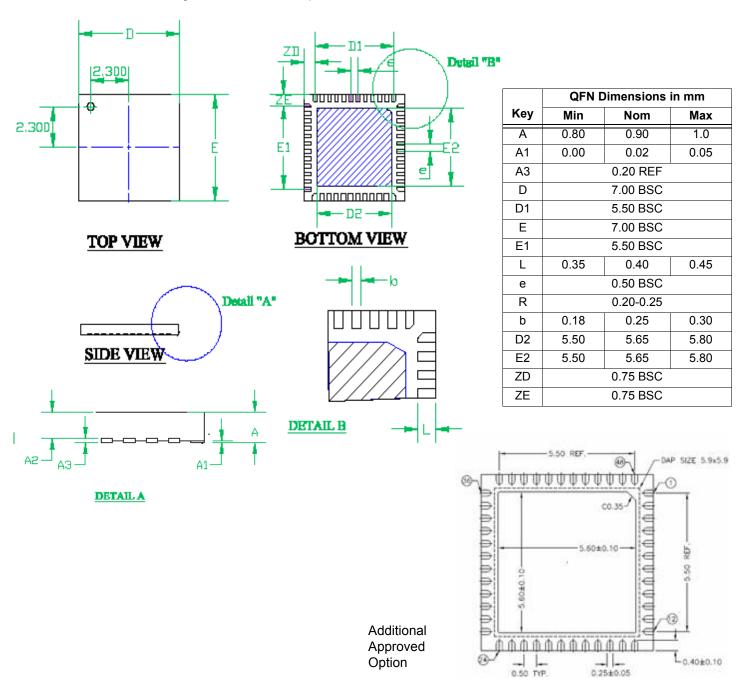

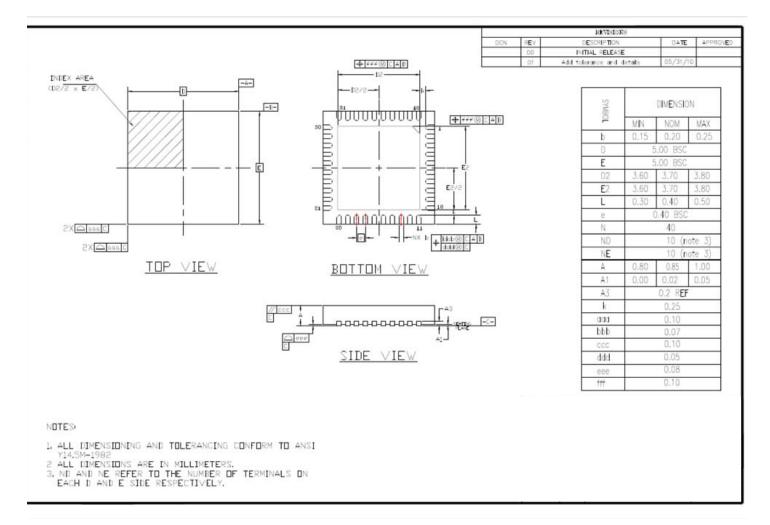

48QFN Package Outline and Package Dimensions 283

40QFN Package Outline and Package Dimensions 284

Pb Free Process- Package Classification Reflow Temperatures 284

DISCLAIMER 285

```

## TSI™ CONFIDENTIAL 7 V 1.2 09/14

**DOCUMENT REVISION HISTORY 286**

#### 92HD66B

## FOUR CHANNEL HD AUDIO CODEC WITH DUAL CAPLESS HEADPHONE AMPLIFIERS

## **LIST OF FIGURES**

Multi-channel capture 20

Multi-channel timing diagram 20

EAPD System level Example 24

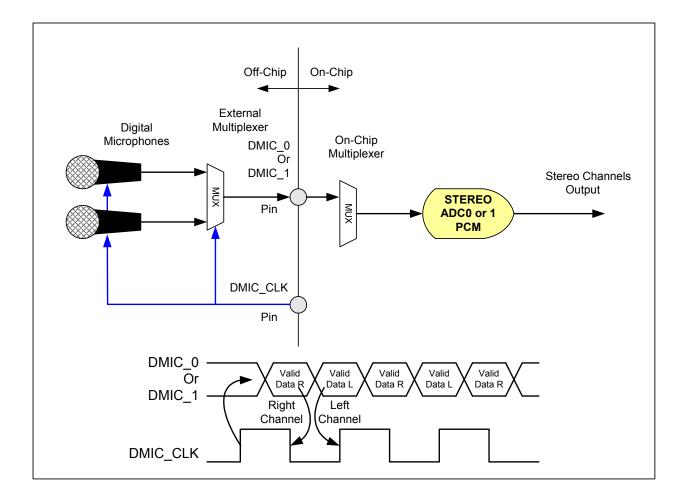

Single Digital Microphone (data is ported to both left and right channels 26

Stereo Digital Microphone Configuration 27

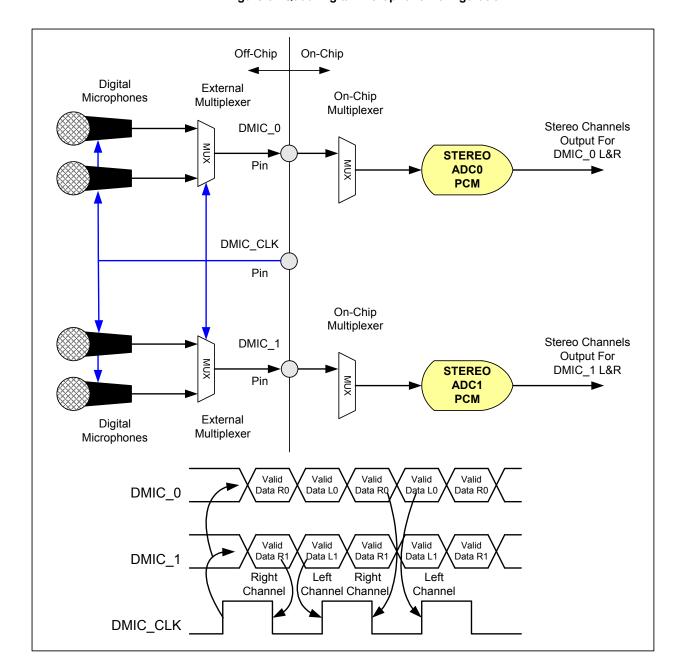

Quad Digital Microphone Configuration 28

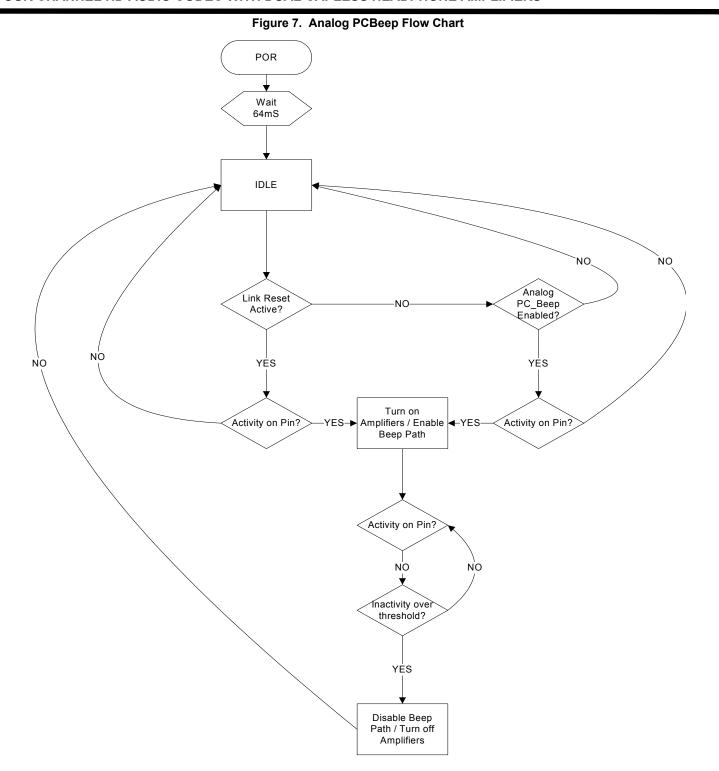

Analog PCBeep Flow Chart 30

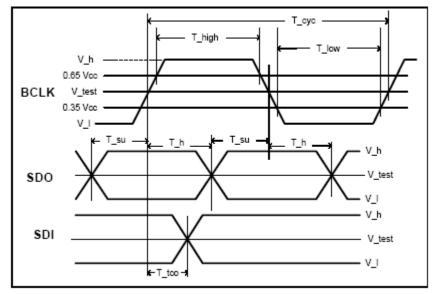

HD Audio Bus Timing 41

Common Port Configurations 43

48-pin Package Functional Diagram 44

40-pin Package Functional Diagram 45

48-pin Package Widget Diagram 46

40-pin Package Widget Diagram 47

48-Pin Pinout 278

40-Pin Pinout 279

48QFN Package Diagram 283

40QFN Package Diagram 284

#### LIST OF TABLES

Port Functionality 11

Analog Output Port Behavior 11

Resistor Tolerance 13

48 pin Jack Detect 13

40 pin Jack Detect 13

SPDIF OUT 0 or 1 Behavior 14

SPDIF Behavior 15

Power Management 17

Example channel mapping 20

EAPD Pin Mode Select 22

Control bit descriptions for BTL amplifier and Headphone amplifier enable configurations 22

BTL Amp Enable Configuration 22

EAPD Analog PC Beep behavior 23

EAPD Behavior 23

Valid Digital Mic Configurations 25

DMIC CLK and DMIC 0,1 Operation During Power States 25

Dig0Pin (Pin 48/40) Function Selection 33

Dig1Pin (Pin 46/38) Function Selection 33

Electrical Specification: Maximum Ratings 35

**Recommended Operating Conditions 35**

Analog Performance 36

Capless Headphone Supply 41

HD Audio Bus Timing 41

SPDIF Timing 42

Digital Mic timing 42

**GPIO Characteristics 42**

Pin Configuration Default Settings 48

High Definition Audio Widget 50

Widget Descriptions 51

48-PinTable 280

40-Pin Table 281

Reflow 284

#### 1. DESCRIPTION

## 1.1. Overview

The 92HD66B provide stereo 24- bit, full duplex resolution supporting sample rates up to 192kHz by the DAC and ADC. SPDIF outputs support sample rates of 192kHz, 96kHz, 88.2kHz, 48kHz, and 44.1kHz. SPDIF input supports 96KHz, 88.2KHz, 48KHz, and 44.1KHz sample rates. Additional sample rates are supported by the driver software.

The 92HD66B supports a wide range of desktop and laptop 4-channel configurations. The 2 independent SPDIF output interfaces provides connectivity to consumer electronic equipment or to a home entertainment system. Simultaneous HDMI and SPDIF output is possible. All inputs can be programmed with 0-30 dB gain in 10 dB steps allowing for line or microphone use of any input.

Port presence detect capabilities allow the CODEC to detect when audio devices are connected to the CODEC. The fully parametric TSI SoftEQ can be initiated upon headphone jack insertion and removal for protection of notebook speakers.

The 92HD66B operates with a 3.3V digital supply and a 5V analog supply. It allows for 1.5V and 3.3V HDA signaling; the correct signalling level is selected based on the power supply voltage on the DVDD-IO pin.

The 92HD66B is offered in a 48 or 40 pin QFN Environmental (ROHS) package.

## 1.2. Orderable Part Numbers

| 92HD66B1X5NDGXyyX | 4ch, 40QFN, 1.5V HDA Signaling, 5V AVDD                      |

|-------------------|--------------------------------------------------------------|

| 92HD66B1X3NDGXyyX | 4ch, 40QFN, 1.5V HDA Signaling, 3.3V AVDD                    |

| 92HD66B2X5NDGXyyX | 4ch, 40QFN, 3.3V HDA Signaling, 5V AVDD                      |

| 92HD66B2X3NDGXyyX | 4ch, 40QFN, 3.3V HDA Signaling, 3.3V AVDD                    |

| 92HD66B3X5NLGXyyX | 4ch, 48QFN, switchable 1.5V or 3.3V HDA Signaling, 5V AVDD   |

| 92HD66B3X3NLGXyyX | 4ch, 48QFN, switchable 1.5V or 3.3V HDA Signaling, 3.3V AVDD |

yy = silicon stepping/revision, contact sales for current data. Add an "8" to the end for tape and reel delivery.

#### 2. DETAILED DESCRIPTION

## 2.1. Port Functionality

| Pins (40-pin) | Pins (48-pin) | Port       | Input            | Output | Head phone | Mic Bias<br>(Vref pin) | Input boost amp  |

|---------------|---------------|------------|------------------|--------|------------|------------------------|------------------|

| 22/23/32/33   | 29/30/39/40   | Α          | Yes              | Yes    | Yes        | Yes <sup>1</sup>       | Yes              |

| 24/25/35/36   | 31/32/42/43   | В          | Yes              | Yes    | Yes        | Yes <sup>1</sup>       | Yes              |

| 14/15         | 19/20         | С          | Yes              | Yes    |            | Yes                    | Yes              |

| -             | -             | D          |                  |        |            |                        |                  |

| -             | 15/16         | E          | Yes              | Yes    |            | Yes                    | Yes              |

| 12/13         | 17/18         | F          | Yes              | Yes    | Yes        |                        | Yes              |

| 40            | 48            | SPDIF_OUT0 | Yes <sup>2</sup> | Yes    |            |                        | Yes <sup>3</sup> |

| 38            | 46            | SPDIF_OUT1 | Yes <sup>2</sup> | Yes    |            |                        | Yes <sup>3</sup> |

| 37            | 45            | SPDIF_IN   | Yes              |        |            |                        |                  |

| 3 (CLK=2)     | 4 (CLK=2)     | DMIC0      | Yes              |        |            |                        | Yes              |

**Table 1. Port Functionality**

- Ports A and B provide internal microphone bias on the headphone out pins. No external VrefOut pin is needed.

- 2. DMIC1

- 3. Boost amp is only available for DMIC input and is not associated with the pin widget

#### 2.1.1. Port Characteristics

Universal (Bi-directional) jacks are supported on ports A, B, C, E (48-pin package only), and F. Ports A, B, and F are designed to drive 32 ohm (nominal) headphones or a 10K (nominal) load. Line Level outputs are intended to drive an external 10K load (nominal) and an on board shunt resistor of 20-47K (nominal). However, applications may support load impedances of 2.8K ohms and above when implementing ports capable of operating as microphone inputs or line outputs. Input ports are 75K (nominal) at the pin.

DAC full scale outputs and intended full scale input levels are greater than 1V rms at 5V (+5%/-10%) to meet WLP requirements. Line output ports and Headphone output ports on the codec may be configured for +3dBV full scale output levels by using a vendor specific verb.

Output ports implement anti-pop circuits to prevent pops/clicks associated with turning power on/off or charging and discharging output coupling capacitors (except for cap-less headphone ports). Unused ports should be left unconnected. When updating existing designs to use the codec, ensure that there are no conflicts between the output ports on the codec and existing circuitry.

| AFG<br>Power<br>State | Input<br>Enable | Output<br>Enable | Used as<br>output for<br>DAC/Mixer | Used as output for analog PC_Beep | Used as input for ADC, mixer | Port Behavior                                                                                   |

|-----------------------|-----------------|------------------|------------------------------------|-----------------------------------|------------------------------|-------------------------------------------------------------------------------------------------|

| D0-D2                 | 1               | 1                | Don't care                         | Don't care                        | Yes                          | Not allowed. Port is active as Input.                                                           |

|                       | 1               | 1                | Don't care                         | Don't care                        | No                           | Not allowed. Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

Table 2. Analog Output Port Behavior

| AFG<br>Power<br>State | Input<br>Enable | Output<br>Enable | Used as<br>output for<br>DAC/Mixer                                                   | Used as<br>output for<br>analog<br>PC_Beep | Used as<br>input for<br>ADC, mixer | Port Behavior                                                                      |

|-----------------------|-----------------|------------------|--------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------|------------------------------------------------------------------------------------|

|                       | 1               | 0                | NA                                                                                   | NA                                         | Yes                                | Active - Port enabled as input                                                     |

|                       | 1               | 0                | NA                                                                                   | NA                                         | No                                 | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

|                       | 0               | 1                | currently used by DAC, mixer,<br>beep, or is traditional line or<br>headphone output |                                            | NA                                 | Active - Port enabled as output                                                    |

|                       | 0               | 1                | not currently used by DAC,<br>mixer, beep, and is cap-less<br>headphone output       |                                            | NA                                 | Inactive (Power Down)                                                              |

|                       | 0               | 0                | NA                                                                                   | NA                                         |                                    | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

| D3                    | 1               | 1                | NA                                                                                   | NA                                         | Don't care                         | Not allowed. Port is active as Input.                                              |

|                       | 1               | 0                | NA                                                                                   | NA                                         | Don't care                         | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

|                       | 0               | 1                | currently used by DAC, mixer,<br>beep, or is traditional line or<br>headphone output |                                            | Don't care                         | Low power state. If enabled, Beep will output from the port                        |

|                       | 0               | 1                | not currently used by DAC,<br>mixer, beep, and is cap-less<br>headphone output       |                                            | Don't care                         | Inactive (Power Down)                                                              |

|                       | 0               | 0                | NA NA                                                                                |                                            | Don't care                         | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

| D3cold                | -               | -                |                                                                                      |                                            |                                    | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

| D4                    | -               | -                |                                                                                      |                                            |                                    | Inactive (Power Down) - Port keeps output coupling caps charged if port uses caps. |

| D5                    | -               | -                |                                                                                      |                                            |                                    | Off - Charge on coupling caps (if used) will not be maintained.                    |

Table 2. Analog Output Port Behavior

## 2.2. Vref\_Out

Ports A, B, C, & E (48-pin package only) support Vref\_Out pins for biasing electret cartridge microphones. Settings of 80% AVDD, 50% AVDD, GND, and Hi-Z are supported. Attempting to program a pin widget control with a reserved or unsupported value will cause the associated Vref\_Out pin to assume a Hi-Z state and the pin widget control Vref\_En field will return a value of '000' (Hi-Z) when read.

#### 2.3. Jack Detect

Plugs inserted to a jack are detected using SENSE inputs as described in the tables below. Per HDA015-B, the detection circuit operates when the CODEC is in D0 - D3 and can also operate if both the CODEC and Controller are in D3 (no bus clock.) Jack detection requires that all supplies (analog and digital) are active and stable. When AVDD is not present, the value reported in the pin widget is invalid.

When the HD Audio bus is in a low power state (reset asserted and clock stopped) the CODEC will generate a Power State Change Request when a change in port connectivity is sensed and then generate an unsolicited response after the HD Audio link has been brought out of a low power state and the device has been enumerated. Per HDA015-B, this will take less than 10mS.

The following table summarizes the proper resistor tolerances for different analog supply voltages.

| AVdd Nominal     | Resistor Tolerance | Resistor Tolerance |

|------------------|--------------------|--------------------|

| Voltage (+/- 5%) | Pull-Up            | SENSE_A/B          |

| 4.75V or 5.0V    | 1%                 | 1%                 |

**Table 3. Resistor Tolerance**

| Resistor | SENSE_A | SENSE_B                                       |

|----------|---------|-----------------------------------------------|

| 39.2K    | PORT A  | PORT E                                        |

| 20.0K    | PORT B  | Mono                                          |

| 10.0K    | PORT C  | SPDIF0/DMIC1                                  |

| 5.11K    | PORT F  | SPDIF1/DMIC1                                  |

| 2.49K    |         | Pull-up to Avreg (X5)<br>Pull-up to AVDD (X3) |

Table 4. 48 pin Jack Detect

.

| Resistor | SENSE_A                                       |

|----------|-----------------------------------------------|

| 39.2K    | PORT A                                        |

| 20.0K    | PORT B                                        |

| 10.0K    | PORT C                                        |

| 5.11K    | PORT F                                        |

| 2.49K    | Pull-up to Avreg (X5)<br>Pull-up to AVDD (X3) |

Table 5. 40 pin Jack Detect

See reference design for more information on Jack Detect implementation.

## 2.4. SPDIF Output

Both SPDIF Outputs can operate at 44.1kHz, 48kHz, 88.2kHz, 96kHz and 192KHz as defined in the Intel High Definition Audio Specification with resolutions up to 24 bits. This insures compatibility with all consumer audio gear and allows for convenient integration into home theater systems and media center PCs.

Note: Peak to peak jitter is currently limited to less than 4.5nS (half of the internal master clock cycle) which does not meet the IEC-60958-3 0.05UI requirement at 192KHz.

The two SPDIF output converters can not be aligned in phase with the DACs. Even when attached to the same stream, the two SPDIF output converters may be misaligned with respect to their frame boundaries.

Per HDA015-B, the SPDIF outputs support the ability to provide clocking information even when no stream is selected for the converter, or when in a low power state. Also, as stated in the DCN, the SPDIF output ports support port presence detect.

SPDIF Outputs are outlined in tables below. .

| AFG<br>Power<br>State | RESET#                | GPIO0<br>Enable | Input<br>Enable | Output<br>Enable | Keep<br>Alive<br>En | Converter<br>Dig En | Stream<br>ID | Pin<br>Mode                  | Pin Behavior                                                               |   |                                                      |                                                      |                                                      |

|-----------------------|-----------------------|-----------------|-----------------|------------------|---------------------|---------------------|--------------|------------------------------|----------------------------------------------------------------------------|---|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| D0-D4                 | Asserted<br>(Low)     | -               | -               | -                | -                   | -                   | -            |                              | Hi-Z immediately after power on, otherwise the previous state is retained. |   |                                                      |                                                      |                                                      |

| D0-D4                 | De-Asserted<br>(High) | 0               | 0               | 0                | -                   | -                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

| D0-D4                 | De-Asserted<br>(High) | 1               | -               | -                | -                   | -                   | -            | GPIO                         | Active - Pin reflects GPIO0 configuration (internal pull-down enabled)     |   |                                                      |                                                      |                                                      |

| D0-D4                 | De-Asserted<br>(High) | 0               | 1               | 0                | -                   | -                   | -            | SPDIF<br>IN or<br>DMIC<br>IN | Pin functions as SPDIF input or DMIC input                                 |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  |                     | 0                   | -            |                              | Active - Pin drives 0                                                      |   |                                                      |                                                      |                                                      |

|                       | D0 De-Asserted (High) |                 |                 |                  |                     |                     |              | 0                            | 1                                                                          | 0 |                                                      | Active - Pin drives SPDIF-format, but data is zeroes |                                                      |

|                       |                       |                 | 0               | 1                |                     |                     | 1-15         |                              | Active - Pin drives SPDIFOut1 data                                         |   |                                                      |                                                      |                                                      |

| D0                    |                       |                 |                 |                  |                     |                     |              |                              |                                                                            | 0 | -                                                    |                                                      | Active - Pin drives SPDIF-format, but data is zeroes |

|                       |                       |                 |                 |                  | 1                   | 1                   | 0            |                              | Active - Pin drives SPDIF-format, but data is zeroes                       |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  |                     |                     | 1-15         |                              | Active - Pin drives SPDIFOut1 data                                         |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  | 0                   | 0                   | -            |                              | Active - Pin drives 0                                                      |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  | 0                   | 1                   | -            |                              | Active - Pin drives 0                                                      |   |                                                      |                                                      |                                                      |

| D1-D2                 | De-Asserted<br>(High) | 0               | 0               | 1                | 1                   | 0                   | -            | SPDIF                        | Active - Pin drives SPDIF-format, but data is zeroes                       |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  | 1                   | 1                   | -            |                              | Active - Pin drives SPDIF-format, but data is zeroes                       |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  | 0                   | 0                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

|                       |                       |                 |                 |                  | 0                   | 1                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

| D3                    | D3 De-Asserted (High) |                 | 0               | 1                | 1                   | 1                   | 1            | 0                            | -                                                                          |   | Active - Pin drives SPDIF-format, but data is zeroes |                                                      |                                                      |

|                       |                       |                 |                 |                  | 1                   | 1                   | -            |                              | Active - Pin drives SPDIF-format, but data is zeroes                       |   |                                                      |                                                      |                                                      |

| D3cold                | De-Asserted<br>(High) | 0               | 0               | 1                | -                   | -                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

| D4                    | De-Asserted<br>(High) | 0               | 0               | 1                | -                   | -                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

| D5                    | -                     | -               | -               | -                | -                   | -                   | -            |                              | Hi-Z                                                                       |   |                                                      |                                                      |                                                      |

Table 6. SPDIF OUT 0 or 1 Behavior

## 2.5. SPDIF Input

SPDIF IN can operate at 44.1 KHz, 48 KHz, or 96 KHz, and implements internal Jack Sensing (Port presence Detect).

A sophisticated digital PLL allows automatic rate detection and accurate data recovery. The ability to directly accept consumer SPDIF voltage levels eliminates the need for costly external receiver ICs.

Status flags from the input stream are updated only after the entire valid block has been received (or at least when all bits of a particular status flag have been received) to ensure that software does not read an invalid mixture of old and new data.

In general, the SPDIF input block does not alter the data received. However, it is sometimes necessary to alter the data when the converter widget settings do not match the stream format. The following table outlines a few cases and the expected behavior.

Port presence detect for SPDIF\_IN operates differently from other ports. Once the PLL has locked and valid framing (no errors) has been detected, then the port presence detect bit is set. In D3, and D3 without a clock, it is not possible to check for proper framing. Monitoring of activity (rising and falling edges) is sufficient to verify a change in connectivity in D3. If no clock is present, then the internal oscillator is used until a clock is restored. When the HD Audio bus is in a low power state (reset asserted and clock stopped) the CODEC will generate a Power State Change Request when a change in SPDIF\_IN port connectivity is sensed and then generate an unsolicited response after the HD Audio link has been brought out of a low power state and the device has been enumerated. Per HDA015-B, this will take less than 10mS.

| Conflict                                                                                                  | Behavior                                                                                                                                                                                                                                                                                   | Resolution                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Converter widget rate does not equal the stream rate                                                      | Although the SPDIF input block is designed to handle inputs slightly above or below the programmed rate, samples may be lost if the input rate is much higher than the rate programmed into the converter widget.                                                                          | Program the converter widget with the same rate as indicated by the input stream.                                                                                                                                                                                                                                                               |

| Converter widget programmed for a word length less than the word length provided by the input stream      | If the input stream indicates non PCM data, the data will be truncated to the requested word length. If LPCM data is indicated in the input stream, the CODEC will round the received data to the requested length. <sup>1</sup>                                                           | Program the converter widget with the word length indicated in the input stream.                                                                                                                                                                                                                                                                |

| Converter widget programmed with a word length greater than the word length provided by the input stream. | Regardless of content, 24 bits per channel of data will be transferred from the SPDIF input stream to the HD Audio bus interface. Truncation or rounding to the requested word length will be handled as described as above. Any non-zero data in the incoming stream will cause problems. | Program the converter widget with the word length indicated in the input stream.  Although not recommended, application or driver software may program the converter widget with a word length of 24 bits, truncate the input to the word length indicated by the input stream, then right extend the data using 0s to the desired word length. |

Table 7. SPDIF Behavior

Rounding may be disabled by setting the disable bit (AFG vendor specific verb -see widget list) or setting the SPDIF\_IN converter widget Frmt StrmType field to 1 (non-PCM)

## 2.6. Mono Output

The Mono Out port source selection, power state, and mute characteristics are all independently controlled by the mono output port controls. The mono output pin is not available on the 40-pin package options.

The following sources are available for the Mono Out pin:

- DAC0 Output: When selected (by using the port connection list), the DAC0 left and right outputs are summed together.

- DAC1 Output: When selected (by using the port connection list), the DAC1 left and right outputs are summed together.

- Mixer Output: When selected (by using the port connection list), the mixer left and right outputs are summed together.

The stereo inputs are scaled by -6dB and then summed to provide an output that is the average of the two inputs. The full scale output at mono out is designed to be about 0dBV. Like the stereo line and headphone outputs, it is not possible to adjust to a +3dBV output level using a vendor defined verb.

## 2.7. Analog Mixer

The mixer supports independent gain (-34.5 to +12dB in 1.5dB steps) on each input as well as independent mutes on each input. The following inputs are available: The output of the mixer may be sent to the ADC where the ADC record gain can adjust the volume. If the output of the mixer is sent to an analog port, then a separate volume control is provided to adjust the output volume. This mixer output volume control supports a gain range of -46.5dB to 0dB in 1.5dB steps. (Selecting -46.5dB will automatically mute the output.)

- Port A

- Port B

- Port C

- Port E (not available on 40-pin option)

- Port F

- DAC0

- DAC1

## 2.8. ADC Multiplexers

The codec implements 2 ADC input multiplexers. These multiplexers incorporate the ADC record gain function (-16 to +30dB gain in 1dB steps) as an output amp and allow a preselection of one of these possible inputs:

- Port A

- Port B

- Port C

- Port E (not available on 40-pin option)

- Port F

- Mixer Output

- DMIC 0

- DMIC 1

## 2.10. Power Management

The HD Audio specification defines power states, power state widgets, and power state verbs. Power management is implemented at several levels. The Audio Function Group (AFG), all converter widgets, and all pin complexes support the power state verb F05/705. Converter widgets are active in D0 and inactive in D1-D3.

The following table describes what functionality is active in each power state.

| Function                  | D0 | D1 <sup>1</sup> | D2           | D3                     | D3cold                 | Vendor<br>Specific D4 <sup>2</sup> | Vendor<br>SpecificD5 <sup>2</sup> |

|---------------------------|----|-----------------|--------------|------------------------|------------------------|------------------------------------|-----------------------------------|

| SPDIF Outputs             | On | On              | On<br>(idle) | On (idle) <sup>6</sup> | Off                    | Off                                | Off                               |

| SPDIF Input               | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| Digital Microphone inputs | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| DAC                       | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| D2S                       | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| ADC                       | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| ADC Volume Control        | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| Ref ADC                   | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| Analog Clocks             | On | Off             | Off          | Off                    | Off                    | Off                                | Off                               |

| GPIO pins                 | On | On              | On           | On <sup>6</sup>        | On                     | On                                 | Off                               |

| VrefOut Pins              | On | On              | Off          | Off                    | Off                    | Off                                | Off                               |

| Input Boost               | On | On              | Off          | Off                    | Off                    | Off                                | Off                               |

| Analog mixer              | On | On              | Off          | Off                    | Off                    | Off                                | Off                               |

| Mixer Volumes             | On | On              | Off          | Off                    | Off                    | Off                                | Off                               |

| Analog PC_Beep            | On | On              | On           | On                     | Off                    | Off                                | Off                               |

| Digital PC_Beep           | On | On              | On           | On <sup>6</sup>        | Off                    | Off                                | Off                               |

| Lo/HP Amps                | On | On              | On           | Low Drive <sup>3</sup> | Low Drive <sup>3</sup> | Low Drive <sup>3</sup>             | Off                               |

| VAG amp                   | On | On              | On           | Low Drive <sup>4</sup> | Low Drive              | Low Drive                          | Off                               |

| Port Sense                | On | On              | On           | On <sup>5</sup>        | Off                    | Off                                | Off                               |

| Reference Bias generator  | On | On              | On           | On                     | On                     | On                                 | Off                               |

| Reference Bandgap core    | On | On              | On           | On                     | On                     | On                                 | Off                               |

| HD Audio-Link             | On | On              | On           | On <sup>6</sup>        | Limited <sup>7</sup>   | Off                                | Off                               |

| PLL                       | On | On              | On           | Off <sup>8</sup>       | Off <sup>9</sup>       | Off                                | Off                               |

Table 3. Power Management

- 1. No DAC or ADC streams are active. Analog mixing and loop thru are supported.

- 2. D4 and D5 power states are entered only when D3cold is requested. D4 and D5 may be viewed as D3cold behavioral options.

- 3. VAG is kept active when ports are disabled or in D3/D3cold/D4. PC\_Beep is supported in D3 but may be attenuated and distorted depending on load impedance.

- 4. VAG is always ramped up and down gradually, except in the case of a sudden power removal. VAG is active in D2/D3 but in a low power state.

- 5. Both AVDD and DVDD must be available for Port Sense to operate.

- Not active if BITCLK is not running (Controller in D3), but can signal power state change request (PME)

- 7. Only double function group reset verbs and link reset supported per ECR15b

#### FOUR CHANNEL HD AUDIO CODEC WITH DUAL CAPLESS HEADPHONE AMPLIFIERS

- 8. PLL remains on if SPDIF\_Out Keep Alive is enabled. PLL disabled only after DAC fading is complete and SDM has settled.

- 9. PLL disabled only after DAC fading is complete and SDM has settled.

The D3-default state is available for HD Audio compliance. The programmable values, exposed via vendor-specific settings, are under TSI Device Driver control for further power reduction. The analog mixer, line and headphone amps, port presence detect, and internal references may be disabled using vendor specific verbs. Use of these vendor specific verbs will cause pops.

The default power state for the Audio Function Group after reset is D3.

## 2.11. AFG D0

The AFG D0 state is the active state for the device. All functions are active if their power state (if they support power management at their node level) has been set to D0.

#### 2.12. AFG D1

D1 is a lower power mode where all converter widgets are disabled. Analog mixer and port functions are active. The part will resume from theD1 to theD0 state within 1 mS.

#### 2.13. AFG D2

The D2 state further reduces power by disabling the mixer and port functions. The port amplifiers and internal references remain active to keep port coupling caps charged and the system ready for a quick resume to either the D1 or D0 state. The part will resume from the D2 state to the D0 state within 2mS.

#### 2.14. AFG D3

The D3-default state is available for HD Audio compliance. All converters are shut down. Port amplifiers and references are active but in a low power state to prevent pops. Resume times may be longer than those from D2, but still less than 10mS to meet Intel low power goals. The default power state for the Audio Function Group after power is applied is D3.

While in AFG D3, the HD Audio controller may be in a D0 state (HD Audio bus active) or in a D3 state (HD Audio bus held in reset with no Bit\_Clk, SData\_Out, or Sync activity.) The expected behavior is as follows (see the HDA015-B section for more information):

| Function                          | HDA Bus active       | HDA Bus stopped                                |

|-----------------------------------|----------------------|------------------------------------------------|

| Port Presence Detect state change | Unsolicited Response | Wake Event followed by an unsolicited response |

| GPIO state change                 | Unsolicited Response | Wake Event followed by an unsolicited response |

#### 2.14.1. AFG D3cold

The D3cold power state is the lowest power state available that does not use vendor specific verbs. While in D3cold, the CODEC will still respond to bus requests to revert to a higher power state (double AFG reset, link reset). However, audio processing, port presence detect, and other functions are disabled. Per the HD Audio bus HDA015-B, the D3cold state is intended to be used just prior to removing power to the CODEC. Typically, power will be removed within 200mS. However, the codec may exit from the D3cold state by generating 2, back-to-back, AFG reset events. Resume time from D3cold is less than 200mS.

## 2.15. Vendor Specific Function Group Power States D4/D5

The codec introduces vendor specific power states. A vendor defined verb is added to the Audio Function Group that combines multiple vendor specific power control bits into logical power states for use by the audio driver. The 2 states defined offer lower power than the 5 existing states defined in the HD Audio specification and HDA015-B. The Vendor Specific D4 state provides lower digital power consumption relative to D3cold by disabling HD Audio link responses. Vendor specific D5 further reduces power consumption on the digital supply by turning off GPIO drivers, and reduces analog power consumption by turning off all analog circuitry except for reset circuits.

States D4/D5 are not entered until D3cold has been requested so are actually D3cold options rather than true, independent, power states. Software can pre-program the D4 or D5 state as a re-definition of how the part will behave when the D3cold power state is requested or software may enter D3cold, then set the D4 or D5 before performing the power state get command. The preferred method is to request D3cold, then select D4 or D5 as desired. This will reduce the severity of pops encountered when entering D4 or D5.

Both power states require a link reset or removal of DVDD to exit.

The CODEC may pop when using these verbs and transition times to an active state (D1 or D0 for example) may take several seconds.

## 2.16. Vendor Specific Function Group Power State "D5 Kill"

Vendor specific "D5 Kill" places the device in a low power, non responsive, state that is intended to disable the CODEC when, for security reasons, it is desired that no audio playback or recording take place.

State "D5 Kill" is not entered until D3cold has been requested. Software pre-programs both the D4 and D5 state request bits (D4 and D5 = 1) then request D3cold. After responding to the Function Group Power State Get verb (needed to enter D3cold), the CODEC will no longer respond to any link activity. The only way to exit this state is to remove power (Power on reset will set the power state to D3.)

"D5 Kill" is identical to vendor specific D5 with the exception that the CODEC will only exit this state when power is removed.

## 2.17. Low-voltage HDA Signaling

The codec is compatible with either 1.5V or 3.3V HDA bus signaling; in the 48-QFN package the voltage selection is done dynamically based on the input voltage of DVDD\_IO.

DVDD\_IO is currently not a logic configuration pin, but rather provides the digital power supply to be used for the HDA bus signals.

When in 1.5V mode, the codec can correctly decode BITCLK, SYNC, RESET# and SDO as they operate at 1.5V; additionally it will drive SDI and SDO at 1.5V. None of the GPIOs are affected, as they always function at their nominal voltage (DVDD or AVDD).

## 2.18. Multi-channel capture

The capability to assign multiple ADC Converters to the same stream is supported to meet the microphone array requirements of Vista and future operating systems. Single converter streams are

still supported this is done by assigning unique non zero Stream IDs to each converter. All capture devices (ADCs 0 and 1) may be used to create a multi-channel input stream. There are no restrictions regarding digital microphones.

The ADC Converters can be associated with a single stream as long the sample rate and the bits per sample are the same. The assignment of converter to channel is done using the "CnvtrlD" widget and is restricted to even values. The ADC converters will always put out a stereo sample and therefore require 2 channels per converter.

The stream will not be generated unless all entries for the targeted converters are set identically, and the total number of assigned converter channels matches the value in the NmbrChan field. These are listed the "Multi-Converter Stream Critical Entries." table.

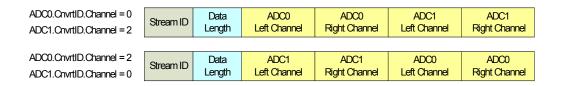

An example of a 4 Channel Steam with ADC0 supplying channels 0&1 and ADC1 supplying channels 2 & 3 is shown below. A 4 Channel stream can be created by assigning the same non-zero stream id "Strm= N" to both ADC0 and ADC1. The sample rates must be set the same and the number of channels must be set to 4 channels "NmbrChan = 0011".

| ADC1 CnvtrID | (NID = 0x08) |        |

|--------------|--------------|--------|

|              | [3:0]        | Ch = 2 |

| ADC0 CnvtrID | (NID = 0x07) |        |

|              | [3:0]        | Ch=0   |

Table 4. Example channel mapping

Figure 1. Multi-channel capture

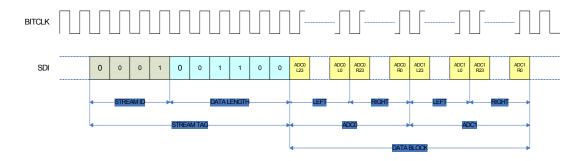

The following figure describes the bus waveform for a 24-bit, 48KHz capture stream with ID set to 1.

Figure 2. Multi-channel timing diagram

| ADC[1:0] Cnvtr | Bit Number | Sub Field Name | Description                                          |

|----------------|------------|----------------|------------------------------------------------------|

|                | [15]       | StrmType       | Stream Type (TYPE):                                  |

|                |            |                | 0: PCM                                               |

|                |            |                | 1: Non-PCM (not supported)                           |

|                | [14]       | FrmtSmplRate   | Sample Base Rate                                     |

|                |            |                | 0= 48kHz                                             |

|                |            |                | 1=44.1KHz                                            |

|                | [13:11]    | SmplRateMultp  | Sample Base Rate Multiple                            |

|                |            |                | 000=48kHz/44.1kHz or less                            |

|                |            |                | 001= x2                                              |

|                |            |                | 010= x3 (not supported)                              |

|                |            |                | 011= x4 192kHz only, 176.4 not supported             |

|                |            |                | 100-111= Reserved                                    |

|                | [10:8]     | SmplRateDiv    | Sample Base Rate Divisor                             |

|                |            |                | 000= Divide by 1                                     |

|                |            |                | 001= Divide by 2 (not supported)                     |

|                |            |                | 010= Divide by 3 (not supported)                     |

|                |            |                | 011= Divide by 4 (not supported)                     |

|                |            |                | 100= Divide by 5 (not supported)                     |

|                |            |                | 101= Divide by 6 (not supported)                     |

|                |            |                | 110= Divide by 7 (not supported)                     |

|                |            |                | 111= Divide by 8 (not supported)                     |

|                | [6:4]      | BitsPerSmpl    | Bits per Sample                                      |

|                |            |                | 000= 8 bits (not supported)                          |

|                |            |                | 001= 16 bits                                         |

|                |            |                | 010= 20 bits                                         |

|                |            |                | 011= 24 bits                                         |

|                |            |                | 100-111= Reserved                                    |

|                | [3:0]      | NmbrChan       | Number of Channels                                   |

|                |            |                | Number of channels for this stream in each "sample   |

|                |            |                | block" of the "packets" in each "frame" on the link. |

|                |            |                | 0000=1 channel (not supported)                       |

|                |            |                | 0001 = 2 channels                                    |

|                |            |                |                                                      |

|                |            |                | 1111= 16 channels.                                   |

|                | [7:4]      | Strm           | Software-programmable integer representing link      |

|                |            |                | stream ID used by the converter widget. By conven-   |

|                | [0.0]      | Oh             | tion stream 0 is reserved as unused.                 |

|                | [3:0]      | Ch             | Integer representing lowest channel used by con-     |

|                |            |                | verter.                                              |

|                |            |                | 0 and 2 are valid Entries                            |

|                |            |                | If assigned to the same stream, one ADC must be      |

|                |            |                | assigned a value of 0 and the other ADC assigned a   |

|                |            |                | value of 2.                                          |

Table 5: Multi-channel

## 2.19. EAPD

The EAPD pin (pin 47) is a dedicated, bi-directional control pin. Although named External Amplifier Power Down (EAPD) by the HD Audio specification, this pin operates as an external amplifier power up signal. The EAPD value is reflected on the EAPD pin; a 1 causes the external amplifier to power up (equivalent to D0), and a 0 causes it to power down (equivalent to D3.) When the EAPD value =

1, the EAPD pin must be placed in a state appropriate to the current power state of the associated Pin Widget even though the EAPD value (in the register) may remain 1. The pin defaults to an open-drain configuration (an external pull-up is recommended.)

Per the HD Audio specification and HDA015-B, multiple ports may control EAPD. The EAPD pin assumes the highest power state of all the EAPD bits in all of the pin complexes. The default value of EAPD is 1 (powered on), but the FG power state will override and the pin will be low.

Vendor specific verbs are available to configure this pin. These verbs retain their values across link and single function group resets but are set to their default values by power on reset:

| MODE1 | MODE0 | EAPD Pin Function | Description                                                            |

|-------|-------|-------------------|------------------------------------------------------------------------|

| 0     | 0     | Open Drain I/O    | Value at pin is wired-AND of EAPD bit and external signal.(default)    |

| 0     | 1     | CMOS Output       | Value of EAPD bit in pin widget is forced at pin                       |

| 1     | 0     | CMOS Input        | External signal controls internal amps. EAPD bit in pin widget ignored |

| 1     | 1     | CMOS Input        | External signal controls internal amps. EAPD bit in pin widget ignored |

Table 6. EAPD Pin Mode Select

| Control Flag      | Description                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| EAPD PIN MODE 1:0 | Defines if EAPD pin is used as input, output, or bi-directional port (Open Drain)                                           |

| HP SD             | 0 = Amp controlled by EAPD pin only (default) / 1 = Amp controlled by power state (pin and FG) only                         |

| HP SD MODE        | 0 = Amp will mute when disabled (default) / 1 = Amp will shut down (enter a low power state) when disabled                  |

| HP SD INV         | 0 = AMP will power down (or mute) when EAPD pin is low (default) / 1 = Amp will power down (or mute) when EAPD pin is high. |

Table 7. Control bit descriptions for BTL amplifier and Headphone amplifier enable configurations

| HP SD | HP SD<br>MODE | HP SD INV | EAPD Pin<br>State | Headphone Amp State                                                                             |

|-------|---------------|-----------|-------------------|-------------------------------------------------------------------------------------------------|

| 0     | 0             | 0         | 0                 | Amplifier is mute (default <sup>1</sup> )                                                       |

| 0     | 0             | 0         | 1                 | Amplifier is active                                                                             |

| 0     | 0             | 1         | 0                 | Amplifier is active                                                                             |

| 0     | 0             | 1         | 1                 | Amplifier is mute                                                                               |

| 0     | 1             | 0         | 0                 | Amplifier is in a low power state                                                               |

| 0     | 1             | 0         | 1                 | Amplifier is active                                                                             |

| 0     | 1             | 1         | 0                 | Amplifier is active                                                                             |

| 0     | 1             | 1         | 1                 | Amplifier is in a low power state                                                               |

| 1     | 0             | NA        | NA                | Amplifier follows pin/function group power state and will mute when disabled                    |

| 1     | 1             | NA        | NA                | Amplifier follows pin/function group power state and will enter a low power state when disabled |

Table 8. BTL Amp Enable Configuration

1. EAPD bit is set to one by default but the EAPD state is 0 after power-on reset because the function group is not in D0. The state after a single or double function group reset will be compliant with HDA015-B.

Each Headphone port has its own configuration bits for SD, SD MODE, and SD INV.

| В | nalog<br>BEEP<br>nabled | EAPD Pin value <sup>1</sup>                                   | Description                                                                                                                                                |

|---|-------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 0                       | Forced to low when in D2 or D3                                | Follows description in HD Audio spec. External amplifier is shut down when pin or function group power state is D2 or D3 independent of value in EAPD bit. |

|   | 1                       | Forced low in D2 or D3<br>unless port is enabled as<br>output | Power state is ignored if port is enabled as output and port EAPD=1 to allow PC_Beep support in D2 and D3                                                  |

#### Table 9. EAPD Analog PC\_Beep behavior

1. When pin is enabled as Open Drain or CMOS output.

| AFG<br>Power<br>State | RESET#             | Analog<br>PC_BEEP    | Port Power<br>State | Pin Behavior                                                                                                     |

|-----------------------|--------------------|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------|

| D0-D3                 | Asserted (Low)     | Enabled <sup>1</sup> | -                   | Active high immediately after power on, otherwise the previous state is retained across FG and link reset events |

| D0-D3                 | Asserted (Low)     | Disabled             | -                   | The previous state is retained across FG and link reset events                                                   |

| D0                    | De-Asserted (High) | -                    | -                   | Active - Pin reflects EAPD bit unless held low by external source.                                               |

| D1                    | De-Asserted (High) | -                    | D0-D1               | Active - Pin reflects EAPD bit unless held low by external source.                                               |

| D2                    | De-Asserted (High) | Disabled             | D0-D2               | Pin forced low to disable external amp                                                                           |

| D2                    | De-Asserted (High) | Enabled              | D0-D2               | Active - EAPD Pin high if any port EAPD bit =1 and that port also enabled as output.                             |

| D3                    | De-Asserted (High) | Disabled             | D0-D3               | Pin forced low to disable external amp                                                                           |

| D3                    | De-Asserted (High) | Enabled              | D0-D3               | Active - EAPD Pin high if any port EAPD bit=1 and that port also enabled as output.                              |

| D3cold                | De-Asserted (High) | -                    | -                   | Pin forced low to disable external amp                                                                           |

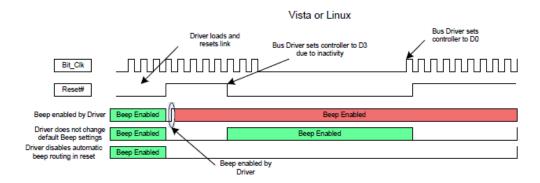

| D4                    | De-Asserted (High) | -                    | -                   | Pin forced low to disable external amp                                                                           |