# CGD15HB62LP

#### **Dual Channel Differential Isolated Gate Driver**

Cree CAS325M12HM2 C2M SiC Half Bridge Module Optimized

| <b>V</b> <sub>Drive</sub> | +18/-5 V |

|---------------------------|----------|

| l <sub>G</sub>            | ±14 A    |

| R <sub>G</sub>            | 5 Ω      |

#### **Features**

- Optimized for Cree's High Performance CAS325M12HM2 Half Bridge Power Modules

- High-Frequency, Ultra-Fast Switching Operation

- On Board 3 W or 6 W Isolated Power Supplies

- Configurable UVLO with Hysteresis

- Direct Mount Low Inductance Design

- On-Board Overcurrent, Overlap, and Reverse Polarity Protection

- Differential Inputs for Increased Noise Immunity

- Differential to Single-Ended Daughter Board Available Upon Request

#### For Use with Cree Module

CAS325M12HM2, 1200 V, 325 A Module Half Bridge CPM2 Variants for Module Junction Temperatures up to 175 °C

#### **Applications**

DC Bus Voltages up to 1000 V

#### **Package**

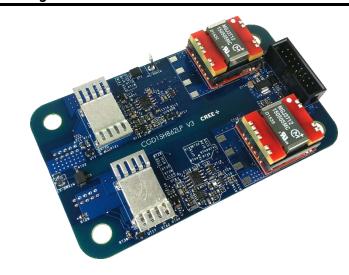

| Part Number | Package | Marking        |

|-------------|---------|----------------|

| CGD15HB62LP | PCBA    | CGD15HB62LP V3 |

#### **Maximum Ratings**

| Symbol              | Parameter                     | Value       | Unit | Test Conditions                 |

|---------------------|-------------------------------|-------------|------|---------------------------------|

| V <sub>DC</sub>     | Supply Voltage                | -0.5 to 18  | V    |                                 |

| Vı                  | Logic Level Inputs            | -0.5 to 5.5 | V    |                                 |

| I <sub>0</sub>      | Output Peak Current           | ±14         | Α    | T <sub>A</sub> = 25 °C          |

| I <sub>O(avg)</sub> | Output Average Current        | ±4          | A    | 14-25 C                         |

| F <sub>max</sub>    | Maximum Switching Frequency   | 115         | kHz  | 3 W Power Supply + CAS325M12HM2 |

| T <sub>op</sub>     | Ambient Operating Temperature | -50 to 95   | °C   |                                 |

| T <sub>stg</sub>    | Storage Temperature           | -50 to 125  | C    |                                 |

#### **Gate Driver Electrical Characterization**

| Symbol                 | Parameter                                          | Min.  | Тур.                                      | Max.  | Unit                                  | Test Conditions                                             |

|------------------------|----------------------------------------------------|-------|-------------------------------------------|-------|---------------------------------------|-------------------------------------------------------------|

| $V_{DC}$               | Supply Voltage                                     | 9     | 12                                        | 18    |                                       |                                                             |

|                        | Secondary UVLO Inactive Level                      | +13.5 | +14                                       | +14.5 | 1                                     |                                                             |

| $V_{\text{UVLO}}$      | Secondary UVLO Active Level                        | +11.2 | +12                                       | +12.7 | 1                                     |                                                             |

|                        | Secondary UVLO Hysteresis                          |       | 2                                         |       | V                                     |                                                             |

| V <sub>IH</sub>        | High Level Logic Input Voltage                     | 3.5   |                                           | 5.5   |                                       | Cinale Federal Institute                                    |

| V <sub>IL</sub>        | Low Level Logic Input Voltage                      | 0     |                                           | 1.5   | 1                                     | Single-Ended Inputs                                         |

| V <sub>IDCM</sub>      | Differential Input Common Mode<br>Range            | -7    | -                                         | +12   |                                       | Differential Inputs                                         |

| $V_{IDTH}$             | Differential Input Threshold<br>Voltage            | -200  | -125                                      | -50   | mV                                    | $V_{\text{ID}} = V_{\text{Pos-Line}} - V_{\text{Neg-Line}}$ |

| $V_{ODH}$              | Differential Output High Level                     | 2.2   | 3.4                                       |       |                                       | I <sub>OD</sub> = -20 mA                                    |

| $V_{\text{ODL}}$       | Differential Output Low Level                      |       | 0.2                                       | 0.4   |                                       | I <sub>OD</sub> = 20 mA                                     |

| $V_{\text{OD}}$        | Differential Output Magnitude                      | 2     | 3.1                                       |       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | R <sub>L</sub> =100 Ω                                       |

| V <sub>GATE,HIGH</sub> | High Level Output Voltage                          |       | +18                                       |       | V                                     |                                                             |

| $V_{GATE,LOW}$         | Low Level Output Voltage                           |       | -5                                        |       |                                       |                                                             |

| V <sub>IOWM</sub>      | Working Isolation Voltage                          |       | 1500                                      |       |                                       | V <sub>RMS</sub>                                            |

| C <sub>ISO</sub>       | Isolation Capacitance                              |       | 17                                        |       | pF                                    | Per Channel                                                 |

| CMTI                   | Common Mode Transient<br>Immunity                  | 100   |                                           |       | kV/µs                                 |                                                             |

| R <sub>GIC-ON</sub>    | Output Resistance <sup>1</sup>                     |       | 0.4                                       | 1.5   | - Gate Drive IC                       |                                                             |

| $R_{\text{GIC-OFF}}$   | Output Resistance <sup>1</sup>                     |       | 0.3                                       | 1.2   | Ω                                     | Gate Drive IC                                               |

| R <sub>GEXT-ON</sub>   | External Output Resistance <sup>2</sup>            |       | 4.99                                      |       | 12                                    | External SMD Resistor                                       |

| R <sub>GEXT-OFF</sub>  | External Output Resistance <sup>2</sup>            |       | 4.99                                      |       |                                       |                                                             |

| D <sub>VF-OFF</sub>    | Turn-off Diode Forward Voltage                     | 0.62  | 0.67                                      | 0.82  | V                                     |                                                             |

| t <sub>ON</sub>        | Output Rise Time                                   |       | 250                                       |       |                                       | C <sub>Load</sub> = 19 nF                                   |

| t <sub>OFF</sub>       | Output Fall Time                                   |       | 140                                       |       |                                       | From 10% to 90%                                             |

| t <sub>PHL/PLH</sub>   | Propagation Delay                                  |       | 75                                        |       | ns                                    |                                                             |

| t <sub>PD</sub>        | Over-current Propagation Delay to FAULT Signal Low |       | 40                                        |       |                                       | Does Not Include<br>Blanking                                |

| R <sub>SS</sub>        | Soft-Shutdown Resistance <sup>3</sup>              |       | 30.1                                      |       | Ω                                     |                                                             |

| t <sub>OFF-SS</sub>    |                                                    |       | Output pulled low through R <sub>SS</sub> |       |                                       |                                                             |

<sup>&</sup>lt;sup>1</sup> Output resistance of totem pole IC

$<sup>^2</sup>$  Additional output resistance is added with SMD resistors. A diode is provided to allow control of turn-off separately. The diode makes the effective turn-off resistance be the parallel combination of the  $R_{\text{GEXT-ON}}$  and  $R_{\text{GEXT-OFF}}$  while the turn-on effective resistance is  $R_{\text{GEXT-ON}}$ . Standard value is 4.99  $\Omega$  for both turn-on and turn-off. See Figure 1 for configuration.

<sup>&</sup>lt;sup>3</sup> Soft-Shutdown Resistor will safely turn off the Gate in the event an over-current is detected by the Desaturation Protection circuit.

# **Input Connector Information**

| Pin<br>Number | Name          | Description                                                                                                                                                                                        |

|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDC           | Power Supply Input Pin                                                                                                                                                                             |

| 2             | Common        | Common                                                                                                                                                                                             |

| 3             | HS-P (*)      | Positive Line of 5 V Differential High Side PWM Signal Pair. Terminated Into 250 Ω.                                                                                                                |

| 4             | HS-N (*)      | Negative Line of 5 V Differential High Side PWM Signal Pair. Terminated Into 250 Ω.                                                                                                                |

| 5             | LS-P (*)      | Positive Line of 5 V Differential Low Side PWM Signal Pair.<br>Terminated Into 250 Ω.                                                                                                              |

| 6             | LS-N (*)      | Negative Line of 5 V Differential Low Side PWM Signal Pair.<br>Terminated Into 250 Ω.                                                                                                              |

| 7             | FAULT - P (*) | Positive Line of 5 V Differential Fault Condition Signal Pair. Drive Strength 20 mA.                                                                                                               |

| 8             | FAULT - N (*) | Negative Line of 5 V Differential Fault Condition Signal Pair. Drive Strength 20 mA.                                                                                                               |

| 9             | RTD-P (*)     | Positive Line of 5 V Temperature Dependent Resistor Output Signal Pair.  Drive Strength 20 mA. Temperature Measurement is Encoded Via PWM.                                                         |

| 10            | RTD-N (*)     | Negative Line of 5 V Temperature Dependent Resistor Output Signal Pair. Drive Strength 20mA. Temperature Measurement is Encoded Via PWM.                                                           |

| 11            | PS-Dis        | Pull Down to Disable Power Supply. Pull Up, or Leave Floating to Enable. Gate-Source will be Connected with 10 k $\Omega$ when disabled.                                                           |

| 12            | Common        | Common                                                                                                                                                                                             |

| 13            | PWM-EN        | Pull Down to Disable PWM Input Logic. Pull Up/Leave floating to enable. Gate-source will be held low through gate resistor if power supplies are enabled.                                          |

| 14            | Common        | Common                                                                                                                                                                                             |

| 15            | OC-EN         | Over-current Protection Enable. Pull down to disable detection of over-current fault. PWM and UVLO will continue to function. Pull up or leave floating to enable detection of over-current fault. |

| 16            | Common        | Common                                                                                                                                                                                             |

<sup>(\*)</sup> Inputs 3 – 10 are differential pairs.

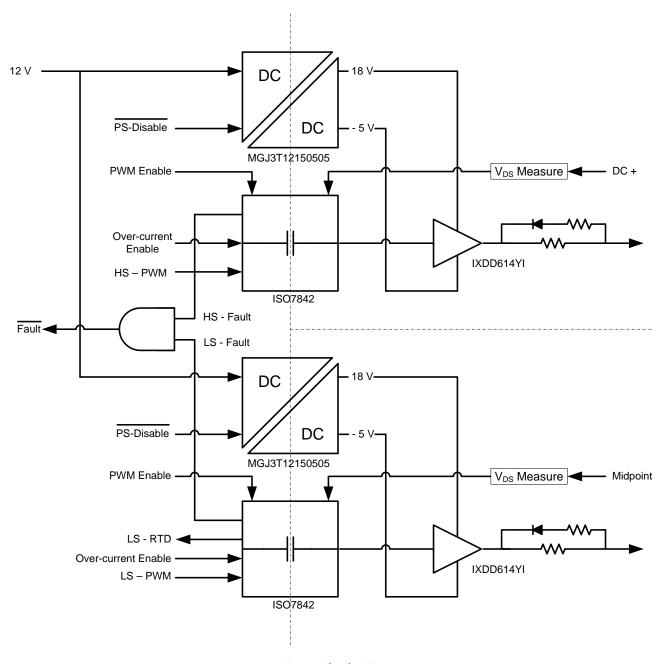

## **Block Diagram**

Fig 1. Block Diagram

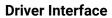

Fig 2. Top View

| Connector | Name         | Description                                                                                                    |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------|

| JT2       | Signal Input | Description in Input Connection Information                                                                    |

| JT1       | HS-Drain     | High Side Over-current protection connector Connect to DC +                                                    |

| JT3       | LS-Drain     | Low Side Over-current protection connector Connect to the Midpoint or populate RT19 with a 0 $\Omega$ resistor |

| JB1       | HS-GS        | Red – Gate<br>Green – Source                                                                                   |

| JB2       | LS-GS        | Red – Gate<br>Green – Source<br>Blue – RTD                                                                     |

#### **Signal Description**

- **PWM Signals**: High side and low side PWM must be differential signals<sup>4</sup>. The termination impedance of the differential receiver is 250 Ω. A reference single-ended to differential converter is available as an optimized companion product. Overlap protection is provided to prevent both the high side and low side gates from turning on simultaneously. The overlap protection should not be used as a dead time generator.

- **FAULT Signal**: The fault signal is a differential output<sup>4</sup> with a maximum drive strength of 20mA. A high signal (positive line > negative line) means there are no fault conditions for either gate driver channel. This signal will be low if a UVLO or over-current fault is detected on either channel. See below for further description for what the individual faults indicate.

- UVLO Fault: The UVLO circuit detects when the output rails of the isolated DC/DC converter falls below safe operating conditions for the gate driver. A UVLO fault indicates that the potential between the split output rails has fallen below the UVLO active level. The gate for the channel where the fault occurred will be pulled low through R<sub>G</sub> for the duration of the fault regardless of the PWM input signal. The fault will automatically clear once the potential has risen above the UVLO inactive level. There is hysteresis for this fault to ensure safe operating conditions, and the inactive and active regions can be configured through on-board resistors. The UVLO faults for both channels are combined along with the over-current fault in the FAULT output signal.

- Over-Current Fault: An over-current fault is an indication of an over-current event in the SiC power module. The over-current protection circuit measures the drain-source voltage, and the fault will indicate if this voltage has risen above a level corresponding to the safe current limit. A drain sense connection is provided by quick-connect spade connectors for both high side and low side. The low side drain connection can optionally be connected on-board to the high side source through jumper RT19. When a fault has occurred the corresponding gate driver channel will be disabled, and the gate will be pulled down through a soft-shutdown resistor, R<sub>SS</sub><sup>3</sup>. The drain-source limit can be configured through on-board resistors. The over-current protection is enabled by default, but it can be disabled by pulling the OC-EN pin low. The gate driver will operate correctly with this protection disabled. The over-current fault is latched upon detection and must be cleared by the user with a low pulse of at least 2.5 ns on the OC-EN signal.

- RTD Signal: RTD output is a differential signal<sup>4</sup> that measures the resistance of the RTD integrated into XAS325M12HM2 modules. The signal is a 50 kHz PWM that encodes the resistance of the RTD. The minimum and maximum duty cycles are 5% and 95% respectively to guarantee a signal is always present. The approximate temperature of the module can be determined from this resistance<sup>5</sup>. The module temperature can be calculated using the formula,  $T_{RTD} = 5.42 * (DutyCycle) 244 °C$ .

- PS-Dis Signal: PS-DIS signal disables the output of the isolated DC/DC converters for the two channels.

It is a single-ended input that must be pulled low to turn off the power supplies. This can be used for startup sequencing.

<sup>&</sup>lt;sup>4</sup> A single-ended to differential converter for both input and output is available as an optimized companion product.

<sup>&</sup>lt;sup>5</sup> See CAS325M12HM2 with Optional RTD Application Note for further description of the RTD measurements.

- **PWM-EN Signal**: This is a single-ended input that enables the PWM inputs for both channels. When this signal is pulled down the differential receivers for both channels are disabled and the gates will both be pulled low through R<sub>G</sub>. All protection circuitry and power supplies will continue to operate including FAULT and RTD outputs.

- Over-Voltage and Reverse Polarity Protection: Power input on pin 1 of connector JT2 features a Zener diode to protect the gate driver from damage by connecting a power source that exceeds the voltage rating of the gate driver. If over-voltage protection has occurred power should be removed to allow the PTC fuse to reset. There is also a diode in-line with the power input to protect against connecting a power source with positive and negative polarity reversed.

#### **Input Connector**

- SBH11-PBPC-D08-ST-BK

- Drain connector for Overcurrent Protection: TE Connectivity 735187-2

#### **Suggested Mating Parts**

- SFH210-PPPC-D08-ID-BK

- SFH11-PBPC-D08-ST-BK

- SFH11-PBPC-D08-RA-BK

- Drain connector for Overcurrent: TE Connectivity 2-520272-2

#### **Power Estimates**

The gate driver power required is calculated using the formula below. The gate charge is dependent on the datasheets of the module being driven. The gate driver voltage  $(V_{GD})$  is 23V for this gate driver. Once the required gate driver power is calculated the required input power can be calculated from the MGJ3T12150505MC and MGJ6T12150505MC efficiency curves on the power supplies datasheet. This calculation is for one channel of the gate driver.

$$P_{SW} = Q_G * F_{SW} * \Delta V_{GD}$$

$P_{SW}$ : gate driver power  $Q_G$ : total gate charge  $F_{SW}$ : switching frequency

$\Delta V_{GD}$ : total gate drive voltage ( $V_{GATE,HIGH} - V_{GATE,LOW}$ )

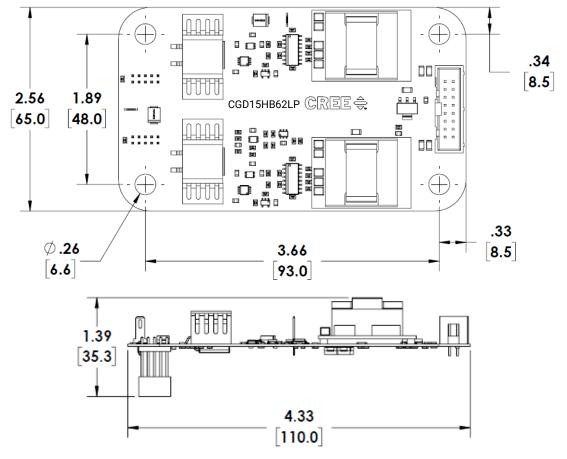

## Dimensions [in(mm)]

Fig 3. Dimensions

#### **Important Notes**

Suitability of this product for any application may depend on product parameters not specified in this document. Accordingly, buyers are cautioned to evaluate actual products against their needs and not to rely solely on the data and information presented in this document.

The product described has not been designed or tested for use in, and is not intended for use in, applications implanted into the human body or in applications in which failure of the product could lead to death, personal injury or property damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines, cardiac defibrillators or similar emergency medical equipment, vehicle navigation, communication or control systems, or air traffic control systems.

The product described is not eligible for Distributor Stock Rotation or Inventory Price Protection.

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru 4 moschip.ru 9