#### Is Now Part of

## ON Semiconductor®

## To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

September 2001 Revised December 2001

#### FIN1022

### 2 X 2 LVDS High Speed Crosspoint Switch

#### **General Description**

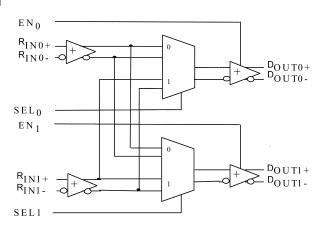

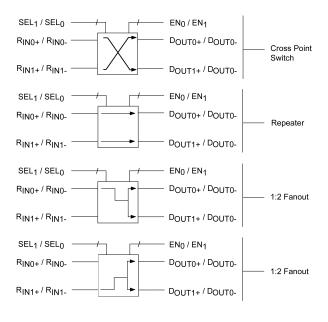

This non-blocking 2x2 crosspoint switch has a fully differential input to output data path for low noise generation and low pulse width distortion. The device can be used as a high speed crosspoint switch, 2:1 multiplexer, 1:2 demultiplexer or 1:2 signal splitter. The inputs can directly interface with LVDS and LVPECL levels.

#### **Features**

- Low jitter, 800 Mbps full differential data path

- Worst case jitter of 190ps with PRBS = 2<sup>23</sup> – 1 data pattern at 800 Mbps

- Rail-to-rail common mode range is 0.5V to 3.25V

- Worst case power dissipation is less than 126 mW

- Open-circuit fail safe protection

- Fast switch time of 1.1 ns typical

- 35 ps typical pin channel to channel skew

- 3.3V power supply operation

- Non-blocking switch

- LVDS receiver inputs accept LVPECL signals directly

- 7.5 kV HBM ESD protection

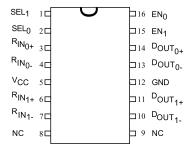

- 16-lead SOIC package and TSSOP package

- Inter-operates with TIA/EIA 644-1995 specification

- See the Fairchild Interface Solutions web page for cross reference information: www.fairchildsemi.com/products/interface/lvds.html

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                          |

|--------------|----------------|------------------------------------------------------------------------------|

| FIN1022M     | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| FIN1022MTC   | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code

#### **Logic Symbol**

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Name                              | Description                                                                                           |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|

| R <sub>IN0+</sub> , R <sub>IN1+</sub> | LVDS non-inverting data inputs                                                                        |

| R <sub>IN0-</sub> , R <sub>IN1-</sub> | LVDS inverting data inputs                                                                            |

| $D_{OUT0+},D_{OUT1+}$                 | LVDS non-inverting data outputs                                                                       |

| $D_{OUT0-}, D_{OUT1-}$                | LVDS inverting data outputs                                                                           |

| EN <sub>0</sub>                       | LVTTL input for enabling D <sub>OUT0+</sub> /D <sub>OUT0-</sub>                                       |

| EN <sub>1</sub>                       | LVTTL input for enabling D <sub>OUT1+</sub> /D <sub>OUT1-</sub>                                       |

| SEL <sub>0</sub>                      | LVTTL input for selecting $R_{IN0+}/R_{IN0-}$ or $R_{IN1+}/R_{IN1-}$ for output $D_{OUT0+}/D_{OUT0-}$ |

| SEL <sub>1</sub>                      | LVTTL input for selecting $R_{IN0+}/R_{IN0-}$ or $R_{IN1+}/R_{IN1-}$ for output $D_{OUT1+}/D_{OUT1-}$ |

| V <sub>CC</sub>                       | Power Supply                                                                                          |

| GND                                   | Ground                                                                                                |

#### **Function Table**

| Inputs           |                  |                 | Outputs         |                    |                    | Mode               |                    |                                                  |

|------------------|------------------|-----------------|-----------------|--------------------|--------------------|--------------------|--------------------|--------------------------------------------------|

| SEL <sub>0</sub> | SEL <sub>1</sub> | EN <sub>0</sub> | EN <sub>1</sub> | D <sub>OUT0+</sub> | D <sub>OUT0-</sub> | D <sub>OUT1+</sub> | D <sub>OUT1-</sub> | Wode                                             |

| L/O              | L/O              | Н               | Н               | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | 1:2 Splitter                                     |

| L/O              | Н                | Н               | Н               | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | R <sub>IN1+</sub>  | R <sub>IN1</sub>   | Repeater                                         |

| Н                | L/O              | Н               | Н               | R <sub>IN1+</sub>  | R <sub>IN1-</sub>  | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | Switch                                           |

| Н                | Н                | Н               | Н               | R <sub>IN1+</sub>  | R <sub>IN1-</sub>  | R <sub>IN1+</sub>  | R <sub>IN1-</sub>  | 1:2 Splitter                                     |

| Х                | L/O              | L/O             | Н               | Z                  | Z                  | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | D <sub>OUT0</sub> Disabled                       |

| X                | Н                | L/O             | Н               | Z                  | Z                  | R <sub>IN1+</sub>  | R <sub>IN1-</sub>  | D <sub>OUT0</sub> Disabled                       |

| L/O              | Х                | Н               | L/O             | R <sub>IN0+</sub>  | R <sub>IN0-</sub>  | Z                  | Z                  | D <sub>OUT1</sub> Disabled                       |

| Н                | Х                | Н               | L/O             | R <sub>IN1+</sub>  | R <sub>IN1-</sub>  | Z                  | Z                  | D <sub>OUT1</sub> Disabled                       |

| X                | Х                | L/O             | L/O             | Z                  | Z                  | Z                  | Z                  | D <sub>OUT0</sub> and D <sub>OUT1</sub> Disabled |

| OPEN             | L / O = LOV      | V or OPEN       | H = HI          | GH Logic Lev       | vel L=             | LOW Logic          | Level              | X = Don't Care Z = High Impeda                   |

Z = High Impedance

#### **Function Diagrams**

#### **Absolute Maximum Ratings**(Note 1)

(Soldering, 10 seconds) 260°C

## Recommended Operating Conditions

$\begin{array}{lll} \mbox{Supply Voltage (V_{CC})} & 3.0 \mbox{V to } 3.6 \mbox{V} \\ \mbox{Input Voltage (V_{IN})} & 0 \mbox{ to } \mbox{V}_{CC} \\ \mbox{Operating Temperature (T_A)} & -40 \mbox{°C to } +85 \mbox{°C} \\ \end{array}$

Electrostatic Discharge

(HBM 1.5 kΩ, 100 pF) >7500V

Electrostatic Discharge

(MM  $0\Omega$ , 100 pF) >300V

Note 1: The "Absolute Maximum Ratings": are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature and output/input loading variables. Fairchild does not recommend operation of circuits outside databook specification.

#### **DC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified (Note 2)

| Symbol             | Parameter                                                      | Test Conditions                                                  | Min  | Typ<br>(Note 3) | Max  | Units |  |

|--------------------|----------------------------------------------------------------|------------------------------------------------------------------|------|-----------------|------|-------|--|

| LVDS Diffe         | rential Driver Characteristics                                 |                                                                  |      |                 |      |       |  |

| V <sub>OD</sub>    | Output Differential Voltage                                    | $R_L = 75 \Omega$ , See Figure 3                                 | 270  | 365             | 475  |       |  |

|                    |                                                                | $R_L$ = 75 Ω, See Figure 3<br>$T_A$ = 25°C and $V_{CC}$ = 3.3V   | 285  | 365             | 440  | mV    |  |

| $\Delta V_{OD}$    | V <sub>OD</sub> Magnitude Change from Differential LOW-to-HIGH | $R_L = 75 \Omega$ , See Figure 3                                 |      |                 | 35   | mV    |  |

| Vos                | Offset Voltage                                                 | See Figure 3                                                     | 1.0  | 1.2             | 1.45 | V     |  |

| $\Delta V_{OS}$    | Offset Magnitude Change from Differential LOW-to-HIGH          | See Figure 3                                                     |      |                 | 35   | mV    |  |

| I <sub>OZD</sub>   | Disabled Output Leakage Current                                | V <sub>OUT</sub> = 3.6V or GND, Driver Disabled                  |      |                 | ±10  | μΑ    |  |

| I <sub>OFF</sub>   | Power-Off Current                                              | $V_{CC} = 0V$ , $V_{IN}$ or $V_{OUT} = 3.6V$ or $0V$             |      |                 | ±20  | μΑ    |  |

| Ios                | Short Circuit Output Current                                   | V <sub>OUT</sub> = 0V, Driver Enabled                            |      |                 | -10  |       |  |

|                    |                                                                | V <sub>OUTx+</sub> = 0V, V <sub>OUTx-</sub> = 0V, Driver Enabled |      |                 | -10  | mA    |  |

| LVDS Diffe         | rential Receiver Characteristics                               |                                                                  |      |                 |      |       |  |

| V <sub>TH</sub>    | Differential Input Threshold HIGH                              | V <sub>IC</sub> = 0.05V or 1.2V or 3.25V                         |      |                 | 100  | mV    |  |

| $V_{TL}$           | Differential Input Threshold LOW                               | V <sub>CC</sub> = 3.3V                                           | -100 |                 |      | IIIV  |  |

| V <sub>IC</sub>    | Input Common Mode Voltage                                      |                                                                  | 0.05 |                 | 3.25 | V     |  |

| I <sub>IND</sub>   | Input Current (Differential Inputs)                            | V <sub>IN</sub> = GND                                            |      |                 | ±20  |       |  |

|                    | 1                                                              | $V_{IN} = V_{CC}$                                                |      |                 | ±20  | μΑ    |  |

| LVTTL Con          | trol Characteristics                                           |                                                                  |      |                 |      |       |  |

| V <sub>IH</sub>    | Input High Voltage                                             |                                                                  | 2    |                 |      | V     |  |

| V <sub>IL</sub>    | Input Low Voltage                                              |                                                                  |      |                 | 0.8  | V     |  |

| I <sub>IN</sub>    | Input Current                                                  | V <sub>IN</sub> = 3.6V or GND                                    |      |                 | ±20  | μΑ    |  |

| Device Cha         | aracteristics                                                  |                                                                  |      |                 |      |       |  |

| V <sub>IK</sub>    | Input Clamp Voltage                                            | $I_{IK} = -18 \text{ mA}$                                        | -1.5 |                 |      | V     |  |

| I <sub>PU/PD</sub> | Output Power-Up/Power-Down<br>High Z Leakage Current           | V <sub>CC</sub> = 0V to 1.5V                                     |      |                 | ±10  | μА    |  |

| C <sub>IN</sub>    | Input Capacitance                                              |                                                                  |      | 4.5             |      | pF    |  |

| C <sub>OUT</sub>   | Output Capacitance                                             |                                                                  |      | 4.5             |      | pF    |  |

| I <sub>CC</sub>    | Power Supply Current                                           | No Load, All Drivers Enabled                                     |      |                 | 35   | mA    |  |

|                    |                                                                | $R_L = 75 \Omega$ , All Drivers Enabled                          |      |                 | 35   | mA    |  |

|                    |                                                                | $R_L = 75 \Omega$ , All Drivers Enabled                          |      |                 | 35   | mA    |  |

Note 2: This part will only function with datasheet specification when a resistive load is applied to the driver outputs.

Note 3: All typical values are at  $T_A=25^{\circ}C$  and with  $V_{CC}=3.3V.$

#### **AC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified

| Symbol            | Parameter                                                                  | Test Conditions                                 | Min | Typ<br>(Note 4) | Max | Units |

|-------------------|----------------------------------------------------------------------------|-------------------------------------------------|-----|-----------------|-----|-------|

| t <sub>PLHD</sub> | Differential Output Propagation Delay                                      |                                                 | 0.7 |                 | 1.6 | no    |

|                   | LOW-to-HIGH                                                                | $R_L = 75 \Omega, C_L = 5 pF,$                  | 1.0 | 1.2             | 1.3 | ns    |

| t <sub>PHLD</sub> | Differential Output Propagation Delay                                      | V <sub>CC</sub> = 3.3V, T <sub>A</sub> = 25°C   | 0.7 |                 | 1.6 | ns    |

|                   | HIGH-to-LOW                                                                | See Figure 4 and Figure 5                       | 1.0 | 1.2             | 1.3 | 115   |

| t <sub>TLHD</sub> | Differential Output Rise Time (20% to 80%)                                 | 1                                               | 290 |                 | 580 | ps    |

| t <sub>THLD</sub> | Differential Output Fall Time (80% to 20%)                                 |                                                 | 290 |                 | 580 | ps    |

| t <sub>PLH</sub>  | Selection Propagation Delay                                                |                                                 | 0.6 |                 | 1.5 | ns    |

|                   | LOW-to-HIGH (SEL <sub>n</sub> to OUT <sub>n</sub> )                        | $R_L = 75 \Omega, C_L = 5 pF,$                  | 0.9 | 1.1             | 1.2 | ns    |

| t <sub>PHL</sub>  | Selection Propagation Delay                                                | V <sub>CC</sub> = 3.3V, T <sub>A</sub> = 25°C   | 0.6 |                 | 1.5 |       |

|                   | HIGH-to-LOW (SEL <sub>n</sub> to OUT <sub>n</sub> )                        | See Figure 6 and Figure 7                       | 0.9 | 1.1             | 1.2 | ns    |

| t <sub>ZHD</sub>  | Differential Output Enable Time                                            |                                                 |     |                 | 3.5 |       |

|                   | from Z-to-HIGH                                                             |                                                 |     |                 | 3.3 | ns    |

| t <sub>ZLD</sub>  | Differential Output Enable Time                                            | 1                                               |     |                 | 3.5 |       |

|                   | from Z-to-LOW                                                              | $R_L = 75\Omega$ , $C_L = 5 pF$                 |     |                 | 3.3 | ns    |

| t <sub>HZD</sub>  | Differential Output Disable Time                                           | See Figure 8 and Figure 9                       |     |                 | 3.5 | ns    |

|                   | from HIGH-to-Z                                                             |                                                 |     |                 | 3.3 | 115   |

| t <sub>LZD</sub>  | Differential Output Disable Time                                           | 1                                               |     |                 | 3.5 | ns    |

|                   | from LOW-to-Z                                                              |                                                 |     |                 | 3.3 | 115   |

| t <sub>SET</sub>  | Input (IN <sub>n+</sub> /IN <sub>n-</sub> ) Setup Time to SEL <sub>n</sub> | See Figure 10                                   | 0.5 | 0.3             |     | ns    |

| t <sub>HOLD</sub> | Input (IN <sub>n+</sub> /IN <sub>n-</sub> ) Hold Time to SEL <sub>n</sub>  | See Figure 10                                   | 0.5 | 0.3             |     | ns    |

| t <sub>JIT</sub>  | Output Peak-to-Peak Jitter                                                 | 2 <sup>23</sup> –1 PRBS Sequence at 800 Mbps    |     |                 | 190 | ps    |

|                   |                                                                            | 50% Duty Cycle at 800 Mbps                      |     | 20              | 35  | ps    |

| f <sub>TOG</sub>  | Maximum Toggle Frequency                                                   | $R_L = 75 \Omega$ , $C_L = 5 pF$ , See Figure 4 | 800 | 900             |     | Mbps  |

| t <sub>SKEW</sub> | Within Device Channel-to-Channel Skew                                      |                                                 |     | 35              | 80  | ps    |

|                   | Pulse Skew  t <sub>PLHD</sub> -t <sub>PHLD</sub>                           |                                                 |     | 0               | 225 | ps    |

|                   | Part-to-Part Skew (Note 5)                                                 |                                                 |     | 100             | 500 | ps    |

**Note 4:** All typical values are at  $T_A = 25^{\circ}\text{C}$  and with  $V_{CC} = 3.3\text{V}$ .

Note 5: Part-to-part skew is the maximum delay time difference on like edges (LOW-to-HIGH or HIGH-to-LOW) for the same V<sub>CC</sub> and temperature conditions.

#### **Required Specifications**

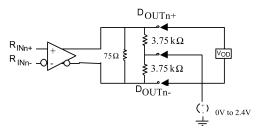

- 1. When the true and complement LVDS outputs (having a 75 $\Omega$  connected between outputs) are connected to 3.75 k $\Omega$  resistors and the common point of those 3.75 k $\Omega$  resistors are connected to a voltage source that sweeps from 0 to 2.4V, the DC V<sub>OD</sub> and  $\Delta$ V<sub>OD</sub> are still maintained (see Figure 1).

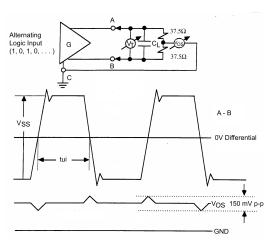

- 2. When the true and complement LVDS outputs (having a 5 pF capacitor attached between outputs) are connected with 37.5 $\Omega$  resistors each to common point, then the common point does not vary by more than 150 mV under all process, temperature and voltage conditions when the outputs switch either from LOW-to-HIGH or from HIGH-to-LOW (see Figure 2).

- Pull-down resistors are required on Enable (EN<sub>0</sub> and EN<sub>1</sub>) and select (SEL<sub>0</sub> and SEL<sub>1</sub>) inputs.

- 4. Fail safe protection on the outputs that draw less than 20  $\mu A$  of current (worst case) on the LVDS inputs. In this condition, if the input is in fail safe selected to  $\text{OUT}_{0+}/\text{OUT}_{0-}$  (say) and the outputs are Enabled then  $\text{OUT}_{0+}=\text{HIGH}$  and  $\text{OUT}_{0-}=\text{LOW}.$  This prevents noise from being amplified when the connection is broken.

- 5. In the disabled state the outputs can go beyond  $V_{CC}$  but there should be no appreciable leakage (see  $I_{OZD}$  and  $I_{OFF}$  specifications)

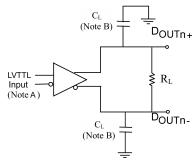

FIGURE 1. Common Mode Supply Test Circuit

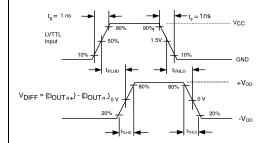

FIGURE 2. Dynamic  $\mathbf{V}_{\text{OS}}$  Test Circuit and Waveforms

#### Required Specifications (Continued)

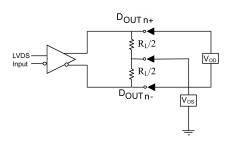

FIGURE 3. LVDS Driver DC Test Circuit

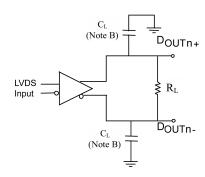

Note A: All input pulses have frequency = 50 MHz,  $t_R$  or  $t_F$  = 500 ps Note B:  $C_L$  includes all probe and jig capacitances

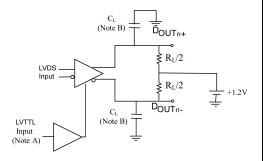

#### FIGURE 4. LVDS Input to LVDS Driver Propagation Delay and Transition Time Circuit

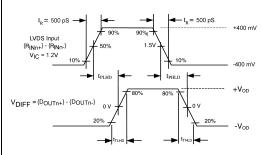

FIGURE 5. LVDS Input to LVDS Output AC Waveforms

FIGURE 6. LVTTL Input to LVDS Driver Propagation Delay and Transition Time Test Circuit

#### Required Specifications (Continued)

Note A: All input pulses have frequency = 10MHz,  $t_R$  or  $t_F$  < = 1 ns. Note B:  $C_L$  includes all probe and jig capacitances.

#### FIGURE 7. LVTTL Input to LVDS Output AC Waveforms

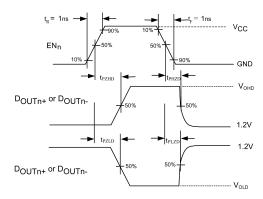

FIGURE 8. Differential Driver Enable and Disable Test Circuits

FIGURE 9. Enable and Disable AC Waveforms

#### Required Specifications (Continued) Valid data output Invalid Data Output -SET--SET-Select Select R<sub>IN+</sub> $R_{\mathsf{IN}}$ + D<sub>OUT+</sub> D<sub>OUT+</sub> — tPLH -- tPLH Valid data output Invalid Data Output HOLD HOLD Select Select $R_{IN+}$ R<sub>IN+</sub> DOUTH $D_{\mbox{OUT+}}$ — tPLH-— t<sub>PLH</sub>— Undefined State

FIGURE 10. Set-up and Hold Time Specification

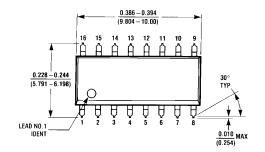

#### Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A

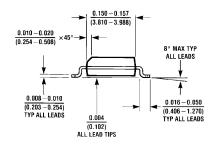

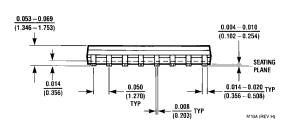

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 7.72 TYP. DIMENSIONS METRIC ONLY (1.78 TYP) 0.42 TYP LAND PATTERN RECOMMENDATION GAGE PLANE 6.4 0.25 4.4 ± 0.1 -B-3.2 SEATING PLANE 0.6 ± 0.1 DETAIL A TYPICAL, SCALE: 40X △ 0.2 C B A ALL LEAD TIPS PIN #1 IDENT SEE DETAIL A (0.90)□ 0.1 C ALL LEAD TIPS -C-0.65 TYP 0.10 ± 0.05 TYP 0.09-0.20 TYP

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC16

A BS

c (S)

0.30 TYP

0.13 M

Ф

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

MTC16 (REV C)

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

FIN1022MTC FIN1022MTCX FIN1022M

#### **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9