# LV8111VB

# BI-CMOS LSI 3-phase Brushless Motor Driver for Polygon Mirror Motor

### Overview

The LV8111VB is a 3-phase brushless motor driver for polygon mirror motor driving of LBP.

A circuit needed to drive of polygon mirror motor can be composed of a single-chip. Also, the output transistor is made DMOS by using BiDC process, and by adopting the synchronous rectification method, the lower power consumption (Heat generation) is achieved.

### Feature

- 3-phase bipolar drive

- Direct PWM drive + synchronous rectification

- $I_{O} max1 = 2.5A$

- IO max2 = 3.0A (t  $\le 0.1$ ms)

- Output current control circuit

- PLL speed control circuit

- Phase lock detection output (with mask function)

- Current limiter, constraint protection, thermal shutdown, under-voltage protection circuit

- Circuit to switch slowing down method while stopped (Free run or Short-circuit brake)

- Constraint protection detection signal switching circuit (FG or LD)

- Forward / Reverse switching circuit

- Compatible with Hall FG

- Hall bias pin (Bias current cut in a stopped state)

- 5V regulator output

- SDCC function (Speed Detection Current Control)

### **Typical Applications**

- Laser beam printer (LBP)

- Plain paper copier (PPC)

- Multi function printer (MFP)

ON Semiconductor®

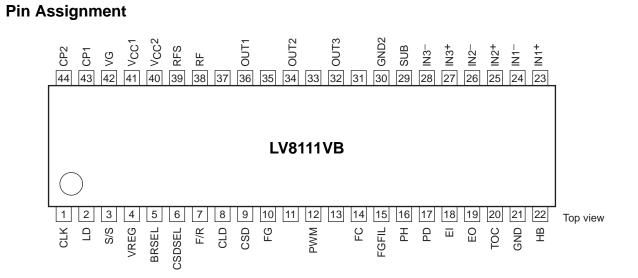

SSOP44K(275mil) Exposed Pad

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 15 of this data sheet.

### Specifications Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                      | Ratings     | Unit |

|-----------------------------|---------------------|---------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max | V <sub>CC</sub> pin             | 37          | V    |

|                             | VG max              | VG pin                          | 42          | V    |

| Output current              | IO max1             | *1                              | 2.5         | А    |

|                             | I <sub>O</sub> max2 | t ≤ 0.1ms *1                    | 3.0         | А    |

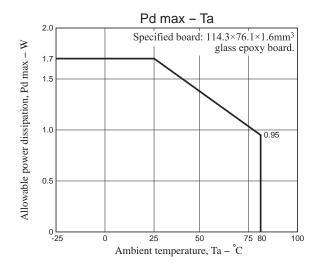

| Allowable Power dissipation | Pd max              | Mounted on a specified board *2 | 1.7         | W    |

| Operation temperature       | Topr                |                                 | -25 to +80  | °C   |

| Storage temperature         | Tstg                |                                 | -55 to +150 | °C   |

| Junction temperature        | Tj max              |                                 | 150         | °C   |

\*1. Tj max =  $150^{\circ}$ C must not be exceeded.

\*2. Specified board: 114.3mm × 76.1mm × 1.6mm, glass epoxy board.

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                          | Symbol           | Conditions | Ratings  | Unit |

|------------------------------------|------------------|------------|----------|------|

| Supply voltage range               | V <sub>CC</sub>  |            | 10 to 35 | V    |

| 5V constant voltage output current | I <sub>REG</sub> |            | 0 to -30 | mA   |

| LD pin applied voltage             | V <sub>LD</sub>  |            | 0 to 5.5 | V    |

| LD pin output current              | I <sub>LD</sub>  |            | 0 to 15  | mA   |

| FG pin applied voltage             | V <sub>FG</sub>  |            | 0 to 5.5 | V    |

| FG pin output current              | I <sub>FG</sub>  |            | 0 to 15  | mA   |

| HB pin output current              | I <sub>HB</sub>  |            | 0 to -30 | mA   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### Electrical Characteristics at $Ta = 25^{\circ}C$ , $V_{CC} = 24V$

| Deveryor                          | O: make al            | Conditions                                                    |      | Ratings              |      |       |

|-----------------------------------|-----------------------|---------------------------------------------------------------|------|----------------------|------|-------|

| Parameter                         | Symbol                | Conditions                                                    | min  | typ                  | max  | Unit  |

| Current drain                     | ICC1                  |                                                               |      | 5.5                  | 6.5  | mA    |

|                                   | I <sub>CC</sub> 2     | In a stop state                                               |      | 1.0                  | 1.5  | mA    |

| 5V Constant Voltage Output        |                       |                                                               |      |                      |      |       |

| Output voltage                    | VREG                  |                                                               | 4.65 | 5.0                  | 5.35 | V     |

| Line regulation                   | ∆VREG1                | V <sub>CC</sub> = 10 to 35V                                   |      | 20                   | 100  | mV    |

| Load regulation                   | ∆VREG2                | I <sub>O</sub> = -5 to -20mA                                  |      | 25                   | 60   | mV    |

| Temperature coefficient           | ∆VREG3                | Design target value *                                         |      | 0                    |      | mV/°C |

| Output Block                      |                       |                                                               |      |                      |      |       |

| Output ON resistance              | R <sub>ON</sub>       | I <sub>O</sub> = 1A , Sum of the lower and upper side outputs |      | 1.5                  | 1.9  | Ω     |

| Output leakage current            | lOleak                | Design target value *                                         |      |                      | 10   | μΑ    |

| Lower side Diode forward voltage  | V <sub>D</sub> 1      | I <sub>D</sub> = -1A                                          |      | 1.0                  | 1.35 | V     |

| Upper side Diode forward voltage  | V <sub>D</sub> 2      | I <sub>D</sub> = 1A                                           |      | 1.0                  | 1.35 | V     |

| Charge Pump Output (VG pin)       |                       | ·                                                             |      |                      |      |       |

| Output voltage                    | VG <sub>OUT</sub>     |                                                               |      | V <sub>CC</sub> +4.9 |      | V     |

| CP1 pin                           | •                     | •                                                             | •    |                      |      | •     |

| Output ON resistance (High level) | V <sub>OH</sub> (CP1) | I <sub>CP1</sub> = -2mA, Design target value *                |      | 500                  | 700  | Ω     |

| Output ON resistance (Low level)  | V <sub>OL</sub> (CP1) | I <sub>CP1</sub> = 2mA                                        |      | 300                  | 400  | Ω     |

\* Design target value, Do not measurement.

| Continued from preceding page.       | 1                                     |                                          |         |         |          |       |

|--------------------------------------|---------------------------------------|------------------------------------------|---------|---------|----------|-------|

| Parameter                            | Symbol                                | Conditions                               |         | Ratings | 1        | Unit  |

|                                      | Gymbol                                | Conditions                               | min     | typ     | max      | Offic |

| Hall Amplifier Block                 |                                       |                                          |         |         | [        |       |

| Input bias current                   | I <sub>HB</sub> (HA)                  |                                          | -2      | -0.5    |          | μA    |

| Common mode input voltage range      | VICM                                  |                                          | 0.5     |         | VREG-2.0 | V     |

| Hall input sensitivity               |                                       |                                          | 80      |         |          | mVp-  |

| Hysteresis                           | ∆V <sub>IN</sub> (HA)                 |                                          | 15      | 24      | 42       | mV    |

| Input voltage $L \rightarrow H$      | V <sub>SLH</sub>                      |                                          |         | 12      |          | mV    |

| Input voltage $H \rightarrow L$      | V <sub>SHL</sub>                      |                                          |         | -12     |          | mV    |

| Hall Bias (HB pin) P-channel Output  | 1                                     |                                          | 1       |         | 1        |       |

| Output voltage ON resistance         | V <sub>OL</sub> (HB)                  | $I_{HB} = -20 \text{mA}$                 |         | 20      | 30       | Ω     |

| Output leakage current               | IL(HB)                                | $V_{O} = 0V$                             |         |         | 10       | μA    |

| FG Amplifier Schmitt Block (IN1)     |                                       |                                          |         |         |          |       |

| Input amplifier gain                 | G <sub>FG</sub>                       | Design target value *                    |         | 5       |          | time  |

| Input hysteresis (H $\rightarrow$ L) | V <sub>SHL</sub> (FGS)                | Input referred, Design target value *    |         | 0       |          | mV    |

| Input hysteresis (L $\rightarrow$ H) | V <sub>SLH</sub> (FGS)                | Input referred, Design target value *    |         | 10      |          | mV    |

| Hysteresis                           | V <sub>FGL</sub>                      | Input referred, Design target value *    |         | 10      |          | mV    |

| FGFIL pin                            | 1                                     |                                          |         |         |          |       |

| High level output voltage            | $V_{OH}(FGFIL)$                       |                                          | 2.7     | 3.0     | 3.3      | V     |

| Low level output voltage             | V <sub>OL</sub> (FGFIL)               |                                          | 0.75    | 0.85    | 0.95     | V     |

| External capacitor charge current    | ICHG1                                 | V <sub>CHG</sub> 1 = 1.5V                | -5      | -4      | -3       | μA    |

| External capacitor discharge current | ICHG <sup>2</sup>                     | V <sub>CHG</sub> 2 = 1.5V                | 3       | 4       | 5        | μA    |

| Amplitude                            | V(FGFIL)                              |                                          | 1.95    | 2.15    | 2.35     | Vp-p  |

| FG Output                            |                                       |                                          |         |         | 1        | -     |

| Output ON resistance                 | V <sub>OL</sub> (FG)                  | I <sub>FG</sub> = 7mA                    |         | 20      | 30       | Ω     |

| Output leakage current               | I <sub>L</sub> (FG)                   | V <sub>O</sub> = 5.5V                    |         |         | 10       | μA    |

| PWM Oscillator                       |                                       |                                          |         |         | 1        | -     |

| High level output voltage            | V <sub>OH</sub> (PWM)                 |                                          | 2.95    | 3.2     | 3.45     | V     |

| Low level output voltage             | V <sub>OL</sub> (PWM)                 |                                          | 1.3     | 1.5     | 1.7      | V     |

| External capacitor charge current    | ICHG(PWM)                             | V <sub>PWM</sub> = 2V                    | -90     | -70     | -50      | μA    |

| Oscillation frequency                | f(PWM)                                | C = 150pF                                | 180     | 225     | 270      | kHz   |

| Amplitude                            | V(PWM)                                |                                          | 1.5     | 1.7     | 1.9      | Vp-p  |

| Recommended operation frequency      | <sup>f</sup> OPR                      |                                          | 15      |         | 300      | kHz   |

| range                                |                                       |                                          |         |         |          |       |

| CSD Oscillation Circuit              |                                       |                                          |         |         |          |       |

| High level output voltage            | V <sub>OH</sub> (CSD)                 |                                          | 2.7     | 3.0     | 3.3      | V     |

| Low level output voltage             | V <sub>OL</sub> (CSD)                 |                                          | 0.8     | 1.0     | 1.2      | V     |

| Amplitude                            | V(CSD)                                |                                          | 1.75    | 2.0     | 2.25     | Vp-p  |

| External capacitor charge current    | I <sub>CHG</sub> 1(CSD)               |                                          | -14     | -10     | -6       | μA    |

| External capacitor discharge current | I <sub>CHG</sub> 2(CSD)               |                                          | 8       | 11      | 14       | μA    |

| Oscillation frequency                | f(CSD)                                | $C = 0.068 \mu$ F, Design target value * | 30      | 40      | 50       | Hz    |

| Phase comparing output               |                                       |                                          |         |         |          |       |

| Output ON resistance (high level)    | VPDH                                  | I <sub>OH</sub> = -100μA                 |         | 500     | 700      | Ω     |

| Output ON resistance (low level)     | V <sub>PDL</sub>                      | I <sub>OL</sub> = 100μA                  |         | 500     | 700      | Ω     |

| Phase Lock Detection Output          |                                       |                                          |         |         | r        | 1     |

| Output ON resistance                 | V <sub>OL</sub> (LD)                  | I <sub>LD</sub> = 10mA                   |         | 20      | 30       | Ω     |

| Output leakage current               | I <sub>L</sub> (LD)                   | V <sub>O</sub> = 5.5V                    |         |         | 10       | μA    |

| Error Amplifier Block                | · · · · · · · · · · · · · · · · · · · |                                          |         |         |          |       |

| Input offset voltage                 | V <sub>IO</sub> (ER)                  | Design target value *                    | -10     |         | +10      | mV    |

| Input bias current                   | I <sub>B</sub> (ER)                   |                                          | -1      |         | +1       | μA    |

| High level output voltage            | V <sub>OH</sub> (ER)                  | I <sub>EI</sub> = -100μA                 | El+0.7  | EI+0.85 | El+1.0   | V     |

| Low level output voltage             | V <sub>OL</sub> (ER)                  | I <sub>EI</sub> = 100μA                  | EI-1.75 | El-1.6  | EI-1.45  | V     |

| DC bias level                        | V <sub>B</sub> (ER)                   |                                          | -5%     | VREG/2  | 5%       | V     |

\* Design target value, Do not measurement.

| Parameter                              | Symbol                  | Conditions                                 |           | Ratings |       | Unit  |

|----------------------------------------|-------------------------|--------------------------------------------|-----------|---------|-------|-------|

|                                        | Cymbol                  | r                                          |           | typ     | max   | 0 m   |

| Current Control Circuit                |                         |                                            | 1 1       |         |       |       |

| Drive gain                             | GDF                     | While phase locked                         | 0.5       | 0.55    | 0.6   | times |

| Current Limiter Circuit (pins RF and   | l RFS)                  |                                            | 1 1       |         |       |       |

| Limiter voltage                        | V <sub>RF</sub>         |                                            | 0.465     | 0.515   | 0.565 | V     |

| Under-voltage Protection               |                         |                                            | · · · · · |         |       |       |

| Operation voltage                      | VSD                     |                                            | 8.3       | 8.7     | 9.1   | V     |

| Hysteresis                             | ΔVSD                    |                                            | 0.2       | 0.35    | 0.5   | V     |

| CLD Circuit                            |                         |                                            | · · · · · |         |       |       |

| External capacitor charge current      | ICLD                    | V <sub>CLD</sub> = 0V                      | -4.5      | -3.0    | -1.5  | μΑ    |

| Operation voltage                      | V <sub>H</sub> (CLD)    |                                            | 3.25      | 3.5     | 3.75  | V     |

| Thermal Shutdown Operation             |                         |                                            |           |         |       |       |

| Thermal shutdown operation temperature | TSD                     | Design target value (Junction temperature) | 150       | 175     |       | °C    |

| Hysteresis                             | ∆TSD                    | Design target value (Junction temperature) |           | 30      |       | °C    |

| CLK pin                                |                         |                                            |           |         |       |       |

| External input frequency               | f <sub>I</sub> (CLK)    |                                            | 0.1       |         | 10    | kHz   |

| High level input voltage               | V <sub>IH</sub> (CLK)   |                                            | 2.0       |         | VREG  | V     |

| Low level input voltage                | V <sub>IL</sub> (CLK)   |                                            | 0         |         | 1.0   | V     |

| Input open voltage                     | V <sub>IO</sub> (CLK)   |                                            | VREG-0.5  |         | VREG  | V     |

| Hysteresis                             | V <sub>IS</sub> (CLK)   |                                            | 0.2       | 0.3     | 0.4   | V     |

| High level input current               | I <sub>IH</sub> (CLK)   | V <sub>CLK</sub> = VREG                    | -10       | 0       | +10   | μA    |

| Low level input current                | IIL(CLK)                | V <sub>CLK</sub> = 0V                      | -110      | -85     | -60   | μA    |

| CSDSEL pin                             |                         |                                            | 1         |         |       |       |

| High level input voltage               | V <sub>IH</sub> (CSD)   |                                            | 2.0       |         | VREG  | V     |

| Low level input voltage                | V <sub>IL</sub> (CSD)   |                                            | 0         |         | 1.0   | V     |

| Input open voltage                     | V <sub>IO</sub> (CSD)   |                                            | VREG-0.5  |         | VREG  | V     |

| High level input current               | I <sub>IH</sub> (CSD)   | V <sub>CSDSEL</sub> = VREG                 | -10       | 0       | +10   | μA    |

| Low level input current                | I <sub>IL</sub> (CSD)   | VCSDSEL = 0V                               | -110      | -85     | -60   | μA    |

| S/S pin                                |                         | 000011                                     | 11        |         |       |       |

| High level input voltage               | V <sub>IH</sub> (SS)    |                                            | 2.0       |         | VREG  | V     |

| Low level input voltage                | V <sub>IL</sub> (SS)    |                                            | 0         |         | 1.0   | V     |

| Input open voltage                     | V <sub>IO</sub> (SS)    |                                            | VREG-0.5  |         | VREG  | V     |

| Hysteresis                             | V <sub>IS</sub> (SS)    |                                            | 0.2       | 0.3     | 0.4   | V     |

| High level input current               | I <sub>IH</sub> (SS)    | V <sub>S/S</sub> = VREG                    | -10       | 0       | +10   | μA    |

| Low level input current                | ljL(SS)                 | V <sub>S/S</sub> =0V                       | -110      | -85     | -60   | μA    |

| BRSEL pin                              |                         | 5,5                                        | 1         |         |       |       |

| High level input voltage               | VIH(BRSEL)              |                                            | 2.0       |         | VREG  | V     |

| Low level input voltage                | V <sub>IL</sub> (BRSEL) |                                            | 0         |         | 1.0   | V     |

| Input open voltage                     | V <sub>IO</sub> (BRSEL) |                                            | VREG-0.5  |         | VREG  | V     |

| High level input current               | I <sub>IH</sub> (BRSEL) | V <sub>BRSEL</sub> = VREG                  | -10       | 0       | +10   | μA    |

| Low level input current                | III (BRSEL)             | VBRSEL = 0V                                | -110      | -85     | -60   | μΑ    |

| F/R pin                                | ·L                      | DIVEL                                      |           |         |       | ·     |

| High level input voltage               | V <sub>IH</sub> (FR)    |                                            | 2.0       |         | VREG  | V     |

| Low level input voltage                | V <sub>IL</sub> (FR)    |                                            | 0         |         | 1.0   | V     |

| Input open voltage                     | V <sub>IO</sub> (FR)    |                                            | VREG-0.5  |         | VREG  | v     |

| High level input current               | I <sub>IH</sub> (FR)    | V <sub>F/R</sub> = VREG                    | -10       | 0       | +10   | μA    |

|                                        | ייי)חוי                 | $V_{F/R} = 0V$                             | -10       | U       | .10   | μΑ    |

\* Design target value, Do not measurement.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

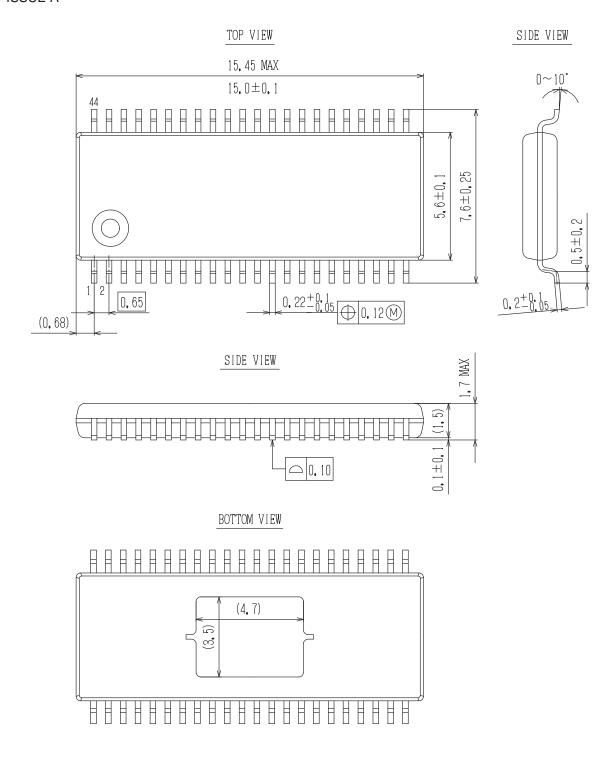

### **Package Dimensions**

unit : mm

SSOP44K (275mil) Exposed Pad CASE 940AF ISSUE A

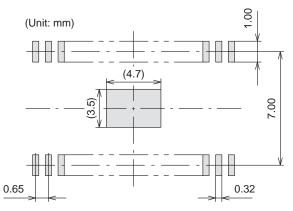

### **SOLDERING FOOTPRINT\***

#### NOTES:

- 1. The measurements are for reference only, and unable to guarantee.

- 2. Please take appropriate action to design the actual Exposed Die Pad and Fin portion.

- 3. After setting, verification on the product must be done.

(Although there are no recommended design for Exposed Die Pad and Fin portion Metal mask and shape for Through-Hole pitch (Pitch & Via etc), checking the soldered joint condition and reliability verification of soldered joint will be needed. Void • gradient • insufficient thickness of soldered joint or bond degradation could lead IC destruction because thermal conduction to substrate becomes poor.)

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### www.onsemi.com 7

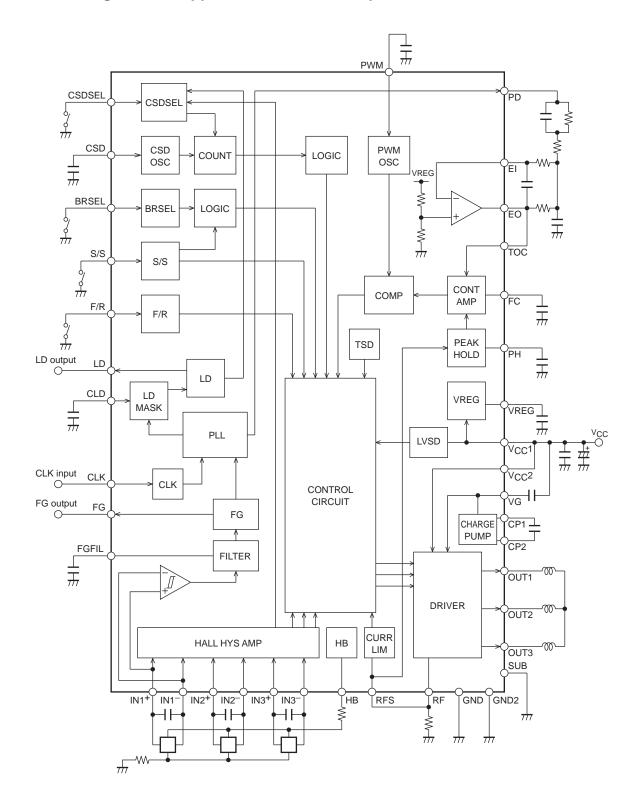

# **Block Diagram and Application Circuit Example**

| Pin F   | unctio   | n                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin name | Function                                                                                                                                     | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1       | CLK      | Clock input pin (10kHz maximum)                                                                                                              | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2       | LD       | Phase lock detection output pin.<br>Goes ON during PLL-phase lock.<br>Open drain output.                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3       | S/S      | Start/Stop input pin.<br>Start with low-level input.<br>Stop with high-level input or open input                                             | VREG<br>3<br>5kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ<br>10kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4       | VREG     | 5V regulator output pin.<br>(the control circuit power supply)<br>Connect a capacitor between this pin and GND for<br>stabilization.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | BRSEL    | Brake selection pin.<br>By low-level, short-circuit braking when the S/S pin is in a<br>stopped state.<br>(Brake for the inspection process) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6       | CSDSEL   | Motor constraint protection detection signal selection pin.<br>Select FG with low,<br>and LD with high or in an open state.                  | VREG<br>55kΩ \$<br>55kΩ \$<br>55kΩ \$<br>55kΩ \$<br>50 \$<br>10 \$<br>10\$ |

|         | ed from prece | eding page.                                                                                                                                                                                                                                                                                                           |                                                                                                   |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Pin No. | Pin name      | Function                                                                                                                                                                                                                                                                                                              | Equivalent circuit                                                                                |

| 7       | F/R           | Forward / Reverse selection pin.                                                                                                                                                                                                                                                                                      |                                                                                                   |

| 8       | CLD           | Phase lock signal mask time setting pin.<br>Connect a capacitor between this pin and GND.<br>When it is not necessary to mask, this pin must be left open.                                                                                                                                                            | VREG<br>500Ω<br>500Ω<br>8<br>2kΩ<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| 9       | CSD           | Pin for both the constraint protection circuit operation time<br>setting and the initial reset pulse setting.<br>Connect a capacitor between this pin and GND.<br>If the motor constraint protection circuit is not used,<br>a capacitor and a resistor must be connected in parallel<br>between the CSD pin and GND. |                                                                                                   |

| 10      | FG            | FG Schmitt output pin.<br>Open drain output.                                                                                                                                                                                                                                                                          |                                                                                                   |

| 12      | PWM           | Pin to set the oscillation frequency of PWM.<br>Connect a capacitor between this pin and GND.                                                                                                                                                                                                                         | VREG<br>2000<br>2000<br>12<br>2k0<br>7/7<br>7/7<br>7/7                                            |

| 14      | FC            | Frequency characteristics correction pin of the current<br>control circuit.<br>Connect a capacitor between this pin and GND.                                                                                                                                                                                          | VREG                                                                                              |

# LV8111VB

| Continue | ad from prace | ding page                                                                                                                                                                  |                                            |

|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|          | ed from prece |                                                                                                                                                                            | Equivalent sizevit                         |

| Pin No.  | Pin name      | Function                                                                                                                                                                   | Equivalent circuit                         |

| 15       | FGFIL         | FG filter pin.<br>When the noise of the FG signal is a problem, connect a<br>capacitor between this pin and GND.                                                           | VREG                                       |

| 16       | РН            | Pin to stabilize the RF waveform.<br>Connect a capacitor between this pin and GND.                                                                                         | VREG                                       |

| 17       | PD            | Phase comparison output pin.<br>The phase error is output by using the duty changes of the<br>pulse.                                                                       |                                            |

| 18       | EI            | Error amplifier input pin.                                                                                                                                                 | VREG                                       |

| 19       | EO            | Error amplifier output pin.                                                                                                                                                | VREG<br>(19)<br>100kΩ<br>777<br>777<br>777 |

| 20       | TOC           | Torque command voltage input pin.<br>Normally, this pin must be connected with the EO pin.<br>On-duty of upper-side output Tr increases when the TOC<br>voltage decreases. |                                            |

| 21       | GND           | Ground pin of the control circuit block.                                                                                                                                   |                                            |

| 32       | OUT3              | Output pin.                                                                                                                      | Vcc |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 34<br>36 | OUT2<br>OUT1      | As for PWM, a duty control is executed on the upper side FET.                                                                    |     |

| 38       | RF                | Source pin of output MOSFET (lower).<br>Connect low resister (Rf) between this pin and GND.                                      | 38  |

| 39       | RFS               | Output current detection pin.<br>Connect this pin to the RF pin.                                                                 |     |

| 40       | V <sub>CC</sub> 2 | Power supply pin for output.<br>Connect a capacitor between this pin and GND for<br>stabilization.                               |     |

| 41       | V <sub>CC</sub> 1 | Power supply pin for control.                                                                                                    |     |

| 42       | VG                | Charge pump output pin (power supply for the upper side FET gate).<br>Connect a capacitor between this pin and V <sub>CC</sub> . |     |

| 43       | CP1               | Pin to connect a capacitor for charge pump.                                                                                      |     |

| 44       | CP2               | Connect a capacitor between CP1 and CP2.                                                                                         |     |

Function

A high-level state of logic is recognized when  $IN^+ > IN^-$ .

The input amplitude of 100mVp-p or more (differential) is

When the noise of the Hall signal is a problem, connect the

Frame ground pin. Connect this pin with the GND2 pin.

Hall element bias current pin.

Hall amplifier input pin.

Reverse case is a low-level state.

capacitors between IN<sup>+</sup> and IN<sup>-</sup>.

Ground pin of the output circuit block.

desirable in the Hall inputs.

Goes ON when the S/S pin is in a start state. Goes OFF when the S/S pin is in a stopped state. Equivalent circuit

ŀĒ

77

$\pi$

500Ω

W

古

$\frac{1}{1}$

(23)(25)(27)

VREG

VREG

本

\*

$\frac{1}{1}$

(24)(26)(28)

500Ω —₩-

$\frac{1}{1}$

ŀ₽

l⊧\_ \_\_\_\_\_

Continued from preceding page.

Pin name

ΗB

IN1<sup>+</sup>

IN1<sup>-</sup>

IN2+

IN2<sup>-</sup>

IN3+

IN3-

SUB

GND2

Pin No.

22

23

24

25

26

27

28

29

30

## LV8111VB

| <b>3-phase Logic Truth Table</b> | $(IN = "H" indicates the state where in IN^+ > IN^-)$ |

|----------------------------------|-------------------------------------------------------|

|----------------------------------|-------------------------------------------------------|

| -   |         |     |     |         |     |      |        |      |

|-----|---------|-----|-----|---------|-----|------|--------|------|

|     | F/R = H |     |     | F/R = L |     |      | Output |      |

| IN1 | IN2     | IN3 | IN1 | IN2     | IN3 | OUT1 | OUT2   | OUT3 |

| Н   | L       | Н   | L   | Н       | L   | L    | н      | М    |

| н   | L       | L   | L   | Н       | Н   | L    | М      | Н    |

| н   | Н       | L   | L   | L       | Н   | М    | L      | Н    |

| L   | н       | L   | Н   | L       | Н   | Н    | L      | М    |

| L   | Н       | Н   | Н   | L       | L   | Н    | М      | L    |

| L   | L       | Н   | Н   | Н       | L   | М    | Н      | L    |

### S/S Pin

| Input state  | Mode  |

|--------------|-------|

| High or Open | Stop  |

| Low          | Start |

# BRSEL Pin

| Input state  | While stopped       |  |

|--------------|---------------------|--|

| High or Open | Free run            |  |

| Low          | Short-circuit brake |  |

### **CSDSEL** Pin

| Input state  | Mode        |

|--------------|-------------|

| High or Open | LD standard |

| Low          | FG standard |

### LV8111VB Description

1. Speed Control Circuit

This IC can realize a high efficiency, low-jitter, a stable rotation by adopting the PLL speed control method. This PLL circuit compares the phase difference of the edge between the CLK signal and the FG signal and controls by using the output of error. The FG servo frequency under control becomes congruent with the CLK frequency.

$f_{FG}$  (Servo) =  $f_{CLK}$

2. Output Drive Circuit

This IC adopts the direct PWM drive method to reduce power loss in the output. The driving force of the motor is adjusted by changing the on-duty of the output transistor. The PWM switching of the output is performed by the upper-side output transistor.

Also, this IC has a parasitic diode of the output DMOS as a regeneration route when the PWM switching is off. But, this IC is cut down the fever than the diode regeneration by performing synchronous rectification.

3. Current Limiter Circuit

This IC limits the (peak) current at the value

$I = V_{RF} / Rf (V_{RF} = 0.515V (typical), Rf : current detection resister).$

The current limitation operation consists of reducing the PWM output on duty to suppress the current. To prevent malfunction of the current limitation operation when the reverse recovery current of diode is detected, the operation has a delay (approximately 300ns). Since the current change at the motor start-up is fast when the motor coil is lower resistance or smaller inductance, the current more than the setting value may flow during this delay time. In this case, it is necessary to set the limiter value considering the current that increased by the delay.

4. Power Saving Circuit

This IC becomes the power saving state of decreasing the consumption current in the stop state. The bias current of the majority circuits is cut in the power saving state. Also, 5V regulator output is output in the power saving state.

5. Reference Clock

Note that externally-applied clock signal has no noise of chattering. The input circuit has a hysteresis. But, if noise is a problem, that noise must be excluded by inserting capacitor.

When the IC is switched to the start state if the reference clock is no input, the drive is turned off after a few rotations if the motor constraint protection circuit is used. (Clock disconnection protection)

### 6. PWM Frequency

The PWM frequency is determined by using a capacitor C (F) connected to the PWM pin.

$f_{PWM} \approx 1 / (29500 \times C) \cdots 150 pF$  or more  $f_{PWM} \approx 1 / (32000 \times C) \cdots 100 pF$  or more, less than 150 pF

The frequency is oscillated at about 225kHz when a capacitor of 150pF is connected. The GND of a capacitor must be placed as close to the control block GND (GND pin) of the IC as possible to reduce influence of the output.

### 7. Hall Effect Sensor Input Signals

The signal input of the amplitude of hysteresis of 42mV max or more is required in the Hall effect sensor inputs. Also, an input amplitude of over 100mVp-p is desirable in the Hall effect sensor inputs in view of influence of noise. If the output waveform (when the phase changes ) is distorted by noise, that noise must be excluded by inputting capacitors across the inputs.

8. FG Signal

The Hall signal of IN1 is used as the FG signal in the IC. If noise is a problem, the noise of the FG signal can be excluded by inserting a capacitor between the FGFIL pin and GND. But note that normal operation becomes impossible if the value of the capacitor is overlarge. Also, note that the trouble of noise occurs easily when the position of GND of the capacitor is incorrect.

9. Constraint Protection Circuit

This IC has an on-chip constraint protection circuit to protect the IC and the motor in motor constraint mode. When the CSDSEL pin is set to the high level or open input, if the LD output remains high (unlocked statement) for a fixed period in the start state, this circuit operates. In the low level setting case, if the FG signal is not switched for a fixed period in the start state, this circuit operates. Also, the upper-side output transistor is turned off while the constraint protection circuit is operating. This time is set by the capacitance of the capacitor connected to the CSD pin.

The set time (in seconds) is  $102 \times C (\mu F)$

When a capacitor of  $0.068 \mu F$  is connected, the protection time becomes about 7.0 seconds.

The set time must be set well in advance for the motor start-up time. When the motor is decelerated by switching the clock frequency, this protection circuit is not operated. To release the constraint protection state, put the S/S pin into the start again after the stop state, or turn on the power supply again after the turn off state. The CSD pin has a function as the power-on reset pin also. If the CSD pin is connected to GND, the logic circuit goes to the reset state and the speed cannot be controlled.

Therefore, if the constraint protection circuit is not used, a resistor of about  $220k\Omega$  and a capacitor of about 4700pF must be connected in parallel between the CSD pin and GND.

- 10. Phase Lock Signal

- (1) Phase lock range

This IC has no the speed system counter. The speed error range in the phase lock state is indeterminable only by the characteristics of the IC. ( because the accelerations of the change in FG frequency influences.)

When it is necessary to specify for the speed error as a motor, the value obtained while the motor is actually operating must be measured. Since the speed error is likely to occur when the acceleration of FG is larger, the speed error will be the largest when the IC goes into the lock state at motor start-up, or the unlock state by switching the clock.

(2) Phase lock signal mask function

This function can mask the short lock signal that occurred by the hunting when it goes into the lock state. Therefore, the IC will be able to output the stable lock signal. But the mask time causes the delay of the lock signal output. The mask time is set by the capacitance of the capacitor connected between the CLD pin and GND.

The mask time (seconds) is  $1.8\times C~(\mu F)$

When a  $0.1\mu$ F capacitor is connected, the mask time becomes about 180ms.

Set the enough mask time if it must be masked completely.

When there is no need for masking, the CLD pin must be left open.

### 11. Power Supply Stabilization

Since this IC adopts the method of the switching drive for the application that flows large output current, the power supply line is relatively fluctuated. Therefore, the sufficient capacitors to stabilize the power supply voltage must be connected between the  $V_{CC}$  pin and GND as close to the pin as possible. The ground-side of the capacitors must be connected to the GND2 pin that is GND of the output circuit block. If it is impossible to connect a capacitor (electrolytic capacitor) near the pin, the ceramic capacitor of about  $0.1\mu$ F must be connected as close to the pin as possible.

Since the power supply line is more fluctuated when the diodes are inserted in the power supply line to prevent IC destruction due to the reverse connection of the power supply, choose even larger capacitors.

### 12. VREG Stabilization

To stabilize the VREG voltage that is the power supply of the control circuit, connect a capacitor of  $0.1\mu$ F or more. The ground-side of the capacitor must be connected as close to the control block GND (GND pin) of the IC as possible.

### 13. Error Amplifier

External components of the error amplifier block must be placed as close to the IC as possible to reduce influence of noise.

Also, these components must be placed as far as possible from the motor.

### 14. Metal of IC's Backside

The heat radiation can be efficiently diffused by soldering the metal of IC's backside to the printed circuit board.

### 15. SDCC (Speed Detection Current Control)

The SDCC function controls the current limiter value by sensing the motor speed.

When the rotation speed exceeds 95% of the target speed, this function decreases the current limiter value to 75% and reduces the acceleration of the motor. Therefore, it stabilizes the phase lock pull-in and improves the variance of the motor start-up time.

### **ORDERING INFORMATION**

| Device      | Package                                         | Shipping (Qty / Packing) |

|-------------|-------------------------------------------------|--------------------------|

| LV8111VB-AH | SSOP44K (275mil) EP<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright l

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9