# Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL

Data Sheet ADAU1361

## **FEATURES**

24-bit stereo audio ADC and DAC: >98 dB SNR

Sampling rates from 8 kHz to 96 kHz

Low power: 7 mW record, 7 mW playback, 48 kHz at 1.8 V

6 analog input pins, configurable for single-ended or

differential inputs

Flexible analog input/output mixers Stereo digital microphone input

Analog outputs: 2 differential stereo, 2 single-ended stereo,

1 mono headphone output driver

PLL supporting input clocks from 8 MHz to 27 MHz

Analog automatic level control (ALC) Microphone bias reference voltage Analog and digital I/O: 1.8 V to 3.65 V

I<sup>2</sup>C and SPI control interfaces

Digital audio serial data I/O: stereo and time-division multiplexing (TDM) modes

Software-controllable clickless mute

Software power-down

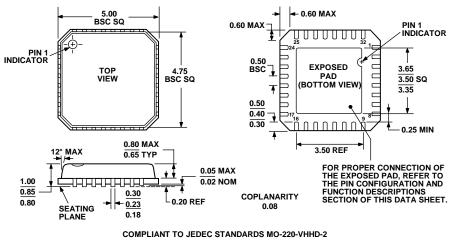

32-lead, 5 mm × 5 mm LFCSP

-40°C to +85°C operating temperature range

## **APPLICATIONS**

Smartphones/multimedia phones

Digital still cameras/digital video cameras

Portable media players/portable audio players

Phone accessories products

#### **GENERAL DESCRIPTION**

The ADAU1361 is a low power, stereo audio codec that supports stereo 48 kHz record and playback at 14 mW from a 1.8 V analog supply. The stereo audio ADCs and DACs support sample rates from 8 kHz to 96 kHz as well as a digital volume control. The ADAU1361 is ideal for battery-powered audio and telephony applications.

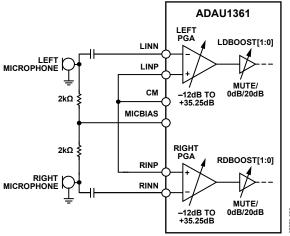

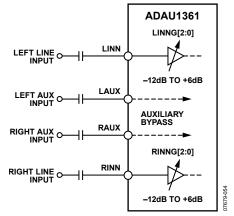

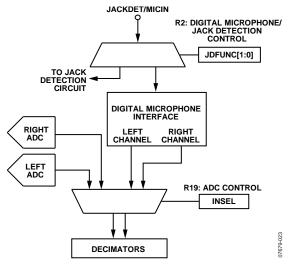

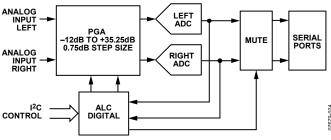

The record path includes an integrated microphone bias circuit and six inputs. The inputs can be mixed and muxed before the ADC, or they can be configured to bypass the ADC. The ADAU1361 includes a stereo digital microphone input.

The ADAU1361 includes five high power output drivers (two differential and three single-ended), supporting stereo headphones, an earpiece, or other output transducer. AC-coupled or capless configurations are supported. Individual fine level controls are supported on all analog outputs. The output mixer stage allows for flexible routing of audio.

The serial control bus supports the I<sup>2</sup>C and SPI protocols. The serial audio bus is programmable for I<sup>2</sup>S, left-/right-justified, and TDM modes. A programmable PLL supports flexible clock generation for all standard integer rates and fractional master clocks from 8 MHz to 27 MHz.

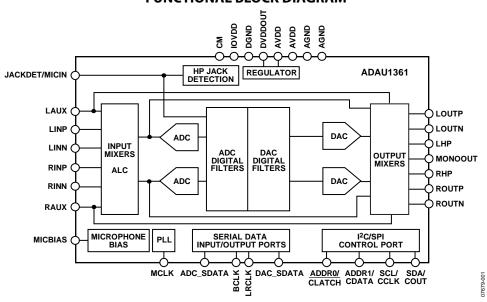

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. D

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    |

|---------------------------------------------|

| Applications1                               |

| General Description                         |

| Functional Block Diagram                    |

| Revision History                            |

| Specifications4                             |

| Analog Performance Specifications4          |

| Power Supply Specifications7                |

| Typical Current Consumption8                |

| Typical Power Management Measurements9      |

| Digital Filters10                           |

| Digital Input/Output Specifications10       |

| Digital Timing Specifications11             |

| Digital Timing Diagrams12                   |

| Absolute Maximum Ratings14                  |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

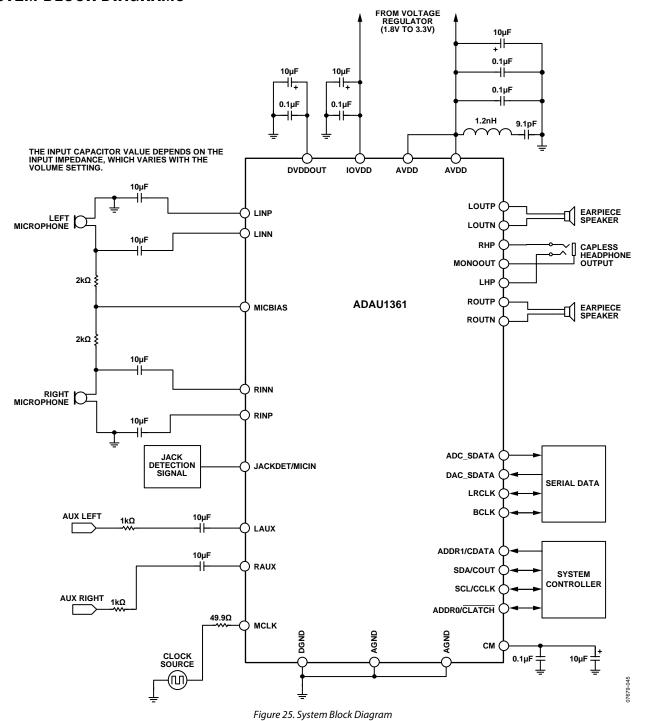

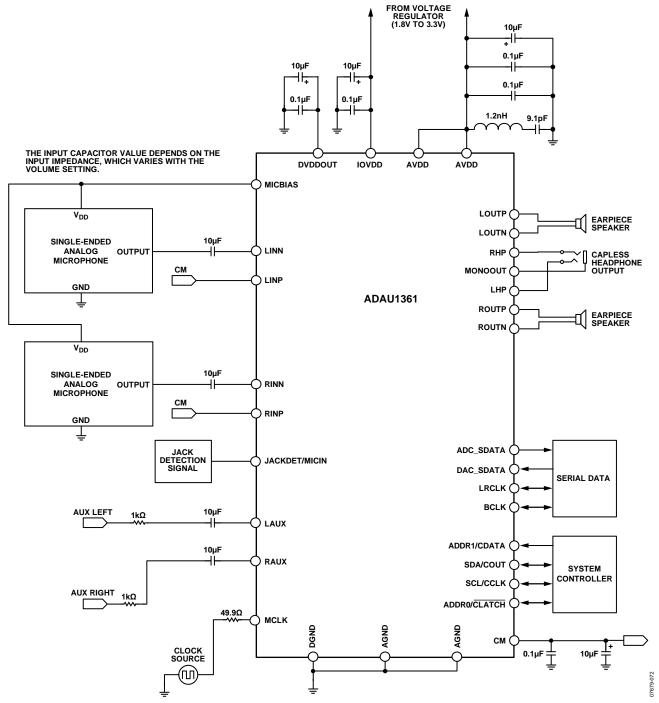

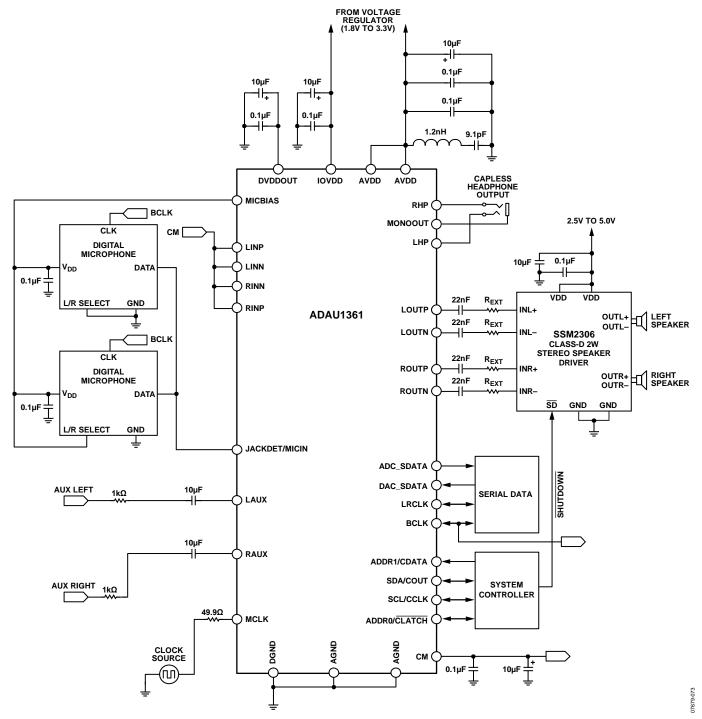

| System Block Diagrams                       |

| Theory of Operation                         |

| Startup, Initialization, and Power24        |

| Power-Up Sequence                           |

| Power Reduction Modes                       |

| Digital Power Supply24                      |

| Input/Output Power Supply24                 |

| Clock Generation and Management24           |

| Clocking and Sampling Rates26               |

| Sampling                | g Rates                 | 26 |

|-------------------------|-------------------------|----|

| PLL                     |                         | 27 |

| Record Sign             | nal Path                | 29 |

| Input Sig               | nal Paths               | 29 |

| Analog-to               | o-Digital Converters    | 31 |

| Automatic I             | Level Control (ALC)     | 32 |

| ALC Para                | ameters                 | 32 |

| Noise Ga                | te Function             | 33 |

| Playback Sig            | gnal Path               | 35 |

| Output Si               | ignal Paths             | 35 |

| Headpho                 | ne Output               | 36 |

| Pop-and-                | -Click Suppression      | 37 |

| Line Out                | puts                    | 37 |

| Control Por             | rts                     | 38 |

| Burst Mo                | ode Writing and Reading | 38 |

| I <sup>2</sup> C Port . |                         | 38 |

| SPI Port.               |                         | 41 |

| Serial Data             | Input/Output Ports      | 42 |

| Application             | s Information           | 44 |

| Power Su                | pply Bypass Capacitors  | 44 |

| GSM Noi                 | ise Filter              | 44 |

| Groundir                | ng                      | 44 |

| Exposed                 | Pad PCB Design          | 44 |

| Control Reg             | gisters                 | 45 |

| Control F               | Register Details        | 46 |

| Outline Dir             | mensions                | 79 |

| Ordering                | g Guide                 | 79 |

# **REVISION HISTORY**

| 8/2018—Rev. C to Rev. D                                   |

|-----------------------------------------------------------|

| Changed t <sub>SODM</sub> to t <sub>SOD</sub> , Table 711 |

| Changes to t <sub>SOD</sub> Parameter, Table 711          |

| Changes to Figure 312                                     |

|                                                           |

| 9/2010—Rev. B to Rev. C                                   |

| Changes to Figure 11                                      |

| 7/2010 P. A. P. P.                                        |

| 5/2010—Rev. A to Rev. B                                   |

| Changes to Burst Mode Writing and Reading Section38       |

| Changes to Table 2645                                     |

| Change to Table 4358                                      |

| Added R67: Dejitter Control, 16,438 (0x4036) Section73    |

| 12/2009—Rev. 0 to Rev. A                                  |

| Changes to Features Section                               |

| Changes to General Description Section                    |

| Changes to Table 16                                       |

| Change to Table 5                                         |

| e e e e e e e e e e e e e e e e e e e                     |

| Changes to Figure 6                                       |

| · ·                                                       |

| Changes to Captions of Figure 15, Figure 16, Figure 18,   |

| and Figure 19                                             |

| Changes to Captions of Figure 21 and Figure 24            |

| Added Figure 22; Renumbered Sequentially19                |

| Change to Figure 25                                       |

| Change to Figure 2621                                     |

| Change to Figure 2722                                     |

| Change to Theory of Operation Section23                   |

| Changes to Power Reduction Modes Section and              |

| Case 1: PLL Is Bypassed Section24                         |

| Changes to PLL Lock Acquisition Section25                 |

| Changes to Core Clock Section26                           |

| Changes to Input Signal Paths Section and Figure 3129                |

|----------------------------------------------------------------------|

| Changes to Figure 32 and Figure 3330                                 |

| Changes to ADC Full-Scale Level Section31                            |

| Change to Automatic Level Control (ALC) Section32                    |

| Changes to Output Signal Paths Section35                             |

| Changes to Headphone Output Section36                                |

| Changes to Jack Detection Section, Pop-and-Click                     |

| Suppression Section, and Line Outputs Section                        |

| Changes to Control Ports Section and I <sup>2</sup> C Port Section38 |

| Added Burst Mode Writing and Reading Section38                       |

| Changes to SPI Port Section41                                        |

| Changes to Serial Data Input/Output Ports Section, Table 24,         |

| and Table 2542                                                       |

| Added Figure 5642                                                    |

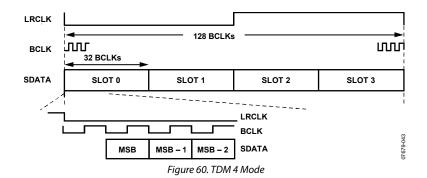

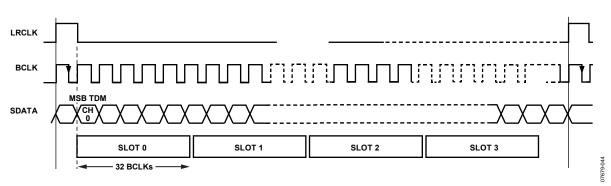

| Changes to Figure 60 and Figure 6143                                 |

| Changes to Table 2645                                                |

| Changes to R2: Digital Microphone/Jack Detection Control,            |

| 16,392 (0x4008) Section and Table 2947                               |

| Changes to Table 3552                                                |

| Changes to Table 3653                                                |

| Changes to R15: Serial Port Control 0, 16,405 (0x4015)               |

| Section and Table 4257                                               |

| Change to Table 4358                                                 |

| Changes to Table 44, R18: Converter Control 1, 16,408                |

| (0x4018) Section, and Table 4559                                     |

| Changes to Table 53, R27: Playback L/R Mixer Right (Mixer 6)         |

| Line Output Control, 16,417 (0x4021) Section, and Table 5465         |

| Changes to Table 55, R29: Playback Headphone Left Volume             |

| Control, 16,419 (0x4023) Section, and Table 56                       |

| Changes to R42: Jack Detect Pin Control, 16,433 (0x4031)             |

| Section and Table 6973                                               |

1/2009—Revision 0: Initial Version

# **SPECIFICATIONS**

Supply voltage (AVDD) = 3.3 V,  $T_A$  = 25°C, master clock = 12.288 MHz (48 kHz  $f_S$ , 256 ×  $f_S$  mode), input sample rate = 48 kHz, measurement bandwidth = 20 Hz to 20 kHz, word width = 24 bits,  $C_{LOAD}$  (digital output) = 20 pF,  $I_{LOAD}$  (digital output) = 2 mA,  $V_{IH}$  = 2 V,  $V_{IL}$  = 0.8 V, unless otherwise noted. Performance of all channels is identical, exclusive of the interchannel gain mismatch and interchannel phase deviation specifications.

# **ANALOG PERFORMANCE SPECIFICATIONS**

Specifications guaranteed at 25°C (ambient).

Table 1.

| Parameter                         | <b>Test Conditions/Comments</b>         | Min | Тур         | Max | Unit          |

|-----------------------------------|-----------------------------------------|-----|-------------|-----|---------------|

| ANALOG-TO-DIGITAL CONVERTERS      | ADC performance excludes mixers and PGA |     |             |     |               |

| ADC Resolution                    | All ADCs                                |     | 24          |     | Bits          |

| Digital Attenuation Step          |                                         |     | 0.375       |     | dB            |

| Digital Attenuation Range         |                                         |     | 95          |     | dB            |

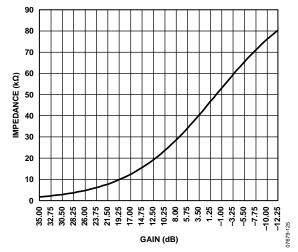

| INPUT RESISTANCE                  |                                         |     |             |     |               |

| Single-Ended Line Input           | –12 dB gain                             |     | 83          |     | kΩ            |

|                                   | 0 dB gain                               |     | 21          |     | kΩ            |

|                                   | 6 dB gain                               |     | 10.5        |     | kΩ            |

| PGA Inverting Inputs              | –12 dB gain                             |     | 84.5        |     | kΩ            |

|                                   | 0 dB gain                               |     | 53          |     | kΩ            |

|                                   | 35.25 dB gain                           |     | 2           |     | kΩ            |

| PGA Noninverting Inputs           | All gains                               |     | 105         |     | kΩ            |

| SINGLE-ENDED LINE INPUT           |                                         |     |             |     |               |

| Full-Scale Input Voltage (0 dB)   | Scales linearly with AVDD               |     | AVDD/3.3    |     | V rms         |

|                                   | AVDD = 1.8 V                            |     | 0.55 (1.56) |     | V rms (V p-p) |

|                                   | AVDD = 3.3 V                            |     | 1.0 (2.83)  |     | V rms (V p-p  |

| Dynamic Range                     | 20 Hz to 20 kHz, -60 dB input           |     |             |     |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                            |     | 94          |     | dB            |

| <b>5</b>                          | AVDD = 3.3 V                            |     | 99          |     | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                            |     | 91          |     | dB            |

|                                   | AVDD = 3.3 V                            |     | 96          |     | dB            |

| Total Harmonic Distortion + Noise | −1 dBFS                                 |     |             |     |               |

|                                   | AVDD = 1.8 V                            |     | -88         |     | dB            |

|                                   | AVDD = 3.3 V                            |     | -90         |     | dB            |

| Signal-to-Noise Ratio             |                                         |     |             |     |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                            |     | 94          |     | dB            |

| 3 ( .,                            | AVDD = 3.3 V                            |     | 99          |     | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                            |     | 91          |     | dB            |

|                                   | AVDD = 3.3 V                            |     | 96          |     | dB            |

| Gain per Step                     |                                         |     | 3           |     | dB            |

| Total Gain Range                  |                                         | -12 |             | +6  | dB            |

| Mute Attenuation                  |                                         |     | -87         | -   | dB            |

| Interchannel Gain Mismatch        |                                         |     | 0.005       |     | dB            |

| Offset Error                      |                                         |     | 0           |     | mV            |

| Gain Error                        |                                         |     | -12         |     | %             |

| Interchannel Isolation            |                                         |     | 68          |     | dB            |

| Power Supply Rejection Ratio      | CM capacitor = 20 μF                    |     |             |     |               |

|                                   | 100 mV p-p @ 217 Hz                     |     | 65          |     | dB            |

|                                   | 100 mV p-p @ 1 kHz                      |     | 67          |     | dB            |

| Parameter                         | Test Conditions/Comments      | Min | Тур             | Max    | Unit          |

|-----------------------------------|-------------------------------|-----|-----------------|--------|---------------|

| PSEUDO-DIFFERENTIAL PGA INPUT     |                               |     |                 | _      |               |

| Full-Scale Input Voltage (0 dB)   | Scales linearly with AVDD     |     | AVDD/3.3        |        | V rms         |

|                                   | AVDD = 1.8 V                  |     | 0.55 (1.56)     |        | V rms (V p-p) |

|                                   | AVDD = 3.3 V                  |     | 1.0 (2.83)      |        | V rms (V p-p) |

| Dynamic Range                     | 20 Hz to 20 kHz, -60 dB input |     |                 |        |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                  |     | 92              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 98              |        | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                  |     | 90              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 95              |        | dB            |

| Total Harmonic Distortion + Noise | −1 dBFS                       |     |                 |        |               |

|                                   | AVDD = 1.8 V                  |     | -88             |        | dB            |

|                                   | AVDD = 3.3 V                  |     | -89             |        | dB            |

| Signal-to-Noise Ratio             |                               |     |                 |        |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                  |     | 92              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 98              |        | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                  |     | 90              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 95              |        | dB            |

| Volume Control Step               | PGA gain                      |     | 0.75            |        | dB            |

| Volume Control Range              | PGA gain                      | -12 |                 | +35.25 | dB            |

| PGA Boost                         |                               |     | 20              |        | dB            |

| Mute Attenuation                  |                               |     | -87             |        | dB            |

| Interchannel Gain Mismatch        |                               |     | 0.005           |        | dB            |

| Offset Error                      |                               |     | 0               |        | mV            |

| Gain Error                        |                               |     | -14             |        | %             |

| Interchannel Isolation            |                               |     | 83              |        | dB            |

| Common-Mode Rejection Ratio       | 100 mV rms, 1 kHz             |     | 65              |        | dB            |

|                                   | 100 mV rms, 20 kHz            |     | 65              |        | dB            |

| FULL DIFFERENTIAL PGA INPUT       | Differential PGA inputs       |     |                 |        |               |

| Full-Scale Input Voltage (0 dB)   | Scales linearly with AVDD     |     | AVDD/3.3        |        | V rms         |

|                                   | AVDD = 1.8 V                  |     | 0.55 (1.56)     |        | V rms (V p-p) |

|                                   | AVDD = 3.3 V                  |     | 1.0 (2.83)      |        | V rms (V p-p) |

| Dynamic Range                     | 20 Hz to 20 kHz, -60 dB input |     |                 |        |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                  |     | 92              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 98              |        | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                  |     | 90              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 95              |        | dB            |

| Total Harmonic Distortion + Noise | -1 dBFS                       |     |                 |        |               |

|                                   | AVDD = 1.8 V                  |     | -70             |        | dB            |

|                                   | AVDD = 3.3 V                  |     | -78             |        | dB            |

| Signal-to-Noise Ratio             |                               |     |                 |        |               |

| With A-Weighted Filter (RMS)      | AVDD = 1.8 V                  |     | 92              |        | dB            |

| -                                 | AVDD = 3.3 V                  |     | 98              |        | dB            |

| No Filter (RMS)                   | AVDD = 1.8 V                  |     | 90              |        | dB            |

|                                   | AVDD = 3.3 V                  |     | 95              |        | dB            |

| Volume Control Step               | PGA gain                      |     | 0.75            |        | dB            |

| Volume Control Range              | PGA gain                      | -12 |                 | +35.25 | dB            |

| PGA Boost                         |                               |     | 20              |        | dB            |

| Mute Attenuation                  |                               |     | <del>-</del> 87 |        | dB            |

| Interchannel Gain Mismatch        |                               |     | 0.005           |        | dB            |

| Offset Error                      |                               |     | 0               |        | mV            |

| Gain Error                        |                               |     | <del>-</del> 14 |        | %             |

| Parameter                               | Test Conditions/Comments                                | Min | Тур             | Max | Unit          |

|-----------------------------------------|---------------------------------------------------------|-----|-----------------|-----|---------------|

| Interchannel Isolation                  |                                                         |     | 83              |     | dB            |

| Common-Mode Rejection Ratio             | 100 mV rms, 1 kHz                                       |     | 65              |     | dB            |

|                                         | 100 mV rms, 20 kHz                                      |     | 65              |     | dB            |

| MICROPHONE BIAS                         | MBIEN = 1                                               |     |                 |     |               |

| Bias Voltage                            |                                                         |     |                 |     |               |

| $0.65 \times AVDD$                      | AVDD = 1.8 V, MBI = 1                                   |     | 1.17            |     | V             |

|                                         | AVDD = 3.3 V, MBI = 1                                   |     | 2.145           |     | V             |

| $0.90 \times AVDD$                      | AVDD = 1.8  V,  MBI = 0                                 |     | 1.62            |     | V             |

|                                         | AVDD = 3.3  V,  MBI = 0                                 |     | 2.97            |     | V             |

| Bias Current Source                     | AVDD = 3.3 V, MBI = 0, MPERF = 1                        |     |                 | 3   | mA            |

| Noise in the Signal Bandwidth           | AVDD = 3.3 V, 1 kHz to 20 kHz                           |     |                 |     |               |

| -                                       | MBI = 0, $MPERF = 0$                                    |     | 42              |     | nV/√Hz        |

|                                         | MBI = 0, MPERF = 1                                      |     | 85              |     | nV/√Hz        |

|                                         | MBI = 1, MPERF = 0                                      |     | 25              |     | nV/√Hz        |

|                                         | MBI = 1, MPERF = 1                                      |     | 37              |     | nV/√Hz        |

| DIGITAL-TO-ANALOG CONVERTERS            | DAC performance excludes mixers and headphone amplifier |     |                 |     |               |

| DAC Resolution                          | All DACs                                                |     | 24              |     | Bits          |

| Digital Attenuation Step                |                                                         |     | 0.375           |     | dB            |

| Digital Attenuation Range               |                                                         |     | 95              |     | dB            |

| DAC TO LINE OUTPUT                      |                                                         |     |                 |     |               |

| Full-Scale Output Voltage (0 dB)        | Scales linearly with AVDD                               |     | AVDD/3.3        |     | V rms         |

| Tall Scale Output voltage (Oub)         | AVDD = 1.8 V                                            |     | 0.50 (1.41)     |     | V rms (V p-p) |

|                                         | AVDD = 3.3 V                                            |     | 0.92 (2.60)     |     | V rms (V p-p) |

| Analog Volume Control Step              | Line output volume control                              |     | 0.75            |     | dB            |

| Analog Volume Control Range             | Line output volume control                              | -57 | 1               | +6  | dB            |

| Mute Attenuation                        |                                                         |     | -87             |     | dB            |

| Dynamic Range                           | 20 Hz to 20 kHz, –60 dB input, line output mode         |     |                 |     |               |

| With A-Weighted Filter (RMS)            | AVDD = 1.8 V                                            |     | 96              |     | dB            |

|                                         | AVDD = 3.3 V                                            |     | 101             |     | dB            |

| No Filter (RMS)                         | AVDD = 1.8 V                                            |     | 93.5            |     | dB            |

| , ,                                     | AVDD = 3.3 V                                            |     | 98              |     | dB            |

| Total Harmonic Distortion + Noise       | –1 dBFS, line output mode                               |     |                 |     | dB            |

|                                         | AVDD = 1.8 V                                            |     | -90             |     | dB            |

|                                         | AVDD = 3.3 V                                            |     | <del>-</del> 92 |     | dB            |

| Signal-to-Noise Ratio                   | Line output mode                                        |     |                 |     |               |

| With A-Weighted Filter (RMS)            | AVDD = 1.8 V                                            |     | 96              |     | dB            |

|                                         | AVDD = 3.3 V                                            |     | 101             |     | dB            |

| No Filter (RMS)                         | AVDD = 1.8 V                                            |     | 93.5            |     | dB            |

| ( )                                     | AVDD = 3.3 V                                            |     | 98              |     | dB            |

| Power Supply Rejection Ratio            | CM capacitor = 20 μF                                    |     |                 |     |               |

|                                         | 100 mV p-p @ 217 Hz                                     |     | 56              |     | dB            |

|                                         | 100 mV p-p @ 1 kHz                                      |     | 70              |     | dB            |

| Gain Error                              |                                                         |     | 3               |     | %             |

| Guill EllOl                             |                                                         |     | 0.005           |     | dB            |

| Interchannel Gain Mismatch              |                                                         |     |                 |     | UD            |

| Interchannel Gain Mismatch Offset Error |                                                         |     | 0               |     | mV            |

| Parameter                           | Test Conditions/Comments                                   | Min | Тур         | Max | Unit          |

|-------------------------------------|------------------------------------------------------------|-----|-------------|-----|---------------|

| DAC TO HEADPHONE/EARPIECE<br>OUTPUT | Po = output power per channel                              |     |             |     |               |

| Full-Scale Output Voltage (0 dB)    | Scales linearly with AVDD                                  |     | AVDD/3.3    |     | V rms         |

|                                     | AVDD = 1.8 V                                               |     | 0.50 (1.41) |     | V rms (V p-p) |

|                                     | AVDD = 3.3 V                                               |     | 0.92 (2.60) |     | V rms (V p-p) |

| Total Harmonic Distortion + Noise   | −4 dBFS                                                    |     |             |     |               |

| 16 Ω load                           | $AVDD = 1.8 \text{ V}, P_0 = 6.4 \text{ mW}$               |     | -76         |     | dB            |

|                                     | $AVDD = 3.3 \text{ V}, P_0 = 21.1 \text{ mW}$              |     | -82         |     | dB            |

| 32 Ω load                           | $AVDD = 1.8 \text{ V}, P_0 = 3.8 \text{ mW}$               |     | -82         |     | dB            |

|                                     | $AVDD = 3.3 \text{ V}, P_0 = 10.6 \text{ mW}$              |     | -82         |     | dB            |

| Power Supply Rejection Ratio        | CM capacitor = 20 μF                                       |     |             |     |               |

|                                     | 100 mV p-p @ 217 Hz                                        |     | 56          |     | dB            |

|                                     | 100 mV p-p @ 1 kHz                                         |     | 67          |     | dB            |

| Interchannel Isolation              | 1 kHz, 0 dBFS input signal, 32 $\Omega$ load, AVDD = 3.3 V |     |             |     |               |

|                                     | Referred to GND                                            |     | 73          |     | dB            |

|                                     | Referred to CM (capless headphone mode)                    |     | 50          |     | dB            |

| REFERENCE                           |                                                            |     |             |     |               |

| Common-Mode Reference Output        | CM pin                                                     |     | AVDD/2      |     | V             |

# **POWER SUPPLY SPECIFICATIONS**

Table 2.

| Parameter                           | Test Conditions/Comments                  | Min  | Тур  | Max  | Unit |

|-------------------------------------|-------------------------------------------|------|------|------|------|

| SUPPLIES                            |                                           |      |      |      |      |

| Voltage                             | DVDDOUT                                   |      | 1.56 |      | V    |

|                                     | AVDD                                      | 1.8  | 3.3  | 3.65 | V    |

|                                     | IOVDD                                     | 1.63 | 3.3  | 3.65 | V    |

| Digital I/O Current (IOVDD = 1.8 V) | 20 pF capacitive load on all digital pins |      |      |      |      |

| Slave Mode                          | $f_S = 48 \text{ kHz}$                    |      | 0.25 |      | mA   |

|                                     | $f_S = 96 \text{ kHz}$                    |      | 0.48 |      | mA   |

|                                     | $f_S = 8 \text{ kHz}$                     |      | 0.07 |      | mA   |

| Master Mode                         | $f_S = 48 \text{ kHz}$                    |      | 0.62 |      | mA   |

|                                     | $f_S = 96 \text{ kHz}$                    |      | 1.23 |      | mA   |

|                                     | $f_S = 8 \text{ kHz}$                     |      | 0.11 |      | mA   |

| Digital I/O Current (IOVDD = 3.3 V) | 20 pF capacitive load on all digital pins |      |      |      |      |

| Slave Mode                          | $f_S = 48 \text{ kHz}$                    |      | 0.48 |      | mA   |

|                                     | $f_S = 96 \text{ kHz}$                    |      | 0.9  |      | mA   |

|                                     | $f_S = 8 \text{ kHz}$                     |      | 0.13 |      | mA   |

| Master Mode                         | $f_S = 48 \text{ kHz}$                    |      | 1.51 |      | mA   |

|                                     | f <sub>s</sub> = 96 kHz                   |      | 3    |      | mA   |

|                                     | $f_S = 8 \text{ kHz}$                     |      | 0.27 |      | mA   |

| Analog Current (AVDD)               | See Table 3                               |      |      |      |      |

# **TYPICAL CURRENT CONSUMPTION**

Master clock = 12.288 MHz, input sample rate = 48 kHz, input tone = 1 kHz, normal power management settings, ADC input @ -1 dBFS, DAC input @ 0 dBFS. For total power consumption, add the IOVDD current listed in Table 2.

Table 3.

| Operating Voltage    | Audio Path                                               | Clock Generation | Typical AVDD Current Consumption (mA) |

|----------------------|----------------------------------------------------------|------------------|---------------------------------------|

| AVDD = IOVDD = 3.3 V | Record stereo differential to ADC                        | Direct MCLK      | 5.24                                  |

|                      |                                                          | Integer PLL      | 6.57                                  |

|                      | DAC stereo playback to line output (10 k $\Omega$ )      | Direct MCLK      | 5.55                                  |

|                      |                                                          | Integer PLL      | 6.90                                  |

|                      | DAC stereo playback to headphone (16 $\Omega$ )          | Direct MCLK      | 55.5                                  |

|                      |                                                          | Integer PLL      | 56.8                                  |

|                      | DAC stereo playback to headphone (32 $\Omega$ )          | Direct MCLK      | 30.9                                  |

|                      |                                                          | Integer PLL      | 32.25                                 |

|                      | DAC stereo playback to capless headphone (32 $\Omega$ )  | Direct MCLK      | 56.75                                 |

|                      |                                                          | Integer PLL      | 58                                    |

|                      | Record aux stereo bypass to line output (10 k $\Omega$ ) | Direct MCLK      | 1.9                                   |

|                      |                                                          | Integer PLL      | 3.3                                   |

| AVDD = IOVDD = 1.8 V | Record stereo differential to ADC                        | Direct MCLK      | 4.25                                  |

|                      |                                                          | Integer PLL      | 5.55                                  |

|                      | DAC stereo playback to line output (10 k $\Omega$ )      | Direct MCLK      | 4.7                                   |

|                      |                                                          | Integer PLL      | 5.7                                   |

|                      | DAC stereo playback to headphone (16 $\Omega$ )          | Direct MCLK      | 30.81                                 |

|                      |                                                          | Integer PLL      | 32                                    |

|                      | DAC stereo playback to headphone (32 Ω)                  | Direct MCLK      | 18.3                                  |

|                      |                                                          | Integer PLL      | 19.5                                  |

|                      | DAC stereo playback to capless headphone (32 $\Omega$ )  | Direct MCLK      | 32.6                                  |

|                      |                                                          | Integer PLL      | 33.7                                  |

|                      | Record aux stereo bypass to line output (10 k $\Omega$ ) | Direct MCLK      | 1.9                                   |

|                      |                                                          | Integer PLL      | 3.07                                  |

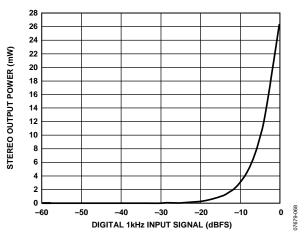

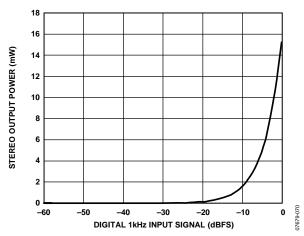

# **TYPICAL POWER MANAGEMENT MEASUREMENTS**

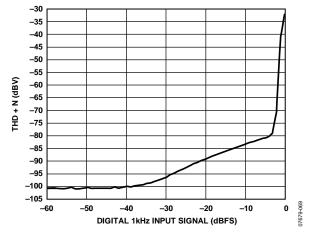

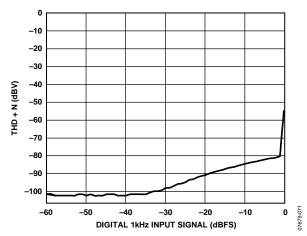

Master clock = 12.288 MHz, integer PLL, input sample rate = 48 kHz, input tone = 1 kHz. Pseudo-differential input to ADCs, DACs to line output with 10 k $\Omega$  load. ADC input @ -1 dBFS, DAC input @ 0 dBFS. In Table 4, the mixer boost and power management conditions are set for MXBIAS[1:0], ADCBIAS[1:0], HPBIAS[1:0], and DACBIAS[1:0]. RBIAS[1:0] and PBIAS[1:0] do not have an extreme power saving mode and are therefore set for power saving mode in the extreme power saving rows in Table 4.

Table 4.

| Operating Voltage              | Power Management<br>Setting | Mixer Boost<br>Setting | Typical<br>AVDD Current<br>Consumption (mA) | Typical ADC<br>THD + N (dB) | Typical Line Output<br>THD + N (dB) |

|--------------------------------|-----------------------------|------------------------|---------------------------------------------|-----------------------------|-------------------------------------|

| AVDD = IOVDD = 3.3 V           | Normal (default)            | Normal operation       | 9.6                                         | -91                         | -92.5                               |

| אטיט – טטיט ( = 3.3 V – טטיט ) |                             | Boost Level 1          | 9.75                                        | -91.5                       | -92.5                               |

|                                |                             | Boost Level 2          | 9.92                                        | -91.5                       | -92.5                               |

|                                |                             | Boost Level 3          | 10.25                                       | -91.5                       | -92.5                               |

|                                | Extreme power saving        | Normal operation       | 7.09                                        | -84.5                       | -87                                 |

|                                |                             | Boost Level 1          | 7.19                                        | -84.8                       | -87.1                               |

|                                |                             | Boost Level 2          | 7.29                                        | -84.8                       | -87.1                               |

|                                |                             | Boost Level 3          | 7.49                                        | -85                         | -87.1                               |

|                                | Power saving                | Normal operation       | 7.67                                        | -89.5                       | -90                                 |

|                                |                             | Boost Level 1          | 7.77                                        | -89.5                       | -90                                 |

|                                |                             | Boost Level 2          | 7.86                                        | -89.8                       | -90                                 |

|                                |                             | Boost Level 3          | 8.07                                        | -89.8                       | -90                                 |

|                                | Enhanced performance        | Normal operation       | 10.55                                       | -91                         | -93.5                               |

|                                |                             | Boost Level 1          | 10.74                                       | <b>-91</b>                  | -93.5                               |

|                                |                             | Boost Level 2          | 10.93                                       | -91                         | -93.5                               |

|                                |                             | Boost Level 3          | 11.33                                       | -91                         | -93.5                               |

| AVDD = IOVDD = 1.8 V           | Normal (default)            | Normal operation       | 8.1                                         | -88                         | -91.2                               |

|                                |                             | Boost Level 1          | 8.26                                        | -88                         | -91.2                               |

|                                |                             | Boost Level 2          | 8.41                                        | -88                         | -91.2                               |

|                                |                             | Boost Level 3          | 8.73                                        | -88                         | -91.2                               |

|                                | Extreme power saving        | Normal operation       | 5.73                                        | -85                         | -86                                 |

|                                |                             | Boost Level 1          | 5.82                                        | -85.4                       | -86                                 |

|                                |                             | Boost Level 2          | 5.91                                        | -85.5                       | -86                                 |

|                                |                             | Boost Level 3          | 6.1                                         | -85.5                       | -86                                 |

|                                | Power saving                | Normal operation       | 6.27                                        | -86                         | -89.4                               |

|                                |                             | Boost Level 1          | 6.36                                        | -86.1                       | -89.5                               |

|                                |                             | Boost Level 2          | 6.46                                        | -86.3                       | -89.5                               |

|                                |                             | Boost Level 3          | 6.65                                        | -86.3                       | -89.5                               |

|                                | Enhanced performance        | Normal operation       | 9.01                                        | -88                         | -91.5                               |

|                                |                             | Boost Level 1          | 9.2                                         | -88                         | -91.5                               |

|                                |                             | Boost Level 2          | 9.38                                        | -88                         | -91.5                               |

|                                |                             | Boost Level 3          | 9.76                                        | -88                         | -91.5                               |

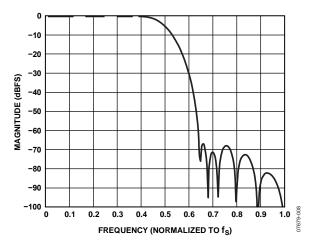

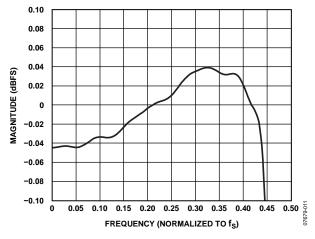

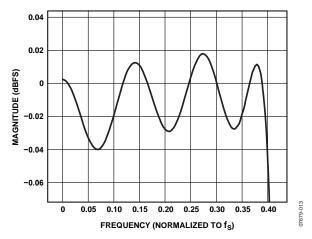

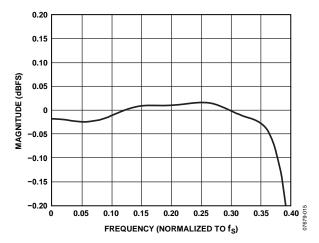

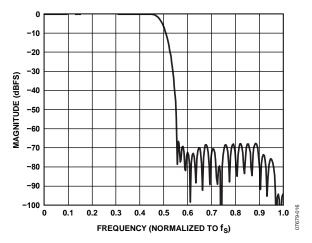

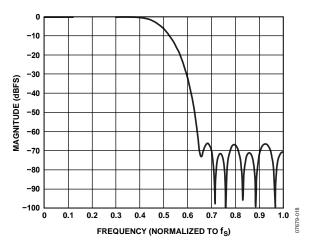

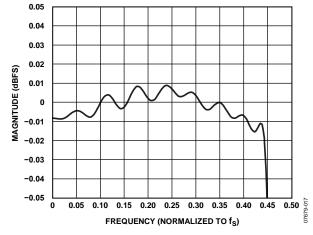

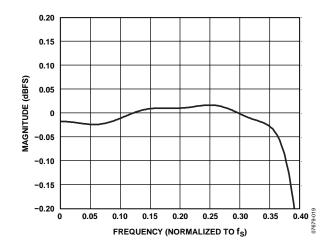

# **DIGITAL FILTERS**

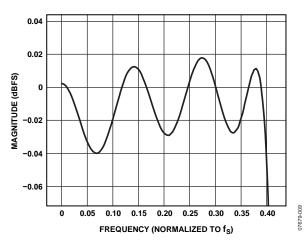

Table 5.

| Parameter                | Mode                      | Factor                    | Min | Тур    | Max   | Unit |

|--------------------------|---------------------------|---------------------------|-----|--------|-------|------|

| ADC DECIMATION FILTER    | All modes, typ @ 48 kHz   |                           |     |        |       |      |

| Pass Band                |                           | 0.4375 f <sub>s</sub>     |     | 21     |       | kHz  |

| Pass-Band Ripple         |                           |                           |     | ±0.015 |       | dB   |

| Transition Band          |                           | 0.5 f <sub>s</sub>        |     | 24     |       | kHz  |

| Stop Band                |                           | <b>0.5625</b> fs          |     | 27     |       | kHz  |

| Stop-Band Attenuation    |                           |                           |     | 67     |       | dB   |

| Group Delay              |                           | 22.9844/fs                |     | 479    |       | μs   |

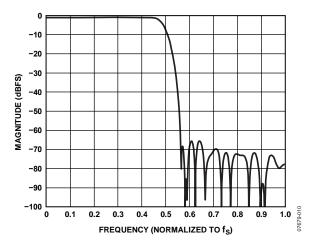

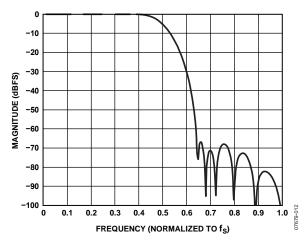

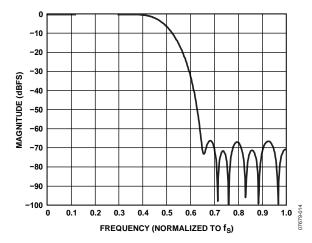

| DAC INTERPOLATION FILTER |                           |                           |     |        |       |      |

| Pass Band                | 48 kHz mode, typ @ 48 kHz | 0.4535 fs                 |     | 22     |       | kHz  |

|                          | 96 kHz mode, typ @ 96 kHz | <b>0.3646</b> fs          |     | 35     |       | kHz  |

| Pass-Band Ripple         | 48 kHz mode, typ @ 48 kHz |                           |     |        | ±0.01 | dB   |

|                          | 96 kHz mode, typ @ 96 kHz |                           |     |        | ±0.05 | dB   |

| Transition Band          | 48 kHz mode, typ @ 48 kHz | <b>0.5</b> f <sub>s</sub> |     | 24     |       | kHz  |

|                          | 96 kHz mode, typ @ 96 kHz | 0.5 f <sub>s</sub>        |     | 48     |       | kHz  |

| Stop Band                | 48 kHz mode, typ @ 48 kHz | <b>0.5465</b> fs          |     | 26     |       | kHz  |

|                          | 96 kHz mode, typ @ 96 kHz | 0.6354 f <sub>s</sub>     |     | 61     |       | kHz  |

| Stop-Band Attenuation    | 48 kHz mode, typ @ 48 kHz |                           |     | 69     |       | dB   |

|                          | 96 kHz mode, typ @ 96 kHz |                           |     | 68     |       | dB   |

| Group Delay              | 48 kHz mode, typ @ 48 kHz | 25/f <sub>s</sub>         |     | 521    |       | μs   |

|                          | 96 kHz mode, typ @ 96 kHz | 11/f <sub>s</sub>         |     | 115    |       | μs   |

# **DIGITAL INPUT/OUTPUT SPECIFICATIONS**

-40°C <  $T_A$  < +85°C, IOVDD =  $3.3~V \pm 10\%$ .

Table 6.

| Parameter                              | Test Conditions/Comments                        | Min Typ     | Max                | Unit |

|----------------------------------------|-------------------------------------------------|-------------|--------------------|------|

| INPUT SPECIFICATIONS                   |                                                 |             |                    |      |

| Input Voltage High (V <sub>IH</sub> )  |                                                 | 0.7 × IOVDD |                    | V    |

| Input Voltage Low (V <sub>IL</sub> )   |                                                 |             | $0.3 \times IOVDD$ | V    |

| Input Leakage                          |                                                 |             |                    |      |

| Pull-Ups/Pull-Downs Disabled           | I <sub>IH</sub> @ V <sub>IH</sub> = 3.3 V       | -0.17       | +0.17              | μΑ   |

|                                        | $I_{IL} @ V_{IL} = 0 V$                         | -0.17       | +0.17              | μΑ   |

|                                        | $I_{IL} @ V_{IL} = 0 V (MCLK pin)$              | -13.5       | -0.5               | μΑ   |

| Pull-Ups Enabled                       | I <sub>IH</sub> @ V <sub>IH</sub> = 3.3 V       | -0.7        | +0.7               | μΑ   |

|                                        | $I_{IL} @ V_{IL} = 0 V$                         | -13.5       | -0.5               | μΑ   |

| Pull-Downs Enabled                     | I <sub>IH</sub> @ V <sub>IH</sub> = 3.3 V       | 2.7         | 8.3                | μΑ   |

|                                        | $I_{IL} @ V_{IL} = 0 V$                         | -0.18       | +0.18              | μΑ   |

| Input Capacitance                      |                                                 |             | 5                  | рF   |

| OUTPUT SPECIFICATIONS                  |                                                 |             |                    |      |

| Output Voltage High (V <sub>OH</sub> ) | I <sub>OH</sub> = 2 mA @ 3.3 V, 0.85 mA @ 1.8 V | 0.8 × IOVDD |                    | V    |

| Output Voltage Low (Vol)               | I <sub>OL</sub> = 2 mA @ 3.3 V, 0.85 mA @ 1.8 V |             | $0.1 \times IOVDD$ | V    |

# **DIGITAL TIMING SPECIFICATIONS**

$-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}, \text{IOVDD} = 3.3 \text{ V} \pm 10\%.$

Table 7. Digital Timing

|                       |                  | Limit            |      |                                                                                                     |

|-----------------------|------------------|------------------|------|-----------------------------------------------------------------------------------------------------|

| Parameter             | t <sub>MIN</sub> | t <sub>MAX</sub> | Unit | Description                                                                                         |

| MASTER CLOCK          |                  |                  |      |                                                                                                     |

| t <sub>MP</sub>       | 74               | 488              | ns   | MCLK period, $256 \times f_s$ mode.                                                                 |

| t <sub>MP</sub>       | 37               | 244              | ns   | MCLK period, $512 \times f_s$ mode.                                                                 |

| t <sub>MP</sub>       | 24.7             | 162.7            | ns   | MCLK period, $768 \times f_s$ mode.                                                                 |

| $t_{MP}$              | 18.5             | 122              | ns   | MCLK period, $1024 \times f_s$ mode.                                                                |

| SERIAL PORT           |                  |                  |      |                                                                                                     |

| t <sub>BIL</sub>      | 5                |                  | ns   | BCLK pulse width low.                                                                               |

| t <sub>BIH</sub>      | 5                |                  | ns   | BCLK pulse width high.                                                                              |

| t <sub>LIS</sub>      | 5                |                  | ns   | LRCLK setup. Time to BCLK rising.                                                                   |

| t <sub>LIH</sub>      | 5                |                  | ns   | LRCLK hold. Time from BCLK rising.                                                                  |

| t <sub>SIS</sub>      | 5                |                  | ns   | DAC_SDATA setup. Time to BCLK rising.                                                               |

| t <sub>SIH</sub>      | 5                |                  | ns   | DAC_SDATA hold. Time from BCLK rising.                                                              |

| t <sub>SOD</sub>      |                  | 50               | ns   | ADC_SDATA delay. Time from BCLK falling in master or slave mode. Full range of IOVDD.               |

|                       |                  | 25               | ns   | ADC_SDATA delay. Time from BCLK falling in master or slave mode. $IOVDD = 3.3 \text{ V} \pm 10\%$ . |

| SPI PORT              |                  |                  |      |                                                                                                     |

| f <sub>CCLK</sub>     |                  | 10               | MHz  | CCLK frequency.                                                                                     |

| <b>t</b> ccpl         | 10               |                  | ns   | CCLK pulse width low.                                                                               |

| t <sub>CCPH</sub>     | 10               |                  | ns   | CCLK pulse width high.                                                                              |

| t <sub>CLS</sub>      | 5                |                  | ns   | CLATCH setup. Time to CCLK rising.                                                                  |

| tclh                  | 10               |                  | ns   | CLATCH hold. Time from CCLK rising.                                                                 |

| t <sub>CLPH</sub>     | 10               |                  | ns   | CLATCH pulse width high.                                                                            |

| t <sub>CDS</sub>      | 5                |                  | ns   | CDATA setup. Time to CCLK rising.                                                                   |

| t <sub>CDH</sub>      | 5                |                  | ns   | CDATA hold. Time from CCLK rising.                                                                  |

| t <sub>COD</sub>      |                  | 50               | ns   | COUT three-stated. Time from CLATCH rising.                                                         |

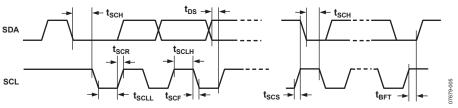

| I <sup>2</sup> C PORT |                  |                  |      |                                                                                                     |

| f <sub>SCL</sub>      |                  | 400              | kHz  | SCL frequency.                                                                                      |

| t <sub>SCLH</sub>     | 0.6              | 100              | μs   | SCL high.                                                                                           |

| t <sub>SCLL</sub>     | 1.3              |                  | μs   | SCL low.                                                                                            |

| t <sub>scs</sub>      | 0.6              |                  | μs   | Setup time; relevant for repeated start condition.                                                  |

| t <sub>sch</sub>      | 0.6              |                  | μs   | Hold time. After this period, the first clock is generated.                                         |

| t <sub>DS</sub>       | 100              |                  | ns   | Data setup time.                                                                                    |

| tscr                  | 122              | 300              | ns   | SCL rise time.                                                                                      |

| <b>t</b> scf          |                  | 300              | ns   | SCL fall time.                                                                                      |

| t <sub>SDR</sub>      |                  | 300              | ns   | SDA rise time.                                                                                      |

| t <sub>SDF</sub>      |                  | 300              | ns   | SDA fall time.                                                                                      |

| t <sub>BFT</sub>      | 0.6              |                  | μs   | Bus-free time. Time between stop and start.                                                         |

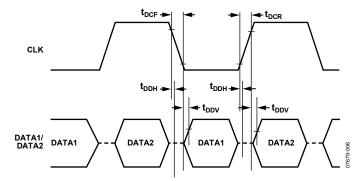

| DIGITAL MICROPHONE    |                  |                  | '    | $R_{LOAD} = 1 M\Omega$ , $C_{LOAD} = 14 pF$ .                                                       |

| t <sub>DCF</sub>      |                  | 10               | ns   | Digital microphone clock fall time.                                                                 |

| t <sub>DCR</sub>      |                  | 10               | ns   | Digital microphone clock rise time.                                                                 |

| t <sub>DDV</sub>      | 22               | 30               | ns   | Digital microphone delay time for valid data.                                                       |

| t <sub>DDH</sub>      | 0                | 12               | ns   | Digital microphone delay time for data three-stated.                                                |

# **DIGITAL TIMING DIAGRAMS**

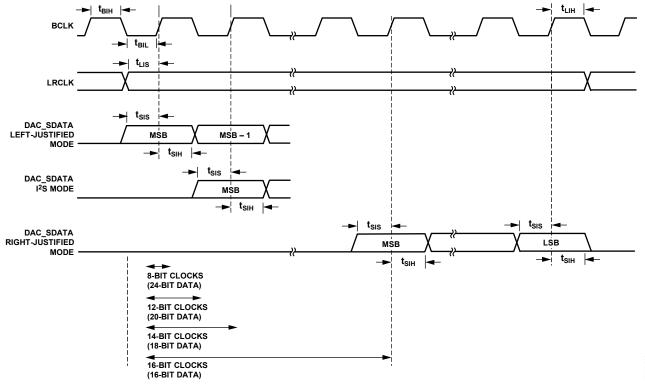

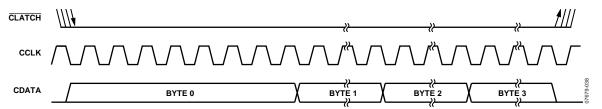

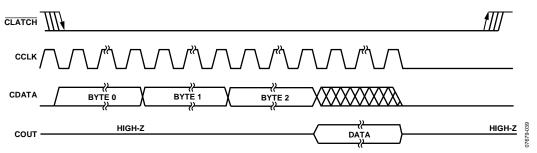

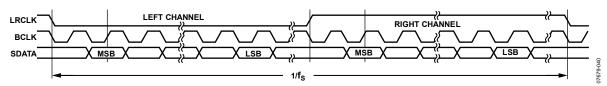

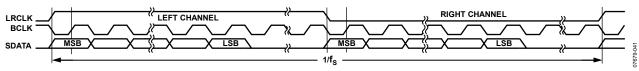

Figure 2. Serial Input Port Timing

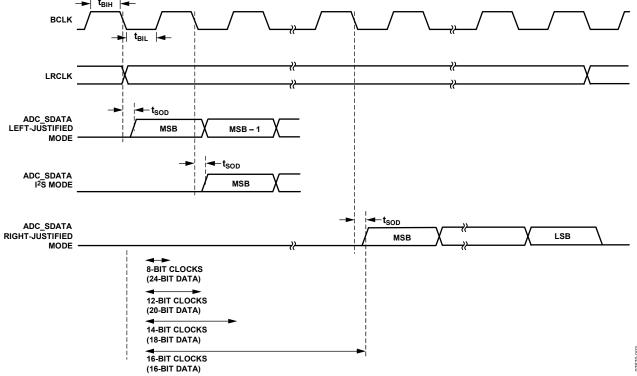

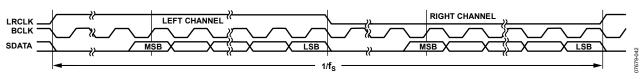

Figure 3. Serial Output Port Timing

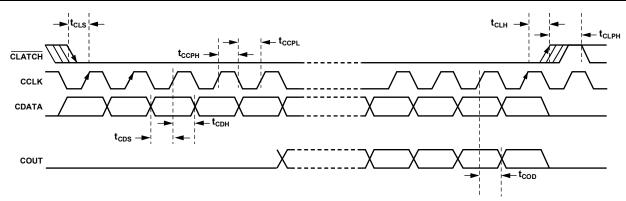

Figure 4. SPI Port Timing

Figure 5. I<sup>2</sup>C Port Timing

Figure 6. Digital Microphone Timing

# **ABSOLUTE MAXIMUM RATINGS**

## Table 8.

| Parameter                           | Rating                  |

|-------------------------------------|-------------------------|

| Power Supply (AVDD)                 | −0.3 V to +3.65 V       |

| Input Current (Except Supply Pins)  | ±20 mA                  |

| Analog Input Voltage (Signal Pins)  | -0.3 V to AVDD + 0.3 V  |

| Digital Input Voltage (Signal Pins) | -0.3 V to IOVDD + 0.3 V |

| Operating Temperature Range         | -40°C to +85°C          |

| Storage Temperature Range           | −65°C to +150°C         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# THERMAL RESISTANCE

$\theta_{JA}$  represents thermal resistance, junction-to-ambient;  $\theta_{JC}$  represents thermal resistance, junction-to-case. All characteristics are for a 4-layer board.

**Table 9. Thermal Resistance**

| Package Type  | θја  | <b>Ө</b> зс | Unit |

|---------------|------|-------------|------|

| 32-Lead LFCSP | 50.1 | 17          | °C/W |

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

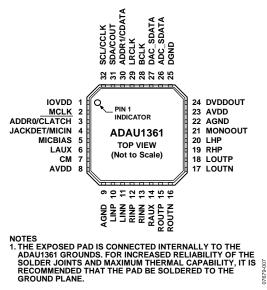

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. Pin Configuration

**Table 10. Pin Function Descriptions**

| Pin No. | Mnemonic      | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IOVDD         | PWR               | Supply for Digital Input and Output Pins. The digital output pins are supplied from IOVDD, which also sets the highest input voltage that should be seen on the digital input pins. IOVDD should be set between 1.8 V and 3.3 V. The current draw of this pin is variable because it is dependent on the loads of the digital outputs. IOVDD should be decoupled to DGND with a 100 nF capacitor and a 10 µF capacitor. |

| 2       | MCLK          | D_IN              | External Master Clock Input.                                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | ADDR0/CLATCH  | D_IN              | I <sup>2</sup> C Address Bit 0 (ADDR0).  SPI Latch Signal (CLATCH). Must go low at the beginning of an SPI transaction and high at the end of a transaction. Each SPI transaction can take a different number of CCLKs to complete, depending on the address and read/write bit that are sent at the beginning of the SPI transaction.                                                                                  |

| 4       | JACKDET/MICIN | D_IN              | Detect Insertion/Removal of Headphone Plug (JACKDET).                                                                                                                                                                                                                                                                                                                                                                   |

|         |               |                   | Digital Microphone Stereo Input (MICIN).                                                                                                                                                                                                                                                                                                                                                                                |

| 5       | MICBIAS       | A_OUT             | Bias Voltage for Electret Microphone.                                                                                                                                                                                                                                                                                                                                                                                   |

| 6       | LAUX          | A_IN              | Left Channel Single-Ended Auxiliary Input. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                            |

| 7       | СМ            | A_OUT             | AVDD/2 V Common-Mode Reference. A 10 $\mu$ F to 47 $\mu$ F standard decoupling capacitor should be connected between this pin and AGND to reduce crosstalk between the ADCs and DACs. This pin can be used to bias external analog circuits, as long as they are not drawing current from CM (for example, the noninverting input of an op amp).                                                                        |

| 8       | AVDD          | PWR               | 1.8 V to 3.65 V Analog Supply for DAC and Microphone Bias. This pin should be decoupled locally to AGND with a 100 nF capacitor.                                                                                                                                                                                                                                                                                        |

| 9       | AGND          | PWR               | Analog Ground. The AGND and DGND pins can be tied together on a common ground plane.  AGND should be decoupled locally to AVDD with a 100 nF capacitor.                                                                                                                                                                                                                                                                 |

| 10      | LINP          | A_IN              | Left Channel Noninverting Input or Single-Ended Input 0. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                              |

| 11      | LINN          | A_IN              | Left Channel Inverting Input or Single-Ended Input 1. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                 |

| 12      | RINP          | A_IN              | Right Channel Noninverting Input or Single-Ended Input 2. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                             |

| 13      | RINN          | A_IN              | Right Channel Inverting Input or Single-Ended Input 3. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                |

| 14      | RAUX          | A_IN              | Right Channel Single-Ended Auxiliary Input. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                           |

| 15      | ROUTP         | A_OUT             | Right Line Output, Positive. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                                          |

| 16      | ROUTN         | A_OUT             | Right Line Output, Negative. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                                          |

| 17      | LOUTN         | A_OUT             | Left Line Output, Negative. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                                           |

| 18      | LOUTP         | A_OUT             | Left Line Output, Positive. Biased at AVDD/2.                                                                                                                                                                                                                                                                                                                                                                           |

| Pin No.  | Mnemonic    | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                            |

|----------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19       | RHP         | A_OUT             | Right Headphone Output. Biased at AVDD/2.                                                                                                                                                                                                                                                              |

| 20       | LHP         | A_OUT             | Left Headphone Output. Biased at AVDD/2.                                                                                                                                                                                                                                                               |

| 21       | MONOOUT     | A_OUT             | Mono Output or Virtual Ground for Capless Headphone. Biased at AVDD/2 when set as mono output.                                                                                                                                                                                                         |

| 22       | AGND        | PWR               | Analog Ground. The AGND and DGND pins can be tied together on a common ground plane.  AGND should be decoupled locally to AVDD with a 100 nF capacitor.                                                                                                                                                |

| 23       | AVDD        | PWR               | 1.8 V to 3.3 V Analog Supply for ADC, Output Driver, and Input to Digital Supply Regulator. This pin should be decoupled locally to AGND with a 100 nF capacitor.                                                                                                                                      |

| 24       | DVDDOUT     | PWR               | Digital Core Supply Decoupling Point. The digital supply is generated from an on-board regulator and does not require an external supply. DVDDOUT should be decoupled to DGND with a 100 nF capacitor and a 10 $\mu$ F capacitor.                                                                      |

| 25       | DGND        | PWR               | Digital Ground. The AGND and DGND pins can be tied together on a common ground plane. DGND should be decoupled to DVDDOUT and to IOVDD with 100 nF capacitors and 10 µF capacitors.                                                                                                                    |

| 26       | ADC_SDATA   | D_OUT             | ADC Serial Output Data.                                                                                                                                                                                                                                                                                |

| 27       | DAC_SDATA   | D_IN              | DAC Serial Input Data.                                                                                                                                                                                                                                                                                 |

| 28       | BCLK        | D_IO              | Serial Data Port Bit Clock.                                                                                                                                                                                                                                                                            |

| 26<br>29 | LRCLK       | D_IO              | Serial Data Port Fit Clock.  Serial Data Port Frame Clock.                                                                                                                                                                                                                                             |

|          | _           | _                 |                                                                                                                                                                                                                                                                                                        |

| 30       | ADDR1/CDATA | D_IN              | I <sup>2</sup> C Address Bit 1 (ADDR1).  SPI Data Input (CDATA).                                                                                                                                                                                                                                       |

| 31       | SDA/COUT    | D_IO              | I <sup>2</sup> C Data (SDA). This pin is a bidirectional open-collector input/output. The line connected to this pin should have a 2 kΩ pull-up resistor.  SPI Data Output (COUT). This pin is used for reading back registers and memory locations. It is three-state when an SPI read is not active. |

| 32       | SCL/CCLK    | D_IN              | $I^2C$ Clock (SCL). This pin is always an open-collector input when in $I^2C$ control mode. The line connected to this pin should have a 2 k $\Omega$ pull-up resistor.  SPI Clock (CCLK). This pin can run continuously or be gated off between SPI transactions.                                     |

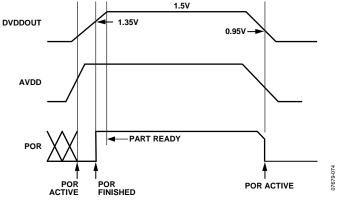

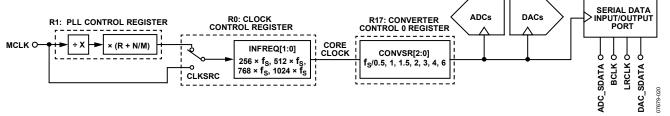

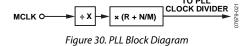

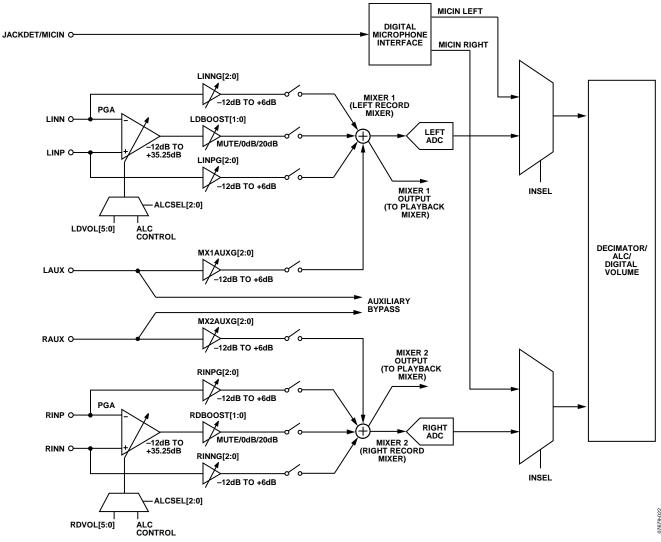

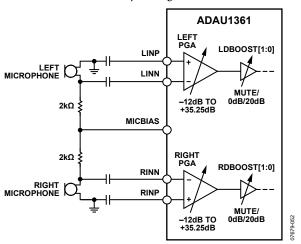

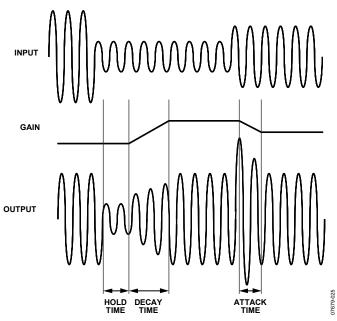

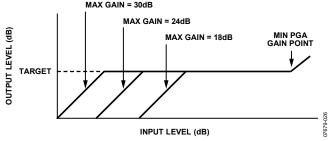

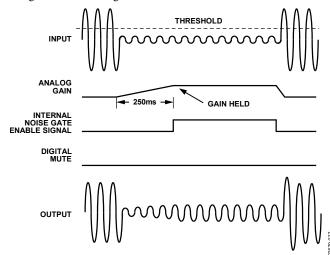

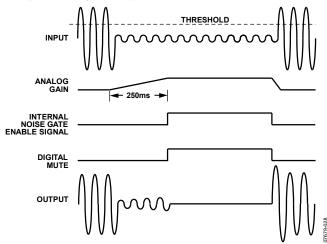

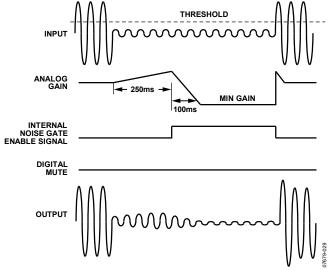

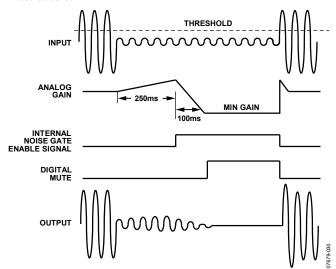

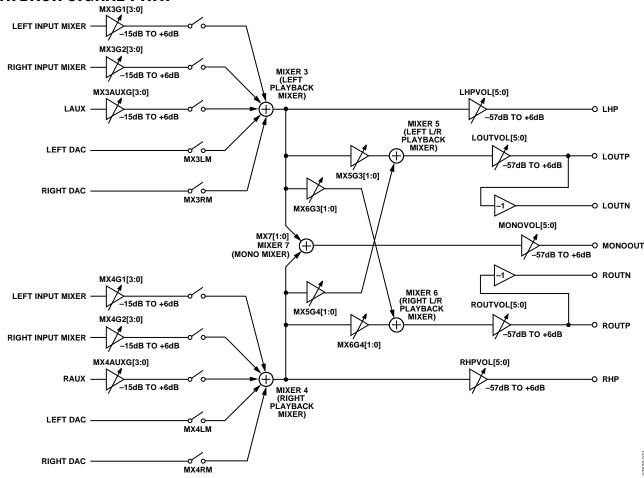

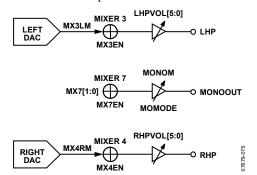

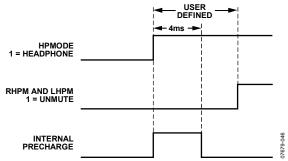

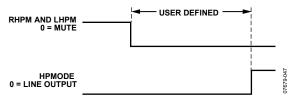

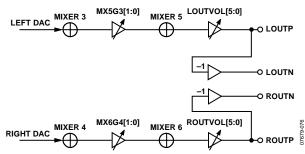

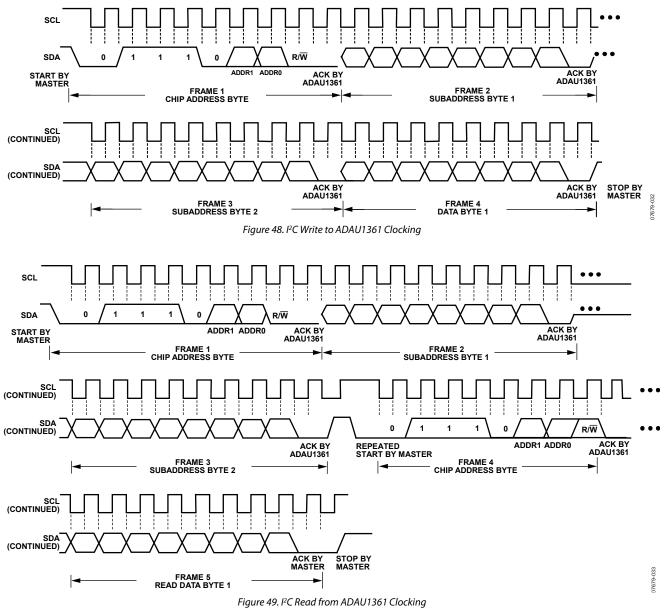

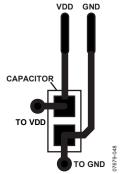

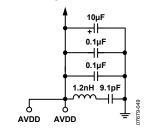

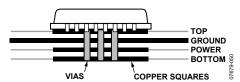

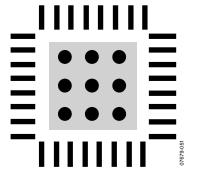

| EP       | Exposed Pad |                   | Exposed Pad. The exposed pad is connected internally to the ADAU1361 grounds. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the ground plane. See the Exposed Pad PCB Design section for more information.              |