# MC9S12VR-Family Reference Manual

# S12 Microcontrollers

MC9S12VRRMV2

Rev. 2.8

October 2, 2012

freescale.com

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://freescale.com/

A full list of family members and options is included in the appendices.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the CPU. For CPU information please refer to CPU12-1 in the CPU12 & CPU12X Reference Manual.

Table 0-1. Revision History

| Date             | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27-June-2011     | Rev 2.3           | Corrected ADC conditional text settings, ADC resolution is 10 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 29-July-2011     | Rev 2.4           | Corrected ETRIG0/ETRIG1 in pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 06-February-2012 | Rev 2.5           | <ul> <li>Corrected register name in register summary page 585 address 0x024F</li> <li>Corrected PartID</li> <li>Added Maskset 2N05E</li> <li>Updated electricals: Num 5 &amp; 6 Table I-2, Num 2 Table D-2, Num 2 Table J-1, Table A-12, A-13 &amp; A-14, Num 13 &amp; 14 Table A-8, Table A-4</li> </ul>                                                                                                                                                                                                                                        |

| 09-February-2012 | Rev 2.6           | Added HVI[3:0] to Table A-4 Num 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15-May-2012      | Rev 2.7           | <ul> <li>Correced NVM timing parameter</li> <li>Updated stop current values</li> <li>Added 1.16 ADC Result Reference</li> <li>Added Bandgap Spec Table B-1 Num 15 &amp; 16</li> <li>Added Order Info Appendix</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| 02-October-2012  | Rev 2.8           | <ul> <li>Minor Corrections</li> <li>Corrected Table B-1 Num 8 ACLK frequency is typ 20KHz</li> <li>Added Max value to Table A-13 Num 5</li> <li>Table M-1New NVM timing parameters</li> <li>Added Section C.3.2, "ATD Analog Input Parasitics</li> <li>See Section Chapter 2, "Port Integration Module (S12VRPIMV2) Revision History</li> <li>See Section Chapter 4, "S12 Clock, Reset and Power Management Unit (S12CPMU_UHV) Revision History</li> <li>Added Table B-2</li> <li>Changed Num 2 in Table H-2 inductive load max 450mH</li> </ul> |

| Chapter    | Device Overview MC9512Vn-Faililly                  |

|------------|----------------------------------------------------|

| Chapter 2  | Port Integration Module (S12VRPIMV2)               |

| Chapter 3  | S12G Memory Map Controller (S12GMMCV1)             |

| Chapter 4  | Clock, Reset and Power Management (S12CPMU_UHV)119 |

| Chapter 5  | Background Debug Module (S12SBDMV1)175             |

| Chapter 6  | S12S Debug Module (S12SDBGV2)199                   |

| Chapter 7  | Interrupt Module (S12SINTV1)243                    |

| Chapter 8  | Analog-to-Digital Converter (ADC12B6CV2)251        |

| Chapter 9  | Pulse-Width Modulator (S12PWM8B8CV2)277            |

| Chapter 10 | Serial Communication Interface (S12SCIV5)307       |

| Chapter 11 | Serial Peripheral Interface (S12SPIV5)345          |

| Chapter 12 | Timer Module (TIM16B8CV3)371                       |

| Chapter 13 | High-Side Drivers - HSDRV (S12HSDRV1)399           |

| Chapter 14 | Low-Side Drivers - LSDRV (S12LSDRV1)411            |

| Chapter 15 | LIN Physical Layer (S12LINPHYV1)425                |

| Chapter 16 | Supply Voltage Sensor - (BATSV2)443                |

| Chapter 17 | 64 KByte Flash Module (S12FTMRG64K512V1)457        |

| Appendix A | MCU Electrical Specifications509                   |

| Appendix B | VREG Electrical Specifications523                  |

| Appendix C | ATD Electrical Specifications525                   |

| Appendix D | HSDRV Electrical Specifications531                 |

| Appendix E | PLL Electrical Specifications533                   |

| Appendix F | IRC Electrical Specifications535                   |

| Appendix G | LINPHY Electrical Specifications537                |

| Appendix H | LSDRV Electrical Specifications541                 |

| Appendix I | BATS Electrical Specifications                     |

| Appendix J | PIM Electrical Specifications547                   |

| Appendix K | SPI Electrical Specifications                      |

| Appendix L | XOSCLCP Electrical Specifications | .555 |

|------------|-----------------------------------|------|

| Appendix M | FTMRG Electrical Specifications   | .557 |

| Appendix N | Package Information               | .565 |

| Appendix O | Detailed Register Address Map     | .571 |

# Chapter 1 Device Overview MC9S12VR-Family

| 1.1  | Introduction                                       | . 21 |

|------|----------------------------------------------------|------|

| 1.2  | Features                                           | . 22 |

|      | 1.2.1 MC9S12VR-Family Member Comparison            |      |

| 1.3  | Chip-Level Features                                |      |

| 1.4  | Module Features                                    | . 24 |

|      | 1.4.1 HCS12 16-Bit Central Processor Unit (CPU)    | . 24 |

|      | 1.4.2 On-Chip Flash with ECC                       |      |

|      | 1.4.3 On-Chip SRAM                                 |      |

|      | 1.4.4 Main External Oscillator (XOSCLCP)           |      |

|      | 1.4.5 Internal RC Oscillator (IRC)                 |      |

|      | 1.4.6 Internal Phase-Locked Loop (IPLL)            |      |

|      | 1.4.7 Clock and Power Management Unit (CPMU)       |      |

|      | 1.4.8 System Integrity Support                     |      |

|      | 1.4.9 Timer (TIM)                                  |      |

|      | 1.4.10 Pulse Width Modulation Module (PWM)         |      |

|      | 1.4.11 LIN physical layer transceiver (LINPHY)     |      |

|      | 1.4.12 Serial Peripheral Interface Module (SPI)    |      |

|      | 1.4.13 Serial Communication Interface Module (SCI) |      |

|      | 1.4.14 Analog-to-Digital Converter Module (ATD)    |      |

|      | 1.4.15 Supply Voltage Sense (BATS)                 |      |

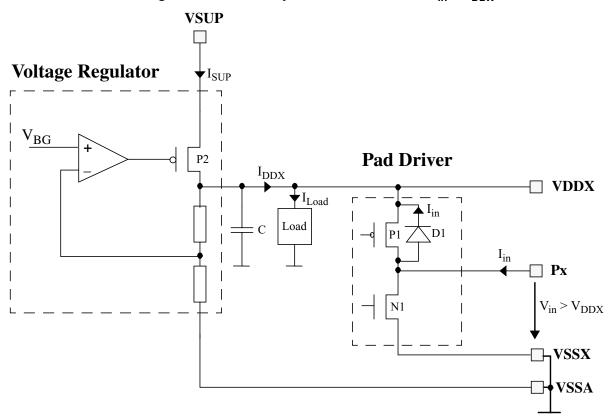

|      | 1.4.16 On-Chip Voltage Regulator system (VREG)     |      |

|      | 1.4.17 Low-side drivers (LSDRV)                    |      |

|      | 1.4.18 High-side drivers (HSDRV)                   |      |

|      | 1.4.19 Background Debug (BDM)                      |      |

|      | 1.4.20 Debugger (DBG)                              |      |

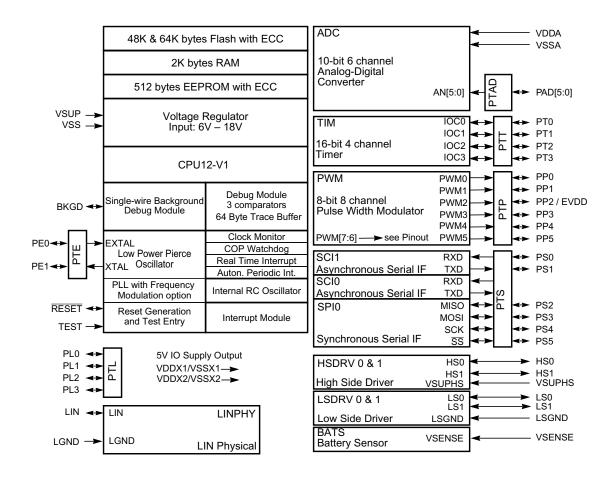

| 1.5  | Block Diagram                                      |      |

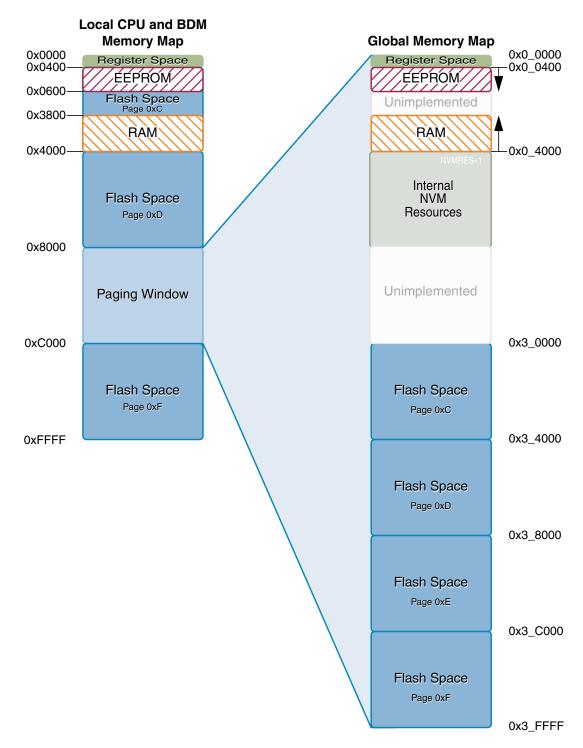

| 1.6  | Family Memory Map                                  |      |

|      | 1.6.1 Part ID Assignments                          |      |

| 1.7  | Signal Description and Device Pinouts              |      |

|      | 1.7.1 Pin Assignment Overview                      |      |

|      | 1.7.2 Detailed Signal Descriptions                 |      |

|      | 1.7.3 Power Supply Pins                            |      |

| 1.8  | Device Pinouts                                     |      |

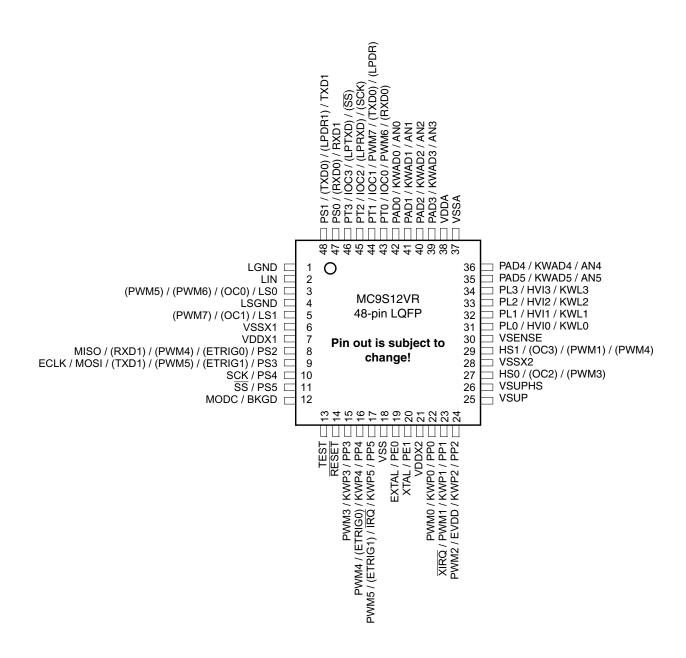

|      | 1.8.1 Pinout 48-pin LQFP                           |      |

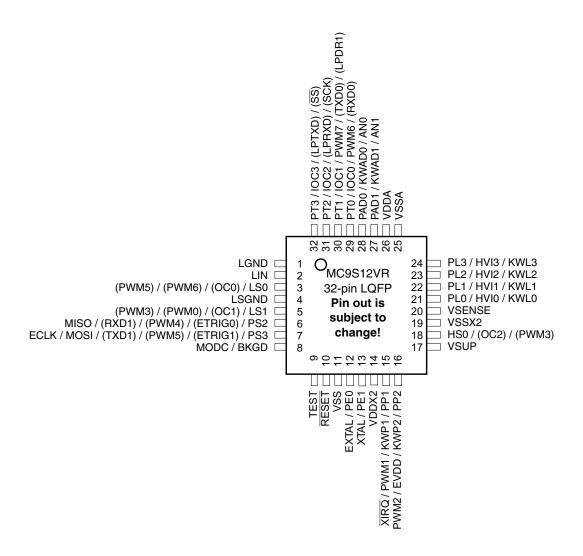

|      | 1.8.2 Pinout 32-pin LQFP                           |      |

| 1.9  | Modes of Operation                                 |      |

|      | 1.9.1 Chip Configuration Summary                   |      |

|      | 1.9.2 Low Power Operation                          |      |

| 1.10 | Security                                           |      |

|      | Resets and Interrupts                              |      |

| 1,11 | 1.11.1 Resets                                      |      |

|      | 1.11.2 Interrupt Vectors                           |      |

|      | 1.11.3 Effects of Reset                            |      |

|      | THE LIEU OF ROOM                                   | . 10 |

|      |                                                    |      |

|      | API external clock output (API_EXTCLK)              |      |

|------|-----------------------------------------------------|------|

|      | COP Configuration                                   |      |

|      | ADC External Trigger Input Connection               |      |

| 1.15 | ADC Special Conversion Channels                     | . 48 |

|      |                                                     |      |

|      | Chapter 2                                           |      |

|      | Port Integration Module (S12VRPIMV2)                |      |

| 2.1  | Introduction                                        | . 49 |

|      | 2.1.1 Overview                                      | . 49 |

|      | 2.1.2 Features                                      | . 50 |

| 2.2  | External Signal Description                         | . 51 |

| 2.3  | Memory Map and Register Definition                  | . 53 |

|      | 2.3.1 Register Map                                  |      |

|      | 2.3.2 Register Descriptions                         |      |

|      | 2.3.3 Port E Data Register (PORTE)                  |      |

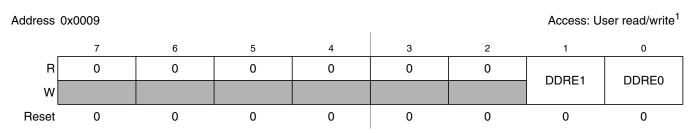

|      | 2.3.4 Port E Data Direction Register (DDRE)         |      |

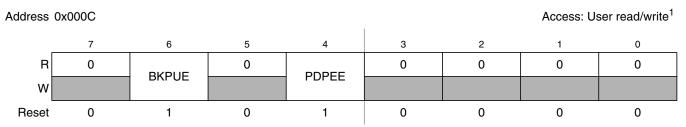

|      | 2.3.5 Port E, BKGD pin Pull Control Register (PUCR) |      |

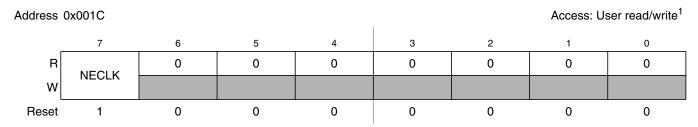

|      | 2.3.6 ECLK Control Register (ECLKCTL)               |      |

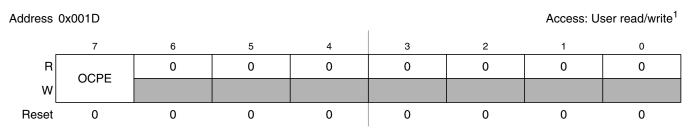

|      | 2.3.7 PIM Miscellaneous Register (PIMMISC)          |      |

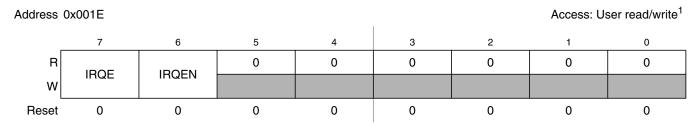

|      | 2.3.8 IRQ Control Register (IRQCR)                  |      |

|      | 2.3.9 Reserved Register                             |      |

|      | 2.3.10 Port T Data Register (PTT)                   |      |

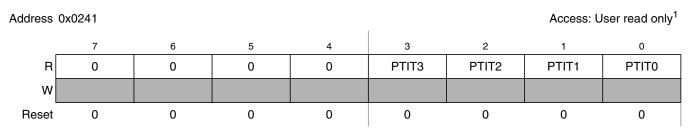

|      | 2.3.11 Port T Input Register (PTIT)                 |      |

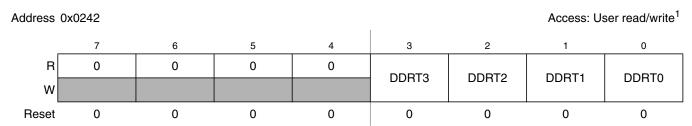

|      | 2.3.12 Port T Data Direction Register (DDRT)        |      |

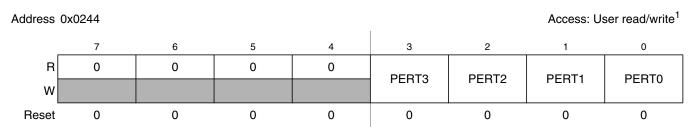

|      | 2.3.13 Port T Pull Device Enable Register (PERT)    |      |

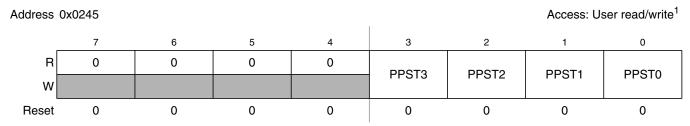

|      | 2.3.14 Port T Polarity Select Register (PPST)       |      |

|      | 2.3.15 Module Routing Register 0 (MODRR0)           |      |

|      | 2.3.16 Module Routing Register 1 (MODRR1)           |      |

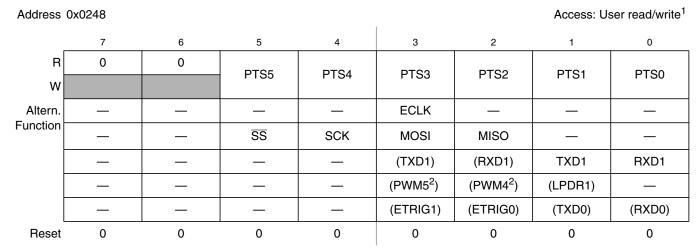

|      | 2.3.17 Port S Data Register (PTS)                   | . 68 |

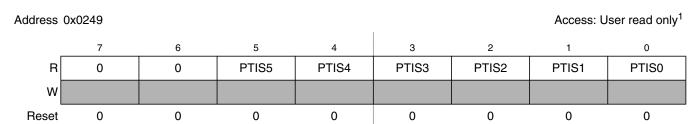

|      | 2.3.18 Port S Input Register (PTIS)                 | . 70 |

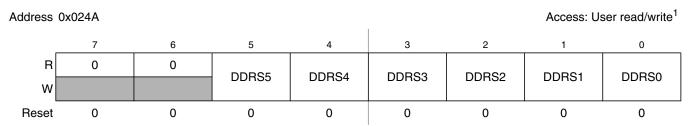

|      | 2.3.19 Port S Data Direction Register (DDRS)        |      |

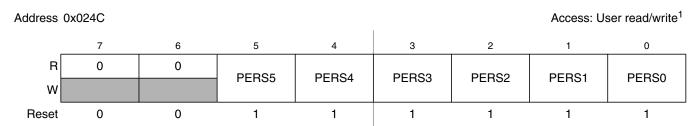

|      | 2.3.20 Port S Pull Device Enable Register (PERS)    | . 72 |

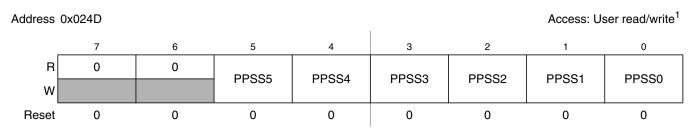

|      | 2.3.21 Port S Polarity Select Register (PPSS)       | . 73 |

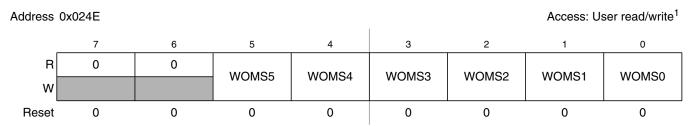

|      | 2.3.22 Port S Wired-Or Mode Register (WOMS)         | . 73 |

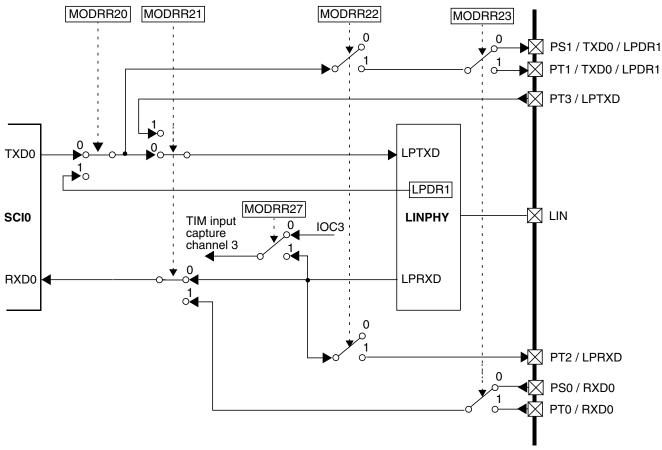

|      | 2.3.23 Module Routing Register 2 (MODRR2)           | . 74 |

|      | 2.3.24 Port P Data Register (PTP)                   | . 76 |

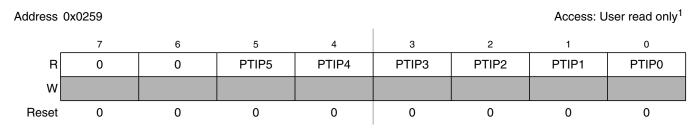

|      | 2.3.25 Port P Input Register (PTIP)                 |      |

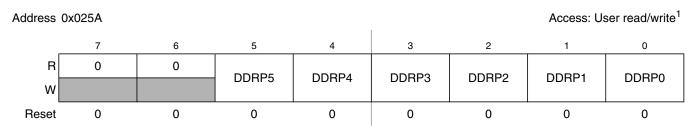

|      | 2.3.26 Port P Data Direction Register (DDRP)        | . 79 |

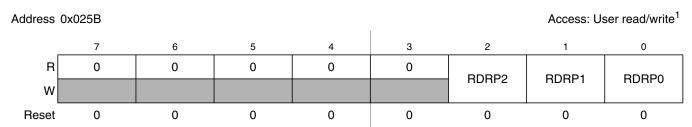

|      | 2.3.27 Port P Reduced Drive Register (RDRP)         | . 80 |

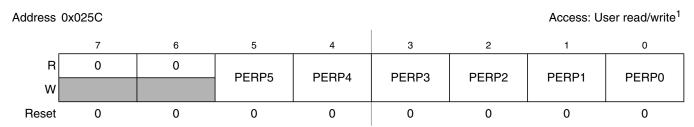

|      | 2.3.28 Port P Pull Device Enable Register (PERP)    | . 80 |

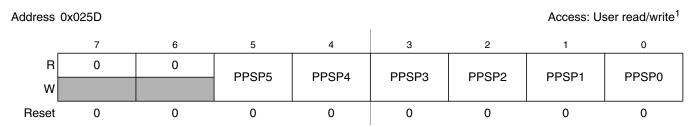

|      | 2.3.29 Port P Polarity Select Register (PPSP)       | . 81 |

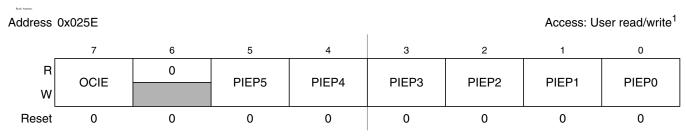

|      | 2.3.30 Port P Interrupt Enable Register (PIEP)      |      |

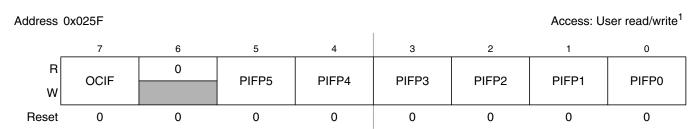

|      | 2.3.31 Port P Interrupt Flag Register (PIFP)        |      |

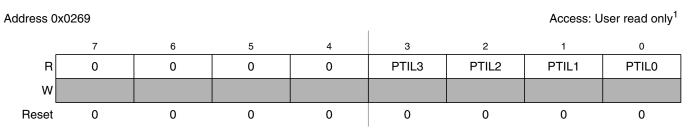

|      | 2.3.32 Port L Input Register (PTIL)                 |      |

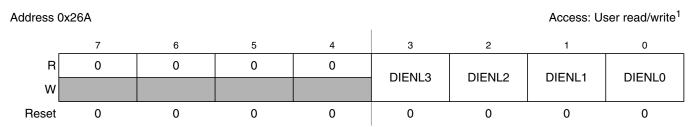

|      | 2.3.33 Port L Digital Input Enable Register (DIENL) |      |

|      |                                                     |      |

|     | 2.3.34    | Port L Analog Access Register (PTAL)                 | 84  |

|-----|-----------|------------------------------------------------------|-----|

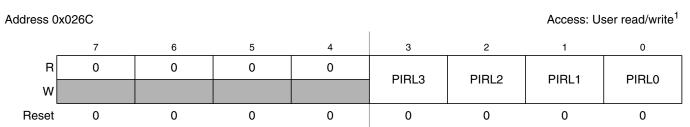

|     |           | Port L Input Divider Ratio Selection Register (PIRL) |     |

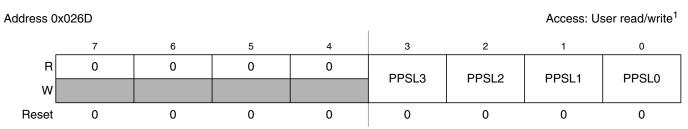

|     |           | Port L Polarity Select Register (PPSL)               |     |

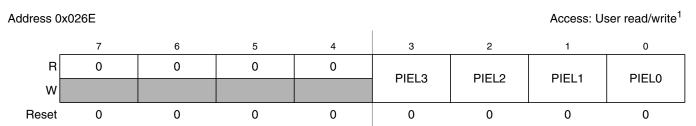

|     |           | Port L Interrupt Enable Register (PIEL)              |     |

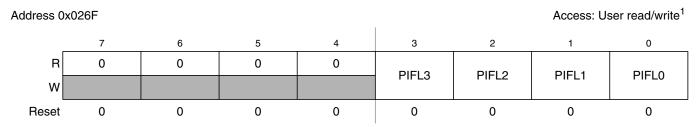

|     |           | Port L Interrupt Flag Register (PIFL)                |     |

|     |           | Port AD Data Register (PT1AD)                        |     |

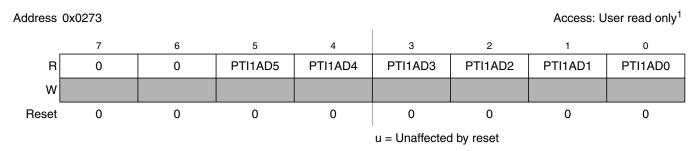

|     |           | Port AD Input Register (PTI1AD)                      |     |

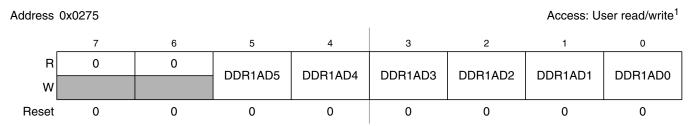

|     |           | Port AD Data Direction Register (DDR1AD)             |     |

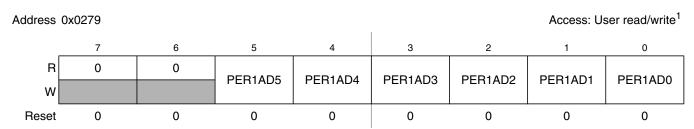

|     |           | Port AD Pull Enable Register (PER1AD)                |     |

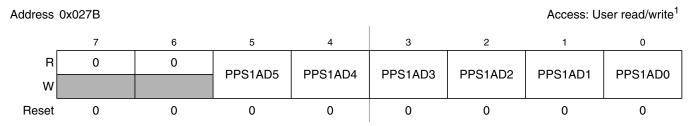

|     |           | Port AD Polarity Select Register (PPS1AD)            |     |

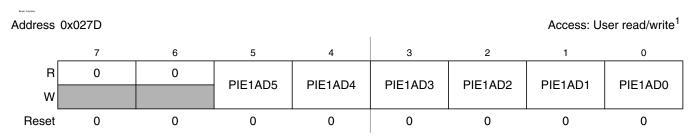

|     |           | Port AD Interrupt Enable Register (PIE1AD)           |     |

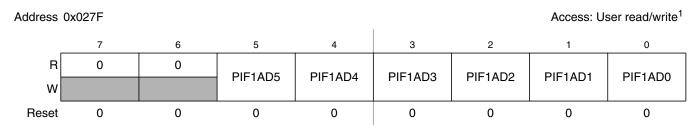

|     |           | Port AD Interrupt Flag Register (PIF1AD)             |     |

| 2.4 |           | nal Description                                      |     |

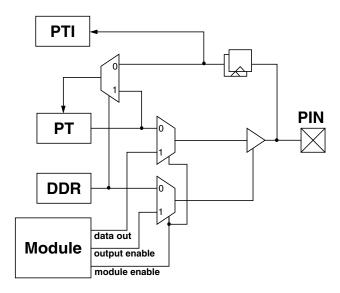

|     | 2.4.1     | General                                              | 92  |

|     | 2.4.2     | Registers                                            | 92  |

|     | 2.4.3     | Pins and Ports                                       | 94  |

|     | 2.4.4     | Interrupts                                           | 97  |

| 2.5 | Initializ | cation and Application Information                   | 99  |

|     | 2.5.1     | Port Data and Data Direction Register writes         | 99  |

|     | 2.5.2     | ADC External Triggers ETRIG1-0                       |     |

|     | 2.5.3     | Over-Current Protection on EVDD                      |     |

|     | 2.5.4     | Open Input Detection on HVI Pins                     | 100 |

|     |           | Chapter 3                                            |     |

|     |           | S12G Memory Map Controller (S12GMMCV1)               |     |

| 3.1 | Introdu   | ction                                                |     |

|     | 3.1.1     | Glossary                                             |     |

|     | 3.1.2     | Overview                                             |     |

|     | 3.1.3     | Features                                             |     |

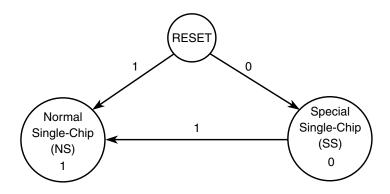

|     | 3.1.4     | Modes of Operation                                   |     |

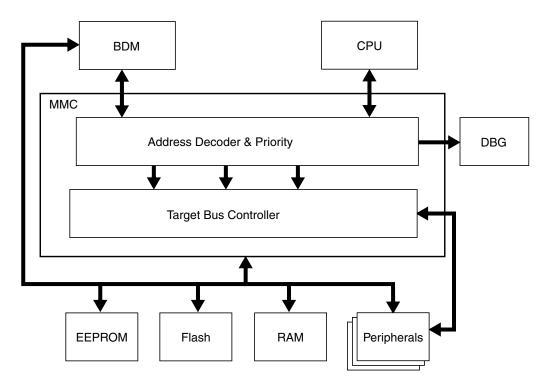

|     | 3.1.5     | Block Diagram                                        |     |

| 3.2 |           | d Signal Description                                 |     |

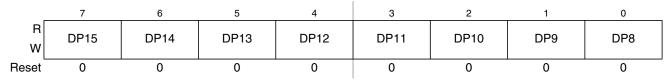

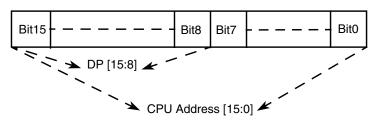

| 3.3 |           | y Map and Registers                                  |     |

|     | 3.3.1     | Module Memory Map                                    |     |

|     | 3.3.2     | Register Descriptions                                |     |

| 3.4 |           | nal Description                                      |     |

|     | 3.4.1     | MCU Operating Modes                                  |     |

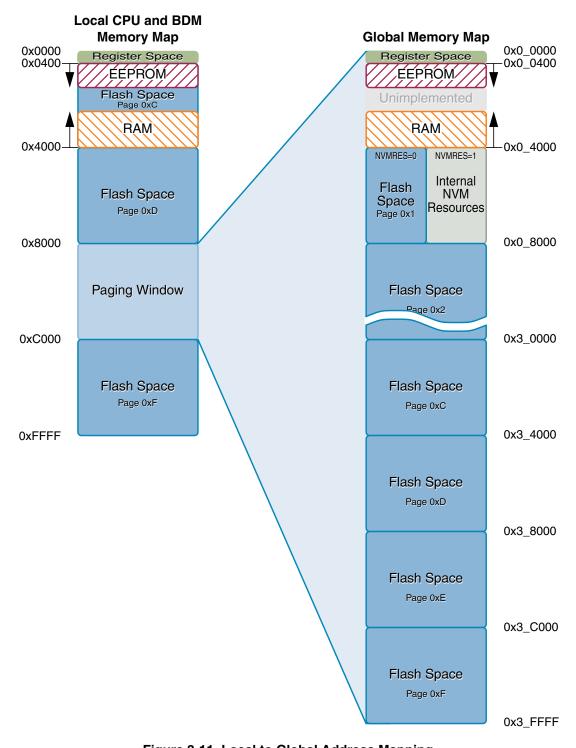

|     | 3.4.2     | Memory Map Scheme                                    |     |

|     | 3.4.3     | Unimplemented and Reserved Address Ranges            |     |

|     | 3.4.4     | Prioritization of Memory Accesses                    |     |

|     | 3.4.5     | Interrupts                                           | 117 |

# Chapter 4

|     | (         | Clock, Reset and Power Management (S12CPMU_UHVV1)  |       |

|-----|-----------|----------------------------------------------------|-------|

| 4.1 | Introdu   |                                                    | . 119 |

|     | 4.1.1     | Features                                           | . 119 |

|     | 4.1.2     | Modes of Operation                                 | . 121 |

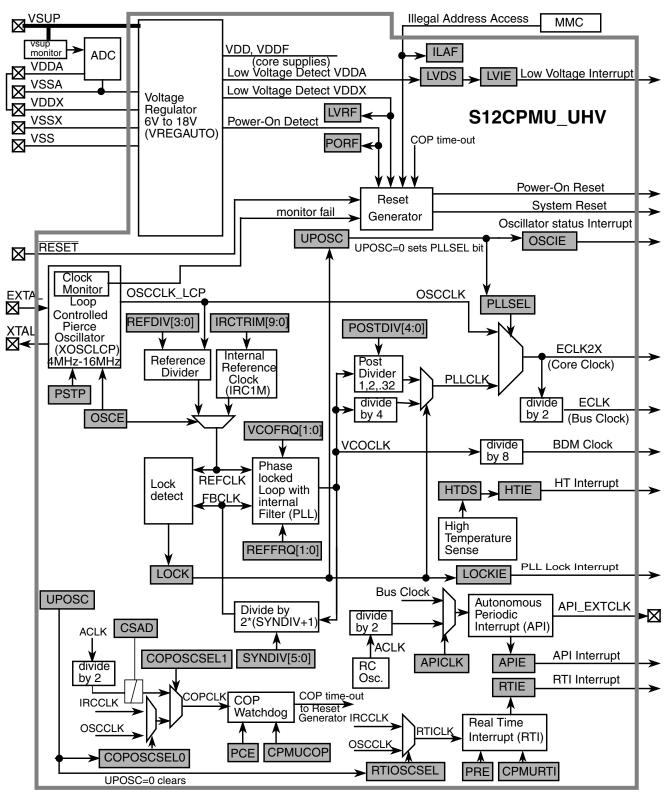

|     | 4.1.3     | S12CPMU_UHV Block Diagram                          | . 123 |

| 4.2 | Signal I  | Description                                        | . 125 |

|     | 4.2.1     | RESET                                              | . 125 |

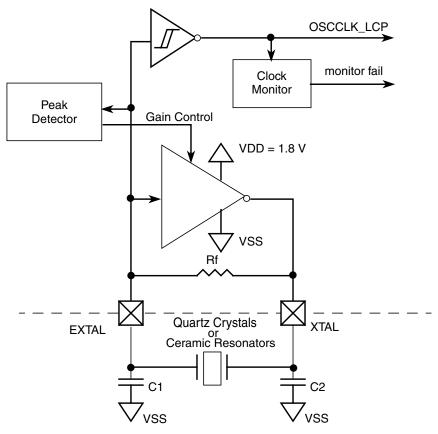

|     | 4.2.2     | EXTAL and XTAL                                     | . 125 |

|     | 4.2.3     | VSUP — Regulator Power Input Pin                   | . 125 |

|     | 4.2.4     | VDDA, VSSA — Regulator Reference Supply Pins       | . 125 |

|     | 4.2.5     | VDDX, VSSX— Pad Supply Pins                        |       |

|     | 4.2.6     | VSS, VSSC — Ground Pins                            | . 126 |

|     | 4.2.7     | API EXTCLK — API external clock output pin         | . 126 |

|     | 4.2.8     | VDD—Internal Regulator Output Supply (Core Logic)  |       |

|     | 4.2.9     | VDDF—Internal Regulator Output Supply (NVM Logic)  |       |

|     | 4.2.10    | 1 = = =                                            |       |

| 4.3 | Memor     | y Map and Registers                                | . 127 |

|     | 4.3.1     | Module Memory Map                                  | . 127 |

|     | 4.3.2     | Register Descriptions                              | . 129 |

| 4.4 | Functio   | nal Description                                    | . 162 |

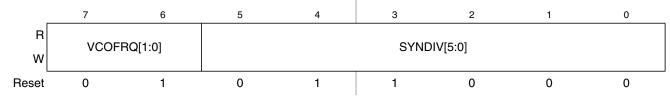

|     | 4.4.1     | Phase Locked Loop with Internal Filter (PLL)       | . 162 |

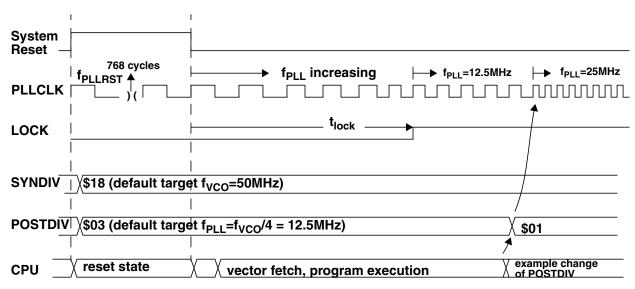

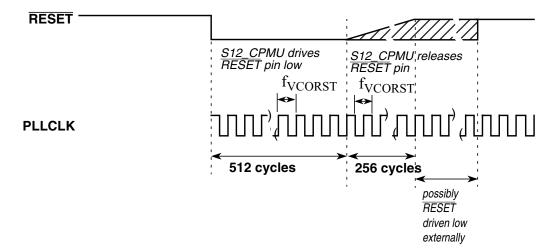

|     | 4.4.2     | Startup from Reset                                 |       |

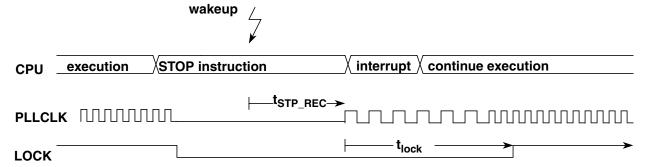

|     | 4.4.3     | Stop Mode using PLLCLK as Bus Clock                |       |

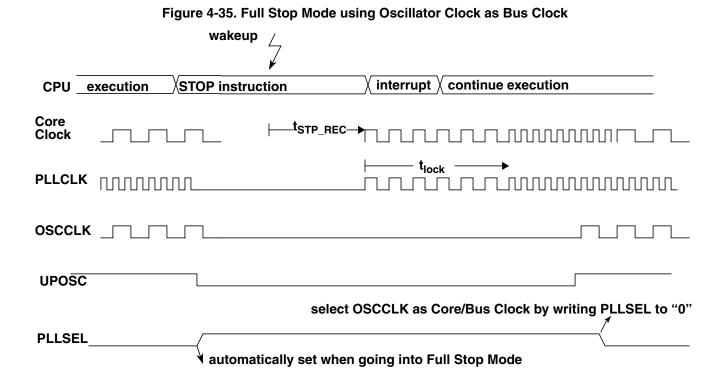

|     | 4.4.4     | Full Stop Mode using Oscillator Clock as Bus Clock | . 165 |

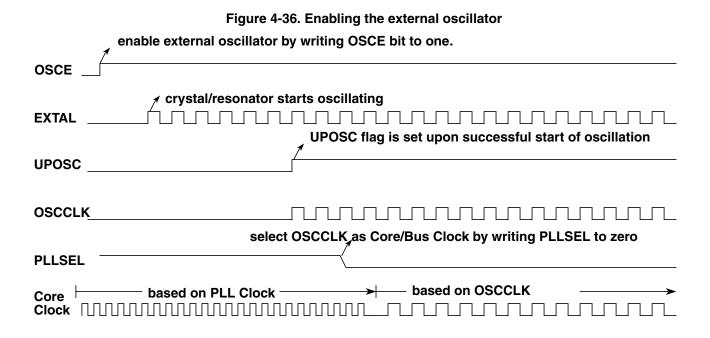

|     | 4.4.5     | External Oscillator                                |       |

|     | 4.4.6     | System Clock Configurations                        | . 16  |

| 4.5 | Resets    |                                                    | . 168 |

|     | 4.5.1     | General                                            | . 168 |

|     | 4.5.2     | Description of Reset Operation                     | . 168 |

|     | 4.5.3     | Power-On Reset (POR)                               | . 171 |

|     | 4.5.4     | Low-Voltage Reset (LVR)                            | . 171 |

| 4.6 | Interrup  | ots                                                | . 171 |

|     | 4.6.1     | Description of Interrupt Operation                 | . 171 |

| 4.7 | Initializ | ration/Application Information                     | . 173 |

|     | 4.7.1     | General Initialization information                 | . 173 |

|     | 4.7.2     | Application information for COP and API usage      | . 173 |

|     |           | Chapter 5                                          |       |

|     |           | Background Debug Module (S12SBDMV1)                |       |

| 5.1 |           | ction                                              |       |

|     | 5.1.1     | Features                                           |       |

|     | 5.1.2     | Modes of Operation                                 |       |

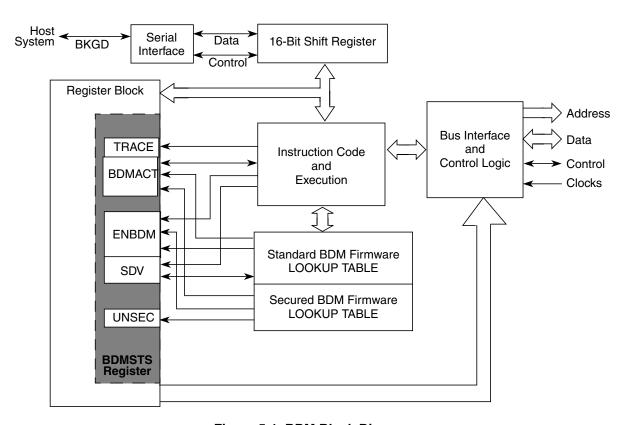

|     | 5.1.3     | Block Diagram                                      | . 177 |

MC9S12VR Family Reference Manual, Rev. 2.8

|     | LAterna        | l Signal Description                         | 1// |

|-----|----------------|----------------------------------------------|-----|

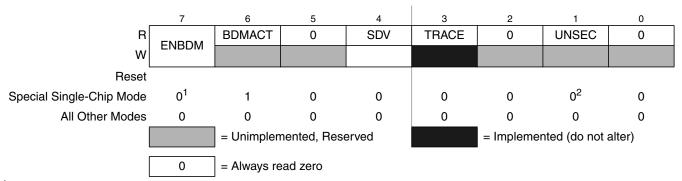

| 5.3 | Memory         | y Map and Register Definition                | 177 |

|     | 5.3.1          | Module Memory Map                            | 177 |

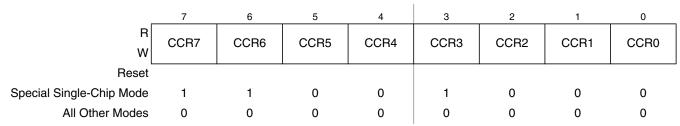

|     | 5.3.2          | Register Descriptions                        | 178 |

|     | 5.3.3          | Family ID Assignment                         | 182 |

| 5.4 | Function       | nal Description                              |     |

|     | 5.4.1          | Security                                     |     |

|     | 5.4.2          | Enabling and Activating BDM                  |     |

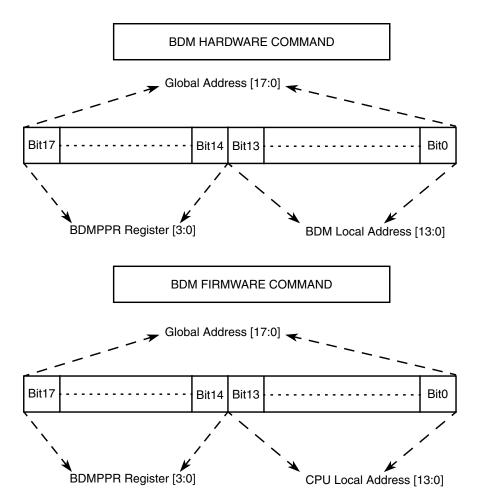

|     | 5.4.3          | BDM Hardware Commands                        |     |

|     | 5.4.4          | Standard BDM Firmware Commands               |     |

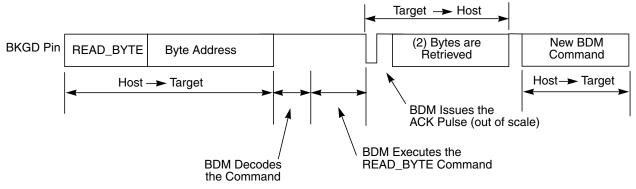

|     | 5.4.5          | BDM Command Structure                        |     |

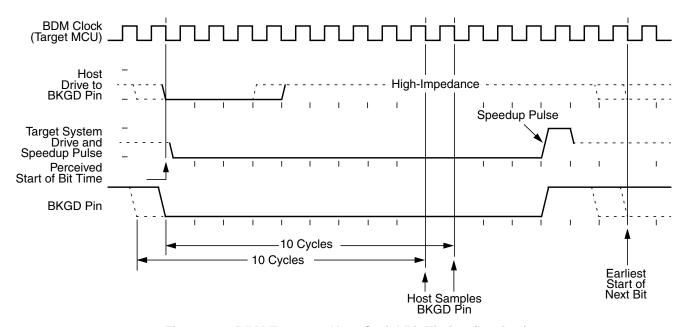

|     | 5.4.6          | BDM Serial Interface                         |     |

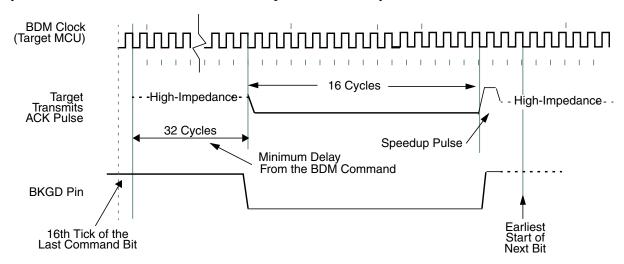

|     | 5.4.7          | Serial Interface Hardware Handshake Protocol |     |

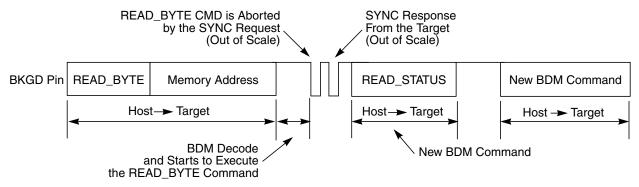

|     | 5.4.8          | Hardware Handshake Abort Procedure           |     |

|     | 5.4.9          | SYNC — Request Timed Reference Pulse         |     |

|     |                | Instruction Tracing                          |     |

|     | 5.4.11         | Serial Communication Time Out                | 196 |

|     |                |                                              |     |

|     |                | Chapter 6                                    |     |

|     |                | S12S Debug Module (S12SDBGV2)                |     |

| 6.1 | Introduc       | etion                                        | 199 |

| 0.1 | 6.1.1          | Glossary Of Terms                            |     |

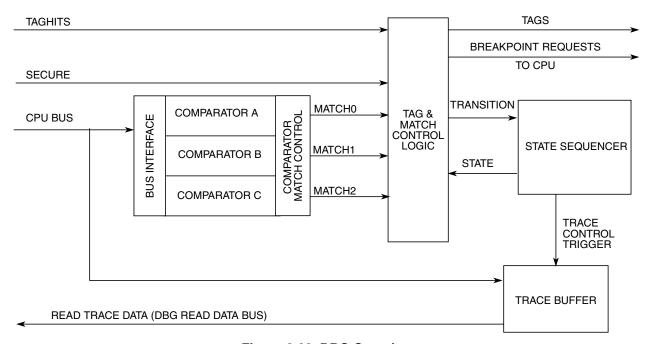

|     | 6.1.2          | Overview                                     |     |

|     | 6.1.3          | Features                                     |     |

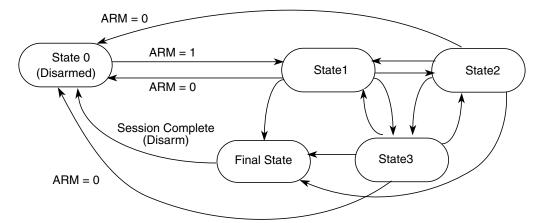

|     | 6.1.4          | Modes of Operation                           |     |

|     | 6.1.5          | Block Diagram                                |     |

| 6.2 | Externa        | l Signal Description                         |     |

| 6.3 |                | y Map and Registers                          |     |

|     | 6.3.1          | Module Memory Map                            |     |

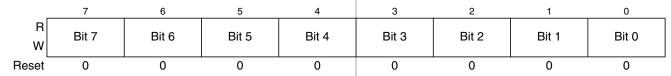

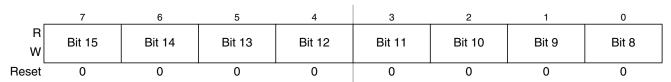

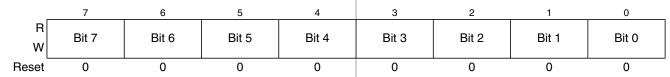

|     | 6.3.2          | Register Descriptions                        |     |

| 6.4 | Function       | nal Description                              |     |

|     |                | S12SDBG Operation                            |     |

|     | 6.4.2          | Comparator Modes                             |     |

|     | 6.4.3          | Match Modes (Forced or Tagged)               |     |

|     | 6.4.4          | State Sequence Control                       |     |

|     | 6.4.5          | Trace Buffer Operation                       |     |

|     | 6.4.6          | Tagging                                      |     |

|     | 6.4.7          | Breakpoints                                  |     |

| 6.5 | Applica        | tion Information                             |     |

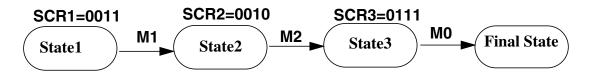

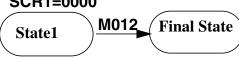

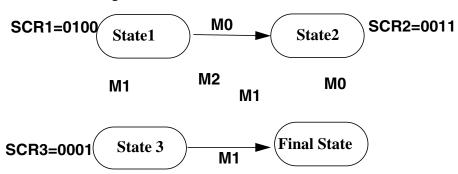

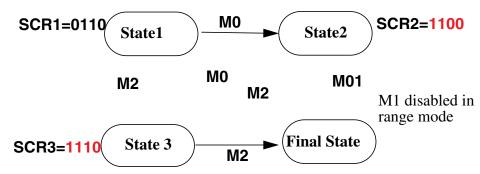

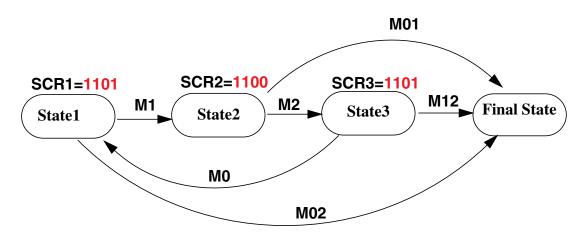

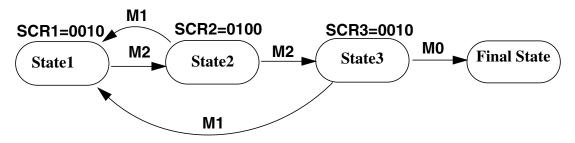

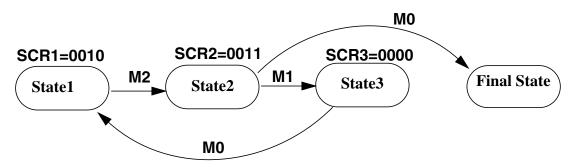

|     | 6.5.1          | State Machine scenarios                      | 236 |

|     | 6.5.2          | Scenario 1                                   | 236 |

|     | 6.5.3          | Scenario 2                                   |     |

|     | 6.5.4          | Scenario 3                                   |     |

|     |                |                                              |     |

|     | 6.5.5          | Scenario 4                                   | 237 |

|     | 6.5.5<br>6.5.6 | Scenario 4                                   |     |

|     | 6.5.7    | Scenario 6                               | 239 |

|-----|----------|------------------------------------------|-----|

|     | 6.5.8    | Scenario 7                               |     |

|     | 6.5.9    | Scenario 8                               | 240 |

|     | 6.5.10   | Scenario 9                               | 240 |

|     | 6.5.11   | Scenario 10                              | 240 |

|     |          | Chapter 7                                |     |

|     |          | Interrupt Module (S12SINTV1)             |     |

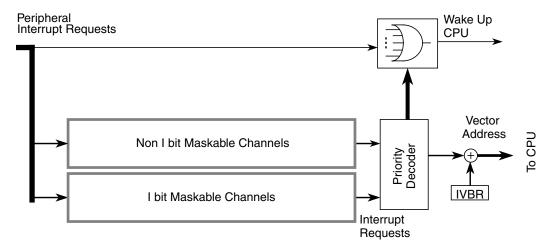

| 7.1 | Introduc | tion                                     | 243 |

|     | 7.1.1    | Glossary                                 | 243 |

|     | 7.1.2    | Features                                 | 243 |

|     | 7.1.3    | Modes of Operation                       | 244 |

|     | 7.1.4    | Block Diagram                            | 244 |

| 7.2 | External | Signal Description                       | 245 |

| 7.3 | Memory   | Map and Register Definition              | 245 |

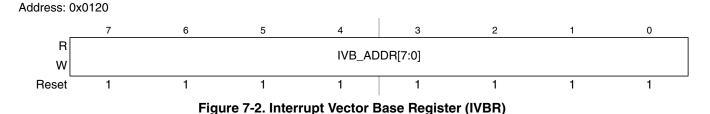

|     | 7.3.1    | Register Descriptions                    | 245 |

| 7.4 | Function | nal Description                          |     |

|     | 7.4.1    | S12S Exception Requests                  |     |

|     | 7.4.2    | Interrupt Prioritization                 |     |

|     | 7.4.3    | Reset Exception Requests                 |     |

|     | 7.4.4    | Exception Priority                       |     |

| 7.5 |          | ation/Application Information            |     |

|     | 7.5.1    | Initialization                           |     |

|     | 7.5.2    | Interrupt Nesting                        |     |

|     | 7.5.3    | Wake Up from Stop or Wait Mode           | 248 |

|     |          | Chapter 8                                |     |

|     |          | Analog-to-Digital Converter (ADC12B6CV2) |     |

| 8.1 | Introduc | Block Description                        | 251 |

| 0.1 | 8.1.1    | Features                                 |     |

|     |          | Modes of Operation                       |     |

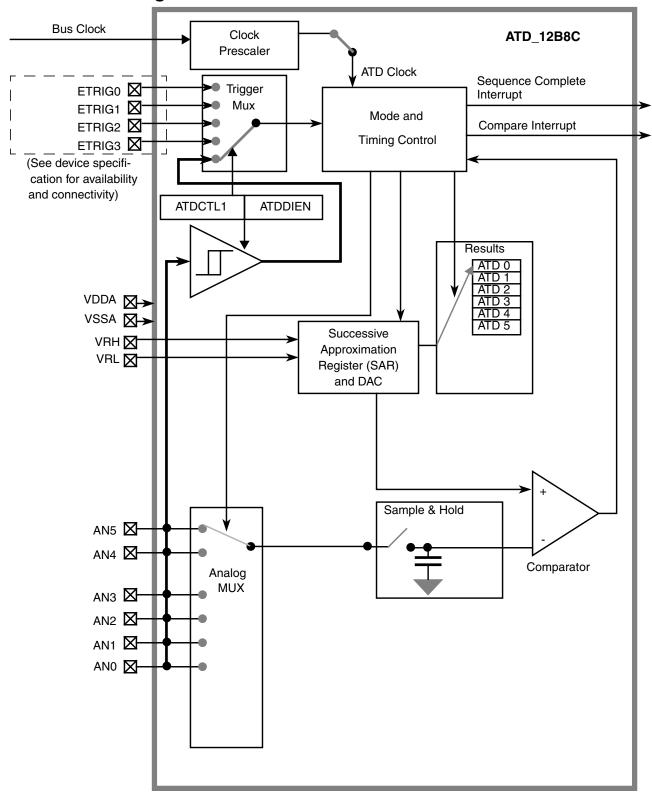

|     | 8.1.3    | Block Diagram                            |     |

| 8.2 |          | Description                              |     |

| 0.2 | 8.2.1    | Detailed Signal Descriptions             |     |

| 8.3 |          | Map and Register Definition              |     |

| 0.0 | 8.3.1    | Module Memory Map                        |     |

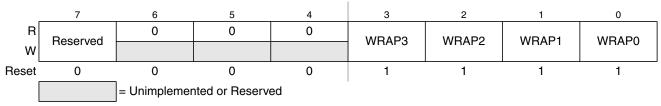

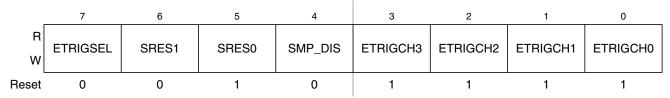

|     | 8.3.2    | Register Descriptions                    |     |

| 8.4 |          | nal Description                          |     |

|     | 8.4.1    | Analog Sub-Block                         |     |

|     | 8.4.2    | Digital Sub-Block                        |     |

| 8.5 | Resets . |                                          |     |

| 8.6 | Interrup | ts                                       | 275 |

|     | _        |                                          |     |

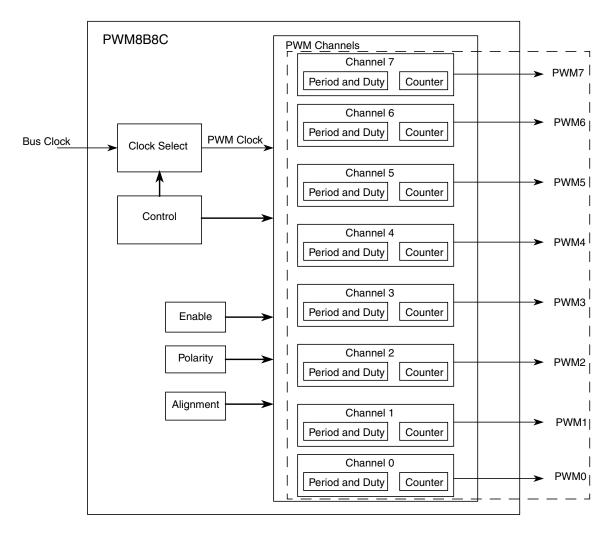

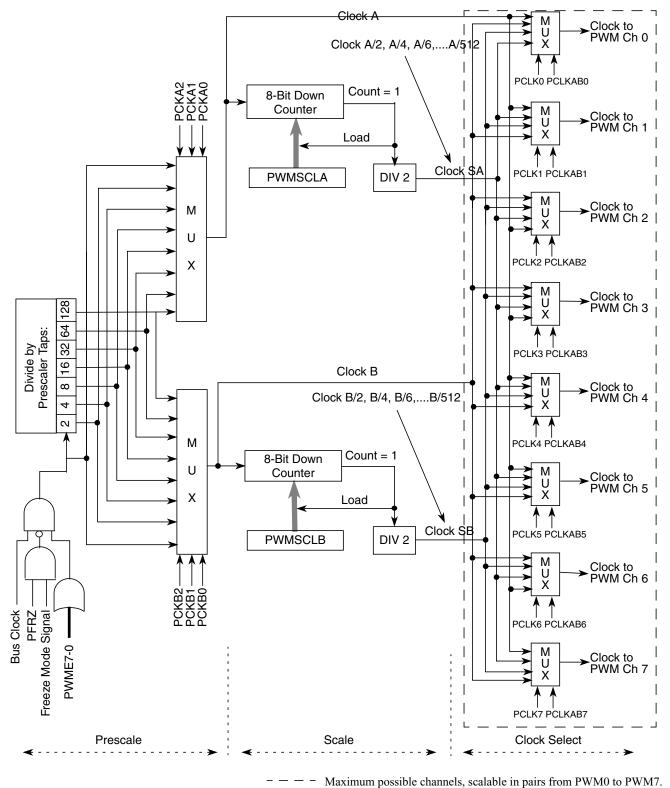

# Chapter 9 Pulse-Width Modulator (S12PWM8B8CV2)

| 9.1  | Introduction                                     | 277 |

|------|--------------------------------------------------|-----|

|      | 9.1.1 Features                                   |     |

|      | 9.1.2 Modes of Operation                         | 277 |

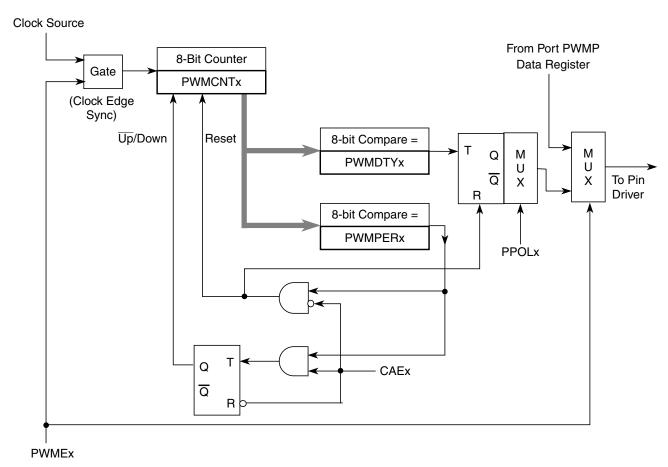

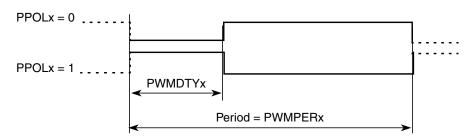

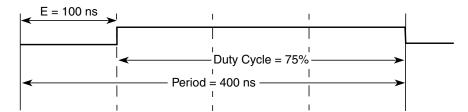

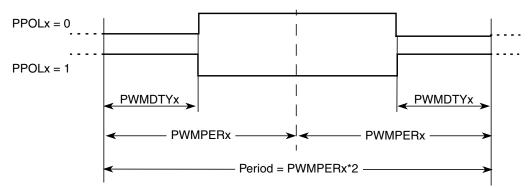

|      | 9.1.3 Block Diagram                              | 278 |

| 9.2  | External Signal Description                      |     |

|      | 9.2.1 PWM7 - PWM0 — PWM Channel 7 - 0            | 278 |

| 9.3  | Memory Map and Register Definition               | 279 |

|      | 9.3.1 Module Memory Map                          | 279 |

|      | 9.3.2 Register Descriptions                      | 279 |

| 9.4  | Functional Description                           |     |

|      | 9.4.1 PWM Clock Select                           |     |

|      | 9.4.2 PWM Channel Timers                         |     |

| 9.5  | Resets                                           |     |

| 9.6  | Interrupts                                       | 305 |

|      | Observatory 4.0                                  |     |

|      | Chapter 10                                       |     |

|      | Serial Communication Interface (S12SCIV5)        |     |

| 10.1 | Introduction                                     |     |

|      | 10.1.1 Glossary                                  |     |

|      | 10.1.2 Features                                  |     |

|      | 10.1.3 Modes of Operation                        |     |

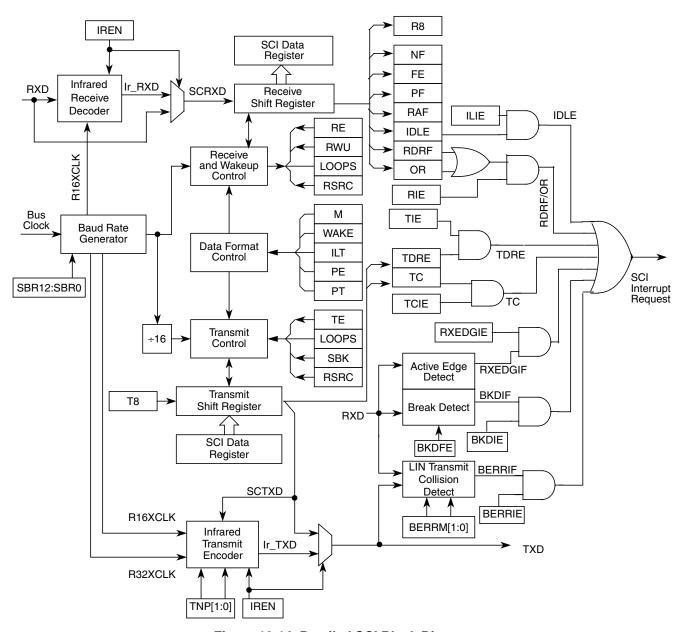

| 40.  | 10.1.4 Block Diagram                             |     |

| 10.2 | External Signal Description                      |     |

|      | 10.2.1 TXD — Transmit Pin                        |     |

| 10.2 | 10.2.2 RXD — Receive Pin                         |     |

| 10.3 | Memory Map and Register Definition               |     |

|      | 10.3.1 Module Memory Map and Register Definition |     |

| 10.4 | 10.3.2 Register Descriptions                     |     |

| 10.4 | Functional Description                           |     |

|      | 10.4.2 LIN Support                               |     |

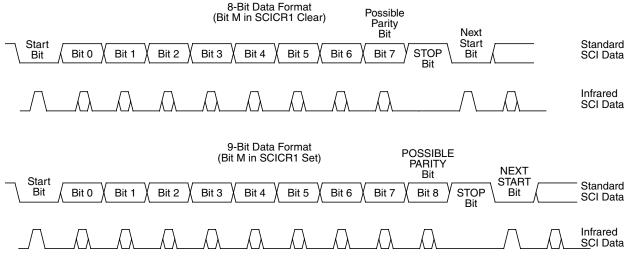

|      | 10.4.3 Data Format                               |     |

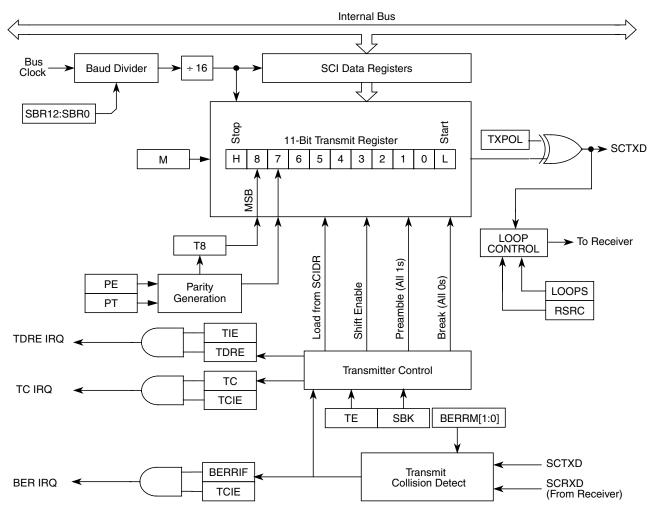

|      | 10.4.4 Baud Rate Generation                      |     |

|      | 10.4.5 Transmitter                               |     |

|      | 10.4.6 Receiver                                  |     |

|      | 10.4.7 Single-Wire Operation                     |     |

|      | 10.4.8 Loop Operation                            |     |

| 10.5 | Initialization/Application Information           |     |

|      | 10.5.1 Reset Initialization                      |     |

|      | 10.5.2 Modes of Operation                        |     |

|      | 10.5.3 Interrupt Operation                       |     |

|      | 10.5.4 Recovery from Wait Mode                   |     |

|      |                                                  |     |

|      | 10.5.5 Recovery from Stop Mode                                    | 344 |

|------|-------------------------------------------------------------------|-----|

|      | Chapter 11                                                        |     |

|      | Serial Peripheral Interface (S12SPIV5)                            |     |

| 11.1 | Introduction                                                      |     |

|      | 11.1.1 Glossary of Terms                                          |     |

|      | 11.1.2 Features                                                   |     |

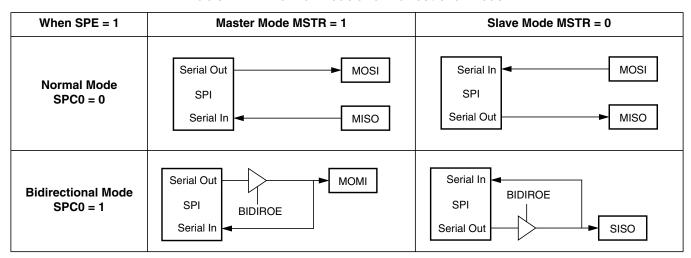

|      | 11.1.3 Modes of Operation                                         |     |

|      | 11.1.4 Block Diagram                                              |     |

| 11.2 | External Signal Description                                       |     |

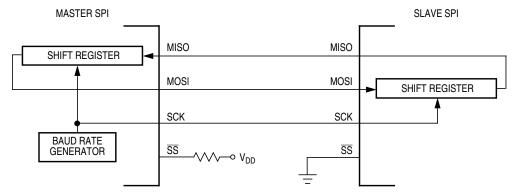

|      | 11.2.1 MOSI — Master Out/Slave In Pin                             |     |

|      | 11.2.2 MISO — Master In/Slave Out Pin                             |     |

|      | 11.2.3 $\overline{SS}$ — Slave Select Pin                         |     |

|      | 11.2.4 SCK — Serial Clock Pin                                     |     |

| 11.3 | Memory Map and Register Definition                                |     |

|      | 11.3.1 Module Memory Map                                          |     |

|      | 11.3.2 Register Descriptions                                      |     |

| 11.4 | Functional Description                                            |     |

|      | 11.4.1 Master Mode                                                |     |

|      | 11.4.2 Slave Mode                                                 |     |

|      | 11.4.3 Transmission Formats                                       |     |

|      | 11.4.4 SPI Baud Rate Generation                                   |     |

|      | 11.4.5 Special Features                                           |     |

|      | 11.4.6 Error Conditions                                           |     |

|      | 11.4.7 Low Power Mode Options                                     | 368 |

|      | Chapter 12                                                        |     |

|      | Timer Module (TIM16B8CV3)                                         |     |

| 12.1 | Introduction                                                      | 371 |

|      | 12.1.1 Features                                                   | 371 |

|      | 12.1.2 Modes of Operation                                         | 372 |

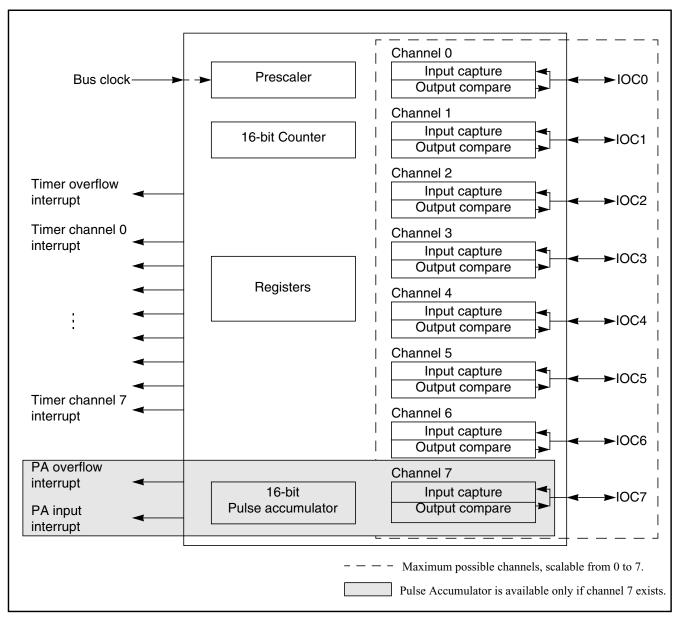

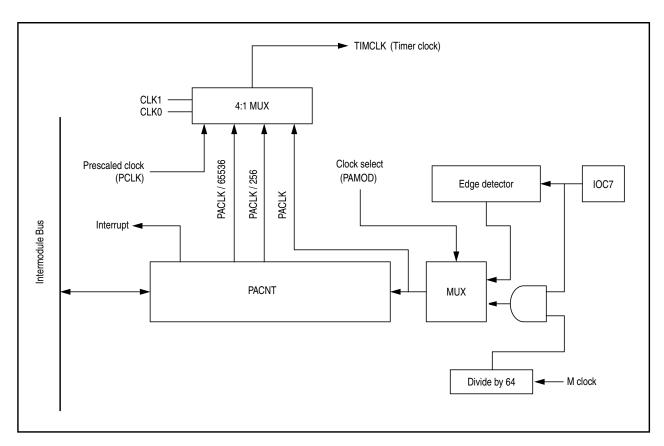

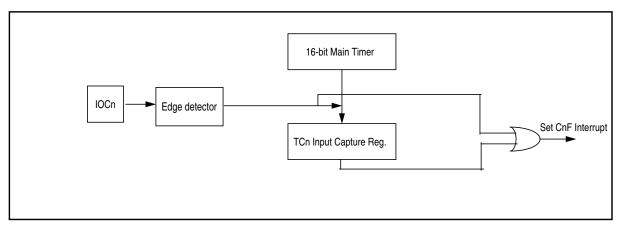

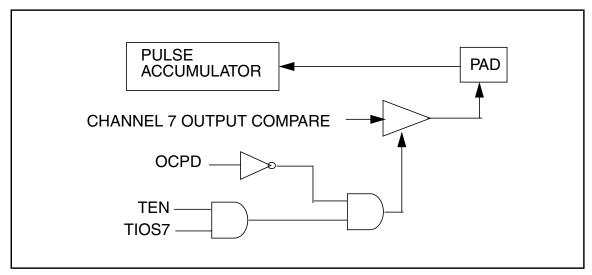

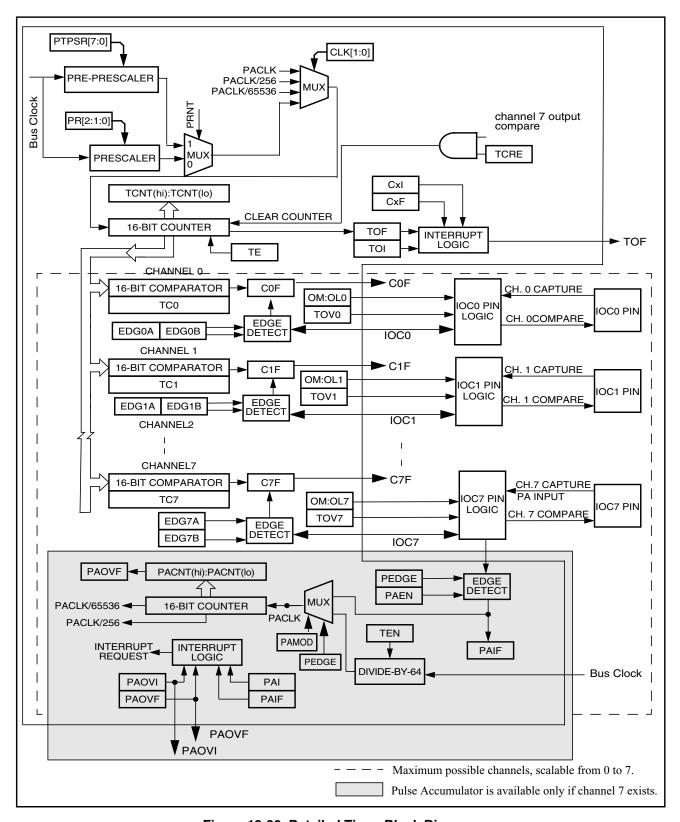

|      | 12.1.3 Block Diagrams                                             | 373 |

| 12.2 | External Signal Description                                       |     |

|      | 12.2.1 IOC7 — Input Capture and Output Compare Channel 7          | 375 |

|      | 12.2.2 IOC6 - IOC0 — Input Capture and Output Compare Channel 6-0 | 375 |

| 12.3 | Memory Map and Register Definition                                | 375 |

|      | 12.3.1 Module Memory Map                                          | 375 |

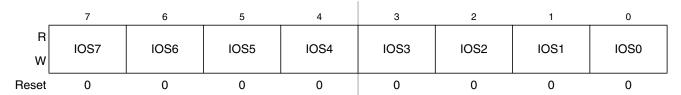

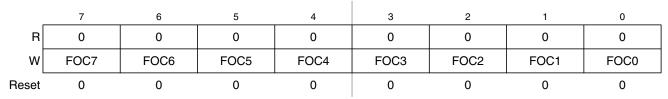

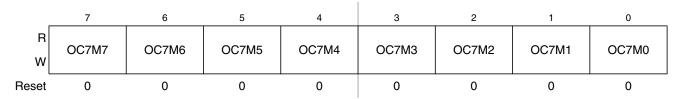

|      | 12.3.2 Register Descriptions                                      | 376 |

| 12.4 | Functional Description                                            | 393 |

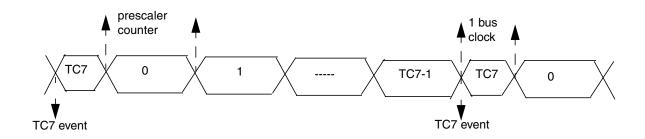

|      | 12.4.1 Prescaler                                                  | 395 |

|      | 12.4.2 Input Capture                                              | 395 |

|      | 12.4.3 Output Compare                                             |     |

|      | 12.4.4 Pulse Accumulator                                          |     |

|      | 12.4.5 Event Counter Mode                                         | 397 |

|      |                                                                   |     |

|      | 12.4.6 Gated Time Accumulation Mode                 | 397 |

|------|-----------------------------------------------------|-----|

| 12.5 | Resets                                              | 397 |

| 12.6 | Interrupts                                          | 397 |

|      | 12.6.1 Channel [7:0] Interrupt (C[7:0]F)            | 398 |

|      | 12.6.2 Pulse Accumulator Input Interrupt (PAOVI)    | 398 |

|      | 12.6.3 Pulse Accumulator Overflow Interrupt (PAOVF) | 398 |

|      | 12.6.4 Timer Overflow Interrupt (TOF)               | 398 |

|      |                                                     |     |

|      | Chapter 13                                          |     |

|      | High-Side Drivers - HSDRV (S12HSDRV1)               |     |

| 13.1 | Introduction                                        |     |

|      | 13.1.1 Features                                     |     |

|      | 13.1.2 Modes of Operation                           |     |

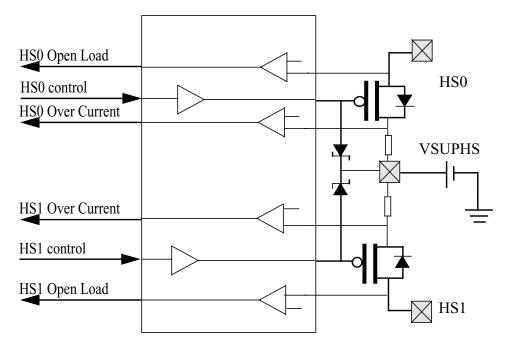

|      | 13.1.3 Block Diagram                                |     |

| 13.2 | External Signal Description                         |     |

|      | 13.2.1 HS0, HS1— High Side Driver Pins              |     |

|      | 13.2.2 VSUPHS — High Side Driver Power Pin          |     |

| 10.0 | 13.2.3 VSSXHS — High Side Driver Ground Pin         |     |

| 13.3 | Memory Map and Register Definition                  |     |

|      | 13.3.1 Module Memory Map                            |     |

|      | 13.3.2 Register Definition                          |     |

|      |                                                     |     |

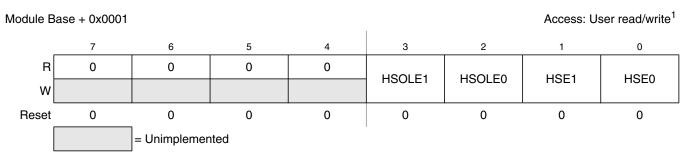

|      | 13.3.4 HSDRV Configuration Register (HSCR)          |     |

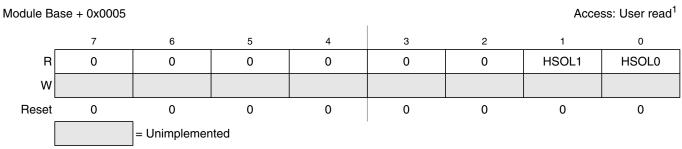

|      | 13.3.6 HSDRV Status Register (HSSR)                 |     |

|      | 13.3.7 HSDRV Status Register (HSSR)                 |     |

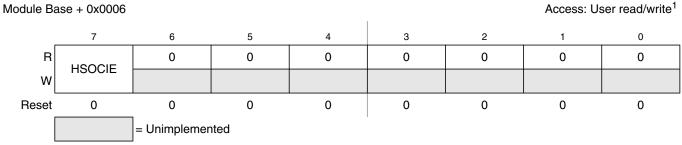

|      | 13.3.8 HSDRV Interrupt Flag Register (HSIF)         |     |

| 13 4 | Functional Description                              |     |

| 13.1 | 13.4.1 General                                      |     |

|      | 13.4.2 Open Load Detection                          |     |

|      | 13.4.3 Over-Current Detection                       |     |

|      | 13.4.4 Interrupts                                   |     |

| 13.5 | Application Information                             |     |

|      | 13.5.1 Use Cases                                    | 410 |

|      |                                                     |     |

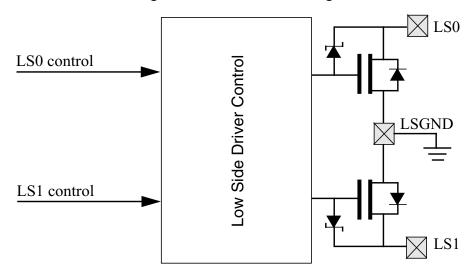

|      | Chapter 14                                          |     |

|      | Low-Side Drivers - LSDRV (S12LSDRV1)                |     |

| 14.1 | Introduction                                        | 411 |

|      | 14.1.1 Features                                     |     |

|      | 14.1.2 Modes of Operation                           |     |

|      | 14.1.3 Block Diagram                                |     |

| 14.2 | External Signal Description                         |     |

|      | 14.2.1 LS0, LS1— Low Side Driver Pins               |     |

|      | 14.2.2 LSGND — Low Side Driver Ground Pin           | 413 |

| 14.3  | Memory Map and Register Definition            | . 413 |

|-------|-----------------------------------------------|-------|

|       | 14.3.1 Module Memory Map                      | 413   |

|       | 14.3.2 Register Definition                    |       |

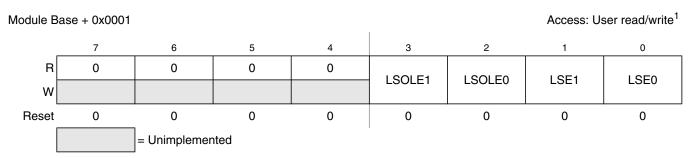

|       | 14.3.3 Port LS Data Register (LSDR)           | 415   |

|       | 14.3.4 LSDRV Configuration Register (LSCR)    |       |

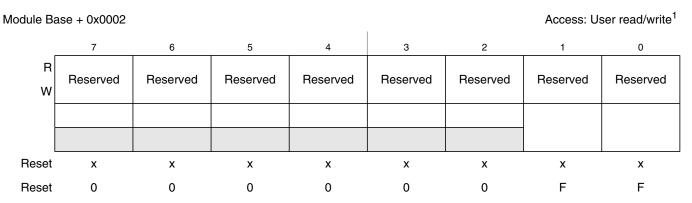

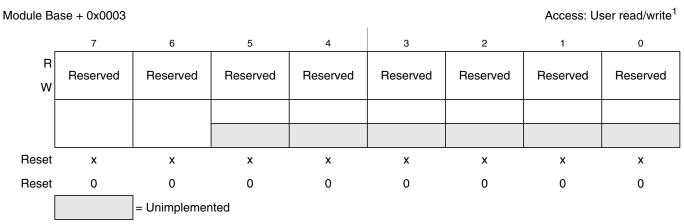

|       | 14.3.5 Reserved Register                      |       |

|       | 14.3.6 Reserved Register                      |       |

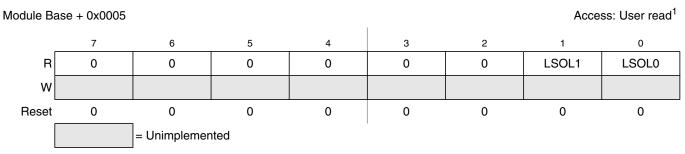

|       | 14.3.7 LSDRV Status Register (LSSR)           |       |

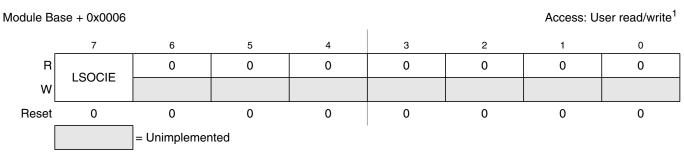

|       | 14.3.8 LSDRV Interrupt Enable Register (LSIE) |       |

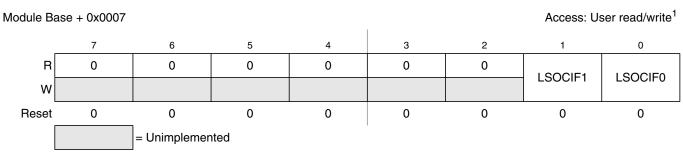

|       | 14.3.9 LSDRV Interrupt Flag Register (LSIF)   |       |

| 14 4  | Functional Description                        |       |

|       | 14.4.1 General                                |       |

|       | 14.4.2 Open-Load Detection                    |       |

|       | 14.4.3 Over-Current Detection                 |       |

|       | 14.4.4 Interrupts                             |       |

| 14.5  | Application Information                       |       |

| 1 110 | 14.5.1 Use Cases                              |       |

|       |                                               |       |

|       | Chapter 15                                    |       |

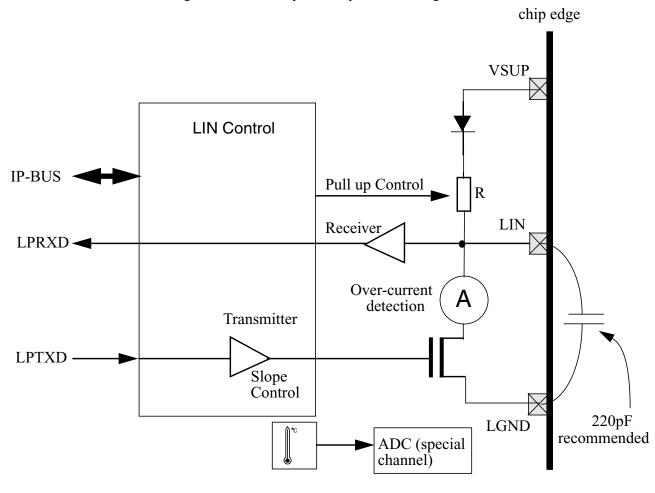

|       | LIN Physical Layer (S12LINPHYV1)              |       |

| 15.1  | Introduction                                  | 425   |

| 13.1  | 15.1.1 Features                               |       |

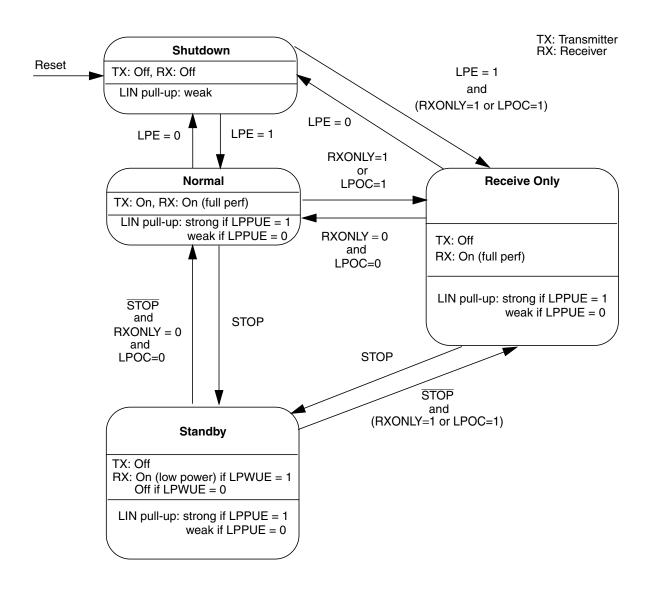

|       | 15.1.2 Modes of Operation                     |       |

|       | 15.1.3 Block Diagram                          |       |

| 15.2  | External Signal Description                   |       |

| 13.2  | 15.2.1 LIN — LIN Bus Pin                      |       |

|       | 15.2.2 LGND — LIN Ground Pin                  |       |

|       | 15.2.3 VSUP — Positive Power Supply           |       |

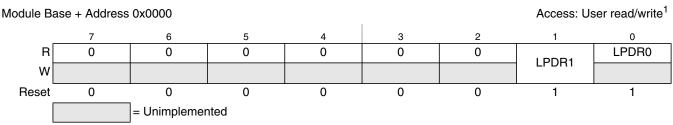

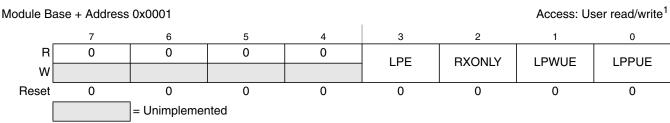

| 15 3  | Memory Map and Register Definition            |       |

| 10.0  | 15.3.1 Module Memory Map                      |       |

|       | 15.3.2 Register Descriptions                  |       |

| 15.4  | Functional Description                        |       |

| 10    | 15.4.1 General                                |       |

|       | 15.4.2 Slew Rate Selection                    |       |

|       | 15.4.3 Modes                                  |       |

|       | 15.4.4 Interrupts                             |       |

| 15.5  | Application Information                       |       |

| 10.0  | 15.5.1 Over-current handling                  |       |

|       | 15.5.2 Use Cases                              |       |

|       |                                               |       |

|       | Chapter 16                                    |       |

|       | Supply Voltage Sensor - (BATSV2)              |       |

| 16.1  | Introduction                                  | 443   |

| 10.1  | 16.1.1 Features                               |       |

|       | 20.2.2 20.0.200                               |       |

|             | 16.1.2 Modes of Operation                                       | 443 |

|-------------|-----------------------------------------------------------------|-----|

|             | 16.1.3 Block Diagram                                            | 444 |

| 16.2        | External Signal Description                                     | 444 |

|             | 16.2.1 VSENSE — Supply (Battery) Voltage Sense Pin              | 444 |

|             | 16.2.2 VSUP — Voltage Supply Pin                                |     |

| 16.3        | Memory Map and Register Definition                              |     |

|             | 16.3.1 Register Summary                                         |     |

|             | 16.3.2 Register Descriptions                                    |     |

| 16.4        | Functional Description                                          |     |

|             | 16.4.1 General                                                  |     |

|             | 16.4.2 Interrupts                                               |     |

|             | 1                                                               |     |

|             | Chapter 17                                                      |     |

|             | 64 KByte Flash Module (S12FTMRG64K512V1)                        |     |

| 17.1        | Introduction                                                    | 457 |

| _,,,_       | 17.1.1 Glossary                                                 |     |

|             | 17.1.2 Features                                                 |     |

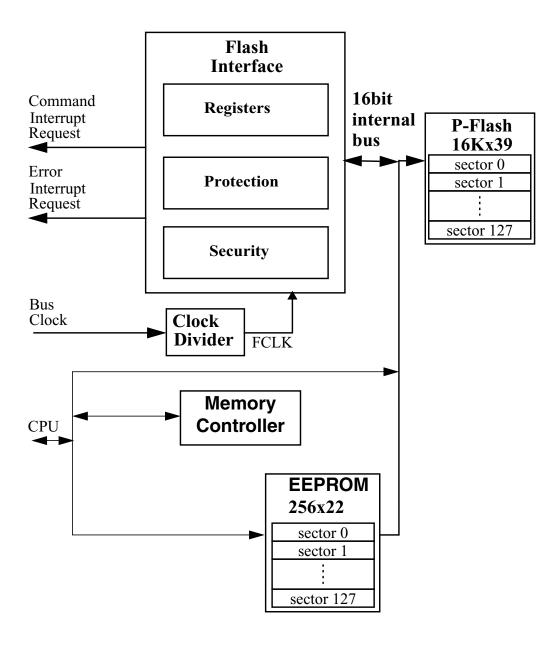

|             | 17.1.3 Block Diagram                                            |     |

| 17.2        | External Signal Description                                     |     |

|             |                                                                 |     |

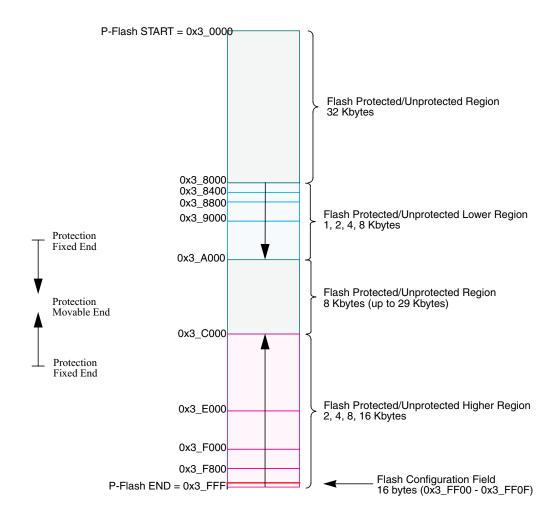

| 1710        | 17.3.1 Module Memory Map                                        |     |

|             | 17.3.2 Register Descriptions                                    |     |

| 17.4        | Functional Description                                          |     |

| 2711        | 17.4.1 Modes of Operation                                       |     |

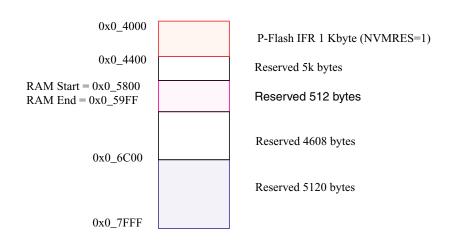

|             | 17.4.2 IFR Version ID Word                                      |     |

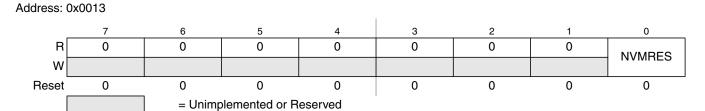

|             | 17.4.3 Internal NVM resource (NVMRES)                           |     |

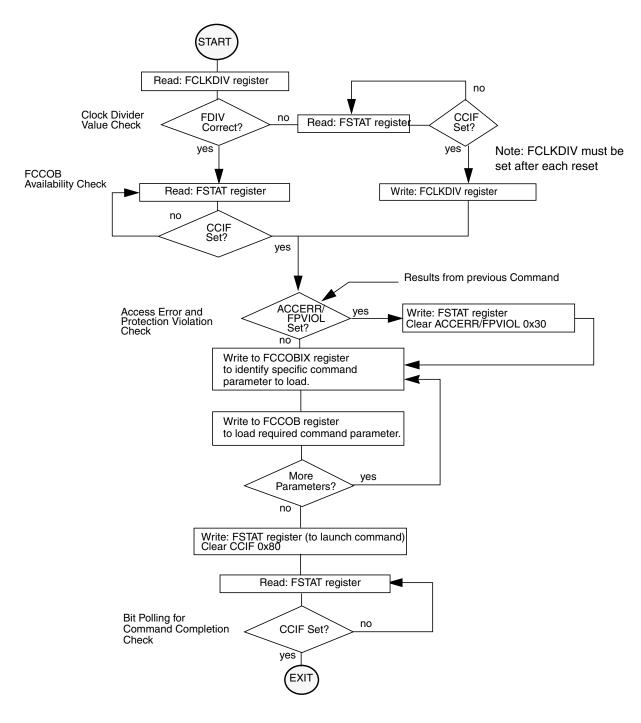

|             | 17.4.4 Flash Command Operations                                 |     |

|             | 17.4.5 Allowed Simultaneous P-Flash and EEPROM Operations       |     |

|             | 17.4.6 Flash Command Description                                |     |

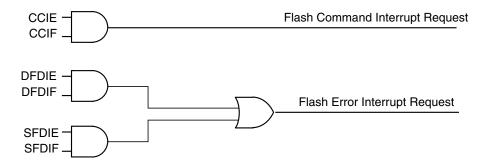

|             | 17.4.7 Interrupts                                               |     |

|             | 17.4.8 Wait Mode                                                |     |

|             | 17.4.9 Stop Mode                                                |     |

| 17.5        | Security                                                        |     |

|             | 17.5.1 Unsecuring the MCU using Backdoor Key Access             |     |

|             | 17.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM |     |

|             | 17.5.3 Mode and Security Effects on Flash Command Availability  |     |

| 17.6        | Initialization                                                  |     |

|             |                                                                 |     |

|             | Appendix A                                                      |     |

|             | MCU Electrical Specifications                                   |     |

| <b>A.</b> 1 | General                                                         |     |

|             | A.1.1 Parameter Classification                                  | 509 |

|             | A.1.2 Pins                                                      |     |

|             | A.1.3 Current Injection                                         | 511 |

|             |                                                                 |     |

MC9S12VR Family Reference Manual, Rev. 2.8

Freescale Semiconductor

|                   | A.1.4 Absolute Maximum Ratings511                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | A.1.5 ESD Protection and Latch-up Immunity513                                                                                                                                                                                                                                                                     |

|                   | A.1.6 Operating Conditions                                                                                                                                                                                                                                                                                        |

|                   | A.1.7 Power Dissipation and Thermal Characteristics                                                                                                                                                                                                                                                               |

|                   | A.1.8 I/O Characteristics                                                                                                                                                                                                                                                                                         |

|                   | A.1.9 Supply Currents                                                                                                                                                                                                                                                                                             |

|                   | Appendix B VREG Electrical Specifications                                                                                                                                                                                                                                                                         |

|                   | Appendix C                                                                                                                                                                                                                                                                                                        |

| G 1               | ATD Electrical Specifications                                                                                                                                                                                                                                                                                     |

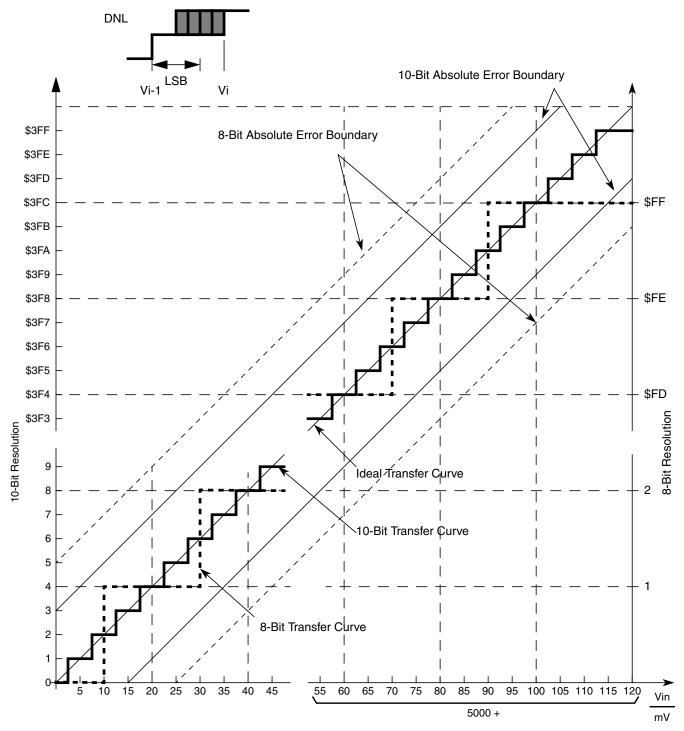

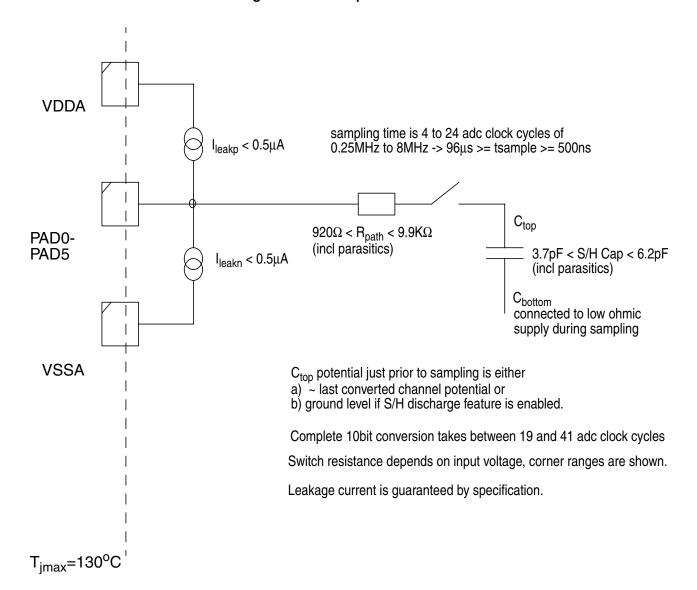

| C.1               | ATD Operating Characteristics                                                                                                                                                                                                                                                                                     |

| C.2               | Factors Influencing Accuracy                                                                                                                                                                                                                                                                                      |

|                   | C.2.1 Port AD Output Drivers Switching                                                                                                                                                                                                                                                                            |

|                   | C.2.3 Source Capacitance                                                                                                                                                                                                                                                                                          |

|                   | C.2.4 Current Injection                                                                                                                                                                                                                                                                                           |

| C.3               | ATD Accuracy                                                                                                                                                                                                                                                                                                      |

|                   | C.3.1 ATD Accuracy Definitions                                                                                                                                                                                                                                                                                    |

|                   | Appendix D                                                                                                                                                                                                                                                                                                        |

|                   | HSDRV Electrical Specifications                                                                                                                                                                                                                                                                                   |

| D.1               | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2               | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

|                   | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2               | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2               | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2               | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics 531 Static Characteristics 531 Dynamic Characteristics 532  Appendix E PLL Electrical Specifications  Reset, Oscillator and PLL 533 E.1.1 Phase Locked Loop 533  Appendix F IRC Electrical Specifications  Appendix G LINPHY Electrical Specifications |

| D.2<br>D.3        | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

| D.2<br>D.3<br>E.1 | HSDRV Electrical Specifications  Operating Characteristics                                                                                                                                                                                                                                                        |

# Appendix H LSDRV Electrical Specifications

| H.1<br>H.2 | Static Characteristics                                                                                     |             |

|------------|------------------------------------------------------------------------------------------------------------|-------------|

|            | Appendix I                                                                                                 |             |

|            | BATS Electrical Specifications                                                                             |             |

| I.1        | Maximum Ratings                                                                                            |             |

| I.2<br>I.3 | Static Electrical Characteristics                                                                          |             |

| 1.3        | Dynamic Electrical Characteristics                                                                         | . 343       |

|            | Appendix J                                                                                                 |             |

|            | PIM Electrical Specifications                                                                              |             |

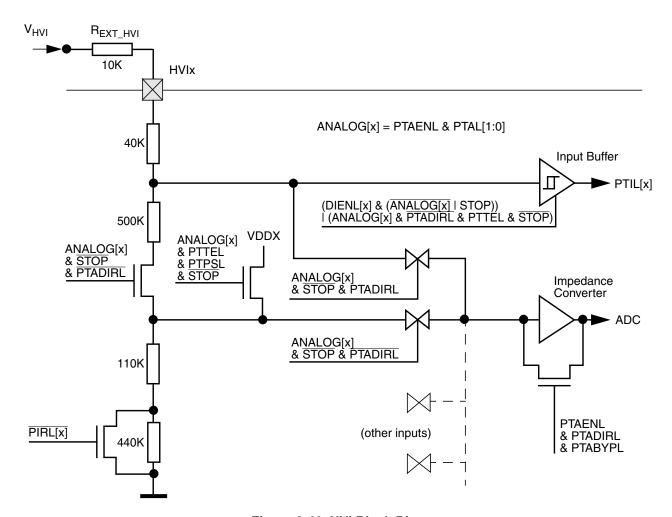

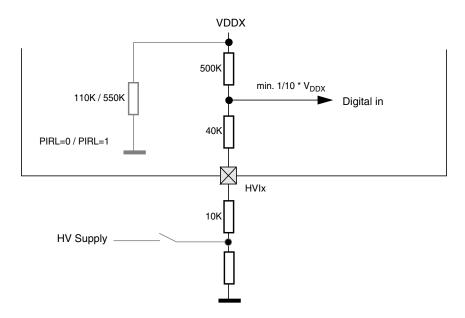

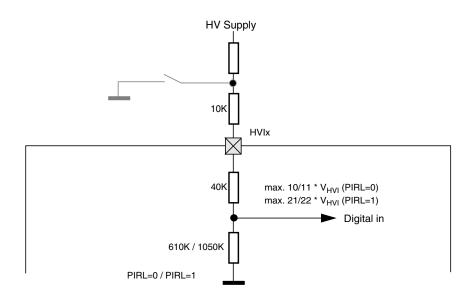

| J.1        | High-Voltage Inputs (HVI) Electrical Characteristics                                                       | . 547       |

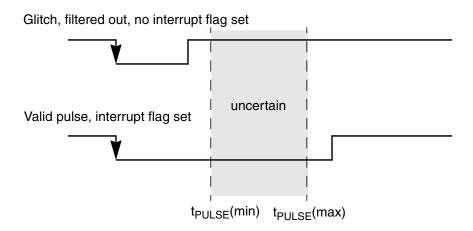

| J.2        | Pin Interrupt Characteristics                                                                              |             |

|            | A man a malifar IV                                                                                         |             |

|            | Appendix K                                                                                                 |             |

| TZ 4       | SPI Electrical Specifications                                                                              | <b>7.40</b> |

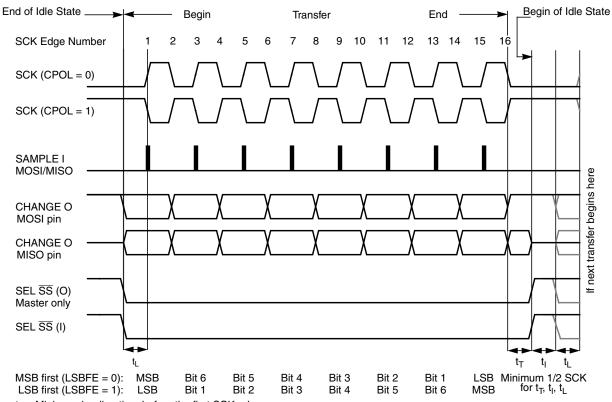

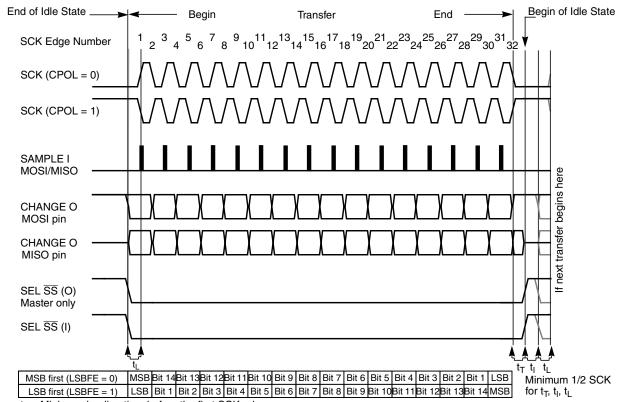

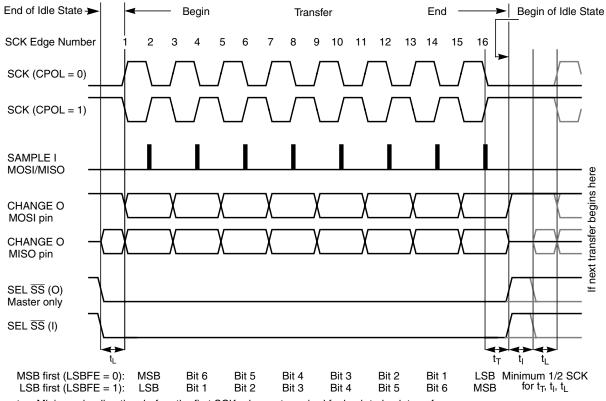

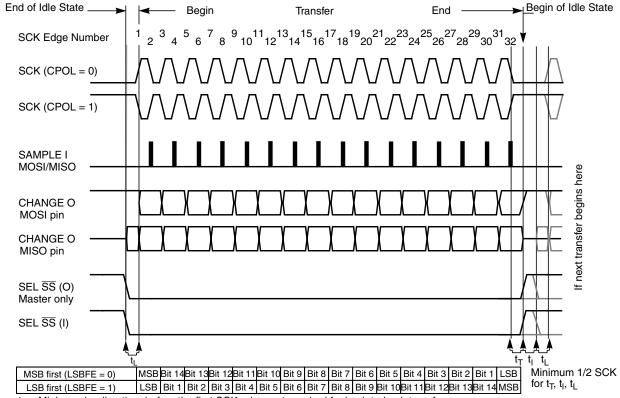

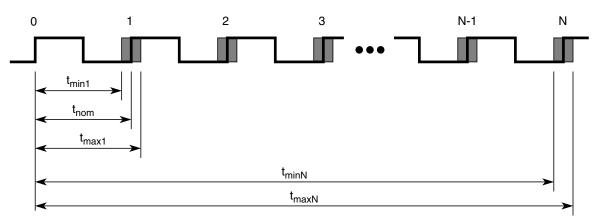

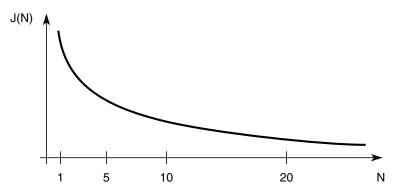

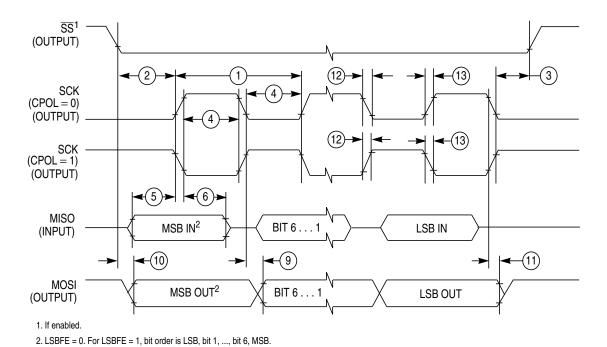

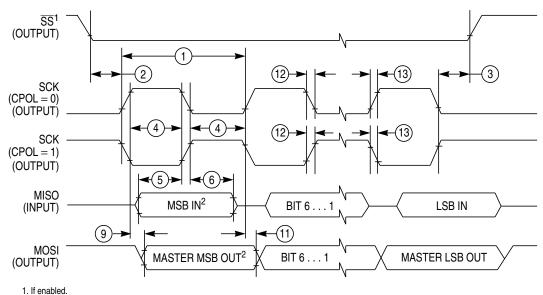

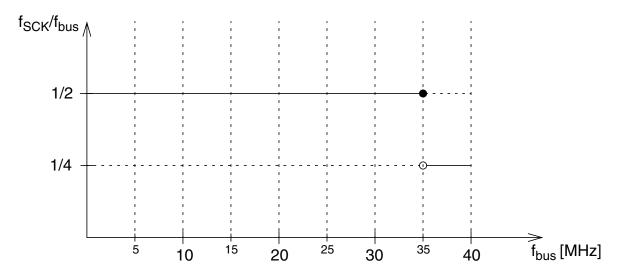

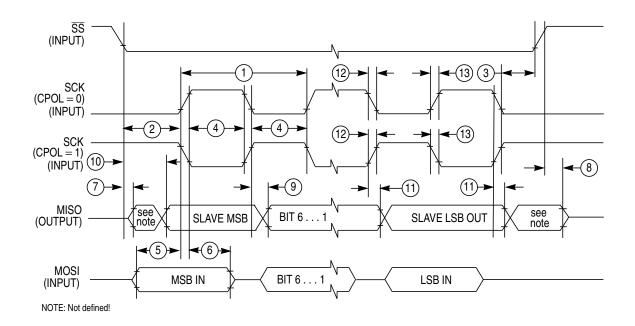

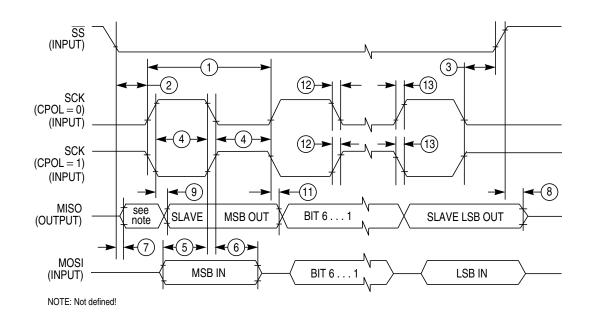

| K.1        | Timing                                                                                                     |             |

|            | K.1.1 Waster Wode                                                                                          |             |

|            | 11.1.2 Stave Mode                                                                                          | . 551       |

|            | Appendix L                                                                                                 |             |

|            | XOSCLCP Electrical Specifications                                                                          |             |

|            | A managed by NA                                                                                            |             |

|            | Appendix M                                                                                                 |             |

| N          | FTMRG Electrical Specifications                                                                            | 557         |

| M.1        | Timing Parameters                                                                                          |             |

|            | M.1.1 Erase Verify An Blocks (Blank Check) (FCMD=0x01)  M.1.2 Erase Verify Block (Blank Check) (FCMD=0x02) |             |

|            | M.1.3 Erase Verify P-Flash Section (FCMD=0x03).                                                            |             |

|            | M.1.4 Read Once (FCMD=0x04)                                                                                |             |

|            | M.1.5 Program P-Flash (FCMD=0x06)                                                                          |             |

|            | M.1.6 Program Once (FCMD=0x07)                                                                             |             |

|            | M.1.7 Erase All Blocks (FCMD=0x08)                                                                         |             |

|            | M.1.8 Erase P-Flash Block (FCMD=0x09)                                                                      |             |

|            | M.1.10 Unsecure Flash (FCMD=0x0B)                                                                          |             |

|            | M.1.11 Verify Backdoor Access Key (FCMD=0x0C)                                                              |             |

|            | M.1.12 Set User Margin Level (FCMD=0x0D)                                                                   |             |

|            | M.1.13 Set Field Margin Level (FCMD=0x0E)                                                                  |             |

|            | M.1.14 Erase Verify D-Flash Section (FCMD=0x10)                                                            | . 560       |

|            | M.1.15 Program D-Flash (FCMD=0x11)                                                                         | . 560       |

|            |                                                                                                            |             |

Freescale Semiconductor

MC9S12VR Family Reference Manual, Rev. 2.8

17

|     | M.1.16 Erase D-Flash Sector (FCMD=0x12)  |    |

|-----|------------------------------------------|----|

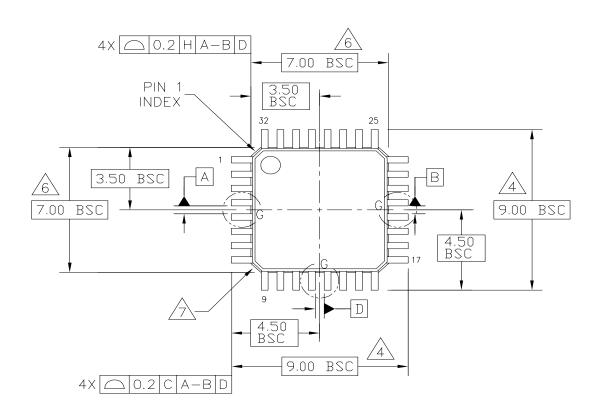

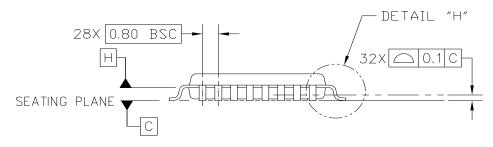

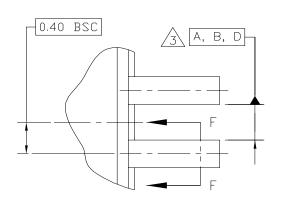

|     | Appendix N Package Information           |    |

|     | Appendix O Detailed Register Address Map |    |

| 0.1 | Detailed Register Map                    | 71 |

# Chapter 1 Device Overview MC9S12VR-Family

**Table 1-1. Revision History**

| Version<br>Number | Revision<br>Date | Description of Changes                                                                                                                 |  |

|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0               | 26-November-2010 | Added Block Diagram     Minor Corrections from Shared Review                                                                           |  |

| 2.0               | 11-April-2011    | <ul> <li>New Revision for Maskset N05E PartID=\$3201</li> <li>Added 6 PWM Channels</li> <li>Pinout changes for PWM channels</li> </ul> |  |

#### 1.1 Introduction

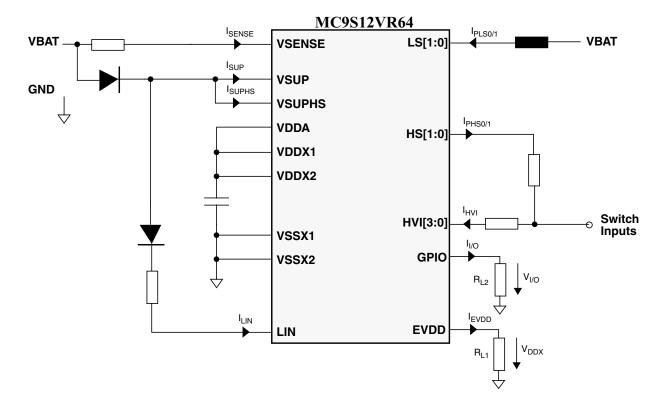

The MC9S12VR-Family is an optimized automotive 16-bit microcontroller product line focused on low-cost, high-performance, and low pin-count. This family integrates an S12 microcontroller with a LIN Physical interface, a 5V regulator system to supply the microcontroller, and analog blocks to control other elements of the system which operate at vehicle battery level (e.g. relay drivers, high-side driver outputs, wake up inputs). The MC9S12VR-Family is targeted at generic automotive applications requiring single node LIN communications. Typical examples of these applications include window lift modules, seat modules and sun-roof modules to name a few.

The MC9S12VR-Family uses many of the same features found on the MC9S12G family, including error correction code (ECC) on flash memory, EEPROM for diagnostic or data storage, a fast analog-to-digital converter (ADC) and a frequency modulated phase locked loop (IPLL) that improves the EMC performance. The MC9S12VR-Family delivers an optimized solution with the integration of several key system components into a single device, optimizing system architecture and achieving significant space savings. The MC9S12VR-Family delivers all the advantages and efficiencies of a 16-bit MCU while retaining the low cost, power consumption, EMC, and code-size efficiency advantages currently enjoyed by users of Freescale's existing 8-bit and 16-bit MCU families. Like the MC9S12XS family, the MC9S12VR-Family will run 16-bit wide accesses without wait states for all peripherals and memories. Misaligned single cycle 16 bit RAM access is not supported. The MC9S12VR-Family will be available in 32-pin and 48-pin LQFP. In addition to the I/O ports available in each module, further I/O ports are available with interrupt capability allowing wake-up from stop or wait modes.

The MC9S12VR-Family is a general-purpose family of devices created with relay based motor control in mind and is suitable for a range of applications, including:

- Window lift modules

- Door modules

- Seat controllers

- Smart actuators

• Sun roof modules

## 1.2 Features

This section describes the key features of the MC9S12VR-Family.

# 1.2.1 MC9S12VR-Family Member Comparison

Table 1-2 provides a summary of different members of the MC9S12VR-Family and their features. This information is intended to provide an understanding of the range of functionality offered by this microcontroller family.

Table 1-2. MC9S12VR - Family

| Feature                                          | MC9S12VR48                                                                           | MC9S12VR64 |

|--------------------------------------------------|--------------------------------------------------------------------------------------|------------|

| CPU                                              | HCS12                                                                                |            |

| Flash memory (ECC)                               | 48 Kbytes                                                                            | 64 Kbytes  |

| EEPROM (ECC)                                     | 512 [                                                                                | Bytes      |

| RAM                                              | 2 Kb                                                                                 | ytes       |

| LIN physical layer                               | -                                                                                    | 1          |

| SPI                                              | -                                                                                    | 1          |

| SCI                                              | Up                                                                                   | to 2       |

| Timer                                            | 4ch x                                                                                | 16-bit     |

| PWM                                              | 8ch x 8-bit or<br>4ch x 16-bit                                                       |            |

| ADC                                              | 6 ch x 10-bit available on external pins and four internal channels. see Table 1-13. |            |

| Frequency modulated PLL                          | Yes                                                                                  |            |

| Internal 1 MHz RC oscillator                     | Yes                                                                                  |            |

| Autonomous window watchdog                       | -                                                                                    | 1          |

| Low-side drivers (protected for inductive loads) | 2                                                                                    |            |

| High-side drivers                                | Up to 2                                                                              |            |

| High voltage Inputs                              | 4                                                                                    |            |

| General purpose I/Os (5V)                        | Up to 28                                                                             |            |

| Direct battery sense pin                         | Yes                                                                                  |            |

| Supply voltage sense                             | Yes                                                                                  |            |

| Chip temperature sensor                          | 1 general sensor                                                                     |            |

| Feature                 | MC9S12VR48                                                                      | MC9S12VR64 |

|-------------------------|---------------------------------------------------------------------------------|------------|

| Supply voltage          | V <sub>SUP</sub> = 6V - 18 V (normal operation) up to 40V (protected operation) |            |

| EVDD output current     | 20mA @ 5V                                                                       |            |

| Maximum execution speed | 25 MHz                                                                          |            |

| Package                 | 32 pins<br>48 pins                                                              |            |

## 1.3 Chip-Level Features

On-chip modules available within the family include the following features:

- HCS12 CPU core

- 64 or 48 Kbyte on-chip flash with ECC

- 512 byte EEPROM with ECC

- 2 Kbyte on-chip SRAM

- Phase locked loop (IPLL) frequency multiplier with internal filter

- 1 MHz internal RC oscillator with +/-1.3% accuracy over rated temperature range

- 4-16MHz amplitude controlled pierce oscillator

- Internal COP (watchdog) module (with separate clock source)

- Timer module (TIM) supporting input/output channels that provide a range of 16-bit input capture, output compare and counter (up to 4 channels)

- Pulse width modulation (PWM) module (up to 8 x 8-bit channels)

- 10-bit resolution successive approximation analog-to-digital converter (ADC) with up to 6 channels available on external pins

- One serial peripheral interface (SPI) module

- One serial communication interface (SCI) module supporting LIN communications (with RX connected to a timer channel for internal oscillator calibration purposes, if desired)

- Up to one additional SCI (not connected to LIN physical layer)

- One on-chip LIN physical layer transceiver fully compliant with the LIN 2.1 standard

- On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

- Autonomous periodic interrupt (API) (combination with cyclic, watchdog)

- Two protected low-side outputs to drive inductive loads

- Up to two protected high-side outputs

- 4 high-voltage inputs with wake-up capability and readable internally on ADC

- Up to two 10mA high-current outputs

- 20mA high-current output for use as Hall sensor supply

- Battery voltage sense with low battery warning, internally reverse battery protected

- Chip temperature sensor

### 1.4 Module Features

The following sections provide more details of the modules implemented on the MC9S12VR-Family.

## 1.4.1 HCS12 16-Bit Central Processor Unit (CPU)

The HCS12 CPU is a high-speed, 16-bit processing unit that has a programming model identical to that of the industry standard M68HC11 central processor unit (CPU).

- Full 16-bit data paths supports efficient arithmetic operation and high-speed math execution

- Supports instructions with odd byte counts, including many single-byte instructions. This allows much more efficient use of ROM space.

- Extensive set of indexed addressing capabilities, including:

- Using the stack pointer as an indexing register in all indexed operations

- Using the program counter as an indexing register in all but auto increment/decrement mode

- Accumulator offsets using A, B, or D accumulators

- Automatic index predecrement, preincrement, postdecrement, and postincrement (by -8 to +8)

## 1.4.2 On-Chip Flash with ECC

On-chip flash memory on the MC9S12VR features the following:

- 64 or 48 Kbyte of program flash memory

- Automated program and erase algorithm

- Protection scheme to prevent accidental program or erase

- 512 Byte EEPROM

- 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 4 bytes

- Automated program and erase algorithm

- User margin level setting for reads

## 1.4.3 On-Chip SRAM

22

• 2 Kbytes of general-purpose RAM

## 1.4.4 Main External Oscillator (XOSCLCP)

- Loop control Pierce oscillator using 4 MHz to 16 MHz crystal

- Current gain control on amplitude output

- Signal with low harmonic distortion

- Low power

- Good noise immunity

- Eliminates need for external current limiting resistor

- Transconductance sized for optimumstart-up margin for typical crystals

- Oscillator pins shared with GPIO functionality

## 1.4.5 Internal RC Oscillator (IRC)

- Factory trimmed internal reference clock

- Frequency: 1 MHz

- Trimmed accuracy over  $-40^{\circ}$ C to  $+105^{\circ}$ C ambient temperature range:  $\pm 1.3\%$

## 1.4.6 Internal Phase-Locked Loop (IPLL)

- Phase-locked-loop clock frequency multiplier

- No external components required

- Reference divider and multiplier allow large variety of clock rates

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- Reference clock sources:

- Internal 1 MHz RC oscillator (IRC)

# 1.4.7 Clock and Power Management Unit (CPMU)

- Real time interrupt (RTI)

- Clock monitor (CM)

- System reset generation

# 1.4.8 System Integrity Support

- Power-on reset (POR)

- Illegal address detection with reset

- Low-voltage detection with interrupt or reset

- Computer operating properly (COP) watchdog with option to run on internal RC oscillator

- Configurable as window COP for enhanced failure detection

- Can be initialized out of reset using option bits located in flash memory

- Clock monitor supervising the correct function of the oscillator

## 1.4.9 Timer (TIM)

- Up to 4 x 16-bit channels for input capture or output compare

- 16-bit free-running counter with 8-bit precision prescaler

## 1.4.10 Pulse Width Modulation Module (PWM)

- Up to eight 8-bit channels or reconfigurable four 16-bit channel PWM resolution

- Programmable period and duty cycle per channel

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

## 1.4.11 LIN physical layer transceiver (LINPHY)

- Compliant with LIN physical layer 2.1

- Standby mode with glitch-filtered wake-up.

- Slew rate selection optimized for the baud rates: 10kBit/s, 20kBit/s and Fast Mode (up to 250kBit/s).

- Selectable pull-up of  $30k\Omega$  or  $330k\Omega$  (in Shutdown Mode,  $330k\Omega$  only)

- Current limitation by LIN Bus pin rising and falling edges

- Over-current protection with transmitter shutdown

# 1.4.12 Serial Peripheral Interface Module (SPI)

- Configurable 8- or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or slave

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

## 1.4.13 Serial Communication Interface Module (SCI)

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 13-bit baud rate selection

24

Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wake-up

- Break detect and transmit collision detect supporting LIN

- Internal connection to one SCI routable to external pins

## 1.4.14 Analog-to-Digital Converter Module (ATD)

- Up to 6-channel, 10-bit analog-to-digital converter

- 8-/10-bit resolution

- 3 us, 10-bit single conversion time

- Left or right justified result data

- Internal oscillator for conversion in stop modes

- Wake up from low power modes on analog comparison > or <= match

- Continuous conversion mode

- Multiple channel scans

- Pins can also be used as digital I/O

- Up to 6 pins can be used as keyboard wake-up interrupt (KWI)

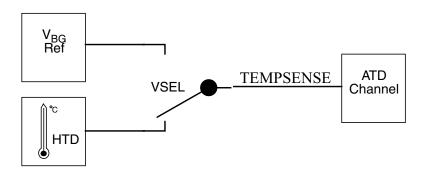

- Internal voltages monitored with the ATD module

- $V_{SUP}$ ,  $V_{SENSE}$ , chip temperature sensor, high voltage inputs, LIN physical temperature sense,  $V_{RH}$ ,  $V_{RL}$ ,  $V_{DDF}$

## 1.4.15 Supply Voltage Sense (BATS)

- VSENSE & VSUP pin low or a high voltage interrupt

- VSENSE & VSUP pin can be routed via an internal divider to the internal ADC

# 1.4.16 On-Chip Voltage Regulator system (VREG)

- Voltage regulator

- Linear voltage regulator directly supplied by VSUP (protected VBAT)

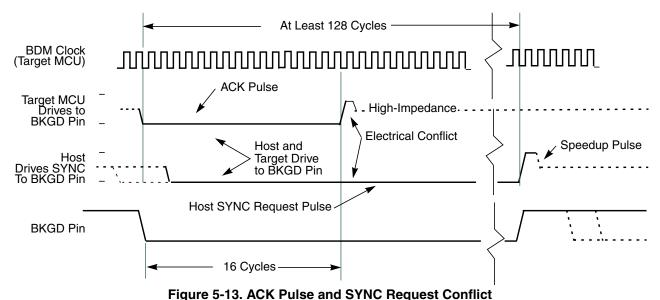

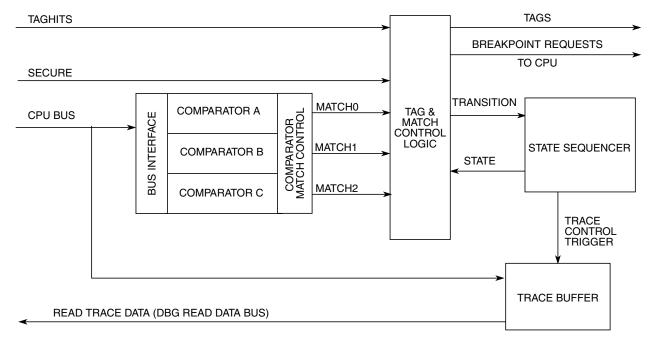

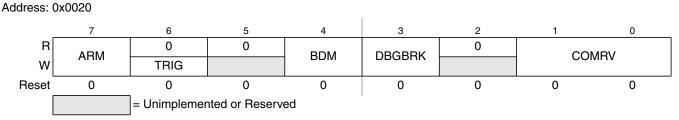

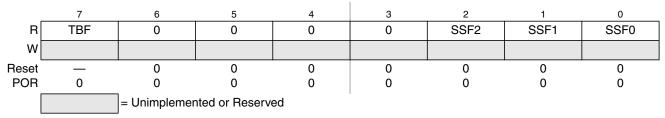

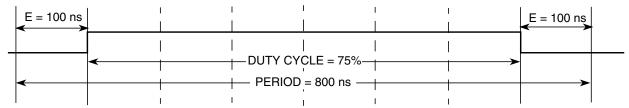

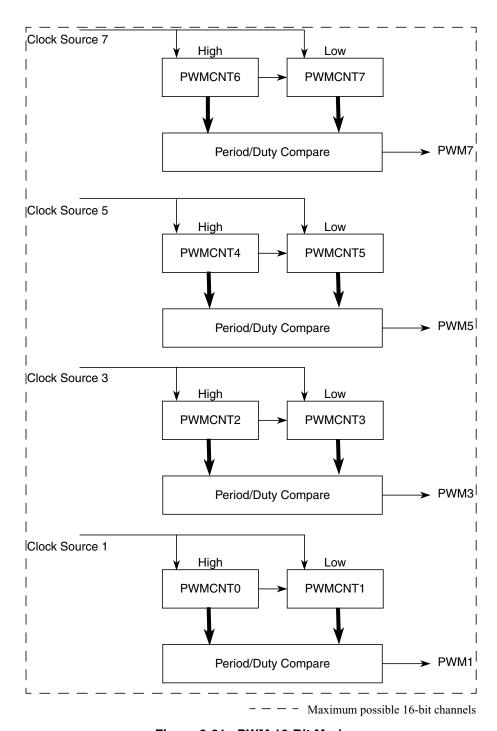

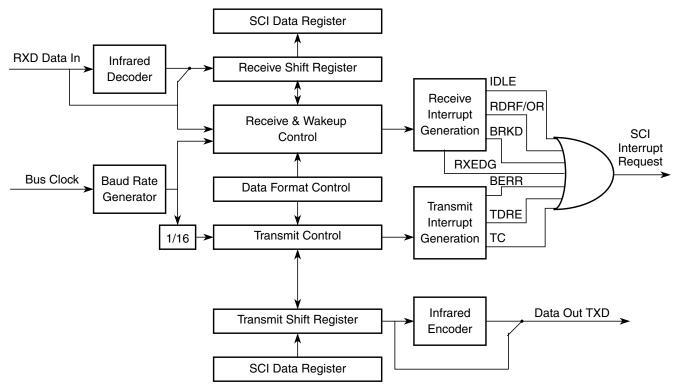

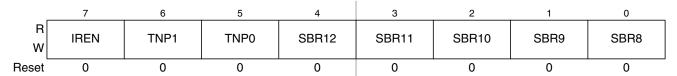

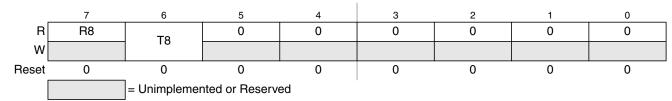

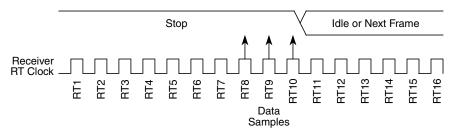

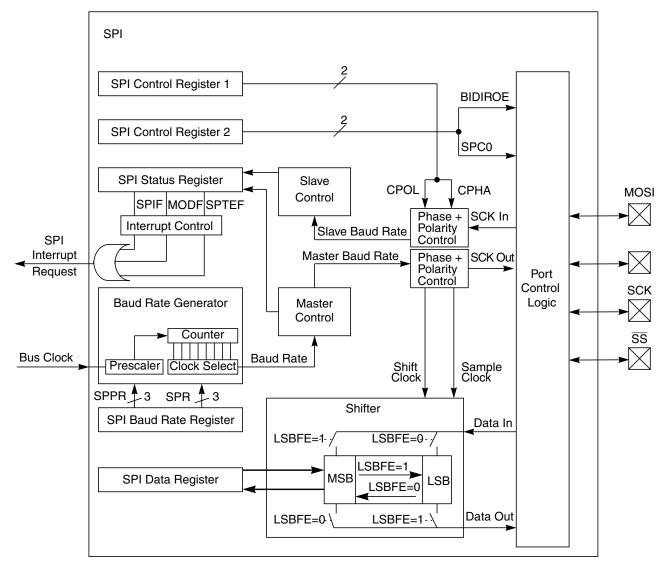

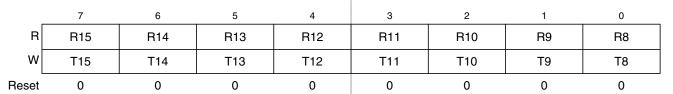

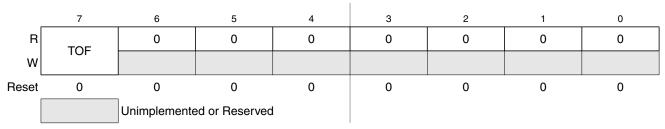

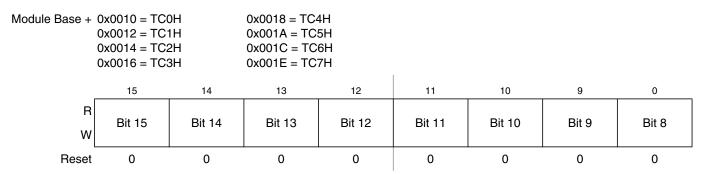

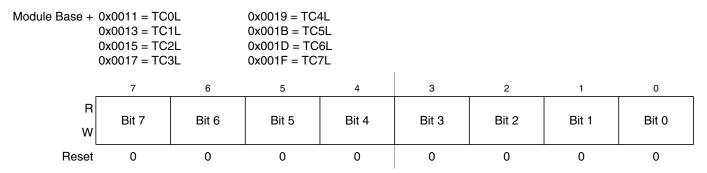

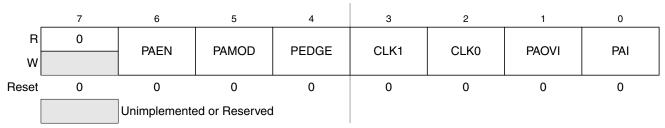

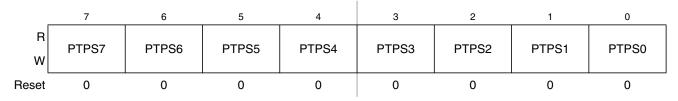

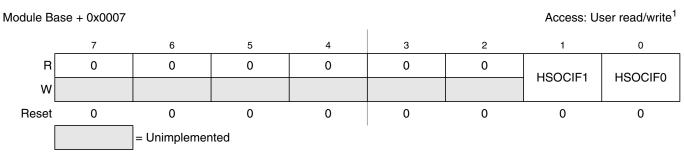

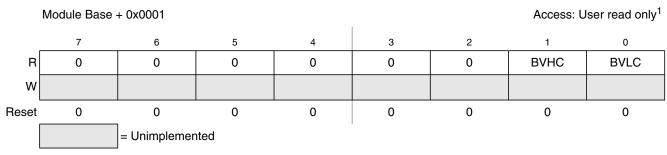

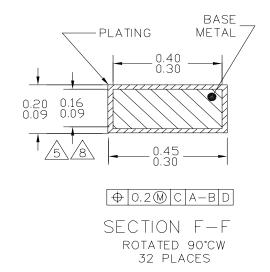

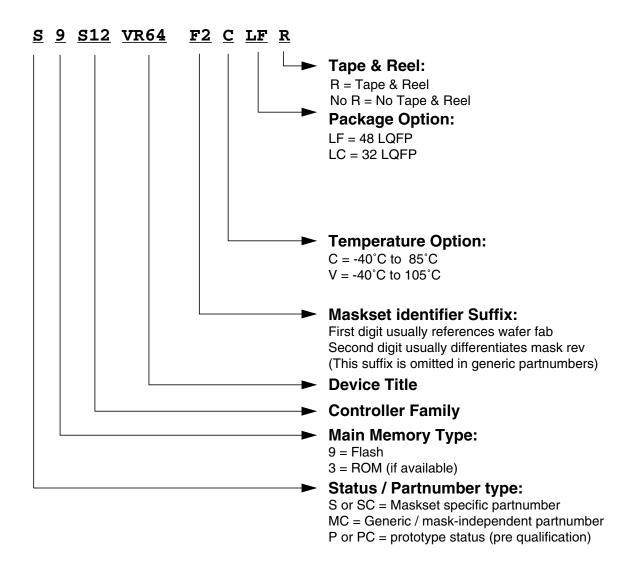

- Low-voltage detect with low-voltage interrupt on V<sub>SUP</sub>