## Atmel AT42QT1040

# Four-key QTouch® Touch Sensor IC

#### DATASHEET

#### **Features**

- Number of QTouch<sup>®</sup> Keys:

- Up to four

- Discrete Outputs:

- Four discrete outputs indicating individual key touch

- Technology:

- Patented spread-spectrum charge-transfer (direct mode)

- Electrode Design:

- Simple self-capacitance style (refer to the *Touch Sensors Design Guide*)

- Electrode Materials:

- Etched copper, silver, carbon, Indium Tin Oxide (ITO)

- Electrode Substrates:

- PCB, FPCB, plastic films, glass

- Panel Materials:

- Plastic, glass, composites, painted surfaces (low particle density metallic paints possible)

- Panel Thickness:

- Up to 10 mm glass, 5 mm plastic (electrode size dependent)

- Key Sensitivity:

- Fixed key threshold, sensitivity adjusted via sample capacitor value

- Adjacent Key Suppression

- Patented Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology to enable accurate key detection

- Interface:

- Pin-per-key outputs, plus debug mode to observe sensor signals

- Moisture Tolerance:

- Increased moisture tolerance based on hardware design and firmware tuning

- Signal Processing:

- Self-calibration, auto drift compensation, noise filtering

- Applications:

- Mobile, consumer, white goods, toys, kiosks, POS, and so on

- Power:

- 1.8 V 5.5 V

- Package:

- 20-pin 3 x 3 mm VQFN RoHS compliant

# 1. Pinout and Schematic

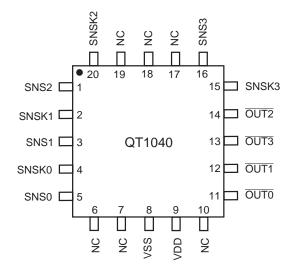

# 1.1 Pinout Configuration

# 1.2 Pin Descriptions

Table 1-1. Pin Listing

| 1 SNS 2 SNSi 3 SNS | 1 1/0       | Sense pin  Sense pin and option detect  Sense pin | To Cs2  To Cs1 and option resistor + key  To Cs1 | Leave open  Connect to option resistor* |

|--------------------|-------------|---------------------------------------------------|--------------------------------------------------|-----------------------------------------|

|                    | 1 I/O       | ·                                                 | key                                              | resistor*                               |

| 3 SNS              |             | Sense pin                                         | To Cs1                                           |                                         |

|                    | (0 I/O      |                                                   |                                                  | Leave open                              |

| 4 SNSI             |             | Sense pin and option detect                       | To Cs0 and option resistor + key                 | Connect to option resistor*             |

| 5 SNS              | 0 I/O       | Sense pin                                         | To Cs0                                           | Leave open                              |

| 6 N/C              | ; –         | -                                                 |                                                  | -                                       |

| 7 N/C              | ; –         | -                                                 |                                                  | _                                       |

| 8 Vss              | s P         | Supply ground                                     |                                                  | -                                       |

| 9 Vdd              | I Р         | Power                                             |                                                  | _                                       |

| 10 N/C             | ; –         | -                                                 |                                                  | _                                       |

| 11 OUT             | 0 OD        | Out 0                                             | Alternative function: Debug CLK                  | Leave open                              |

| 12 OUT             | 71 OD       | Out 1                                             | Alternative function: Debug DATA                 | Leave open                              |

| 13 OUT             | <u>3</u> OD | Out 3                                             |                                                  | Leave open                              |

| 14 OUT             | <u>2</u> OD | Out 2                                             |                                                  | Leave open                              |

| 15 SNSI            | (3 I/O      | Sense pin                                         | To Cs3 + key                                     | Leave open                              |

| 16 SNS             | 3 I/O       | Sense pin                                         | To Cs3                                           | Leave open                              |

| 17 N/C             | ; –         | _                                                 |                                                  | _                                       |

| 18 N/C             | ; –         | -                                                 |                                                  | _                                       |

| 19 N/C             | ; –         | _                                                 |                                                  | _                                       |

| 20 SNSI            | (2 1/0      | Sense pin                                         | To Cs2 + key                                     | Leave open                              |

<sup>\*</sup> Option resistor should always be fitted even if channel is unused and Cs capacitor is not fixed.

I/O CMOS input and output OD CMOS open drain output P Ground or power

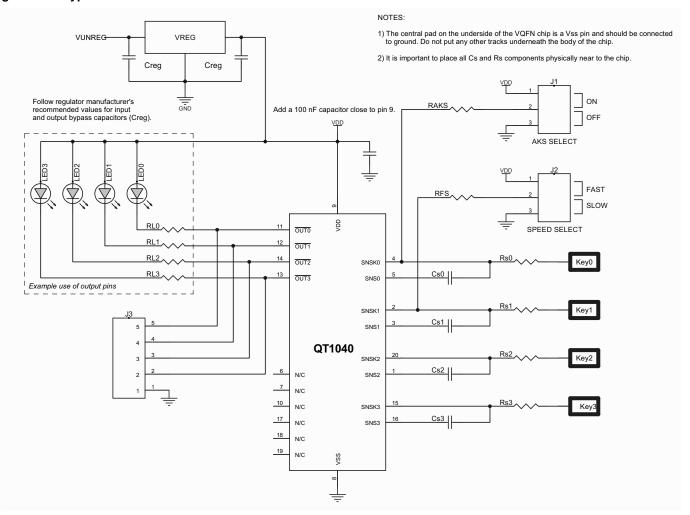

#### 1.3 Schematic

Figure 1-1. Typical Circuit

Suggested regulator manufacturers:

- Torex (XC6215 series)

- Seiko (S817 series)

- BCDSemi (AP2121 series)

For component values in Figure 1-1 check the following sections:

- Section 3.1 on page 7: Cs capacitors (Cs0 Cs3)

- Section 3.5 on page 7: Voltage levels

- Section 3.3 on page 7: LED traces

## 2. Overview of the AT42QT1040

#### 2.1 Introduction

The AT42QT1040 (QT1040) is a digital burst mode charge-transfer ( $QT^{TM}$ ) capacitive sensor driver designed for touch-key applications. The device can sense from one to four keys; one to three keys can be disabled by not installing their respective sense capacitors. Any of the four channels can be disabled in this way.

The device includes all signal processing functions necessary to provide stable sensing under a wide variety of changing conditions, and the outputs are fully de-bounced. Only a few external parts are required for operation.

The QT1040 modulates its bursts in a spread-spectrum fashion in order to heavily suppress the effects of external noise, and to suppress RF emissions.

## 2.2 Signal Processing

#### 2.2.1 Detect Threshold

The internal signal threshold level is fixed at 10 counts of change with respect to the internal reference level. This in turn adjusts itself slowly in accordance with the drift compensation mechanism. See Section 3.1 on page 7 for details on how to adjust the sensitivity of each key.

When going out of detect there is a hysteresis element to the detection. The signal threshold must drop below 8 counts of change with respect to the internal reference level to register as un-touched.

#### 2.2.2 Detection Integrator

The device features a detection integration mechanism, which acts to confirm a detection in a robust fashion. A perkey counter is incremented each time the key has exceeded its threshold, and a key is only finally declared to be touched when this counter reaches a fixed limit of 5. In other words, the device has to exceed its threshold, and stay there for 5 acquisitions in succession without going below the threshold level, before the key is declared to be touched.

#### 2.2.3 Burst Length Limitations

Burst length is the number of times the charge transfer process is performed on a given channel; that is, the number of pulses it takes to measure the key capacitance.

The maximum burst length is 2048 pulses. The recommended design is to use a capacitor that gives a signal of <1000 pulses. Longer bursts take more time and use more power.

Note that the keys are independent of each other. It is therefore possible, for example, to have a signal of 100 on one key and a signal of 1000 on another.

Refer to Application Note QTAN0002, Secrets of a Successful QTouch Design (downloadable from the Atmel website), for more information on using a scope to measure the pulses and hence determine the burst length. Refer also to the Touch Sensors Design Guide.

#### 2.2.4 Adjacent Key Suppression Technology

The device includes the Atmel-patented Adjacent Key Suppression (AKS) technology, to allow the use of tightly spaced keys on a keypad with no loss of selectability by the user.

There is one global AKS group, implemented so that only one key in the group may be reported as being touched at any one time.

The use of AKS is selected by connecting a 1 M $\Omega$  resistor between Vdd and the SNSK0 pin (see Section 4.1 on page 9 for more information). When AKS is disabled, any combinations of keys can enter detect.

#### 2.2.5 Auto Drift Compensation

Signal drift can occur because of changes in Cx and Cs over time. It is crucial that drift be compensated for, otherwise false detections, non-detections, and sensitivity shifts will follow.

Drift compensation is performed by making the reference level track the raw signal at a slow rate, but only while there is no detection in effect. The rate of adjustment must be performed slowly otherwise legitimate detections could be ignored.

Once an object is sensed and a key is in detect, the drift compensation mechanism ceases, since the signal is legitimately high and should not therefore cause the reference level to change.

The QT1040 drift compensation is *asymmetric*, that is, the reference level drift-compensates in one direction faster than it does in the other. Specifically, it compensates faster for decreasing (towards touch) signals than for increasing (away from touch) signals. The reason for this difference in compensation rates is that increasing signals should not be compensated for quickly, since a nearby finger could be compensated for partially or entirely before even approaching the sense electrode. However, decreasing signals need to be compensated for more quickly. For example, an obstruction over the sense pad (for which the sensor has already made full allowance) could suddenly be removed, leaving the sensor with an artificially elevated reference level and thus become insensitive to touch. In this latter case, the sensor will compensate for the object's removal very quickly, usually in only a few seconds.

Negative drift (that is, towards touch) occurs at a rate of ~3 seconds, while positive drift occurs at a rate of ~1 second.

Drifting only occurs when no keys are in detect state.

#### 2.2.6 Response Time

The QT1040 response time is highly dependent on run mode and burst length, which in turn is dependent on Cs and Cx. With increasing Cs, response time slows, while increasing levels of Cx reduce response time. The response time will also be slower in slow mode due to a longer time between burst measurements. This mode offers an increased detection latency in favor of reduced average current consumption.

#### 2.2.7 Spread Spectrum

The QT1040 modulates its internal oscillator by  $\pm 7.5\%$  during the measurement burst. This spreads the generated noise over a wider band reducing emission levels. This also reduces susceptibility since there is no longer a single fundamental burst frequency.

#### 2.2.8 Max On-duration

If an object or material obstructs the sense pad, the signal may rise enough to create a detection, preventing further operation. To prevent this, the sensor includes a timer known as the Max On-duration feature which monitors detections. If a detection exceeds the timer setting, the sensor performs an automatic recalibration. Max On-duration is set to ~30s.

# 3. Wiring and Parts

#### 3.1 Cs Sample Capacitors

Cs0 – Cs3 are the charge sensing sample capacitors; normally they are identical in nominal value. The optimal Cs values depend on the corresponding keys electrode design, the thickness of the panel and its dielectric constant. Thicker panels require larger values of Cs. Values can be in the range 2.2 nF (for faster operation) to 22 nF (for best sensitivity); typical values are 4.7 nF to 10 nF.

The value of Cs should be chosen such that a light touch on a key mounted in a production unit or a prototype panel causes a reliable detection. The chosen Cs value should never be so large that the key signals exceed ~1000, as reported by the chip in the debug data.

The Cs capacitors must be X7R or PPS film type, for stability. For consistent sensitivity, they should have a 10% tolerance. Twenty percent tolerance may cause small differences in sensitivity from key to key and unit to unit. If a key is not used, the Cs capacitor may be omitted.

#### 3.2 Rs Resistors

The series resistors Rs0 – Rs3 are in line with the electrode connections (close to the QT1040 chip) and are used to limit electrostatic discharge (ESD) currents and to suppress radio frequency (RF) interference. A typical value is 4.7 k $\Omega$ , but up to 20 k $\Omega$  can be used if it is found to be of benefit.

Although these resistors may be omitted, the device may become susceptible to external noise or radio frequency interference (RFI). For details on how to select these resistors refer to Application Note QTAN0002, Secrets of a Successful QTouch Design, and the Touch Sensors Design Guide, both downloadable from the Touch Technology area of the Atmel website, www.atmel.com.

## 3.3 LED Traces and Other Switching Signals

For advice on LEDs and nearby traces, refer to Application Note QTAN0002, Secrets of a Successful QTouch Design, and the Touch Sensors Design Guide, both downloadable from the Touch Technology area of Atmel's website, www.atmel.com.

#### 3.4 PCB Cleanliness

Modern no-clean flux is generally compatible with capacitive sensing circuits.

**CAUTION:** If a PCB is reworked to correct soldering faults relating to the device, or to any associated traces or components, be sure that you fully understand the nature of the flux used during the rework process. Leakage currents from hygroscopic ionic residues can stop capacitive sensors from functioning. If you have any doubts, a thorough cleaning after rework may be the only safe option.

## 3.5 Power Supply

See Section 5.2 on page 15 for the power supply range. If the power supply fluctuates slowly with temperature, the device tracks and compensates for these changes automatically with only minor changes in sensitivity. If the supply voltage drifts or shifts quickly, the drift compensation mechanism is not able to keep up, causing sensitivity anomalies or false detections.

The usual power supply considerations with QT parts apply to the device. The power should be clean and come from a separate regulator if possible. However, this device is designed to minimize the effects of unstable power, and except in extreme conditions should not require a separate Low Dropout (LDO) regulator.

See under Figure 1.3 on page 4 for suggested regulator manufacturers.

**Caution:** A regulator IC shared with other logic can result in erratic operation and is **not** advised.

A single ceramic  $0.1~\mu F$  bypass capacitor, with short traces, should be placed very close to the power pins of the IC. Failure to do so can result in device oscillation, high current consumption, erratic operation, and so on.

It is assumed that a larger bypass capacitor (for example, 1  $\mu$ F) is somewhere else in the power circuit; for example, near the regulator.

To assist with transient regulator stability problems, the QT1040 waits 500 µs any time it wakes up from a sleep state (that is, in Sleep mode) before acquiring, to allow Vdd to fully stabilize.

## 3.6 VQFN Package Restrictions

The central pad on the underside of the VQFN chip should be connected to ground. Do not run any tracks underneath the body of the chip, only ground. Figure 3-1 shows an example of good/bad tracking.

Figure 3-1. Examples of Good and Bad Tracking

**Example of BAD tracking**

# 4. Detailed Operations

## 4.1 Adjacent Key Suppression

The use of AKS is selected by the connection of a 1  $M\Omega$  resistor (RAKS resistor) between the SNSK0 pin and either Vdd (AKS mode on) or Vss (AKS mode off).

Table 4-1. RAKS Resistor

| RAKS Connected To                                                                                                           | Mode    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Vdd                                                                                                                         | AKS on  |  |  |

| Vss                                                                                                                         | AKS off |  |  |

| The RAKS resistor should always be connected to either Vdd or Vss and should not be changed during operation of the device. |         |  |  |

**Note:** Changing the RAKS option will affect the sensitivity of the particular key. Always check that the sensitivity is suitable after a change. Retune Cs0 if necessary.

## 4.2 Discrete Outputs

There are four discrete outputs (channels 0 to 3), located on pins  $\overline{\text{OUT0}}$  to  $\overline{\text{OUT3}}$ . An output pin goes active when the corresponding key is touched. The outputs are open-drain type and are active-low.

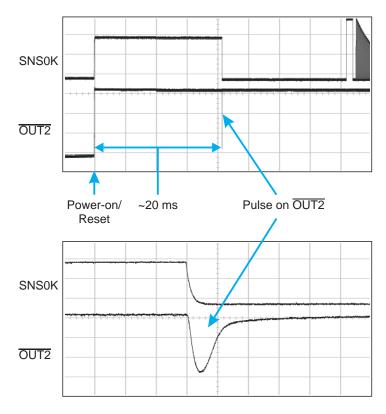

On the  $\overline{\text{OUT2}}$  pin there is a ~500 ns low pulse occurring approximately 20 ms after a power-up/reset (see Figure 4-1 for an example oscilloscope trace of this pulse at two zoom levels). This pulse may need to be considered from the system design perspective.

The discrete outputs have sufficient current sinking capability to directly drive LEDs. Try to limit the sink current to less than 5 mA per output and be cautious if connecting LEDs to a power supply other than Vdd; if the LED supply is higher than Vdd it may cause erratic behavior of the QT1040 and *back-power* the QT1040 through its I/O pins.

Figure 4-1. ~500 ns Pulse On OUT2 Pin

## 4.3 Speed Selection

Speed selection is determined by a 1 M $\Omega$  resistor (RFS resistor) connected between SNSK1 and either Vdd (Fast Mode) or Vss (Slow Mode).

Table 4-2. RFS Resistor

| RFS Connected To | Mode      |

|------------------|-----------|

| Vdd              | Fast mode |

| Vss              | Slow mode |

In Fast Mode, the device sleeps for 16 ms between burst acquisitions. In Slow Mode, the device sleeps for 64 ms between acquisitions. Hence, Slow Mode conserves more power but results in slightly less responsiveness.

**Note:** The RFS resistor should always be connected to either Vdd or Vss and not changed during operation of the device. Changing the RFS option will affect the sensitivity of the particular key. Always check that the sensitivity is suitable after a change. Retune Cs1 if necessary.

#### 4.4 Moisture Tolerance

The presence of water (condensation, sweat, spilt water, and so on) on a sensor can alter the signal values measured and thereby affect the performance of any capacitive device. The moisture tolerance of QTouch devices can be improved by designing the hardware and fine-tuning the firmware following the recommendations in the application note Atmel AVR3002: Moisture Tolerant QTouch Design (www.atmel.com/Images/doc42017.pdf).

#### 4.5 Calibration

Calibration is the process by which the sensor chip assesses the background capacitance on each channel. During calibration, a number of samples are taken in quick succession to get a baseline for the channel reference value.

Calibration takes place ~50 ms after power is applied to the device. Calibration also occurs if the Max On-duration is exceeded or a positive re-calibration occurs.

## 4.6 Debug Mode

An added feature to this device is a debug option whereby internal parameters from the IC can be clocked out and monitored externally.

Debug mode is entered by shorting the CS3 capacitor (SNSK3 and SNS3 pins) on power-up and removing the short within 5 seconds.

Note:

If the short is not removed within 5 seconds, debug mode is still entered, but with Channel 3 unusable until a re-calibration occurs. Note that as Channel 3 will show as being in detect, a recalibration will occur after Max On-duration (~30 seconds).

Debug CLK pin (OUT0) and Debug Data pin (OUT1) float while debug data is not being output and are driven outputs once debug output starts (that is, not open drain).

The serial data is clocked out at a rate of ~200 kHz, MSB first, as in Table 4-3.

Table 4-3. Serial Data Output

| Byte | Purpose               | Notes                                                        |  |

|------|-----------------------|--------------------------------------------------------------|--|

| 0    | Frame Number          | Framing index number 0-255                                   |  |

| 1    | Chip Version          | Upper nibble: major revision<br>Lower nibble: minor revision |  |

| 2    | Reference 0 Low Byte  | Unsigned 16-bit integer                                      |  |

| 3    | Reference 0 High Byte | Onsigned 10-bit integer                                      |  |

| 4    | Reference 1 Low Byte  | Unsigned 16-bit integer                                      |  |

| 5    | Reference 1 High Byte | Onsigned 10-bit integer                                      |  |

| 6    | Reference 2 Low Byte  | Unsigned 16-bit integer                                      |  |

| 7    | Reference 2 High Byte | Onsigned 10-bit integer                                      |  |

| 8    | Reference 3 Low Byte  | Unsigned 16-bit integer                                      |  |

| 9    | Reference 3 High Byte |                                                              |  |

| 10   | Signal 0 Low Byte     | Unsigned 16-bit integer                                      |  |

| 11   | Signal 0 High Byte    | Onsigned 10-bit integer                                      |  |

| 12   | Signal 1 Low Byte     | Unsigned 16-bit integer                                      |  |

| 13   | Signal 1 High Byte    | Onsigned 10-bit integer                                      |  |

| 14   | Signal 2 Low Byte     | Unsigned 16-bit integer                                      |  |

| 15   | Signal 2 High Byte    | onsigned ro-bit integer                                      |  |

| 16   | Signal 3 Low Byte     | Unsigned 16-bit integer                                      |  |

| 17   | Signal 3 High Byte    | Unsigned to-bit integer                                      |  |

Table 4-3. Serial Data Output (Continued)

| Byte | Purpose           | Notes                                    |  |

|------|-------------------|------------------------------------------|--|

| 18   | Delta 0 Low Byte  | Signed 16 bit integer                    |  |

| 19   | Delta 0 High Byte | Signed 16-bit integer                    |  |

| 20   | Delta 1 Low Byte  | Signed 16-bit integer                    |  |

| 21   | Delta 1 High Byte | Signed To-bit integer                    |  |

| 22   | Delta 2 Low Byte  | Signed 16 hit integer                    |  |

| 23   | Delta 2 High Byte | Signed 16-bit integer                    |  |

| 24   | Delta 3 Low Byte  | Signed 16 hit integer                    |  |

| 25   | Delta 3 High Byte | Signed 16-bit integer                    |  |

| 26   | Flags             | Various operational flags                |  |

| 27   | Flags2            | Unsigned bytes                           |  |

| 28   | Status Byte       | Unsigned byte. See Table 4-4             |  |

| 29   | Frame Number      | Repeat of framing index number in byte 0 |  |

Table 4-4. Status Byte (Byte 28)

| Bit 7 | Bit 6 | Bit 5               | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|---------------------|-------|-------|-------|-------|-------|

| CAL   | Num   | ber of Keys (2 – 4) |       | Key 3 | Key 2 | Key 1 | Key 0 |

Bit 7: This bit is set during calibration

Bits 4 – 6: Contains the number of keys active

Bits 0 – 3: Show the touch status of the corresponding keys

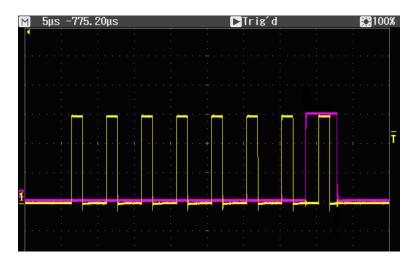

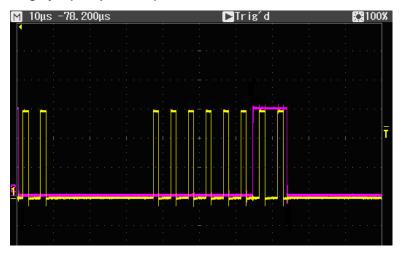

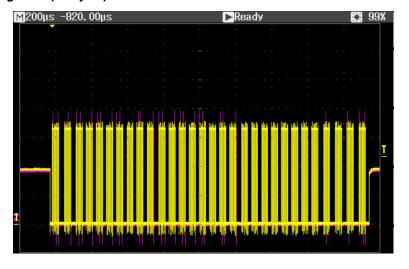

Figure 4-2 to Figure 4-5 show the usefulness of the debug data out feature. Channels can be monitored and tweaked to the specific application with great accuracy.

Figure 4-2. Byte Clocked Out (~5 µs Period)

Figure 4-3. Byte Following Byte (~ 30 µs Period)

Figure 4-4. Full Debug Send (30 Bytes)

Figure 4-5. Debug Lines Floating Between Debug Data Sends (30 Bytes, ~2 ms to Send)

# 5. Specifications

## 5.1 Absolute Maximum Specifications

| Vdd                                                  | -0.5 to +6.0 V          |

|------------------------------------------------------|-------------------------|

| Max continuous pin current, any control or drive pin | ±10 mA                  |

| Voltage forced onto any pin                          | -0.5 V to (Vdd + 0.5) V |

**CAUTION:** Stresses beyond those listed under *Absolute Maximum Specifications* may cause permanent damage the device. This is a stress rating only and functional operation of the device at these or other conditions beyo those indicated in the operational sections of this specification is not implied. Exposure to absolute maximis specification conditions for extended periods may affect device reliability

## 5.2 Recommended Operating Conditions

| Operating temperature  | -40°C to +85°C  |

|------------------------|-----------------|

| Storage temperature    | −55°C to +125°C |

| Vdd                    | 1.8 V to 5.5 V  |

| Supply ripple + noise  | ±20 mV maximum  |

| Cx capacitance per key | 2 to 20 pF      |

# 5.3 DC Specifications

Vdd = 5.0 V, Cs = 4.7 nF, Ta = recommended range, unless otherwise noted

| Parameter | Description                   | Min       | Тур   | Max       | Units | Notes                |

|-----------|-------------------------------|-----------|-------|-----------|-------|----------------------|

| Vil       | Low input logic level         | -0.5      | _     | 0.3       | V     |                      |

| Vih       | High input logic level        | 0.6 × Vdd | Vdd   | Vdd + 0.5 | V     |                      |

| Vol       | Low output voltage            | 0         | _     | 0.7       | V     | 10 mA sink current   |

| Voh       | High output voltage           | 0.8 × Vdd | _     | Vdd       | V     | 10 mA source current |

| lil       | Input leakage current         | _         | <0.05 | 1         | μA    |                      |

| Rrst      | Internal RST pull-up resistor | 20        | _     | 50        | kΩ    |                      |

# 5.4 Timing Specifications

| Parameter | Description                  | Min  | Тур | Max  | Units | Notes                 |

|-----------|------------------------------|------|-----|------|-------|-----------------------|

| TBS       | Burst duration               | _    | 3.5 | _    | ms    | Cx = 5 pF, Cs = 18 nF |

| Fc        | Burst center frequency       | _    | 119 | _    | kHz   |                       |

| Fm        | Burst modulation, percentage | -7.5 | _   | +7.5 | %     |                       |

| Tpw       | Burst pulse width            | _    | 2   | _    | μs    |                       |

# 5.5 Power Consumption

| Vdd (V) | AKS Mode (RAKS) | Speed (RFS) | Power Consumption (μA) |

|---------|-----------------|-------------|------------------------|

|         | Off             | Slow        | 31                     |

| 1.8     | Off             | Fast        | 104                    |

| 1.0     | On              | Slow        | 36                     |

|         | On              | Fast        | 114                    |

|         | Off             | Slow        | 100                    |

| 3.3     | Off             | Fast        | 340                    |

| 3.3     | On              | Slow        | 117                    |

|         | On              | Fast        | 380                    |

|         | Off             | Slow        | 215                    |

| 5.0     | Off             | Fast        | 710                    |

| 3.0     | On              | Slow        | 245                    |

|         | On              | Fast        | 800                    |

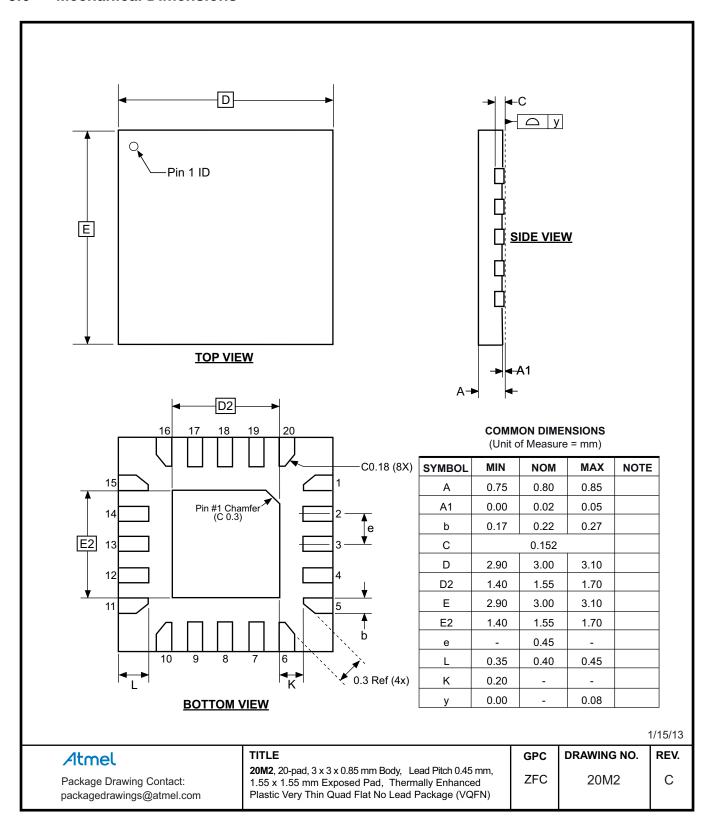

## 5.6 Mechanical Dimensions

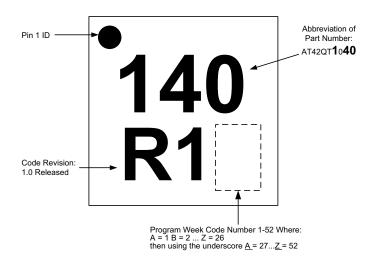

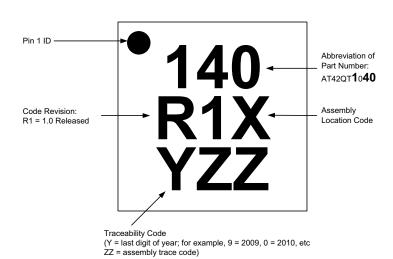

## 5.7 Marking

Either of the following two markings may be used:

#### 5.8 Part Number

| Part Number    | Description                         |

|----------------|-------------------------------------|

| AT42QT1040-MMH | 20-pin 3 x 3 mm VQFN RoHS compliant |

The part number comprises:

AT = Atmel

42 = Touch Business Unit

QT = Charge-transfer technology

1040 = (1) Keys only (04) number of channels (0) variant number

MMH = Package identifier

# 5.9 Moisture Sensitivity Level (MSL)

| MSL Rating | Peak Body Temperature | Specifications      |

|------------|-----------------------|---------------------|

| MSL1       | 260°C                 | IPC/JEDEC J-STD-020 |

# **Revision History**

| Revision No.               | History                                    |  |

|----------------------------|--------------------------------------------|--|

| Revision A – March 2009    | Initial release for chip revision 1.0      |  |

| Revision B – April 2009    | Update to pin listing in Table 1-1         |  |

| Revision C – November 2012 | Updated Atmel logo and other minor changes |  |

| Revision D – May 2013      | Updated template                           |  |

# Notes

#### **Atmel Corporation**

1600 Technology Drive San Jose, CA 95110 USA

**Tel:** (+1) (408) 441-0311 **Fax:** (+1) (408) 487-2600

www.atmel.com

#### **Atmel Asia Limited**

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG

**Tel:** (+852) 2245-6100 **Fax:** (+852) 2722-1369

#### Atmel München GmbH

Business Campus

Parkring 4

D-85748 Garching bei München

GERMANY

**Tel:** (+49) 89-31970-0 **Fax:** (+49) 89-3194621

#### Atmel Japan G.K.

16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032

JAPAN

**Tel:** (+81) (3) 6417-0300 **Fax:** (+81) (3) 6417-0370

© 2013 Atmel Corporation. All rights reserved. / Rev.: 9524D-AT42-05/2013

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, QTouch<sup>®</sup>and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be registered trademarks or trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

AT42QT1040-MMH AT42QT1040-MMHR

# **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9