# CX25870/871

# Video Encoder with Adaptive Flicker Filtering and HDTV Output

Conexant's CX25870/871 is specifically designed to meet TV out system requirements for the next-generation desktop PCs, notebook PCs, game consoles and set-top boxes. With pin and software-forward compatibility to the Bt868/869, manufacturers can quickly bring to market new solutions that support adaptive flicker filtering, ATSC High-Definition Television (HDTV) output, and resolutions from 320 x 200 (minimum) to 1024 x 768 (maximum).

Adaptive flicker filtering is a Conexant technology in which the encoder looks at the characteristics of the video content on a pixel-by-pixel basis and automatically determines the optimal amount of flicker filtering required. If an end-user wants to work on a spreadsheet while watching a DVD movie in a window, both the text-intensive application requiring a lot of flicker filtering and the DVD movie requiring very little flicker filtering can look their best. The amount of flicker filtering and overscan compensation is entirely flexible.

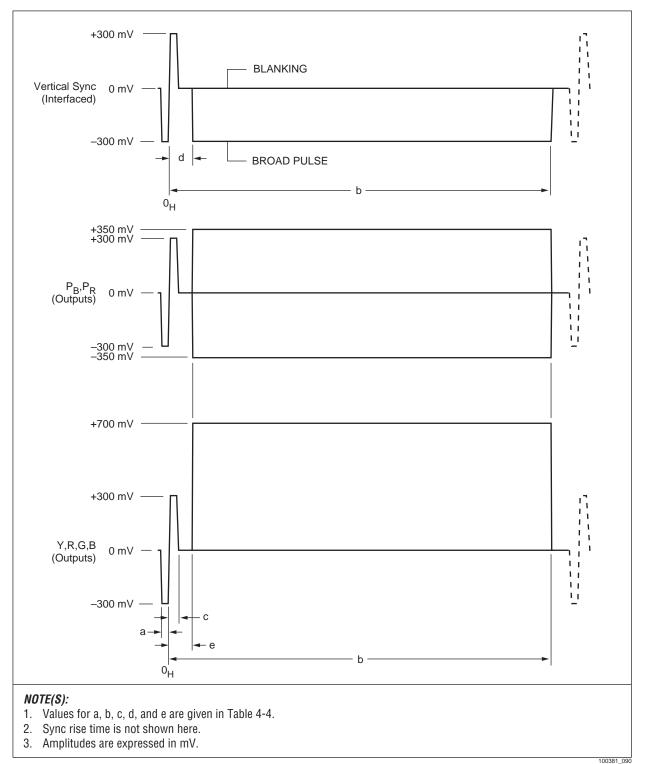

The CX25870/871 also provides a 3-wire analog RGB or  $YP_RP_B$  HDTV output. While the encoder is in HDTV output mode, the device will automatically insert horizontal tri-level synchronization pulses and vertical synchronization broad pulses. The CX25870/871 is compliant with the EIA770-3, SMPTE 274M/293M/296M standards and supports ATSC HDTV resolutions including 480p, 720p, and 1080i.

All worldwide standard definition outputs are supported, including NTSC-M (N. America, Taiwan), NTSC-J (Japan), PAL-B,D,G,H,I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay, Paraguay), PAL-Nc (Argentina), PAL-60 (China) and SECAM. The CX25870 and CX25871 are functionally identical, except the CX25871 can output standard definition video with Macrovision Level 7.1.L1 copy protection capability.

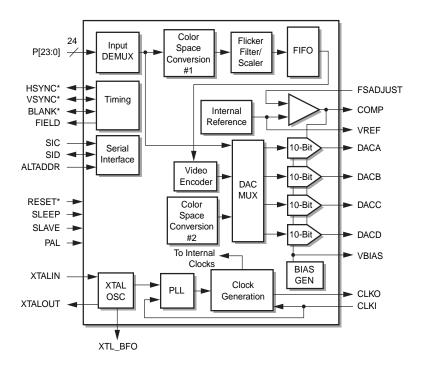

### **Functional Block Diagram**

#### **Distinguishing Features**

- HDTV Output Mode (patents pending) – Compliant with EIA770-3 and SMPTE274M/293M/296M

- standards

- Automatic tri-level sync generation

Component (YP<sub>R</sub>P<sub>B</sub>) or RGB HDTV

- Outputs

Direct YP<sub>R</sub>P<sub>B</sub> or RGB output from progressive RGB graphics video in 1080i, 720p, 480p ATSC resolutions

- Software and register

- forward-compatibility with the Bt868/869

- Ability to accept many different input data formats:

- 15/16/24-bit RGB multiplexed or nonmultiplexed

- 16-bit 4:2:2 and 24-bit 4:4:4 YCrCb multiplexed or nonmultiplexed

- Flexible pixel ordering with various alternate formats

- Worldwide video output support: NTSC-M, J, 4.43, PAL-B, D, G, H, I, M, N, Nc, 60, and SECAM

- Interlaced and noninterlaced outputs

- S-Video output (simultaneous with composite NTSC, PAL, or SECAM)

- SCART RGB or Y/C output for Europe

4th DAC is composite video

EN50-049 and IEC 933-1 compliant

- 5-Line vertical filtering scaling for overscan compensation and flicker reduction

- Adaptive Flicker Filtering for enhanced image and peaking filters for text sharpness (patents pending)

- CCIR601/ITU-RBT.601 (i.e., 480i) and CCIR656 compatible input modes

- Luma and chroma comb filtering

- 4 x 10-bit DACs

- Programmable power management

- Master, pseudo-master or slave timing

- operation

- Auto detection of TV

- 44 autoconfiguration modes

- Wide-Screen Signaling (WSS) support for variable clock rates

Adheres to EIAJ CPR-1024 and

- Adheres to EIAJ CPR-1024 and ITU-R TST.1119-1 standards

Full register set readback capability

- Full register set readback capability

- 3.3 V operation with scalable low voltage graphic controller interface from 1.8 V to 1.1 V

- Buffered crystal clock output pin

- Component YUV analog output

- Colorstream TM (EIA 770.2) and Super Colorstream TM component video outputs

- Macrovision 7.1.L1 copy protection (CX25871)

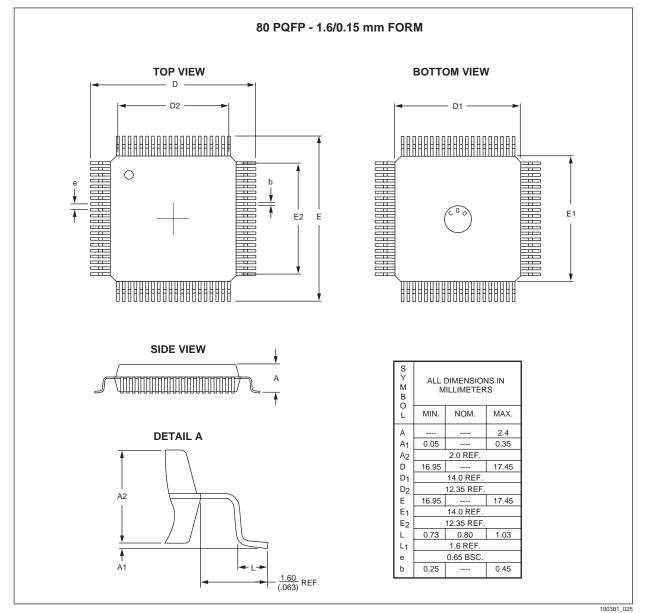

- Compact 80-pin PQFP package

# **Ordering Information**

| Model Number                                                                                                        | Package                  | Ambient Temperature Range |

|---------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|

| CX25870                                                                                                             | 80-pin PQFP              | 0 °C – 70 °C              |

| CX25871 <sup>(1)</sup>                                                                                              | 80-pin PQFP 0 °C – 70 °C |                           |

| <b>NOTE(S):</b><br>1. Macrovision 7.1.L1 compliant (customer must possess Macrovision license to purchase CX25871). |                          |                           |

© 2001, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>TM</sup>, the Conexant C symbol, and "What's Next in Communications Technologies"<sup>TM</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

**Reader Response:** Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

# **Table of Contents**

|     | List | of Figu   | resvii                                             |

|-----|------|-----------|----------------------------------------------------|

|     | List | of Table  | es xi                                              |

| 1.0 | Fun  | ctional l | Description                                        |

|     | 1.1  | Pin Des   | scriptions                                         |

|     | 1.2  | GUI Co    | ntroller Programmability and Frequency Requirement |

|     | 1.3  | Device    | <b>Description</b>                                 |

|     |      | 1.3.1     | Overview                                           |

|     |      | 1.3.2     | Serial Interface                                   |

|     |      | 1.3.3     | Low Voltage Graphics Interface                     |

|     |      | 1.3.4     | Reset                                              |

|     |      | 1.3.5     | Device Initialization                              |

|     |      | 1.3.6     | Clocking and Timing Generation                     |

|     |      |           | 1.3.6.1 3:2 Clocking Mode                          |

|     |      | 1.3.7     | Master, Pseudo-Master, and Slave Interfaces        |

|     |      |           | 1.3.7.1 Master Interface                           |

|     |      |           | 1.3.7.2 Reason for BLANK*                          |

|     |      |           | 1.3.7.3 Pseudo-Master Interface                    |

|     |      |           | 1.3.7.4 Slave Interface                            |

|     |      |           | 1.3.7.5 Slave Interface Without a Crystal          |

|     |      | 1.3.8     | Autoconfiguration and Interface Bits               |

|     |      | 1.3.9     | Adaptations for Clock-Limited Master Devices       |

|     |      | 1.3.10    | Input Formats                                      |

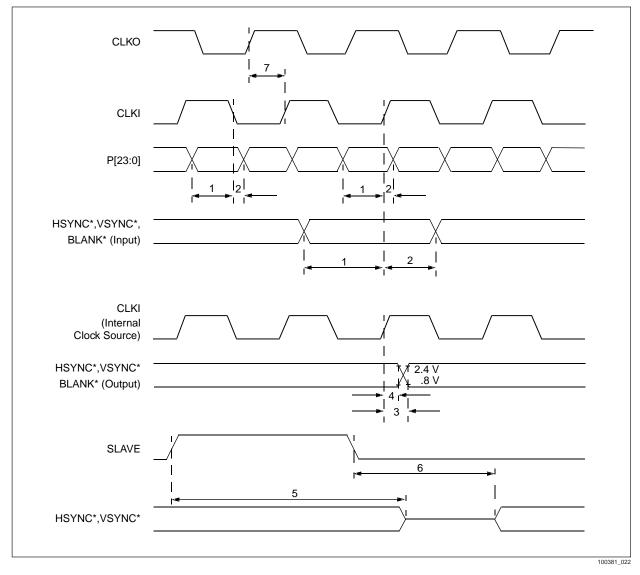

|     |      | 1.3.11    | Input Pixel Timing                                 |

|     |      | 1.3.12    | YCrCb Inputs (For Standard TV Outputs)             |

|     |      | 1.3.13    | RGB Inputs (For Standard TV Outputs)    1-29       |

|     |      | 1.3.14    | Input Pixel Horizontal Sync                        |

|     |      | 1.3.15    | Input Pixel Vertical Sync                          |

|     |      | 1.3.16    | Input Pixel Blanking                               |

|     |      | 1.3.17    | Overscan Compensation                              |

|     |      | 1.3.18    | Standard Flicker Filtering                         |

|     |      | 1.3.19    | Adaptive Flicker Filter                            |

|     |      | 1.3.20    | VGA Registers Involved in the TV Out Process       |

|     |      | 1.3.21    | Output Modes                                       |

|     |      | 1.3.22   | Analog Horizontal Sync                                           | . 1-40 |

|-----|------|----------|------------------------------------------------------------------|--------|

|     |      | 1.3.23   | Analog Vertical Sync.                                            |        |

|     |      | 1.3.24   | Analog Video Blanking                                            |        |

|     |      | 1.3.25   | Video Output Standards Supported                                 |        |

|     |      | 1.3.26   | Subcarrier Generation                                            | . 1-51 |

|     |      | 1.3.27   | Subcarrier Phase Reset/Offset                                    | . 1-51 |

|     |      | 1.3.28   | Burst Generation                                                 |        |

|     |      | 1.3.29   | Video Amplitude Scaling and SINX/X Compensation                  |        |

|     |      | 1.3.30   | Chrominance Disable                                              |        |

|     |      | 1.3.31   | FIELD Pin Output                                                 |        |

|     |      | 1.3.32   | Buffered Crystal Clock Output.                                   |        |

|     |      | 1.3.33   | Noninterlaced Output                                             |        |

|     |      | 1.3.34   | Closed Captioning (CC)                                           |        |

|     |      | 1.3.35   | Wide Screen Signaling (WSS)                                      |        |

|     |      | 1.3.36   | Chrominance and Luminance Processing                             |        |

|     |      | 1.3.37   | Color Bar and Blue Field Generation                              |        |

|     |      | 1.3.38   | CCIR656 Mode Operation                                           |        |

|     |      | 1.3.39   | CCIR601 Mode Operation for DVD Playback                          |        |

|     |      |          | 1.3.39.1 CCIR601 Data In/NTSC Out                                |        |

|     |      |          | 1.3.39.2 CCIR601 Data In/PAL Out                                 |        |

|     |      |          | 1.3.39.3 VGA- Compatible RGB Data In/NTSC Out                    |        |

|     |      | 1.3.40   | SECAM Output                                                     |        |

|     |      | 1.3.41   | Macrovision Copy Protection                                      |        |

|     |      | 1.3.42   | HDTV Output Mode                                                 |        |

|     |      | 1.3.43   | SCART Output                                                     |        |

|     |      | 1.3.44   | Interlaced Standard Definition Analog Component Video TV Outputs |        |

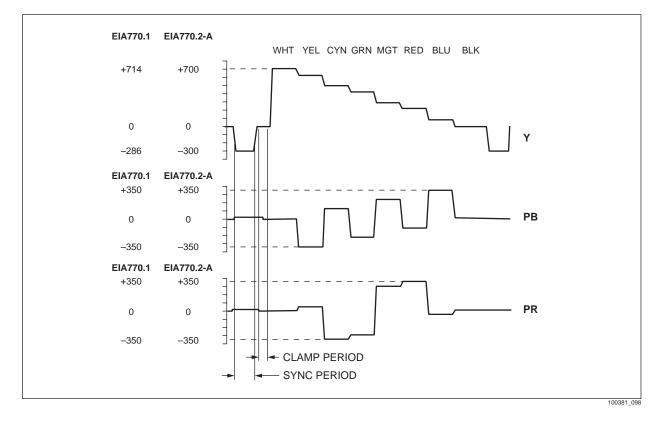

|     |      | 1.3.45   | VGA(RGB)—DAC Output Operation                                    |        |

|     |      | 1.3.46   | TV Auto-Detection Procedures                                     |        |

|     |      | 1.3.47   | Sleep/Power Management                                           | . 1-89 |

| 2.0 | Inte | rnal Rec | jisters                                                          | 2-1    |

|     |      |          | al Registers                                                     | . 2-5  |

|     |      |          | -                                                                |        |

|     | 2.2  |          | Address                                                          |        |

|     | 2.3  |          | Registers                                                        |        |

|     | 2.4  | Reading  | g Registers                                                      | . 2-6  |

| 3.0 | PC I | Board Co | onsiderations                                                    | 3-1    |

|     | 3.1  | Compor   | nent Placement                                                   | . 3-1  |

|     | 3.2  | Power a  | and Ground Planes                                                | . 3-2  |

|     | 3.3  | Recomr   | nended Schematics and Layout for CX25870/871                     | . 3-8  |

|     | 3.4  |          | ling                                                             |        |

|     |      | 3.4.1    | Device Decoupling                                                |        |

|     |      | 3.4.2    | Power Supply Decoupling.                                         |        |

|     |      | 3.4.3    | COMP Decoupling                                                  |        |

|       |         | 3.4.4<br>3.4.5      | VREF Decoupling                                                                    |        |

|-------|---------|---------------------|------------------------------------------------------------------------------------|--------|

|       | 2.5     |                     |                                                                                    |        |

|       | 3.5     | <b>Signal</b> 3.5.1 | Interconnect                                                                       |        |

|       |         | 3.5.2               | Analog Signal Interconnect                                                         |        |

|       | 3.6     |                     | itions Information                                                                 |        |

|       | 0.0     | 3.6.1               | Changes Required to Accommodate CX25870/871 in Bt868/869-Designs                   |        |

|       |         | 0.0.1               | 3.6.1.1 Software                                                                   |        |

|       |         |                     | 3.6.1.2 Hardware                                                                   |        |

|       |         | 3.6.2               | Programmable Video Adjustment Controls                                             | 3-15   |

|       |         |                     | 3.6.2.1 Contrast                                                                   |        |

|       |         |                     | 3.6.2.2 Saturation.                                                                |        |

|       |         |                     | 3.6.2.3 Brightness                                                                 |        |

|       |         |                     | 3.6.2.4 Hue                                                                        |        |

|       |         |                     | 3.6.2.5 Sharpness                                                                  |        |

|       |         |                     | 3.6.2.6       Dot Crawl         3.6.2.7       Standard and Adaptive Flicker Filter |        |

|       |         |                     | 3.6.2.7Standard and Adaptive Flicker Filter3.6.2.8Position                         |        |

|       |         |                     | 3.6.2.9 Size                                                                       |        |

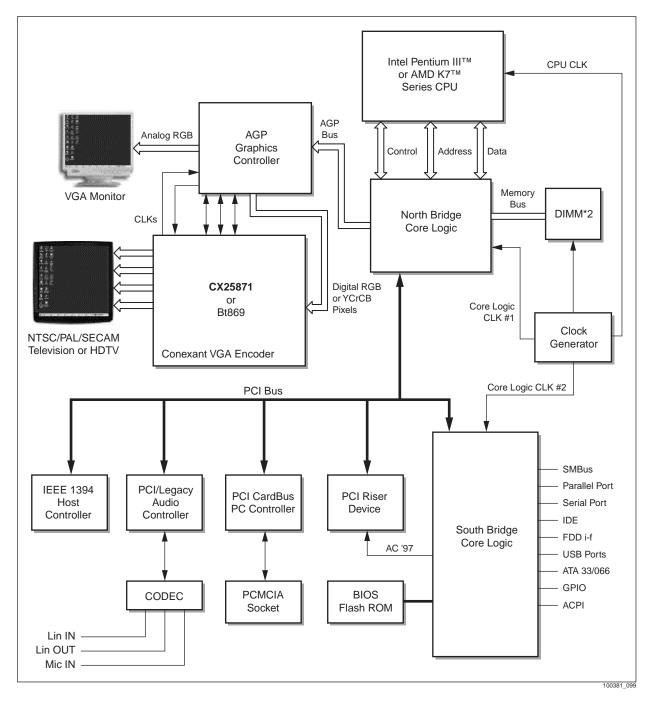

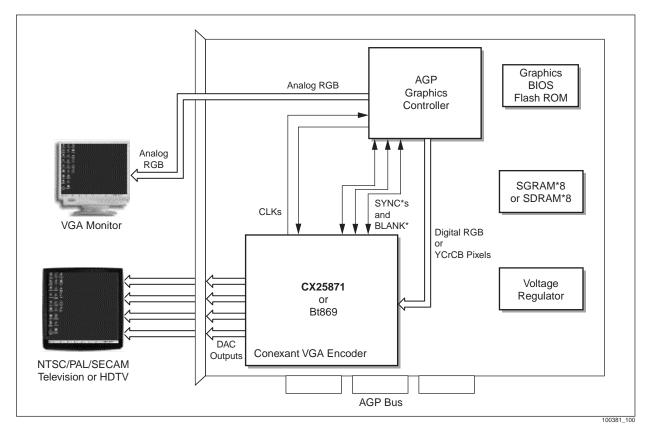

|       |         | 3.6.3               | System Block Diagrams                                                              |        |

|       |         | 3.6.4               | Electrostatic Discharge and Latchup Considerations                                 |        |

|       |         | 3.6.5               | Clock and Subcarrier Stability                                                     |        |

|       |         | 3.6.6               | Filtering Radio Frequency Modulator Connection                                     | 3-29   |

|       | 3.7     | <b>CX870E</b>       | VK Evaluation Kit.                                                                 | . 3-31 |

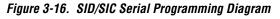

|       | 3.8     | Serial I            | nterface                                                                           | 3-33   |

|       |         | 3.8.1               | Data Transfer on the Serial Interface Bus                                          |        |

| 4.0   | Para    | metric              | Information                                                                        | 4-1    |

|       | 4.1     | DC Elec             | strical Parameters                                                                 | 4-1    |

|       | 4.2     | AC Flee             | trical Parameters                                                                  | 4-4    |

|       | 4.3     |                     | nical Drawing for 80-Pin PQFP                                                      |        |

| Annor | A viba  | Scalin              | g and I/O Timing Register Calculations                                             | ۸_1    |

|       |         |                     |                                                                                    |        |

| Apper | ndix B. | Approv              | ved Crystal Vendors                                                                | B-1    |

| Apper | ndix C. | Autoco              | onfiguration Mode Register Values and Details                                      | C-1    |

| Apper | ndix D. | Closed              | d Caption Pseudo Code                                                              | D-1    |

| Apper | ndix E. | CX258               | 70/871 HDTV Output Mode                                                            | E-1    |

|       | E.1     | Introdu             | ction                                                                              | E-1    |

|       | ·       | E.1.1<br>E.1.2      | Allowable Interfaces for HDTV Output Mode                                          | E-1    |

| E.1.3  | Interface Timing Between the HDTV Source Device (Master) and CX25870/ CX25871 (Timing Slave) E-3    |

|--------|-----------------------------------------------------------------------------------------------------|

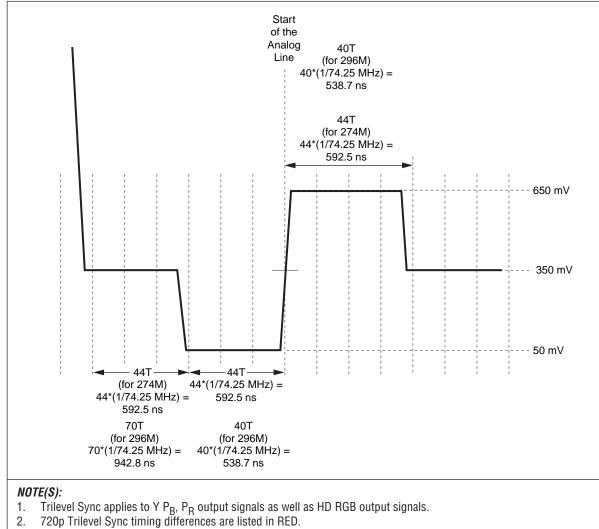

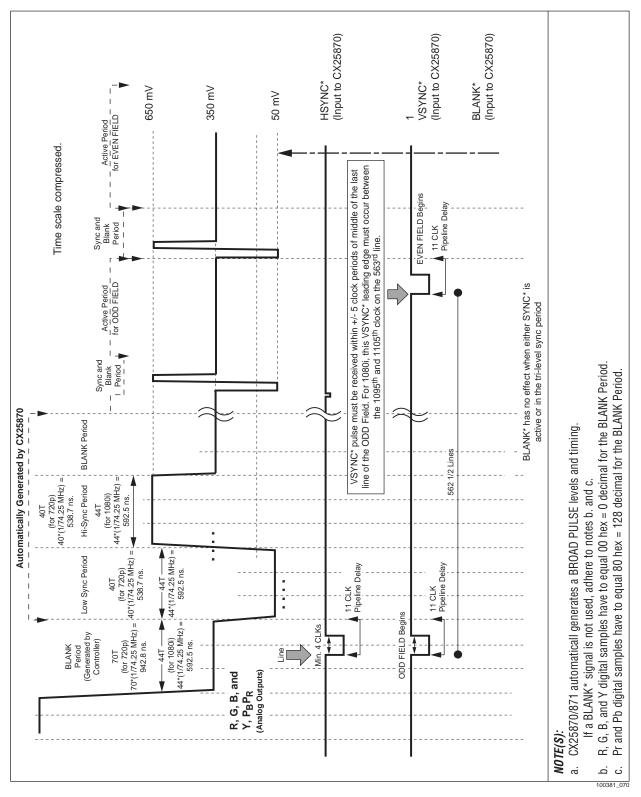

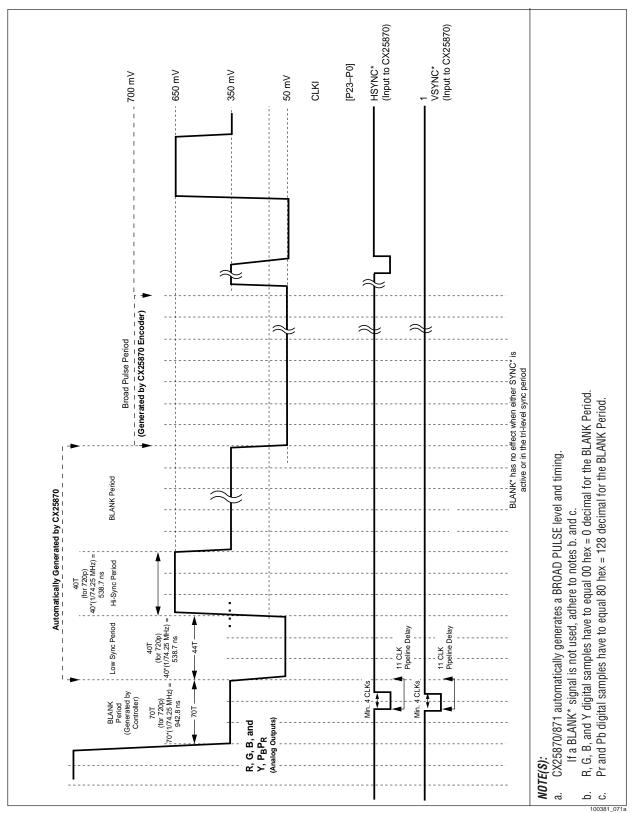

| E.1.4  | Automatic Trilevel Sync Generation E-5                                                              |

| E.1.5  | Allowable Resolutions E-7                                                                           |

| E.1.6  | 720p Support with Character Clock Based Data Masters E-8                                            |

| E.1.7  | Automatic Insertion of Broad Pulses E-9                                                             |

| E.1.8  | HDTV Output Mode Register and Bit Definitions E-9                                                   |

| E.1.9  | Color Space Conversion Functionality to Support Analog RGB or YPBPR Component Video<br>Outputs E-11 |

| E.1.10 | Timing Diagrams for HDTV Output Mode E-11                                                           |

# **List of Figures**

| Figure 1-1.  | Pinout Diagram for CX25870/871 1-1                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

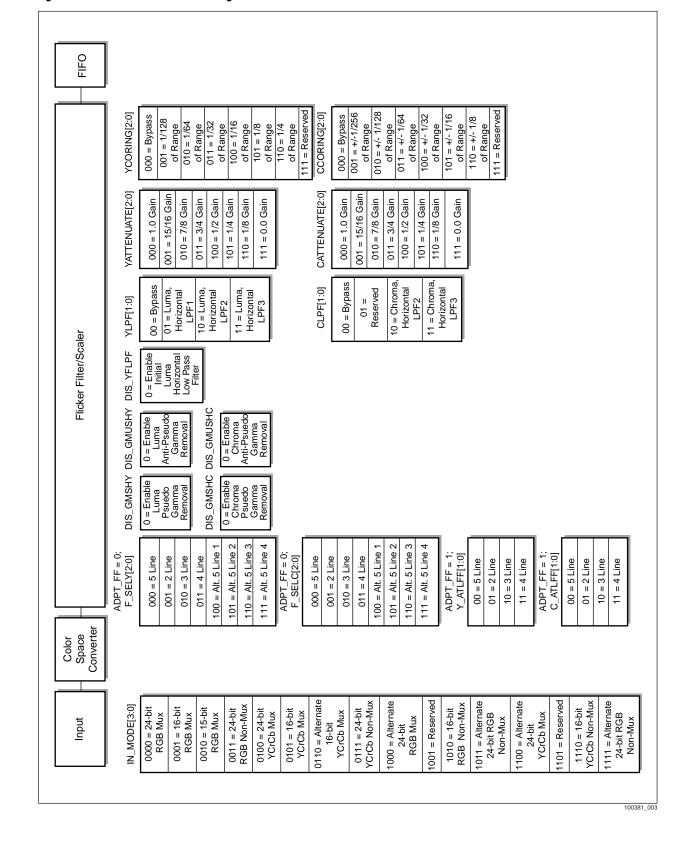

| Figure 1-2.  | Flicker Filter Control Diagram 1-8                                                                                                                           |

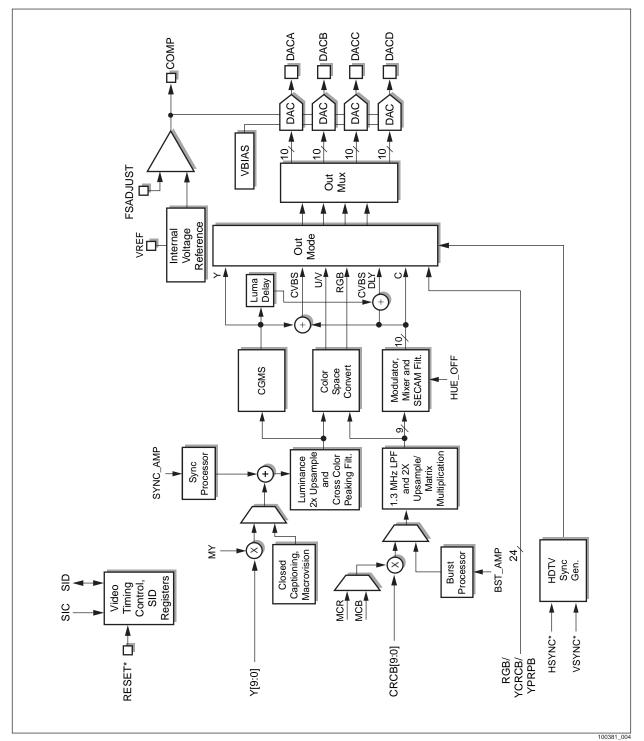

| Figure 1-3.  | CX25870/871 Encoder Core Block Diagram 1-9                                                                                                                   |

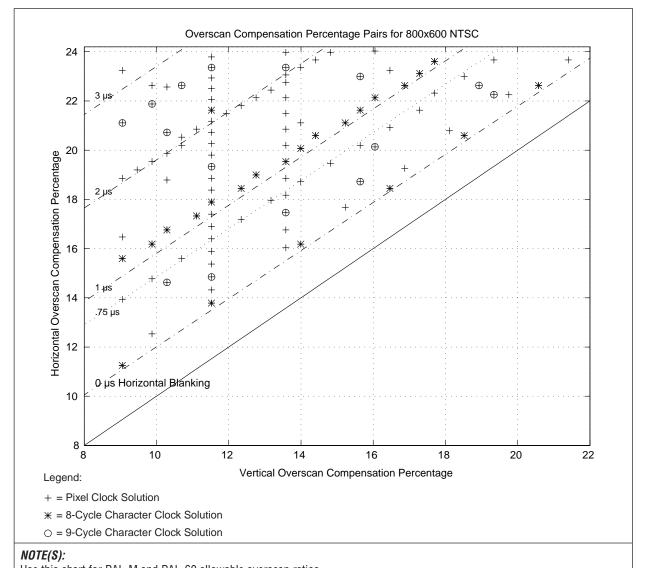

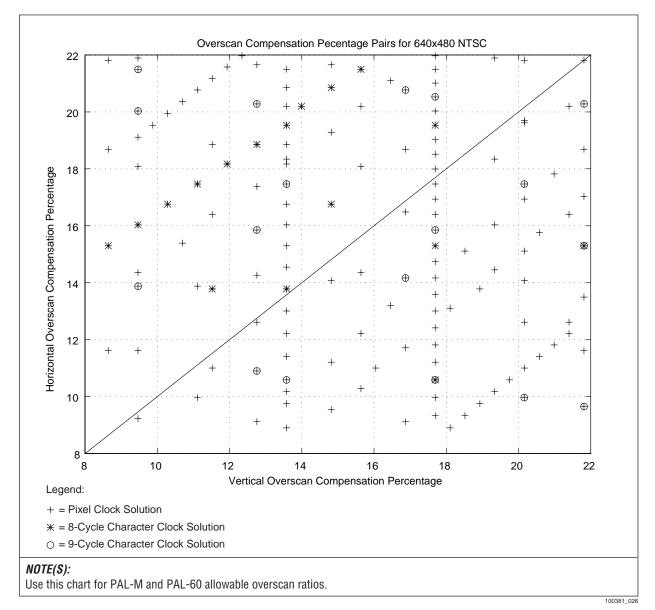

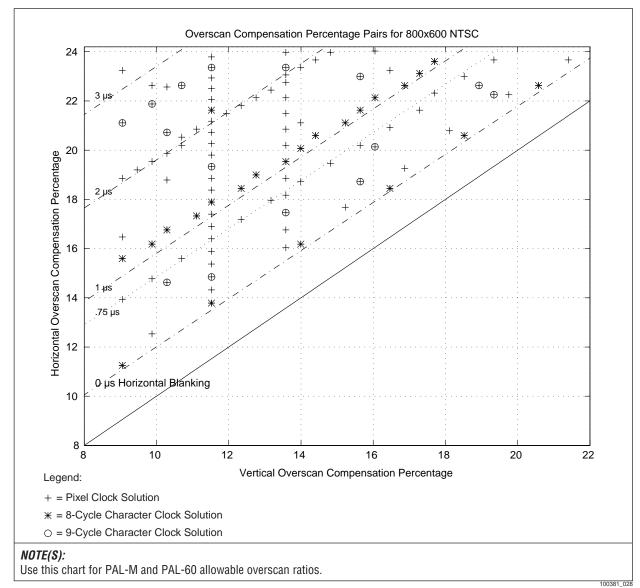

| Figure 1-4.  | Allowable Overscan Compensation Ratios for Dual Display, 800x600 Input/NTSC Output 1-15                                                                      |

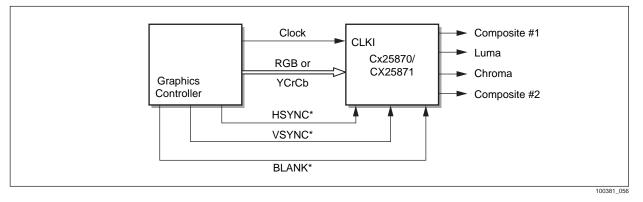

| Figure 1-5.  | Operating the CX25870/871 in Master Interface                                                                                                                |

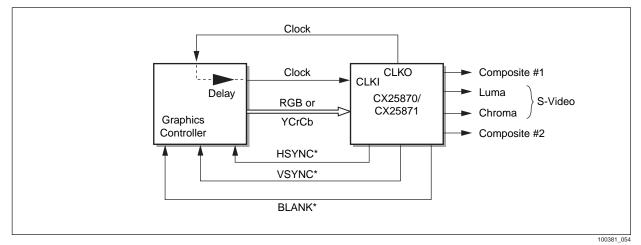

| Figure 1-6.  | Operating the CX25870/871 in Pseudo-Master Interface                                                                                                         |

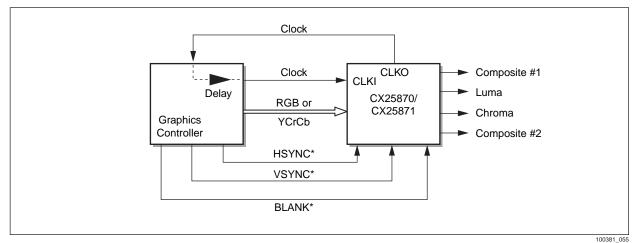

| Figure 1-7.  | Operating the CX25870/871 in Slave Interface                                                                                                                 |

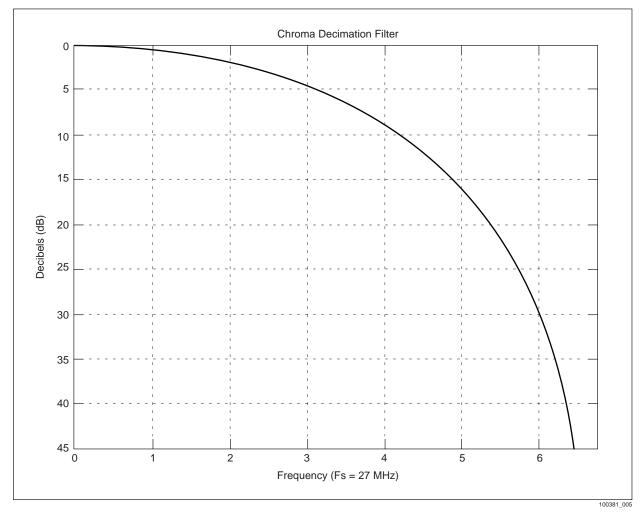

| Figure 1-8.  | Decimation Filter at Fs=27 MHz 1-28                                                                                                                          |

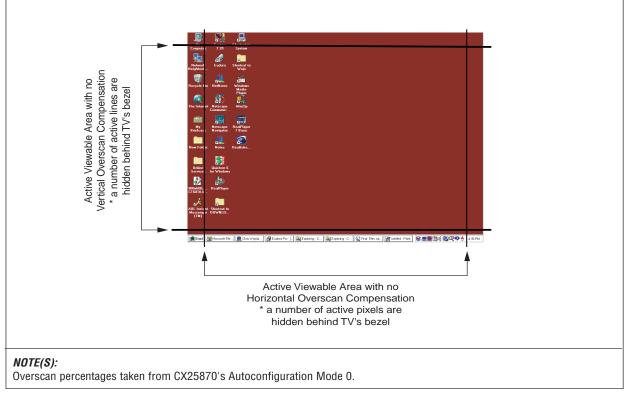

| Figure 1-9.  | Windows Desktop Image From Encoder Without Overscan Compensation 1-33                                                                                        |

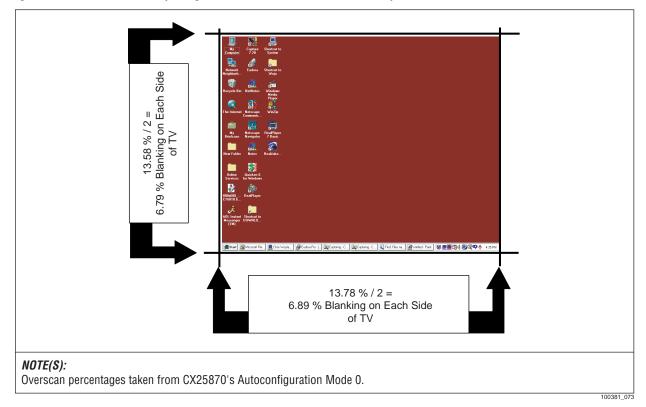

| Figure 1-10. | Windows Desktop Image From CX25870 With Overscan Compensation 1-34                                                                                           |

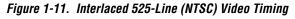

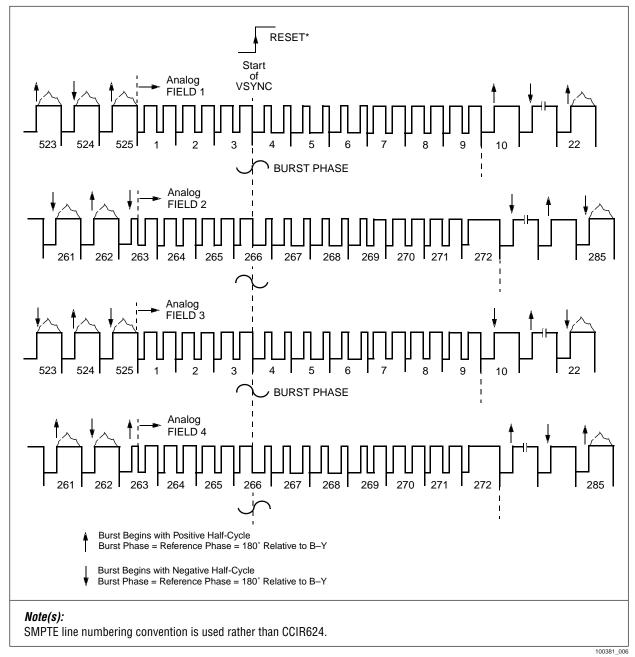

| Figure 1-11. | Interlaced 525-Line (NTSC) Video Timing                                                                                                                      |

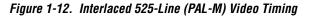

| Figure 1-12. | Interlaced 525-Line (PAL-M) Video Timing                                                                                                                     |

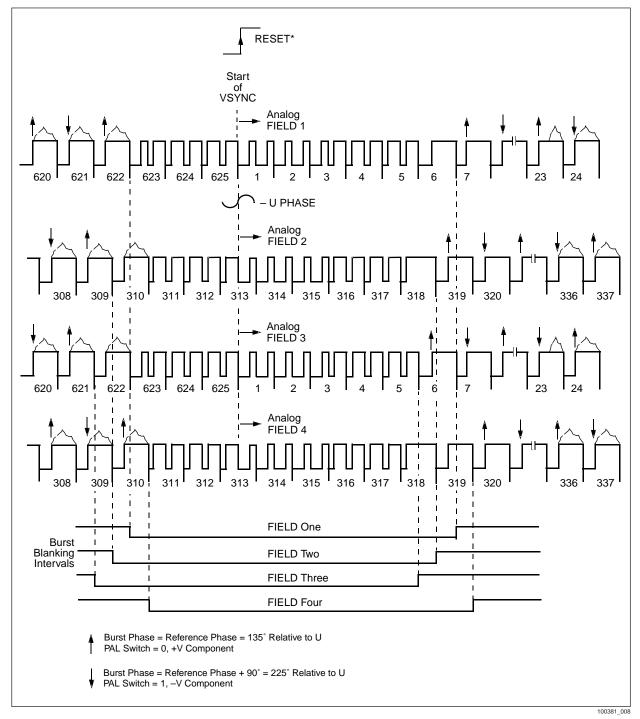

| Figure 1-13. | Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing (Fields 1–4) 1-45                                                                                   |

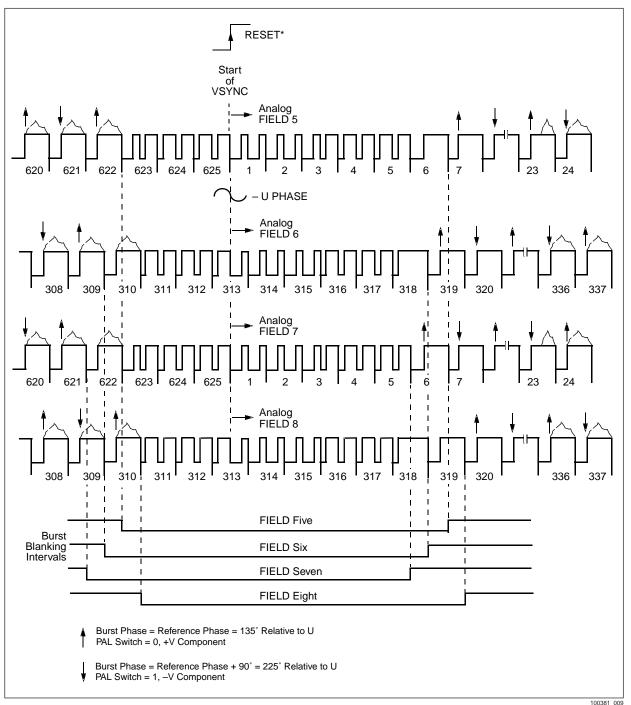

| Figure 1-14. | Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing (Fields 5–8) 1-46                                                                                   |

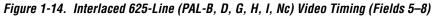

| Figure 1-15. | Interlaced 625-Line (PAL-N) Video Timing (Fields 1–4)                                                                                                        |

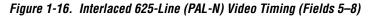

| Figure 1-16. | Interlaced 625-Line (PAL-N) Video Timing (Fields 5–8)                                                                                                        |

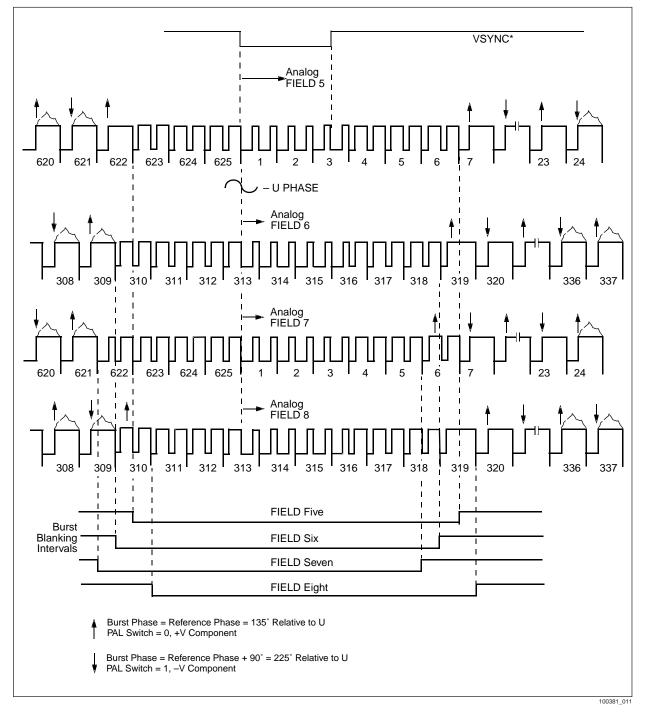

| Figure 1-17. | Noninterlaced 262-Line (NTSC) Video Timing 1-49                                                                                                              |

| Figure 1-18. | Noninterlaced 262-Line (PAL-M) Video Timing                                                                                                                  |

| Figure 1-19. | Noninterlaced 312-Line (PAL-B, D, G, H, I, N, Nc) Video Timing                                                                                               |

| Figure 1-20. | Interlaced 625-Line (SECAM-B, D, G, K, K1, L, M) Video Timing (Fields 1-4) 1-50                                                                              |

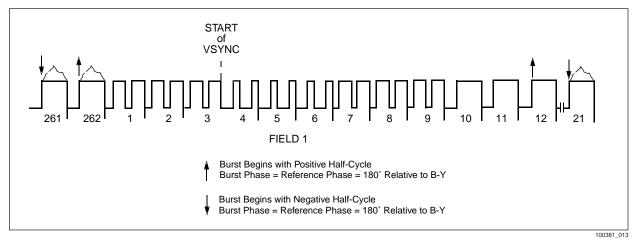

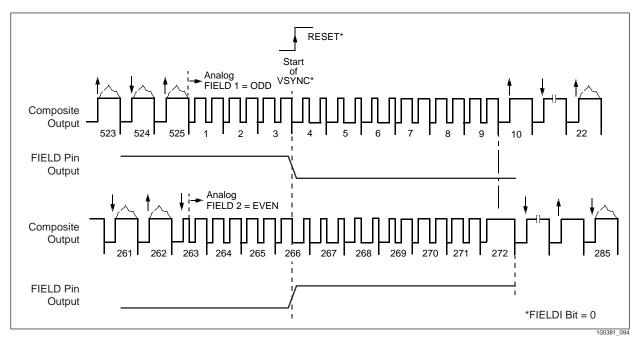

| Figure 1-21. | FIELD Pin Output Timing Diagram (NTSC-M, J, 4.43)1-53                                                                                                        |

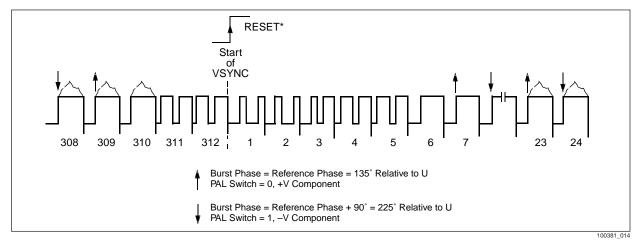

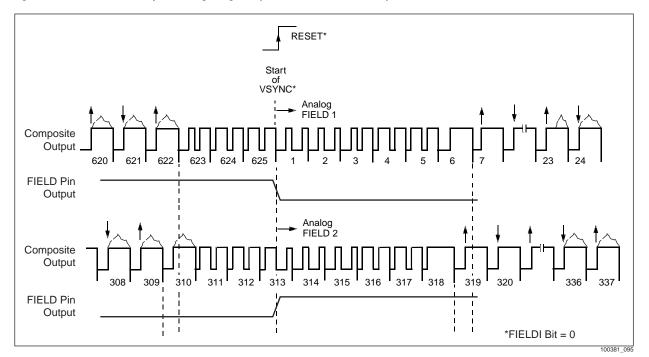

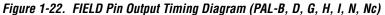

| Figure 1-22. | FIELD Pin Output Timing Diagram (PAL-B, D, G, H, I, Nc)                                                                                                      |

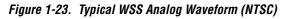

| Figure 1-23. | Typical WSS Analog Waveform (NTSC)                                                                                                                           |

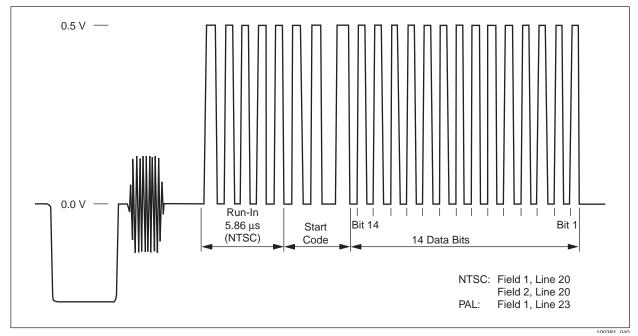

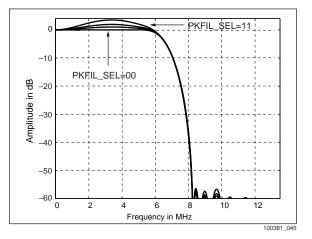

| Figure 1-24. | Luminance Upsampling Filter                                                                                                                                  |

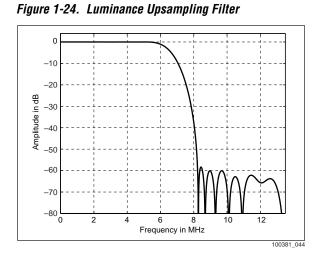

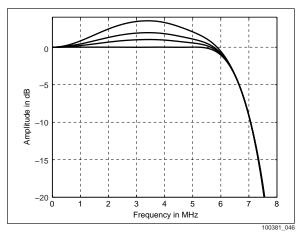

| Figure 1-25. | Text Sharpness (Luminance Upsampling) Filter with Peaking Options                                                                                            |

| Figure 1-26. | Close-Up of Text Sharpness (Luminance Upsampling )Filter with Peaking and Reduction Op-<br>tions 1-59                                                        |

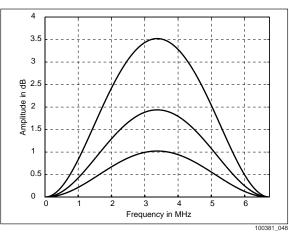

| Figure 1-27. | Text Sharpness (Luminance Peaking) Filter Options                                                                                                            |

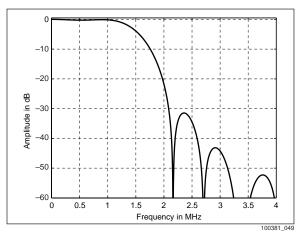

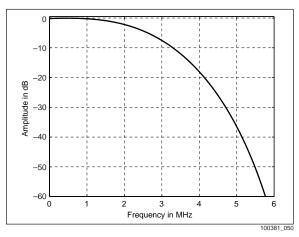

| Figure 1-28. | Chrominance Filter (CHROMA_BW = 0) - default 1-60                                                                                                            |

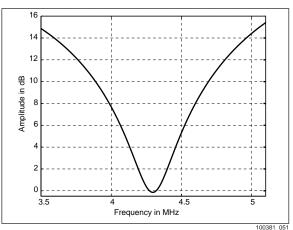

| Figure 1-29. | Chrominance Wide Bandwidth Filter (CHROMA_BW = 1) 1-60                                                                                                       |

| Figure 1-30. | SECAM High Frequency Pre-emphasis Filter                                                                                                                     |

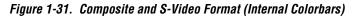

| Figure 1-31. | Composite and S-Video Format (Internal Colorbars)                                                                                                            |

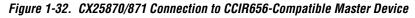

| Figure 1-32. | CX25870/871 Connection to CCIR656-Compatible Master Device                                                                                                   |

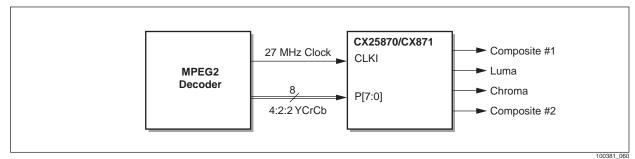

| Figure 1-33. | DVD Playback Utilizing Graphics Controller for Color-Space and Progressive Scan Conversion 1-67                                                              |

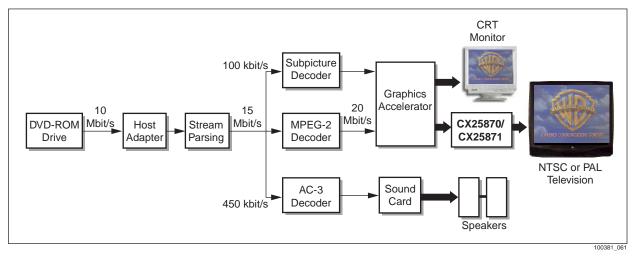

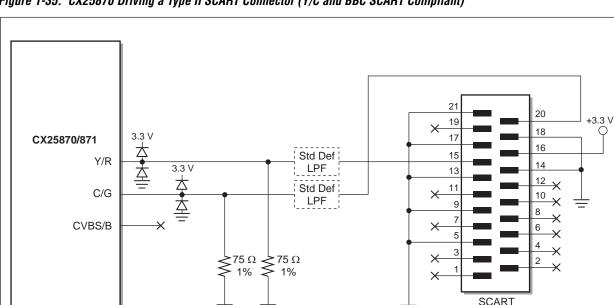

| Figure 1-34. | CX25870 Driving a Type I SCART Connector (EN 50-049 and IEC 933-1 Compliant) 1-78                                                                            |

| Figure 1-35. | CX25870 Driving a Type II SCART Connector (Y/C and BBC SCART Compliant) 1-79                                                                                 |

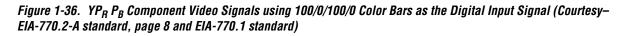

| Figure 1-36. | YPR PB Component Video Signals using 100/0/100/0 Color Bars as the Digital Input Signal (Courtesy– EIA-770.2-A standard, page 8 and EIA-770.1 standard) 1-81 |

| Figure 1-37. | Filterless DAC Outputs for VGA (RGB)—DAC Output Operation                                                                   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

| Figure 3-1.  | Power Plane Illustration                                                                                                    |

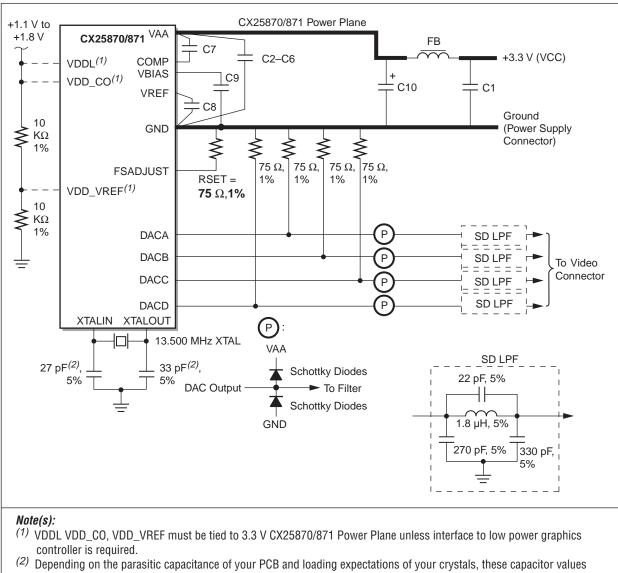

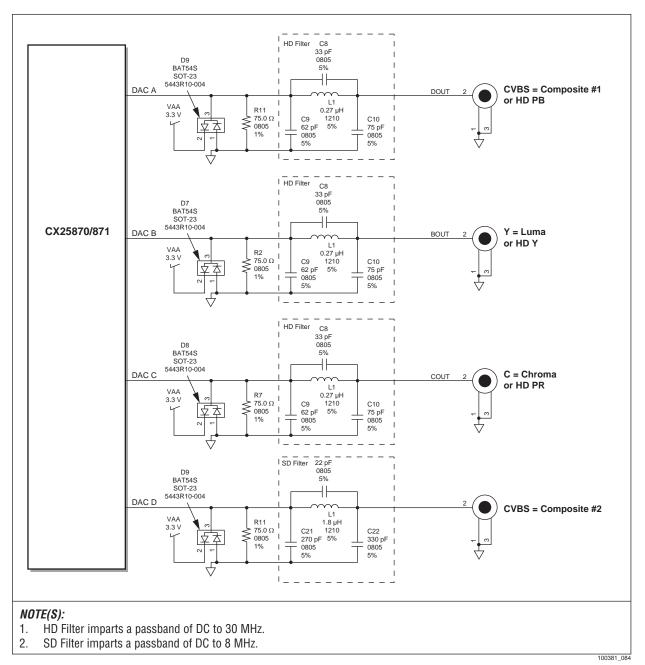

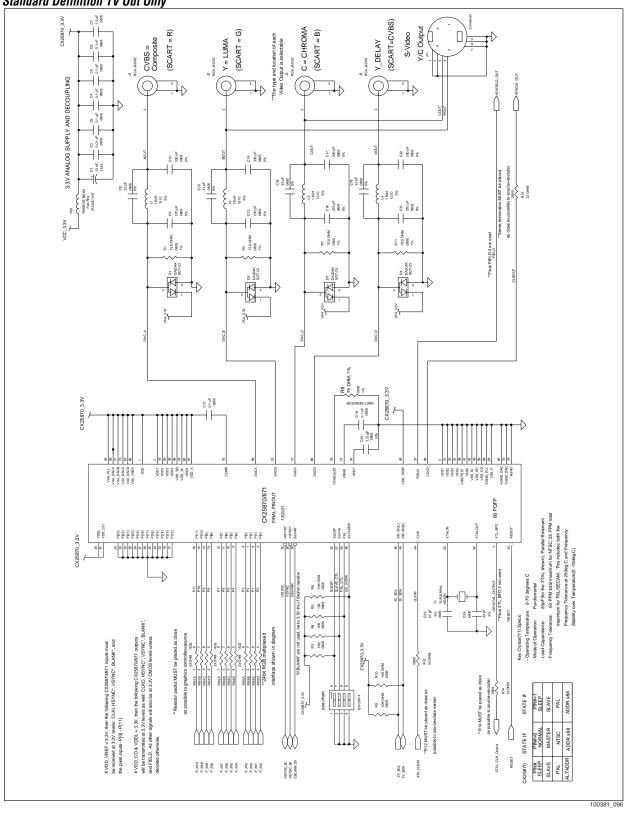

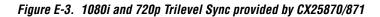

| Figure 3-2.  | Connection Diagram for Output Filters and Other Key Passive Components/Standard Definition TV Out Only 3-3                  |

| Figure 3-3.  | Connection Diagram for Output Filters and Other Key Passive Components/Standard and HDTV<br>Out 3-4                         |

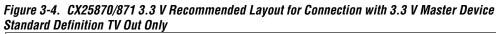

| Figure 3-4.  | CX25870/871 3.3 V Recommended Layout for Connection with 3.3 V Master De-<br>vice Standard Definition TV Out Only 3-6       |

| Figure 3-5.  | CX25870/871 3.3 V/1.8 V Recommended Layout for Connection with 1.8 V Master De-<br>vice Standard Definition TV Out Only 3-7 |

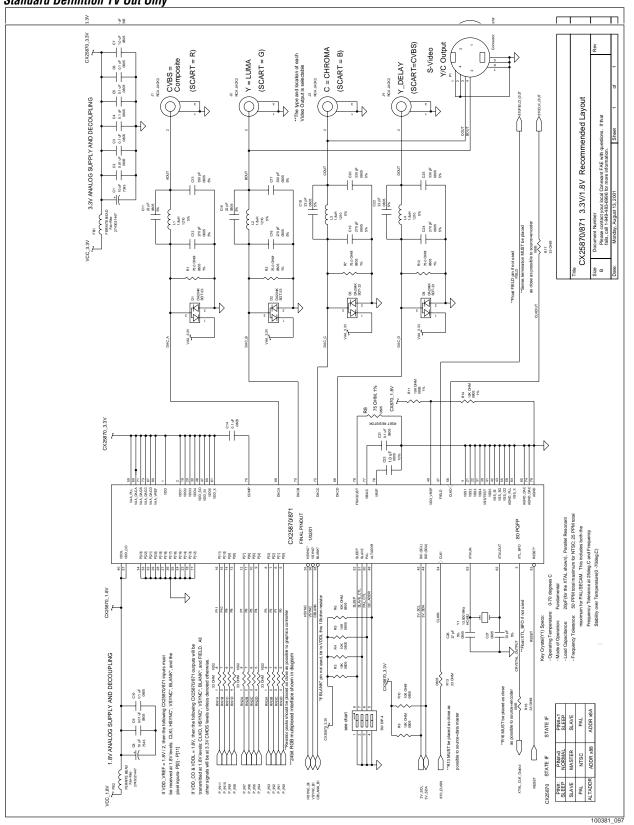

| Figure 3-6.  | Conexant Recommended GUI for CX25870/871                                                                                    |

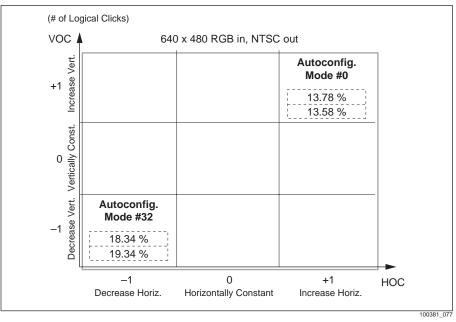

| Figure 3-7.  | CX25870/871 Autoconfiguration Modes for 640x480 RGB in, NTSC Out Desktop Resolutions 3-22                                   |

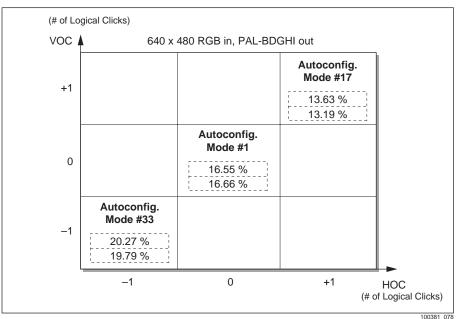

| Figure 3-8.  | CX25870/871 Autoconfiguration Modes for 40x480 RGB In, PAL-BDGHI Out Desktop Resolu-<br>tions 3-22                          |

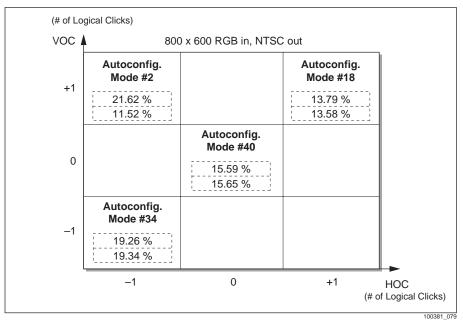

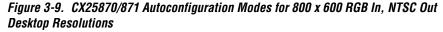

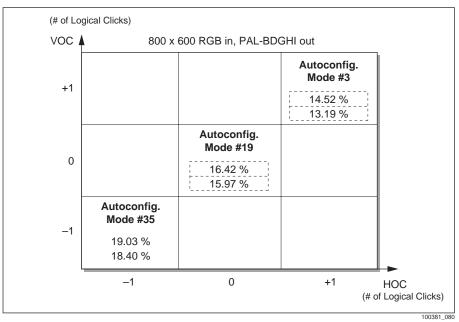

| Figure 3-9.  | CX25870/871 Autoconfiguration Modes for 800 x 600 RGB In, NTSC Out Desktop Resolutions 3-23                                 |

| Figure 3-10. | CX25870/871 Autoconfiguration Modes for 800 x 600 RGB In, PAL-BDGHI Out Desktop Reso-<br>lutions 3-23                       |

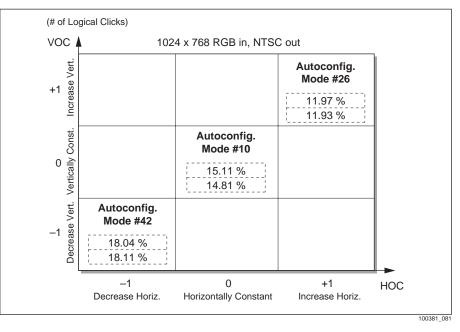

| Figure 3-11. | CX25870/871 Autoconfiguration Modes for 1024 x 768 RGB In, NTSC Out Desktop Resolutions 3-24                                |

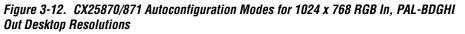

| Figure 3-12. | CX25870/871 Autoconfiguration Modes for 1024 x 768 RGB In, PAL-BDGHI Out Desktop Resolutions 3-24                           |

| Figure 3-13. | Direction-less Size Control Pad                                                                                             |

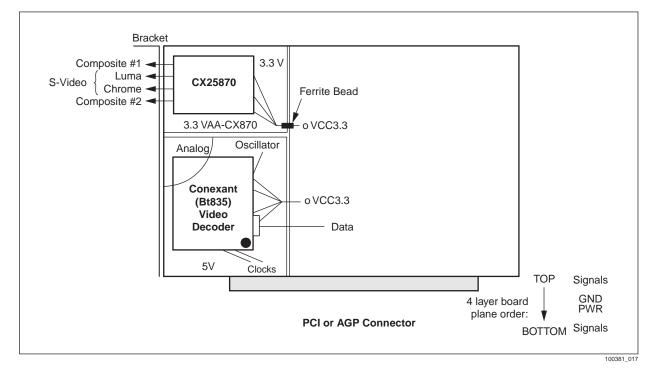

| Figure 3-14. | System Block Diagram for Desktop/Portable PC with TV Out                                                                    |

| Figure 3-15. | System Block Diagram for Graphics Card with TV Out                                                                          |

| Figure 3-16. | SID/SIC Diagram                                                                                                             |

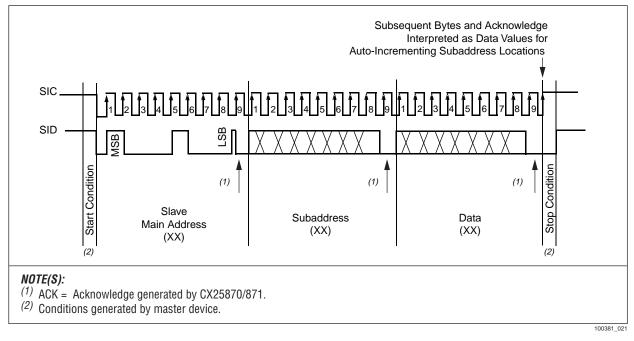

| Figure 4-1.  | Timing Details for All Interfaces                                                                                           |

| Figure 4-2.  | Master Interface Timing Relationship/Noninterlaced RGB/YCrCb Input                                                          |

| Figure 4-3.  | Pseudo-Master Interface Timing Relationship – Active Line/Noninterlaced RGB Input 4-9                                       |

| Figure 4-4.  | Pseudo-Master Timing Relationship Blank Line/Noninterlaced RGB/YCrCb Input 4-10                                             |

| Figure 4-5.  | Slave Interface Timing Relationship/Noninterlaced RGB/YCrCb Input                                                           |

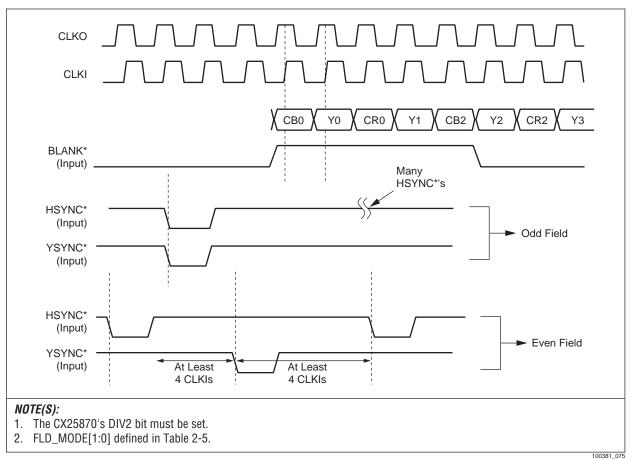

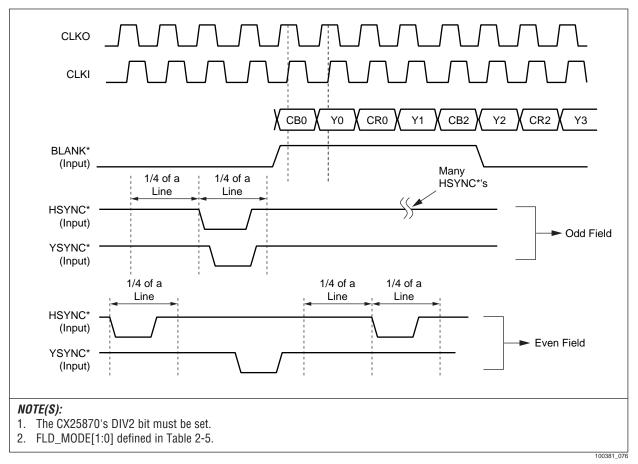

| Figure 4-6.  | Slave Interface Timing Relationship/Interlaced Nonmultiplexed RGB Input (FLD_MODE = 10 – Default) 4-12                      |

| Figure 4-7.  | Slave Interface Timing Relationship/Interlaced Nonmultiplexed YCrCb Input (FLD_MODE = 01) 4-13                              |

| Figure 4-8.  | Slave Interface Timing Relationship/Interlaced Nonmultiplexed YCrCb Input (FLD_MODE = 00)<br>4-14                           |

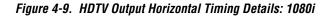

| Figure 4-9.  | HDTV Output Horizontal Timing Details: 1080i                                                                                |

| Figure 4-10. | HDTV Output Horizontal Timing Details: 720p                                                                                 |

| Figure 4-11. | 80-Pin PQFP Package Diagram                                                                                                 |

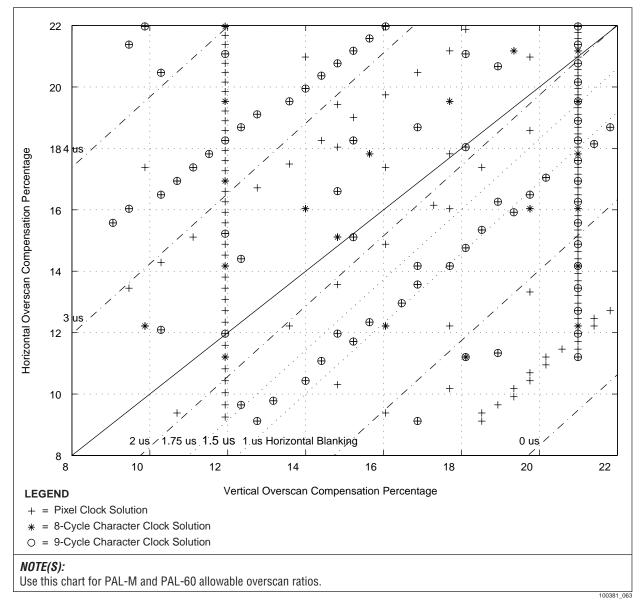

| Figure A-1.  | Allowable Overscan Compensation Ratios for Dual Display, 640x480 Input, NTSC Output with 20 Clock HBlank Period A-4         |

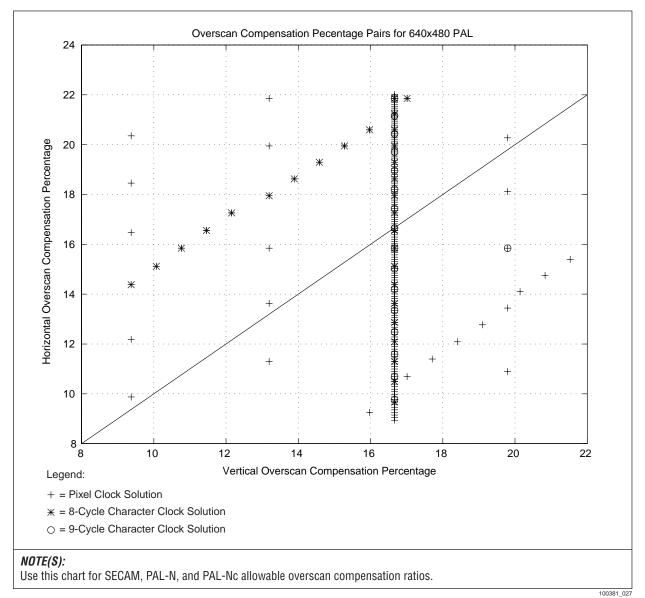

| Figure A-2.  | Allowable Overscan Compensation Ratios for Dual Display, 640x480 Input, PAL-BDGHI Output with 20 Clock HBlank Period A-5    |

| Figure A-3.  | Allowable Overscan Compensation Ratios for Dual Display, 800x600 Input, NTSC Output . A-6                                   |

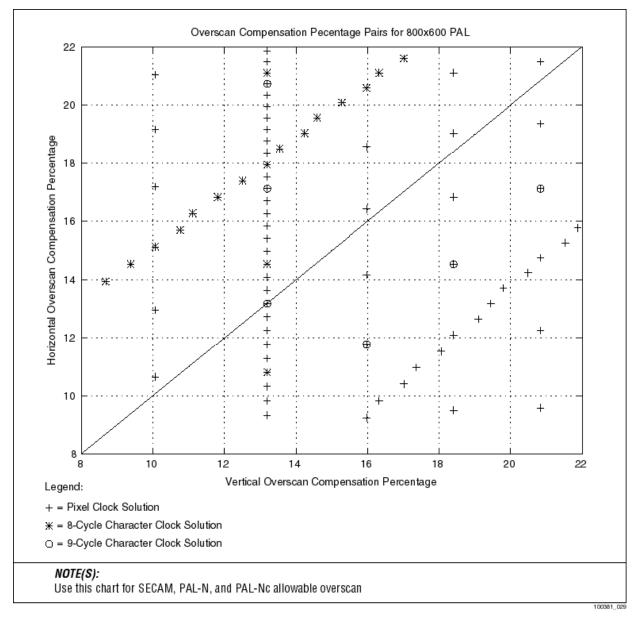

| Figure A-4.  | Allowable Overscan Compensation Ratios for Dual Display, 800x600 Input, PAL–BDGHI Output, Standard Clocking Mode A-7        |

|              |                                                                                                                             |

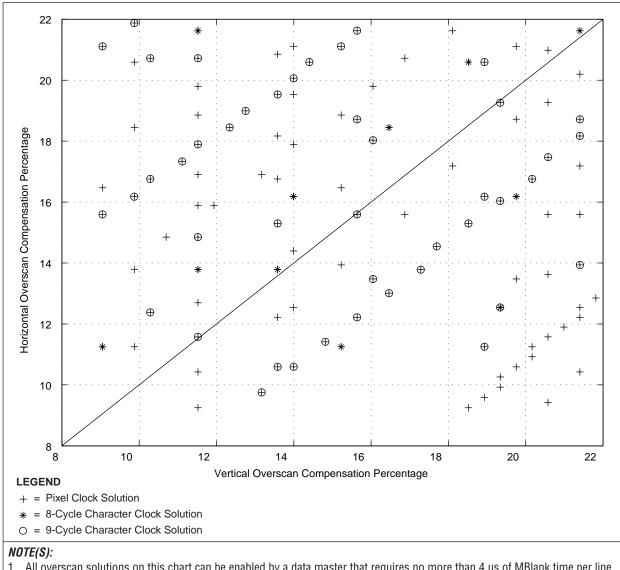

| Figure A-5. | Allowable Overscan Compensation Ratios for Dual Display, 800x600 Input, NTSC Output in 3:2<br>Clocking Mode A-8                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

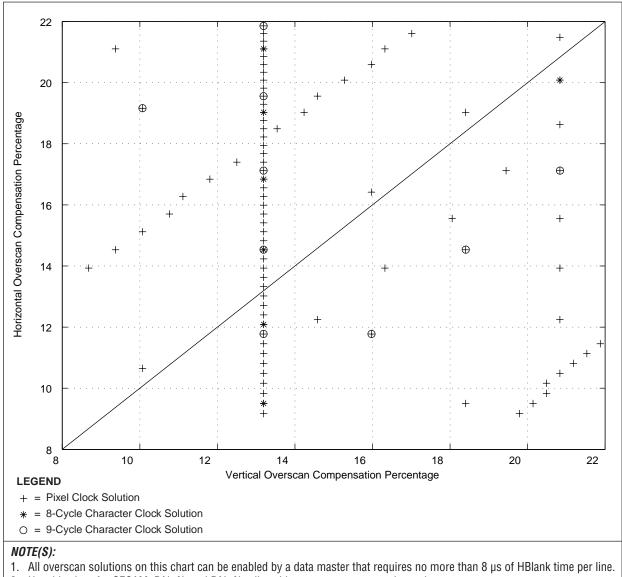

| Figure A-6. | Allowable Overscan Compensation Ratios for Dual Display, 800x600 Input, PAL-BDGHI Output in 3:2 Clocking Mode A-9                                                                                              |

| Figure A-7. | Allowable Overscan Compensation Ratios for Dual Display, 1024x768 Input, NTSC Output<br>A-10                                                                                                                   |

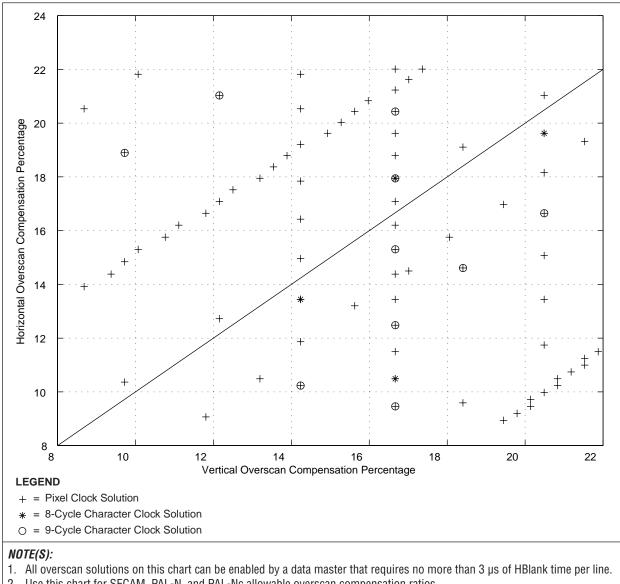

| Figure A-8. | Allowable Overscan Compensation Ratios for Dual Display, 1024x768 Input, PAL-BDGHI Out-<br>put A-11                                                                                                            |

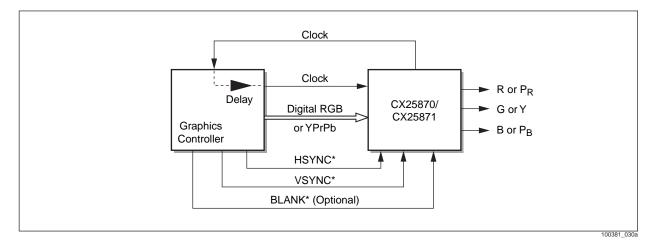

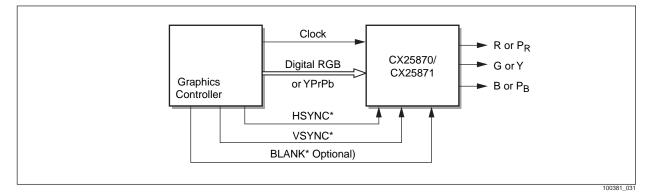

| Figure E-1. | CX25870/871's Pseudo-Master Interface with a Graphics Controller as the Timing Master E-2                                                                                                                      |

| Figure E-2. | CX25870/871's Slave Interface with a Graphics Controller as the Timing Master E-2                                                                                                                              |

| Figure E-3. | Typical Trilevel Sync Provided by CX25870/871 E-7                                                                                                                                                              |

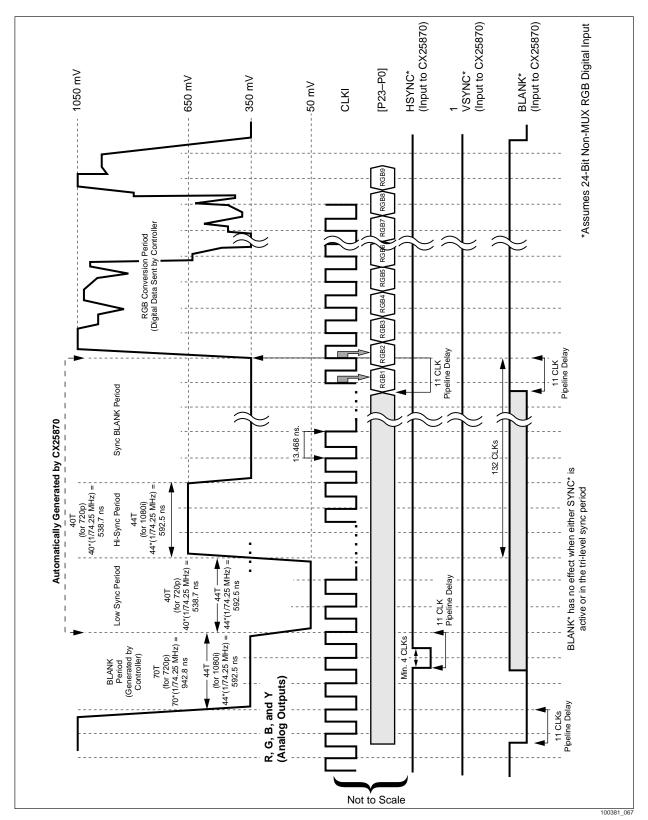

| Figure E-4. | Proper Interface Timing Between the HDTV Source Device (Master) and CX25870/871 (Timing Slave): Active Line in 1080i and 720p ATSC Format (RASTER_SEL[1:0] = 11 or 10), for R, G, B, and Y Analog Outputs E-12 |

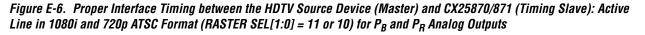

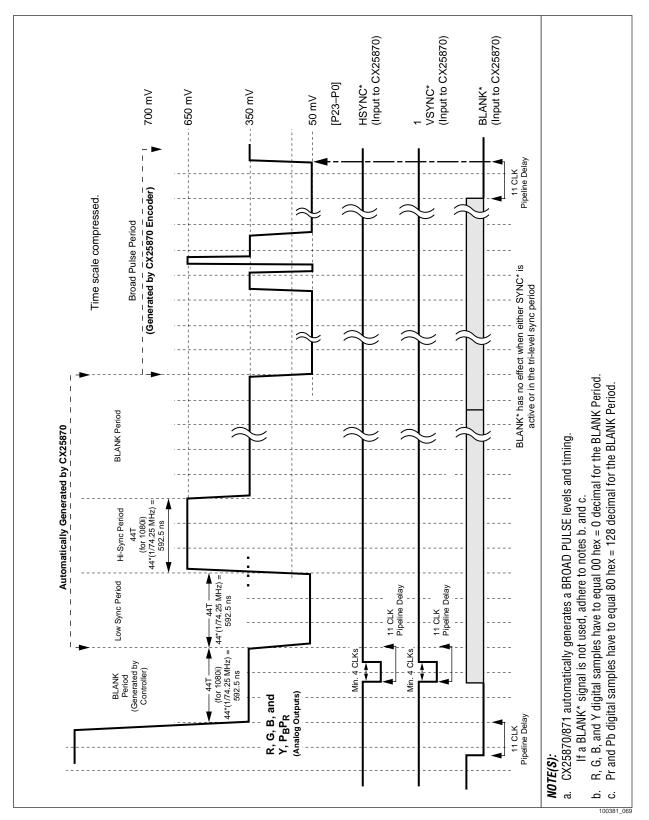

| Figure E-5. | Proper Interface Timing Between the HDTV Source Device (Master) and CX25870/871 (Timing Slave): Active Line in 1080i and 720p ATSC Format (RASTER_SEL[1:0] = 11 or 10) for $P_8$ and $P_R$ Analog Outputs E-13 |

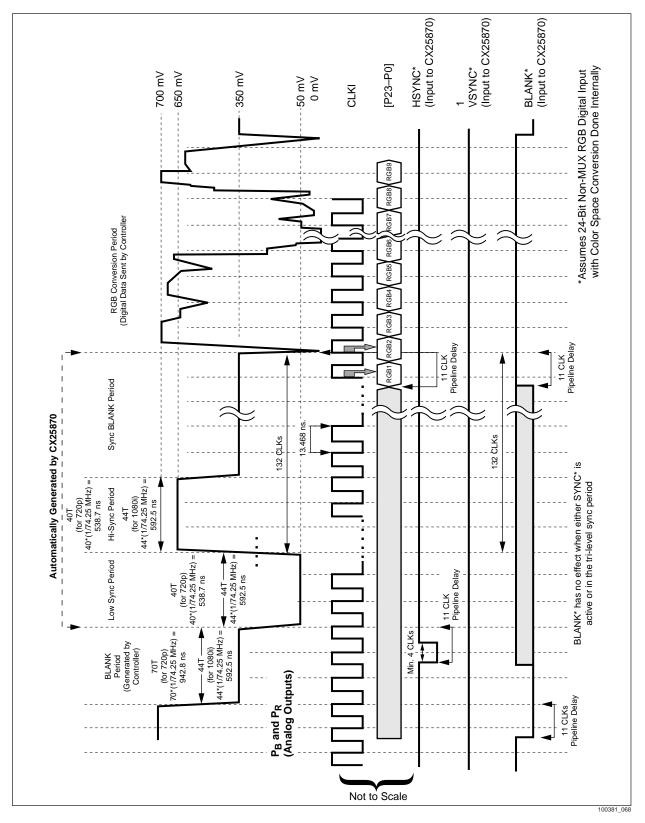

| Figure E-6. | Proper Interface Timing Between the HDTV Source Device (Master) and CX25870/871 (Timing Slave): Broad Pulse Line in 1080i ATSC Format (RASTER_SEL[1:0] = 11) – Odd Field E-14                                  |

| Figure E-7. | Proper Interface Timing Between the HDTV Source Device (Master) and CX25870/871 (Timing Slave): Two Successive Active Fields in 1080i ATSC Format (RASTER_SEL[1:0] = 11) E-15                                  |

| Figure E-8. | Proper Interface Timing Between the HDTV Source Device (Master) and CX25870/871 (Timing Slave): Broad Pulse Line in 720p ATSC Format (RASTER_SEL[1:0] = 10) E-16                                               |

# **List of Tables**

| Table 1-1.  | Pin Assignments                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Table 1-2.  | Data Pin Assignments for Multiplexed Input Formats                                                                           |

| Table 1-3.  | Data Pin Assignments for Nonmultiplexed Input Formats                                                                        |

| Table 1-4.  | Maximum Programmability and Frequency Requirements 1-7                                                                       |

| Table 1-5.  | Autoconfiguration Solutions that Utilize 3:2 Clocking Mode                                                                   |

| Table 1-6.  | Master Interface without a BLANK* Signal (Default Immediately after any Autoconfiguration Command) 1-21                      |

| Table 1-7.  | Master Interface with a BLANK* Input to the CX25870/871 1-22                                                                 |

| Table 1-8.  | Pseudo-Master Interface without a BLANK* Signal                                                                              |

| Table 1-9.  | Pseudo-Master Interface with a BLANK* Input to the CX25870/871 1-23                                                          |

| Table 1-10. | Slave Interface without a BLANK* Signal                                                                                      |

| Table 1-11. | Slave Interface with a BLANK* Input to the CX25870/871 1-24                                                                  |

| Table 1-12. | Adjustment to the CX25870/871 MSC Registers 1-25                                                                             |

| Table 1-13. | Adjustment to the PLL_INT and PLL_FRACT Registers                                                                            |

| Table 1-14. | Summary of Allowable BLANK* Signal Directions by Interface                                                                   |

| Table 1-15. | Optimal Adaptive and Standard Flicker Filter Settings for Common PC Applications 1-38                                        |

| Table 1-16. | VGA/CRTC Registers Involved in TV Out Process                                                                                |

| Table 1-17. | Important Bit Settings for Various Video Outputs                                                                             |

| Table 1-18. | Composite and Luminance Amplitude 1-62                                                                                       |

| Table 1-19. | Composite and Chrominance Magnitude                                                                                          |

| Table 1-20. | Register Values for 640x480 / 800x600 / 1024x768 RGB In, SECAM-L Out 1-69                                                    |

| Table 1-21. | Vital SECAM Bitsettings–Register 0xA2 1-72                                                                                   |

| Table 1-22. | SECAM Specific Registers                                                                                                     |

| Table 1-23. | Serial Writes Required to Switch CX25870/871 into SCART Output Operation 1-76                                                |

| Table 1-24. | Default SCART Outgoing Signal Assignments                                                                                    |

| Table 1-25. | CX25870 SCART Outputs for Different SCART Standards 1-78                                                                     |

| Table 1-26. | Common Registers Required to Switch CX25870/25871 into EIA-770.2-A- or EIA-770.1-Compli-<br>ant Component Video Outputs 1-82 |

| Table 1-27. | Unique Registers Required to Switch CX25870/25871 into EIA-770.2-A- Compliant Component Video Outputs 1-82                   |

| Table 1-28. | Serial Writes Required to Switch CX25870/871 into VGA/DAC Output Operation 1-84                                              |

| Table 1-29. | Serial Writes Required to Remove Bilevel Syncs from all VGA/DAC Outputs 1-85                                                 |

| Table 1-30. | ESTATUS[1:0] Read-back Bit Map 1-88                                                                                          |

| Table 2-1.  | Register Bit Map (* Indicates Read-Only Register) 2-1                                                                        |

| Table 2-2.  | Serial Address Configuration                                                                                                 |

| Table 2-3.  | Bit Map for Read-Only Registers                                                                                              |

| Table 2-4.  | Data Details Defined for Read-Only Registers                                                                                 |

| Table 2-5.  | Programming Detail 2-9                                                                                                       |

| Table 3-1.  | Typical Parts List for Key Passive Components                                                                                |

| Table 3-2.  | Relative Register Map for CX25870/871    3-11                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------|

| Table 3-3.  | Hardware Modifications to Bt868/869-based PCB Required to Accommodate the CX25870/871<br>3-12                     |

| Table 3-4.  | CX25870 Optimal Adaptive Flicker Filter Bit Settings                                                              |

| Table 4-1.  | Recommended Operating Condition                                                                                   |

| Table 4-2.  | Absolute Maximum Rating                                                                                           |

| Table 4-3.  | DC Characteristics for CX25870/871                                                                                |

| Table 4-4.  | AC Characteristics for CX25870/871                                                                                |

| Table A-1.  | Target Video Parameters for Standard Definition TV Output Formats                                                 |

| Table A-2.  | Key Parameters for Supported Standard Definition Video Output Formats A-3                                         |

| Table A-3.  | Constant Values Dependent on Encoding Mode A-3                                                                    |

| Table A-4.  | Overscan Values, 640 x 480 NTSC, Pixel-Based Controller, 1-Pixel Resolution, 2.5 µs HBlank<br>A-12                |

| Table A-5.  | Overscan Values, 640 x 480 NTSC, Character Clock-Based Controller, 8-Pixel Resolution, 2.5 µs HBlank A-14         |

| Table A-6.  | Overscan Values, 640 x 480 NTSC, Character Clock-Based Controller, 9-Pixel Resolution, 2.5 µs HBlank A-15         |

| Table A-7.  | Overscan Values, 640 x 480 PAL-BDGHI, Pixel-Based Controller, 1-Pixel Resolution, 2.5 µs<br>HBlank A-16           |

| Table A-8.  | Overscan Values, 640 x 480 PAL-BDGHI, Character Clock-Based Controller, 8-Pixel Resolution, 2.5 µs HBlank A-19    |

| Table A-9.  | Overscan Values, 640 x 480 PAL-BDGHI, Character Clock-Based Controller, 9-Pixel Resolution, 2.5 µs HBlank A-20    |

| Table A-10. | Overscan Values, 800 x 600 NTSC, Pixel-Based Controller, 1-Pixel Resolution A-21                                  |

| Table A-11. | Overscan Values, 800 x 600 NTSC, Character Clock-Based Controller, 8-Pixel Resolution, 0–1.5<br>µs HBlank A-25    |

| Table A-12. | Overscan Values, 800 x 600 NTSC, Character Clock-Based Controller, 9-Pixel Resolution, 0–3.0<br>µs HBlank A-26    |

| Table A-13. | Overscan Values 800 x 600 NTSC, Pixel-Based Controller, 1-Pixel Resolution, 3:2 Clocking Mode A-27                |

| Table A-14. | Overscan Values 800 x 600 NTSC, Character Clocked-Based Controller, 8-Pixel Resolution, 3:2<br>Clocking Mode A-31 |

| Table A-15. | Overscan Values 800 x 600 NTSC, Character Clocked-Based Controller, 9-Pixel Resolution, 3:2<br>Clocking Mode A-32 |

| Table A-16. | Overscan Values, 800 x 600 PAL-BDGHI, Pixel-Based Controller, 1-Pixel Resolution, >2.5 µs<br>HBlank A-34          |

| Table A-17. | Overscan Values, 800 x 600 PAL-BDGHI, Character Clock-Based Controller, 8-Pixel Resolution A-36                   |

| Table A-18. | Overscan Values, 800 x 600 PAL-BDGHI, Character Clock-Based Controller, 9-Pixel Resolution A-37                   |

| Table A-19. | Overscan Values 800 x 600 PAL-BDGHI, Pixel-Based Controller, 1-Pixel Resolution, 3:2 Clocking<br>Mode A-38        |

| Table A-20. | Overscan Values 800 x 600 PAL-BDGHI, Character Clock-Based Controller, 8-Pixel Resolution, 3:2 Clocking Mode A-41 |

| Table A-21. | Overscan Values 800 x 600 PAL-BDGHI, Character Clock-Based Controller, 9-Pixel Resolution, 3:2 Clocking Mode A-41 |

| Table A-22. | Overscan Values 1024 x 768 NTSC, Pixel-Based Controller, 1-Pixel Resolution, >1.50 ms. Hblank A-42                |

| Table A-23. | Overscan Values 1024 x 768 NTSC, Character Clock-Based Controller, 8Pixel Resolution, >1.50                       |

|             | μs HBlank A-46                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------|

| Table A-24. | Overscan Values 1024 x 768 NTSC, Character Clock-Based Controller, 9-Pixel Resolution A-47              |

| Table A-25. | Overscan Values 1024 x 768 PAL-BDGHI, Pixel-Based Controller, 1-Pixel Resolution, >3 ms.<br>Hblank A-49 |

| Table A-26. | 1024 x 768 PAL-BDGHI, Character Clock-Based Controller, 8-Pixel Resolution , >4 ms. Hblank A-52         |

| Table A-27. | Overscan Values 1024 x 768 PAL-BDGHI, Character Clock-Based Controller, 9-Pixel Resolution<br>A-52      |

| Table C-1.  | CX25870/871 Register Values for Autoconfiguration Modes 0–4 C-1                                         |

| Table C-2.  | CX25870/871 Register Values for Autoconfiguration Modes 5–10                                            |

| Table C-3.  | CX25870/871 Register Values for Autoconfiguration Modes 11–15 C-6                                       |

| Table C-4.  | CX25870/871 Register Values for Autoconfiguration Modes 16–21 C-8                                       |

| Table C-5.  | CX25870/871 Register Values for Autoconfiguration Modes 22–26 C-10                                      |

| Table C-6.  | CX25870/871 Register Values for Autoconfiguration Modes 27–30 C-12                                      |

| Table C-7.  | CX25870/871 Register Values for Autoconfiguration Modes 31–36 C-14                                      |

| Table C-8.  | CX25870/871 Register Values for Autoconfiguration Modes 37–42 C-16                                      |

| Table C-9.  | CX25870/871 Register Values for Autoconfiguration Modes 43–47 C-18                                      |

| Table E-1.  | CX25870 Register Settings for 24-Bit RGB Multiplexed In, Y/P <sub>R</sub> /P <sub>B</sub> HDTV Out E-4  |

| Table E-2.  | Default State of CX25870/871 Immediately After Switch into HDTV Output Mode E-5                         |

| Table E-3.  | CX25870/871 RASTER_SEL[1:0] bit functionality E-6                                                       |

| Table E-4.  | CX25870/871 HDTV Supported Formats E-7                                                                  |

| Table E-5.  | Register Bit Map for HDTV-specific registers E-9                                                        |

| Table E-6.  | CX25870/871 Registers 0x2E & 0x32 – HDTV Output Mode Bit Descriptions E-10                              |

# **1.0 Functional Description**

# 1.1 Pin Descriptions

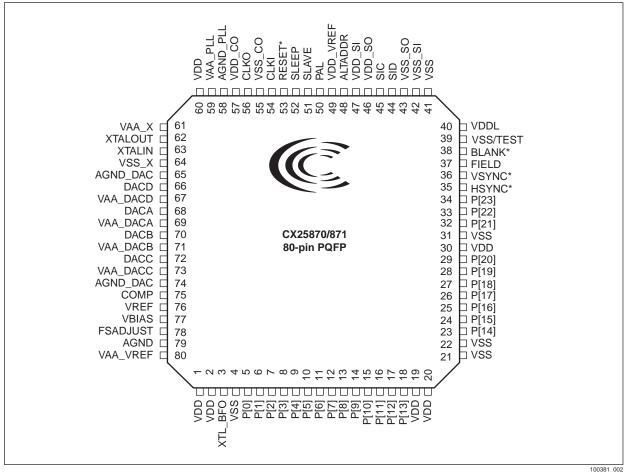

The pinout diagram is illustrated in Figure 1-1. Pin names, input/output assignments, numbers, and descriptions are listed in Tables 1-1, 1-2, and 1-3.

Figure 1-1. Pinout Diagram for CX25870/871

Flicker-Free Video Encoder with Ultrascale Technology

Aside from pins 2, 3, 65, 66, and 67, which are no connects within the Bt868/869, the CX25870/871 is completely pin-to-pin compatible with Conexant's first generation VGA encoder.

| Table 1-1. | Pin Assignments | (1 of 3) |

|------------|-----------------|----------|

|------------|-----------------|----------|

| Pin Name | I/O | Pin #  | Description                                                                                                                                                                                                       |

|----------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAA_VREF | —   | 80     | Analog power. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                           |

| AGND     | —   | 79     | Analog ground. All AGND and VSS pins must be connected together on the same PCB plane to prevent latchup.                                                                                                         |

| FSADJUST | I   | 78     | Full-scale adjust control pin. A resistor (RSET) connected between this pin and GND controls the full-scale output current on the analog outputs.                                                                 |

| VBIAS    | 0   | 77     | DAC bias voltage. A 0.1 $\mu F$ ceramic capacitor must be used to bypass this pin to GND. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                   |

| VREF     | 0   | 76     | Voltage reference pin. A 1.0 $\mu F$ ceramic capacitor must be used to decouple this pin to GND. The decoupling capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum. |

| СОМР     | 0   | 75     | Compensation pin. A 0.1 $\mu F$ ceramic capacitor must be used to bypass this pin to VAA. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                   |

| VAA_DACC | _   | 73     | DACC Analog power. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                      |

| DACC     | 0   | 72     | DACC Analog output.                                                                                                                                                                                               |

| VAA_DACB | _   | 71     | DACB Analog power. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                      |

| DACB     | 0   | 70     | DACB Analog output.                                                                                                                                                                                               |

| VAA_DACA | —   | 69     | DACA Analog power. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                      |

| DACA     | 0   | 68     | DACA Analog output.                                                                                                                                                                                               |

| VAA_DACD | _   | 67     | DACD analog power. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                      |

| DACD     | 0   | 66     | DACD analog output. If unused, DACD should be left as a no connect.                                                                                                                                               |

| AGND_DAC | _   | 65, 74 | Common DAC Analog ground return. All AGND and VSS pins must be connected together on the same PCB plane to prevent latchup.                                                                                       |

| VSS_X    | _   | 64     | Crystal oscillator ground pin. This pin should be tied to the ground plane.                                                                                                                                       |

| XTALIN   | I   | 63     | A crystal can be connected to these pins. The pixel clock output (CLKO) is                                                                                                                                        |

| XTALOUT  | 0   | 62     | derived from these pins with a PLL. XTALIN can be driven as a CMOS input pin.<br>Internally, this is a CMOS inverter tying XTALOUT to XTALIN. If XTALOUT is<br>unused, it should be left as a no connect.         |

| VDD_X    | —   | 61     | Crystal oscillator supply pin. This pin should be tied to the power supply.                                                                                                                                       |

| VAA_PLL  | -   | 59     | Analog power for PLL. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                   |

| AGND_PLL |     | 58     | Analog ground for PLL. All AGND and VSS pins must be connected together on the same PCB plane to prevent latchup.                                                                                                 |

**1.0 Functional Description**

1.1 Pin Descriptions

| Table 1-1. | Pin Assignments | (2 of 3) |

|------------|-----------------|----------|

|------------|-----------------|----------|

| Pin Name | I/O | Pin # | Description                                                                                                                                                                                                                                                                                                              |  |

|----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD_CO   | -   | 57    | Clock output supply pin. This pin should be tied to the power supply. For low voltage infacing this pin should be tied to the low voltage supply.                                                                                                                                                                        |  |

| CLKO     | 0   | 56    | Pixel clock output (TTL compatible). This pin is three-state if the CLKI pin provides the encoder clock.                                                                                                                                                                                                                 |  |

| VSS_CO   | —   | 55    | Clock output ground pin. This pin should be tied to the ground plane.                                                                                                                                                                                                                                                    |  |

| CLKI     | Ι   | 54    | Pixel clock input (TTL compatible). This may be used as either the encoder clock or a delayed version of the CLKO pin synchronized with the pixel data input.                                                                                                                                                            |  |

| RESET*   | I   | 53    | Reset control input (TTL compatible). A logical 0 applied for a minimum of 20 CLKI clock cycles resets and disables video timing (horizontal, vertical, subcarrier counters) to the start of VSYNC of the first field and resets the serial interface registers. RESET* must be a logical 1(3.3 V) for normal operation. |  |

| SLEEP    | I   | 52    | Power-down control input (TTL compatible). A logical 1 configures the device for power-down mode. A logical 0 configures the device for normal operation.                                                                                                                                                                |  |

| SLAVE    | I   | 51    | Slave/master mode select input (TTL compatible). A logical 1 configures the device for slave video timing operation. A logical 0 configures the device for master video timing operation.                                                                                                                                |  |

| PAL      | I   | 50    | PAL/NTSC mode select input (TTL compatible). A logical 1 configures the device for PAL video format and Autoconfiguration Mode 1. A logical 0 configures the device for NTSC video format and Autoconfiguration Mode 0.                                                                                                  |  |

| VDD_VREF | I   | 49    | Input threshold adjustment. This pin should be tied to VDD for 3.3 V input swings or VDDL/2 for low voltage input swings.                                                                                                                                                                                                |  |

| ALTADDR  | I   | 48    | Alternate slave address input (TTL compatible). A logical 0 configures the device to respond to a serial write address of 0x88. A logical 1 configures the device to respond to a serial write address of 0x8A. In addition, serial reads address 0x89 (ALTADDR = 0) or 0x8B (ALTADDR = 1) are possible with this        |  |

| VDD_SI   | _   | 47    | Serial interface input supply pin. This pin should be tied to VDD (3.3 V).                                                                                                                                                                                                                                               |  |

| VDD_S0   | _   | 46    | Serial interface output supply pin. This pin should be tied to VDD (3.3 V).                                                                                                                                                                                                                                              |  |

| SIC      | I   | 45    | Serial interface clock input (TTL compatible).                                                                                                                                                                                                                                                                           |  |

| SID      | I/O | 44    | Serial interface data input/output (TTL compatible). Data is written to and read from the device via this serial bus.                                                                                                                                                                                                    |  |

| VSS_SO   | _   | 43    | Serial interface input ground pin. This pin should be tied to the ground plane.                                                                                                                                                                                                                                          |  |

| VSS_SI   | _   | 42    | Serial interface input ground pin. This pin should be tied to the ground plane.                                                                                                                                                                                                                                          |  |

| VDDL     | —   | 40    | Digital power for low voltage interface. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup. For a low voltage interface, this pin should be tied to the low voltage supply.                                                                                                       |  |

| VSS/TEST | Ι   | 39    | Test pin. Should be tied to VSS for normal operation.                                                                                                                                                                                                                                                                    |  |

| BLANK*   | 1/0 | 38    | Composite blanking control (TTL compatible). This can be generated by the encoder or supplied from the graphics controller. If internal blanking is used, this pin can be used to indicate the control character clock edge. If unused, BLANK* should be tied high through a 10 k $\Omega$ pullup resistor.              |  |

| Pin Name | I/O | Pin #                      | Description                                                                                                                                                                                                                                                                                       |  |

|----------|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FIELD    | 0   | 37                         | Field control output (TTL compatible). FIELD transitions after the rising edge of CLK, two clock cycles following falling HSYNC*. It is a logical 0 during odd fields and is a logical 1 during even fields. If unused, FIELD should be left as a no connect.                                     |  |

| VSYNC*   | I/O | 36                         | Vertical sync input/output (TTL compatible). As an output (timing master operation), VSYNC* is output following the rising edge of CLK. As an input (timing slave operation), VSYNC* is clocked on the rising edge of CLK.                                                                        |  |

| HSYNC*   | I/O | 35                         | Horizontal sync input/output (TTL compatible). As an output (timing master operation), HSYNC* is output following the rising edge of CLK. As an input (timing slave operation), HSYNC* is clocked on the rising edge of CLK.                                                                      |  |

| P[23:21] | I   | 34-32                      | Pixel inputs. See Table 1-2. The input data is sampled on both the rising and                                                                                                                                                                                                                     |  |

| P[20:14] | 1   | 29-23                      | falling edge of CLK for multiplexed modes, and on the rising edge of CLK in<br>nonmultiplexed modes. A higher bit index corresponds to a greater bit                                                                                                                                              |  |

| P[13:0]  | Ι   | 18-5                       | significance.                                                                                                                                                                                                                                                                                     |  |

| VSS      | -   | 4, 21, 22,<br>31, 41       | Digital ground for core logic. All AGND and VSS pins must be connected together on the same PCB plane to prevent latchup.                                                                                                                                                                         |  |

| XTL_BFO  | 0   | 3                          | Buffered crystal clock output. On power-up, the encoder will transmit a 0 to 3.3 V signal at a frequency equal to the frequency of the crystal found between the XTALIN/XTALOUT ports. Normally the XTL_BFO output is at a rate of 13.500 MHz. If unused, XTL_BFO should be left as a no connect. |  |

| VDD      | _   | 1, 2, 19,<br>20, 30,<br>60 | Digital power for core logic. All VAA and VDD pins must be connected together on the same PCB plane to prevent latchup.                                                                                                                                                                           |  |

Flicker-Free Video Encoder with Ultrascale Technology

|             |                    |                       | Falling Ed              | ge of CLKI              |                                 |                                      |                                      |

|-------------|--------------------|-----------------------|-------------------------|-------------------------|---------------------------------|--------------------------------------|--------------------------------------|

| N_MODE[3:0] | 0000               | 0010/0001             | 0101                    | 0100                    | 1000                            | 0110                                 | 1100                                 |

| Pin         | 24-bit<br>RGB Mode | 15/16-bit<br>RGB Mode | 16-bit<br>YCrCb<br>Mode | 24-bit<br>YCrCb<br>Mode | Alternate<br>24-bit RGB<br>Mode | Alternate<br>16-bit<br>YCrCb<br>Mode | Alternate<br>24-bit<br>YCrCb<br>Mode |

| P[11]       | R7                 | R4                    | Y7                      | ¥7                      | R7                              | _                                    | Cr7                                  |

| P[10]       | R6                 | R3                    | Y6                      | Y6                      | R6                              | _                                    | Cr6                                  |

| P[9]        | R5                 | R2                    | Y5                      | Y5                      | R5                              | _                                    | Cr5                                  |

| P[8]        | R4                 | R1                    | Y4                      | Y4                      | R4                              | _                                    | Cr4                                  |

| P[7]        | R3                 | R0                    | Y3                      | Y3                      | R3                              | Y7                                   | Cr3                                  |

| P[6]        | G7                 | G5 <sup>(1)</sup>     | Y2                      | Y2                      | R2                              | Y6                                   | Cr2                                  |

| P[5]        | G6                 | G4                    | Y1                      | Y1                      | R1                              | Y5                                   | Cr1                                  |

| P[4]        | G5                 | G3                    | Y0                      | Y0                      | R0                              | Y4                                   | Cr0                                  |

| P[3]        | R2                 | —                     | _                       | Cb3                     | G7                              | Y3                                   | ¥7                                   |

| P[2]        | R1                 | —                     | _                       | Cb2                     | G6                              | Y2                                   | Y6                                   |

| P[1]        | R0                 | _                     | _                       | Cb1                     | G5                              | Y1                                   | Y5                                   |

| P[0]        | G1                 | —                     | _                       | Cb0                     | G4                              | Y0                                   | Y4                                   |

|             |                    |                       | Rising Ed               | ge of CLKI              |                                 |                                      |                                      |

| P[11]       | G4                 | G2                    | Cr/Cb7                  | Cr7                     | G3                              | _                                    | Y3                                   |

| P[10]       | G3                 | G1                    | Cr/Cb6                  | Cr6                     | G2                              |                                      | Y2                                   |

| P[9]        | G2                 | GO                    | Cr/Cb5                  | Cr5                     | G1                              | _                                    | Y1                                   |

| P[8]        | B7                 | B4                    | Cr/Cb4                  | Cr4                     | GO                              | _                                    | Y0                                   |

| P[7]        | B6                 | B3                    | Cr/Cb3                  | Cr3                     | B7                              | Cr/Cb7                               | Cb7                                  |

| P[6]        | B5                 | B2                    | Cr/Cb2                  | Cr2                     | B6                              | Cr/Cb6                               | Cb6                                  |

| P[5]        | B4                 | B1                    | Cr/Cb1                  | Cr1                     | B5                              | Cr/Cb5                               | Cb5                                  |

| P[4]        | B3                 | BO                    | Cr/Cb0                  | Cr0                     | B4                              | Cr/Cb4                               | Cb4                                  |

| P[3]        | GO                 | —                     | _                       | Cb7                     | B3                              | Cr/Cb3                               | Cb3                                  |

| P[2]        | B2                 | _                     | _                       | Cb6                     | B2                              | Cr/Cb2                               | Cb2                                  |

| P[1]        | B1                 | —                     | _                       | Cb5                     | B1                              | Cr/Cb1                               | Cb1                                  |

| P[0]        | BO                 |                       | _                       | Cb4                     | BO                              | Cr/Cb0                               | Cb0                                  |

## Table 1-2. Data Pin Assignments for Multiplexed Input Formats

<sup>(1)</sup> G5 is ignored in 15-bit RGB Multiplexed Input Mode.

| IN_MODE[3:0] | 1010                 | 1110                      | 0011                 | 0111                      | 1011                              | 1111                                   |

|--------------|----------------------|---------------------------|----------------------|---------------------------|-----------------------------------|----------------------------------------|

| Pin          | 16-bit<br>nonmux RGB | 16-bit<br>nonmux<br>YCrCb | 24-bit<br>nonmux RGB | 24-bit<br>nonmux<br>YCrCb | Alternate<br>16-bit<br>nonmux RGB | Alternate<br>24-bit<br>nonmux<br>YCrCb |

| P[23]        | —                    | _                         | B7                   | Cb7                       | R7                                | Cr7                                    |

| P[22]        | _                    |                           | B6                   | Cb6                       | R6                                | Cr6                                    |

| P[21]        | —                    | —                         | B5                   | Cb5                       | R5                                | Cr5                                    |

| P[20]        | —                    | _                         | B4                   | Cb4                       | R4                                | Cr4                                    |

| P[19]        | R4                   | Y7                        | B3                   | Cb2                       | R3                                | Cr3                                    |

| P[18]        | R3                   | Y6                        | B2                   | Cb2                       | R2                                | Cr2                                    |

| P[17]        | R2                   | Y5                        | B1                   | Cb1                       | R1                                | Cr1                                    |

| P[16]        | R1                   | Y4                        | BO                   | Cb0                       | R0                                | Cr0                                    |

| P[15]        | RO                   | Y3                        | G7                   | Cr7                       | G7                                | Y7                                     |

| P[14]        | G5                   | Y2                        | G6                   | Cr6                       | G6                                | Y6                                     |

| P[13]        | G4                   | Y1                        | G5                   | Cr5                       | G5                                | Y5                                     |

| P[12]        | G3                   | Y0                        | G4                   | Cr4                       | G4                                | Y4                                     |

| P[11]        | G2                   | Cr/Cb7                    | G3                   | Cr3                       | G3                                | Y3                                     |

| P[10]        | G1                   | Cr/Cb6                    | G2                   | Cr2                       | G2                                | Y2                                     |

| P[9]         | GO                   | Cr/Cb5                    | G1                   | Cr1                       | G1                                | Y1                                     |

| P[8]         | B4                   | Cr/Cb4                    | GO                   | Cr0                       | GO                                | YO                                     |

| P[7]         | B3                   | Cr/Cb3                    | R7                   | Y7                        | B7                                | Cb7                                    |

| P[6]         | B2                   | Cr/Cb2                    | R6                   | Y6                        | B6                                | Cb6                                    |

| P[5]         | B1                   | Cr/Cb1                    | R5                   | Y5                        | B5                                | Cb5                                    |

| P[4]         | B0                   | Cr/Cb0                    | R4                   | Y4                        | B4                                | Cb4                                    |

| P[3]         | —                    | _                         | R3                   | Y3                        | B3                                | Cb3                                    |

| P[2]         | —                    | _                         | R2                   | Y2                        | B2                                | Cb2                                    |

| P[1]         | —                    | _                         | R1                   | Y1                        | B1                                | Cb1                                    |

| P[0]         | —                    | _                         | R0                   | Y0                        | BO                                | Cb0                                    |

Flicker-Free Video Encoder with Ultrascale Technology 1.2 GUI Controller Programmability and Frequency Requirement

# 1.2 GUI Controller Programmability and Frequency Requirement

Programmability and frequency requirements for the Graphics Controller/Data Master device are defined in Table 1-4 for the most common input resolutions.

| Desktop Input Mode           | Maximum Total |              | Maximum<br>End of Active to<br>Vsync | Maximum F  | requencies  |

|------------------------------|---------------|--------------|--------------------------------------|------------|-------------|

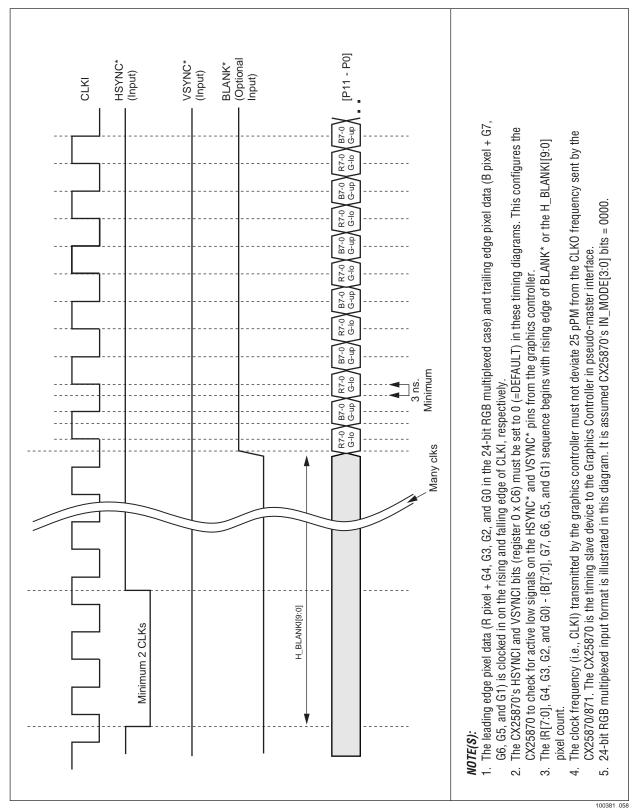

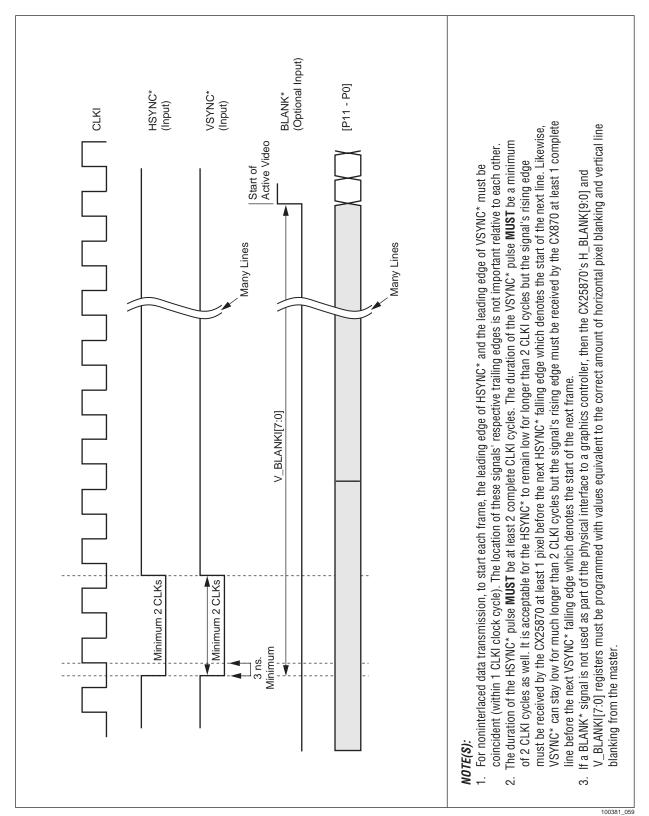

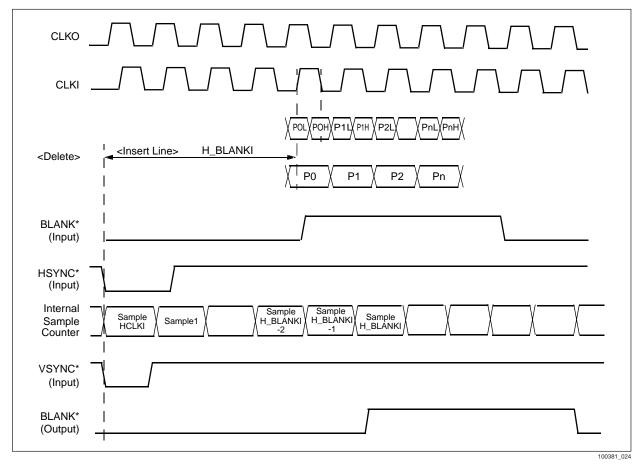

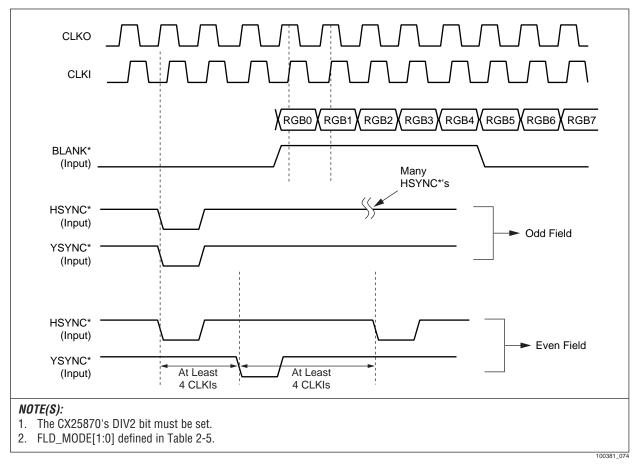

|                              | Pixels/HTOTAL | Lines/VTOTAL | Lines                                | Line (kHz) | Pixel (MHz) |