LTC6412

### 800MHz, 31dB Range Analog-Controlled VGA

### FEATURES

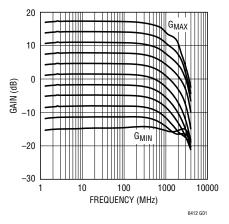

- 800MHz –3dB Small-Signal Bandwidth

- Continuously-Adjustable Gain Control

- -14dB to +17dB Linear-in-dB Gain Range

- 35dBm OIP3 at 240MHz Across All Gain Settings

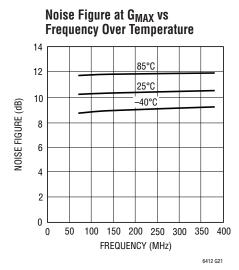

- 10dB Noise Figure at Maximum Gain

- (IIP3 NF) = +8dBm at 240MHz Across All Gains

- 2.7nV/√Hz Input Referred Noise

- Differential Inputs and Outputs

- **50**Ω Input Impedance Across all Gains

- Single Supply Operation from 3V to 3.6V

- 110mA Supply Current

- 4mm × 4mm × 0.75mm 24-Pin QFN Package

### **APPLICATIONS**

- IF Signal Chain Automatic Gain Control (AGC)

- 2.5G and 3G Cellular Basestation Transceivers

- WiMAX, WiBro, WLAN Receivers

- Satellite and GPS Receiver IF

### DESCRIPTION

The LTC<sup>®</sup>6412 is a fully differential variable gain amplifier with linear-in-dB analog gain control. It is designed for AC-coupled operation in IF receiver chains from 1MHz to 500MHz. The part has a constant OIP3 across a wide output amplitude range and across the 31dB gain control range. The output noise (NF + Gain) is also flat versus gain to provide a uniform spurious-free dynamic range (SFDR) >120dB over the full gain control range at 240MHz.

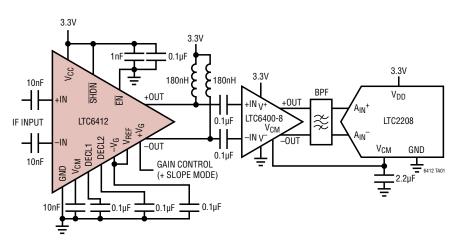

The LTC6412 is ideal for interfacing with the LT<sup>®</sup>5527 and LT5557 downconverting mixers, LTC6410-6 IF amplifier and the LTC6400/LTC6401/LTC6416 ADC drivers for use in 12-, 14-, and 16-bit ADC applications.

The LTC6412 recovers quickly from an overdrive condition, and the  $\overline{EN}$  pin allows for a fast output signal disable to protect sensitive downstream components. Asserting the  $\overline{SHDN}$  pin reduces the current consumption below 1mA for power-down or sleep modes.

**Δ**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

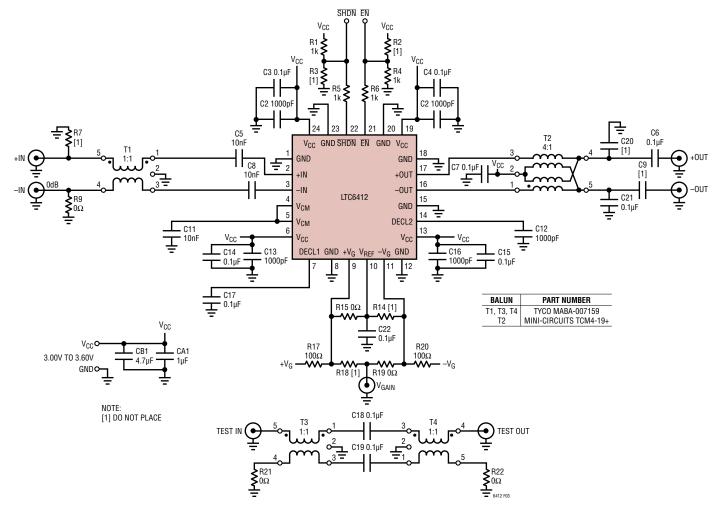

### TYPICAL APPLICATION

3.3V Fully Differential 240MHz IF Receiver Chain with 31dB Gain Control

#### VGA Gain vs Frequency Over Gain Control Range

### ABSOLUTE MAXIMUM RATINGS

#### (Note 1)

| Total Supply Voltage (V <sub>CC</sub> to GND)                                    | 3.8V       |

|----------------------------------------------------------------------------------|------------|

| Amplifier Input Current (+IN, -IN)                                               | ±20mA      |

| Amplifier Output Current (+OUT, -OUT)                                            | ±70mA      |

| Input Current (+V <sub>G</sub> , -V <sub>G</sub> , V <sub>REF</sub> , EN, SHDN ) | ±10mA      |

| Input Current (V <sub>CM</sub> , DECL1, DECL2)                                   | ±10mA      |

| RF Input Power, Continuous, 50Ω                                                  | +15dBm     |

| RF Input Power, 100 $\mu$ s pulse, 50 $\Omega$                                   | +20dBm     |

| Operating Temperature Range (Note 2)40                                           | °C to 85°C |

| Specified Temperature Range (Note 3)40                                           | °C to 85°C |

| Storage Temperature Range65°                                                     | C to 150°C |

| Junction Temperature                                                             | 150°C      |

|                                                                                  |            |

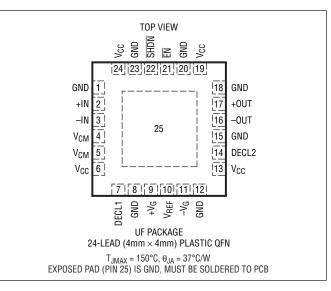

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION                    | SPECIFIED TEMPERATURE RANGE |

|------------------|------------------|---------------|----------------------------------------|-----------------------------|

| LTC6412CUF#PBF   | LTC6412CUF#TRPBF | 6412          | 24-Lead (4mm $\times$ 4mm) Plastic QFN | 0°C to 70°C                 |

| LTC6412IUF#PBF   | LTC6412IUF#TRPBF | 6412          | 24-Lead (4mm $\times$ 4mm) Plastic QFN | –40°C to 85°C               |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

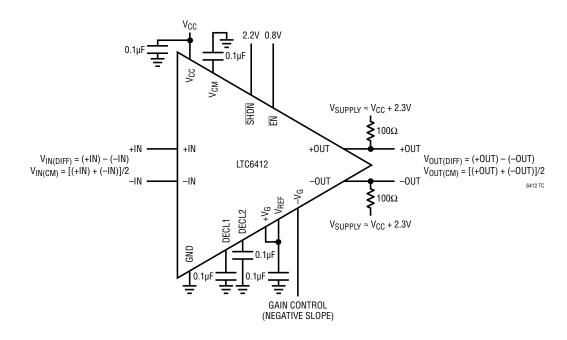

**DC ELECTRICAL CHARACTERISTICS** The • denotes specifications that apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . DC electrical performance measured using DC test circuit schematic.  $V_{IN(DIFF)}$  is defined as (+IN) - (-IN).  $V_{OUT(DIFF)}$  is defined as (+OUT) - (-OUT).  $V_{IN(CM)}$  is defined as [(+IN) + (-IN)]/2.  $V_{OUT(CM)}$  is defined as [(+OUT) + (-OUT)]/2. Unless noted otherwise, default operating conditions are  $V_{CC} = 3.3V$ ,  $\overline{EN} = 0.8V$ ,  $\overline{SHDN} = 2.2V$ ,  $+V_G$  tied to  $V_{REF}$  (negative gain slope mode),  $V_{OUT(CM)} = 3.3V$ . Differential power gain defined at  $Z_{SOURCE} = 50\Omega$  differential and  $Z_{LOAD} = 200\Omega$ differential.

| SYMBOL                                 | PARAMETER                                        | CONDITIONS                                                                                                  |   | MIN            | ТҮР    | MAX            | UNITS        |

|----------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---|----------------|--------|----------------|--------------|

| Gain Charact                           | eristics                                         |                                                                                                             |   |                |        |                |              |

| G <sub>MAX</sub>                       | Maximum Differential Power Gain (Note 4)         | $-V_{G} = 0V, V_{IN(DIFF)} = 100mV$                                                                         | • | 16.1<br>15.5   | 17.1   | 18.1<br>18.7   | dB<br>dB     |

| G <sub>MIN</sub>                       | Minimum Differential Power Gain (Note 4)         | $-V_{G} = 1.2V, V_{IN(DIFF)} = 200mV$                                                                       | • | -16.2<br>-16.8 | -14.9  | -13.6<br>-13.0 | dB<br>dB     |

| G <sub>RANGE</sub>                     | Differential Power Gain Range                    | G <sub>MAX</sub> -G <sub>MIN</sub>                                                                          | • | 30.7<br>30.1   | 31.9   | 33.1<br>33.7   | dB<br>dB     |

| TC <sub>GAIN</sub>                     | Temperature Coefficient of Gain at Fixed $V_{G}$ | $-V_{G} = 0V \text{ to } 1.2V$                                                                              |   |                | -0.007 |                | dB/°C        |

| G <sub>SLOPE</sub>                     | Gain Control Slope                               | $-V_G = 0.2V$ to 1.0V, 85 Points, Slope of the Least-Square Fit Line                                        | • | -34.1<br>-34.7 | -32.9  | -31.7<br>-31.1 | dB/V<br>dB/V |

| G <sub>CONF(AVE)</sub>                 | Average Conformance Error to Gain Slope Line     | -V <sub>G</sub> = 0.2V to 1.0V, 85 Points, Standard<br>Error to the Least-Square Fit Line                   |   |                | 0.12   | 0.20           | dB           |

| G <sub>CONF(MAX)</sub>                 | Maximum Conformance Error to Gain Slope<br>Line  | –V <sub>G</sub> = 0.2V to 1.0V, 85 points, Maximum<br>Error to the Least-Square Fit Line                    |   |                | 0.20   | 0.45           | dB           |

| +IN and -IN F                          | lins                                             |                                                                                                             |   |                |        |                |              |

| R <sub>IN(GMAX)</sub>                  | Differential Input Resistance at Maximum Gain    | $-V_{G} = 0V, V_{IN(DIFF)} = 100mV$                                                                         | • | 49<br>47       | 57     | 65<br>67       | Ω<br>Ω       |

| R <sub>IN(GMIN)</sub>                  | Differential Input Resistance at Minimum Gain    | $-V_{G} = 1.2V, V_{IN(DIFF)} = 200mV$                                                                       | • | 49<br>47       | 57     | 65<br>67       | Ω<br>Ω       |

| V <sub>INCM(GMAX)</sub>                | Input Common Mode Voltage at Maximum Gain        | $-V_{G} = 0V$ , DC Blocking Capacitor to Input                                                              |   |                | 640    |                | mV           |

| VINCM(GMIN)                            | Input Common Mode Voltage at Minimum Gain        | $-V_{G} = 1.2V$ , DC Blocking Capacitor to Input                                                            |   |                | 640    |                | mV           |

| +V <sub>G</sub> , -V <sub>G</sub> , an | d V <sub>REF</sub> Pins                          |                                                                                                             |   |                |        |                |              |

| R <sub>IH(+VG)</sub>                   | +V <sub>G</sub> Input High Resistance            | +V <sub>G</sub> = 1.0V, -V <sub>G</sub> Tied to V <sub>REF</sub> ,<br>$R_{IN(+VG)} = 1V/\Delta I_{IL(+VG)}$ | • | 7.8<br>7.2     | 9.2    | 10.6<br>11.6   | kΩ<br>kΩ     |

| R <sub>IH(-VG)</sub>                   | –V <sub>G</sub> Input High Resistance            | $-V_G = 1.0V$ , $+V_G$ Tied to $V_{REF}$ ,<br>$R_{IN(-VG)} = 1V/\Delta I_{IL(-VG)}$                         | • | 7.8<br>7.2     | 9.2    | 10.6<br>11.6   | kΩ<br>kΩ     |

| I <sub>IL(+VG)</sub>                   | +V <sub>G</sub> Input Low Current                | $+V_{G} = 0V, -V_{G}$ Tied to $V_{REF}$                                                                     | • | -9<br>-10      | -5     | -1<br>-1       | μΑ<br>μΑ     |

| I <sub>IL(-VG)</sub>                   | -V <sub>G</sub> Input Low Current                | $-V_{G} = 0V$ , $+V_{G}$ Tied to $V_{REF}$                                                                  | • | -9<br>-10      | -5     | -1<br>-1       | μΑ<br>μΑ     |

| V <sub>REF</sub>                       | Internal Bias Voltage                            | $-V_{G} = 0V$ , $+V_{G}$ Tied to $V_{REF}$                                                                  | • | 590<br>580     | 615    | 640<br>650     | mV<br>mV     |

**DC ELECTRICAL CHARACTERISTICS** The • denotes specifications that apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. DC electrical performance measured using DC test circuit schematic.  $V_{IN(DIFF)}$  is defined as (+IN) - (-IN).  $V_{OUT(DIFF)}$  is defined as (+OUT) - (-OUT).  $V_{IN(CM)}$  is defined as [(+IN) + (-IN)]/2.  $V_{OUT(CM)}$  is defined as [(+OUT) + (-OUT)]/2. Unless noted otherwise, default operating conditions are  $V_{CC} = 3.3V$ , EN = 0.8V, SHDN = 2.2V,  $+V_G$  tied to  $V_{REF}$  (negative gain slope mode),  $V_{OUT(CM)} = 3.3V$ . Differential power gain defined at  $Z_{SOURCE} = 50\Omega$  differential and  $Z_{LOAD} = 200\Omega$  differential.

| SYMBOL                   | PARAMETER                                | CONDITIONS                                |   | MIN | ТҮР | MAX        | UNITS    |

|--------------------------|------------------------------------------|-------------------------------------------|---|-----|-----|------------|----------|

| SHDN Pin                 |                                          | ·                                         |   |     |     |            |          |

| VIL(SHDN)                | SHDN Input Low Voltage                   |                                           | • |     |     | 0.8        | V        |

| V <sub>IH(SHDN)</sub>    | SHDN Input High Voltage                  |                                           | • | 2.2 |     |            | V        |

| IIL(SHDN)                | SHDN Input Low Current                   | <u>SHDN</u> = 0.8V                        | • | -60 | -30 | -1         | μA       |

| IIH(SHDN)                | SHDN Input High Current                  | <u>SHDN</u> = 2.2V                        | • | -30 | -15 | -1         | μA       |

| EN Pin                   |                                          |                                           |   |     |     |            |          |

| $V_{IL(\overline{EN})}$  | EN Input Low Voltage                     |                                           | • |     |     | 0.8        | V        |

| V <sub>IH(ĒN)</sub>      | EN Input High Voltage                    |                                           |   | 2.2 |     |            | V        |

| I <sub>IL(EN)</sub>      | EN Input Low Current                     | ĒN = 0.8V                                 | • | -60 | -30 | -1         | μA       |

| I <sub>IH(ĒN)</sub>      | EN Input High Current                    | ĒN = 2.2V                                 |   | -30 | -15 | -1         | μA       |

| Power Supp               | ly                                       | ·                                         |   |     |     |            |          |

| V <sub>S</sub>           | Operating Supply Range                   |                                           |   | 3.0 | 3.3 | 3.6        | V        |

| I <sub>S(TOT)</sub>      | Total Supply Current                     | All $V_{CC}$ Pins Plus +OUT and –OUT Pins | • |     | 110 | 135<br>140 | mA<br>mA |

| I <sub>S(OUT)</sub>      | Sum of Supply Current to OUT Pins        | $I_{S(OUT)} = I_{+OUT} + I_{-OUT}$        | • |     | 44  | 55<br>60   | mA<br>mA |

| $I_{\Delta(OUT)}$        | Delta of Supply Current to OUT Pins      | Current Imbalance to +OUT and –OUT        | • |     | 0.5 | 1.5<br>2.0 | mA<br>mA |

| $I_{S(\overline{SHDN})}$ | Supply Current in Shutdown               | $I_{S(OUT)}$ at $\overline{SHDN} = 0.8V$  | • |     | 0.5 | 1.3<br>2.0 | mA<br>mA |

| PSRR <sub>MAX</sub>      | Power Supply Rejection Ratio at Max Gain | –V <sub>G</sub> = 0V, Output Referred     |   | 40  | 53  |            | dB       |

| PSRR <sub>MIN</sub>      | Power Supply Rejection Ratio at Min Gain | –V <sub>G</sub> = 1.2V, Output Referred   |   | 40  | 53  |            | dB       |

**AC ELECTRICAL CHARACTERISTICS** The • denotes specifications that apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Typical AC electrical performance measured in demo board DC1464A (Figure 3, Test Circuit A) unless otherwise noted. Default operating conditions are  $V_{CC} = 3.3V$ ,  $\overline{EN} = 0.8V$ ,  $\overline{SHDN} = 2.2V$ ,  $+V_G$  tied to  $V_{REF}$  (negative gain slope mode), and  $Z_{SOURCE} = Z_{LOAD} = 50\Omega$  unless otherwise noted.

| SYMBOL                  | PARAMETER                                              | CONDITIONS                                                                                                                                     | MIN TYP MAX | UNITS                                        |

|-------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------|

| Small Signa             | al                                                     |                                                                                                                                                |             | <u> </u>                                     |

| BW <sub>GMAX</sub>      | -3dB Bandwidth for Sdd21 at Maximum Gain               | -V <sub>G</sub> = 0V, Test Circuit B                                                                                                           | 800         | MHz                                          |

| BW <sub>GMIN</sub>      | –3dB Bandwidth for Sdd21 at Minimum Gain               | –V <sub>G</sub> = 1.2V, Test Circuit B                                                                                                         | 800         | MHz                                          |

| Sdd11                   | Input Match at $Z_{SOURCE} = 50\Omega$ Differential    | -V <sub>G</sub> = 0V to 1.2V, 10MHz-500MHz,<br>Test Circuit B                                                                                  | -20         | dB                                           |

| Sdd22                   | Output Match at $Z_{LOAD}$ = 200 $\Omega$ Differential | -V <sub>G</sub> = 0V to 1.2V, 10MHz-250MHz,<br>Test Circuit B                                                                                  | -10         | dB                                           |

| Sdd12                   | Reverse Isolation                                      | -V <sub>G</sub> = 0V to 1.2V, 10MHz-500MHz,<br>Test Circuit B                                                                                  | -80         | dB                                           |

| Transient R             | esponse                                                |                                                                                                                                                |             |                                              |

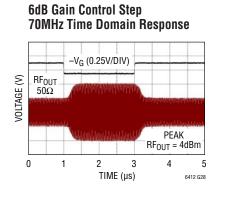

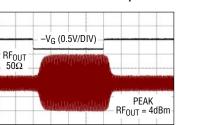

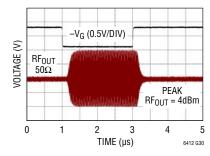

| t <sub>STEP(6dB)</sub>  | 6dB Gain Step Response Time                            | $\begin{array}{l} \mbox{Peak P}_{OUT} = +4dBm, -V_G = 0.2V \mbox{ to } 0.4V, \\ \mbox{Time to Settle Within 1dB of Final P}_{OUT} \end{array}$ | 0.4         | μs                                           |

| t <sub>STEP(12dB)</sub> | 12dB Gain Step Response Time                           | Peak $P_{OUT}$ = +4dBm, $-V_G$ = 0.2V to 0.6V,<br>Time to Settle Within 1dB of Final $P_{OUT}$                                                 | 0.4         | μs                                           |

| t <sub>STEP(20dB)</sub> | 20dB Gain Step Response Time                           | Peak $P_{OUT}$ = +4dBm, $-V_G$ = 0.2V to 0.8V,<br>Time to Settle Within 1dB of Final $P_{OUT}$                                                 | 0.4         | μs                                           |

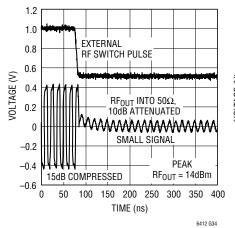

| t <sub>OVDR</sub>       | Overdrive Recovery Time at 70MHz                       | $-V_G = 0V$ , $P_{IN} = +3dBm$ to $-17dBm$ , Time to Settle Within 1dB of Final $P_{OUT}$                                                      | 25          | ns                                           |

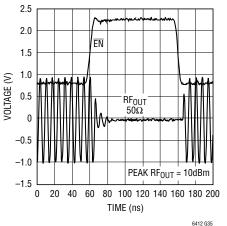

| t <sub>OFF</sub>        | Output Amplifier Disable Time                          | $P_{OUT}$ = 0dBm at $\overline{EN}$ = 0V, –V <sub>G</sub> = 0V,<br>$\overline{EN}$ = 0V to 3V, Time for P <sub>OUT</sub> ≤ –20dBm              | 25          | ns                                           |

| t <sub>ON</sub>         | Output Amplifier Enable Time                           | $P_{OUT} = 0dBm \text{ at } \overline{EN} = 0V, -V_G = 0V, \overline{EN} = 3V \text{ to}$<br>0V, Time for $P_{OUT} \ge -1dBm$                  | 20          | ns                                           |

| 70MHz Sign              | al                                                     |                                                                                                                                                |             | <u>.                                    </u> |

| G <sub>MAX</sub>        | Maximum Gain                                           | $-V_{G} = 0V$ , Test Circuit B                                                                                                                 | 17          | dB                                           |

| G <sub>MIN</sub>        | Minimum Gain                                           | –V <sub>G</sub> = 1.2V, Test Circuit B                                                                                                         | -15         | dB                                           |

| G <sub>RANGE</sub>      | Gain Range                                             | G <sub>MAX</sub> -G <sub>MIN</sub>                                                                                                             | 32          | dB                                           |

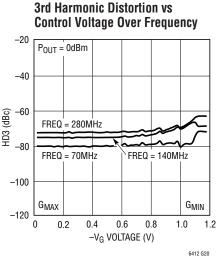

| HD2                     | Second Harmonic Distortion                             | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                                                   | -80         | dBc                                          |

| HD3                     | Third Harmonic Distortion                              | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                                                   | -80         | dBc                                          |

| IM3                     | Third-Order Intermodulation                            | $f_1 = 69.5MHz$ , $f_2 = 70.5MHz$ ,<br>$P_{OUT} = -6dBm/Tone$ , $-V_G = 0V$ to 1.0V                                                            | -90         | dBc                                          |

| OIP3                    | Output Third-Order Intercept                           | $f_1 = 69.5MHz$ , $f_2 = 70.5MHz$ ,<br>$P_{OUT} = -6dBm/Tone$ , $-V_G = 0V$ to 1.0V                                                            | 39          | dBm                                          |

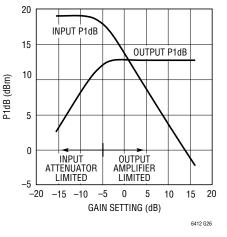

| P1dB <sub>GMAX</sub>    | Output 1dB Compression Point at Max Gain               | -V <sub>G</sub> = 0V (Note 6)                                                                                                                  | 13          | dBm                                          |

| NF <sub>GMAX</sub>      | Noise Figure at Maximum Gain                           | -V <sub>G</sub> = 0V (Note 5)                                                                                                                  | 10          | dB                                           |

| NF <sub>GMIN</sub>      | Noise Figure at Minimum Gain                           | -V <sub>G</sub> = 1.2V (Note 5)                                                                                                                | 42          | dB                                           |

| 140MHz Sig              | nal                                                    |                                                                                                                                                |             | <u> </u>                                     |

| G <sub>MAX</sub>        | Maximum Gain                                           | –V <sub>G</sub> = 0V, Test Circuit B                                                                                                           | 17          | dB                                           |

| G <sub>MIN</sub>        | Minimum Gain                                           | –V <sub>G</sub> = 1.2V, Test Circuit B                                                                                                         | -15         | dB                                           |

| G <sub>RANGE</sub>      | Gain Range                                             | G <sub>MAX</sub> -G <sub>MIN</sub>                                                                                                             | 32          | dB                                           |

| HD2                     | Second Harmonic Distortion                             | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                                                   | -80         | dBc                                          |

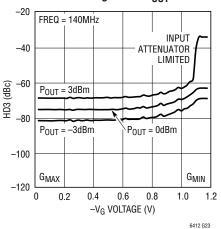

| HD3                     | Third Harmonic Distortion                              | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                                                   | -75         | dBc                                          |

**AC ELECTRICAL CHARACTERISTICS** The • denotes specifications that apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Typical AC electrical performance measured in demo board DC1464A (Figure 3, Test Circuit A) unless otherwise noted. Default operating conditions are  $V_{CC} = 3.3V$ ,  $\overline{EN} = 0.8V$ ,  $\overline{SHDN} = 2.2V$ ,  $+V_G$  tied to  $V_{REF}$  (negative gain slope mode), and  $Z_{SOURCE} = Z_{LOAD} = 50\Omega$  unless otherwise noted.

| SYMBOL               | PARAMETER                                | CONDITIONS                                                                                                           |  | MIN  | ΤΥΡ   | MAX  | UNITS |

|----------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|------|-------|------|-------|

| IM3                  | Third-Order Intermodulation              | $f_1 = 139.5MHz$ , $f_2 = 140.5MHz$ ,<br>$P_{OUT} = -6dBm/Tone$ , $-V_G = 0V$ to 1.0V                                |  |      | -88   |      | dBc   |

| OIP3                 | Output Third-Order Intercept             | $f_1$ = 139.5MHz, $f_2$ = 140.5MHz, $P_{OUT}$ = –6dBm/Tone, $-V_G$ = 0V to 1.0V                                      |  |      | 38    |      | dBm   |

| P1dB <sub>GMAX</sub> | Output 1dB Compression Point at Max Gain | $-V_{G} = 0V$ (Note 6)                                                                                               |  |      | 13    |      | dBm   |

| NF <sub>GMAX</sub>   | Noise Figure at Maximum Gain             | $-V_{G} = 0V$ (Note 5)                                                                                               |  |      | 10    |      | dB    |

| NF <sub>GMIN</sub>   | Noise Figure at Minimum Gain             | -V <sub>G</sub> = 1.2V (Note 5)                                                                                      |  |      | 42    |      | dB    |

| 240MHz Sig           | gnal                                     |                                                                                                                      |  |      |       |      |       |

| G <sub>MAX</sub>     | Maximum Gain                             | $-V_{G} = 0V$ , Test Circuit B                                                                                       |  |      | 17    |      | dB    |

| G <sub>MIN</sub>     | Minimum Gain                             | -V <sub>G</sub> = 1.2V, Test Circuit B                                                                               |  |      | -14   |      | dB    |

| G <sub>RANGE</sub>   | Gain Range                               | G <sub>MAX</sub> -G <sub>MIN</sub>                                                                                   |  |      | 31    |      | dB    |

| HD2                  | Second Harmonic Distortion               | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                         |  |      | -70   |      | dBc   |

| HD3                  | Third Harmonic Distortion                | $P_{OUT} = 0dBm, -V_G = 0V \text{ to } 1.0V$                                                                         |  |      | -70   |      | dBc   |

| IM3                  | Third-Order Intermodulation              | $f_1 = 239.5$ MHz, $f_2 = 240.5$ MHz,<br>$P_{OUT} = -6$ dBm/Tone, $-V_G = 0$ V to 1.0V                               |  |      | -82   |      | dBc   |

| OIP3                 | Output Third-Order Intercept             | f <sub>1</sub> = 239.5MHz, f <sub>2</sub> = 240.5MHz,<br>P <sub>OUT</sub> = -6dBm/Tone, -V <sub>G</sub> = 0V to 1.0V |  | 35   |       |      | dBm   |

| P1dB <sub>GMAX</sub> | Output 1dB Compression Point at Max Gain | $-V_{G} = 0V$ (Note 6)                                                                                               |  | 12   |       |      | dBm   |

| NF <sub>GMAX</sub>   | Noise Figure at Maximum Gain             | $-V_{G} = 0V$ (Note 5)                                                                                               |  | 10   |       |      | dB    |

| NF <sub>GMIN</sub>   | Noise Figure at Minimum Gain             | -V <sub>G</sub> = 1.2V (Note 5)                                                                                      |  | 42   |       | dB   |       |

| 280MHz/32            | OMHz Signal                              |                                                                                                                      |  |      |       |      |       |

| G <sub>MAX</sub>     | Maximum Gain                             | $f = 320MHz, P_{OUT} = -3dBm, -V_{G} = 0V$                                                                           |  |      | 16.9  |      | dB    |

| G <sub>MID</sub>     | Medium Gain                              | f = 320MHz, P <sub>OUT</sub> = -5dBm, -V <sub>G</sub> = 0.6V                                                         |  |      | 1.5   |      | dB    |

| G <sub>MIN</sub>     | Minimum Gain                             | f = 320MHz, P <sub>OUT</sub> = -5dBm, -V <sub>G</sub> = 1.2V                                                         |  |      | -14.2 |      | dB    |

| G <sub>RANGE</sub>   | Gain Range                               | 320MHz, G <sub>MAX</sub> -G <sub>MIN</sub>                                                                           |  | 29.7 | 31.1  | 32.5 | dB    |

| IM3 <sub>GMAX</sub>  | Third-Order Intermodulation at Max Gain  | $f_1 = 280MHz$ , $f_2 = 320MHz$ ,<br>$P_{OUT} = -3dBm/Tone$ , $-V_G = 0V$                                            |  |      | -72   |      | dBc   |

| IM3 <sub>GMID</sub>  | Third-Order Intermodulation at Mid Gain  | f <sub>1</sub> = 280MHz, f <sub>2</sub> = 320MHz,<br>P <sub>OUT</sub> = -5dBm/Tone, -V <sub>G</sub> = 0.6V           |  |      | -71   | -65  | dBc   |

| IM3 <sub>GMIN</sub>  | Third-Order Intermodulation at Min Gain  | f <sub>1</sub> = 280MHz, f <sub>2</sub> = 320MHz,<br>P <sub>OUT</sub> = -5dBm/Tone, -V <sub>G</sub> = 1.2V           |  |      | -56   |      | dBc   |

| 0IP3 <sub>GMAX</sub> | Output Third-Order Intercept at Max Gain | $f_1 = 280MHz$ , $f_2 = 320MHz$ ,<br>$P_{OUT} = -3dBm/Tone$ , $-V_G = 0V$                                            |  |      | 31.0  |      | dBm   |

| 0IP3 <sub>GMID</sub> | Output Third-Order Intercept at Mid Gain | $f_1 = 280MHz$ , $f_2 = 320MHz$ ,<br>$P_{OUT} = -5dBm/Tone$ , $-V_G = 0.6V$                                          |  | 26.0 | 30.5  |      | dBm   |

| 0IP3 <sub>GMIN</sub> | Output Third-Order Intercept at Min Gain | f <sub>1</sub> = 280MHz, f <sub>2</sub> = 320MHz,<br>P <sub>OUT</sub> = -5dBm/Tone, -V <sub>G</sub> = 1.2V           |  |      | 23.0  |      | dBm   |

**AC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications that apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. Typical AC electrical performance measured in demo board DC1464A (Figure 3, Test Circuit A) unless otherwise noted. Default operating conditions are V<sub>CC</sub> = 3.3V, EN = 0.8V, SHDN = 2.2V, +V<sub>G</sub> tied to V<sub>REF</sub> (negative gain slope mode), and  $Z_{SOURCE} = Z_{LOAD} = 50\Omega$  unless otherwise noted.

| SYMBOL               | PARAMETER                                | CONDITIONS                                                                            | MIN | ТҮР  | MAX | UNITS |  |  |  |

|----------------------|------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|--|

| 380MHz Sig           | 380MHz Signal                            |                                                                                       |     |      |     |       |  |  |  |

| G <sub>MAX</sub>     | Maximum Gain                             | -V <sub>G</sub> = 0V, Test Circuit B                                                  |     | 17   |     | dB    |  |  |  |

| G <sub>MIN</sub>     | Minimum Gain                             | –V <sub>G</sub> = 1.2V, Test Circuit B                                                |     | -14  |     | dB    |  |  |  |

| G <sub>RANGE</sub>   | Gain Range                               | G <sub>MAX</sub> -G <sub>MIN</sub>                                                    |     | 31   |     | dB    |  |  |  |

| IM3                  | Third-Order Intermodulation              | $f_1 = 379.5MHz$ , $f_2 = 380.5MHz$ ,<br>$P_{OUT} = -6dBm/Tone$ , $-V_G = 0V$ to 1.0V |     | -72  |     | dBc   |  |  |  |

| OIP3                 | Output Third-Order Intercept             | $f_1 = 379.5MHz$ , $f_2 = 380.5MHz$ ,<br>$P_{OUT} = -6dBm/Tone$ , $-V_G = 0V$ to 1.0V |     | 30   |     | dBm   |  |  |  |

| P1dB <sub>GMAX</sub> | Output 1dB Compression Point at Max Gain | $-V_{G} = 0V$ (Note 6)                                                                |     | 11   |     | dBm   |  |  |  |

| NF <sub>GMAX</sub>   | Noise Figure at Maximum Gain             | $-V_{G} = 0V$ (Note 5)                                                                |     | 10.5 |     | dB    |  |  |  |

| NF <sub>GMIN</sub>   | Noise Figure at Minimum Gain             | -V <sub>G</sub> = 1.2V (Note 5)                                                       |     | 42   |     | dB    |  |  |  |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. RF input power rating is guaranteed by design and engineering characterization, but not production tested. The absolute maximum continuous RF input power shall not exceed +15dBm

**Note 2:** The LTC6412C/LTC6412I are guaranteed functional over the operating temperature range of -40°C to 85°C.

Note 3: The LTC6412C is guaranteed to meet specified performance from 0°C to 70°C. It is designed, characterized and expected to meet specified performance from -40°C and 85°C but is not tested or QA sampled at these temperatures. The LT6412I is guaranteed to meet specified performance from -40°C to 85°C.

Note 4: Power gain is defined at  $Z_{SOURCE} = 50\Omega$  and  $Z_{LOAD} = 200\Omega$ . Voltage gain for this test condition is 6dB higher than the stated power gain.

**Note 5:**  $e_n$  can be calculated from 50 $\Omega$  NF with the formula:  $e_n = \sqrt{\{4kT(50)(10^{NF/10} - 1)\}}$

where

$e_n$  = Input referred voltage noise in V/ $\sqrt{Hz}$

$NF = 50\Omega$  noise figure in dB

k = Boltzmann's constant =  $1.38 \cdot 10^{-23}$  J/°K

T = Absolute temperature in °K = °C + 273

**Note 6:** P1dB compression of the output amplifier cannot be achieved in the minimum gain state while complying with the absolute maximum rating for input RF power.

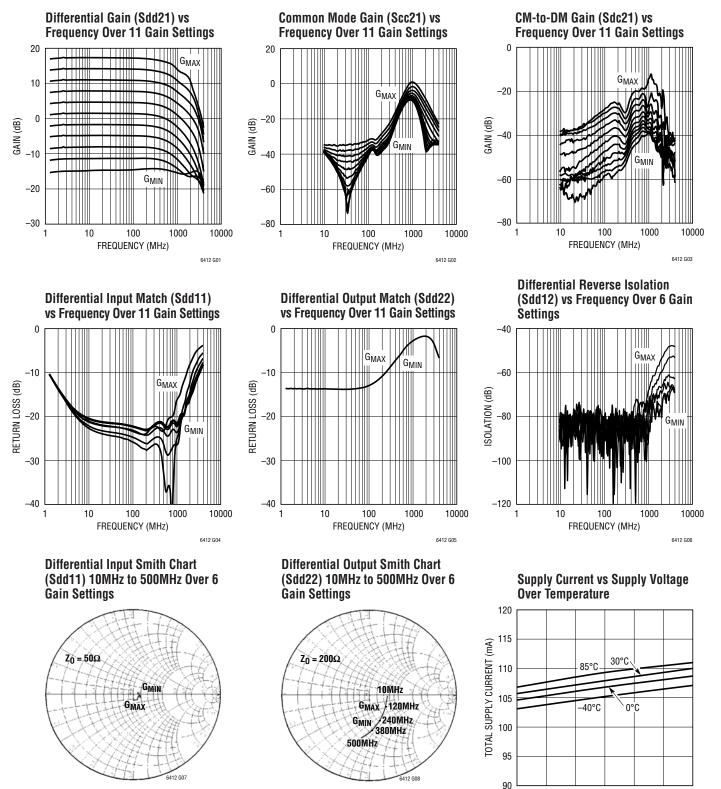

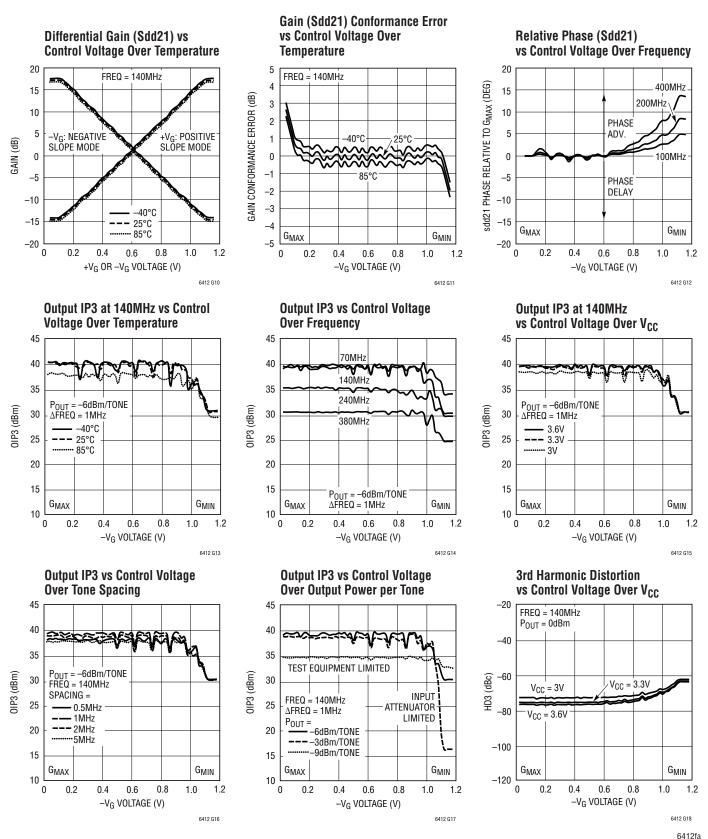

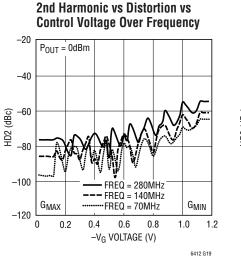

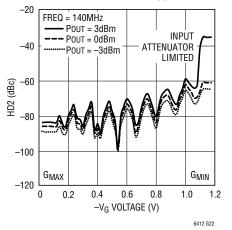

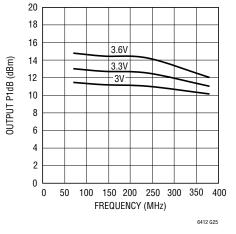

# **TYPICAL PERFORMANCE CHARACTERISTICS** Electrical Performance in Test Circuits A and B at $T_A = 25^{\circ}C$ and $V_{CC} = 3.3V$ unless otherwise noted.

6412 G09 6412fa

3.6

3.5

3.0

3.1

3.2

3.3

SUPPLY VOLTAGE (V)

3.4

# **TYPICAL PERFORMANCE CHARACTERISTICS** Electrical Performance in Test Circuits A and B at $T_A = 25^{\circ}C$ and $V_{CC} = 3.3V$ unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Electrical Performance in Test Circuits A and B at  $T_A = 25^{\circ}C$  and  $V_{CC} = 3.3V$  unless otherwise noted.

2nd Harmonic Distortion vs Control Voltage Over P<sub>OUT</sub>

3rd Harmonic Distortion vs Control Voltage Over P<sub>OUT</sub>

Input and Output  $P_{1dB}$  vs Gain Setting at 140MHz

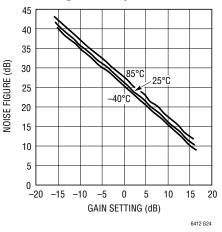

140MHz Noise Figure vs Gain Setting Over Temperature

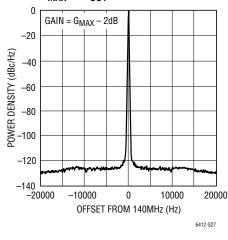

140MHz Sideband Noise Near  $G_{MAX}$  at  $P_{OUT} = +8dBm$

# **TYPICAL PERFORMANCE CHARACTERISTICS** Electrical Performance in Test Circuits A and B at $T_A = 25^{\circ}C$ and $V_{CC} = 3.3V$ unless otherwise noted.

VOLTAGE (V)

0

/OLTAGE (V)

0

1

2

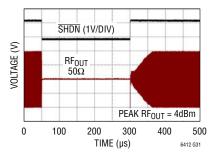

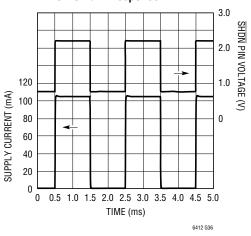

SHDN Step at G = 3dB with  $\overline{EN} = 0V$

**70MHz Time Domain Response**

SHDN (1V/DIV)

200

RFOUT

50Ω

100

#### SHDN Step at $G_{MAX}$ with $\overline{EN} = 0V$ **70MHz Time Domain Response**

#### **10dB Gain Control Step** 70MHz Time Domain Response

3

PEAK RF<sub>OUT</sub> = 4dBm

400

500

6412 G32

TIME (µs)

4

5

6412 G29

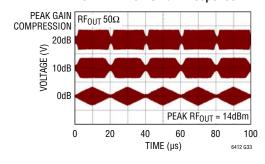

#### 20dB Gain Control Step 70MHz Time Domain Response

Overdrive Compression at G<sub>MAX</sub> 70MHz Time Domain Response

#### **Overdrive Recovery at GMAX 70MHz Time Domain Response**

#### Output EN Step at G<sub>MAX</sub> 140MHz Time Domain Response

TIME (µs)

300

#### **SHDN** Supply Current Time Domain Response

### PIN FUNCTIONS

**GND (Pins 1, 8, 12, 15, 18, 20, 23):** Ground. Pins are connected to each other internally. For best RF performance, all ground pins should be connected to the printed circuit board ground plane.

**+IN (Pin 2):** Positive Signal Input Pin. Has an internally generated DC Bias. A 10nF DC blocking capacitor is recommended.

**–IN (Pin 3):** Negative Signal Input Pin. Has an internally generated DC Bias. A 10nF DC blocking capacitor is recommended.

$V_{CM}$  (Pins 4, 5): Input Common Mode Voltage Pins. Two pins are tied together internally and serve as a virtual ground for the differential inputs, +IN and -IN. Capacitive decoupling to ground with 10nF close to the pins is recommended to help terminate any residual common mode input signal.

$V_{CC}$  (Pins 6, 13, 19, 24): Positive Power Supply. All four pins must be tied to the same voltage, usually 3.3V. Bypass each pin with 1000pF and 0.1µF capacitors close to the pins.

**DECL1 (Pin 7):** Decoupling Pin. Serves to reduce internal noise. Bypass to ground with a  $0.1\mu$ F capacitor close to the pin.

+ $V_G$  (Pin 9): Positive Gain Control Pin. Input signal pin used for positive mode gain control. Otherwise, pin is typically connected to  $V_{REF}$  for negative mode gain control. Pin is internally pulled to ground with a 10k resistor. In positive gain slope mode, the gain control slope is approximately +32dB/V at 140MHz with a gain control range of 0.1V to 1.1V.

$V_{REF}$  (Pin 10): Internal Bias Voltage Pin. Typically tied to  $-V_G$  pin for positive gain control or tied to  $+V_G$  for negative gain control. Determines the midpoint voltage of the gain-vs-V<sub>G</sub> characteristic. Bypass to ground with 0.1µF capacitor close to the pin. Not intended for use as an external reference voltage.

-V<sub>G</sub> (Pin 11): Negative Gain Control Pin. Input signal pin used for negative mode gain control. Otherwise, pin is typically connected to  $V_{REF}$  for positive mode gain control. Pin is internally pulled to ground with a 10k resistor. In negative gain slope mode, the gain control slope is approximately -32dB/V at 140MHz with a gain control range of 0.1V to 1.1V.

**DECL2 (Pin 14):** Decoupling Pin. Serves to reduce internal noise. Bypass to ground with a 1000pF capacitor close to the pin.

**–OUT (Pin 16):** Negative Amplifier Output Pin. A transformer with a center tap tied to  $V_{CC}$  or a choke inductor is recommended to conduct DC quiescent current to the open-collector output device. For best performance, DC bias voltage to –OUT must be within 100mV of  $V_{CC}$ .

+OUT (Pin 17): Positive Amplifier Output Pin. A transformer with a center tap tied to  $V_{CC}$  or a choke inductor is recommended to conduct DC quiescent current to the open-collector output device. For best performance, DC bias voltage to +OUT must be within 100mV of  $V_{CC}$ .

**EN** (Pin 21): Output Signal Enable Pin. Pin is internally pulled high with  $100k\Omega$  to V<sub>CC</sub>. Assert pin to a low voltage to enable the output amplifier signal. Output amplifier impedance and DC current are not affected by the EN state. Connect pin to ground if enable function is not used.

**SHDN** (Pin 22): Shutdown Pin. Pin is internally pulled high with  $100k\Omega$  to V<sub>CC</sub>. Assert pin to a low voltage to shut down the circuit and greatly reduce the supply current. Proper sequencing of the EN and SHDN pins is required to avoid non-monotonic output signal behavior. See Applications Information section for details. Connect pin to V<sub>CC</sub> if shutdown function is not used.

**Exposed Pad (Pin 25):** Ground. The Exposed Pad should have multiple via holes to an underlying ground plane for low inductance and good thermal dissipation.

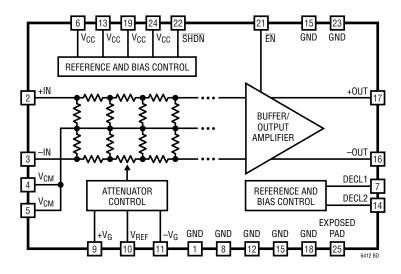

### **BLOCK DIAGRAM**

### DC TEST CIRCUIT

## OPERATION

The LTC6412 employs an interpolated, tapped attenuator circuit architecture to generate the variable-gain characteristic of the amplifier. The tapped attenuator is fed to a buffer and output amplifier to complete the differential signal path shown in the Block Diagram. This circuit architecture provides good RF input power handling capability along with a constant output noise and output IP3 characteristic that are desirable for most IF signal chain applications. The internal control circuitry takes the gain control signal from the  $\pm V_G$  terminals and converts this to an appropriate set of control signals to the attenuator ladder. The attenuator control circuit ensures that the linear-in-dB gain response is continuous and monotonic over the gain range for both slow and fast moving input control signals while exhibiting very little input impedance variation over gain. These design considerations result in a gain-vs-V<sub>G</sub> characteristic with a  $\pm 0.1$ dB ripple and a 0.5µs gain response time that is slower than a similar digital step attenuator design.

An often overlooked characteristic of an analog-controlled VGA is upconverted amplitude modulation (AM) noise from the gain control terminals. The VGA behaves as a 2-quadrant multiplier, so some minimal care is required to avoid excessive AM sideband noise generation. The following table demonstrates the effect of the baseline 20nV/ $\sqrt{Hz}$  equivalent input control noise from the LTC6412 circuit along with the effect of a higher combined input noise due to a noisy external control circuit.

| CONTROL INPUT TOTAL NOISE<br>Voltage (nV/\Hz) | PEAK AM NOISE AT 10kHz OFFSET<br>NEAR MAXIMUM GAIN (dBc/Hz) |

|-----------------------------------------------|-------------------------------------------------------------|

| 20                                            | -142                                                        |

| 40                                            | -136                                                        |

| 70                                            | -131                                                        |

| 100                                           | -128                                                        |

| 200                                           | -122                                                        |

The baseline equivalent  $20\text{nV}/\sqrt{\text{Hz}}$  input noise is seen to produce worst-case AM sidebands of -142dBc/Hz which is near the -147dBm/Hz output noise floor at maximum gain for a nominal 0dBm output signal. An input control noise voltage less than  $80\text{nV}/\sqrt{\text{Hz}}$  is generally recommended to avoid measurable AM sideband noise. While op amp control circuit output noise voltage is usually below  $80\text{nV}/\sqrt{\text{Hz}}$ , some low power DAC outputs exceed  $150\text{nV}/\sqrt{\text{Hz}}$ . DACs with output noise in the range of  $100\text{nV}/\sqrt{\text{Hz}}$  to  $150\text{nV}/\sqrt{\text{Hz}}$  can usually be accommodated with a suitable 2:1 or 3:1 resistor divider network on the DAC output to suppress the noise amplitude by the same ratio. Noisy DACs in excess of  $150\text{nV}/\sqrt{\text{Hz}}$  should be avoided if minimal AM noise is important in the application.

#### Introduction

The LTC6412 is a high linearity, fully-differential analogcontrolled variable-gain amplifier (VGA) optimized for application frequencies in the range of 1MHz to 500MHz. The VGA architecture provides a constant OIP3 and constant output noise level (NF + Gain) over the 31dB gain-control range and thus exhibits a uniform spurious-free dynamic range (SFDR) over gain. This constant SFDR characteristic is ideal for use in receiver IF chains that are upstream from a signal sink such as a demodulator or ADC.

The low supply voltage requirements and fully differential design are compatible with many other LTC mixer, amplifier and ADC products for use in compact, low voltage, fully differential receiver chains. For non-differential systems, the 50 $\Omega$  input impedance and 200 $\Omega$  output impedance are easily converted to single-ended 50 $\Omega$  ports with inexpensive 1:1 and 4:1 baluns.

### **Gain Characteristics**

The LTC6412 provides a continuously adjustable gain range of -14dB to 17dB that is linear-in-dB with respect to the control voltages applied to  $+V_G$  and  $-V_G$ . These control pins can be operated with a differential signal, but it is more common to operate one of the  $V_G$  pins with a single-ended control signal while connecting the other  $V_G$  pin to the provided  $V_{REF}$  pin. In this way, either a positive gain-control slope or negative gain-control slope is easily achieved:

Negative Gain-Control Slope. Tie  $+V_G$  to  $V_{REF}$  and apply gain control voltage to the  $-V_G$  pin. Gain decreases with increasing  $-V_G$  voltage.

Positive Gain-Control Slope. Tie  $-V_G$  to  $V_{REF}$  and apply gain control voltage to the  $+V_G$  pin. Gain increases with increasing  $+V_G$  voltage.

When connected in this typical single-ended configuration, the active control input range extends from 0.1V to 1.1V. This control input range can be extended using a resistor divider with a suitably low output resistance. For example, two series resistors of 1k each would extend the control input range from 0.2V to 2.2V while providing an effective  $500\Omega$  Thevinin equivalent source resistance, a relatively small loading effect compared to the 10k input resistance of the +V<sub>G</sub>/–V<sub>G</sub> terminals.

### **Port Characteristics**

The LTC6412 provides a nominal  $50\Omega$  differential input impedance and  $200\Omega$  differential output impedance over the operating frequency range.

The input impedance characteristic derives from the differential attenuator ladder shown in the Block Diagram. The internal circuit controls the RF connections to this attenuator ladder and generates the appropriate common mode DC voltage to this port. The differential attenuator ladder creates a virtual ground node that needs a capacitor bypass to ground at the V<sub>CM</sub> pin to effectively attenuate any common mode signal presented to the input port. The +V<sub>IN</sub> and -V<sub>IN</sub> pins are connected to the input signal through DC blocking capacitors as shown in Test Circuit A and Test Circuit B, Figures 1-4.

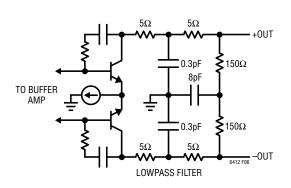

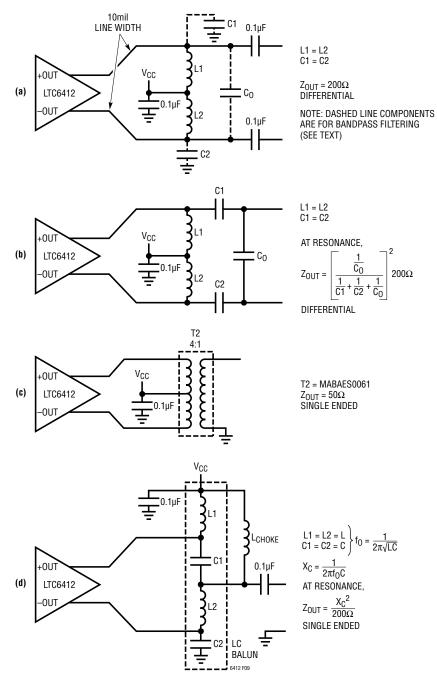

The output impedance characteristic derives from the opencollector equivalent circuit shown in Figure 7. The action of the differential shunt, lowpass filter, and internal feedback presents an effective differential output impedance of  $200\Omega$  to  $300\Omega$  between the +OUT and -OUT pins over the operating band. The +V<sub>OUT</sub> and -V<sub>OUT</sub> pins are connected to the output port using shunt inductors or a transformer to provide a DC path to the supply voltage. The DC block to the circuit output is usually accomplished using series capacitors. These blocking capacitors can be avoided if a flux transformer is used at the output. Figure 9 illustrates a few common inductor and balun transformer methods for coupling the AC signal and DC supply to the output pins. This is discussed further in the Typical Application Circuits section.

#### **Power Supplies**

Inductance to the supply path can degrade the performance of the LTC6412. It is recommended that low inductance bypass capacitors are installed very close to each of the V<sub>CC</sub> pins. 1000pF and 0.1µF parallel capacitors are recommended with the smaller capacitor placed closer to the V<sub>CC</sub> pin. Do not leave any supply pins disconnected. For best performance, DC bias voltage to the +OUT and –OUT pins must be within 100mV of V<sub>CC</sub>. The Exposed Pad on the underside of the package must be connected to ground with low inductance and low thermal resistance. Refer to details of DC1464A (Test Circuit A) for an example of proper  $^{6412ta}$

grounding and supply decoupling. Failure to provide low impedance supply and ground at high frequencies can cause oscillations and increased distortion.

### Enable/Shutdown

Both the  $\overline{EN}$  pin and  $\overline{SHDN}$  pin are self-biased to V<sub>CC</sub> through their respective 100k pull-up resistors, so the default open-pin state is powered on with the output amplifier signal path disabled. Pulling the  $\overline{EN}$  pin low completes the signal path from the attenuator ladder through the output amplifier. The  $\overline{EN}$  pin essentially provides a fast muting function while the  $\overline{SHDN}$  pin provides slower power on/off function.

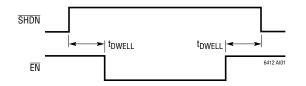

For applications requiring the  $\overline{SHDN}$  function, it is recommended that the output amplifier signal path be disabled with a high  $\overline{EN}$  voltage before transitioning the  $\overline{SHDN}$  signal. When enabling the amplifier, allow at least  $\overline{Sms}$  dwell time between the rising  $\overline{SHDN}$  transition and the falling  $\overline{EN}$  transition to avoid non-monotonic output signal behavior though the VGA. The opposite delay sequence is recommended for the falling  $\overline{SHDN}$  transition, but this is less critical as the output signal amplitude will drop abruptly regardless of the  $\overline{EN}$  pin.

### Layout/Grounding

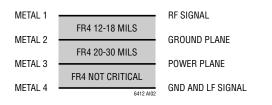

The high frequency performance of the LTC6412 requires special attention to proper RF grounding, bias decoupling and termination. The recommended PCB stack-up for a 4-layer board is shown below for 1oz copper clad FR-4 laminate with a relative dielectric constant,  $\varepsilon_r = 4.2-4.5$  at 1GHz.

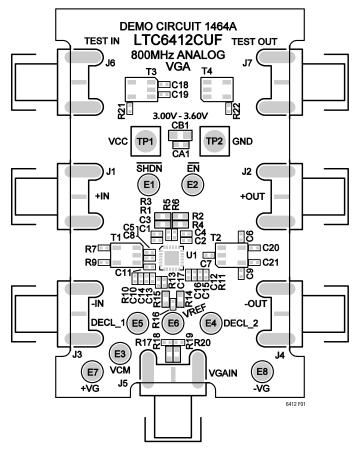

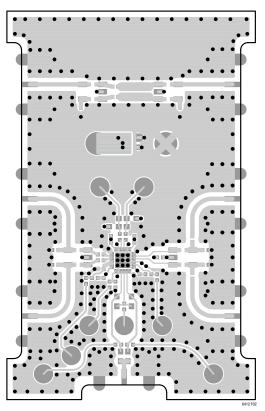

The topside metal and silkscreen drawings for Test Circuit A illustrate the recommended decoupling capacitor placement, signal routing and grounding. Ground vias directly beneath the Exposed Pad are critical; use as many as possible. Ground vias to the other ground pins are less critical.

### ESD

The LTC6412 is protected with reverse-biased ESD diodes on all I/O pins. If any I/O pin is forced one diode drop above the positive supply or one diode drop below the negative supply, then large currents may flow through the diodes. No damage to the devices will occur if the current is kept below 10 mA. The +OUT/–OUT pins have additional series diodes to the positive supply and can sustain approximately 2V overshoot above the positive supply before conducting appreciable currents.

### **Signal Compression Characteristics**

The graph entitled, Input and Output P1dB, illustrates an important characteristic of the LTC6412 VGA. At gain settings above –5dB, the output amplifier limits the linear power handling capability, but at gain settings below –5dB, the input attenuator ladder limits the linear power handling capability. The linear input power limitations at minimum gain do not affect the overall performance of a signal chain if the preceding mixer or amplifier stage exhibits an OP1dB < 19dBm and an OIP3 < 50dBm.

### **Test Circuits**

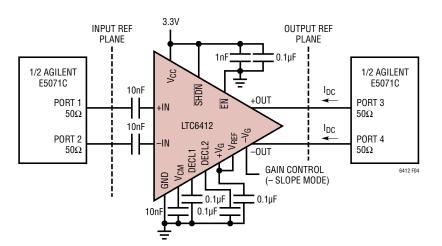

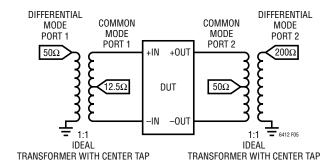

The fully-differential nature of the LTC6412 design requires two test circuits to generate the performance information presented in this data sheet.

Test Circuit A is DC1464A, a 2-port demonstration circuit with input/output balun transformers to allow for direct connection to a 2-port network analyzer or other single-ended 50 $\Omega$  test system. The balun transformers limit the high and low frequency performance of the LTC6412 but allow for simple and reasonably accurate measurements from 70MHz to 380MHz. The gain control signal is supplied to either of the V<sub>G</sub> turrets for DC control measurements or through the V<sub>GAIN</sub> SMA connector for transient control signal measurements. Clip leads to the gain control turrets are susceptible to noise pickup and should be lowpass

filtered to avoid AM upconversion artifacts. While using the  $\pm V_G$  turrets, a 4.7µF capacitor from the  $V_{GAIN}$  SMA input to ground provides an effective lowpass filter.

Typical data curves quoted for Test Circuit A are measured at the plane of the SMA connectors and are NOT corrected for any losses introduced by the input and output baluns, estimated at approximately 0.5dB and 1.2dB, respectively. All typical AC data reported in this data sheet correspond to Test Circuit A, except for mixed-mode S-parameters of the form Sdd21, Scc21, etc.

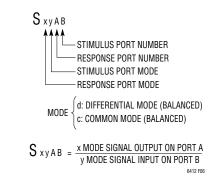

Test Circuit B uses a 4-port network analyzer to measure differential mode and common mode S-parameters beyond the frequency limitations imposed by the balun transformers and associated circuitry. A matching calibration set establishes the measurement reference planes shown in Test Circuit B. The output plane is defined at the edge of the package while the input plane is defined at the edge of the input pair of 0402 capacitors. The IC land and ground via pattern are identical to that shown for Test Circuit A. The ground via pattern directly beneath the package is critical to provide the proper RF ground to produce the RF characteristics quoted in this data sheet. All mixed-mode S-parameter typical data curves of the form SxyAB correspond to Test Circuit B following the definitions described in Figures 5 and 6.

#### **Typical Application Circuits**

Grounding and supply decoupling should closely follow the suggested layout shown for Test Circuit A, but the input and output networks can be customized to suit various application requirements.

On the input side, the differential port impedance is very close to  $50\Omega$  over all gain settings and application frequencies. In a differential signal chain, the differential input signal is easily supplied from a preceding differential output stage with a suitable DC blocking capacitor of approximately 10nF. If the system employs a single-ended input signal to the VGA, then a suitable balun is required to convert to a differential input signal. The passive conversion from  $50\Omega$  single-ended to  $50\Omega$  differential is most effectively accomplished with a 1:1 transmission-line balun such as the ETC1-1-13 or MABA-007159. These 1:1 balun devices are relatively inexpensive and offer excellent electrical characteristics such as low loss, broad band response and good phase matching.

Figure 1. Top Silkscreen for DC1464A. Test Circuit A

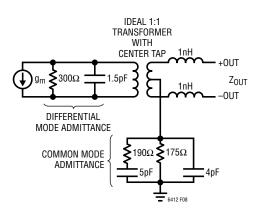

On the output side, the differential port admittance is very close to  $300\Omega$ ||1.5pF across all gain settings and application frequencies. This output port circuit must provide a path for DC output supply current as well as any balun, matching, or filtering functions required by the application. Thus, the design options for the output circuitry are more varied. A brief list of the more common output circuits is shown in Figure 9 along with a few design guidelines to estimate component values. Final design simulations should use the small-signal equivalent circuit model in Figure 8 to properly account for loading effects of the output terminals.

Figure 9a shows the simplest differential output configuration employing two suitable inductors, L1 = L2, to pass the DC supply current without loading the output nodes at the application frequency. The PCB trace widths

Figure 2. Top Metal for DC1464A. Test Circuit A

from the output pins should be narrow in keeping with the high impedance of these terminals; 8 to 10mil trace width on 1oz copper is a good choice. The  $0.1\mu$ F capacitors serve to DC block and decouple as needed. These capacitor values are adequate down to a few MHz and can be scaled down for higher application frequencies.

If bandpass filtering is needed at the VGA output of Figure 9a, then L1 and L2 can be designed to resonate with a shunt capacitor, C<sub>0</sub>, at the frequency of interest,  $\omega = 1/\sqrt{C_0(L1 + L2)}$ . Alternately, L1 = L2 can be designed to resonate with two separate capacitors, C1 = C2, so any common mode noise is filtered as well.

Figure 9b shows a further variation of the tuned differential output where the DC blocking capacitors are brought inside the tank resonator to participate in the bandpass filter and transform the VGA output impedance to a lower value. Here too, the  $C_0$  capacitor can be split into two separate shunt capacitors to ground, so any common mode noise is filtered as well.

Figure 9c shows a flux transformer used to achieve a  $50\Omega$  single-ended output. The flux transformer does not provide the large bandwidth typical of the output transmission-line transformer shown in Figure 3, but it usually performs well over smaller bandwidths, especially when tuned with shunt capacitors (not shown). The flux transformer design eliminates DC blocking capacitors and is attractive in rugged applications where the amplifier output is subjected to ESD events and other forms of transient electrical overstress that do not pass through a typical RF flux transformer such as the MABAES0061.

Figure 9d shows a discrete LC balun suitable for bandwidths of approximately 15% to 30%. Larger bandwidths are difficult to achieve with the number of components shown, and smaller bandwidths are often limited by component tolerance effects. Despite these limitations, the discrete LC balun can be a cost effective output circuit solution. At resonance, the tuned circuit produces an impedance transformation along with the differential-to-single-ended conversion.

### **DC-Coupled Operation**

The LTC6412 is intended for AC-coupled operation. The translation between the fixed input DC common mode voltage and higher open-collector output DC bias point makes it impractical to use in DC-coupled applications.

Figure 3. Demo Board DC1464A Circuit Schematic. Test Circuit A

Figure 4. 4-Port Analysis Schematic. Test Circuit B

Figure 5. Schematic of Mixed-Mode S-Parameters Reported for Test Circuit B

Figure 6. Definition of Mixed-Mode S-Parameters Reported for Test Circuit B

Figure 7. Large-Signal Output Equivalent Circuit Schematic

Figure 8. Small-Signal Output Equivalent Circuit Model

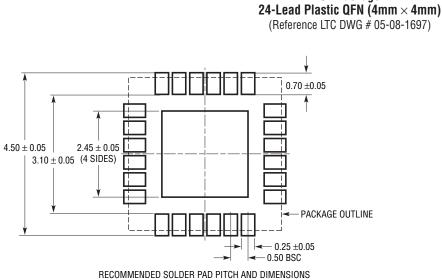

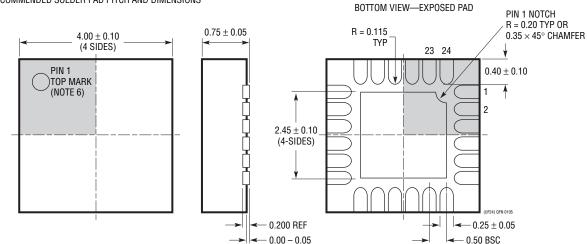

### PACKAGE DESCRIPTION

NOTE: 1. DRAWING PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGD-X)—TO BE APPROVED 2. DRAWING NOT TO SCALE

**UF Package**

ALL DIMENSIONS ARE IN MILLIMETERS

AL DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE, IF PRESENT

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON THE TOP AND BOTTOM OF PACKAGE

### **REVISION HISTORY**

| REV | DATE | DESCRIPTION                                                                       | PAGE NUMBER |

|-----|------|-----------------------------------------------------------------------------------|-------------|

| Α   | 4/10 | Change TC <sub>GAIN</sub> Typical to –0.007dB/°C in DC Electrical Characteristics | 3           |

### **RELATED PARTS**

| PART NUMBER                                      | DESCRIPTION                                                                | COMMENTS                                                                                                                                      |

|--------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed Gain IF Amplifiers//                       | ADC Drivers                                                                |                                                                                                                                               |

| LT1993-2, LT1993-4,<br>LT1993-10                 | 800MHz Differential Amplifier/ADC Drivers                                  | -72dBc IM3 at 70MHz 2V <sub>P-P</sub> Composite, A <sub>V</sub> = 2V/V, 4V/V, 10V/V                                                           |

| LTC6400-8, LTC6400-14,<br>LTC6400-20, LTC6400-26 | 1.8GHz Low Noise, Low Distortion Differential ADC Drivers                  | -71dBc IM3 at 240MHz $2V_{P\text{-}P}$ Composite, $I_S$ = 90mA, $A_V$ = 8dB, 14dB, 20dB, 26dB                                                 |

| LTC6401-8, LTC6401-14,<br>LTC6401-20, LTC6401-26 | 1.3GHz Low Noise, Low Distortion Differential ADC Drivers                  | -74dBc IM3 at 140MHz $2V_{P\text{-}P}$ Composite, $I_S$ = 50mA, $A_V$ = 8dB, 14dB, 20dB, 26dB                                                 |

| LT6402-6, LT6402-12,<br>LT6402-20                | 300MHz Differential Amplifier/ADC Drivers                                  | -71dBc IM3 at 20MHz $2V_{P-P}$ Composite, $A_V = 6dB$ , 12dB, 20dB                                                                            |

| LTC6410-6                                        | 1.4GHz Differential IF Amplifier with Configurable<br>Input Impedance      | OIP3 = 36dBm at 70MHz, Flexible Interface to Mixer IF Port                                                                                    |

| LTC6416                                          | 2GHz, 16-Bit Differential ADC Buffer                                       | –72dBc IM2 at 300MHz $2V_{P-P}$ Composite, $I_S$ = 42mA, $e_N$ = 2.8nV/ $\sqrt{\text{Hz}},$ $A_V$ = 0dB, 300MHz ±0.1dB Bandwidth              |

| LTC6420-20                                       | Dual 1.8GHz Low Noise, Low Distortion<br>Differential ADC Drivers          | Dual Version of the LTC6400-20, $A_V = 20$ dB                                                                                                 |

| LTC6421-20                                       | Dual 1.3GHz Low Noise, Low Distortion<br>Differential ADC Drivers          | Dual Version of the LTC6401-20, $A_V = 20$ dB                                                                                                 |

| IF Amplifiers/ADC Drivers                        | with Digitally Controlled Gain                                             |                                                                                                                                               |

| LT5514                                           | Ultralow Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain | OIP3 = 47dBm at 100MHz, Gain Range 10.5dB to 33dB by 1.5dB                                                                                    |

| LT5524                                           | Low Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain      | OIP3 = 40dBm at 100MHz, Gain Range 4.5dB to 37dB by 1.5dB                                                                                     |

| LT5554                                           | High Dynamic Range 7-Bit Digitally Controlled IF<br>VGA/ADC Driver         | OIP3 = 46dBm at 200MHz, Gain Range 1.725 to 17.6dB by 0.125dB                                                                                 |

| Baseband Differential Am                         | plifiers                                                                   |                                                                                                                                               |

| LT1994                                           | Low Noise, Low Distortion Differential<br>Amplifier/ADC Driver             | 16-Bit SNR, SFDR at 1MHz, Rail-to-Rail Outputs                                                                                                |

| LTC6403-1                                        | Low Noise Rail-to-Rail Output Differential<br>Amplifier/ADC Driver         | 16-Bit SNR, SFDR at 3MHz, Rail-to-Rail Outputs, $e_N = 2.8$ nV/ $\sqrt{Hz}$                                                                   |

| LTC6404-1, LTC6404-2                             | Low Noise Rail-to-Rail Output Differential<br>Amplifier/ADC Driver         | 16-Bit SNR, SFDR at 10MHz, Rail-to-Rail Outputs, e <sub>N</sub> = 1.5nV/√Hz,<br>LTC6404-1 is Unity-Gain Stable, LTC6404-2 is Gain-of-2 Stable |

| LTC6406                                          | 3GHz Rail-to-Rail Input Differential Amplifier/ADC Driver                  | –65dBc IM3 at 50MHz 2V_{P-P} Composite, Rail-to-Rail Inputs, $e_{N}$ = 1.6nV/ $\sqrt{\text{Hz}},$ 18mA                                        |

| LT6411                                           | Low Power Differential ADC Driver/Dual Selectable Gain Amplifier           | -83dBc IM3 at 70MHz $2V_{P-P}$ Composite, $A_V = 1$ , -1 or 2, 16mA, Excellent for Single-Ended to Differential Conversion                    |

| Low Noise DAC for Gain (                         | Control                                                                    |                                                                                                                                               |

| LTC2630-10                                       | Low Power, Internal Reference, Single Supply<br>10-Bit DAC                 | SPI Input, 2.5V Output Range, Resistor Divide Output by ~2:1                                                                                  |

| LTC2640-10                                       | Low Power, Internal Reference, Single Supply<br>10-Bit DAC                 | SPI Input, 2.5V Output Range, Resistor Divide Output by ~2:1                                                                                  |

| LTC2641-12                                       | Low Noise, Low Power, Single Supply 12-Bit DAC                             | SPI Input, Low Glitch Impulse, Power-On to Zero-Scale                                                                                         |

| LTC2642-12                                       | Low Noise, Low Power, Single Supply 12-Bit DAC                             | SPI Input, Low Glitch Impulse, Power-On to Mid-Scale                                                                                          |

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

#### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9