## HardStore 8K x 8 nvSRAM

#### **Features**

# High-performance CMOS nonvolatile static RAM 8192 x 8 bits 25, 35 and 45 ns Access Times

- 12, 20 and 25 ns Output Enable Access TimesHardware STORE Initiation

- ☐ Hardware STORE Initiation (STORE Cycle Time < 10 ms)</p>

- ☐ Automatic STORE Timing

- 10<sup>5</sup> STORE cycles to EEPROM

- ☐ 10 years data retention in EEPROM

- ☐ Automatic RECALL on Power Up

- Hardware RECALL Initiation (RECALL Cycle Time < 20 μs)</li>

- Unlimited RECALL cycles from EEPROM

- Unlimited Read and Write to SRAM

- $\hfill \square$  Single 5 V  $\pm$  10 % Operation

- Operating temperature ranges:

- 0 to 70 °C -40 to 85 °C

- ☐ QS 9000 Quality Standard

- ESD characterization according MIL STD 883C M3015.7-HBM (classification see IC Code Numbers)

- ☐ RoHS compliance and Pb- free

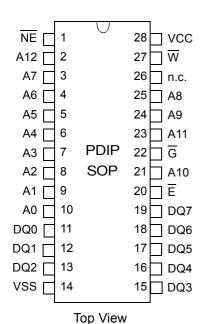

- ☐ Packages: PDIP28 (300 mil) SOP28 (330 mil)

## Description

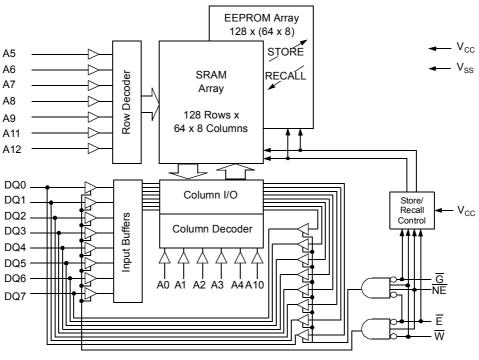

The U630H64 has two separate modes of operation: SRAM mode and nonvolatile mode, determined by the state of the NE pin.

In SRAM mode, the memory operates as an ordinary static RAM. In nonvolatile operation, data is transferred in parallel from SRAM to EEPROM or from EEPROM to SRAM. In this mode SRAM functions are disabled.

The U630H64 is a fast static RAM (25, 35, 45 ns), with a nonvolatile electrically erasable PROM (EEPROM) element incorporated in each static memory cell. The SRAM can be read and written an unlimited number of times, while independent nonvolatile data resides in EEPROM. Data transfers from the SRAM to the EEPROM (the STORE operation), or from the

EEPROM to the SRAM (the RECALL operation) are initiated through the state of the NE pin. The U630H64 combines the high

performance and ease of use of a

fast SRAM with nonvolatile data

integrity.

Once a STORE cycle is initiated, further input or output are disabled until the cycle is completed.

Internally, RECALL is a two step procedure. First, the SRAM data is cleared and second, the nonvolatile information is transferred into the SRAM cells.

The RECALL operation in no way alters the data in the EEPROM cells. The nonvolatile data can be recalled an unlimited number of times.

### **Pin Configuration**

### **Pin Description**

| Signal Name | Signal Description   |

|-------------|----------------------|

| A0 - A12    | Address Inputs       |

| DQ0 - DQ7   | Data In/Out          |

| Ē           | Chip Enable          |

| G           | Output Enable        |

| W           | Write Enable         |

| NE          | Nonvolatile Enable   |

| VCC         | Power Supply Voltage |

| VSS         | Ground               |

### **Block Diagram**

**Truth Table for SRAM Operations**

| Operating Mode       | Ē | NE | w | G | DQ0 - DQ7          |

|----------------------|---|----|---|---|--------------------|

| Standby/not selected | Н | *  | * | * | High-Z             |

| Internal Read        | L | Н  | Н | Н | High-Z             |

| Read                 | L | Н  | Н | L | Data Outputs Low-Z |

| Write                | L | Н  | L | * | Data Inputs High-Z |

<sup>\*</sup> H or L

## **Characteristics**

All voltages are referenced to  $V_{SS}$  = 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified. Dynamic measurements are based on a rise and fall time of  $\leq$  5 ns, measured between 10 % and 90 % of  $V_I$ , as well as input levels of  $V_{IL}$  = 0 V and  $V_{IH}$  = 3 V. The timing reference level of all input and output signals is 1.5 V, with the exception of the  $t_{dis}$ -times and  $t_{en}$ -times, in which cases transition is measured  $\pm$  200 mV from steady-state voltage.

| Absolute Maximum Ratir | ıgs <sup>a</sup> | Symbol           | Min.     | Max.                 | Unit |

|------------------------|------------------|------------------|----------|----------------------|------|

| Power Supply Voltage   |                  | V <sub>CC</sub>  | -0.5     | 7                    | V    |

| Input Voltage          |                  | V <sub>I</sub>   | -0.3     | V <sub>CC</sub> +0.5 | V    |

| Output Voltage         |                  | Vo               | -0.3     | V <sub>CC</sub> +0.5 | V    |

| Power Dissipation      |                  | P <sub>D</sub>   |          | 1                    | W    |

| Operating Temperature  | C-Type<br>K-Type | T <sub>a</sub>   | 0<br>-40 | 70<br>85             | °C   |

| Storage Temperature    |                  | T <sub>stg</sub> | -65      | 150                  | °C   |

a: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Recommended Operating Conditions | Symbol          | Conditions                             | Min. | Max.                 | Unit |

|----------------------------------|-----------------|----------------------------------------|------|----------------------|------|

| Power Supply Voltage             | V <sub>CC</sub> |                                        | 4.5  | 5.5                  | V    |

| Input Low Voltage                | V <sub>IL</sub> | -2 V at Pulse Width<br>10 ns permitted | -0.3 | 0.8                  | V    |

| Input High Voltage               | V <sub>IH</sub> |                                        | 2.2  | V <sub>CC</sub> +0.3 | V    |

|                                                                                                   |                      |                                                                                       |                                                                                                                                                             | С-Т  | уре            | K-T  | уре            |                |

|---------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|----------------|----------------|

| DC Characteristics                                                                                | Symbol               |                                                                                       | onditions                                                                                                                                                   | Min. | Max.           | Min. | Max.           | Unit           |

| Operating Supply Current <sup>b</sup>                                                             | I <sub>CC1</sub>     | V <sub>CC</sub><br>V <sub>IL</sub><br>V <sub>IH</sub>                                 | = 5.5 V<br>= 0.8 V<br>= 2.2 V                                                                                                                               |      |                |      |                |                |

|                                                                                                   |                      | t <sub>c</sub><br>t <sub>c</sub><br>t <sub>c</sub>                                    | = 25 ns<br>= 35 ns<br>= 45 ns                                                                                                                               |      | 90<br>80<br>75 |      | 95<br>85<br>80 | mA<br>mA<br>mA |

| Average Supply Current during STORE <sup>c</sup>                                                  | I <sub>CC2</sub>     | V <sub>CC</sub> E W V <sub>IL</sub> V <sub>IH</sub>                                   | = $5.5 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ -0.2 V<br>$\geq \text{V}_{\text{CC}}$ -0.2 V<br>$\leq 0.2 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ -0.2 V |      | 6              |      | 7              | mA             |

| Standby Supply Current <sup>d</sup> (Cycling TTL Input Levels)                                    | I <sub>CC(SB)1</sub> | V <sub>CC</sub>                                                                       | = 5.5 V<br>≥ V <sub>IH</sub>                                                                                                                                |      |                |      |                |                |

|                                                                                                   |                      | t <sub>c</sub><br>t <sub>c</sub><br>t <sub>c</sub>                                    | = 25 ns<br>= 35 ns<br>= 45 ns                                                                                                                               |      | 30<br>23<br>20 |      | 34<br>27<br>23 | mA<br>mA<br>mA |

| Average Supply Current<br>at t <sub>cR</sub> = 200 ns <sup>b</sup><br>(Cycling CMOS Input Levels) | I <sub>CC3</sub>     | $\begin{array}{c} \underline{V}_{CC} \\ \overline{W} \\ V_{IL} \\ V_{IH} \end{array}$ | = $5.5 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ - $0.2 \text{ V}$<br>$\leq 0.2 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ - $0.2 \text{ V}$                 |      | 15             |      | 15             | mA             |

| Standby Supply Current <sup>d</sup> (Stable CMOS Input Levels)                                    | I <sub>CC(SB)</sub>  | V <sub>CC</sub><br>E<br>V <sub>IL</sub><br>V <sub>IH</sub>                            | = $5.5 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ -0.2 V<br>$\leq 0.2 \text{ V}$<br>$\geq \text{V}_{\text{CC}}$ -0.2 V                                       |      | 1              |      | 1              | mA             |

b: I<sub>CC1</sub> and I<sub>CC3</sub> are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded. The current I<sub>CC1</sub> is measured for WRITE/READ - ratio of 1/2.

c: I<sub>CC2</sub> is the average current required for the duration of the STORE cycle (STORE Cycle Time).

d: Bringing  $\overline{E} \ge V_{IH}$  will not produce standby current levels until any nonvolatile cycle in progress has timed out. See MODE SELECTION table. The current  $I_{CC(SB)1}$  is measured for WRITE/READ - ratio of 1/2.

# U630H64

| DC Characteristics                                        | Symbol                               |                                                       | onditions                     | С-Т  | C-Type |      | K-Type |                          |

|-----------------------------------------------------------|--------------------------------------|-------------------------------------------------------|-------------------------------|------|--------|------|--------|--------------------------|

| DC Characteristics                                        | Symbol                               | Contaitions                                           |                               | Min. | Max.   | Min. | Max.   | Unit                     |

| Output High Voltage Output Low Voltage                    | V <sub>OH</sub><br>V <sub>OL</sub>   | V <sub>CC</sub><br>I <sub>OH</sub><br>I <sub>OL</sub> | = 4.5 V<br>=-4 mA<br>= 8 mA   | 2.4  | 0.4    | 2.4  | 0.4    | V<br>V                   |

| Output High Current Output Low Current                    | I <sub>OH</sub><br>I <sub>OL</sub>   | V <sub>CC</sub><br>V <sub>OH</sub><br>V <sub>OL</sub> | = 4.5 V<br>= 2.4 V<br>= 0.4 V | 8    | -4     | 8    | -4     | mA<br>mA                 |

| Input Leakage Current                                     |                                      | V <sub>CC</sub>                                       | = 5.5 V                       |      |        |      |        |                          |

| High<br>Low                                               | I <sub>IH</sub><br>I <sub>IL</sub>   | V <sub>IH</sub><br>V <sub>IL</sub>                    | = 5.5 V<br>= 0 V              | -1   | 1      | -1   | 1      | μ <b>Α</b><br>μ <b>Α</b> |

| Output Leakage Current                                    |                                      | $V_{CC}$                                              | = 5.5 V                       |      |        |      |        |                          |

| High at Three-State- Output<br>Low at Three-State- Output | I <sub>OHZ</sub><br>I <sub>OLZ</sub> | V <sub>OH</sub><br>V <sub>OL</sub>                    | = 5.5 V<br>= 0 V              | -1   | 1      | -1   | 1      | μ <b>Α</b><br>μ <b>Α</b> |

## **SRAM Memory Operations**

| No. | Switching Characteristics                        | Syn                 | nbol                | 2    | 25   |      | 35   |      | .5   | Unit |

|-----|--------------------------------------------------|---------------------|---------------------|------|------|------|------|------|------|------|

| NO. | Read Cycle                                       | Alt.                | IEC                 | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

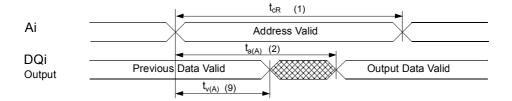

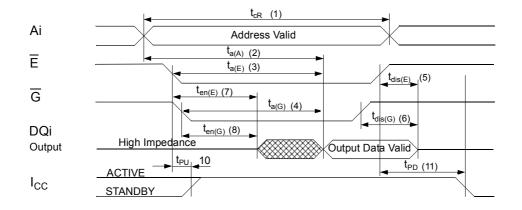

| 1   | Read Cycle Time <sup>f</sup>                     | t <sub>AVAV</sub>   | t <sub>cR</sub>     | 25   |      | 35   |      | 45   |      | ns   |

| 2   | Address Access Time to Data Valid <sup>9</sup>   | t <sub>AVQV</sub>   | t <sub>a(A)</sub>   |      | 25   |      | 35   |      | 45   | ns   |

| 3   | Chip Enable Access Time to Data Valid            | t <sub>ELQV</sub>   | t <sub>a(E)</sub>   |      | 25   |      | 35   |      | 45   | ns   |

| 4   | Output Enable Access Time to Data Valid          | t <sub>GLQV</sub>   | t <sub>a(G)</sub>   |      | 12   |      | 20   |      | 25   | ns   |

| 5   | E HIGH to Output in High-Zh                      | t <sub>EHQZ</sub>   | t <sub>dis(E)</sub> |      | 13   |      | 17   |      | 20   | ns   |

| 6   | G HIGH to Output in High-Z <sup>h</sup>          | t <sub>GHQZ</sub>   | t <sub>dis(G)</sub> |      | 13   |      | 17   |      | 20   | ns   |

| 7   | E LOW to Output in Low-Z                         | t <sub>ELQX</sub>   | t <sub>en(E)</sub>  | 5    |      | 5    |      | 5    |      | ns   |

| 8   | G LOW to Output in Low-Z                         | t <sub>GLQX</sub>   | t <sub>en(G)</sub>  | 0    |      | 0    |      | 0    |      | ns   |

| 9   | Output Hold Time after Addr. Change <sup>g</sup> | t <sub>AXQX</sub>   | t <sub>v(A)</sub>   | 3    |      | 3    |      | 3    |      | ns   |

| 10  | Chip Enable to Power Active <sup>e</sup>         | t <sub>ELICCH</sub> | t <sub>PU</sub>     | 0    |      | 0    |      | 0    |      | ns   |

| 11  | Chip Disable to Power Standby <sup>d, e</sup>    | t <sub>EHICCL</sub> | t <sub>PD</sub>     |      | 25   |      | 35   |      | 45   | ns   |

e: Parameter guaranteed but not tested.

f: Device is continuously selected with  $\overline{E}$  and  $\overline{G}$  both LOW.

g: Address valid prior to or coincident with  $\overline{E}$  transition LOW. h: Measured  $\pm$  200 mV from steady state output voltage.

Read Cycle 1: Ai-controlled (during Read cycle:  $\overline{E} = \overline{G} = V_{IL}$ ,  $\overline{W} = \overline{NE} = V_{IH}$ )<sup>f</sup>

Read Cycle 2:  $\overline{G}$ -,  $\overline{E}$ -controlled (during Read cycle:  $\overline{W} = \overline{NE} = V_{IH})^g$

| No. | Switching Characteristics                 |                   | Symbol            |                       | 2    | 5    | 3    | 5    | 4    | 5    | Hnit |

|-----|-------------------------------------------|-------------------|-------------------|-----------------------|------|------|------|------|------|------|------|

| NO. | Write Cycle                               | Alt. #1           | Alt. #2           | IEC                   | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| 12  | Write Cycle Time                          | t <sub>AVAV</sub> | t <sub>AVAV</sub> | t <sub>cW</sub>       | 25   |      | 35   |      | 45   |      | ns   |

| 13  | Write Pulse Width                         | t <sub>WLWH</sub> |                   | t <sub>w(W)</sub>     | 20   |      | 30   |      | 35   |      | ns   |

| 14  | Write Pulse Width Setup Time              |                   | t <sub>WLEH</sub> | t <sub>su(W)</sub>    | 20   |      | 30   |      | 35   |      | ns   |

| 15  | Address Setup Time                        | t <sub>AVWL</sub> | t <sub>AVEL</sub> | t <sub>su(A)</sub>    | 0    |      | 0    |      | 0    |      | ns   |

| 16  | Address Valid to End of Write             | t <sub>AVWH</sub> | t <sub>AVEH</sub> | t <sub>su(A-WH)</sub> | 20   |      | 30   |      | 35   |      | ns   |

| 17  | Chip Enable Setup Time                    | t <sub>ELWH</sub> |                   | t <sub>su(E)</sub>    | 20   |      | 30   |      | 35   |      | ns   |

| 18  | Chip Enable to End of Write               |                   | t <sub>ELEH</sub> | t <sub>w(E)</sub>     | 20   |      | 30   |      | 35   |      | ns   |

| 19  | Data Setup Time to End of Write           | t <sub>DVWH</sub> | t <sub>DVEH</sub> | t <sub>su(D)</sub>    | 12   |      | 18   |      | 20   |      | ns   |

| 20  | Data Hold Time after End of Write         | t <sub>WHDX</sub> | t <sub>EHDX</sub> | t <sub>h(D)</sub>     | 0    |      | 0    |      | 0    |      | ns   |

| 21  | Address Hold after End of Write           | t <sub>WHAX</sub> | t <sub>EHAX</sub> | t <sub>h(A)</sub>     | 0    |      | 0    |      | 0    |      | ns   |

| 22  | W LOW to Output in High-Z <sup>h, i</sup> | t <sub>WLQZ</sub> |                   | t <sub>dis(W)</sub>   |      | 10   |      | 13   |      | 15   | ns   |

| 23  | W HIGH to Output in Low-Z                 | t <sub>WHQX</sub> |                   | t <sub>en(W)</sub>    | 5    |      | 5    |      | 5    |      | ns   |

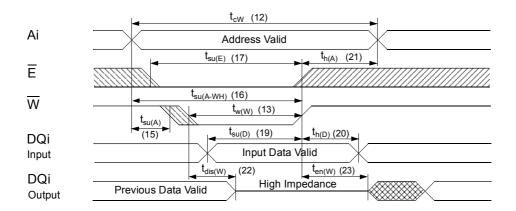

## Write Cycle #1: W-controlled

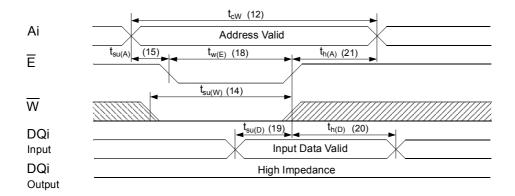

## Write Cycle #2: E-controlled

- $\underline{\underline{\mathsf{If}}\ \overline{\mathsf{W}}\ \mathsf{is}\ \mathsf{LOW}\ \mathsf{and}}$  when  $\overline{\mathsf{E}}$  goes LOW, the outputs remain in the high impedance state.

- j:  $\overline{E}$  or  $\overline{W}$  and  $\overline{NE}$  must be  $\geq V_{IH}$  during address transitions.

## **Nonvolatile Memory Operations**

| No. | STORE Cycle Inhibit and                  | Sym                  | nbol | Min.    | Max.   | Unit |  |

|-----|------------------------------------------|----------------------|------|---------|--------|------|--|

| NO. | Automatic Power Up RECALL                | Alt.                 | IEC  | IVIIII. | IVIAA. | Unit |  |

| 24  | Power Up RECALL Duration <sup>k, e</sup> | t <sub>RESTORE</sub> |      |         | 650    | μS   |  |

|     | Low Voltage Trigger Level                | V <sub>SWITCH</sub>  |      | 4.0     | 4.5    | V    |  |

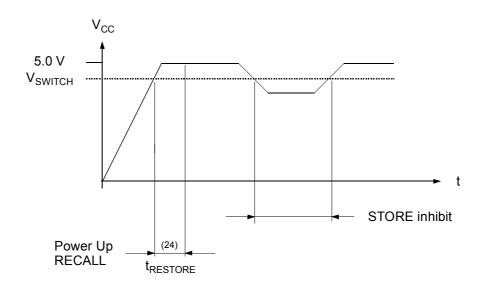

k:  $t_{\text{RESTORE}}$  starts from the time  $V_{\text{CC}}$  rises above  $V_{\text{SWITCH}}$ .

## STORE Cycle Inhibit and Automatic Power Up RECALL

## **Mode Selection**

| Ē      | w      | G      | NE     | Mode               | Power            | Notes |

|--------|--------|--------|--------|--------------------|------------------|-------|

| L      | Н      | L      | L      | Nonvolatile RECALL | Active           | I     |

| L      | L      | Н      | L      | Nonvolatile STORE  | I <sub>CC2</sub> |       |

| L<br>L | L<br>H | L<br>H | L<br>* | No operation       | Active           |       |

<sup>\*</sup> H or L

I: An automatic RECALL also takes place at power up, starting when  $V_{CC}$  exceeds  $V_{SWITCH}$  and takes  $t_{RESTORE}$ .  $V_{CC}$  must not drop below  $V_{SWITCH}$  once it has been exceeded for the RECALL to function properly.

# U630H64

## **STORE Cycles**

| No. | STORE Cycle W-controlled                 | Sym               | nbol                | Min.    | Max.   | Unit  |

|-----|------------------------------------------|-------------------|---------------------|---------|--------|-------|

| NO. |                                          | Alt.              | IEC                 | IVIIII. | iviax. | Oilit |

| 25  | STORE Cycle Time <sup>m</sup>            | t <sub>WLQX</sub> | t <sub>d(W)S</sub>  |         | 10     | ms    |

| 26  | STORE Initiation Cycle Time <sup>n</sup> | t <sub>WLNH</sub> | t <sub>w(W)S</sub>  | 25      |        | ns    |

| 27  | Output Disable Setup to NE Fall          | t <sub>GHNL</sub> | t <sub>su(G)S</sub> | 5       |        | ns    |

| 28  | NE Setup                                 | t <sub>NLWL</sub> | t <sub>su(N)S</sub> | 5       |        | ns    |

| 29  | Chip Enable Setup                        | t <sub>ELWL</sub> | t <sub>su(E)S</sub> | 5       |        | ns    |

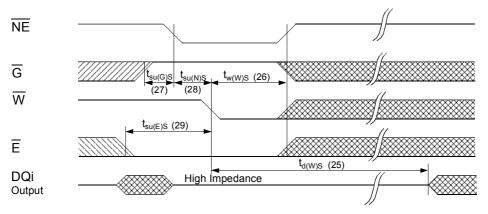

# STORE Cycle: W-controlled°

| No  | STORE Cycle E-controlled       | Sym                | nbol                | Min.    | Max.   | Unit  |

|-----|--------------------------------|--------------------|---------------------|---------|--------|-------|

| No. |                                | Alt.               | IEC                 | IVIIII. | iviax. | Offic |

| 30  | STORE Cycle Time               | t <sub>ELQXS</sub> | t <sub>d(E)S</sub>  |         | 10     | ms    |

| 31  | STORE Initiation Cycle Time    | t <sub>ELNHS</sub> | t <sub>w(E)S</sub>  | 25      |        | ns    |

| 32  | Output Disable Setup to E Fall | t <sub>GHEL</sub>  | t <sub>su(G)S</sub> | 5       |        | ns    |

| 33  | NE Setup                       | t <sub>NLEL</sub>  | t <sub>su(N)S</sub> | 5       |        | ns    |

| 34  | Write Enable Setup             | t <sub>WLEL</sub>  | t <sub>su(W)S</sub> | 5       |        | ns    |

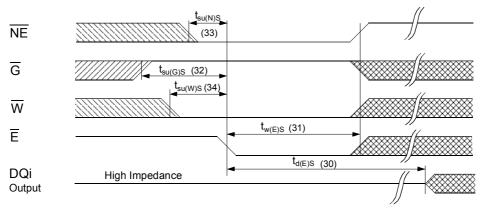

## STORE Cycle: E-controlled<sup>o</sup>

## **RECALL Cycles**

| No. | RECALL Cycle NE-controlled                | Symbol            |                      | M:   | Max.   | llmit |

|-----|-------------------------------------------|-------------------|----------------------|------|--------|-------|

|     |                                           | Alt.              | IEC                  | Min. | iviax. | Unit  |

| 35  | RECALL Cycle Time <sup>p</sup>            | t <sub>NLQX</sub> | t <sub>d(N)R</sub>   |      | 20     | μS    |

| 36  | RECALL Initiation Cycle Time <sup>q</sup> | t <sub>NLNH</sub> | t <sub>w(N)R</sub>   | 25   |        | ns    |

| 37  | Output Enable Setup                       | t <sub>GLNL</sub> | t <sub>su(G)R</sub>  | 5    |        | ns    |

| 38  | Write Enable Setup                        | t <sub>WHNL</sub> | t <sub>su(W)R</sub>  | 5    |        | ns    |

| 39  | Chip Enable Setup                         | t <sub>ELNL</sub> | t <sub>su(E)R</sub>  | 5    |        | ns    |

| 40  | NE Fall to Output Inactive                | t <sub>NLQZ</sub> | t <sub>dis(N)R</sub> |      | 25     | ns    |

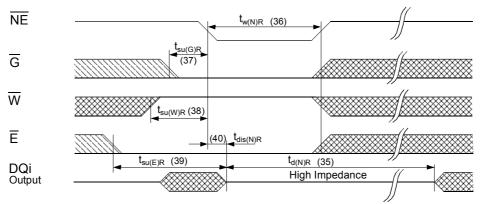

## RECALL Cycle: NE-controlled<sup>o</sup>

| No. | RECALL Cycle E-controlled    | Symbol             |                     | Min.  | Max.   | Unit |

|-----|------------------------------|--------------------|---------------------|-------|--------|------|

|     |                              | Alt.               | IEC                 | WIII. | iviax. | Oill |

| 41  | RECALL Cycle Time            | t <sub>ELQXR</sub> | $t_{d(E)R}$         |       | 20     | μS   |

| 42  | RECALL Initiation Cycle Time | t <sub>ELNHR</sub> | t <sub>w(E)R</sub>  | 25    |        | ns   |

| 43  | NE Setup                     | t <sub>NLEL</sub>  | t <sub>su(N)R</sub> | 5     |        | ns   |

| 44  | Output Enable Setup          | t <sub>GLEL</sub>  | t <sub>su(G)R</sub> | 5     |        | ns   |

| 45  | Write Enable Setup           | t <sub>WHEL</sub>  | t <sub>su(W)R</sub> | 5     |        | ns   |

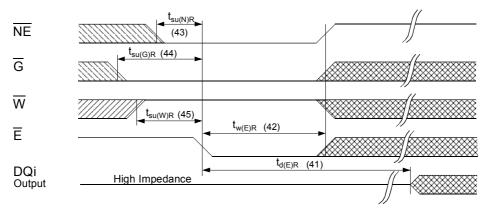

# RECALL Cycle: E-controlled<sup>o</sup>

## U630H64

| No. | RECALL Cycle G-controlled    | Symbol             |                     | Min.    | Max.   | Unit  |

|-----|------------------------------|--------------------|---------------------|---------|--------|-------|

|     |                              | Alt.               | IEC                 | IVIIII. | iviax. | Oilit |

| 46  | RECALL Cycle Time            | t <sub>GLQXR</sub> | t <sub>d(G)R</sub>  |         | 20     | μS    |

| 47  | RECALL Initiation Cycle Time | t <sub>GLNH</sub>  | t <sub>w(G)R</sub>  | 25      |        | ns    |

| 48  | NE Setup                     | t <sub>NLGL</sub>  | t <sub>su(N)R</sub> | 5       |        | ns    |

| 49  | Write Enable Setup           | t <sub>WHGL</sub>  | t <sub>su(W)R</sub> | 5       |        | ns    |

| 50  | Chip Enable Setup            | t <sub>ELGL</sub>  | t <sub>su(E)R</sub> | 5       |        | ns    |

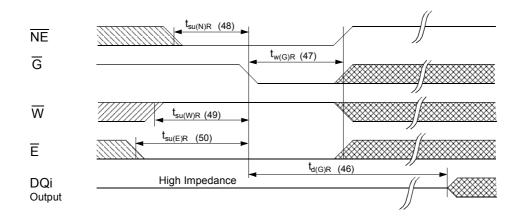

## RECALL Cycle: G-controlledo, r

- m: Measured with  $\overline{W}$  and  $\overline{NE}$  both returned HIGH, and  $\overline{G}$  returned LOW. Note that STORE cycles are inhibited/aborted by  $V_{CC} < V_{SWITCH} (STORE inhibit)$ .

- Once  $t_{w(W)S}$  has been satisfied by  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{E}$ , the STORE cycle is completed automatically. Any of  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{E}$  may be used to terminate the STORE initiation cycle.

- If  $\overline{E}$  is LOW for any period of time in which  $\overline{W}$  is HIGH while  $\overline{G}$  and  $\overline{NE}$  are LOW, than a RECALL cycle may be initiated.

- For  $\overline{E}$ -controlled STORE during  $t_{w(E)S}$   $\overline{W}$ ,  $\overline{G}$ ,  $\overline{NE}$  have to be static. Measured with  $\overline{W}$  and  $\overline{NE}$  both HIGH, and  $\overline{G}$  and  $\overline{E}$  LOW. Once  $t_{w(N)R}$  has been satisfied by  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{E}$ , the RECALL cycle is completed automatically. Any of  $\overline{NE}$ ,  $\overline{G}$  or  $\overline{E}$  may be used to terminate the RECALL initiation cycle.

- If  $\overline{W}$  is LOW at any point in which both  $\overline{E}$  and  $\overline{NE}$  are LOW and  $\overline{G}$  is HIGH, than a STORE cycle will be initiated instead of a RECALL.

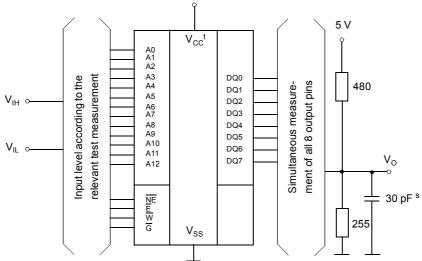

#### **Test Configuration for Functional Check**

- s: In measurement of  $t_{dis}$ -times and  $t_{en}$ -times the capacitance is 5 pF.

- t: Between  $V_{CC}$  and  $V_{SS}$  must be connected a high frequency bypass capacitor 0.1  $\mu F$  to avoid disturbances.

| Capacitance <sup>e</sup> | Conditions                          | Symbol | Min. | Max. | Unit |

|--------------------------|-------------------------------------|--------|------|------|------|

| Input Capacitance        | $V_{CC} = 5.0 V$ $V_{I} = V_{SS}$   | Cı     |      | 8    | pF   |

| Output Capacitance       | f = 1 MHz<br>T <sub>a</sub> = 25 °C | Co     |      | 7    | pF   |

All pins not under test must be connected with ground by capacitors.

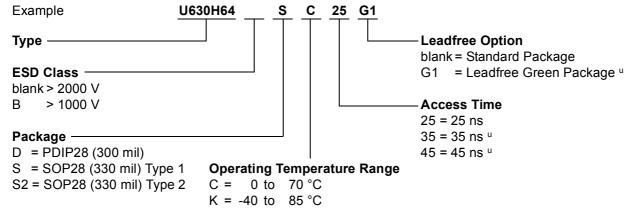

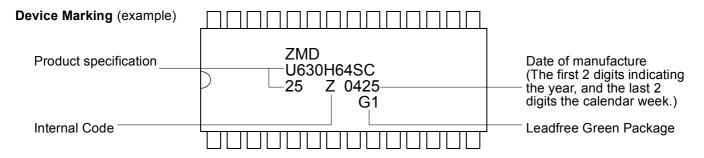

#### **Ordering Code**

u: on special request

#### **Device Operation**

The U630H64 has two separate modes of operation: SRAM mode and nonvolatile mode, determined by the state of the  $\overline{\text{NE}}$  pin. In SRAM mode, the memory operates as a standard fast static RAM. In nonvolatile mode, data is transferred from SRAM to EEPROM (the STORE operation) or from EEPROM to SRAM (the RECALL operation). In this mode SRAM functions are disabled.

#### **SRAM READ**

The U630H64 performs a READ cycle whenever E and  $\overline{G}$  are LOW while  $\overline{W}$  and  $\overline{NE}$  are HIGH. The address specified on pins A0 - A12 determines which of the 8192 data bytes will be accessed. When the READ is initiated by an address transition, the outputs will be valid after a delay of  $t_{cR}$ . If the READ is initiated by  $\overline{E}$  or  $\overline{G}$ , the outputs will be valid at  $t_{a(E)}$  or at  $t_{a(G)}$ , whichever is later. The data outputs will repeatedly respond to address changes within the  $t_{cR}$  access time without the need for transition on any control input pins, and will remain valid until another address change or until  $\overline{E}$  or  $\overline{G}$  is brought HIGH or  $\overline{W}$  or  $\overline{NE}$  is brought LOW.

#### **SRAM WRITE**

A WRITE cycle is performed whenever  $\overline{E}$  and  $\overline{W}$  are LOW and  $\overline{NE}$  is HIGH. The address inputs must be stable prior to entering the WRITE cycle and must remain stable until either  $\overline{E}$  or  $\overline{W}$  goes HIGH at the end of the cycle. The data on pins DQ0 - 7 will be written into the memory if it is valid  $t_{su(D)}$  before the end of a  $\overline{W}$  controlled WRITE or  $t_{su(D)}$  before the end of an  $\overline{E}$  controlled WRITE.

It is recommended that  $\overline{G}$  is kept HIGH during the entire WRITE cycle to avoid data bus contention on the common I/O lines. If  $\overline{G}$  is left LOW, internal circuitry will turn off the output buffers  $t_{\text{dis}\,(W)}$  after  $\overline{W}$  goes LOW.

#### **Noise Consideration**

The U630H64 is a high speed memory and therefore must have a high frequency bypass capacitor of approximately 0.1  $\mu\text{F}$  connected between  $\text{V}_{\text{CC}}$  and  $\text{V}_{\text{SS}}$  using leads and traces that are as short as possible. As with all high speed CMOS ICs, normal carefull routing of power, ground and signals will help prevent noise problems.

## **Hardware Nonvolatile STORE**

A STORE cycle is performed when  $\overline{\text{NE}}$ ,  $\overline{\text{E}}$  and  $\overline{\text{W}}$  are LOW while  $\overline{\text{G}}$  is HIGH. While any sequence to achieve this state will initiate a STORE, only  $\overline{\text{W}}$  initiation and  $\overline{\text{E}}$  initiation are practical without risking an unintentional SRAM WRITE that would disturb SRAM data. During a

STORE cycle, previous nonvolatile data is erased and the SRAM contents are then programmed into nonvolatile elements. Once a STORE cycle is initiated, further input and output is disabled and the DQ0 - 7 pins are tristated until the cycle is completed.

If  $\overline{E}$  and  $\overline{G}$  are LOW and  $\overline{W}$  and  $\overline{NE}$  are HIGH at the end of the cycle, a READ will be performed and the outputs will go active, indicating the end of the STORE.

#### **Hardware Nonvolatile RECALL**

A RECALL cycle is performed when  $\overline{E}$ ,  $\overline{G}$  and  $\overline{NE}$  are LOW while  $\overline{W}$  is HIGH. Like the STORE cycle, RECALL is initiated when the last of the three clock-signals goes to the RECALL state. Once initiated, the RECALL cycle will take "RECALL Cycle Time" to complete, during which all inputs are ignored. When the RECALL completes, any READ or WRITE state on the input pins will take effect.

Internally, RECALL is a two step procedure. First, the SRAM data is cleared and second, the nonvolatile information is transferred into the SRAM cells. The RECALL in no way alters the data in the nonvolatile cells. The nonvolatile data can be recalled an unlimited number of times.

Like the STORE cycle, a transition must occur on some control pins to cause a RECALL, preventing inadvertend multi-triggering.

## **Automatic Power Up RECALL**

On power up, once  $V_{CC}$  exceeds the sense voltage of  $V_{SWITCH}$ , a RECALL cycle is automatically initiated. The voltage on the  $V_{CC}$  pin must not drop below  $V_{SWITCH}$  once it has risen above it in order for the RECALL to operate properly. Due to this automatic RECALL, SRAM operation cannot commence until  $t_{RESTORE}$  after  $V_{CC}$  exceeds  $V_{SWITCH}$ . If the U630H64 is in a WRITE state at the end of power up RECALL, the SRAM data will be corrupted.

To help avoid this situation, a 10 K $\Omega$  resistor should be connected between  $\overline{W}$  and system  $V_{CC}$

### **Hardware Protection**

The U630H64 offers two levels of protection to suppress inadvertent STORE cycles. If the control signals  $(\overline{E},\,\overline{G},\,\overline{W}$  and  $\overline{NE})$  remain in the STORE condition at the end of a STORE cycle, a second STORE cycle will not be started. The STORE (or RECALL) will be initiated only after a transition on any one of these signals to the required state. In addition to multi-trigger protection, the U630H64 offers hardware protection through  $V_{CC}$  Sense. When  $V_{CC}$  <  $V_{SWITCH}$  the externally initiated STORE operation will be inhibited.

## **Low Average Active Power**

The U630H64 has been designed to draw significantly less power when  $\overline{E}$  is LOW (chip enabled) but the access cycle time is longer than 55 ns.

When  $\overline{E}$  is HIGH the chip consumes only standby current.

The overall average current drawn by the part depends on the following items:

- 1. CMOS or TTL input levels

- 2. the time during which the chip is disabled ( $\overline{E}$  HIGH)

- 3. the cycle time for accesses ( $\overline{E}$  LOW)

- 4. the ratio of READs to WRITEs

- 5. the operating temperature

- 6. the V<sub>CC</sub> level

The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

#### LIFE SUPPORT POLICY

ZMD products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the ZMD product could create a situation where personal injury or death may occur. Components used in life-support devices or systems must be expressly authorized by ZMD for such purpose.

#### LIMITED WARRANTY

The information in this document has been carefully checked and is believed to be reliable. However Zentrum Mikroelektronik Dresden AG (ZMD) makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it. The information in this document describes the type of component and shall not be considered as assured characteristics.

ZMD does not guarantee that the use of any information contained herein will not infringe upon the patent, trademark, copyright, mask work right or other rights of third parties, and no patent or licence is implied hereby. This document does not in any way extent ZMD's warranty on any product beyond that set forth in its standard terms and conditions of sale.

ZMD reserves terms of delivery and reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9