# High Efficiency Step-Up LED Driver with Integrated Power Diode

#### **Features**

- Wide input range: 2.7V to 5.5V

- Highly integrated solution with high efficiency

- ► Integrated 30V power diode

- ▶ Integrated 30V power MOSFET

- Integrated 2-channel current sinks, up to 8-LEDs per string

- ▶ High accuracy up to 30mA/ch

- ▶ 0.6% current matching at 20mA

- ▶ 1.5% current accuracy at 20mA

- · Dual dimming control scheme

- ▶ I<sup>2</sup>C interface control with 256 steps

- ▶ Wide range PWM Dimming for CABC

- 100Hz to 100kHz Frequency

- 0.1%~100% Duty Cycle at 10kHz

- Input PWM glitch filter

- I2C interface for various controls

- Programmable current sink ramp up/down time and shape (Exponential/Linear)

- Selectable 1MHz and 500kHz switching frequency with frequency shift option

- Programmable OVP (30V/24V), current limit (1A/0.7A) and LX pin slew rate

- LED open/short protection

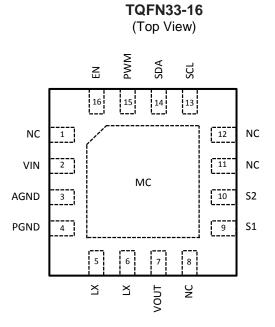

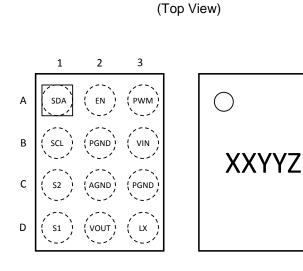

- Pb-free Packages: TQFN33-16, WLCSP-12

- -40°C to +85°C Temperature Range

# **Applications**

- Smartphone/Tablet Backlight

- PDA/GPS Backlight

# **Brief Description**

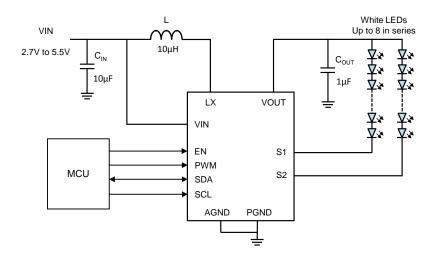

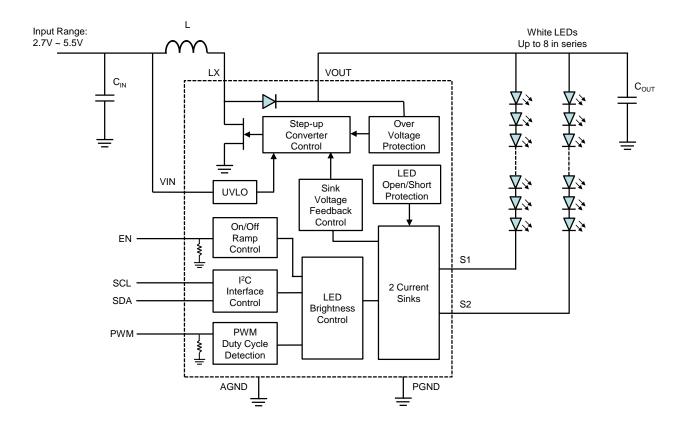

KTD3122 is the ideal power solution for white LED backlighting used with small to medium size LCD panels. It is a highly integrated step-up converter accommodating single cell lithium ion batteries or 5V regulated supply. KTD3122 integrates a 30V power diode and a 30V power MOSFET as well as compensation and soft start circuitry, which results in a simpler and smaller solution with much fewer external components. Adjustable switching frequency (1MHz/500kHz) and OVP threshold (30V/24V) allow the use of a smaller inductor and capacitor to further reduce the solution size.

KTD3122 has two regulated current sinks up to 30mA per string. With a maximum of 30V at the output of the step-up converter, each string can connect up to 8 LEDs in series, or up to 16 LEDs total.

KTD3122 is equipped with I<sup>2</sup>C interface for various controls. For additional flexibility, wide frequency (100Hz to 100kHz) and duty cycle range (0.1% to 100% at 10kHz) PWM dimming control is included and can support Content Adaptive Brightness Control (CABC).

Various protection features are built into KTD3122, including cycle-by-cycle input current limit protection, output over-voltage protection, LED fault (open or short) protection and thermal shutdown protection.

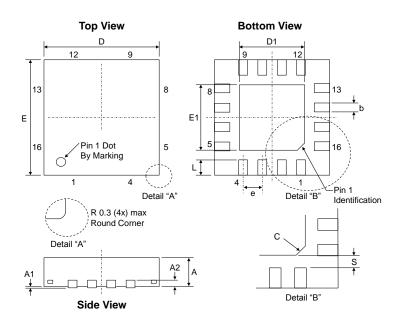

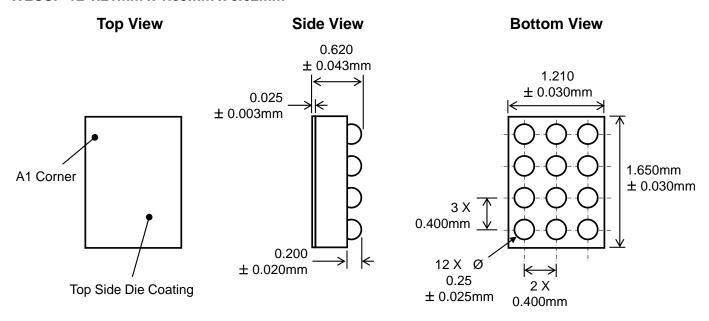

KTD3122 is available in a RoHS compliant and Green 16-lead 3mm x 3mm x 0.75mm Thin-QFN or 12-ball 1.21mm x 1.65mm x 0.62mm WLCSP package.

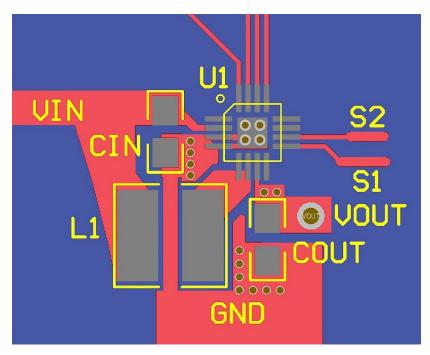

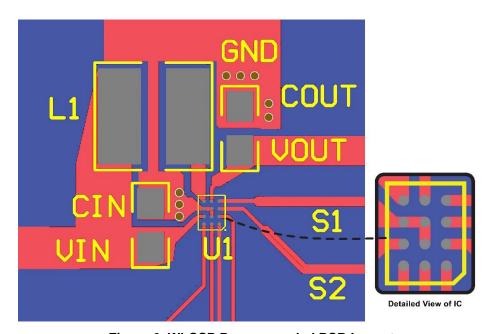

# **Typical Application**

# **Pin Descriptions**

| Pin #<br>(TQFN33-16) | Pin #<br>(WLCSP-12) | Name | Function                                                                                                                            |

|----------------------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 14                   | A1                  | SDA  | Bi-direction data pin of the I <sup>2</sup> C interface. If I <sup>2</sup> C interface is not used, SDA should be connected to VIN. |

| 16                   | A2                  | EN   | IC enable pin. An active logic high enables the device. There is an internal $400k\Omega$ pull-down resistor at this pin.           |

| 15                   | А3                  | PWM  | PWM dimming input pin. There is an internal 400kΩ pull-down resistor at this pin.                                                   |

| 13                   | B1                  | SCL  | Clock input pin of the I <sup>2</sup> C interface. If I <sup>2</sup> C interface is not used, SCL should be connected to VIN.       |

| 4                    | B2, C3              | PGND | Power Ground pin                                                                                                                    |

| 2                    | В3                  | VIN  | Input supply pin for the device                                                                                                     |

| 10                   | C1                  | S2   | Regulated output current sink #2                                                                                                    |

| 3                    | C2                  | AGND | Analog Ground pin                                                                                                                   |

| 9                    | D1                  | S1   | Regulated output current sink #1                                                                                                    |

| 7                    | D2                  | VOUT | Output pin of the step-up converter                                                                                                 |

| 5, 6                 | D3                  | LX   | Switching pin of the step-up converter                                                                                              |

| 1, 8, 11,12          | -                   | NC   | Not internally connected                                                                                                            |

| MC                   | -                   |      | Metal chassis. Connect to ground for electrical and thermal usage.  MC is internally connected to Analog Ground pin.                |

12-Bump 1.21mm x 1.65mm x 0.62mm WLCSP Package YYZ (Date Code and Assembly Code) XX = Device Code (Top Mask)

WLCSP-12

# Absolute Maximum Ratings<sup>1</sup>

#### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol            | Description                                      | Value           | Units |

|-------------------|--------------------------------------------------|-----------------|-------|

| VIN               | Input voltage pins                               | -0.3 to 6       | V     |

| LX, VOUT          | High voltage pins                                | -0.3 to 34      | V     |

| S1, S2            | High voltage pins                                | -0.3 to 22      | V     |

| SCL, SDA, PWM, EN | Control pins                                     | -0.3 to VIN+0.3 | V     |

| TJ                | Operating Temperature Range                      | -40 to 150      | °C    |

| Ts                | Storage Temperature Range                        | -65 to 150      | °C    |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at leads, 10 sec) | 300             | °C    |

| ESD               | HBM electrical static discharge                  | 2.0             | kV    |

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

# **Thermal Capabilities**

| Symbol                | Description                                           | Value | Units |

|-----------------------|-------------------------------------------------------|-------|-------|

| TQFN33-16             |                                                       |       |       |

| θја                   | Thermal Resistance – Junction to Ambient <sup>2</sup> | 43    | °C/W  |

| PD                    | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C    | 2.0   | W     |

| $\Delta P_D/\Delta T$ | Derating Factor Above T <sub>A</sub> = 25°C           | -20   | mW/°C |

| WLCSP-12              |                                                       |       |       |

| θЈΑ                   | Thermal Resistance – Junction to Ambient <sup>2</sup> | 90    | °C/W  |

| PD                    | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C    | 1.1   | W     |

| $\Delta P_D/\Delta T$ | Derating Factor Above T <sub>A</sub> = 25°C           | -11   | mW/°C |

<sup>2.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

# **Ordering Information**

| Part Number   | Marking <sup>3</sup> | Operating Temperature | Package                            |

|---------------|----------------------|-----------------------|------------------------------------|

| KTD3122EFJ-TR | GWYYZ                | -40°C to +85°C        | TQFN33-16                          |

| KTD3122EAZ-TR | GWYYZ                | -40°C to +85°C        | WLCSP-12, 1.21mm x 1.65mm x 0.62mm |

<sup>3. &</sup>quot;YYZ" is the date code and assembly code.

## Electrical Characteristics<sup>4</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C). VIN = 3.6V.

| Symbol                  | Description                          | Conditions                                                      | Min  | Тур  | Max  | Units |

|-------------------------|--------------------------------------|-----------------------------------------------------------------|------|------|------|-------|

| IC Supply               |                                      |                                                                 |      |      |      |       |

| Vin                     | Input operating range                |                                                                 | 2.7  |      | 5.5  | V     |

| UVLO                    | Input under voltage lockout          | Rising edge                                                     |      | 2.5  | 2.65 | V     |

| UVLO <sub>HYST</sub>    | UVLO hysteresis                      |                                                                 |      | 0.15 |      | V     |

|                         | IC standby current                   | Not switching                                                   |      | 1.36 | 2    | mA    |

| lα                      | IC operating current                 | Switching                                                       |      | 1.9  | 2.6  | mA    |

| I <sub>SHDN</sub>       | Shutdown current                     | V <sub>IN</sub> = 5.5V                                          |      | 3    | 5    | μА    |

| Step-Up Co              | nverter                              |                                                                 |      |      |      |       |

| R <sub>DS(ON)</sub>     | NMOS on-resistance                   |                                                                 |      | 0.4  |      | Ω     |

| ILIM                    | Peak NMOS current limit              | Default                                                         |      | 1    |      | Α     |

| fsw                     | Oscillator frequency                 | Default                                                         | 0.9  | 1.0  | 1.1  | MHz   |

| D <sub>max</sub>        | Maximum duty cycle                   | 1MHz setting                                                    |      | 92   | 94   | %     |

| Vov                     | OVP threshold                        | Default                                                         | 27.5 | 30   | 32.5 | V     |

| Current Sin             | ık                                   |                                                                 |      |      |      |       |

|                         |                                      | Current setting = 20mA,<br>T <sub>A</sub> = 25°C                | -1.5 |      | 1.5  | %     |

| Isink                   | Output current accuracy              | Current setting = 1mA,<br>$T_A = 25$ °C                         | -4.5 |      | 4.5  | %     |

|                         |                                      | Current setting = $50\mu$ A,<br>T <sub>A</sub> = $25^{\circ}$ C | -8   |      | 8    | %     |

|                         | Output current matching <sup>5</sup> | Current setting = 20mA,<br>T <sub>A</sub> = 25°C                | -0.6 |      | 0.6  | %     |

| V_sov                   | Current sink over voltage threshold  |                                                                 |      | 6.0  |      | V     |

| T <sub>FAULT</sub>      | Current sink fault delay             |                                                                 |      | 59   |      | ms    |

| <b>Logic Cont</b>       | rol                                  |                                                                 |      |      |      |       |

| $V_{TH	ext{-L}}$        | EN/PWM pin logic low threshold       |                                                                 |      |      | 0.4  | V     |

| $V_{\text{TH-H}}$       | EN/PWM pin logic high threshold      |                                                                 | 1.4  |      |      | V     |

| f <sub>PWM</sub>        | PWM dimming frequency                |                                                                 | 0.1  |      | 100  | kHz   |

| D <sub>PWM</sub>        | PWM dimming duty cycle               | F <sub>PWM</sub> = 10kHz                                        | 0.1  |      | 100  | %     |

| T <sub>PWM_OFF</sub>    | PWM minimum turn off pulse width     |                                                                 | 20   |      |      | ms    |

| R <sub>EN</sub>         | EN pull-down resistor                |                                                                 |      | 400  |      | kΩ    |

| $R_{PWM}$               | PWM pull-down resistor               |                                                                 |      | 400  |      | kΩ    |

| I <sup>2</sup> C-Compat | ible Voltage Specifications (SCL     | , SDA)                                                          |      |      |      |       |

| VIL                     | Input Logic Low Threshold            |                                                                 | _    | _    | 0.4  | V     |

| ViH                     | Input Logic High Threshold           |                                                                 | 1.4  |      |      | V     |

<sup>4.</sup> KTD3122 is guaranteed to meet performance specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>5.</sup> The current matching between channels is defined as ( $I_{S2}$ - $I_{S1}$ )/ ( $I_{S2}$ + $I_{S1}$ ).

# Electrical Characteristics<sup>6</sup> (continued)

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C). VIN = 3.6V.

| Symbol                                                                     | Description                              | Conditions | Min | Тур | Max | Units |

|----------------------------------------------------------------------------|------------------------------------------|------------|-----|-----|-----|-------|

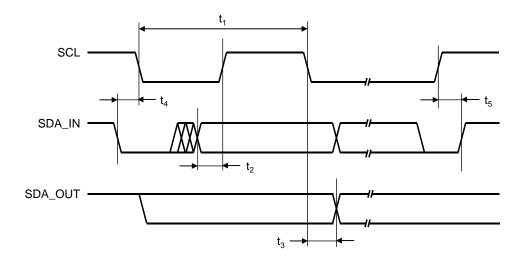

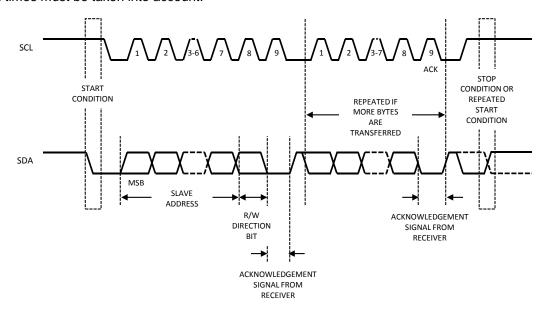

| I <sup>2</sup> C-Compatible Timing Specifications (SCL, SDA), see Figure 1 |                                          |            |     |     |     |       |

| t <sub>1</sub>                                                             | SCL (Clock Period)                       |            | 2.5 |     |     | μS    |

| t <sub>2</sub>                                                             | Data In Setup Time to SCL High           |            | 100 |     |     | ns    |

| t <sub>3</sub>                                                             | Data Out Stable After SCL Low            |            | 0   |     |     | ns    |

| t <sub>4</sub>                                                             | SDA Low Setup Time to SCL Low (Start)    |            | 100 |     |     | ns    |

| <b>t</b> <sub>5</sub>                                                      | SDA High Hold Time After SCL High (Stop) |            | 100 |     |     | ns    |

| Thermal S                                                                  | Shutdown                                 |            |     |     |     |       |

| т                                                                          | IC junction thermal shutdown threshold   |            |     | 150 |     | °C    |

| T <sub>J-TH</sub>                                                          | IC junction thermal shutdown hysteresis  |            |     | 15  |     | °C    |

<sup>6.</sup> KTD3122 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

Figure 1. I<sup>2</sup>C Compatible Interface Timing

# **Typical Characteristics**

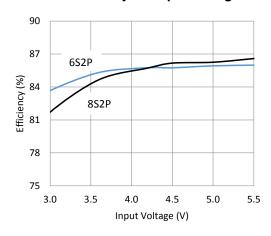

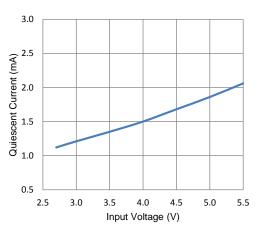

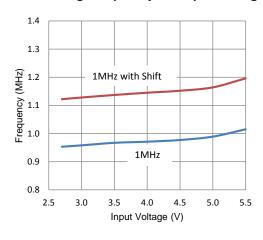

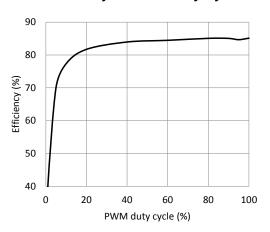

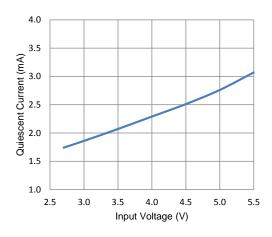

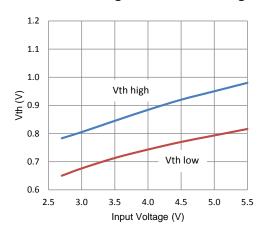

$V_{IN}=3.6V$ , 8S2P LEDs,  $I_{LED}=20mA$ ,  $L=10\mu H$  (Coilcraft LPS4018-103M),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ , register default values, Temp = 25°C unless otherwise specified.

#### Efficiency vs. Input Voltage

## **Quiescent Current (non-switching)**

#### Switching Frequency vs. Input Voltage

## Efficiency vs. PWM Duty Cycle

#### **Quiescent Current (switching)**

#### **EN/PWM Logic Threshold Voltage**

# **Typical Characteristics (continued)**

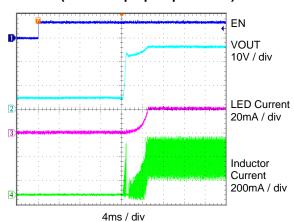

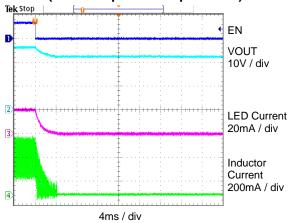

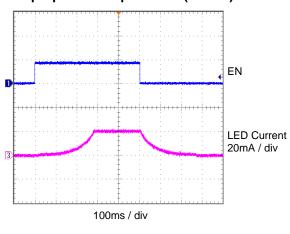

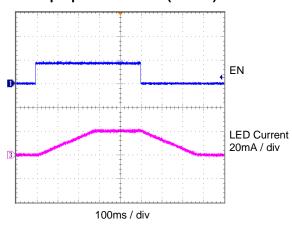

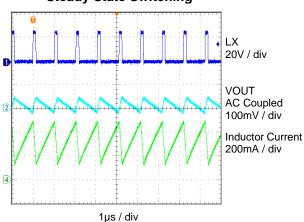

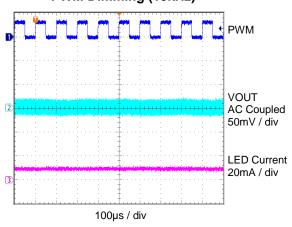

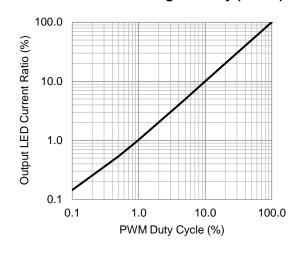

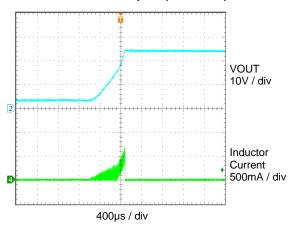

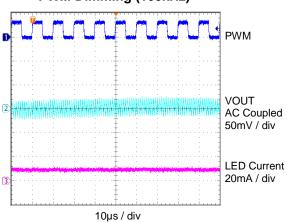

$V_{IN} = 3.6V$ , 8S2P LEDs,  $I_{LED} = 20$ mA,  $L = 10\mu$ H (Coilcraft LPS4018-103M),  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1\mu$ F, register default values, Temp = 25°C unless otherwise specified.

#### Turn On (4ms Ramp up Exponential)

#### **Turn Off (4ms Ramp Down Exponential)**

#### Ramp Up/Down Exponential (256ms)

#### Ramp Up/Down Linear (256ms)

#### Steady State Switching

# **Typical Characteristics (continued)**

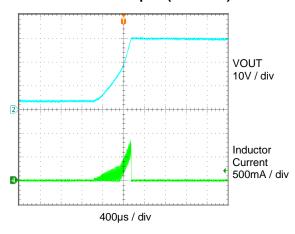

$V_{IN} = 3.6V$ , 8S2P LEDs,  $I_{LED} = 20$ mA,  $L = 10\mu$ H (Coilcraft LPS4018-103M),  $C_{IN} = 10\mu$ F,  $C_{OUT} = 1\mu$ F, register default values, Temp = 25°C unless otherwise specified.

#### Turn On with LED Open (30V OVP)

#### **PWM Dimming (10kHz)**

## **PWM Dimming Linearity (10kHz)**

#### Turn On with LED Open (24V OVP)

#### PWM Dimming (100kHz)

## **Functional Block Diagram**

# **Functional Description**

KTD3122 is a unique current regulated step-up (boost) converter. Two current sinks are integrated to drive 2 strings of LEDs with good current matching.

The voltage step-up is accomplished by a boost topology, using an inductor-based DC-DC switching converter, in which the inductor serves as an energy storage device in the system. By integrating a 30V power NMOS and a 30V power diode, KTD3122 minimizes the number of external components while maintaining high efficiency. Unlike a traditional DC-DC boost converter with a fixed output voltage, KTD3122 dynamically changes its output voltage depending on the load. The use of unique control schemes maintains accurate current regulation in each of the two current sinks while leaving the output voltage at a minimum, increasing the overall conversion efficiency. The internal step-up converter dynamically controls the voltage at the output high enough to drive the LED string with the highest total forward voltage.

The KTD3122 is also equipped with I<sup>2</sup>C interface for various controls.

#### **Full-scale LED Current**

The full-scale current is the LED current when PWM dimming duty cycle is 100% and the LED current ratio is also 100%. It is programmed by the Control register 0x02 bits[1:0] (see Table 2). The four options are 30mA, 25mA, 20mA, 15mA with 20mA as the default.

#### **LED Current Ratio**

The LED current ratio is the ratio between the actual LED current and the full-scale LED current when PWM dimming duty cycle is 100%. It is programmed by the Brightness register 0x03 bits[7:0], (see Table 3). The 256 options are 1/256, 2/256, 3/256, ..., 255/256, 256/256 with 256/256 as the default.

#### **PWM Dimming**

PWM dimming can be enabled or disabled by the PWM register 0x05 bit[5] (see Table 5), with enabled as default. When PWM is disabled, KTD3122 uses 100% as the dimming duty cycle for sink current calculation. When PWM is enabled, it is programmed as active high or active low by register 0x05 bit[4], with active high as default. When PWM dimming is enabled, KTD3122 uses internal 20MHz sampling clock to detect the PWM duty cycle providing good resolution and allowing PWM dimming frequency range to be as wide as 100Hz~100kHz and PWM duty cycle as wide as 0.1%~100% under 10kHz condition.

#### **LED Current**

The final LED current per channel can be calculated as:

$$I_{\mathit{LED}} = I_{\mathit{LED\_FULLSCALE}} \times \mathit{RATIO}_{\mathit{LED}} \times D_{\mathit{PWM}}$$

where  $I_{\mathit{LED\_FULLSCALE}}$  is the full-scale LED current setting,  $\mathit{RATIO}_\mathit{LED}$  is the LED current ratio setting,  $D_\mathit{PWM}$

is the PWM duty cycle if PWM dimming is enabled, otherwise  $D_{PWM} = 1$ . The input PWM signal's duty cycle is converted to a DC value, so the final LED current is also a DC value.

#### Turn On/Off Ramp

KTD3122 can program the ramp up or ramp down time when the current sink is turned on or off, they are controlled by the Ramp register 0x04 Bits[7:4] and Bits[3:0] respectively (see Table 4). The 16 options range from 512µs to 16384ms, with 512µs as default.

The shape of the up/down ramp can also be programmed as Exponential or Linear, they are controlled by the PWM register 0x05 Bit[7] and Bit[6] respectively, with Exponential as default.

#### Channel Enable/Disable

To disable one channel, there are two options.

- Connect the associated sink node to GND. During the startup of the device, it will automatically detect and disable the corresponding channel.

- Program register 0x05 Bits[1:0] to Enable/Disable the channels, with Enable as default.

#### **Switching Frequency**

The step-up converter's switching frequency can be programmed to 1MHz or 500kHz by setting the Control register 0x02 Bit[6], with 1MHz as default. The adjustment of the switching frequency can optimize the efficiency under different load current conditions. The frequency can also be programmed to shift up by 20% using the Control register 0x02 Bit[7], with no shift as default. The frequency shift function is to prevent noise interference if the selected switching frequency is within the sensitive frequency range of the system.

#### **Over Voltage Protection (OVP)**

The output voltage of the step-up converter is protected by OVP, its threshold can be programmed by the Control register 0x02 Bit[5] as 30V or 24V, with 30V as default.

#### **LX Slew Rate**

The slew rate of LX during the switching can affect the step-up converter efficiency and noise interference. Slower speed can minimize the noise interference while sacrificing the efficiency. The speed of LX slew rate can be programmed by the Control register 0x02 Bit[4] as fast or slow, with slow as default.

#### **Current Limit Protection**

The step-up converter is protected by cycle-by-cycle current limit protection, its threshold can be programmed by the Control register 0x02 Bit[3] as 1A or 0.7A, with 1A as default.

#### Disable I<sup>2</sup>C in Shutdown

By default, when the device is in shutdown condition (EN is low), its I<sup>2</sup>C interface is still responding, so user can send I<sup>2</sup>C commands to configure all the registers before enabling the device by EN pin, then there is no need to change the setting after the startup of the device. This is the preferred startup sequence.

There is one disadvantage for this configuration if SCL/SDA's pull up voltage is much less than VIN voltage, which can cause a small leakage current in the shutdown condition. For example, if VIN = 4.2V and SCL/SDA's

pull up voltage is 1.8V, there will be around 3μA additional leakage current from VIN in the shutdown condition. To minimize this small leakage current, KTD3122 provides the option to disable I²C interface in the shutdown condition by the Control register 0x02 Bit[2]. Once this bit is written as '0', in shutdown condition I²C interface will be disabled and user can't program the device. To enable the I²C interface, the EN input must be set high to enable the device first. So in the shutdown condition, it is suggested to set all the configurations first before disabling the I²C interface. Then when the device is enabled again, it can go to the preset condition without any I²C command during the startup.

If I<sup>2</sup>C interface is not needed, both SCL and SDA should be tied to VIN.

#### Software Reset

The user can reset I<sup>2</sup>C registers (0x02, 0x03, 0x04 and 0x05) to their default values by writing to the Software Reset register 0x06 Bit[0] a '1', and then writing '0' (see Table 6).

#### **LED Fault Protection**

Each current sink is protected against LED short or open conditions. If LED short circuit condition arises, the current sink continues to regulate until  $V_{\text{SINK}} > V_{\text{SOV}}$ . When any sink node voltage goes above  $V_{\text{SOV}}$  (6V) for more than 59ms (typ.), that channel's current sink will be turned off, and other channel will still work if it doesn't trigger this fault condition. For example, if two or more LEDs on a channel are shorted, that channel's sink voltage will increase. If the voltage goes above 6V for more than 59ms, the Current Sink Fault Protection will be triggered and only this faulty string will be disabled by shutting off this current sink. The other channel will continue normal operation if it doesn't have a fault condition.

In case of an LED failing open, the current sink voltage of the failed string will go close to ground and dominate the boost converter control loop. As a result the output voltage will move up to the over-voltage threshold. Once the over-voltage incident is flagged internally, the faulty channel(s) will be disabled. Then the output voltage of the boost converter will go back to normal level. During the entire process, the rest of the LED string (healthy LED string) would continue normal operation.

Fault status is stored in the Fault Flag register 0x07 (see Table 7). This is a read-only register. Once a fault is triggered and the associated bit is set, the fault status is only reset by EN pin toggling (low to high) or VIN power-on-reset.

#### **Thermal Shutdown**

Thermal shutdown feature is included in the KTD3122. When the IC's junction temperature (T<sub>J</sub>) reaches 150°C, the IC will immediately enter shutdown mode. Once T<sub>J</sub> drops 15°C to approximately 135°C, the IC will resume normal operation.

## **Application Information**

#### I<sup>2</sup>C Serial Data Bus

The KTD3122 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the bus is called a master, whereas the devices controlled by the master are known as slaves. A master device must generate the serial clock (SCL), control bus access and generate START and STOP conditions to control the bus. The KTD3122 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The KTD3122 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined (Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

#### **Bus Not Busy**

Both data and clock lines remain HIGH.

#### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account.

Figure 2. Data Transfer on I<sup>2</sup>C Serial Bus

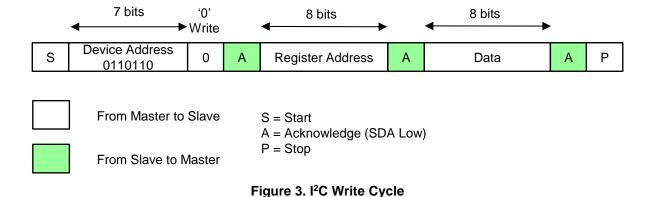

KTD3122's 7-bit slave device address is 0110110 binary (or 0x36h).

There are two kinds of I<sup>2</sup>C data transfer cycles: write cycle and read cycle.

#### I<sup>2</sup>C Write Cycle

For I<sup>2</sup>C write cycle, data is transferred from a master to a slave. The first byte transmitted is the 7-bit slave address plus one bit of '0' for write. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first. Figure 3 shows the sequence of the I<sup>2</sup>C write cycle.

February 2016 – Revision 04d Page 13 Company Confidential

#### I<sup>2</sup>C Write Cycle Steps:

- · Master generates start condition.

- Master sends 7-bit slave address (0110110 for KTD3122) and 1-bit data direction '0' for write.

- Slave sends acknowledge if the slave address is matched.

- Master sends 8-bit register address.

- Slave sends acknowledge.

- · Master sends 8-bit data for that addressed register.

- · Slave sends acknowledge.

- If master sends more data bytes, the register address will be incremented by one after each acknowledge.

- Master generate stop condition to finish the write cycle.

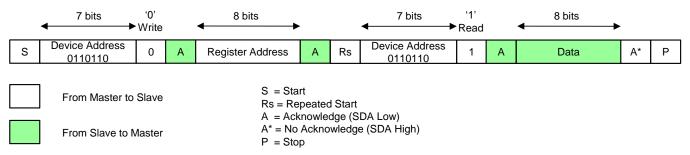

#### I<sup>2</sup>C Read Cycle

For I<sup>2</sup>C read cycle, data is transferred from a slave to a master. But to start the read cycle, master needs to write the register address first to define which register's data to read. Figure 4 shows the steps of the I<sup>2</sup>C read cycle.

Figure 4. I<sup>2</sup>C Read Cycle

#### I<sup>2</sup>C Read Cycle Steps:

- · Master generates start condition.

- Master sends 7-bit slave address (0110110 for KTD3122) and 1-bit data direction '0' for write.

- · Slave sends acknowledge if the slave address is matched.

- Master sends 8-bit register address.

- Slave sends acknowledge.

- · Master generates repeated start condition.

- Master sends 7-bit slave address (0110110 for KTD3122) and 1-bit data direction '1' for read.

- Slave sends acknowledge if the slave address is matched.

- Slave sends the data byte of that addressed register.

- If master sends acknowledge, the register address will be incremented by one after each acknowledge and the slave will continue to send the data for the updated addressed register.

- If master sends no acknowledge, the slave will stop sending the data.

- Master generate stop condition to finish the read cycle.

## I<sup>2</sup>C Register Map

Table 1 summarizes KTD3122's 6 I<sup>2</sup>C registers, their read/write settings and default values. The default value is only reset by power-on-reset of VIN pin, and it will not be reset by EN pin.

Table 1. I<sup>2</sup>C Register Map

| Register Name       | Address (Hex) | Read/Write | Default Value |

|---------------------|---------------|------------|---------------|

| Control Register    | 0x02          | Read/Write | 6D            |

| Brightness Register | 0x03          | Read/Write | FF            |

| Ramp Register       | 0x04          | Read/Write | 00            |

| PWM Register        | 0x05          | Read/Write | 07            |

| SW Reset Register   | 0x06          | Read/Write | 00            |

| Fault Flag Register | 0x07          | Read Only  | 00            |

## I<sup>2</sup>C Register Description

The following tables summarize the setting of each I<sup>2</sup>C register. Reserved bit should be written as '0' and ignored during read.

Table 2. Control Register (Address 0x02, Read/Write)

| Bit 7                                            | Bit 6                               | Bit 5                           | Bit 4                             | Bit 3                           | Bit 2                                  | Bits [1:0]                                                |

|--------------------------------------------------|-------------------------------------|---------------------------------|-----------------------------------|---------------------------------|----------------------------------------|-----------------------------------------------------------|

| Switching                                        | Switching                           | OVP                             | LX Slew                           | Current                         | I <sup>2</sup> C Interface             | Full-scale Channel                                        |

| Frequency Shift                                  | Frequency                           | Control                         | Rate                              | Limit                           | in Shutdown                            | Current                                                   |

| 0 = No Shift<br>(Default)<br>1 = Shift up by 20% | 0 = 500kHz<br>1 = 1MHz<br>(Default) | 0 = 24V<br>1 = 30V<br>(Default) | 0 = Slow<br>(Default)<br>1 = Fast | 0 = 0.7A<br>1 = 1A<br>(Default) | 0 = Disable<br>1 = Enable<br>(Default) | 00 = 15mA<br>01 = 20mA (Default)<br>10 = 25mA<br>11 =30mA |

Table 3. Brightness Register (Address 0x03, Read/Write)

| Bits [7:0]<br>LED Current Ratio                          |  |

|----------------------------------------------------------|--|

| 00000000 = 1/256<br>00000001 = 2/256<br>00000010 = 3/256 |  |

| <br>11111110 = 255/256<br>11111111 = 256/256 (Default)   |  |

Table 4. Ramp Register (Address 0x04, Read/Write)

| Bits [7:4]             | Bits [3:0]             |

|------------------------|------------------------|

| Ramp Up Time           | Ramp Down Time         |

| 0000 = 512us (Default) | 0000 = 512us (Default) |

| 0001 = 1ms             | 0001 = 1ms             |

| 0010 = 2ms             | 0010 = 2ms             |

| 0011 = 4ms             | 0011 = 4ms             |

| 0100 = 8ms             | 0100 = 8ms             |

| 0101 = 16ms            | 0101 = 16ms            |

| 0110 = 32ms            | 0110 = 32ms            |

| 0111 = 64ms            | 0111 = 64ms            |

| 1000 = 128ms           | 1000 = 128ms           |

| 1001 = 256ms           | 1001 = 256ms           |

| 1010 = 512ms           | 1010 = 512ms           |

| 1011 = 1024ms          | 1011 = 1024ms          |

| 1100 = 2048ms          | 1100 = 2048ms          |

| 1101 = 4096ms          | 1101 = 4096ms          |

| 1110 = 8192ms          | 1111 = 8192ms          |

| 1111 = 16384ms         | 1111 = 16384ms         |

Note: If switching frequency shift is enabled (Register 0x02's Bit [7] = 1), the ramp up/down time will be 20% shorter.

Table 5. PWM Register (Address 0x05, Read/Write)

| Bit 7<br>Ramp Up<br>Shape | Bit 6<br>Ramp Down<br>Shape | Bit 5<br>PWM<br>Input | Bit 4<br>PWM Active | Bits [3:2] | Bit 1<br>CH2 | Bit 0<br>CH1 |

|---------------------------|-----------------------------|-----------------------|---------------------|------------|--------------|--------------|

| 0 = Exponential           | 0 = Exponential             | 0 = Enable            | 0 = High Active     | Don't care | 0 = Disable  | 0 = Disable  |

| (Default)                 | (Default)                   | (Default)             | (Default)           |            | 1 = Enable   | 1 = Enable   |

| 1 = Linear                | 1 = Linear                  | 1 = Disable           | 1 = Low Active      |            | (Default)    | (Default)    |

Table 6. Software Reset Register (Address 0x06, Read/Write)

| Bits [7:1] | Bit 0 Software Reset                                                  |

|------------|-----------------------------------------------------------------------|

| Don't care | 0 = Disable (Default)<br>1 = Reset all registers except 0x06 and 0x07 |

Note: After Bit 0 is written as '1' for software reset, '0' should also be written to this bit clear this bit.

Table 7. Fault Flag Register (Address 0x07, Read Only)

| Bits [7:6] | Bit 5<br>S2 LED Open<br>or Short | Bit 4<br>S1 LED Open<br>or Short | Bit 3<br>OVP         | Bit 2<br>UVLO         | Bit 1<br>OCP         | Bit 0<br>Thermal<br>Shutdown         |

|------------|----------------------------------|----------------------------------|----------------------|-----------------------|----------------------|--------------------------------------|

| Reserved   | 0 = Normal<br>1= Open or Short   | 0 = Normal<br>1= Open or Short   | 0 = Normal<br>1= OVP | 0 = Normal<br>1= UVLO | 0 = Normal<br>1= OCP | 0 = Normal<br>1= Thermal<br>Shutdown |

Note: Once fault is triggered, it will only be reset by toggling EN or VIN power-on-reset.

#### **Capacitor Selection**

Small size ceramic capacitors with low ESR are ideal for all applications. A 10uF input capacitor and a 1uF output capacitor are suggested. The voltage rating of these capacitors should exceed the maximum possible voltage at the corresponding pins, and these capacitors should keep as close as possible to the IC.

**Table 8. Recommended Ceramic Capacitor Vendors**

| Manufacturer | Website         |  |  |

|--------------|-----------------|--|--|

| Murata       | www.murata.com  |  |  |

| AVX          | www.avx.com     |  |  |

| Taiyo Yuden  | www.t-yuden.com |  |  |

#### **Inductor Selection**

Depending on the switching frequency (1MHz or 500kHz), an inductor in the range of  $10\mu H$  to  $22\mu H$  with low DCR can be selected for the boost converter. To estimate the inductance required for applications, calculate the maximum input average current as the following

$$I_{\mathit{IN}\,(\mathit{MAX}\,)} = \frac{V_{\mathit{OUT}} \cdot I_{\mathit{OUT}\,(\mathit{MAX}\,)}}{V_{\mathit{IN}} \cdot \eta}$$

February 2016 – Revision 04d Page 16 Company Confidential

where  $\eta$  is the converter efficiency and can be approximated as 90% for the typical case. In order to have smaller current ripple (to improve efficiency and minimize output voltage ripple), larger inductance will be required. If inductor ripple current needs to be less than 40% of the average input current, then

$$\Delta I_L = \frac{V_{IN} \cdot D \cdot T_S}{L} \le 40\% \cdot \frac{V_{OUT} \cdot I_{OUT(MAX)}}{V_{IN} \cdot \eta}$$

Where duty cycle can be estimated as

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

Then

$$\Delta I_L = \frac{V_{\mathit{IN}} \cdot (V_{\mathit{OUT}} - V_{\mathit{IN}}) \cdot T_{\mathit{S}}}{L \cdot V_{\mathit{OUT}}} \leq 40\% \cdot \frac{V_{\mathit{OUT}} \cdot I_{\mathit{OUT}(\mathit{MAX})}}{V_{\mathit{IN}} \cdot \eta}$$

Therefore the inductance can be calculated as

$$L \ge \frac{V_{IN}^2 \cdot (V_{OUT} - V_{IN}) \cdot \eta}{40\% \cdot V_{OUT}^2 \cdot I_{OUT(MAX)} \cdot f_S}$$

where fs is the switching frequency of the boost converter.

**Table 9. Recommended Inductor**

| Application | Inductor Part Number | Value<br>(µH) | DCR<br>(Ω) | Saturation<br>Current (A) | Dimensions<br>(mm) | Manufacturer |

|-------------|----------------------|---------------|------------|---------------------------|--------------------|--------------|

| 2P8S        | LPS4018-103ML        | 10            | 0.200 max  | 1.3                       | 4x4x1.8            | Coilcraft    |

#### **Recommended PCB Layout**

PCB layout is very important for high frequency switching regulators in order to keep the loop stable and minimize noise. The input capacitor (CIN) should be very close to the IC VIN pin and PGND pin in order to get the best decoupling. The path between the inductor, LX pin and the output capacitor (COUT) should be kept as short as possible to minimize noise and ringing. To reduce power loss, the trace between the inductor and LX pin should be as short and wide as possible. Both input and output capacitor GND terminals should be connected together on the PCB top layer and on the bottom layer GND planes.

Figure 5. TQFN Recommended PCB Layout

Figure 6. WLCSP Recommended PCB Layout

# **Package Information**

## **TQFN33-16**

| Dimension | mm    |         |       |  |  |  |

|-----------|-------|---------|-------|--|--|--|

| Dimension | Min.  | Тур.    | Max.  |  |  |  |

| Α         | 0.65  | 0.75    | 0.85  |  |  |  |

| A1        | 0.000 | 0.025   | 0.050 |  |  |  |

| A2        | 0.154 | 0.203   | 0.280 |  |  |  |

| b         | 0.18  | 0.23    | 0.30  |  |  |  |

| С         |       | 0.3REF  |       |  |  |  |

| D         | 2.95  | 3.00    | 3.05  |  |  |  |

| D1        |       | 1.7REF  |       |  |  |  |

| E         | 2.95  | 3.00    | 3.05  |  |  |  |

| E1        |       | 1.7REF  |       |  |  |  |

| е         | 0.45  | 0.50    | 0.55  |  |  |  |

| L         | 0.30  | 0.40    | 0.50  |  |  |  |

| S         |       | 0.25REF |       |  |  |  |

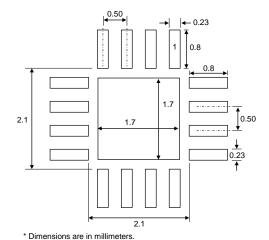

## **Recommended Footprint**

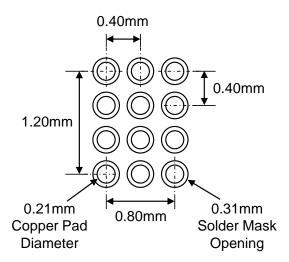

#### WLCSP-12 1.21mm x 1.65mm x 0.62mm

## **Recommended Footprint**

#### (NSMD Pad Type)

<sup>\*</sup> Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru\_6 moschip.ru\_4 moschip.ru\_9