# High Frequency Programmable PECL Clock Generator

#### **Features**

- Jitter peak-peak (Typical) = 35 ps

- LVPECL output

- Default Select option

- Serially configurable multiply ratios

- Output edge rate control

- 16-pin TSSOP

- High frequency

- 3.3 V operation

#### **Benefits**

- High accuracy clock generation

- One pair of differential output drivers

- Phase-locked loop (PLL) multiplier select

- 8-bit feedback counter and 6-bit reference counter for high accuracy

- Minimize electromagnetic interference (EMI)

- Industry standard, low cost package saves on board space For a complete list of related documentation, click here.

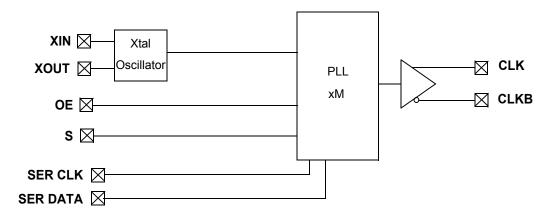

## **Logic Block Diagram**

#### **Contents**

| Pinouts                          | 3 |

|----------------------------------|---|

| Pin Definitions                  | 3 |

| Frequency Table                  | 3 |

| CY2213 Two-Wire Serial Interface |   |

| Introduction                     | 4 |

| Serial Interface Specifications  | 4 |

| Serial Interface Format          | 4 |

| Serial Interface Transfer Format | 4 |

| Absolute Maximum Conditions      | 6 |

| Crystal Requirements             | 6 |

| Electrical Characteristics       | 6 |

| DC Electrical Specifications     | 6 |

| 3.3 V DC Device Characteristics  | 6 |

| AC Electrical Specifications     | 7 |

| AC Device Characteristics        | 7 |

| State Transition Characteristics |   |

| Functional Specifications        | 8 |

| Crystal Innut                    |   |

| Select Input                            | 8  |

|-----------------------------------------|----|

| PECL Clock Output Driver                |    |

| Signal Waveforms                        | 9  |

| Jitter                                  |    |

| Ordering Information                    | 12 |

| Ordering Code Definitions               |    |

| Package Diagrams                        |    |

| Acronyms                                |    |

| Document Conventions                    |    |

| Units of Measure                        |    |

| Document History Page                   | 15 |

| Sales, Solutions, and Legal Information | 16 |

| Worldwide Sales and Design Support      | 16 |

| Products                                | 16 |

| PSoC® Solutions                         | 16 |

| Cypress Developer Community             |    |

| Technical Support                       |    |

### **Pinouts**

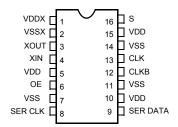

Figure 1. 16-pin TSSOP pinout CY2213

### **Pin Definitions**

| Pin Name | Pin Number | Pin Description                                                              |

|----------|------------|------------------------------------------------------------------------------|

| VDDX     | 1          | 3.3 V Power Supply for Crystal Driver                                        |

| VSSX     | 2          | Ground for Crystal Driver                                                    |

| XOUT     | 3          | Reference Crystal Feedback                                                   |

| XIN      | 4          | Reference Crystal Input                                                      |

| VDD      | 5          | 3.3 V Power Supply (all V <sub>DD</sub> pins must be tied directly on board) |

| OE       | 6          | Output Enable, 0 = output disable, 1 = output enable (no internal pull up)   |

| VSS      | 7          | Ground                                                                       |

| SER CLK  | 8          | Serial Interface Clock                                                       |

| SER DATA | 9          | Serial Interface Data                                                        |

| VDD      | 10         | 3.3 V Power Supply (all V <sub>DD</sub> pins must be tied directly on board) |

| VSS      | 11         | Ground                                                                       |

| CLKB     | 12         | LVPECL Output Clock (complement)                                             |

| CLK      | 13         | LVPECL Output Clock                                                          |

| VSS      | 14         | Ground                                                                       |

| VDD      | 15         | 3.3 V Power Supply (all V <sub>DD</sub> pins must be tied directly on board) |

| S        | 16         | PLL Multiplier Select Input, Pull up Resistor Internal                       |

## **Frequency Table**

| Ī | S | M (PLL Multiplier) | Example Input Crystal Frequency | CLK, CLKB |

|---|---|--------------------|---------------------------------|-----------|

| ĺ | 0 | × 16               | 25 MHz                          | 400 MHz   |

| ĺ | 1 | × 8                | 15.625 MHz                      | 125 MHz   |

#### CY2213 Two-Wire Serial Interface

#### Introduction

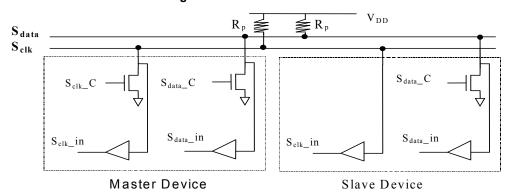

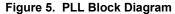

The CY2213 has a two-wire serial interface designed for data transfer operations, and is used for programming the P and Q values for frequency generation.  $S_{clk}$  is the serial clock line controlled by the master device.  $S_{data}$  is a serial bidirectional data line. The CY2213 is a slave device and can either read or write information on the dataline upon request from the master device.

Figure 2 shows the basic bus connections between master and slave device. The buses are shared by a number of devices and are pulled high by a pull up resistor.

#### Serial Interface Specifications

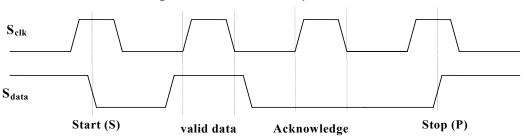

Figure 3 shows the Basic Transmission Specification. To begin and end a transmission, the master device generates a start signal (S) and a stop signal (P). Start (S) is defined as switching the  $S_{data}$  from HIGH to LOW while the  $S_{clk}$  is at HIGH. Similarly, stop (P) is defined as switching the  $S_{data}$  from LOW to HIGH while holding the  $S_{clk}$  HIGH. Between these two signals, data on  $S_{data}$  is synchronous with the clock on the  $S_{clk}$ . Data is allowed to change only at LOW period of clock, and must be stable at the

HIGH period of clock. To acknowledge, drive the  $S_{\text{data}}$  LOW before the  $S_{\text{clk}}$  rising edge and hold it LOW until the  $S_{\text{clk}}$  falling edge.

#### **Serial Interface Format**

Each slave carries an address. The data transfer is initiated by a start signal (S). Each transfer segment is 1 byte in length. The slave address and the read/write bit are first sent from the master device after the start signal. The addressed slave device must acknowledge (Ack) the master device. Depending on the Read/Write bit, the master device either writes data into (logic 0) or reads data (logic 1) from the slave device. Each time a byte of data is successfully transferred, the receiving device must acknowledge. At the end of the transfer, the master device generates a stop signal (P).

#### **Serial Interface Transfer Format**

Figure 3 shows the serial interface transfer format used with the CY2213. Two dummy bytes must be transferred before the first data byte. The CY2213 has only three bytes of latches to store information, and the third byte of data is reserved. Extra data is ignored.

Figure 2. Device Connections

Figure 3. Serial Interface Specifications

Figure 4. CY2213 Transfer Format

| 1 bit          | 7 bits        | 1 bit | 1 bit | 8 bits       | 1 bit | 8 bits       | 1 bit | 8 bits | 1 bit |

|----------------|---------------|-------|-------|--------------|-------|--------------|-------|--------|-------|

| S              | Slave Address | R/W   | Ack   | Dummy Byte 0 | Ack   | Dummy Byte 1 | Ack   | Data 0 | Ack   |

| D <sub>0</sub> | ta 1 Ack      |       |       |              |       |              |       |        |       |

Table 1. Serial Interface Address for the CY2213

1 bit

8 bits

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0   |

Table 2. Serial Interface Programming for the CY2213

|       | b7       | b6       | b5       | b4       | b3       | b2       | b1       | b0       |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|

| Data0 | QCNTBYP  | SELPQ    | Q<5>     | Q<4>     | Q<3>     | Q<2>     | Q<1>     | Q<0>     |

| Data1 | P<7>     | P<6>     | P<5>     | P<4>     | P<3>     | P<2>     | P<1>     | P<0>     |

| Data2 | Reserved |

To program the CY2213 using the two-wire serial interface, set the SELPQ bit HIGH. The default setting of this bit is LOW. The P and Q values are determined by the following formulas:

$$P_{final} = (P_{7..0} + 3) \times 2$$

$$Q_{final} = Q_{5..0} + 2.$$

PLL Frequency = Reference x P/Q = Output

If the QCNTBYP bit is set HIGH, then  $Q_{\text{final}}$  defaults to a value of 1. The default setting of this bit is LOW.

If the SELPQ bit is set LOW, the PLL multipliers are set using the values in the Select Function Table.

CyberClocks  $^{\text{TM}}$  has been developed to generate P and Q values for stable PLL operation. This software is downloadable from www.cypress.com

#### **Absolute Maximum Conditions**

The following table reflects stress ratings only, and functional operation at the maximums are not guaranteed.

| Parameter            | Description                                                       | Min  | Max                   | Unit |

|----------------------|-------------------------------------------------------------------|------|-----------------------|------|

| V <sub>DD, ABS</sub> | Maximum voltage on $V_{DD}$ , or $V_{DDX}$ with respect to ground | -0.5 | 4.0                   | V    |

| V <sub>I, ABS</sub>  | Maximum voltage on any pin with respect to ground                 | -0.5 | V <sub>DD</sub> + 0.5 | V    |

## **Crystal Requirements**

Requirements to use parallel mode fundamental xtal. External capacitors are required in the crystal oscillator circuit. Please refer to the application note entitled **Crystal Oscillator Topics** for details.

| Parameter | Description                   | Min | Max   | Unit |

|-----------|-------------------------------|-----|-------|------|

| $X_{F}$   | Crystal fundamental frequency | 10  | 31.25 | MHz  |

#### **Electrical Characteristics**

#### **DC Electrical Specifications**

| Parameter        | Description                                                                                         | Min  | Max  | Unit     |

|------------------|-----------------------------------------------------------------------------------------------------|------|------|----------|

| $V_{DD}$         | Supply voltage                                                                                      | 3.00 | 3.60 | V        |

| T <sub>A</sub>   | Ambient operating temperature                                                                       | 0    | 70   | °C       |

| V <sub>IL</sub>  | Input signal low voltage at pin S                                                                   | _    | 0.35 | $V_{DD}$ |

| V <sub>IH</sub>  | Input signal high voltage at pin S                                                                  | 0.65 | -    | $V_{DD}$ |

| R <sub>PUP</sub> | Internal pull up resistance                                                                         | 10   | 100  | kΩ       |

| t <sub>PU</sub>  | Power up time for all $V_{DD}$ s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | 500  | ms       |

#### 3.3 V DC Device Characteristics

(Driving load, Figure 6)

| Parameter       | Description                                        | Min   | Тур   | Max   | Unit |

|-----------------|----------------------------------------------------|-------|-------|-------|------|

| V <sub>OH</sub> | Output high voltage, referenced to V <sub>DD</sub> | -1.02 | -0.95 | -0.88 | V    |

| $V_{OL}$        | Output low voltage, referenced to V <sub>DD</sub>  | -1.81 | -1.70 | -1.62 | V    |

(Driving load, Figure 7)

| Parameter       | Description         | Min | Тур | Max | Unit |

|-----------------|---------------------|-----|-----|-----|------|

| V <sub>OH</sub> | Output high voltage | 1.1 | 1.2 | 1.3 | V    |

| $V_{OL}$        | Output low voltage  | 0   | 0   | 0   | V    |

Document Number: 38-07263 Rev. \*K

### **AC Electrical Specifications**

| Parameter            | Description                           |    | Max   | Unit |

|----------------------|---------------------------------------|----|-------|------|

| f <sub>IN</sub>      | Input frequency with driven reference | 1  | 133   | MHz  |

| f <sub>XTAL,IN</sub> | Input frequency with crystal input    | 10 | 31.25 | MHz  |

| C <sub>IN,CMOS</sub> | Input capacitance at S pin [1]        | _  | 10    | pF   |

#### **AC Device Characteristics**

| Parameter                         | Description                                                                       | Min            | Max            | Unit                 |

|-----------------------------------|-----------------------------------------------------------------------------------|----------------|----------------|----------------------|

| t <sub>CYCLE</sub>                | Clock cycle time                                                                  | 2.50 (400 MHz) | 8.00 (125 MHz) | ns                   |

| t <sub>JCRMS</sub>                | Cycle-to-cycle RMS jitter                                                         | -              | 0.25%          | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | _              | 20             | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 6.25           | ps                   |

| t <sub>JCPK</sub>                 | Cycle-to-cycle jitter (pk-pk)                                                     | -              | 1.75%          | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | -              | 140            | ps                   |

|                                   | At 200 MHz frequency, XF = 25 MHz                                                 | -              | 55             | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 43.75          | ps                   |

| t <sub>JPRMS</sub>                | Period jitter RMS                                                                 | _              | 0.25%          | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | -              | 20             | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 6.25           | ps                   |

| t <sub>JPPK</sub>                 | Period jitter (pk-pk)                                                             | -              | 2.0%           | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | _              | 160            | ps                   |

|                                   | At 200 MHz frequency, XF = 25 MHz                                                 | _              | 65             | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 50             | ps                   |

| t <sub>JLT</sub>                  | Long term RMS Jitter (P < 20)                                                     | _              | 1.75%          | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | _              | 140            | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 43.75          | ps                   |

| t <sub>JLT</sub>                  | Long term RMS Jitter (20 ≤ P < 40)                                                | -              | 2.5%           | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | _              | 200            | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 62.5           | ps                   |

| t <sub>JLT</sub>                  | Long term RMS Jitter (40 ≤ P < 60)                                                | -              | 3.5%           | % t <sub>CYCLE</sub> |

|                                   | At 125 MHz frequency                                                              | _              | 280            | ps                   |

|                                   | At 400 MHz frequency                                                              | _              | 87.5           | ps                   |

| Phase Noise                       | Phase Noise at 10 kHz (x8 mode) at 125 MHz                                        | -107           | -92            | dBc                  |

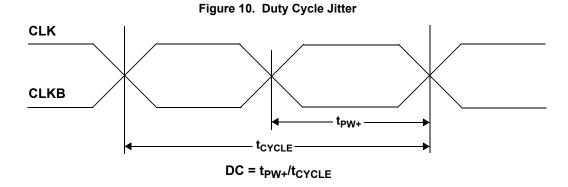

| DC                                | Long term average output duty cycle                                               | 45             | 55             | %                    |

| t <sub>DC,ERR</sub>               | Cycle-cycle duty cycle error at x8 with 15.625 MHz input                          | _              | 70             | ps                   |

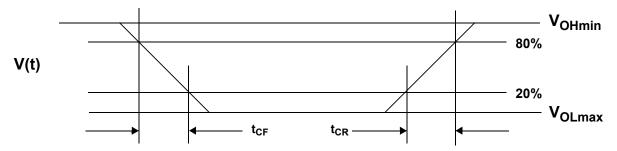

| t <sub>CR</sub> , t <sub>CF</sub> | Output rise and fall times (measured at 20% – 80% of $V_{OHmin}$ and $V_{OLmax})$ | 100            | 400            | ps                   |

| BW <sub>LOOP</sub>                | PLL Loop Bandwidth                                                                | 50 kHz (-3 dB) | 8 MHz (-20 dB) |                      |

Document Number: 38-07263 Rev. \*K

Note

1. Capacitance measured at frequency = 1 MHz, DC Bias = 0.9V, and VAC < 100 mV

#### **State Transition Characteristics**

Specifies the maximum settling time of the CLK and CLKB outputs from device power up. For  $V_{DD}$  and  $V_{DDX}$  any sequences are allowed to power up and power down the CY2213.

| From                | То              | Transition Latency | Description                                                                    |

|---------------------|-----------------|--------------------|--------------------------------------------------------------------------------|

| $V_{DD}/V_{DDX}$ On | CLK/CLKB Normal | 3 ms               | Time from $V_{DD}/V_{DDX}$ is applied and settled to CLK/CLKB outputs settled. |

## **Functional Specifications**

#### **Crystal Input**

The CY2213 receives its reference from an external crystal. Pin XIN is the reference crystal input, and pin XOUT is the reference crystal feedback. The parameters for the crystal are illustrated in AC Device Characteristics on page 7. The oscillator circuit requires external capacitors. Please refer to the application note entitled **Crystal Oscillator Topics** for details.

#### **Select Input**

There is only one select input, pin S. This pin selects the frequency multiplier in the PLL, and is a standard LVCMOS input. The S pin has an internal pull up resistor. The multiplier selection is illustrated in Frequency Table on page 3.

#### **PECL Clock Output Driver**

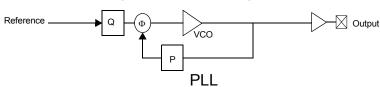

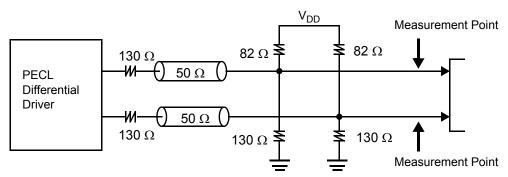

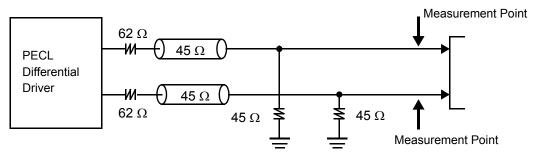

Figure 6 and Figure 7 show the Clock Output Driver.

Figure 6. Output Driving Load (-1)

Figure 7. Output Driving Load (-2)

An alternative termination scheme can be used to drive a standard PECL fanout buffer.

PECL Differential Driver  $N_{DD}$   $N_{DD}$  Measurement Point  $N_{DD}$   $N_{$

Figure 8. Output Driving Load (-3)

The PECL differential driver is designed for low voltage, high frequency operation. It significantly reduces the transient switching noise and power dissipation when compared to conventional CMOS drivers. The nominal value of the channel impedance is  $50\Omega$ . The pull up and pull down resistors provide matching channel termination. The combination of the differential driver and the output network determines the voltage swing on the channel. The output clock is specified at the measurement point indicated in Figure 6 on page 8 and Figure 7 on page 8.

#### Signal Waveforms

A physical signal that appears at the pins of the device is deemed valid or invalid depending on its voltage and timing relations with other signals. This section defines the voltage and timing waveforms for the input and output pins of the CY2213. The Device Characteristics tables list the specifications for the device parameters that are defined here.

Input and Output voltage waveforms are defined as shown in Figure 9. Rise and fall times are defined as the 20% and 80% measurement points of  $V_{OHmin} - V_{OLmax}$ .

The device parameters are defined in Table 3. Figure 10 on page 10 shows the definition of long term duty cycle, which is simply the CLK waveform high time divided by the cycle time (defined at the crossing point). Long term duty cycle is the average over many (>10,000) cycles. DC is defined as the Output Clock Long Term Duty Cycle.

Table 3. Definition of Device Parameters

| Parameter                         | Definition                                         |  |  |

|-----------------------------------|----------------------------------------------------|--|--|

| V <sub>OH</sub> , V <sub>OL</sub> | Clock output high and low voltages                 |  |  |

| $V_{IH}, V_{IL}$                  | V <sub>DD</sub> LVCMOS input high and low voltages |  |  |

| t <sub>CR</sub> , t <sub>CF</sub> | Clock output rise and fall times                   |  |  |

Figure 9. Voltage Waveforms

#### **Jitter**

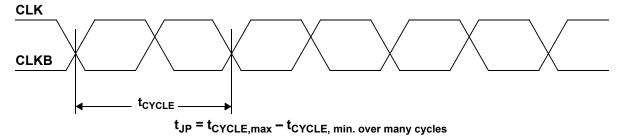

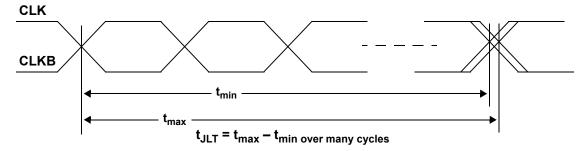

This section defines the specifications that relate to timing uncertainty (or jitter) of the input and output waveforms. Figure 11 shows the definition of period jitter with respect to the falling edge of the CLK signal. Period jitter is the difference between the minimum and maximum cycle times over many cycles (typically 12,800 cycles at 400 MHz). Equal requirements apply for rising edges of the CLK signal.  $t_{\rm JP}$  is defined as the output period jitter.

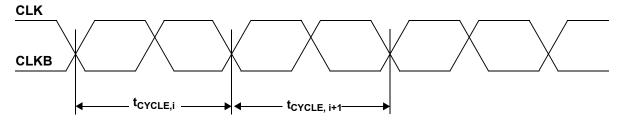

Figure 12 shows the definition of cycle-to-cycle jitter with respect to the falling edge of the CLK signal. Cycle-to-cycle jitter is the difference between cycle times of adjacent cycles over many cycles (typically 12,800 cycles at 400 MHz). Equal requirements

apply for rising edges of the CLK signal.  $t_{\text{JC}}$  is defined as the Clock Output Cycle-to-cycle Jitter.

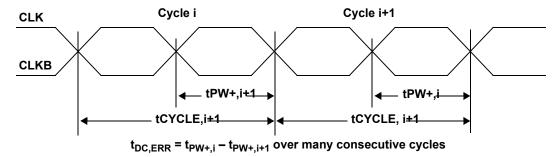

Figure 13 on page 11 shows the definition of cycle-to-cycle duty cycle error. Cycle-to-cycle duty cycle error is defined as the difference between high-times of adjacent cycles over many cycles (typically 12,800 cycles at 400 MHz). Equal requirements apply to the low-times.  $t_{DC,ERR}$  is defined as the Clock Output Cycle-to-cycle Duty Cycle Error.

Figure 14 on page 11 shows the definition of long-term jitter error. Long term jitter is defined as the accumulated timing error over many cycles (typically 12,800 cycles at 400 MHz). It applies to both rising and falling edges.  $t_{\rm JI,T}$  is defined as the long term jitter.

Figure 11. Period Jitter

Figure 12. Cycle-to-cycle Jitter

t<sub>JC</sub> = t<sub>CYLCE,i</sub> - t<sub>CYCLE,i+1</sub> over many consecutive cycles

Figure 13. Cycle-to-cycle Duty Cycle Error

Figure 14. Long-term Jitter

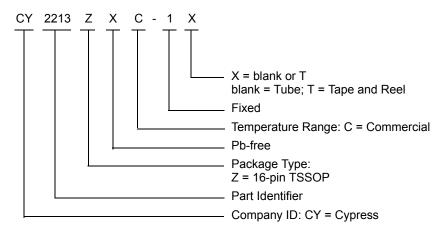

## **Ordering Information**

| Ordering Code                             | Package Type | Operating Range        | Operating Voltage |

|-------------------------------------------|--------------|------------------------|-------------------|

| CY2213ZXC-1                               | 16-pin TSSOP | Commercial, to 400 MHz | 3.3 V             |

| CY2213ZXC-1T 16-pin TSSOP – Tape and Reel |              | Commercial, to 400 MHz | 3.3 V             |

### **Ordering Code Definitions**

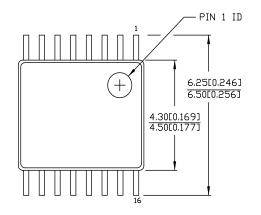

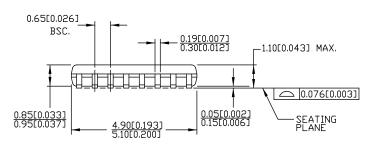

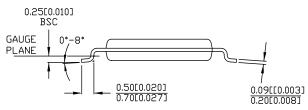

## **Package Diagrams**

Figure 15. 16-pin TSSOP (4.40 mm Body) Z16.173/ZZ16.173 Package Outline, 51-85091

DIMENSIONS IN MMEINCHESJ MIN. MAX.

REFERENCE JEDEC MO-153

PACKAGE WEIGHT 0.05gms

| PART #              |                |  |  |  |

|---------------------|----------------|--|--|--|

| Z16.173 STANDARD PK |                |  |  |  |

| ZZ16.173            | LEAD FREE PKG. |  |  |  |

51-85091 \*E

## **Acronyms**

| Acronym | Description                                         |  |

|---------|-----------------------------------------------------|--|

| CMOS    | complementary metal-oxide semiconductor             |  |

| DC      | duty cycle                                          |  |

| EMI     | electromagnetic interference                        |  |

| LVCMOS  | low voltage complementary metal-oxide semiconductor |  |

| LVPECL  | low voltage pseudo (positive) emitter coupled logic |  |

| OE      | output enable                                       |  |

| PECL    | pseudo (positive) emitter coupled logic             |  |

| PLL     | phase locked loop                                   |  |

| TSSOP   | thin-shrink small outline package                   |  |

## **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure |  |

|--------|-----------------|--|

| °C     | degree Celsius  |  |

| kΩ     | kilohm          |  |

| MHz    | megahertz       |  |

| ms     | millisecond     |  |

| ns     | nanosecond      |  |

| Ω      | ohm             |  |

| %      | percent         |  |

| pF     | picofarad       |  |

| ps     | picosecond      |  |

| V      | volt            |  |

## **Document History Page**

|      | Document Title: CY2213, High Frequency Programmable PECL Clock Generator<br>Document Number: 38-07263 |                    |                    |                                                                                                                                                                                                                  |  |

|------|-------------------------------------------------------------------------------------------------------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev. | ECN                                                                                                   | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                            |  |

| **   | 113090                                                                                                | 02/06/02           | DSG                | Change from Spec number: 38-01100 to 38-07263                                                                                                                                                                    |  |

| *A   | 113512                                                                                                | 05/24/02           | CKN                | Added PLL Block Diagram (Figure 5) and PLL frequency equation                                                                                                                                                    |  |

| *B   | 121882                                                                                                | 12/14/02           | RBI                | Power up requirements added to Operating Conditions                                                                                                                                                              |  |

| *C   | 123215                                                                                                | 12/19/02           | LJN                | Previous revision was released with incorrect *A numbering in footer; *A should have been *B (and was changed accordingly)                                                                                       |  |

| *D   | 124012                                                                                                | 03/05/03           | CKN                | Added -2 to data sheet; edited line 3 of Benefits                                                                                                                                                                |  |

| *E   | 126557                                                                                                | 05/27/03           | RGL                | Added 200 MHz Jitter Spec.<br>Added optional output termination                                                                                                                                                  |  |

| *F   | 2738056                                                                                               | 07/14/09           | CXQ                | Obsolete document.                                                                                                                                                                                               |  |

| *G   | 2742301                                                                                               | 07/22/09           | CXQ                | Undo obsolete document. Removed all references to obsolete -2 option. Changed Ordering Information entry to Pb-free CY2213ZXC-1 and -1T. Revised the version of Package Drawing from 51-85091 ** to 51-85091 *A. |  |

| *H   | 3709157                                                                                               | 08/10/2012         | PURU               | Added Ordering Code Definitions. Updated Package Diagrams (spec 51-85091 (Changed revision from *A to *D)). Added Acronyms and Units of Measure. Updated in new template.                                        |  |

| *    | 4575273                                                                                               | 11/20/2014         | PURU               | Added related documentation hyperlink in page 1. Updated Package Diagrams.                                                                                                                                       |  |

| *J   | 4888407                                                                                               | 08/18/2015         | XHT                | Sunset review, no change                                                                                                                                                                                         |  |

| *K   | 5992889                                                                                               | 12/13/2017         | AESATMP8           | Updated logo and Copyright.                                                                                                                                                                                      |  |

#### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/memory

cypress.com/mcu

cypress.com/psoc

cypress.com/pmic

#### **Products**

ARM® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

cypress.com/arm

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/iot

Memory

Microcontrollers PSoC

Power Management ICs

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless Connectivity cypress.com/wireless

#### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2002-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 38-07263 Rev. \*K Revised December 13, 2017 Page 16 of 16

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

## Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9