Field Programmable SS VersaClock<sup>®</sup> Synthesizer

## Description

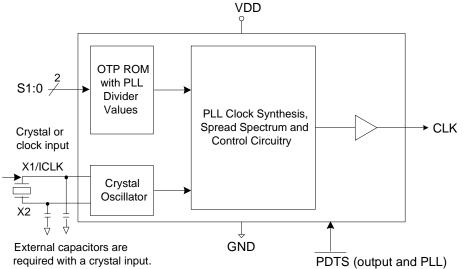

The ICS251 is a low cost, single-output, field programmable clock synthesizer. The ICS251 can generate an output frequency from 314kHz to 200MHz and may employ Spread Spectrum techniques to reduce system electro-magnetic interference (EMI).

Using IDT's VersaClock software to configure the PLL and output, the ICS251 contains a One-Time Programmable (OTP) ROM to allow field programmability. Programming features include 4 selectable configuration registers.

The device employs Phase-Locked Loop (PLL) techniques to run from a standard fundamental mode, inexpensive crystal, or clock. It can replace multiple crystals and oscillators, saving board space and cost.

The device also has a power-down feature that tri-states the clock outputs and turns off the PLLs when the PDTS pin is taken low.

The ICS251 is also available in factory programmed custom versions for high-volume applications.

## Features

- 8-pin SOIC package

- Four addressable registers

- Input crystal frequency of 5 to 27MHz

- Clock input frequency of 3 to 150MHz

- Output clock frequencies up to 200MHz

- Configurable spread spectrum modulation

- Operating voltage of 3.3V

- Replaces multiple crystals and oscillators

- Controllable output drive levels

- Advanced, low-power CMOS process

- RoHS compliant packaging

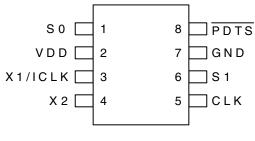

## **Pin Assignment**

8-pin (150 mil) SOIC

## **Pin Descriptions**

## Output Clock Selection Table

| S1 | S0 | CLK (MHz)         | Spread<br>Percentage |

|----|----|-------------------|----------------------|

| 0  | 0  | User Configurable | User Configurable    |

| 0  | 1  | User Configurable | User Configurable    |

| 1  | 0  | User Configurable | User Configurable    |

| 1  | 1  | User Configurable | User Configurable    |

| Pin<br>Number | Pin<br>Name | Pin    | Pin Description                                                                                                                                                                                                                |

|---------------|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number        | Name        | Туре   |                                                                                                                                                                                                                                |

| 1             | S0          | Input  | Select pin 0 for frequency selection on CLK. Internal pull-up resistor.                                                                                                                                                        |

| 2             | VDD         | Power  | Connect to +3.3 V.                                                                                                                                                                                                             |

| 3             | X1/ICLK     | XI     | Connect this pin to a crystal or external clock input.                                                                                                                                                                         |

| 4             | X2          | XO     | Connect this pin to a crystal, or float for clock input.                                                                                                                                                                       |

| 5             | CLK         | Output | Clock output. Weak internal pull-down when tri-state.                                                                                                                                                                          |

| 6             | S1          | Input  | Select pin 1 for frequency selection on CLK. Internal pull-up resistor.                                                                                                                                                        |

| 7             | GND         | Power  | Connect this to ground.                                                                                                                                                                                                        |

| 8             | PDTS        | Input  | Powers down entire chip. Tri-states CLK outputs when low. No internal pull-up resistor. The pin must be tied either directly or through the external resistor to VDD or GND. External resistor value must be less than 15kOhm. |

## **External Components**

The ICS251 requires a minimum number of external components for proper operation.

### **Series Termination Resistor**

Clock output traces over one inch should use series termination. To series terminate a  $50\Omega$  trace (a commonly used trace impedance), place a  $33\Omega$  resistor in series with the clock line, as close to the clock output pin as possible. The nominal impedance of the clock output is  $20\Omega$ .

### **Decoupling Capacitor**

As with any high-performance mixed-signal IC, the ICS251 must be isolated from system power supply noise to perform optimally.

A decoupling capacitor of  $0.01 \mu F$  must be connected between VDD and the PCB ground plane.

### **Crystal Load Capacitors**

The device crystal connections should include pads for small capacitors from X1 to ground and from X2 to ground. These capacitors are used to adjust the stray capacitance of the board to match the nominally required crystal load

capacitance. Because load capacitance can only be increased in this trimming process, it is important to keep stray capacitance to a minimum by using very short PCB traces (and no vias) been the crystal and device. Crystal capacitors must be connected from each of the pins X1 and X2 to ground.

The value (in pF) of these crystal caps should equal (C<sub>L</sub> -6pF) × 2. In this equation, C<sub>L</sub>= crystal load capacitance in pF. Example: For a crystal with a 16pF load capacitance, each crystal capacitor would be 20pF [(16-6) × 2] = 20.

### **PCB Layout Recommendations**

For optimum device performance and lowest output phase noise, the following guidelines should be observed.

1) The  $0.01\mu$ F decoupling capacitor should be mounted on the component side of the board as close to the VDD pin as possible. No vias should be used between the decoupling capacitor and VDD pin. The PCB trace to VDD pin should be kept as short as possible, as should the PCB trace to the ground via. Distance of the ferrite bead and bulk decoupling from the device is less critical.

2) The external crystal should be mounted just next to the device with short traces. The X1 and X2 traces should not be routed next to each other with minimum spaces, instead they should be separated and away from other traces.

3) To minimize EMI, the  $33\Omega$  series termination resistor (if needed) should be placed close to the clock output.

4) An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers. Other signal traces should be routed away from the ICS251. This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.

### **ICS251** Configuration Capabilities

The architecture of the ICS251 allows the user to easily configure the device to a wide range of output frequencies, for a given input reference frequency.

The frequency multiplier PLL provides a high degree of precision. The M/N values (the multiplier/divide values available to generate the target VCO frequency) can be set within the range of M = 1 to 2048 and N = 1 to 1024.

The ICS251 also provides separate output divide values, from 2 through 20, to allow the two output clock banks to support widely differing frequency values from the same PLL.

Each output frequency can be represented as:

$$OutputFreq = \frac{REFFreq}{OutputDivide} \cdot \frac{M}{N}$$

### **Output Drive Control**

The ICS251 has two output drive settings. Low drive should be selected when outputs are less than 100MHz. High drive should be selected when outputs are greater than 100MHz. (Consult the AC Electrical Characteristics for output rise and fall times for each drive option.)

### IDT VersaClock Software

IDT applies years of PLL optimization experience into a user friendly software that accepts the user's target reference clock and output frequencies and generates the lowest jitter, lowest power configuration, with only a press of a button. The user does not need to have prior PLL experience or determine the optimal VCO frequency to support multiple output frequencies.

VersaClock software quickly evaluates accessible VCO frequencies with available output divide values and provides an easy to understand, bar code rating for the target output frequencies. The user may evaluate output accuracy, performance trade-off scenarios in seconds.

### **Spread Spectrum Modulation**

The ICS251 utilizes frequency modulation (FM) to distribute energy over a range of frequencies. By modulating the output clock frequencies, the device effectively lowers energy across a broader range of frequencies; thus, lowering a system's electro-magnetic interference (EMI). The modulation rate is the time from transitioning from a minimum frequency to a maximum frequency and then back to the minimum.

Spread Spectrum Modulation can be applied as either "center spread" or "down spread". During center spread modulation, the deviation from the target frequency is equal in the positive and negative directions. The effective average frequency is equal to the target frequency. In applications where the clock is driving a component with a maximum frequency rating, down spread should be applied. In this case, the maximum frequency, including modulation, is the target frequency. The effective average frequency is less than the target frequency.

The ICS251 operates in both center spread and down spread modes. For center spread, the frequency can be modulated between  $\pm 0.125\%$  to  $\pm 2.0\%$ . For down spread, the frequency can be modulated between -0.25% to -4.0%.

Both output frequency banks will utilize identical spread spectrum percentage deviations and modulation rates, if a common VCO frequency can be identified.

### **Spread Spectrum Modulation Rate**

The spread spectrum modulation frequency applied to the output clock frequency may occur at a variety of rates. For applications requiring the driving of "down-circuit" PLLs, Zero Delay Buffers, or those adhering to PCI standards, the spread spectrum modulation rate should be set to 30–33kHz. For other applications, a 120kHz modulation option is available.

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the ICS251. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Parameter             | Condition          | Min. | Тур. | Max.      | Units |  |

|-----------------------|--------------------|------|------|-----------|-------|--|

| Supply Voltage, VDD   | Referenced to GND. | -0.5 |      | 4.6       | V     |  |

| Inputs                | Referenced to GND. | -0.5 |      | VDD + 0.5 | V     |  |

| Clock Outputs         | Referenced to GND. | -0.5 |      | VDD + 0.5 | V     |  |

| Storage Temperature   |                    | -65  |      | 150       | °C    |  |

| Soldering Temperature | Max 10 seconds.    |      |      | 260       | °C    |  |

| Junction Temperature  |                    |      |      | 125       | °C    |  |

### **Recommended Operation Conditions**

| Parameter                                         | Min.  | Тур. | Max.  | Units |

|---------------------------------------------------|-------|------|-------|-------|

| Ambient Operating Temperature (ICS251M)           | 0     |      | +70   | °C    |

| Ambient Operating Temperature (ICS251MI)          | -40   |      | +85   | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.15 | +3.3 | +3.45 | V     |

| Power Supply Ramp Time                            |       |      | 4     | ms    |

## **DC Electrical Characteristics**

| Parameter                                      | Symbol           | Conditions                                                                   | Min.             | Тур. | Max.      | Units |

|------------------------------------------------|------------------|------------------------------------------------------------------------------|------------------|------|-----------|-------|

| Operating Voltage                              | VDD              |                                                                              | 3.15             | 3.3  | 3.45      | V     |

|                                                |                  | Configuration dependent - see VersaClock estimates.                          |                  |      |           | mA    |

| Operating Supply Current<br>Input High Voltage | IDD              | 33.3333 MHz output, PDTS<br>= 1, no load.<br>Note 1.                         |                  | 14   |           | mA    |

|                                                |                  | $\overline{PDTS} = 0.$                                                       |                  | 500  |           | μA    |

| Input High Voltage                             | V <sub>IH</sub>  | S1:S0.                                                                       | VDD/2 + 1        |      |           | V     |

| Input Low Voltage                              | V <sub>IL</sub>  | S1:S0.                                                                       |                  |      | 0.4       | V     |

| Input High Voltage, PDTS                       | V <sub>IH</sub>  |                                                                              | VDD - 0.5        |      |           | V     |

| Input Low Voltage, PDTS                        | V <sub>IL</sub>  |                                                                              |                  |      | 0.4       | V     |

| Input High Voltage                             | V <sub>IH</sub>  | ICLK.                                                                        | VDD/2 + 1        |      |           | V     |

| Input Low Voltage                              | V <sub>IL</sub>  | ICLK.                                                                        |                  |      | VDD/2 - 1 | V     |

| Output High Voltage (CMOS<br>High)             | V <sub>OH</sub>  | I <sub>OH</sub> = -4mA.                                                      | VDD - 0.4        |      |           | V     |

| Output High Voltage                            | V <sub>OH</sub>  | I <sub>OH</sub> = -8mA (Low Drive);<br>I <sub>OH</sub> = -12mA (High Drive). | 2.4<br>VDD - 0.4 |      |           | V     |

| Output Low Voltage                             | V <sub>OL</sub>  | $I_{OL} = 8mA$ (Low Drive);<br>$I_{OL} = 12mA$ (High Drive).                 |                  |      | 0.4       | V     |

| Short Circuit Current                          | I <sub>OS</sub>  |                                                                              |                  | ±70  |           | mA    |

| Nominal Output Impedance                       | Z <sub>O</sub>   |                                                                              |                  | 20   |           | Ω     |

| Internal Pull-up Resistor                      | R <sub>PUP</sub> | S1:S0, PDTS.                                                                 |                  | 190  |           | kΩ    |

| Internal Pull-down Resistor                    | R <sub>PD</sub>  | CLK output.                                                                  |                  | 120  |           | kΩ    |

| Input Capacitance                              | C <sub>IN</sub>  | Inputs.                                                                      |                  | 4    |           | pF    |

Unless stated otherwise, VDD = 3.3V ±5%, ambient temperature -40 to +85°C

Note 1: Example with 25MHz crystal input with output of  $33.\overline{3}$ MHz, no load, and VDD = 3.3V.

## **AC Electrical Characteristics**

| Unless stated otherwise, $VDD = 3.3V \pm 5\%$ , ambient tempe | erature -40 to +85°C |

|---------------------------------------------------------------|----------------------|

|---------------------------------------------------------------|----------------------|

| Parameter                     | Symbol          | Conditions                                                                | Min.  | Тур.         | Max. | Units |

|-------------------------------|-----------------|---------------------------------------------------------------------------|-------|--------------|------|-------|

|                               | F               | Fundamental crystal.                                                      | 5     |              | 27   | MHz   |

| Input Frequency               | F <sub>IN</sub> | Input clock.                                                              | 3     |              | 150  | MHz   |

| Output Frequency              |                 |                                                                           | 0.314 |              | 200  | MHz   |

| Output Rise Time              | t <sub>OR</sub> | 20% to 80%, Note 1.                                                       |       | 1            |      | ns    |

| Output Fall Time              | t <sub>OF</sub> | 80% to 20%, Note 1.                                                       |       | 1            |      | ns    |

| Duty Cycle                    |                 | Note 2.                                                                   | 40    | 49–51        | 60   | %     |

|                               |                 | PLL lock time from power-up.                                              |       | 4            | 10   | ms    |

|                               |                 | PDTS goes high until stable<br>CLK output, spread<br>spectrum off.        |       | .6           | 2    | ms    |

| Power-up Time                 |                 | PDTS goes high until stable<br>CLK output, spread<br>spectrum on.         |       | 4            | 7    | ms    |

|                               |                 | PDTS goes high until<br>spread spectrum is stable,<br>spread spectrum on. |       | 10           | 50   | ms    |

| One Sigma Clock Period Jitter |                 | Configuration dependent.                                                  |       | 50           |      | ps    |

| Maximum Absolute Jitter       | t <sub>ja</sub> | Deviation from Mean.<br>Configuration dependent.                          |       | <u>+</u> 200 |      | ps    |

Note 1: Measured with 15pF load.

Note 2: Duty cycle is configuration dependent. Most configurations are minimum 45% and maximum 55%.

# **Thermal Characteristics**

| Parameter                              | Symbol        | Conditions      | Min. | Тур. | Max. | Units |

|----------------------------------------|---------------|-----------------|------|------|------|-------|

|                                        | $\theta_{JA}$ | Still air.      |      | 150  |      | °C/W  |

| Thermal Resistance Junction to Ambient | $\theta_{JA}$ | 1 m/s air flow. |      | 140  |      | °C/W  |

|                                        | $\theta_{JA}$ | 3 m/s air flow. |      | 120  |      | °C/W  |

| Thermal Resistance Junction to Case    | $\theta_{JC}$ |                 |      | 40   |      | °C/W  |

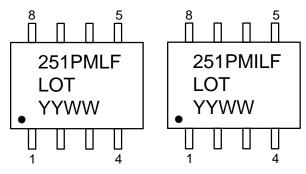

## **Marking Diagrams**

Notes:

- 1. "LOT" is the lot number.

- 2. "YYWW" is the last two digits of the year and week that the part was assembled.

- 3. "I" denotes industrial temp. range (if applicable).

- 4. "LF" denotes RoHS compliant package.

- 5. Bottom marking: country of origin.

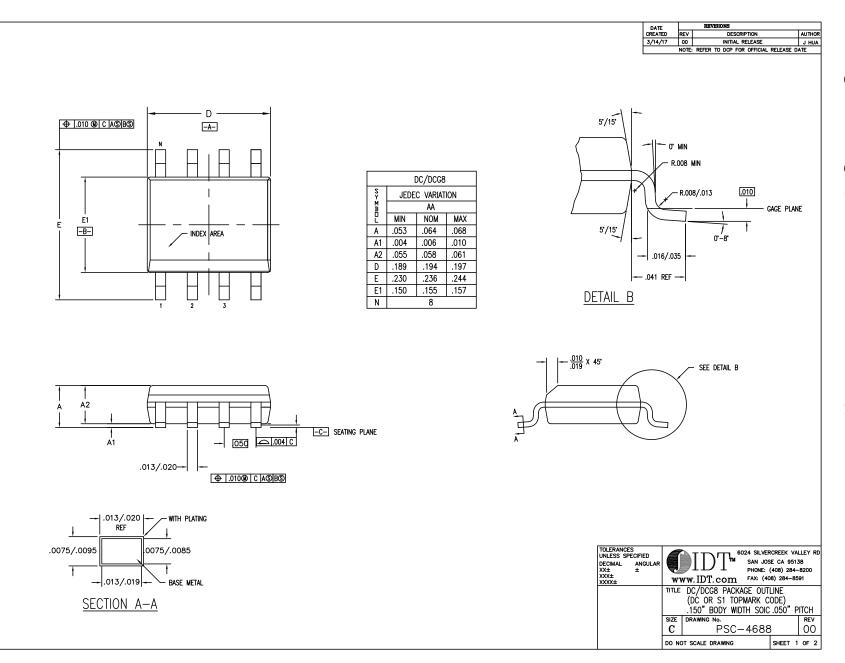

#### Package Drawings (DCG8, 8-SOIC, 150 Mil. Body), cont. DATE CREATED REV 3/14/17 00 REVISIONS REV DESCRIPTION AUTHOR 00 INITIAL RELEASE J HUA NOTE: REFER TO DOP FOR OFFICIAL RELEASE DATE LAND PATTERN DIMENSIONS Ρ2 +e} +P P1 2 3 1 MAX MIN .282 Ρ .274 P1 .142 .150 P2 .150 BSC χ .015 .024 е .050 BSC Ν 8 ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982 TOLERANCES UNLESS SPECIFIED 6024 SILVERCREEK VALLEY RD ጌ DECIMAL ANGULAR XX± ± XXX± XXX± SAN JOSE CA 95138 WWW.IDT.com FAX: (408) 284-8591 TITLE DC/DCG8 PACKAGE OUTLINE (DC OR S1 TOPMARK CODE) .150" BODY WIDTH SOIC .050" PITCH SIZE DRAWING No. REV С PSC-4688 00 DO NOT SCALE DRAWING SHEET 2 OF 2

OCTOBER 10, 2017

9

NOTES:

ALL DIMENSIONS ARE IN INCHES

1

2

## **Ordering Information**

| Part / Order Number | Marking    | Shipping Packaging | Package    | Temperature   |

|---------------------|------------|--------------------|------------|---------------|

| 251PMLF             | See page 7 | Tubes              | 8-pin SOIC | 0 to +70° C   |

| 251PMILF            |            | Tubes              | 8-pin SOIC | -40 to +85° C |

| 251M-XXLF           | 251MXXLF   | Tubes              | 8-pin SOIC | 0 to +70° C   |

| 251MI-XXLF          | 251MIXXLF  | Tubes              | 8-pin SOIC | -40 to +85° C |

| 251M-XXLFT          | 251MXXLF   | Tape and Reel      | 8-pin SOIC | 0 to +70° C   |

| 251MI-XXLFT         | 251MIXXLF  | Tape and Reel      | 8-pin SOIC | -40 to +85° C |

Parts that are ordered with a "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant. The 251M-XXLF and 251MI-XXLF are factory programmed versions of the ICS251PMLF and ICS251PMILF. A unique "-XX" suffix is assigned by the factory for each custom configuration, and a separate data sheet is kept on file. For more information on custom part numbers programmed at the factory, please contact your local IDT sales and marketing representative.

## **Revision History**

| Date             | Description of Change                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 10, 2017 | <ol> <li>Updated marking diagrams.</li> <li>Added legal disclaimer</li> <li>Updated package outline drawings.</li> <li>Updated ordering information.</li> </ol> |

| May 19, 2014     | <ol> <li>Updated Supply Voltage max rating from 7V to 4.6V</li> <li>Updated datasheet with latest version of template.</li> </ol>                               |

**Corporate Headquarters** 6024 Silver Creek Valley Road San Jose, CA 95138 USA www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales Tech Support www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc. All rights reserved.

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

#### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9