# **Dimmable Quasi-Resonant Primary Side Current-Mode Controller for LED Lighting** with Thermal Fold-back

The NCL30083 is a PWM current mode controller targeting isolated flyback and non-isolated constant current topologies. The controller operates in a quasi-resonant mode to provide high efficiency. Thanks to a novel control method, the device is able to precisely regulate a constant LED current from the primary side. This removes the need for secondary side feedback circuitry, biasing and an optocoupler.

The device is highly integrated with a minimum number of external components. A robust suite of safety protection is built in to simplify the design. This device is specifically intended for very compact space efficient designs. It supports step dimming by monitoring the AC line and detecting when the line has been toggled on-off-on by the user to reduce the light intensity in 5 steps down to 5% dimming.

#### Features

- Quasi-resonant Peak Current-mode Control Operation

- Primary Side Sensing (no optocoupler needed)

- Wide V<sub>CC</sub> Range

- Source 300 mA/Sink 500 mA Totem Pole Driver with 12 V Gate Clamp

- Precise LED Constant Current Regulation ±1% Typical

- Line Feed–forward for Enhanced Regulation Accuracy

- Low LED Current Ripple

- 250 mV ±2% Guaranteed Voltage Reference for Current Regulation

- ~ 0.9 Power Factor with Valley Fill Input Stage

- Low Start-up Current (13 µA typ.)

- 5 State Quasi-log Dimmable

- Thermal Fold-back

- Programmable soft-start

- Wide Temperature Range of -40 to +125°C

- Pb-free, Halide-free MSL1 Product

- Robust Protection Features

- Over Voltage / LED Open Circuit Protection

- Over Temperature Protection

- Secondary Diode Short Protection

- Output Short Circuit Protection

- Shorted Current Sense Pin Fault Detection

#### **Typical Applications**

- Integral LED Bulbs

- LED Power Driver Supplies

- LED Light Engines

## **ON Semiconductor®**

www.onsemi.com

#### MARKING DIAGRAM

- AAx = Specific Device Code

- = E or F А

- = Assembly Location = Year

- Y W

х

- = Work Week = Pb-Free Package

- (Note: Microdot may be in either location)

L30083x = Specific Device Code

= R

х

A

L

- = Assembly Location

- = Wafer Lot

- Y = Year

- w = Work Week

- = Pb-Free Package

- Latched and Auto-recoverable Versions

- Brown-out

- V<sub>CC</sub> Under Voltageinocionnections

- Thermal Shutdown 1

sd 📖 🛛 III SS ZCD I VIN Ŀш CS III VCC GND \_\_\_\_ DRV (Top View)

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 35 of this data sheet.

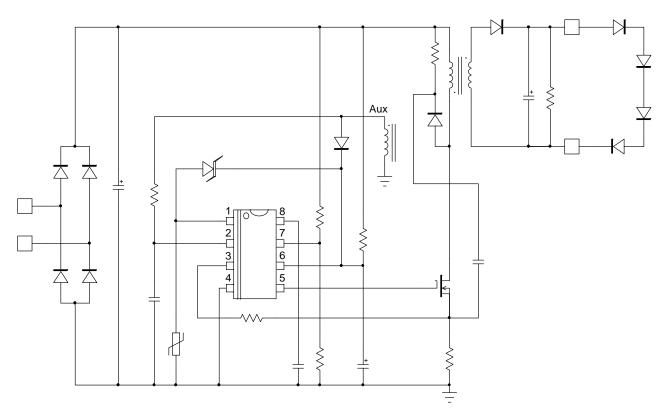

Figure 1. Typical Application Schematic for NCL30083

| Table 1. PIN FUNCTION DESCRIPTION | Table 1 | . PIN FUNCTION DESCRIPTION |

|-----------------------------------|---------|----------------------------|

|-----------------------------------|---------|----------------------------|

| Pin No | Pin Name | Function                           | Pin Description                                                                                                                                                                                                                         |

|--------|----------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SD       | Thermal Fold–back<br>and shutdown  | Connecting an NTC to this pin allows reducing the output current down to 50% of its fixed value before stopping the controller. A Zener diode can also be used to pull–up the pin and stop the controller for adjustable OVP protection |

| 2      | ZCD      | Zero Crossing Detection            | Connected to the auxiliary winding, this pin detects the core reset event.                                                                                                                                                              |

| 3      | CS       | Current sense                      | This pin monitors the primary peak current                                                                                                                                                                                              |

| 4      | GND      | -                                  | The controller ground                                                                                                                                                                                                                   |

| 5      | DRV      | Driver output                      | The current capability of the totem pole gate drive (+0.3/–0.5 A) makes it suitable to effectively drive a broad range of power MOSFETs.                                                                                                |

| 6      | VCC      | Supplies the controller            | This pin is connected to an external auxiliary voltage.                                                                                                                                                                                 |

| 7      | VIN      | Brown–Out<br>Input voltage sensing | This pin observes the HV rail and is used in valley selection. This pin also monitors and protects for low mains conditions.                                                                                                            |

| 8      | SS       | Soft-Start                         | A capacitor connected to ground select the soft-start duration.                                                                                                                                                                         |

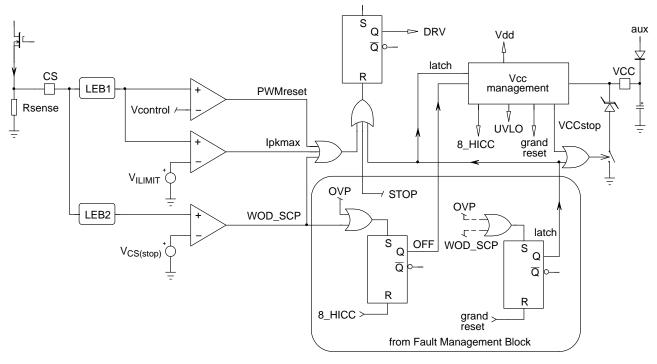

Figure 2. Internal Circuit Architecture

| Symbol                                         | Rating                                                                                                                                  | Value                                         | Unit    |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------|

| V <sub>CC(MAX)</sub><br>I <sub>CC(MAX)</sub>   | Maximum Power Supply voltage, VCC pin, continuous voltage<br>Maximum current for VCC pin                                                | -0.3, +35<br>Internally limited               | V<br>mA |

| V <sub>DRV(MAX)</sub><br>I <sub>DRV(MAX)</sub> | Maximum driver pin voltage, DRV pin, continuous voltage<br>Maximum current for DRV pin                                                  | –0.3, V <sub>DRV</sub> (Note 1)<br>–500, +800 | V<br>mA |

| V <sub>MAX</sub><br>I <sub>MAX</sub>           | Maximum voltage on low power pins (except pins ZCD, SS, DRV and VCC)<br>Current range for low power pins (except pins ZCD, DRV and VCC) | -0.3, +5.5<br>-2, +5                          | V<br>mA |

| V <sub>ZCD(MAX)</sub><br>I <sub>ZCD(MAX)</sub> | Maximum voltage for ZCD pin<br>Maximum current for ZCD pin                                                                              | -0.3, +10<br>-2, +5                           | V<br>mA |

| V <sub>SST(MAX)</sub>                          | Maximum voltage for SS pin                                                                                                              | -0.3, +10                                     | V       |

| $R_{\thetaJ-A}$                                | Thermal Resistance, Junction-to-Air                                                                                                     | 289                                           | °C/W    |

| T <sub>J(MAX)</sub>                            | Maximum Junction Temperature                                                                                                            | 150                                           | °C      |

|                                                | Operating Temperature Range                                                                                                             | -40 to +125                                   | °C      |

|                                                | Storage Temperature Range                                                                                                               | -60 to +150                                   | °C      |

|                                                | ESD Capability, HBM model (Note 2)                                                                                                      | 4                                             | kV      |

|                                                | ESD Capability, MM model (Note 2)                                                                                                       | 200                                           | V       |

#### Table 2. MAXIMUM RATINGS TABLE

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

V<sub>DRV</sub> is the DRV clamp voltage V<sub>DRV(high)</sub> when V<sub>CC</sub> is higher than V<sub>DRV(high)</sub>. V<sub>DRV</sub> is V<sub>CC</sub> unless otherwise noted.

This device series contains ESD protection and exceeds the following tests: Human Body Model 4000 V per JEDEC JESD22–A114–F and Machine Model Method 200 V per JEDEC JESD22–A115–A.

This device contains latch–up protection and exceeds 100 mA per JEDEC Standard JESD78 except for VIN pin which passes 60 mA.

| <b>Table 3. ELECTRICAL CHARACTERISTICS</b> (Unless otherwise noted: For typical values $T_J = 25^{\circ}C$ , $V_{CC} = 12$ V; |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|

| For min/max values $T_J = -40^{\circ}C$ to +125°C, Max $T_J = 150^{\circ}C$ , $V_{CC} = 12 \text{ V}$ )                       |  |

| Description                                                                                                                                                       | Test Condition                                                                                                           | Symbol                                                                                        | Min                   | Тур                     | Max                     | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|-------------------------|-------------------------|----------|

| STARTUP AND SUPPLY CIRCUITS                                                                                                                                       |                                                                                                                          |                                                                                               |                       |                         |                         |          |

| Supply Voltage<br>Startup Threshold<br>Minimum Operating Voltage<br>Hysteresis $V_{CC(on)} - V_{CC(off)}$<br>Internal logic reset                                 | $V_{CC}$ increasing $V_{CC}$ decreasing $V_{CC}$ decreasing $V_{CC}$ decreasing                                          | V <sub>CC(on)</sub><br>V <sub>CC(off)</sub><br>V <sub>CC(HYS)</sub><br>V <sub>CC(reset)</sub> | 16<br>8.2<br>8<br>3.5 | 18<br>8.8<br>-<br>4.5   | 20<br>9.4<br>-<br>5.5   | V        |

| Over Voltage Protection<br>VCC OVP threshold                                                                                                                      |                                                                                                                          | V <sub>CC(OVP)</sub>                                                                          | 26                    | 28                      | 30                      | V        |

| V <sub>CC(off)</sub> noise filter<br>V <sub>CC(reset)</sub> noise filter-                                                                                         |                                                                                                                          | t <sub>VCC(off)</sub><br>t <sub>VCC(reset)</sub>                                              | -<br>-                | 5<br>20                 | -                       | μS       |

| Startup current                                                                                                                                                   |                                                                                                                          | I <sub>CC(start)</sub>                                                                        | -                     | 13                      | 30                      | μΑ       |

| Startup current in fault mode<br>Supply Current<br>Device Disabled/Fault<br>Device Enabled/No output load on pin 5<br>Device Switching (F <sub>sw</sub> = 65 kHz) | $V_{CC} > V_{CC(off)}$ $F_{sw} = 65 \text{ kHz}$ $C_{DRV} = 470 \text{ pF},$ $F_{sw} = 65 \text{ kHz}$                   | I <sub>CC(sFault)</sub><br>I <sub>CC1</sub><br>I <sub>CC2</sub><br>I <sub>CC3</sub>           | -<br>0.8<br>-<br>-    | 46<br>1.2<br>2.3<br>2.7 | 60<br>1.4<br>4.0<br>5.0 | μA<br>mA |

| CURRENT SENSE                                                                                                                                                     |                                                                                                                          |                                                                                               |                       |                         |                         |          |

| Maximum Internal current limit                                                                                                                                    |                                                                                                                          | V <sub>ILIM</sub>                                                                             | 0.95                  | 1                       | 1.05                    | V        |

| Leading Edge Blanking Duration for $V_{ILIM}$<br>(T <sub>j</sub> = -25°C to 125°C)                                                                                |                                                                                                                          | t <sub>LEB</sub>                                                                              | 250                   | 300                     | 350                     | ns       |

| Leading Edge Blanking Duration for $V_{ILIM}$<br>(T <sub>j</sub> = -40°C to 125°C)                                                                                |                                                                                                                          | t <sub>LEB</sub>                                                                              | 240                   | 300                     | 350                     | ns       |

| Input Bias Current                                                                                                                                                | DRV high                                                                                                                 | I <sub>bias</sub>                                                                             | -                     | 0.02                    | -                       | μΑ       |

| Propagation delay from current detection to gate off-state                                                                                                        |                                                                                                                          | t <sub>ILIM</sub>                                                                             | -                     | 50                      | 150                     | ns       |

| Threshold for immediate fault protection activation                                                                                                               |                                                                                                                          | V <sub>CS(stop)</sub>                                                                         | 1.35                  | 1.5                     | 1.65                    | V        |

| Leading Edge Blanking Duration for $V_{CS(stop)}$                                                                                                                 |                                                                                                                          | t <sub>BCS</sub>                                                                              | -                     | 120                     | -                       | ns       |

| Blanking time for CS to GND short detection $V_{\mbox{pinVIN}}$ = 1 V                                                                                             |                                                                                                                          | t <sub>CS(blank1)</sub>                                                                       | 6                     | -                       | 12                      | μs       |

| Blanking time for CS to GND short detection $V_{\text{pinVIN}}$ = 3.3 V                                                                                           |                                                                                                                          | t <sub>CS(blank2)</sub>                                                                       | 2                     | -                       | 4                       | μS       |

| GATE DRIVE                                                                                                                                                        |                                                                                                                          |                                                                                               |                       |                         |                         |          |

| Drive Resistance<br>DRV Sink<br>DRV Source                                                                                                                        |                                                                                                                          | R <sub>SNK</sub><br>R <sub>SRC</sub>                                                          | -<br>-                | 13<br>30                |                         | Ω        |

| Drive current capability<br>DRV Sink (Note 4)<br>DRV Source (Note 4)                                                                                              |                                                                                                                          | I <sub>SNK</sub><br>I <sub>SRC</sub>                                                          |                       | 500<br>300              |                         | mA       |

| Rise Time (10% to 90%)                                                                                                                                            | C <sub>DRV</sub> = 470 pF                                                                                                | tr                                                                                            | -                     | 40                      | -                       | ns       |

| Fall Time (90% to 10%)                                                                                                                                            | C <sub>DRV</sub> = 470 pF                                                                                                | t <sub>f</sub>                                                                                | -                     | 30                      | -                       | ns       |

| DRV Low Voltage                                                                                                                                                   | $\begin{array}{l} V_{CC} = V_{CC(off)} \texttt{+} 0.2 \ V \\ C_{DRV} = 470 \ pF, \\ R_{DRV} = 33 \ k \Omega \end{array}$ | V <sub>DRV(low)</sub>                                                                         | 8                     | -                       | -                       | V        |

| DRV High Voltage                                                                                                                                                  | $V_{CC} = 30 V$<br>$C_{DRV} = 470 \text{ pF},$<br>$R_{DRV} = 33 \text{ k}\Omega$                                         | $V_{\text{DRV}(\text{high})}$                                                                 | 10                    | 12                      | 14                      | V        |

4. Guaranteed by design 5. OTP triggers when  $R_{NTC} = 4.7 \text{ k}\Omega$

| <b>Table 3. ELECTRICAL CHARACTERISTICS</b> (Unless otherwise noted: For typical values $T_J = 25^{\circ}C$ , $V_{CC} = 12 V$ ; |  |

|--------------------------------------------------------------------------------------------------------------------------------|--|

| For min/max values $T_J = -40^{\circ}C$ to +125°C, Max $T_J = 150^{\circ}C$ , $V_{CC} = 12$ V)                                 |  |

| Description                                                                                                                                         | Test Condition                                            | Symbol                             | Min       | Тур         | Мах       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|-----------|-------------|-----------|------|

| ZERO VOLTAGE DETECTION CIRCUIT                                                                                                                      |                                                           |                                    |           |             |           |      |

| ZCD threshold voltage                                                                                                                               | V <sub>ZCD</sub> increasing                               | V <sub>ZCD(THI)</sub>              | 25        | 45          | 65        | mV   |

| ZCD threshold voltage (Note 4)                                                                                                                      | V <sub>ZCD</sub> decreasing                               | V <sub>ZCD(THD)</sub>              | 5         | 25          | 45        | mV   |

| ZCD hysteresis (Note 4)                                                                                                                             | V <sub>ZCD</sub> increasing                               | V <sub>ZCD(HYS)</sub>              | 10        | -           | -         | mV   |

| Threshold voltage for output short circuit or aux. winding short circuit detection                                                                  |                                                           | V <sub>ZCD(short)</sub>            | 0.8       | 1           | 1.2       | V    |

| Short circuit detection Timer                                                                                                                       | $V_{ZCD} < V_{ZCD(short)}$                                | t <sub>OVLD</sub>                  | 70        | 90          | 110       | ms   |

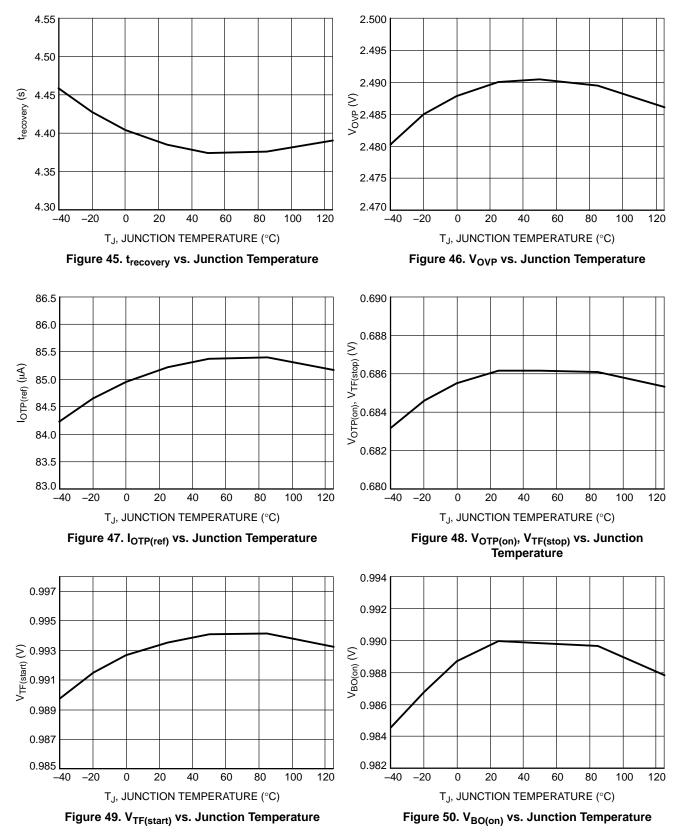

| Auto-recovery timer duration                                                                                                                        |                                                           | t <sub>recovery</sub>              | 3         | 4           | 5         | S    |

| Input clamp voltage<br>High state<br>Low state                                                                                                      | I <sub>pin1</sub> = 3.0 mA<br>I <sub>pin1</sub> = -2.0 mA | V <sub>CH</sub><br>V <sub>CL</sub> | _<br>_0.9 | 9.5<br>-0.6 | _<br>_0.3 | V    |

| Propagation Delay from valley detection to DRV high                                                                                                 | V <sub>ZCD</sub> decreasing                               | t <sub>DEM</sub>                   | -         | -           | 150       | ns   |

| Equivalent time constant for ZCD input (Note 4)                                                                                                     |                                                           | t <sub>PAR</sub>                   | -         | 20          | -         | ns   |

| Blanking delay after on-time                                                                                                                        |                                                           | t <sub>BLANK</sub>                 | 2.25      | 3           | 3.75      | μs   |

| Timeout after last demag transition                                                                                                                 |                                                           | t <sub>TIMO</sub>                  | 5         | 6.5         | 8         | μs   |

| CONSTANT CURRENT CONTROL                                                                                                                            |                                                           |                                    |           |             |           |      |

| Reference Voltage at $T_j = 25^{\circ}C$                                                                                                            |                                                           | V <sub>REF</sub>                   | 245       | 250         | 255       | mV   |

| Reference Voltage $T_j = -40^{\circ}C$ to $125^{\circ}C$                                                                                            |                                                           | V <sub>REF</sub>                   | 242.5     | 250         | 257.5     | mV   |

| 70% reference voltage                                                                                                                               |                                                           | V <sub>REF70</sub>                 | -         | 175         | -         | mV   |

| 40% reference Voltage                                                                                                                               |                                                           | V <sub>REF40</sub>                 | -         | 100         | -         | mV   |

| 25% reference Voltage                                                                                                                               |                                                           | V <sub>REF25</sub>                 | -         | 62.5        | -         | mV   |

| 10% reference Voltage                                                                                                                               |                                                           | V <sub>REF10</sub>                 | -         | 25          | -         | mV   |

| 5% reference Voltage                                                                                                                                |                                                           | V <sub>REF05</sub>                 | -         | 12.5        | -         | mV   |

| Current sense lower threshold for detection of the leakage inductance reset time                                                                    |                                                           | V <sub>CS(low)</sub>               | 30        | 55          | 80        | mV   |

| LINE FEED-FORWARD                                                                                                                                   |                                                           |                                    |           |             |           |      |

| V <sub>VIN</sub> to I <sub>CS(offset)</sub> conversion ratio                                                                                        |                                                           | K <sub>LFF</sub>                   | 15        | 17          | 19        | μA/V |

| Offset current maximum value                                                                                                                        | $V_{pinVIN} = 4.5 V$                                      | I <sub>offset(MAX)</sub>           | 67.5      | 76.5        | 85.5      | μA   |

| $V_{\mbox{\scriptsize REF}}$ value below which the offset current source is turned off                                                              | V <sub>REF</sub> decreases                                | V <sub>REF(off)</sub>              | -         | 37.5        | -         | mV   |

| $V_{\mbox{\scriptsize REF}}$ value above which the offset current source is turned on                                                               | V <sub>REF</sub> increases                                | V <sub>REF(on)</sub>               | -         | 50          | -         | mV   |

| VALLEY SELECTION                                                                                                                                    |                                                           |                                    |           |             |           |      |

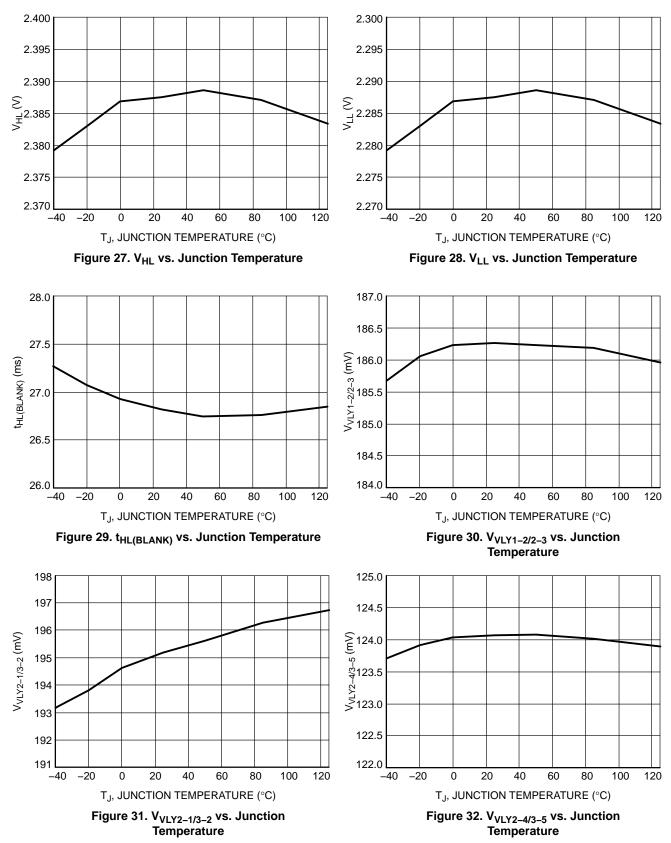

| Threshold for line range detection $V_{in}$ increasing (1 <sup>st</sup> to 2 <sup>nd</sup> valley transition for $V_{REF} > 0.75$ V)                | $V_{\mbox{VIN}}$ increases                                | V <sub>HL</sub>                    | 2.28      | 2.4         | 2.52      | V    |

| Threshold for line range detection V <sub>in</sub> decreasing $(2^{nd} \text{ to } 1^{st} \text{ valley transition for } V_{REF} > 0.75 \text{ V})$ | V <sub>VIN</sub> decreases                                | V <sub>LL</sub>                    | 2.18      | 2.3         | 2.42      | V    |

| Blanking time for line range detection                                                                                                              |                                                           | t <sub>HL(blank)</sub>             | 15        | 25          | 35        | ms   |

4. Guaranteed by design 5. OTP triggers when  $R_{NTC} = 4.7 \text{ k}\Omega$

| Table 3. ELECTRICAL CHARACTERISTICS (Unless otherwise noted: For typical values $T_J = 25^{\circ}C$ , $V_{CC} = 12 V$ ; |  |

|-------------------------------------------------------------------------------------------------------------------------|--|

| For min/max values $T_J = -40^{\circ}$ C to +125°C, Max $T_J = 150^{\circ}$ C, $V_{CC} = 12$ V)                         |  |

| Description                                                                                                                                                                                                                  | Test Condition                                           | Symbol                                                 | Min   | Тур          | Max   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|-------|--------------|-------|------|

| VALLEY SELECTION                                                                                                                                                                                                             |                                                          | •                                                      |       |              |       |      |

| Valley thresholds                                                                                                                                                                                                            |                                                          | 1                                                      |       |              |       | mV   |

| 1 <sup>st</sup> to 2 <sup>nd</sup> valley transition at LL and 2 <sup>nd</sup> to 3 <sup>rd</sup> valley HL                                                                                                                  | V <sub>REF</sub> decreases                               | V <sub>VLY1-2/2-3</sub>                                | 177.5 | 187.5        | 197.5 |      |

| 2 <sup>nd</sup> to 1 <sup>st</sup> valley transition at LL and 3 <sup>rd</sup> to 2 <sup>nd</sup> valley HL                                                                                                                  | V <sub>REF</sub> increases                               | V <sub>VLY2-1/3-2</sub>                                | 185.0 | 195.0        | 205.0 |      |

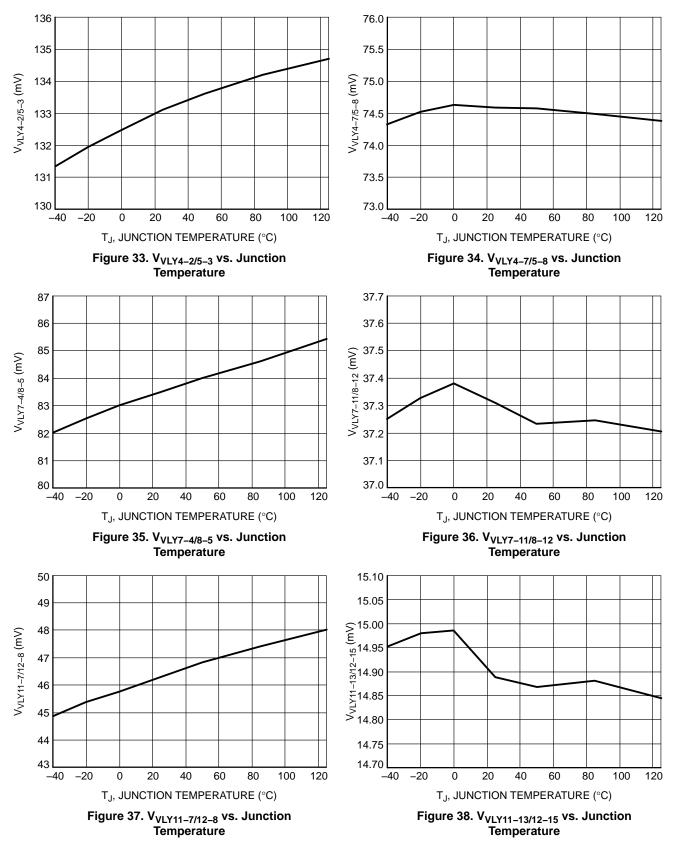

| 2 <sup>nd</sup> to 4 <sup>th</sup> valley transition at LL and 3 <sup>rd</sup> to 5 <sup>th</sup> valley HL                                                                                                                  | V <sub>REF</sub> decreases                               | V <sub>VLY2-4/3-5</sub>                                | 117.5 | 125.0        | 132.5 |      |

| 4 <sup>th</sup> to 2 <sup>nd</sup> valley transition at LL and 5 <sup>th</sup> to 3 <sup>rd</sup> valley HL                                                                                                                  | V <sub>REF</sub> increases                               | V <sub>VLY4-2/5-3</sub>                                | 125.0 | 132.5        | 140.0 |      |

| 4 <sup>th</sup> to 7 <sup>th</sup> valley transition at LL and 5 <sup>th</sup> to 8 <sup>th</sup> valley HL                                                                                                                  | V <sub>REF</sub> decreases                               | V <sub>VLY4-7/5-8</sub>                                | -     | 75.0         | -     |      |

| 7 <sup>th</sup> to 4 <sup>th</sup> valley transition at LL and 8 <sup>th</sup> to 5 <sup>th</sup> valley HL<br>7 <sup>th</sup> to 11 <sup>th</sup> valley transition at LL and 8 <sup>th</sup> to 12 <sup>th</sup> valley HL | V <sub>REF</sub> increases                               | V <sub>VLY7-4/8-5</sub>                                | -     | 82.5         | -     |      |

| $11^{\text{th}}$ to $7^{\text{th}}$ valley transition at LL and $3^{\text{th}}$ to $12^{\text{th}}$ valley HL                                                                                                                | V <sub>REF</sub> decreases<br>V <sub>REF</sub> increases | V <sub>VLY7–11/8–12</sub><br>V <sub>VLY11–7/12–8</sub> | _     | 37.5<br>50.0 |       |      |

| 11 <sup>th</sup> to 13 <sup>th</sup> valley transition at LL and 12 <sup>th</sup> to 15 <sup>th</sup> valley HL                                                                                                              | V <sub>REF</sub> decreases                               | VLY11-7/12-8<br>V <sub>VLY11-13/12-15</sub>            | _     | 15.0         | _     |      |

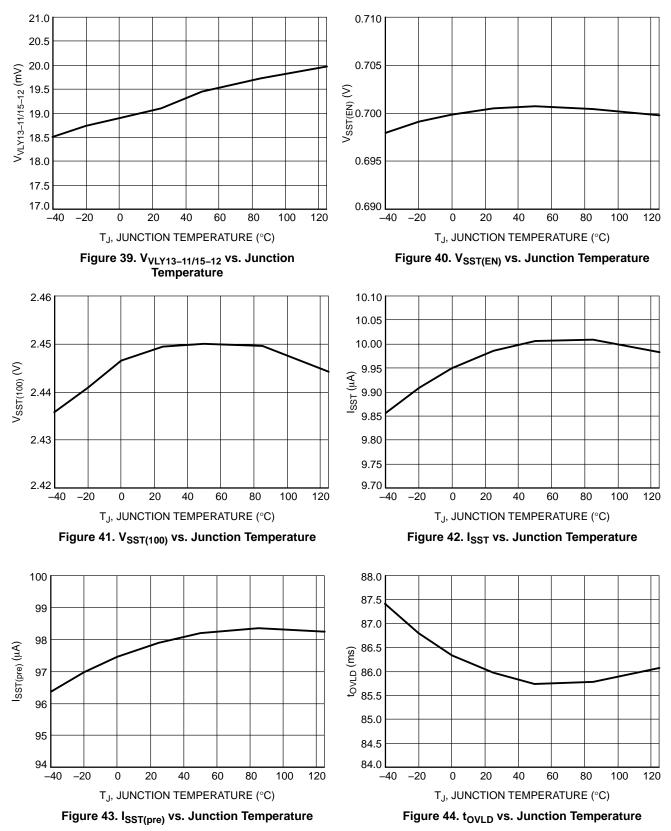

| 13 <sup>th</sup> to 11 <sup>th</sup> valley transition at LL and 15 <sup>th</sup> to 12 <sup>th</sup> valley HL                                                                                                              | V <sub>REF</sub> increases                               | VLY11-13/12-15<br>V <sub>VLY13-11/15-12</sub>          | -     | 20.0         | -     |      |

| SOFT-STAT PIN                                                                                                                                                                                                                | I                                                        |                                                        |       |              |       |      |

| SS pin voltage for zero output current (enable)                                                                                                                                                                              |                                                          | V <sub>SST(EN)</sub>                                   | 0.66  | 0.7          | 0.74  | V    |

| SS pin voltage for 100% of output current                                                                                                                                                                                    |                                                          | V <sub>SST100</sub>                                    | 2.25  | 2.45         | 2.65  | V    |

| Clamping voltage for SS pin                                                                                                                                                                                                  |                                                          | V <sub>SST(CLP)</sub>                                  | -     | 7.8          | -     | V    |

| Soft-start current source                                                                                                                                                                                                    |                                                          | I <sub>SST</sub>                                       | 8.5   | 10           | 11.5  | μΑ   |

| Pre-charge current source                                                                                                                                                                                                    | $V_{SST} < V_{SST(EN)}$                                  | I <sub>SST(pre)</sub>                                  | -     | 100          | -     | μΑ   |

| THERMAL FOLD-BACK AND OVP                                                                                                                                                                                                    |                                                          |                                                        |       |              |       |      |

| SD pin voltage at which thermal fold-back starts                                                                                                                                                                             |                                                          | V <sub>TF(start)</sub>                                 | 0.9   | 1            | 1.2   | V    |

| SD pin voltage at which thermal fold-back stops $(I_{out} = 50\% I_{out(nom)})$                                                                                                                                              |                                                          | V <sub>TF(stop)</sub>                                  | 0.64  | 0.68         | 0.72  | V    |

| Reference current for direct connection of an NTC (Note 5)                                                                                                                                                                   |                                                          | I <sub>OTP(REF)</sub>                                  | 80    | 85           | 90    | μΑ   |

| Fault detection level for OTP (Note 5)                                                                                                                                                                                       | V <sub>SD</sub> decreasing                               | V <sub>OTP(off)</sub>                                  | 0.47  | 0.5          | 0.53  | V    |

| SD pin level at which controller re-start switching after OTP detection                                                                                                                                                      | $V_{\text{SD}}$ increasing                               | V <sub>OTP(on)</sub>                                   | 0.64  | 0.68         | 0.72  | V    |

| Timer duration after which the controller is allowed to start pulsing (Note 5)                                                                                                                                               |                                                          | t <sub>OTP(start)</sub>                                | 180   | -            | 300   | μs   |

| Clamped voltage (SD pin left open)                                                                                                                                                                                           | SD pin open                                              | V <sub>SD(clamp)</sub>                                 | 1.13  | 1.35         | 1.57  | V    |

| Clamp series resistor                                                                                                                                                                                                        |                                                          | R <sub>SD(clamp)</sub>                                 | -     | 1.6          | -     | kΩ   |

| SD pin detection level for OVP                                                                                                                                                                                               | V <sub>SD</sub> increasing                               | V <sub>OVP</sub>                                       | 2.35  | 2.5          | 2.65  | V    |

| Delay before OVP or OTP confirmation (OVP and OTP)                                                                                                                                                                           |                                                          | T <sub>SD(delay)</sub>                                 | 15    | 30           | 45    | μs   |

| THERMAL SHUTDOWN                                                                                                                                                                                                             |                                                          |                                                        |       |              |       |      |

| Thermal Shutdown (Note 4)                                                                                                                                                                                                    | Device switching<br>(F <sub>SW</sub> around 65 kHz)      | T <sub>SHDN</sub>                                      | 130   | 155          | 170   | °C   |

| Thermal Shutdown Hysteresis (Note 4)                                                                                                                                                                                         |                                                          | T <sub>SHDN(HYS)</sub>                                 | -     | 55           | -     | °C   |

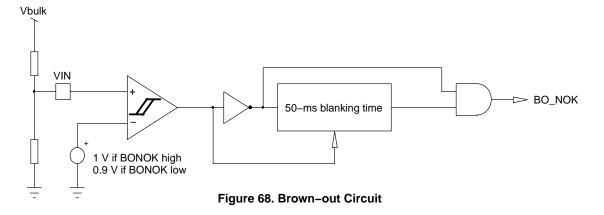

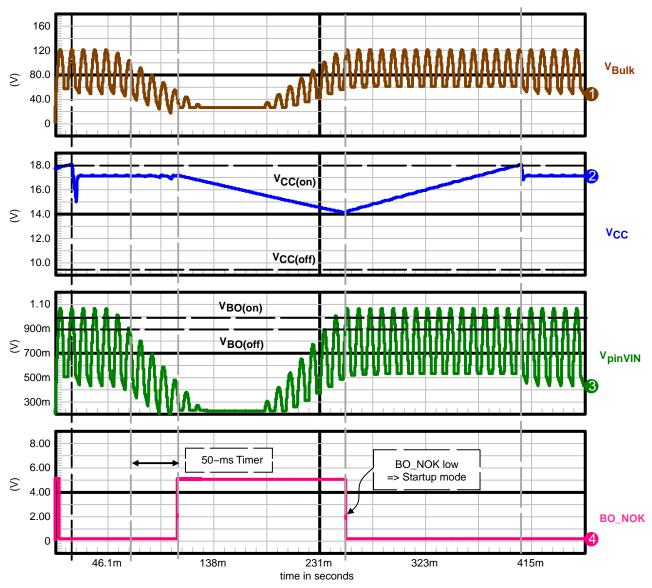

| BROWN-OUT                                                                                                                                                                                                                    |                                                          |                                                        |       |              |       |      |

| Brown–Out ON level (IC start pulsing)                                                                                                                                                                                        | V <sub>SD</sub> increasing                               | V <sub>BO(on)</sub>                                    | 0.90  | 1            | 1.10  | V    |

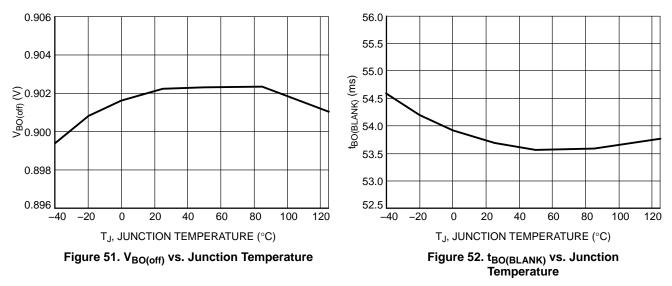

| Brown–Out OFF level (IC shuts down)                                                                                                                                                                                          | V <sub>SD</sub> decreasing                               | V <sub>BO(off)</sub>                                   | 0.85  | 0.9          | 0.95  | V    |

| BO comparators delay                                                                                                                                                                                                         |                                                          | t <sub>BO(delay)</sub>                                 | 1     | 30           | -     | μs   |

| Brown–Out blanking time                                                                                                                                                                                                      |                                                          | t <sub>BO(blank)</sub>                                 | 35    | 50           | 65    | ms   |

| Brown-out pin bias current                                                                                                                                                                                                   |                                                          | I <sub>BO(bias)</sub>                                  | -250  | -            | 250   | nA   |

4. Guaranteed by design 5. OTP triggers when  $R_{NTC} = 4.7 \text{ k}\Omega$

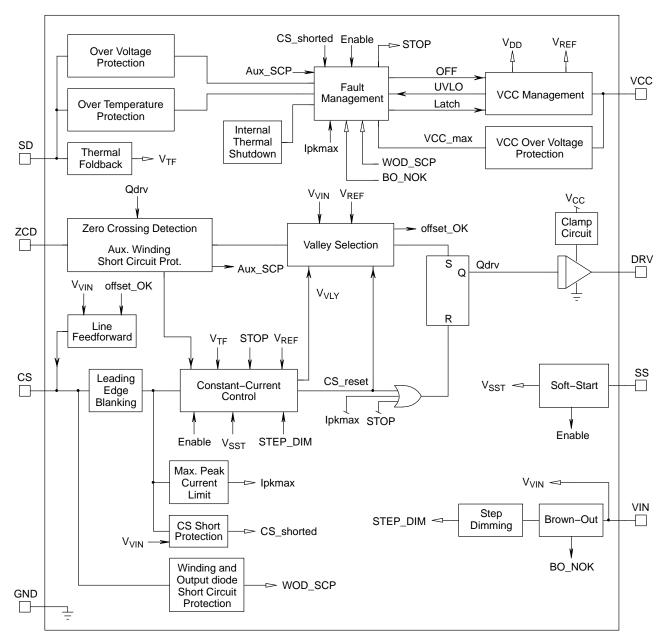

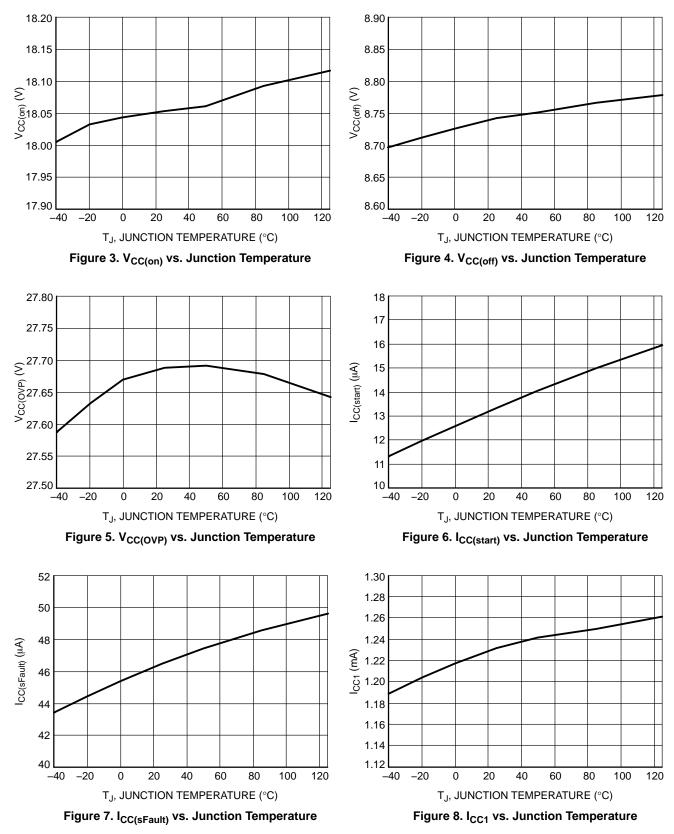

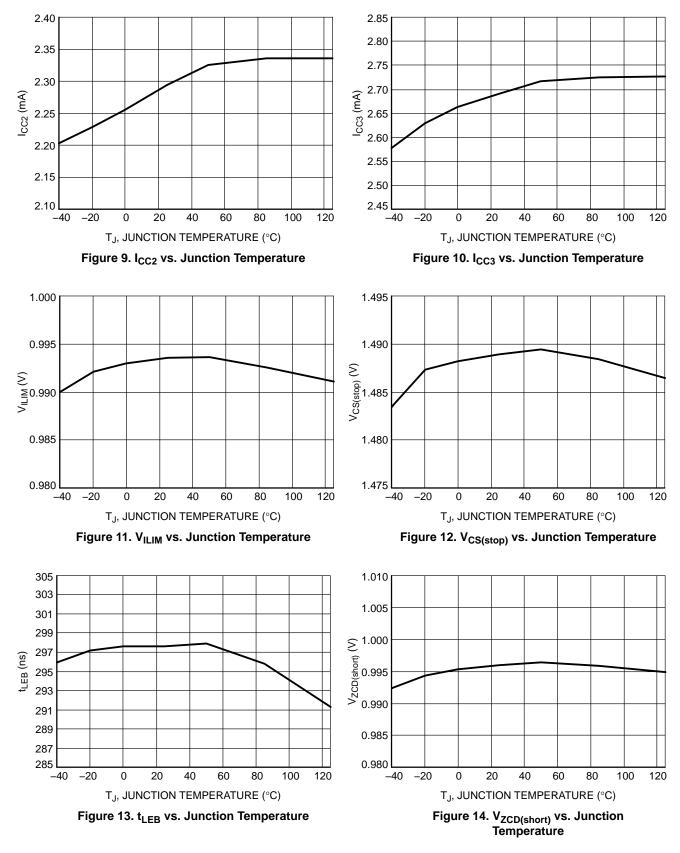

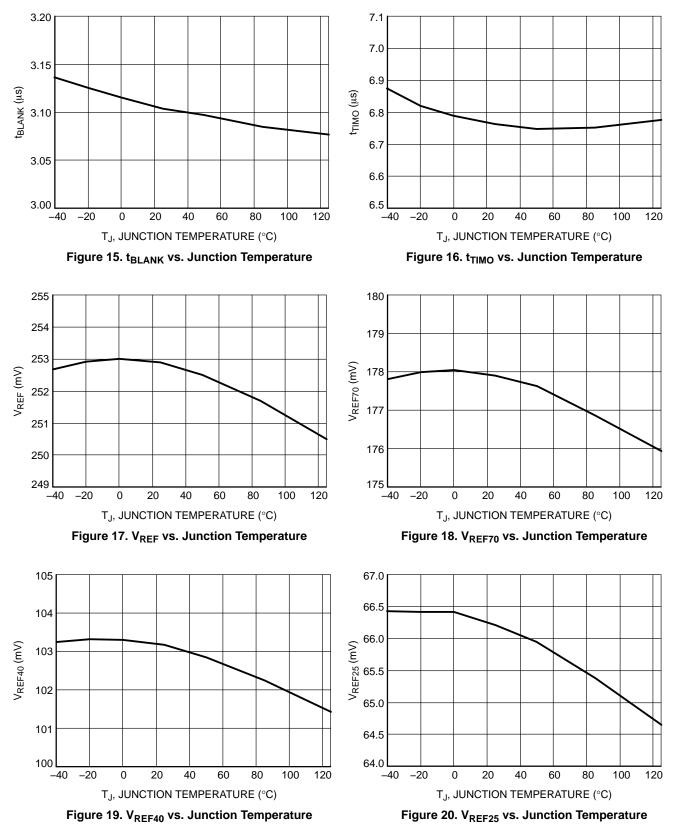

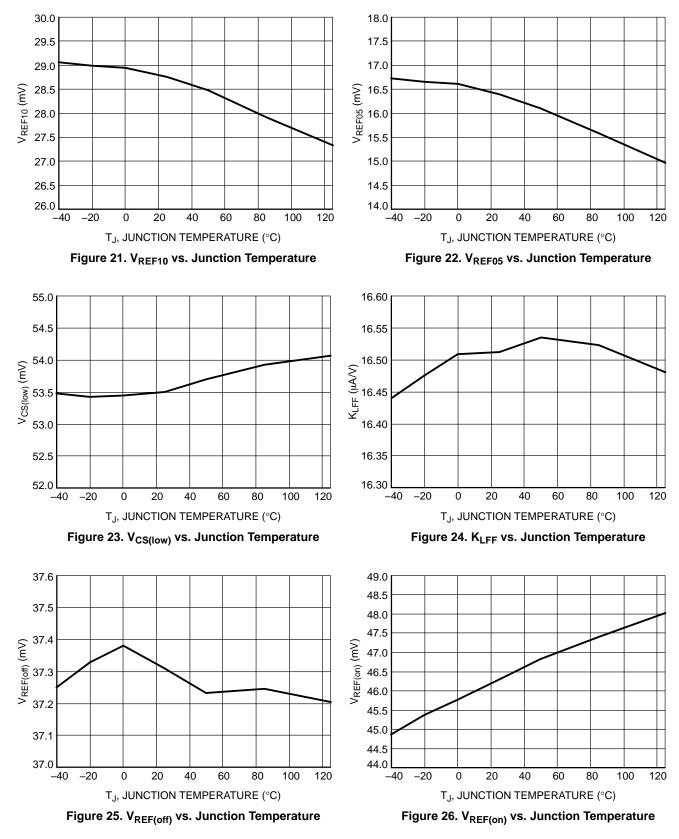

## **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

## **APPLICATION INFORMATION**

The NCL30083 implements a current-mode architecture operating in quasi-resonant mode. Thanks to proprietary circuitry, the controller is able to accurately regulate the secondary side current of the flyback converter without using any opto-coupler or measuring directly the secondary side current.

- Quasi-Resonance Current-Mode Operation: implementing quasi-resonance operation in peak current-mode control, the NCL30083 optimizes the efficiency by switching in the valley of the MOSFET drain-source voltage. Thanks to a smart control algorithm, the controller locks-out in a selected valley and remains locked until the input voltage or the output current set point significantly changes.

- **Primary Side Constant Current Control:** thanks to a proprietary circuit, the controller is able to take into account the effect of the leakage inductance of the transformer and allow accurate control of the secondary side current.

- Line Feed–forward: compensation for possible variation of the output current caused by system slew rate variation.

- **Open LED protection:** if the voltage on the VCC pin exceeds an internal limit, the controller shuts down and waits 4 seconds before restarting pulsing.

- Thermal Fold–back / Over Temperature / Over Voltage Protection: by combining a dual threshold on the SD pin, the controller allows the direct connection of an NTC to ground plus a Zener diode to a monitored voltage. The temperature is monitored and the output current is linearly reduced in the event that the temperature exceeds a prescribed level. If the

temperature continues to increase, the current will be further reduced until the controller is stopped. The control will automatically restart if the temperature is reduced. This pin can implement a programmable OVP shutdown that can also auto–restart the device.

- **Brown–Out:** the controller includes a brown–out circuit which safely stops the controller in case the input voltage is too low. The device will automatically restart if the line recovers.

- Cycle-by-cycle peak current limit: when the current sense voltage exceeds the internal threshold V<sub>ILIM</sub>, the MOSFET is turned off for the rest of the switching cycle.

- Winding Short–Circuit Protection: an additional comparator with a short LEB filter (t<sub>BCS</sub>) senses the CS signal and stops the controller if V<sub>CS</sub> reaches 1.5 x V<sub>ILIM</sub>. For noise immunity reasons, this comparator is enabled only during the main LEB duration t<sub>LEB</sub>.

- Output Short-circuit protection: If a very low voltage is applied on ZCD pin for 90 ms (nominal), the controllers assume that the output or the ZCD pin is shorted to ground and enters shutdown. The auto-restart version (B suffix) waits 4 seconds, then the controller restarts switching. In the latched version (A suffix), the controller is latched as long as V<sub>CC</sub> stays above the V<sub>CC(reset)</sub> threshold.

- **Soft-start:** The soft-start pin can be used to slowly increase the output current at startup and provide a smooth turn-on of the LED light.

- **Step dimming:** Each time the IC detects a brown–out condition, the output current is decreased by discrete steps.

#### **Constant Current Control**

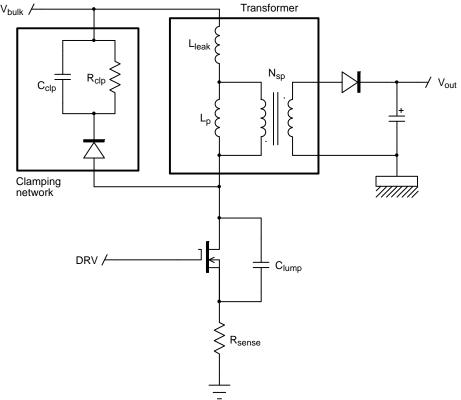

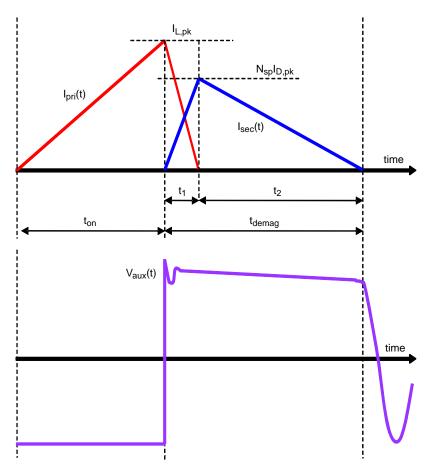

Figure 54 portrays the primary and secondary current of a flyback converter in discontinuous conduction mode (DCM). Figure 53 shows the basic circuit of a flyback converter.

Figure 53. Basic Flyback Converter Schematic

During the on-time of the MOSFET, the bulk voltage  $V_{bulk}$  is applied to the magnetizing and leakage inductors  $L_p$  and  $L_{leak}$  and the current ramps up.

When the MOSFET is turned–off, the inductor current first charges  $C_{lump}$ . The output diode is off until the voltage across  $L_p$  reverses and reaches:

$$N_{sp}(V_{out} + V_f)$$

(eq. 1)

The output diode current increase is limited by the leakage inductor. As a consequence, the secondary peak current is reduced:

$$I_{D,pk} < \frac{I_{L,pk}}{N_{sp}} \tag{eq. 2}$$

The diode current reaches its peak when the leakage inductor is reset. Thus, in order to accurately regulate the output current, we need to take into account the leakage inductor current. This is accomplished by sensing the clamping network current. Practically, a node of the clamp capacitor is connected to  $R_{sense}$  instead of the bulk voltage  $V_{bulk}$ . Then, by reading the voltage on the CS pin, we have an image of the primary current (red curve in Figure 54). When the diode conducts, the secondary current decreases linearly from  $I_{D,pk}$  to zero. When the diode current has turned off, the drain voltage begins to oscillate because of the resonating network formed by the inductors ( $L_p+L_{leak}$ ) and the lump capacitor. This voltage is reflected on the auxiliary winding wired in flyback mode. Thus, by looking at the auxiliary winding voltage, we can detect the end of the conduction time of secondary diode. The constant current control block picks up the leakage inductor current, the end of conduction of the output rectifier and controls the drain current to maintain the output current constant.

We have:

$$I_{out} = \frac{V_{REF}}{2N_{sp}R_{sense}}$$

(eq. 3)

The output current value is set by choosing the sense resistor:

$$R_{sense} = \frac{V_{ref}}{2N_{sp}I_{out}} \qquad (eq. 4)$$

From Equation 3, the first key point is that the output current is independent of the inductor value. Moreover, the leakage inductance does not influence the output current value as the reset time is taken into account by the controller.

Figure 54. Flyback Currents and Auxiliary Winding Voltage in DCM

#### Internal Soft-Start

At startup or after recovering from a fault, there is a small internal soft–start of 40  $\mu s.$

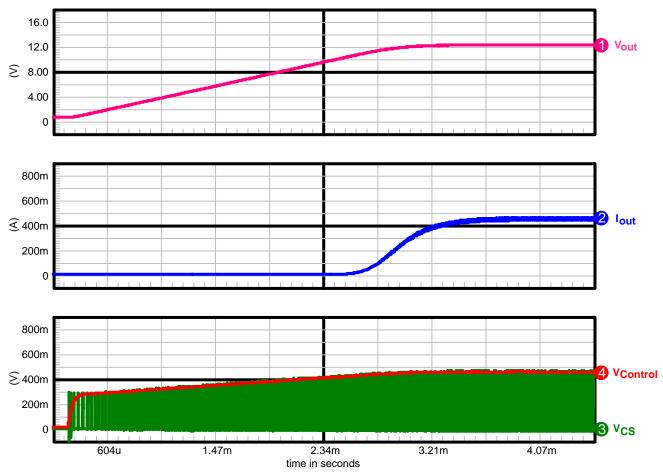

In addition, during startup, as the output voltage is zero volts, the demagnetization time is long and the constant

current control block will slowly increase the peak current towards its nominal value as the output voltage grows. Figure 55 shows a soft–start simulation example for a 9 W LED power supply.

Figure 55. Startup Simulation Showing the Natural Soft-start

#### Cycle-by-Cycle Current Limit

When the current sense voltage exceeds the internal threshold  $V_{ILIM}$ , the MOSFET is turned off for the rest of the switching cycle (Figure 56).

#### Winding and Output Diode Short-Circuit Protection

In parallel with the cycle–by–cycle sensing of the CS pin, another comparator with a reduced LEB ( $t_{BCS}$ ) and a higher threshold (1.5 V typical) is able to sense winding short–circuit and immediately stops the DRV pulses. The controller goes into auto–recovery mode in version B.

In version A, the controller is latched. In latch mode, the DRV pulses stop and VCC ramps up and down. The circuit un–latches when VCC pin voltage drops below  $V_{CC(reset)}$  threshold.

Figure 56. Winding Short Circuit Protection, Max. Peak Current Limit Circuits

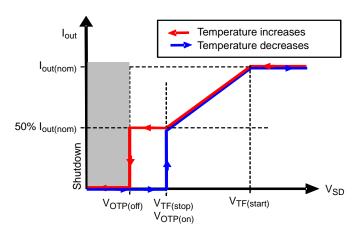

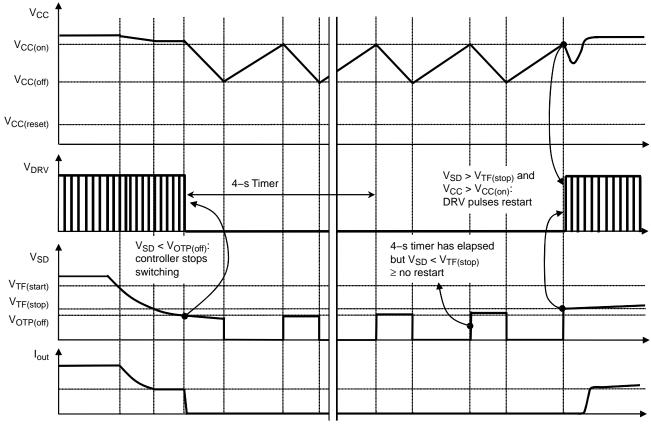

# Thermal Fold–back and Over Voltage / Over Temperature Protection

The thermal fold-back circuit reduces the current in the LED string when the ambient temperature exceeds a set point. The current is gradually reduced to 50% of its nominal value if the temperature continues to rise. (Figure 58). The thermal foldback starting temperature depends on the Negative Coefficient Temperature (NTC) resistor chosen by the power supply designer.

Indeed, the SD pin allows the direct connection of an NTC to sense the ambient temperature. When the SD pin voltage  $V_{SD}$  drops below  $V_{TF(start)}$ , the internal reference for the constant current control  $V_{REF}$  is decreased proportionally to  $V_{SD}$ . When  $V_{SD}$  reaches  $V_{TF(stop)}$ ,  $V_{REF}$  is clamped to  $V_{REF50}$ , corresponding to 50% of the nominal output current.

If  $V_{SD}$  drops below  $V_{OTP}$ , the controller enters into the auto-recovery fault mode for version B, meaning that the 4–s timer is activated. The controller will re–start switching after the 4–s timer has elapsed and when  $V_{SD} > V_{OTP(on)}$  to provide some temperature hysteresis (around 10°C).

For version A, this protection is latched: reset occurs when  $V_{CC} < V_{CC(reset)}$ .

The thermal fold–back and OTP thresholds correspond roughly to the following resistances:

- Thermal fold–back starts when  $R_{NTC} \leq 11.76 \text{ k}\Omega$ .

- Thermal fold–back stops when  $R_{NTC} \le 8.24 \text{ k}\Omega$ .

- OTP triggers when  $R_{NTC} \le 5.88 \text{ k}\Omega$ .

- OTP is removed when  $R_{NTC} \ge 8.24 \text{ k}\Omega$ .

Figure 57. Output Current Reduction versus SD Pin Voltage

At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller is not allowed to start pulsing for at least 180 µs in order to allow the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin. This is to avoid flickering of the LED light in case of over temperature.

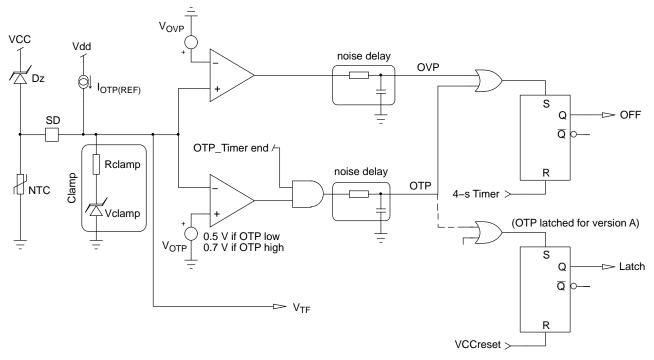

Figure 58. Thermal Fold-back and OVP/OTP Circuitry

In case of over voltage, the Zener diode starts to conduct and inject current inside the internal clamp resistor  $\mathsf{R}_{\mathsf{clamp}}$  thus causing the pin SD voltage to increase. When this

voltage reaches the OVP threshold (2.5 V typ.), the controller shuts–down and waits for at least 4 seconds before restarting switching.

Figure 59. OVP with SD Pin Chronograms

Figure 60. Thermal Fold-back / OTP Chronograms

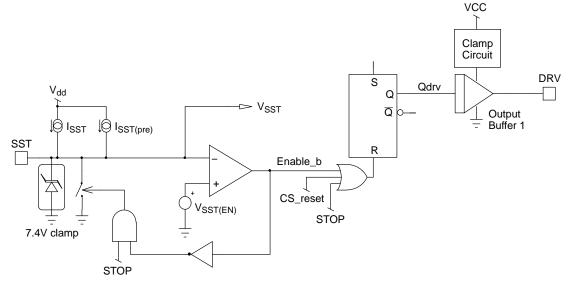

#### Soft-Start

The NCL30083 provides a soft–start pin allowing increasing slowly the LEDs light at startup. An internal current source  $I_{SST}$  charges the soft–start capacitor. The generated voltage ramp directly controls the amount of current flowing in the LEDs.

At startup, if there are no faults (except "Enable\_b" high), an internal pre-charging current source  $I_{SST(pre)}$  connected

in parallel with  $I_{SST}$  charges the soft–start capacitor until it reaches the  $V_{SST(EN)}$  threshold. After that,  $I_{SST(pre)}$  is turned off and the soft–start capacitor keep on charging with the soft–start current source  $I_{SST}$ .

When a fault is detected, the soft–start pin is discharged down to  $V_{SST(EN)}$  to provide a clean soft–start when the fault is removed.

Figure 61. Soft-start Pin Bloc Diagram

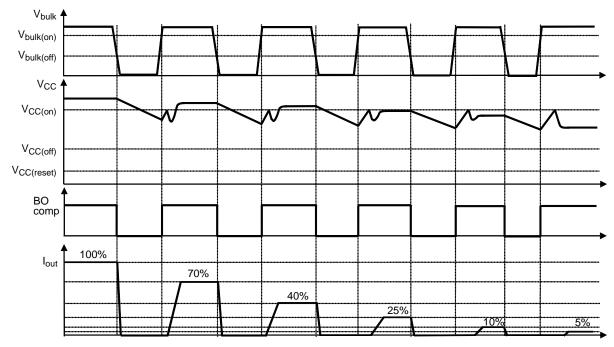

#### **Step Dimming**

The step dimming function decreases the output current from 100% to 5% of its nominal value in discrete steps. There are 5 steps in total. Table 4 shows the different steps value and the corresponding output current set–point. Each time a brown–out is detected, the output current is decreased by decreasing the reference voltage  $V_{REF}$  setting the output current value.

When the 5% dimming step is reached, if a brown–out event occurs, the controller restarts at 100% of the output current.

| Table 4. | DIMMING | STEPS |

|----------|---------|-------|

|----------|---------|-------|

| Dimming Step | l <sub>out</sub> | Perceived Light |  |  |  |

|--------------|------------------|-----------------|--|--|--|

| ON           | 100%             | 100%            |  |  |  |

| 1            | 70%              | 84%             |  |  |  |

| 2            | 40%              | 63%             |  |  |  |

| 3            | 25%              | 50%             |  |  |  |

| 4            | 10%              | 32%             |  |  |  |

| 5            | 5%               | 17%             |  |  |  |

Note:

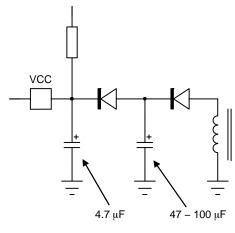

The power supply designer must ensure that  $V_{CC}$  stays high enough when the light is turned–off to let the controller memorize the dimming step state.

The power supply designer should use a split  $V_{CC}$  circuit for step dimming with a capacitor allowing providing enough  $V_{CC}$  for 1 s (47  $\mu F$  to 100  $\mu F$  capacitor).

The step dimming state is memorized by the controller until  $V_{CC}$  crosses  $V_{CC(reset)}$ .

Figure 62. Split VCC Supply

Figure 63. Step Dimming Chronograms

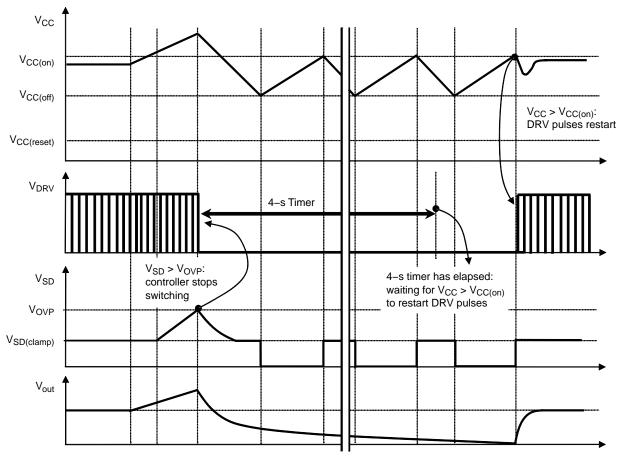

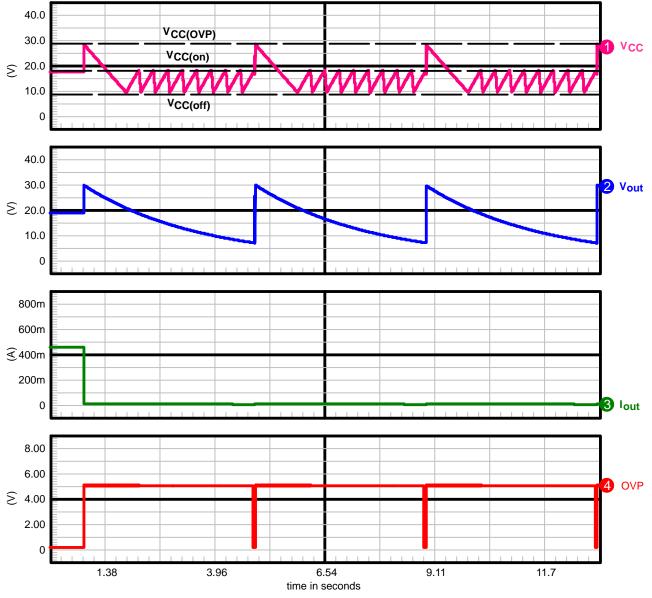

#### V<sub>CC</sub> Over Voltage Protection (Open LED Protection)

If no output load is connected to the LED power supply, the controller must be able to safely limit the output voltage excursion. In the NCL30083, when the V<sub>CC</sub> voltage reaches the V<sub>CC(OVP)</sub> threshold, the controller stops the DRV pulses and the 4–s timer starts counting. The IC re–start pulsing after the 4–s timer has elapsed and when V<sub>CC</sub>  $\geq$  V<sub>CC(on)</sub>.

Figure 64. Open LED Protection Chronograms

#### Valley Lockout

Quasi-Square wave resonant systems have a wide switching frequency excursion. The switching frequency increases when the output load decreases or when the input voltage increases. The switching frequency of such systems must be limited.

The NCL30083 changes valley as the input voltage increases and as the output current set-point is varied (thermal fold-back and step dimming). This limits the switching frequency excursion. Once a valley is selected, the controller stays locked in the valley until the input voltage or the output current set-point varies significantly. This avoids valley jumping and the inherent noise caused by this phenomenon.

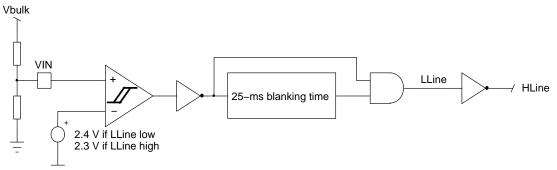

The input voltage is sensed by the VIN pin. The internal logic selects the operating valley according to VIN pin voltage (line range detector in Figure 65), SD pin voltage and dimming state imposed by the Step Dimming circuit.

By default, when the output current is not dimmed, the controller operates in the first valley at low line and in the second valley at high line.

## Figure 65. Line Range Detector

### Table 5. VALLEY SELECTION

|                                                                                                   |            |                            | VIN pin v                          | oltage for valle                    | y change                                                                                          |     |            |                            |

|---------------------------------------------------------------------------------------------------|------------|----------------------------|------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------|-----|------------|----------------------------|

| I <sub>out</sub> value at which the<br>controller changes valley<br>(I <sub>out</sub> decreasing) |            | V <sub>VIN</sub> decreases |                                    |                                     | I <sub>out</sub> value at which the<br>controller changes valley<br>(I <sub>out</sub> increasing) |     |            |                            |

|                                                                                                   |            | 0                          | -LL-                               | 2.3 V                               | -HL-                                                                                              | 5 V |            |                            |

|                                                                                                   | 100%       |                            | 1 <sup>st</sup>                    |                                     | 2 <sup>nd</sup>                                                                                   |     | 100%       |                            |

| ses                                                                                               | 75%<br>50% |                            | 2 <sup>nd</sup>                    |                                     | 3 <sup>rd</sup>                                                                                   |     | 78%<br>53% | out                        |

| l <sub>out</sub> decreases                                                                        | 30%        |                            | 4 <sup>th</sup><br>7 <sup>th</sup> |                                     | 5 <sup>th</sup><br>8 <sup>th</sup>                                                                |     | 33%        | l <sub>out</sub> increases |

| lout                                                                                              | 15%<br>6%  |                            | 11 <sup>th</sup>                   |                                     | 12 <sup>th</sup>                                                                                  |     | 20%<br>8%  | Ses                        |

|                                                                                                   | 0%         |                            | 13 <sup>th</sup>                   |                                     | 15 <sup>th</sup>                                                                                  |     | 0%         |                            |

|                                                                                                   |            | 0                          | -LL-                               | 2.4 V<br>V <sub>VIN</sub> increases | -HL-                                                                                              | 5 V |            |                            |

|                                                                                                   |            |                            | VIN pin v                          | oltage for valle                    | y change                                                                                          |     |            |                            |

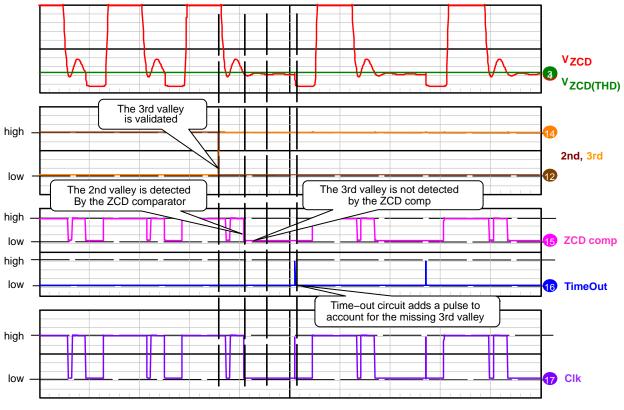

#### Zero Crossing Detection Block

The ZCD pin allows detecting when the drain-source voltage of the power MOSFET reaches a valley.

A valley is detected when the voltage on pin 1 crosses below the  $V_{ZCD(THD)}$  internal threshold.

At startup or in case of extremely damped free oscillations, the ZCD comparator may not be able to detect

the valleys. To avoid such a situation, the NCL30083 features a Time–Out circuit that generates pulses if the voltage on ZCD pin stays below the  $V_{ZCD(THD)}$  threshold for 6.5 µs.

The Time–out also acts as a substitute clock for the valley detection and simulates a missing valley in case of too damped free oscillations.

Figure 66. Time-out Chronograms

Because of this time-out function, if the ZCD pin or the auxiliary winding is shorted, the controller will continue switching leading to improper regulation of the LED current. Moreover during an output short circuit, the controller will strive to maintain the constant current operation.

In order to avoid these scenarios, a secondary timer starts counting when the ZCD voltage is below the  $V_{ZCD(short)}$  threshold. If this timer reaches 90 ms, the controller detects a fault and enters the auto-recovery fault mode (controller shuts-down and waits 4–s before re–starting switching).

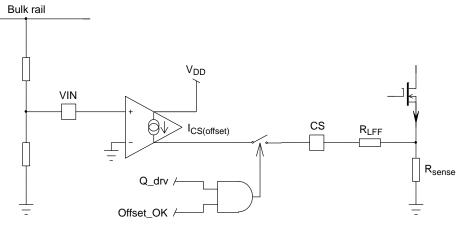

#### Line Feed-forward

Because of the propagation delays, the MOSFET is not turned–off immediately when the current set–point is reached. As a result, the primary peak current is higher than expected and the output current increases. To compensate the peak current increase brought by the propagation delay, a positive voltage proportional to the line voltage is added on the current sense signal. The amount of offset voltage can be adjusted using the R<sub>LFF</sub> resistor as shown in Figure 67.

The offset voltage is applied only during the MOSFET on-time.

This offset voltage is removed at light load during dimming when the output current drops below 15% of the programmed output current.

Figure 67. Line Feed–Forward Schematic

#### Brown-out

In order to protect the supply against a very low input voltage, the NCL30083 features a brown–out circuit with a fixed ON/OFF threshold. The controller is allowed to start if a voltage higher than 1 V is applied to the VIN pin and shuts-down if the VIN pin voltage decreases and stays below 0.9 V for 50 ms nominal. Exiting a brown-out condition overrides the hiccup on V<sub>CC</sub> (V<sub>CC</sub> does not wait to reach V<sub>CC(off)</sub>) and the IC immediately goes into startup mode (I<sub>CC</sub> = I<sub>CC(start)</sub>).

Figure 69. Brown–Out Chronograms (Valley Fill circuit is used)

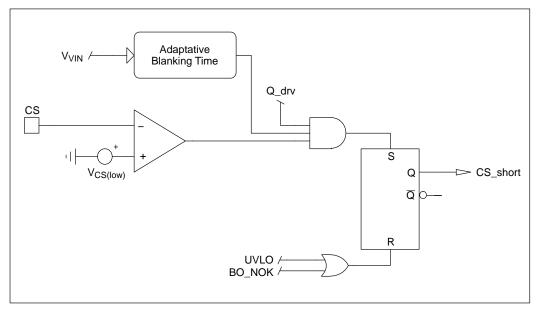

### **CS Pin Short Circuit Protection**

Normally, if the CS pin or the sense resistor is shorted to ground, the Driver will not be able to turn off, leading to potential damage of the power supply. To avoid this, the NCL30083 features a circuit to protect the power supply against a short circuit of the CS pin. When the MOSFET is on, if the CS voltage stays below  $V_{CS(low)}$  after the adaptive blanking timer has elapsed, the controller shuts down and will attempt to restart on the next  $V_{CC}$  hiccup.

Figure 70. CS Pin Short Circuit Protection Schematic

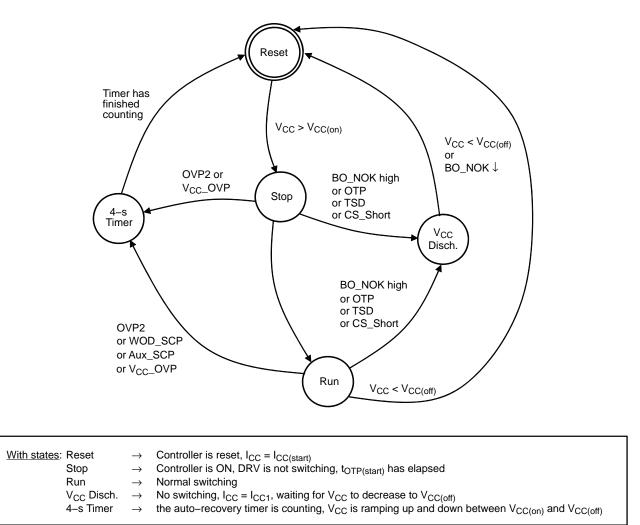

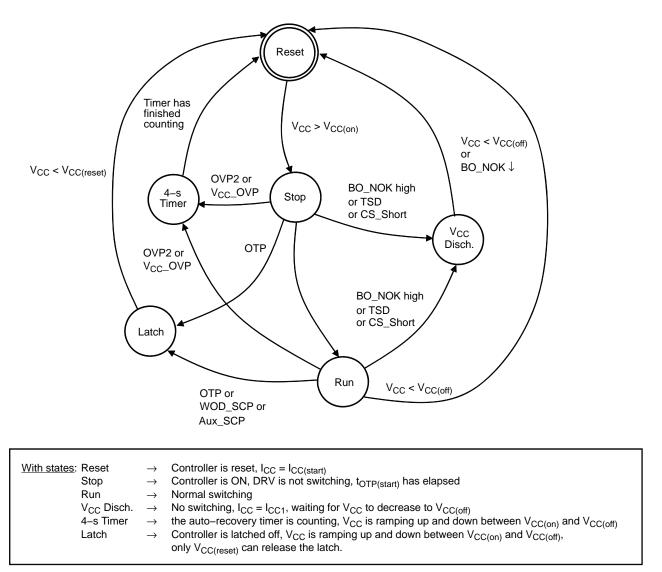

#### Fault Management

OFF Mode

The circuit turns off whenever a major condition prevents it from operating:

- Incorrect feeding of the circuit: "UVLO high". The UVLO signal becomes high when V<sub>CC</sub> drops below V<sub>CC(off)</sub> and remains high until V<sub>CC</sub> exceeds V<sub>CC(on)</sub>.

- OTP

- V<sub>CC</sub> OVP

- OVP2 (additional OVP provided by SD pin)

- Output diode short circuit protection: "WOD\_SCP high"

- Output / Auxiliary winding Short circuit protection: "Aux\_SCP high"

- Die over temperature (TSD)

- Brown–Out: "BO\_NOK" high

- Pin CS short circuited to GND: "CS\_short high"

In this mode, the DRV pulses are stopped. The VCC voltage decrease through the controller own consumption  $(I_{CC1})$ .

For the output diode short circuit protection, the CS pin short circuit protection, the output / aux. winding short circuit protection and the OVP2, the controller waits 4 seconds (auto-recovery timer) and then initiates a startup sequence ( $V_{CC} \ge V_{CC(on)}$ ) before re-starting switching.

#### Latch Mode

This mode is activated by the output diode short–circuit protection (WOD\_SCP), the OTP and the Aux–SCP in **version A only.**

In this mode, the DRV pulses are stopped and the controller is latched. There are hiccups on  $V_{CC}. \label{eq:VCC}$

The circuit un–latches when  $V_{CC} < V_{CC(reset)}$ .

Figure 71. State Diagram for B Version Faults

Figure 72. State Diagram for A Version Faults

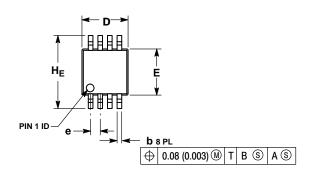

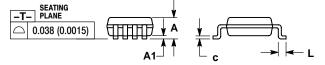

### PACKAGE DIMENSIONS

Micro8<sup>™</sup> CASE 846A-02 **ISSUE J**

NOTES:

- I. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (1000) EDR DIRO

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

846A-01 OBSOLETE, NEW STANDARD 846A-02.

|     | MILLIMETERS |      |      | INCHES    |       |       |

|-----|-------------|------|------|-----------|-------|-------|

| DIM | MIN         | NOM  | MAX  | MIN       | NOM   | MAX   |

| Α   |             |      | 1.10 |           |       | 0.043 |

| A1  | 0.05        | 0.08 | 0.15 | 0.002     | 0.003 | 0.006 |

| b   | 0.25        | 0.33 | 0.40 | 0.010     | 0.013 | 0.016 |

| c   | 0.13        | 0.18 | 0.23 | 0.005     | 0.007 | 0.009 |

| D   | 2.90        | 3.00 | 3.10 | 0.114     | 0.118 | 0.122 |

| Е   | 2.90        | 3.00 | 3.10 | 0.114     | 0.118 | 0.122 |

| e   | 0.65 BSC    |      |      | 0.026 BSC |       |       |

| L   | 0.40        | 0.55 | 0.70 | 0.016     | 0.021 | 0.028 |

| HE  | 4.75        | 4.90 | 5.05 | 0.187     | 0.193 | 0.199 |

RECOMMENDED **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

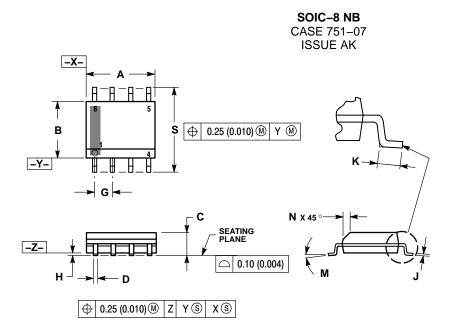

### PACKAGE DIMENSIONS

NOTES:

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |  |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |  |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |  |

| G   | 1.27 BSC    |      | 0.050 BSC |       |  |

| н   | 0.10        | 0.25 | 0.004     | 0.010 |  |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |  |

| к   | 0.40        | 1.27 | 0.016     | 0.050 |  |

| м   | 0 °         | 8 °  | 0 °       | 8 °   |  |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |  |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |  |

#### **SOLDERING FOOTPRINT\***

#### **OPTIONS**

| Controller | Output SCP    | Winding/Output Diode SCP | Over Temperature Protection |

|------------|---------------|--------------------------|-----------------------------|

| NCL30083A  | Latched       | Latched                  | Latched                     |

| NCL30083B  | Auto-recovery | Auto-recovery            | Auto-recovery               |

#### **ORDERING INFORMATION**

| Device         | Package Marking | Package Type                     | Shipping <sup>†</sup> |

|----------------|-----------------|----------------------------------|-----------------------|

| NCL30083ADMR2G | AAE             | Micro8<br>(Pb–Free, Halide–Free) | 4000 / Tape & Reel    |

| NCL30083BDMR2G | AAF             | Micro8<br>(Pb–Free, Halide–Free) | 4000 / Tape & Reel    |

| NCL30083BDR2G  | L30083B         | SOIC-8<br>(Pb-Free)              | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

ON Semiconductor and a registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product sherein, soft and social application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, or the part. SCILLC and the specificatious use, even if such claim alleges that SCILLC was negligent regarding the desi

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

## Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9