#### MAX14746/MAX14747

# USB Detection with Smart Power Selector Li+ Chargers

#### **General Description**

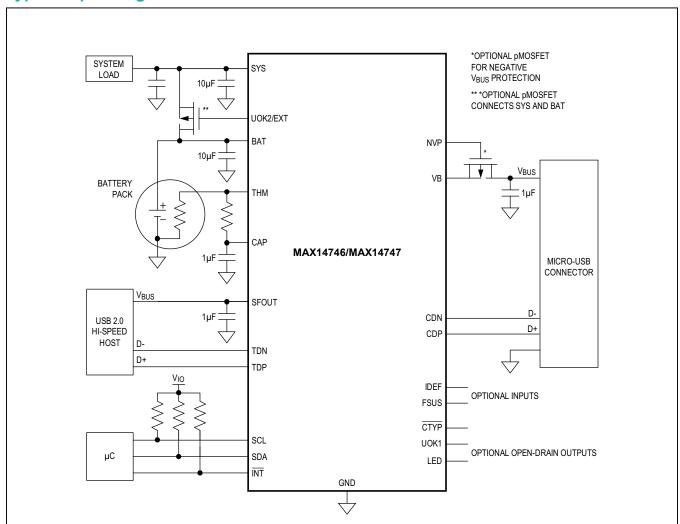

The MAX14746/MAX14747 are a series of USB charger detectors with an integrated Smart Power Selector™ linear charger solutions that provide a single-chip solution for charging and charger detection.

The MAX14746/MAX14747 charger detectors are compliant to USB Battery Charger Detection Rev 1.2\* and capable of detecting multiple USB battery-charging methods, including Standard Downstream Ports (SDP), Charging Downstream Ports (CDP), and Dedicated Charger Ports (DCP). The devices also detect common proprietary charge adapters, including those from Apple.

The MAX14746/MAX14747 battery chargers feature Smart Power Selector operation, allowing operation with dead or no battery present. The devices limit USB  $V_{BUS}$  current based on the detect charger source type. If the charger power source is unable to supply the entire system load, the smart-power control circuit supplements the system load with current from the battery.

The devices protect against overvoltage faults up to 28V.

This series of USB charger detectors are available with several options, with slight variations in, for example, power-up states. These variations are noted throughout this data sheet.

There are five options available, with slight variations in, for example, power-up states (see Ordering Information). The devices are available in a 25-ball, 0.4mm pitch wafer-level package (WLP), and are specified over the -40°C to +85°C extended temperature range.

#### **Applications**

- Portable Consumer Devices

- Portable Digital Cameras

- Portable Digital Video Cameras

- Portable Industrial Devices

\*Except DCD timeout extended from 900ms to 2s for the MAX14746/MAX14747.

Smart Power Selector  $^{\text{TM}}$  is a trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- Flexible System Design to Operate with Any USB Charger Source

- Compliant to USB Battery Charger Rev 1.2 Specification\*

- Supports Proprietary USB Charging Sources, Including Apple

- · D+/D- Bias Voltage Supported

- Easy to Implement Li+ Battery Charging

- · Smart Power Selector

- Fully Compliant with Dead Battery/Weak Battery Charging According to USB 2.0 Specification

- JEITA Charge Protection

- · Thermal Protection

- Internal USB D+/D- Switch to Manage Connection

- Integrates High Level of Protection

- 28V Tolerant Input on VB

- ±15kV Human Body Model ESD Protection on CDP and CDN

Ordering Information appears at end of data sheet.

#### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                     |

|-------------------------------------------------------|

| BAT, INT, THM, LED, UOK1, CTYP, IDEF, FSUS,           |

| TDN, TDP, CDN, CDP, SYS, SCL, SDA0.3V to +6V          |

| UOK2/EXTV <sub>SYS</sub> + 0.3V                       |

| SFOUT, CAP0.3V to min ((V <sub>VB</sub> + 0.3V), +6V) |

| VB0.3V to +30V                                        |

| NVP0.3V to (V <sub>VB</sub> + 0.3V)                   |

| Continuous Current into VB, BAT, SYS±3A               |

| Continuous Current into any Other Terminal            | ±100mA          |

|-------------------------------------------------------|-----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| WLP (derate 19.2mW/°C above +70°C)                    | 1536mW          |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -65°C to +150°C |

| Reflow Temperature                                    | +260°C          |

## **Package Thermal Characteristics (Note 1)**

$\mathsf{WLP}$

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) ........52°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                   | SYMBOL                 | CONDITIONS                                                                                       | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| SUPPLY CHARACTERISTICS                      |                        |                                                                                                  |     |      |     |       |

| VB Input Voltage Range                      | V <sub>VB</sub>        |                                                                                                  | 0   |      | 28  | V     |

| V <sub>BAT</sub> Input Voltage Range        | V <sub>BAT</sub>       |                                                                                                  | 0   |      | 5.5 | V     |

| VB Detection Threshold                      | V                      | V <sub>VB</sub> rising                                                                           | 3.8 | 3.9  | 4.1 | V     |

| VB Detection Threshold                      | V <sub>VBDET</sub>     | V <sub>VB</sub> falling                                                                          | 3.0 | 3.1  | 3.2 | V     |

| VB Overvoltage Threshold                    | V <sub>VBOV</sub>      | V <sub>VB</sub> rising                                                                           | 7.2 | 7.5  | 7.8 | V     |

| VB Overvoltage Hysteresis                   | V <sub>VBOV_HYS</sub>  |                                                                                                  |     | 200  |     | mV    |

| VB Valid Trip Point                         | V <sub>VB_TRIP</sub>   |                                                                                                  | 30  | 145  | 290 | mV    |

| VB Valid Trip Point Hysteresis              | V <sub>VB_TP_HYS</sub> |                                                                                                  |     | 275  |     | mV    |

| VB Charger-Detection-Active Supply Current  | I <sub>B_CDETON</sub>  | V <sub>BAT</sub> = 0V, I <sub>SYS</sub> = 0mA<br>charger detection active, analog switch open    |     |      | 2.5 | mA    |

| VB Charger-Detection-Idle<br>Supply Current | IB_CDCIDLE             | V <sub>BAT</sub> = 0V, I <sub>SYS</sub> = 0mA<br>charger detection idle,<br>analog switch closed |     |      | 2   | mA    |

| V <sub>CCINT</sub> UVLO Threshold           | V <sub>UVLO</sub>      | V <sub>CCINT</sub> rising (Note 3)                                                               | 1.6 | 2.2  | 2.6 | V     |

| V <sub>CCINT</sub> UVLO Hysteresis          | V <sub>UVLO_HYS</sub>  | (Note 3)                                                                                         |     | 50   |     | mV    |

| BAT Overvoltage Threshold                   | V <sub>BATOV</sub>     | V <sub>BAT</sub> rising, VB not connected                                                        | 4.8 | 5.15 | 5.7 | V     |

| BAT Overvoltage Hysteresis                  | V <sub>BATOV_HYS</sub> |                                                                                                  |     | 100  |     | mV    |

| BAT UVLO Threshold                          | V <sub>BAT_UVLO</sub>  | V <sub>BAT</sub> rising (Note 4)                                                                 | 1.9 | 2.05 | 2.2 | V     |

| BAT UVLO Hysteresis                         | V <sub>BAT_UVLOH</sub> |                                                                                                  |     | 50   |     | mV    |

## **Electrical Characteristics (continued)**

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                            | SYMBOL                 | CONI                                       | DITIONS                      | MIN                                            | TYP                                         | MAX                                            | UNITS |

|--------------------------------------|------------------------|--------------------------------------------|------------------------------|------------------------------------------------|---------------------------------------------|------------------------------------------------|-------|

| BAT Supply Current With VB           | I <sub>BAT_NOCHG</sub> | V <sub>BAT</sub> = 4.2V, VB co             | onnected,                    |                                                | 4                                           | 8                                              | μА    |

| BAT Supply Current No VB             | I <sub>BAT_NOVB</sub>  | V <sub>BAT</sub> = 4.2V, VB no             | ot connected                 |                                                | 6                                           | 11                                             | μA    |

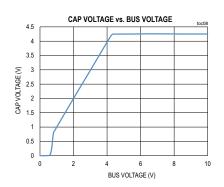

| CAP Regulator Voltage                | V <sub>CAP</sub>       | V <sub>VB</sub> = 5V                       |                              | 3.9                                            | 4.2                                         | 4.7                                            | V     |

| 050117.0                             | .,                     | V <sub>VB</sub> = 6.0V, I <sub>SFOU</sub>  | <sub>T</sub> = 0mA           | 5.0                                            | 5.25                                        | 5.5                                            | .,    |

| SFOUT Regulator Voltage              | V <sub>SFOUT</sub>     | V <sub>VB</sub> = 5.0V, I <sub>SFOU</sub>  | <sub>T</sub> = 15mA          |                                                | 4.9                                         |                                                | V     |

| SFOUT Overvoltage Protection Voltage | V <sub>SFOUT_OVP</sub> | (Note 5)                                   |                              |                                                | 17                                          |                                                | V     |

| NVP Clamp Voltage                    | V <sub>NVP</sub>       | Measured between V <sub>VB</sub> > 10V     | VB and NVP,                  | 5                                              | 7                                           | 10                                             | V     |

| NVP Resistance                       | R <sub>NVP</sub>       | V <sub>VB</sub> < 5V                       |                              | 120                                            | 200                                         | 300                                            | Ω     |

| THERMAL PROTECTION                   |                        |                                            |                              |                                                |                                             |                                                |       |

| Thermal Shutdown Threshold           | T <sub>SHDN_LIM</sub>  | (Note 6)                                   |                              |                                                | 150                                         |                                                | °C    |

| Current Reduce Thermal Threshold     | T <sub>CHG_LIM</sub>   | (Note 7)                                   |                              |                                                | 120                                         |                                                | °C    |

| VB-TO-SYS PATH                       |                        |                                            |                              |                                                |                                             |                                                |       |

| SYS Regulation Voltage               | V <sub>SYS_REG</sub>   | I <sub>SYS</sub> = 5mA                     | MAX14746                     | V <sub>BAT</sub> _<br>REG <sup>+</sup><br>0.14 | V <sub>BAT</sub><br>REG <sup>+</sup><br>0.2 | V <sub>BAT</sub> _<br>REG <sup>+</sup><br>0.26 | V     |

|                                      |                        |                                            | MAX14747                     |                                                | 4.8                                         |                                                |       |

| VB-to-SYS Voltage Drop               | V <sub>VB_SYS</sub>    |                                            |                              |                                                | 40                                          |                                                | mV    |

| VB-to-SYS On-Resistance              | R <sub>VB_SYS</sub>    | V <sub>VB</sub> = 4.4V, I <sub>SYS</sub> = | 400mA                        |                                                | 160                                         | 350                                            | mΩ    |

| Soft-Start Input Current Time        | tss_vb_sys             |                                            |                              |                                                | 1                                           |                                                | ms    |

|                                      |                        | FSUS = 1                                   |                              |                                                | 0                                           |                                                |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 000 |                                                | 96.5                                        |                                                |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 001 |                                                | 475                                         | 500                                            |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 010 |                                                | 633                                         |                                                |       |

| USB Input Current Limit              | I <sub>LIMIT</sub>     | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 011 |                                                | 737                                         |                                                | mA    |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 100 |                                                | 944                                         |                                                |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 101 |                                                | 1048                                        |                                                |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 110 |                                                | 1570                                        |                                                |       |

|                                      |                        | IDEF = 0, IBusLim<br>= 11, ILimSet[2:0] =  | = 1, IBusDetSw[1:0]<br>= 111 |                                                | 1885                                        |                                                | -     |

## **Electrical Characteristics (continued)**

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                                | SYMBOL                    | CONDITIONS                                              | MIN  | TYP                    | MAX  | UNITS |

|------------------------------------------|---------------------------|---------------------------------------------------------|------|------------------------|------|-------|

| CHARGER PATH                             |                           |                                                         |      |                        |      |       |

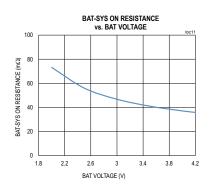

| BAT to SYS On-Resistance                 | D                         | V <sub>BAT</sub> = 5V, I <sub>BAT</sub> = 400mA         |      | 40                     | 80   | mΩ    |

| DAT to 313 Off-Nesistance                | R <sub>BAT_SYS</sub>      | V <sub>BAT</sub> = 1.9V, I <sub>BAT</sub> = 100mA       |      | 83                     |      | 11152 |

| BAT to SYS Switch-On<br>Threshold        | V <sub>BAT_SYS_ON</sub>   | V <sub>SYS</sub> falling                                | 10   | 22                     | 35   | mV    |

| BAT to SYS Switch-Off<br>Threshold       | V <sub>BAT_SYS_OFF</sub>  | V <sub>SYS</sub> rising                                 | -3   | -1.5                   | 0    | mV    |

|                                          |                           | SysMin[2:0] = 000, V <sub>BAT</sub> > 3.6V              |      | V <sub>BAT</sub> + 0.1 |      |       |

|                                          |                           | SysMin[2:0] = 000, V <sub>BAT</sub> < 3.4V              |      | 3.6                    |      |       |

|                                          |                           | SysMin[2:0] = 001, V <sub>BAT</sub> < 3.4V              |      | 3.7                    |      |       |

| SYS Charger Current-                     | .,                        | SysMin[2:0] = 010, V <sub>BAT</sub> < 3.4V              |      | 3.8                    |      |       |

| Limiting Threshold Voltage               | V <sub>SYS_LIM</sub>      | SysMin[2:0] = 011, V <sub>BAT</sub> < 3.4V              |      | 3.9                    |      |       |

|                                          |                           | SysMin[2:0] =100, V <sub>BAT</sub> < 3.4V               | 3.86 | 4                      | 4.14 |       |

|                                          |                           | SysMin[2:0] =101, V <sub>BAT</sub> < 3.4V               |      | 4.1                    |      |       |

|                                          |                           | SysMin[2:0] =110, V <sub>BAT</sub> < 3.4V               |      | 4.2                    |      |       |

|                                          |                           | SysMin[2:0] =111, V <sub>BAT</sub> < 3.4V               |      | 4.3                    |      |       |

| Charger Current Soft-Start Time          |                           |                                                         |      | 1                      |      | ms    |

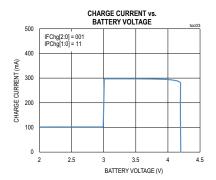

| BATTERY CHARGER LEVELS                   |                           |                                                         |      |                        |      |       |

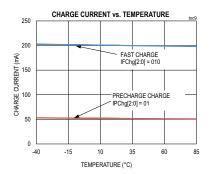

|                                          |                           | IPChg[1:0] = 00                                         |      | 30                     |      |       |

| Precharge Current                        | I <sub>PCHG</sub>         | IPChg[1:0] = 01                                         |      | 50                     |      | mA    |

| <b>3</b>                                 | 1 0110                    | IPChg[1:0] = 10                                         |      | 70                     |      | _     |

|                                          |                           | PChg[1:0] = 11                                          |      | 100                    |      |       |

|                                          |                           | VPChg = 0, VPChgLow[1:0] = 00, V <sub>BAT</sub> rising  |      | 2.15                   |      | _     |

|                                          |                           | VPChg = 0, VPChgLow[1:0] = 01, V <sub>BAT</sub> rising  | 2.15 | 2.25                   | 2.35 |       |

|                                          |                           | VPChg = 0, VPChgLow[1:0] = 10, V <sub>BAT</sub> rising  |      | 2.35                   |      |       |

| Prequalification Threshold               | V <sub>BAT_PCHG</sub>     | VPChg = 0, VPChgLow[1:0] = 11, V <sub>BAT</sub> rising  |      | 2.45                   |      | V     |

| 1. Toqualiloudion Tilloonolu             | *BAI_PCHG                 | VPChg = 1, VPChgHigh[1:0] = 00, V <sub>BAT</sub> rising |      | 2.7                    |      |       |

|                                          |                           | VPChg = 1, VPChgHigh[1:0] = 01, V <sub>BAT</sub> rising | 2.70 | 2.80                   | 2.90 | 1     |

|                                          |                           | VPChg = 1, VPChgHigh[1:0] = 10, V <sub>BAT</sub> rising |      | 2.9                    |      |       |

|                                          |                           | VPChg = 1, VPChgHigh[1:0] = 11, V <sub>BAT</sub> rising |      | 3                      |      | 1     |

| Prequalification Threshold<br>Hysteresis | V <sub>BAT_PCHG_HYS</sub> |                                                         |      | 100                    |      | mV    |

## **Electrical Characteristics (continued)**

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                 | SYMBOL                | CONI                                                 | DITIONS              | MIN         | TYP  | MAX   | UNITS |  |

|---------------------------|-----------------------|------------------------------------------------------|----------------------|-------------|------|-------|-------|--|

|                           |                       | IFChg[2:0] = 000                                     |                      |             | 700  |       |       |  |

|                           |                       | IFChg[2:0] = 001 300                                 |                      |             |      | 1     |       |  |

|                           |                       | IFChg[2:0] = 010                                     |                      | 180         | 200  | 220   |       |  |

| BAT Charge Current Set    |                       | IFChg[2:0] = 011                                     |                      |             | 600  |       |       |  |

| Range                     | IFCHG                 | IFChg[2:0] = 100                                     |                      |             | 800  |       | mA    |  |

|                           |                       | IFChg[2:0] = 101                                     |                      |             | 900  |       | 1     |  |

|                           |                       | IFChg[2:0] = 110                                     |                      |             | 350  |       |       |  |

|                           |                       | IFChg[2:0] = 111                                     |                      |             | 450  |       |       |  |

|                           |                       | ChgDone[2:0] = 00                                    | 0                    |             | 10   |       |       |  |

|                           |                       | ChgDone[2:0] = 00                                    | 1                    |             | 20   |       |       |  |

|                           |                       | ChgDone[2:0] =                                       |                      |             | 40   |       |       |  |

|                           |                       | 010                                                  | TA = 0°C to +60°C    | 30          |      | 50    |       |  |

| Charge Done Qualification | I <sub>CHG_DONE</sub> | ChgDone[2:0] = 01                                    | 1                    |             | 50   |       | mA    |  |

|                           |                       | ChgDone[2:0] = 100                                   |                      |             | 60   |       |       |  |

|                           |                       | ChgDone[2:0] = 101                                   |                      |             | 80   |       |       |  |

|                           |                       | ChgDone[2:0] = 11                                    | 0                    |             | 100  |       |       |  |

|                           |                       | ChgDone[2:0] = 11                                    | 1                    |             | 120  |       |       |  |

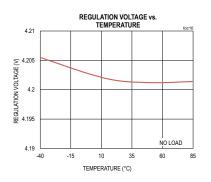

|                           |                       | BatRegSel = 0, Ba                                    | tRegLow[1:0] = "00"  |             | 4.05 |       |       |  |

|                           |                       | BatRegSel = 0, Ba                                    | tRegLow[1:0] = "01"  |             | 4.1  |       |       |  |

|                           |                       | BatRegSel = 0, Ba                                    | tRegLow[1:0] = "10"  |             | 4.15 |       |       |  |

|                           |                       | BatRegSel = 0, Bat<br>T <sub>A</sub> =+25°C          | tRegLow[1:0] = "11", | 4.179       | 4.2  | 4.221 |       |  |

|                           |                       | BatRegSel = 0, Bat<br>T <sub>A</sub> =-40°C to +85°C | tRegLow[1:0] = "11", | 4.158       | 4.2  | 4.242 |       |  |

| BAT Regulation Voltage    | V <sub>BAT_REG</sub>  | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "000"  |             | 4.25 |       | V     |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "001"  | = "001" 4.3 |      |       | 1     |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "010"  |             | 4.35 |       |       |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "011"  |             | 4.4  |       |       |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "100"  |             | 4.45 |       |       |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "101"  |             | 4.5  |       |       |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "110"  |             | 4.55 |       | 1     |  |

|                           |                       | BatRegSel = 1, Ba                                    | tRegHi[2:0] = "111"  |             | 4.6  |       |       |  |

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                                               | SYMBOL                  | CONDITIONS                                                                       | MIN TYP | MAX | UNITS              |

|---------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------|---------|-----|--------------------|

|                                                         |                         | BatReChg[1:0] = 00                                                               | 50      |     |                    |

| DAT Dashanna Thuashald                                  |                         | BatReChg[1:0] = 01                                                               | 100     |     |                    |

| BAT Recharge Threshold                                  | V <sub>BAT_RECHG</sub>  | BatReChg[1:0] = 10                                                               | 150     |     | mV                 |

|                                                         |                         | BatReChg[1:0] = 11                                                               | 200     |     |                    |

| BATTERY CHARGER TIMING                                  |                         |                                                                                  |         |     | •                  |

|                                                         |                         | PChgTmr[1:0] = 00                                                                | 30      |     |                    |

| Maximum Prequalification                                |                         | PChgTmr[1:0] = 01                                                                | 60      |     | Minutes            |

| Time                                                    | t <sub>PCHG</sub>       | PChgTmr[1:0] = 10                                                                | 120     |     | Minutes            |

|                                                         |                         | PChgTmr[1:0] = 11                                                                | 240     |     |                    |

|                                                         |                         | FChgTmr[1:0] = 00                                                                | 75      |     |                    |

| Mavimum Fast Charge Time                                |                         | FChgTmr[1:0] = 01                                                                | 150     |     | Minutes            |

| Maximum Fast-Charge Time                                | t <sub>FCHG</sub>       | FChgTmr[1:0] = 10                                                                | 300     |     | Minutes            |

|                                                         |                         | FChgTmr[1:0] = 11                                                                | 600     |     |                    |

|                                                         | tтоснg                  | MtChgTmr[1:0] = 00                                                               | 30      |     |                    |

| Maintain Channa Tina                                    |                         | MtChgTmr[1:0] = 01                                                               | 15      |     | Minutes            |

| Maintain-Charge Time                                    |                         | MtChgTmr[1:0] = 10                                                               | 0       |     | Minutes            |

|                                                         |                         | MtChgTmr[1:0] = 11                                                               | 60      |     |                    |

| Charge-Timer Accuracy                                   | osc                     |                                                                                  | -10     | +10 | %                  |

| Charge-Timer Extend<br>Threshold                        | IFC_HALF                | Charge current reduced due to overcurrent or overtemperature condition (Note 10) | 50      |     | %I <sub>FCHG</sub> |

| Charge-Timer Suspend<br>Threshold                       | I <sub>FC_FIFTH</sub>   | Charge current reduced due to overcurrent or overtemperature condition (Note 10) | 20      |     | %I <sub>FCHG</sub> |

| BATTERY DETECTION                                       |                         | ,                                                                                |         |     | - 1                |

|                                                         |                         | BatDetCntl = 0, V <sub>BAT</sub> > V <sub>BAT_UVLO</sub>                         | 61      |     | ms                 |

| V <sub>VB</sub> Rising to Battery Detection Valid Delay | t <sub>BUS_BATDET</sub> | BatDetCntl = 0, V <sub>BAT</sub> < V <sub>BAT_UVLO</sub>                         | 1.031   |     | s                  |

| tion valid Delay                                        | _                       | BatDetCntl = 1                                                                   | 46      |     | ms                 |

| V <sub>BAT</sub> Falling to BatDet                      |                         | BatDetCntl = 0                                                                   | 1.015   |     | s                  |

| Update Delay                                            | tBATDET_F               | BatDetCntl = 1                                                                   | 15      |     | ms                 |

|                                                         |                         | BatDetCntl = 0, V <sub>BAT</sub> > V <sub>BAT UVLO</sub>                         | 1.03    |     | _                  |

| V <sub>BAT</sub> Rising to BatDet                       | t <sub>BATDET_R</sub>   | BatDetCntl = 0, V <sub>BAT</sub> < V <sub>BAT_UVLO</sub>                         | 1.015   |     | s                  |

| Update Delay                                            | _                       | BatDetCntl = 1                                                                   | 15      |     | ms                 |

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                                 | SYMBOL               | CC                                      | ONDITIONS    | MIN | TYP   | MAX | UNITS             |

|-------------------------------------------|----------------------|-----------------------------------------|--------------|-----|-------|-----|-------------------|

| JEITA BATTERY PACK MONIT                  | OR AND NTC DE        | TECTION                                 |              | ·   |       |     |                   |

| THM Hot Threshold                         |                      | Vfalling                                | MAX14746     |     | 23.8  |     | 0/ \/             |

| THIN HOL THIESHOID                        | T <sub>4</sub>       | V <sub>THM</sub> falling                | MAX14747     |     | 19    |     | %V <sub>CAP</sub> |

| THM Warm Threshold                        | T <sub>3</sub>       | V <sub>THM</sub> falling                | MAX14746     |     | 33.7  |     | %V <sub>CAP</sub> |

| Triwi wariii Triiesiioid                  | 13                   | V I HM railing                          | MAX14747     |     | 30    |     | 70 V CAP          |

| THM Cool Threshold                        | T <sub>2</sub>       | V <sub>THM</sub> rising                 | MAX14746     |     | 63.3  |     | %V <sub>CAP</sub> |

| Triwi Cool Triiconola                     | 12                   | V I HIM Homig                           | MAX14747     |     | 66.75 |     | 70 V CAP          |

| THM Cold Threshold                        | T <sub>1</sub>       | V <sub>THM</sub> rising                 | MAX14746     |     | 72.3  |     | %V <sub>CAP</sub> |

|                                           | - 1                  | - 1111019                               | MAX14747     |     | 77.2  |     |                   |

| THM Disable Threshold                     | T <sub>HMDIS</sub>   | V <sub>THM</sub> rising                 |              |     | 96.6  |     | %V <sub>CAP</sub> |

| THM Threshold Hysteresis                  | T <sub>HMHYS</sub>   |                                         |              |     | 60    |     | mV                |

| THM Input Leakage Current                 | I <sub>LTHM</sub>    |                                         |              | -1  |       | +1  | μA                |

| THM Detection Time                        | t <sub>THM</sub>     |                                         |              |     | 15    |     | ms                |

| CHARGER STATUS OUTPUT                     | (LED)                |                                         |              |     |       |     |                   |

| Output Logic-Low Voltage                  | V <sub>OLED</sub>    | I <sub>SINK</sub> = 10mA                |              |     | 35    | 100 | mV                |

| Temperature Suspend Mode<br>Blink Period  | t <sub>TSUS</sub>    | Blinking with 50 <sup>4</sup>           | % duty cycle |     | 1.5   |     | s                 |

| Timeout Mode Blink Period                 | tтімоит              | Blinking with 50°                       | % duty cycle |     | 0.15  |     | s                 |

| Pulse Time for Fresh Battery<br>Insertion |                      |                                         |              |     | 1     |     | s                 |

| IMPEDANCE-MODE BATTERY                    | DETECTION            |                                         |              | ·   |       |     |                   |

| Discharge Current                         | I <sub>DIS</sub>     | V <sub>BAT</sub> = 3.6V                 |              | 6   | 10    | 14  | mA                |

| Replace Current                           | I <sub>RPL</sub>     | V <sub>BAT</sub> = 3.6V, V <sub>S</sub> | YS > 4.0V    | 6   | 10    | 14  | mA                |

| Test Current Mismatch                     | I <sub>DR_MIS</sub>  |                                         |              | -15 |       | +15 | %                 |

| Discharge Replace Time                    | t <sub>DIS_RPL</sub> | V <sub>BAT</sub> = 3.6V                 |              |     | 15    |     | ms                |

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C to} + 85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.) \text{ (Note 3)}$

| PARAMETER                            | SYMBOL                               | CONDITIONS                                                                                                              | MIN   | TYP  | MAX                | UNITS |

|--------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|------|--------------------|-------|

| CHARGER DETECTION                    |                                      |                                                                                                                         |       |      |                    |       |

| V <sub>DP_SRC</sub> Voltage          | V <sub>DP_SRC</sub>                  | I <sub>LOAD</sub> = 0 to 200μA                                                                                          | 0.5   | 0.6  | 0.7                | V     |

| V <sub>DAT_REF</sub> Voltage         | V <sub>DAT_REF</sub>                 |                                                                                                                         | 0.25  | 0.3  | 0.35               | V     |

| V <sub>LGC</sub> Voltage             | V <sub>LGC</sub>                     |                                                                                                                         | 1.15  | 1.24 | 1.5                | V     |

| I <sub>DM_SINK</sub> Current         | I <sub>DM_SINK</sub>                 | V <sub>OUT</sub> = 0.15V to 3.6V                                                                                        | 50    | 80   | 110                | μA    |

| I <sub>DP_SRC</sub> Current          | I <sub>DP_SRC</sub>                  | V <sub>OUT</sub> = 0V to 2.5V                                                                                           | 5.5   | 8.4  | 10                 | μA    |

| R <sub>DM_DWN</sub>                  | $R_{DM\_DWN}$                        |                                                                                                                         | 14.25 | 20   | 24.8               | kΩ    |

| I <sub>WEAK</sub> Current            | I <sub>WEAK</sub>                    |                                                                                                                         | 0.01  | 0.1  | 0.3                | μA    |

| 25% Resistor-Divider Ratio           | R <sub>25</sub>                      |                                                                                                                         | 22.5  | 25   | 27.5               | %     |

| 47% Resistor-Divider Ratio           | R <sub>47</sub>                      |                                                                                                                         | 43.3  | 47   | 51.7               | %     |

| 71% Resistor-Divider Ratio           | R <sub>71</sub>                      |                                                                                                                         | 69.5  | 71.6 | 73.5               | %     |

| USB Charger Detect Time              | t <sub>DPSRC_ON</sub>                |                                                                                                                         | 40    |      | 60                 | ms    |

| V <sub>BUS</sub> Debounce Time       | t <sub>MDEB</sub>                    |                                                                                                                         | 20    | 30   | 40                 | ms    |

| DCD Debounce                         | tDCD_DEB                             |                                                                                                                         | 36    | 40   | 44                 | ms    |

| DCD Timeout                          | t <sub>DCD_TO</sub>                  |                                                                                                                         |       | 2000 |                    | ms    |

| USB ANALOG SWITCH PERFO              | RMANCE (TDN/                         | TDP)                                                                                                                    |       |      |                    |       |

| Analog-Signal Range                  | V <sub>TDN</sub><br>V <sub>TDP</sub> |                                                                                                                         | 0     |      | V <sub>CCINT</sub> | V     |

| On-Resistance                        | R <sub>ONUSB</sub>                   | V <sub>BAT</sub> = 3.0V, I <sub>CDN</sub> , I <sub>CDP</sub> = 10mA,<br>V <sub>CDN</sub> , V <sub>CDP</sub> = 0 to 3.0V |       | 3    | 6                  | Ω     |

| On-Resistance Match Between Channels | DR <sub>ONUSB</sub>                  | V <sub>BAT</sub> = 3.0V, I <sub>CDN</sub> , I <sub>CDP</sub> = 10mA,<br>V <sub>CDN</sub> , V <sub>CDP</sub> = 400mV     |       |      | 0.5                | Ω     |

| On-Resistance Flatness               | R <sub>FLATUSB</sub>                 | V <sub>BAT</sub> = 3.0V, I <sub>CDN</sub> , I <sub>CDP</sub> = 10mA,<br>V <sub>CDN</sub> , V <sub>CDP</sub> = 0 to 3V   |       | 0.3  | 1                  | Ω     |

| Off-Leakage Current                  | I <sub>LUSB_OFF</sub>                | Switch open, $V_{TDN}/V_{TDP} = 0.3V/2.5V$ , $V_{CDP}/V_{CDN} = 2.5V/0.3V$                                              | -360  |      | +360               | nA    |

| On-Leakage Current                   | I <sub>LUSB_ON</sub>                 | Switch closed, $V_{TDN}/V_{TDP}/V_{CDN}/V_{CDP} = 0.3V/2.5V$                                                            | -360  |      | +360               | nA    |

| Analog Switch Turn-On Time           | t <sub>ON</sub>                      | $I^2$ C stop to switch on, $R_L$ = 50Ω                                                                                  |       | 0.5  | 1                  | ms    |

| Analog Switch Turn-Off Time          | t <sub>OFF</sub>                     | $I^2$ C stop to switch on, $R_L$ = 50Ω                                                                                  |       | 0.1  | 1                  | ms    |

| On-Capacitance                       | C <sub>ON</sub>                      | V <sub>IN</sub> = 0.5V <sub>P-P</sub> DC = 0V, f = 240MHz                                                               |       | 6    |                    | pF    |

| Off-Capacitance                      | C <sub>OFF</sub>                     | V <sub>IN</sub> = 0.5V <sub>P-P</sub> DC = 0V, f = 240MHz                                                               |       | 3.5  |                    | pF    |

$(V_{VB} = 5.0V, V_{BAT} = 4.2V, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{BAT} = 3.6V, V_{VB} = 5.0V, V_{SYS} = V_{SYS\_REG}, T_{A} = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                                       | SYMBOL              | CONDITIONS                                                            | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------|---------------------|-----------------------------------------------------------------------|------|-----|------|-------|

| Off-Isolation                                   | V <sub>ISO</sub>    | $R_S = R_L = 50\Omega$ , $f = 20kHz$ ,<br>$V_{IN} = 0.5V_{P-P}$       |      | -60 |      | dB    |

| DIGITAL INPUTS/OUTPUTS (ID                      | EF, CTYP, INT, U    | JOK_, FSUS)                                                           |      |     |      |       |

| Input Logic High-Voltage                        | V <sub>IH</sub>     |                                                                       | 1.4  |     |      | V     |

| Input Logic Low-Voltage                         | V <sub>IL</sub>     |                                                                       |      |     | 0.4  | V     |

| Leakage Current                                 | I <sub>LEAK</sub>   | CTYP, INT, UOK_ only                                                  | -250 |     | +250 | nA    |

| Open-Drain Output Logic-Low                     | V <sub>ODOL</sub>   |                                                                       |      |     | 0.4  | V     |

| STARTUP TIMINGS                                 |                     |                                                                       |      |     |      |       |

| VB to SYS Rise                                  |                     | IBusLim = 0, FSUSMsK = 0, IDEF = 0                                    |      | 205 |      | ms    |

| VB to SFOUT Rise                                |                     | SFoutAsrt = 0                                                         |      | 205 |      | ms    |

| VB to CTYP Falling Edge                         |                     |                                                                       |      | 205 |      | ms    |

| CTYP to UOK1 Falling Edge                       | tsys_uok1_f         |                                                                       |      | 5.5 |      | ms    |

| UOK1 to UOK2 Falling Edge<br>Delay              | tuok1_uok2          | If UOK2 option enabled                                                |      | 400 |      | ms    |

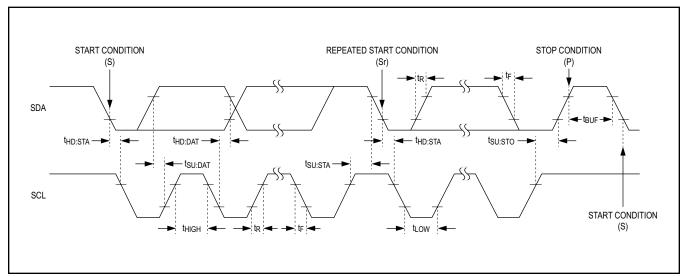

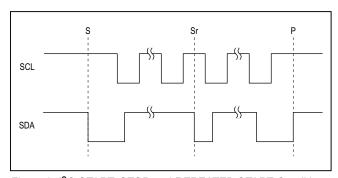

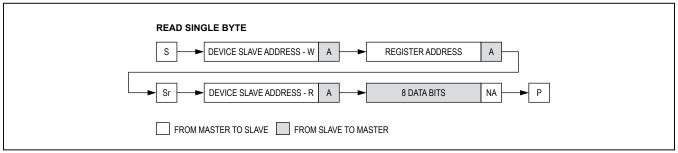

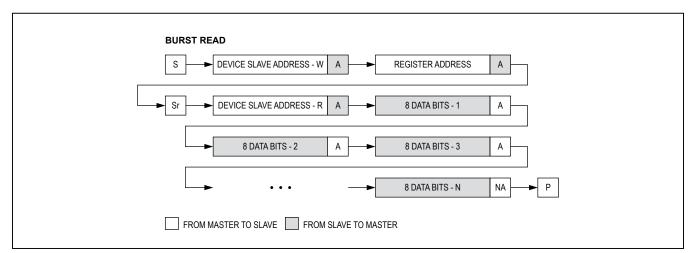

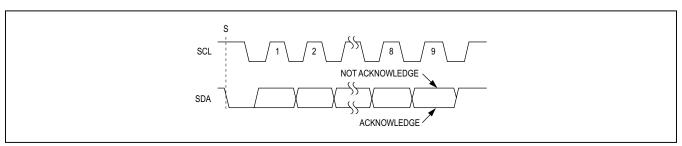

| I <sup>2</sup> C TIMING SPECIFICATIONS          | (FIGURE 1)          |                                                                       |      |     |      |       |

| I <sup>2</sup> C Maximum Clock Frequency        | f <sub>SCL</sub>    |                                                                       |      | 400 |      | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |                                                                       | 1.3  |     |      | μs    |

| START Condition Setup Time                      | t <sub>SU:STA</sub> |                                                                       | 0.6  |     |      | μs    |

| Repeated Start Condition<br>Setup Time          | t <sub>SU:STA</sub> |                                                                       | 0.6  |     |      | μs    |

| START Condition Hold Time                       | thd:sta             |                                                                       | 0.6  |     |      | μs    |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub> |                                                                       | 0.6  |     |      | μs    |

| Clock Low Period                                | t <sub>LOW</sub>    |                                                                       | 1.3  |     |      | μs    |

| Clock High Period                               | t <sub>HIGH</sub>   |                                                                       | 0.6  |     |      | μs    |

| Data Valid to SCL Rise Time                     | t <sub>SU:DAT</sub> | Write-setup time                                                      | 100  |     |      | ns    |

| Data Hold Time to SCL Fall                      | t <sub>HD:DAT</sub> | Write-hold time                                                       | 0    |     |      | ns    |

| SCL, SDA Spike Suppression                      | t <sub>SP</sub>     | Duration of spike on SCL and SDA that is not detected as a valid edge |      | 50  |      | ns    |

| PROTECTION SPECIFICATION                        | IS                  |                                                                       |      |     |      |       |

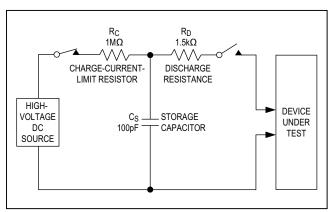

|                                                 |                     | Human Body Model                                                      |      | ±15 |      |       |

| ESD Protection, CDP/CDN                         |                     | IEC61000-4-2 Air Gap                                                  |      | ±4  |      | kV    |

|                                                 |                     | IEC61000-4-2 Contact                                                  |      | ±5  |      |       |

| ESD Protection, All Other Pins                  |                     | Human Body Model                                                      |      | ±2  |      | kV    |

- Note 2: All units are production tested at +25°C. Specifications over temperature are guaranteed by design.

- $V_{CCINT} = V_{CAP}$  (if CAP is present) or  $V_{BAT}$  (if CAP is not present). Note 3:

- Note 4: Threshold is valid when V<sub>VBDET</sub> < V<sub>VB</sub> < V<sub>VBOV</sub>. When V<sub>SYS</sub> < V<sub>BAT UVLO</sub>, the BAT-SYS switch opens and BAT is connected to SYS through a diode.

- When  $V_{VB} > V_{SFOUT\_OVP}$ , SFOUT LDO turns off. Note 5:

- Note 6: When the die temperature exceeds T<sub>SFOUT\_TLIM</sub>, SFOUT regulator and SYS limiter turns off. V<sub>SYS</sub> is supplied by V<sub>BAT</sub>.

- Note 7: When the die temperature exceeds T<sub>CHG</sub> LIM, charger current starts to reduce.

Note 8: V<sub>SYS</sub>\_LIM is the SYS voltage below which the charger starts to limit the charging current.

- Note 9: When  $V_{SYS}$  drops below  $V_{SYS}$  HLD, the battery charger does not move to the maintain charge state.

- Note 10: The charge timer extend threshold is the charge current level below which the charge timer clock runs at half speed. The charge timer suspend threshold is the charge current level below which the charge timer clock is paused.

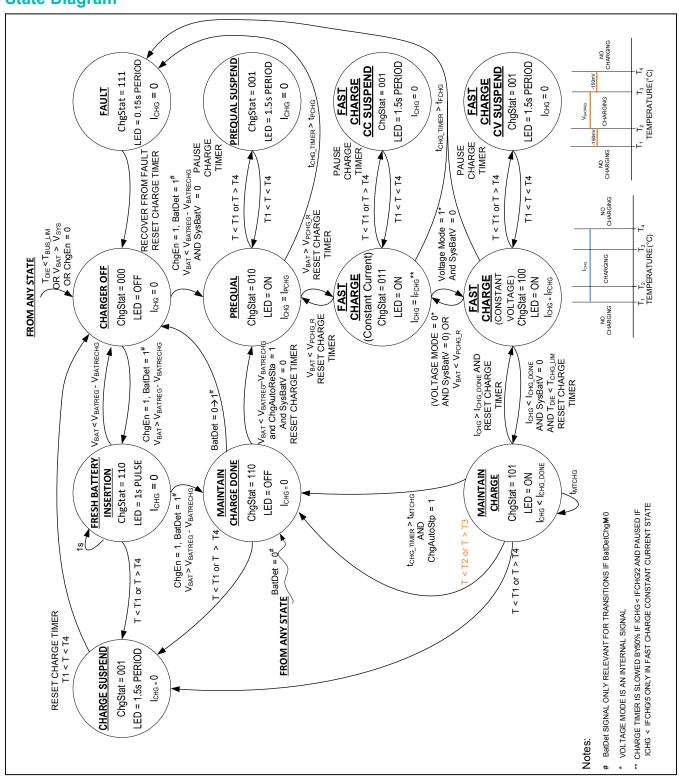

#### **Timing Diagram**

Figure 1. I<sup>2</sup>C Timing Diagram

Maxim Integrated | 10 www.maximintegrated.com

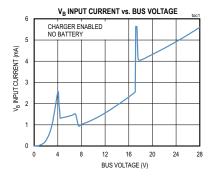

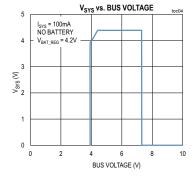

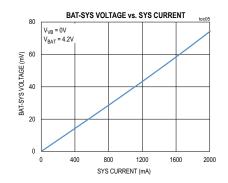

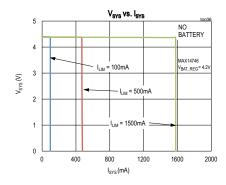

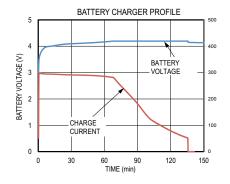

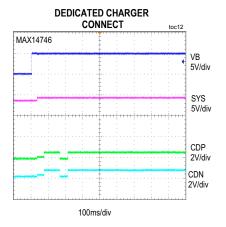

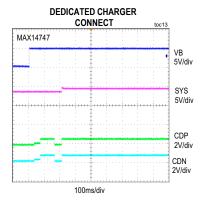

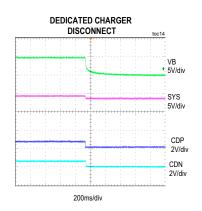

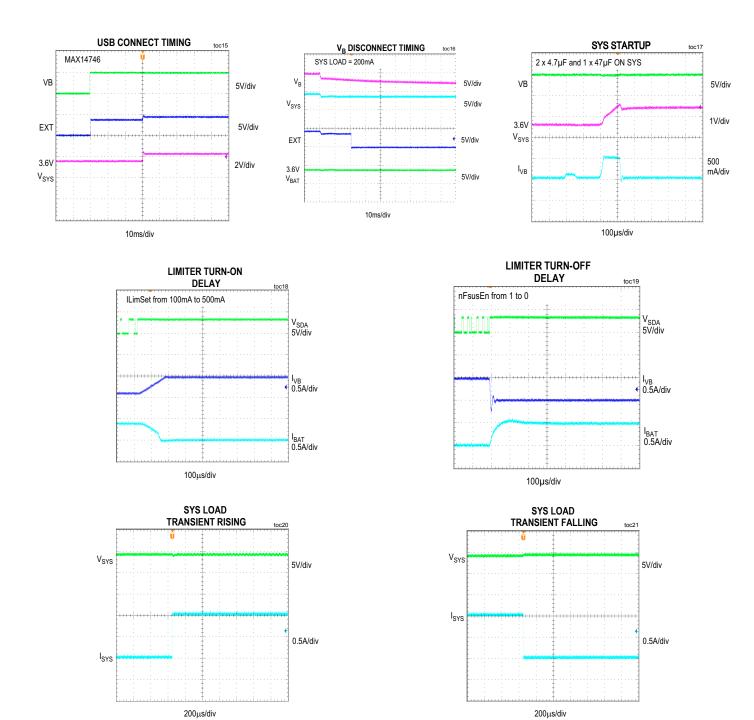

## **Typical Operating Characteristics**

$(V_{BAT} = 3.6V, V_{VB} = 5V, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

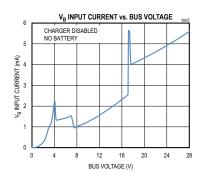

## **Typical Operating Characteristics (continued)**

$(V_{BAT} = 3.6V, V_{VB} = 5V, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(V_{BAT} = 3.6V, V_{VB} = 5V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

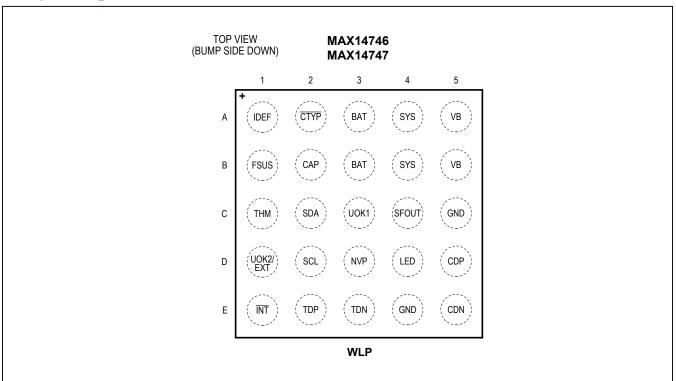

# **Bump Configuration**

# **Bump Descriptions**

| BUMP   | NAME | FUNCTION                                                                                                                                                                                                                                                                                        |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | IDEF | Current-Limit Setting Input. IDEF has an internal $470k\Omega$ pulldown resistor to GND. IDEF is only active if FSUSMsk bit is set to 0 and FSUS is LOW 0 = Input current limit determined by I <sup>2</sup> C settings (IBusLim, ILimSet, IBusDetSw bits) 1 = Input current limit set to 100mA |

| A2     | CTYP | Charger Type Output. CTYP is an open-drain output that asserts when DCP, CDP, or Apple 2A adapter is detected.                                                                                                                                                                                  |

| A3, B3 | BAT  | Battery Connection. Connect a single-cell Li+ battery from BAT to GND. Connect a capacitor from BAT to GND with a minimum value of 10µF and a maximum value of 30µF.                                                                                                                            |

| A4, B4 | SYS  | System Load Connection. Connect SYS to the system load. Bypass SYS with a $10\mu F$ low-ESR ceramic capacitor to GND as close as possible to the device. Connect $50\mu F$ additional capacitance to GND away from the device.                                                                  |

| A5, B5 | VB   | USB $V_{BUS}$ Input. VB is the input for the overvoltage protector. VB is monitored to detect the presence of a USB input power supply. Bypass VB with a 1µF ceramic capacitor to GND as close as possible to the device.                                                                       |

| B1     | FSUS | Force-Suspend Enable Input. FSUS is only active if the FSUSMsk bit is set to 0. FSUS has a 470kΩ pulldown resistor to GND.  0 = Current limit determined by IDEF/I <sup>2</sup> C configuration  1 = Input current limit is forced to 0                                                         |

# **Bump Description (continued)**

| ВИМР   | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B2     | CAP      | Internal LDO Bypass Connection. Connect a 1µF ceramic capacitor from CAP to GND as close as possible to the device. Connect the pullup resistor for the battery thermistor output (THM) to CAP. Ensure that the total load current out of CAP is less than 2mA.                                                                                                                                    |

| C1     | THM      | Battery Temperature Thermistor Measurement Input                                                                                                                                                                                                                                                                                                                                                   |

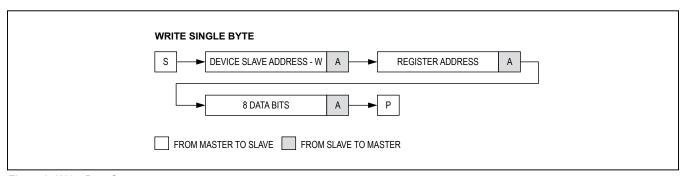

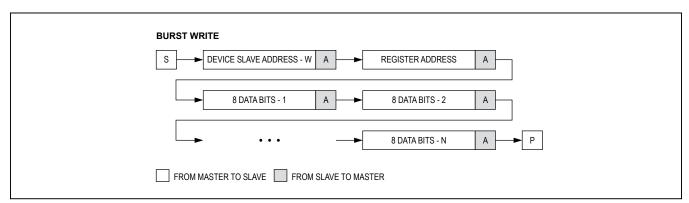

| C2     | SDA      | I <sup>2</sup> C Serial Data Input/Output. Connect an external pullup resistor on SDA to the logic supply voltage.                                                                                                                                                                                                                                                                                 |

| C3     | UOK1     | SYS Voltage Valid and Battery Detect Output. UOK1 is an open-drain output.                                                                                                                                                                                                                                                                                                                         |

| C4     | SFOUT    | Protected LDO Output. SFOUT is powered from VB. Bypass SFOUT with a 1µF ceramic capacitor to GND as close as possible to the device. SFOUT can power the on-board USB 2.0 Hi-Speed host.                                                                                                                                                                                                           |

| C5, E4 | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                             |

| D1     | UOK2/EXT | UOK2: Delayed SYS Voltage Valid and Battery-Detect Output. UOK2 is an open-drain output. EXT: Push-Pull Output Control for External SYS-BAT pMOS Switch. Output pulled high to BAT when the charger is not present.                                                                                                                                                                                |

| D2     | SCL      | I <sup>2</sup> C Serial Clock Input. Connect an external pullup resistor on SCL to the logic supply voltage.                                                                                                                                                                                                                                                                                       |

| D3     | NVP      | Gate Bias and Protection for External PFET. NVP protects VB from negative voltages. Leave unconnected if not used.                                                                                                                                                                                                                                                                                 |

| D4     | LED      | Charging Fault Indicator. LED is an open-drain output that indicates a battery charging fault. When a JEITA temperature fault is detected, LED is pulsed at 50% duty cycle with a period of 1.5s. When a charge timer fault is detected, or the BAT overvoltage threshold (V <sub>BATOV</sub> ) is exceeded, LED is pulsed at 50% duty cycle with a period of 0.15s. Connect LED to GND if unused. |

| D5     | CDP      | USB Connector D+ Input                                                                                                                                                                                                                                                                                                                                                                             |

| E1     | INT      | Interrupt Output. INT is an open-drain output that asserts whenever an unmasked interrupt occurs. Connect an external pullup resistor on INT to the logic supply voltage.                                                                                                                                                                                                                          |

| E2     | TDP      | USB Transceiver D+ Connection. Connect TDP to device microprocessor USB transceiver D+ line.                                                                                                                                                                                                                                                                                                       |

| E3     | TDN      | USB Transceiver D- Connection. Connect TDN to device microprocessor USB transceiver D- line.                                                                                                                                                                                                                                                                                                       |

| E5     | CDN      | USB Connector D- Input                                                                                                                                                                                                                                                                                                                                                                             |

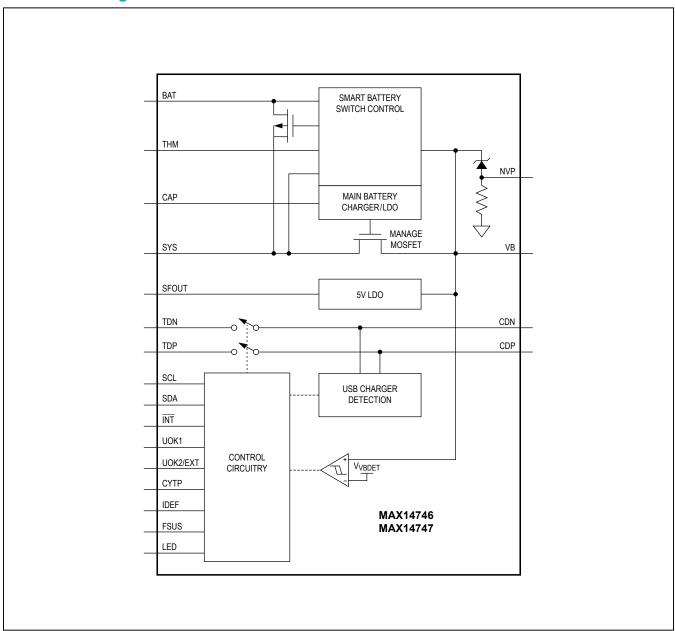

# **Functional Diagram**

#### MAX14746/MAX14747

# USB Detection with Smart Power Selector Li+ Chargers

#### **Detailed Description**

The MAX14746/MAX14747 charger detector solutions integrate a smart-power selector with a linear charger that allows charging a Li+ battery and a powering system to load off the same USB power source. When the USB power source is not present or cannot provide enough power, the Li+ battery helps power the system. The devices protect against voltage faults and transients on VB up to 28V without interrupting operation.

The MAX14746/MAX14747 are compliant to USB Battery Charger Detection Rev 1.2\* as well, as special chargers that bias the D+/D- lines. The devices limit VB input current based on the type of charging device that is detected and two digital inputs (IDEF and FSUS).

The devices monitor overcurrent and overtemperature faults and automatically manages the charger. Configurable interrupts and status information allow the system microcontroller to intervene.

#### **Negative Voltage Protection**

The MAX14746/MAX14747 feature a gate protection circuit for an external PFET that protects against negative voltages on V<sub>BUS</sub>. The NVP output has a resistor to GND and a voltage clamp for the gate of the PFET. The voltage clamp limits the gate-to-source voltage to 7.0V (typ) when the V<sub>BUS</sub> voltage is positive. If a negative voltage is present on V<sub>BUS</sub>, e.g., by a backwards connector, then the PFET turns off and provides negative voltage protection. This negative voltage protection requires that a device downstream from the MAX14746/MAX14747 provide reverse-current blocking on V<sub>BUS</sub>. This is required to allow the PFET to turn off. When the drain of the PFET is negative, current flows out of VB. If this reverse current is limited to a small value, V<sub>VB</sub> drops and the PFET gate-to-source voltage will drop below the threshold voltage.

#### **Supply Voltage Selector**

The MAX14746/MAX14747 select their power source themselves by monitoring the voltages at VB and BAT. The devices select  $V_{VB}$  when it is present; otherwise,  $V_{BAT}$ .

#### **Smart Power Selector**

The MAX14746/MAX14747 feature circuitry that seamlessly distributes power between the USB power supply input on VB, the battery on BAT, and system load on SYS when both an external charger adaptor and a battery are connected.

\*Except DCD timeout extended from 900ms to 2s for the MAX14746/MAX14747.

When the system load requirements are less than the input current limit, residual power from the input charges the battery. When the system load requirements exceed the input current limit, the battery supplies supplemental current to the load. When the battery is connected and there is no external power input, the battery powers the system. When an external power input is connected and the battery is discharged or not present, VB powers the system.

#### **USB Charger Detection**

The MAX14746/MAX14747 charger detection circuitry support full USB Battery Charger Rev 1.2\* detection. The devices detect all charger types, including standard USB ports, charging downstream ports (CDPs), and dedicated chargers. The devices also support Apple power adaptors with resistor dividers on the D+/D- pins at 500mA, 1000mA, and 2000mA current levels. See Charger Detection Timing Diagram.

#### **System Load Switch**

The MAX14746/MAX14747 feature an internal MOSFET that connect SYS to BAT for the battery to provide power to the system load. If the USB supply is at the current limit, the devices enable the switch to prevent the system voltage from falling below the battery voltage by supplying extra current from the battery. The battery is not charged if the system load continuously exceeds the input current limit, so this feature is useful for handling loads that are nominally below the input current limit but have high-current peaks exceeding the input current limit. The system uses battery energy during these peaks, but VB charges the battery at all other times.

#### **External System Load Switch**

The UOK2/EXT pin can be configured to function as a control signal for an external system load switch.

When the EXT functionality is enabled, the UOK2/EXT pin can drive the gate of an external PMOS connected between SYS and BAT.

When a valid VB voltage is present, EXT is pulled up to  $V_{SYS}$ . When VB is disconnected and  $V_{SYS}$  is equal to  $V_{BAT}$ , the EXT pin is driven to GND. This feature provides an extremely low-impedance SYS-BAT connection.

#### **Input-Current Limiter**

The input-current limiter distributes power from the external USB supply to the system load and battery charger. The input current limiter consists of a MOSFET bulk management to optimize the use of available power.

#### **Invalid VB Voltage Protection**

The MAX14746/MAX14747 enter overvoltage lockout (OVL) if  $V_{VB}$  is above the overvoltage threshold. OVL protects the device and downstream circuitry from high-voltage stress up to 28V. The internal circuit remains powered, the charger turns off, the system load switch closes, and an interrupt triggers during OVL.  $V_{VB}$  is also invalid if it is less than  $V_{BAT}$  or less than the USB undervoltage threshold. The device takes the same actions as OVL while  $V_{VB}$  is invalid.

#### **VB Input Current Limit**

The device limits VB input current to prevent input overload. Three methods can set the input current limit:

- a) Set the current limit automatically based on the capabilities of the source as indicated by the ChgTyp [3.0] value read from I<sup>2</sup>C (register 0x02).

- b) Set the current limit manually over I2C.

- c) Set the current limit manually using the IDEF and/ or FSUS inputs.

#### **Thermal Limiting**

If the local temperature exceeds 120°C (typ), the MAX14746/MAX14747 attempt to limit temperature increase by reducing the input current from VB. The system load has priority over charger current, so the device lowers the charge current to reduce overall input current. If the temperature continues to rise and reaches 150°C (typ), the device disconnects VB and the battery powers the entire system load.

#### **Adaptive Battery Charging**

The battery charger draws power from SYS while VB powers the system. The device reduces charge current to prevent  $V_{SYS}$  from falling if the total load exceeds the input current limit.

#### JEITA Compliant Battery Protection/ Charging

The MAX14746/MAX14747 monitor the temperature of the battery for safe charging of Li+ batteries according to JEITA standards. The devices measure the battery pack temperature by using a resistor divider formed by a pullup resistor connected to CAP and the battery pack thermistor. The external pullup allows matching to different thermistor nominal values. The JEITA circuitry supports thermistors with different  $\beta$  values, but the value must be fixed to choose the CAP pullup resistor. Typical  $\boldsymbol{\beta}$  values are 4250 (MAX14747) and 3380 (MAX14746). The THM input measures the voltage across the resistor divider. There are five temperature zones of operation and the charger termination voltage is controlled based on the pack temperature. The charger is automatically controlled and the active current temperture zone can be read from the JEITAStat[3:0] bits over I2C (register 0x03).

# Register Map and Descriptions

| F                                        |            | BIT5 | 1 1         | BIT4           | BIT3          | BIT2          | BIT1           | BIT0           |

|------------------------------------------|------------|------|-------------|----------------|---------------|---------------|----------------|----------------|

| 0x00 R                                   |            |      |             |                | Chip_Id[7:0]  |               |                |                |

| 0x01 R                                   |            |      |             | )              | Chip_Rev[7:0] |               |                |                |

| 0x02 R ChgTyp[3:0]                       | ChgTyp[3:0 | 0:6] | ]           |                | BatDet        |               | ChgStat[2:0]   | :0]            |

| 0x03 R VLim Lim U                        |            | n    | UsbOVP      | SysBatV        | UsbOk         |               | JeitaStat[2:0] | ::0]           |

| 0x04 R RFU RFU                           | RFU        |      | RFU         | RFU            | ThrmSd        | ChgTReg       | DCDTmr         | ChgTmo         |

| 0x05   CoR   ChgTypInt   UsbOVPInt   S   |            | S    | SysBatVInt  | RFU            | BatDetInt     | ChgStatInt    | ChgTRegInt     | ChgTmoInt      |

| 0x06 CoR VLimInt DCDTmrInt               | DCDTmrlnt  |      | lLimInt     | ThrmSdInt      | UsbOkInt      | JeitaStatInt  | JeitaHighTInt  | JeitaTSdInt    |

| 0x07   R/W   ChgTypIntM   UsbOVPIntM  Sy | UsbOVPIntM |      | SysBatVIntM | RFU            | BatDetIntM    | ChgStatIntM   | ChgTRegIntM    | ChgTmoIntM     |

| 0x08 R/W VLimIntM DCDTmrIntM             | DCDTmrlntM |      | LimIntM     | ThrmSdIntM     | UsbOkIntM     | JeitaStatIntM | JeitaHighTIntM | JeitaTSdIntM   |

| 0x09 R/W RFU RFU                         |            |      | nFsusEn     | FSUSMsk        | RFU           | RFU           | DCDEn          | RFU            |

| 0x0A R/W IBusLim RFU                     | RFU        |      | RFU         |                | ILimSet[2:0]  |               | sngl           | IBusDetSw[2:0] |

| 0x0B R/W RFU RFU                         | RFU        |      | RFU         |                | IFChg[2:0]    |               | RFU            | RFU            |

| 0x0C   R/W   JeitaEn   BatUOKMsk   Ba    |            | Bé   | BatDetCntl  | ChgEn          | RFU           |               | ChgDone[2:0]   | 2:0]           |

| 0x0D R/W RFU RFU                         | RFU        |      | MtChg       | MtChgTmr[1:0]  | FChgTmr[1:0]  | nr[1:0]       | PC             | PChgTmr[1:0]   |

| 0x0E R/W BatReChg[1:0]                   | Chg[1:0]   |      | BatRegl     | BatRegLow[1:0] | BatRegSel     |               | BatRegHi[2:0]  | 2:0]           |

| 0x0F R/W RFU RFU                         | RFU        |      | RFU         | RFU            | RFU           | RFU           | RFU            | RFU            |

| 0x10 R/W VPChg   IPChg[1:0]              | IPChg[1:   | =    | 0]          | VPChg          | VPChgLow[1:0] | VPChg         | VPChgHigh[1:0] | BatDetChgM     |

| 0x11 R/W SFOutOrd SFOutAsrt              | SFOutAsrt  |      | AnSwC       | AnSwCntl[1:0]  | ChgTypMan     | ChgAutoStart  | BatDetChgEn    | UsbCompl       |

| 0x12 R/W ChgAutoStp SFOutData            |            |      | RFU         | RFU            |               | SysMin[2:0]   |                | RFU            |

| 0x13 R                                   |            |      |             |                | ILimMon[7:0]  |               |                |                |

RFU = Reserved for future use. Do not change from default value.

<sup>\*\*</sup> Register resets to default value on VB rising edge.

# **Chip ID Register**

| ADDRESS:     | 0x00         |                 |                |                 |              |              |    |   |  |  |  |

|--------------|--------------|-----------------|----------------|-----------------|--------------|--------------|----|---|--|--|--|

| MODE:        | Read Only    |                 |                |                 |              |              |    |   |  |  |  |

| BIT          | 7            | 6               | 5              | 4               | 3            | 2            | 1  | 0 |  |  |  |

| NAME         |              |                 |                | Chip_           | Id[7:0]      |              |    | • |  |  |  |

| RESET        |              | SEE TABLE 4     |                |                 |              |              |    |   |  |  |  |

| Chip_ld[7:0] | The Chip_ld[ | [7:0] bits show | information ab | out the versior | of the MAX14 | 1746/MAX1474 | 7. |   |  |  |  |

# **Chip Revision Register**

| ADDRESS:      | 0x01        |                 |                |                |                |             |               |   |  |  |

|---------------|-------------|-----------------|----------------|----------------|----------------|-------------|---------------|---|--|--|

| MODE:         | Read Only   |                 |                |                |                |             |               |   |  |  |

| BIT           | 7           | 6               | 5              | 4              | 3              | 2           | 1             | 0 |  |  |

| NAME          |             | Chip_Rev[7:0]   |                |                |                |             |               |   |  |  |

| RESET         |             |                 |                | SEE T          | ABLE 4         |             |               |   |  |  |

| Chip_Rev[7:0] | The Chip_Re | ev[7:0] bits sh | ow information | about the revi | sion of the MA | X14746/MAX1 | 4747 silicon. |   |  |  |

# **Status A Register**