# 24/48V Fan Driver/Controller With High-Side Drive

#### **Features**

- ► High-side drive allows use of tachs

- Direct interface to host controller

- ► Noise-immune linear speed control

- 4-bit digital speed control

- Operates from single +24/+48V supply

- Programmable PWM frequency

- Undervoltage lockout

## **Applications**

- ▶ 24/48V chassis cooling tray

- Servers

- SAN equipment

- Cellular and fix wireless systems

- 24/48V PBX system

- Base stations

## **General Description**

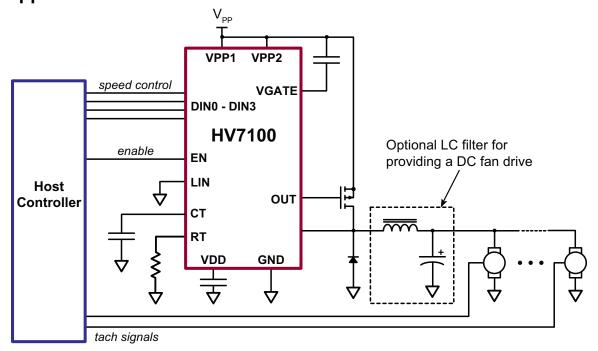

The HV7100 is an integrated PWM speed controller for driving 24 and 48VDC fans. The features and benefits provided by the HV7100 make driving fans simple and low cost. The HV7100 drives a high side external P-channel FET, allowing the use of fans having a ground-based tachometer signal. It has a wide input voltage range of +16 to +90V, ideal for +24 or +48V systems. No low voltage supply is needed.

A 4-bit digital control input provides direct interfacing with a micro controller or system processor to control the fan speed. It can also be used as a stand-alone fan controller, via a thermistor connection to the Linear Control pin.

The HV7100 has a wide PWM frequency range. When driving fans directly with a PWM supply voltage, frequency may be set low, around 50 - 120Hz. When used to drive fans requiring a DC supply, an LC filter may be employed. In this case, PWM frequency may be as high as 100kHz, reducing component sizes in the filter.

The HV7100 is an ideal device to incorporate in fan trays and fan control modules, as it reduces circuit complexity and minimizes parts count and overall cost for thermal management.

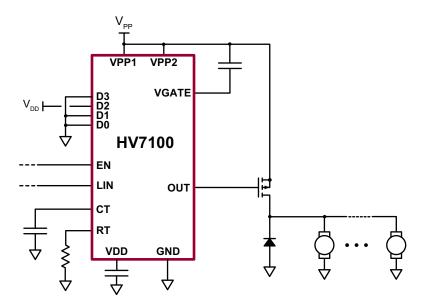

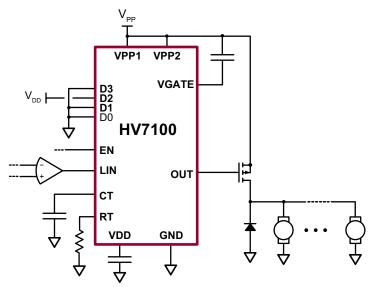

# **Typical Application Circuit**

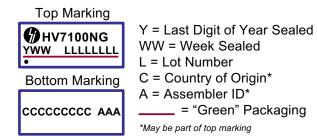

## **Ordering Information**

| Part Number     | Package           | Packing   |

|-----------------|-------------------|-----------|

| HV7100NG-G      | 14-Lead SOIC (NB) | 53/Tube   |

| HV7100NG-G M903 | 14-Lead SOIC (NB) | 2500/Reel |

<sup>-</sup>G denotes a lead (Pb)-free / RoHS compliant package

## **Absolute Maximum Ratings**

| Parameter                                            | Value                        |

|------------------------------------------------------|------------------------------|

| V <sub>PP</sub> to GND                               | -0.5V to 90V                 |

| V <sub>DD</sub> to GND                               | -0.3V to +6V                 |

| Input voltage, LIN                                   | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Input voltage, D <sub>IN</sub> 0 - D <sub>IN</sub> 2 | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Gate to V <sub>PP</sub>                              | +0.5V to -15V                |

| Continuous power dissipation $(T_A = +25^{\circ}C)$  | 750mW                        |

| Operating temperature range                          | -40°C to +85°C               |

| Storage temperature range                            | -65°C to +150°C              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

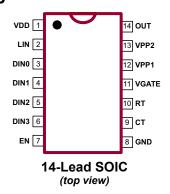

# **Pin Configuration**

## **Product Marking**

Package may or may not include the following marks: Si or **14-Lead SOIC**

# **Recommended Operating Conditions**

| Sym              | Parameter                          | Min | Тур | Max | Units |

|------------------|------------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub>  | Externally applied V <sub>DD</sub> | 3.7 | -   | 5.5 | V     |

| V <sub>PP</sub>  | High voltage supply                | 16  | -   | 75  | V     |

| f <sub>osc</sub> | Oscillator frequency               | 50  | -   | 100 | kHz   |

| R <sub>T</sub>   | Oscillator timing resistor         | 12  | -   | 500 | kΩ    |

# **Typical Thermal Resistance**

| Package      | $oldsymbol{	heta}_{j_{oldsymbol{a}}}$ |

|--------------|---------------------------------------|

| 44-Lead PLCC | 37°C/W                                |

## **Electrical Characteristics**

(Operating specifications are at  $T_A$  = 25°C,  $V_{PP}$  = 16 to 75V,  $V_{DD}$  = 3.0 to 5.5V, unless otherwise noted)

| Sym                   | Parameter                              | neter Min Typ Max Units |      | Units | Conditions |                                                                   |  |  |  |  |

|-----------------------|----------------------------------------|-------------------------|------|-------|------------|-------------------------------------------------------------------|--|--|--|--|

| Supplies              |                                        |                         |      |       |            |                                                                   |  |  |  |  |

| I <sub>PP</sub>       | V <sub>PP</sub> supply current         | -                       | -    | 4.0   | mA         | No ext load on $V_{DD}$ ,<br>$f_{OSC} = 50kHz$ , 250pF on OUT pin |  |  |  |  |

| UV <sub>PP(ON)</sub>  | V <sub>PP</sub> UVLO turn-on threshold | 11.7                    | 13.0 | 14.3  | V          |                                                                   |  |  |  |  |

| UV <sub>PP(HYS)</sub> | V <sub>PP</sub> UVLO hysteresis        | 1.5                     | 2.0  | 2.5   | V          |                                                                   |  |  |  |  |

| $V_{_{\mathrm{DD}}}$  | V <sub>DD</sub> internal regulation    | 3.0                     | 3.3  | 3.6   | V          | V <sub>PP</sub> = 16V to 75V                                      |  |  |  |  |

**Electrical Characteristics (cont.)** (Operating specifications are at  $T_A$  = 25°C,  $V_{PP}$  = 16 to 75V,  $V_{DD}$  = 3.0 to 5.5V, unless otherwise noted)

| Sym                                                                                                                  | Parameter                                                                                                                                                                  | Min                                | Тур                             | Max                                        | Units                | Conditions                                                                                                                                            |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|--------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I <sub>DD(INT)</sub>                                                                                                 | V <sub>DD</sub> supply current                                                                                                                                             | -                                  | -                               | 2.0                                        | mA                   | External applied $V_{DD} = 5.0V$ , $f_{OSC} = 50kHz$                                                                                                  |  |  |

| I <sub>DD(EXT)</sub>                                                                                                 | Current available from internal V <sub>DD</sub> regulator for external circuitry                                                                                           | -                                  | -                               | 2.0                                        | mA                   | ΔV <sub>DD</sub> <200mV                                                                                                                               |  |  |

| Gate Drive                                                                                                           | er                                                                                                                                                                         |                                    |                                 |                                            |                      |                                                                                                                                                       |  |  |

| $V_{GATE}$                                                                                                           | Gate regulator output voltage                                                                                                                                              | -10.2                              | -12                             | -13.8                                      | V                    | Referenced to V <sub>PP</sub>                                                                                                                         |  |  |

| $V_{\text{OUTH}}$                                                                                                    | Gate drive output voltage high                                                                                                                                             | -10.2                              | -12                             | -13.8                                      | V                    | Referenced to V <sub>PP</sub> ,                                                                                                                       |  |  |

| $V_{\text{OUTL}}$                                                                                                    | Gate drive output voltage low                                                                                                                                              | 0                                  | -                               | -0.8                                       | V                    | Test current = 15mA                                                                                                                                   |  |  |

| $R_{\mathrm{SRC}}$                                                                                                   | Pull-up resistance                                                                                                                                                         | -                                  | -                               | 25                                         | Ω                    | Test Current = 15mA                                                                                                                                   |  |  |

| R <sub>SINK</sub>                                                                                                    | Pull-down resistance                                                                                                                                                       | -                                  | -                               | 25                                         | Ω                    | Test Current = -15mA                                                                                                                                  |  |  |

| t <sub>RISE</sub>                                                                                                    | Rise time                                                                                                                                                                  | -                                  | -                               | 100                                        | ns                   | C <sub>LOAD</sub> = 250pF                                                                                                                             |  |  |

| t <sub>FALL</sub>                                                                                                    | Fall time                                                                                                                                                                  | -                                  | -                               | 100                                        | ns                   | C <sub>LOAD</sub> = 250pF                                                                                                                             |  |  |

| Oscillator                                                                                                           |                                                                                                                                                                            |                                    |                                 |                                            |                      |                                                                                                                                                       |  |  |

| f <sub>osc</sub>                                                                                                     | Oscillator frequency                                                                                                                                                       | 51                                 | 60                              | 69                                         | Hz                   | $C_{T} = 100nF, R_{T} = 43.0k\Omega$                                                                                                                  |  |  |

| f <sub>osc</sub>                                                                                                     | Oscillator frequency                                                                                                                                                       | 34                                 | 40                              | 46                                         | kHz                  | $C_{T} = 330 \text{pF}, R_{T} = 19.5 \text{k}\Omega$                                                                                                  |  |  |

| ogic and                                                                                                             | Linear Inputs                                                                                                                                                              |                                    |                                 |                                            |                      |                                                                                                                                                       |  |  |

| / <sub>DIN0-3</sub> (hi),<br>V <sub>EN</sub> (hi)                                                                    | Logic input voltage, high                                                                                                                                                  | 0.7 x V <sub>DD</sub>              | -                               | -                                          | V                    |                                                                                                                                                       |  |  |

|                                                                                                                      |                                                                                                                                                                            |                                    |                                 |                                            |                      |                                                                                                                                                       |  |  |

| $V_{\text{DIN0-3}}(\text{lo}),$ $V_{\text{EN}}(\text{lo})$                                                           | Logic input voltage, low                                                                                                                                                   | -                                  | -                               | 0.3 x V <sub>DD</sub>                      | V                    |                                                                                                                                                       |  |  |

| V <sub>EN</sub> (lo)                                                                                                 | Logic input voltage, low  Enable to gate turn on delay                                                                                                                     | - 0                                | -                               | 0.3 x V <sub>DD</sub>                      | V                    | LIN = V <sub>DD</sub> , D <sub>IN</sub> 0 - D <sub>IN</sub> 3 = 1111                                                                                  |  |  |

| V <sub>EN</sub> (Io)                                                                                                 |                                                                                                                                                                            | -<br>0<br>0                        |                                 |                                            |                      | 33                                                                                                                                                    |  |  |

| V <sub>EN</sub> (lo)                                                                                                 | Enable to gate turn on delay                                                                                                                                               |                                    | -                               | 150                                        | ns                   | LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$<br>LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$                                                            |  |  |

| $V_{EN}(Io)$ $T_{EN(ON)}$ $T_{EN(OFF)}$                                                                              | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down                                                                                         | 0                                  | -                               | 150<br>150                                 | ns<br>ns             | LIN = V <sub>DD</sub> , D <sub>IN</sub> 0 - D <sub>IN</sub> 3 = 1111                                                                                  |  |  |

| T <sub>EN(ON)</sub> T <sub>EN(OFF)</sub> I <sub>DIN0-3</sub>                                                         | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current                                                 | 0<br>200                           | - 330                           | 150<br>150<br>460                          | ns<br>ns<br>kΩ       | LIN = V <sub>DD</sub> , D <sub>IN</sub> 0 - D <sub>IN</sub> 3 = 1111                                                                                  |  |  |

| $V_{EN}(IO)$ $T_{EN(ON)}$ $T_{EN(OFF)}$                                                                              | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current                                                 | 0<br>200                           | - 330                           | 150<br>150<br>460                          | ns<br>ns<br>kΩ       | LIN = V <sub>DD</sub> , D <sub>IN</sub> 0 - D <sub>IN</sub> 3 = 111140C to +85C                                                                       |  |  |

| $V_{EN}(Io)$ $T_{EN(ON)}$ $T_{EN(OFF)}$ $I_{DIN0-3}$ $I_{LIN}$ Duty Cycle                                            | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current                                                 | 0<br>200<br>-1.0                   | 330                             | 150<br>150<br>460<br>1.0                   | ns<br>ns<br>kΩ<br>uA | LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$ 40C to +85C $V_{LIN} = 0.9V$ , $D_{IN} = 0000$                                                            |  |  |

| V <sub>EN</sub> (Io)  T <sub>EN(ON)</sub> T <sub>EN(OFF)</sub> I <sub>DIN0-3</sub> I <sub>LIN</sub> Duty Cycle       | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current  e  Duty cycle                                  | 0<br>200<br>-1.0                   | -<br>-<br>330<br>-<br>20        | 150<br>150<br>460<br>1.0                   | ns<br>ns<br>kΩ<br>uA | LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$ 40C to +85C $V_{LIN} = 0.9V, D_{IN} = 0000$ $V_{LIN} = 2.1V, D_{IN} = 0000$                               |  |  |

| V <sub>EN</sub> (Io)  T <sub>EN(ON)</sub> T <sub>EN(OFF)</sub> I <sub>DINO-3</sub> I <sub>LIN</sub> Duty Cycle  D    | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current  e  Duty cycle Duty cycle                       | 0<br>200<br>-1.0<br>16<br>75       | -<br>-<br>330<br>-<br>20<br>80  | 150<br>150<br>460<br>1.0                   | ns<br>ns<br>kΩ<br>uA | LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$ 40C to +85C $V_{LIN} = 0.9V, D_{IN} = 0000$ $V_{LIN} = 2.1V, D_{IN} = 0000$ $V_{LIN} = 0V, D_{IN} = 0011$ |  |  |

| V <sub>EN</sub> (Io)  T <sub>EN(ON)</sub> T <sub>EN(OFF)</sub> I <sub>DINO-3</sub> I <sub>LIN</sub> Duty Cycle  D  D | Enable to gate turn on delay Enable to gate turn off delay Digital input pull down resistance Linear control input current  e  Duty cycle Duty cycle Duty cycle Duty cycle | 0<br>200<br>-1.0<br>16<br>75<br>16 | -<br>330<br>-<br>20<br>80<br>20 | 150<br>150<br>460<br>1.0<br>24<br>85<br>24 | ns<br>ns<br>kΩ<br>uA | LIN = $V_{DD}$ , $D_{IN}0 - D_{IN}3 = 1111$ 40C to +85C $V_{LIN} = 0.9V, D_{IN} = 0000$ $V_{LIN} = 2.1V, D_{IN} = 0000$                               |  |  |

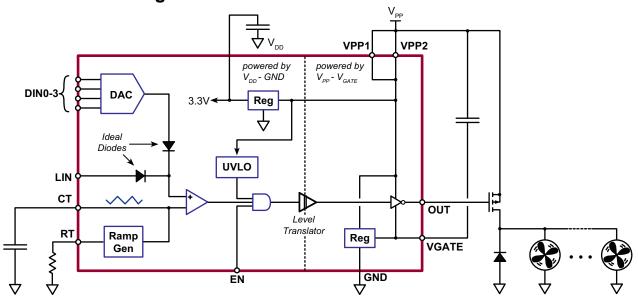

## **Functional Block Diagram**

## **Functional Description**

The HV7100 requires a single +16 to +75V supply to bias its internal circuitry. It internally generates 3.3V for  $V_{\rm DD}$ , and -12V relative to  $V_{\rm PP}$  for driving the external P-channel MOSFET. If an external  $V_{\rm DD}$  is applied (greater than 3.6V but less than 5.5V), the internal regulator will shut off. The HV7100 drives an external P-channel FET to drive the 24V/48V DC fan.

An external diode, connected across the fan terminals, is required to clamp the voltage across the fan to a diode drop during the off period.

#### **Pulse Width Modulator**

The PWM circuit compares the internal triangle wave oscillator (0.5 - 2.5 V pk-pk) with the linear control voltage or the DAC output. Its output is a square-wave PWM signal with duty cycle ranging from 0% to 100%.

When an external PWM signal is applied to the Enable input and the internal PWM generator is not needed,  $R_{\scriptscriptstyle T}$  and LIN should be connected to  $V_{\scriptscriptstyle DD}$  and  $C_{\scriptscriptstyle T}$  connected to GND.

#### **Oscillator**

A capacitor connected between the  $C_{\scriptscriptstyle T}$  and GND sets the frequency of the internal triangular frequency oscillator in conjunction with the timing resistor  $R_{\scriptscriptstyle T}$ .  $R_{\scriptscriptstyle T}$  sets the charge/discharge current into and out of  $C_{\scriptscriptstyle T}$

The frequency is determined by the following equation:

$$f = \frac{(0.258)}{(R_{\scriptscriptstyle T} \times C_{\scriptscriptstyle T})}$$

#### P-Channel Gate Driver

The PWM output of the comparator circuit is level translated and is the input to the gate drive circuit. The gate drive circuit turns an external P-channel FET on and off by applying -12V and 0V (reference to  $V_{\rm pp}$ ), respectively, between its gate and source. The -12V supply to the gate drive circuit is generated internally from  $V_{\rm pp}$ .

#### **Enable**

The EN pin directly controls the gate drive circuit. Pulling this pin to logic ground applies 0V to the external P-channel gate to turn it off. Applying a logic HIGH signal or pulling the voltage to  $V_{\text{DD}}$  resumes the switching cycle of the PWM signal.

#### Speed Control

The fan speed can be controlled in three ways:

**Linear Control** - Applying a DC voltage between 0.5V to 2.5V to the LIN pin varies the duty cycle of the voltage driving the fans from 0% to 100% according to:

$$D = \frac{V_{LIN}}{2} - 0.25$$

Linear control voltage below 0.5V will turn off the fan completely (0% duty cycle), while voltage greater than 2.5V will fully turn the fan on (100% duty cycle).

When using linear control mode, DIN0 – DIN3 should be set to logic 0. If desired, DIN may be used to set a lower limit on the fan speed. This input is immune to moderate noise on the control signal.

**Digital Control** - Applying logic signals to the DIN0 – DIN3 pins sets the duty cycle of the output. 0000 = 0% and 1111 = 100%. See Table 1 for details. In digital control mode, LIN should be set to 0V. DIN0 – DIN3 pins have internal pull downs so that the DAC output will default to 0V when it is not used.

**External PWM** - An external PWM signal can be applied to the Enable pin to directly control the duty cycle. A logic 0 turns the transistor off, and a logic 1 turns it on. When using this control method, connect DIN0 – DIN3, LIN, and  $R_{\scriptscriptstyle T}$  to  $V_{\scriptscriptstyle DD}$ . Connect  $C_{\scriptscriptstyle T}$  to GND.

The DAC output and the Linear Control signals are OR'd together. Whichever has the higher value dominates. This allows an analog temperature sensing circuit to override the digital inputs (DIN0 – DIN3) for added system protection.

The following table illustrates the correlation between the digital inputs and LIN voltage to the PWM duty cycle.

Table 1. DAC signal and LIN voltage to Duty Cycle Programming.

| DIN3 | DIN2 | DIN1 | DIN0 | LIN    | Gate Drive<br>Duty Cycle |

|------|------|------|------|--------|--------------------------|

| 0    | 0    | 0    | 0    | 0.500V | 0%*                      |

| 0    | 0    | 0    | 1    | 0.633V | 6.7%                     |

| 0    | 0    | 1    | 0    | 0.766V | 13.3%                    |

| 0    | 0    | 1    | 1    | 0.900V | 20.0%                    |

| 0    | 1    | 0    | 0    | 1.033V | 26.7%                    |

| 0    | 1    | 0    | 1    | 1.167V | 33.3%                    |

| 0    | 1    | 1    | 0    | 1.300V | 40.0%                    |

| 0    | 1    | 1    | 1    | 1.433V | 46.7%                    |

| 1    | 0    | 0    | 0    | 1.567V | 53.3%                    |

| 1    | 0    | 0    | 1    | 1.700V | 60.0%                    |

| 1    | 0    | 1    | 0    | 1.833V | 66.7%                    |

| 1    | 0    | 1    | 1    | 1.967V | 73.3%                    |

| 1    | 1    | 0    | 0    | 2.100V | 80.0%                    |

| 1    | 1    | 0    | 1    | 2.233V | 86.7%                    |

| 1    | 1    | 1    | 0    | 2.367V | 93.3%                    |

| 1    | 1    | 1    | 1    | 2.500V | 100%*                    |

<sup>\*</sup> Guaranteed 0% @ 0000 and 100% @ 1111

## **PWM Fan Drive**

When using direct PWM drive to the fans, it is best to set a low PWM frequency, in the range of 50Hz -120Hz.

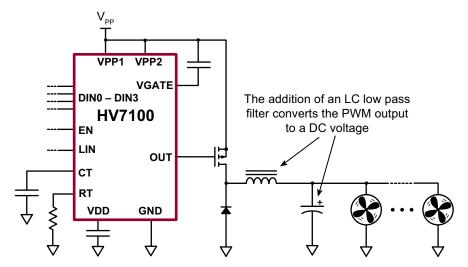

### **DC Fan Drive**

The HV7100 controls the fans with a PWM supply voltage. However, some fans require a steady DC voltage for proper operation. In order for these fans to function properly, an LC low pass filter should be added to cancel the PWM output to a steady DC voltage.

The LC filter also provides another advantage. Some fans draw large spikes of current during start-up and/or during normal operation. Without the LC filter, these current spikes would be drawn directly from the +24 or +48V supply, causing potential conducted EMI problems. The LC filter prevents these spikes from occuring and/or reaching the +24 or +48V supply.

## **Setting a Lower Speed Limit**

When using the linear control input, the digital control inputs may be used to set a lower limit on the duty cycle. This is based on the fact that the higher control setting, linear

or digital, dominates. In the example above, duty cycle is prevented from falling below 25% even if the linear control signal goes to 0V.

# **Pin Description**

| Pin# | Function | Description                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1    | VDD      | Output of an internal linear voltage regulator, which in turn is powered by $V_{pp}$ . It provides power to the internal low-side (ground referenced) circuitry. An external voltage may be applied to this pin, provided it is higher than 3.6V but less than 5.5V. Bypass this pin with a 100nF ceramic capacitor to ground. |  |  |  |  |  |  |

| 2    | LIN      | A DC voltage ranging from 0.5 to 2.5V sets the duty cycle of the gate output from 0% to 100%. This input is immune to moderate noise on the control signal.                                                                                                                                                                    |  |  |  |  |  |  |

| 3    | DIN0     |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 4    | DIN1     | Applying 0000 to 1111 to these logic input pins sets the duty cycle of the gate output from 0 to                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 5    | 5 DIN2   | 100%. A 1-bit increment is equal to 6.67% increment in duty cycle. See Table 1 on page 5                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 6    | DIN3     |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 7    | EN       | Enable input. A logic high applied to this input enables the output.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 8    | GND      | Ground return for all the internal circuitry. This pin must be electrically connected to the ground of the power train and logic return.                                                                                                                                                                                       |  |  |  |  |  |  |

| 9    | СТ       | In conjunction with RT, a capacitor from this pin to ground sets PWM frequency. A triangle wave appears on this pin, with an amplitude of 0.5 - 2.5V and at the PWM frequency.                                                                                                                                                 |  |  |  |  |  |  |

| 10   | RT       | In conjunction with CT, a resistor from this pin to ground sets PWM frequency.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 11   | VGATE    | This is the output pin of the internal linear regulator that biases the gate drive circuit. Bypass with 100nF ceramic capacitor to VPP.                                                                                                                                                                                        |  |  |  |  |  |  |

| 12   | VPP1     | Supply voltage pins. Both must be connected to the supply voltage (+24V/+48V). Connect                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 13   | VPP2     | together as close as possible to the IC. Bypass locally with a ceramic capacitor to ground.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 14   | OUT      | This pin is the output gate driver for an external P-channel power MOSFET.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

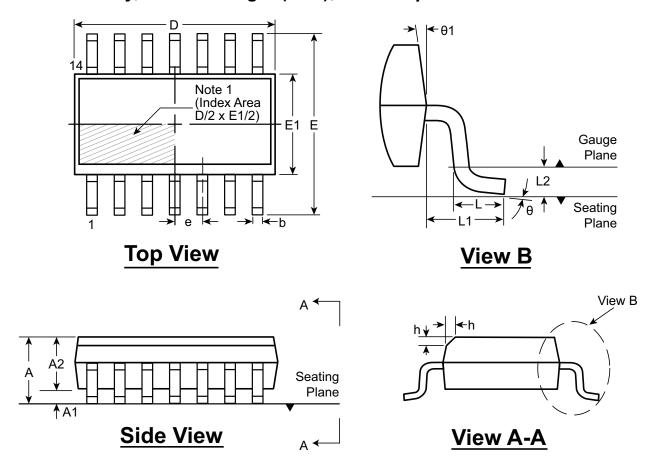

# 14-Lead SOIC (Narrow Body) Package Outline (NG)

8.65x3.90mm body, 1.75mm height (max), 1.27mm pitch

#### Note:

1. This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo     | ol  | Α     | A1   | A2    | b    | D     | E     | E1    | е           | h    | L    | L1          | L2          | θ          | θ1  |

|-----------|-----|-------|------|-------|------|-------|-------|-------|-------------|------|------|-------------|-------------|------------|-----|

| Dimension | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 8.55* | 5.80* | 3.80* |             | 0.25 | 0.40 |             |             | <b>0</b> ° | 5°  |

|           | NOM | -     | -    | -     | -    | 8.65  | 6.00  | 3.90  | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -   |

| ()        | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 8.75* | 6.20* | 4.00* |             | 0.50 | 1.27 |             |             | <b>8</b> º | 15° |

JEDEC Registration MS-012, Variation AB, Issue E, Sept. 2005.

Drawings are not to scale.

Supertex Doc. #: DSPD-14SOICNG, Version F041309.

(The package drawings in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2013 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

многоканальный

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9