# TC35680FSG-002/ TC35681FSG-002

# Bluetooth® Low Energy IC

**Rev 1.0**

The **Bluetooth**® word mark and logos are registered trademarks owned by **Bluetooth** SIG, Inc. Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

# **Table of Contents**

| Preface               |                                                               | 5  |

|-----------------------|---------------------------------------------------------------|----|

| Related               | Documents                                                     | 5  |

| Technica              | al Terms and Abbreviations                                    | 5  |

| 1. Fun                | ction Outlines and Features                                   | 6  |

| 1.1.                  | Function Outlines                                             | 6  |

| 1.2.                  | Features                                                      | 7  |

| 2. Pin                | Assignment                                                    | 10 |

| 2.1.                  | Pin Assignment of TC35680FSG (Top View)                       | 10 |

| 2.2.                  | Pin Assignment of TC35681FSG (Top View)                       | 11 |

| 2.3.                  | Function of Each Pin                                          | 12 |

| 2.4.                  | List of Functions of GPIO Pins                                | 14 |

| 2.4.1.                | Example of GPIO Function Setting                              | 15 |

| 2.4.2.                | Limitation on Assignment of UART Function to GPIO             | 16 |

| 2.4.3.                | Limitation on Assignment of I <sup>2</sup> C Function to GPIO | 16 |

| 2.5.                  | Power Supply Pins                                             | 17 |

| <ol><li>Dev</li></ol> | rice Overview                                                 | 19 |

| 3.1.                  | Internal Block Diagram                                        | 19 |

| 3.1.1.                | Power Supply System                                           | 20 |

| 3.1.2.                | Clock System                                                  | 20 |

| 3.1.3.                | Hardware Start-up Sequence                                    |    |

| 3.2.                  | System Configuration and Operating Mode                       |    |

| 3.3.                  | System Configuration                                          | 23 |

| 3.3.1.                | Standalone System                                             |    |

| 3.3.2.                | Host-Controlled System                                        |    |

| 3.4.                  | Selection and Setting of Operating Mode                       |    |

| 3.4.1.                | HCI Mode                                                      |    |

| 3.4.2.                | Complete Mode                                                 |    |

| 3.4.3.                | User-App Mode                                                 |    |

| 3.5.                  | Start-up Sequence                                             |    |

| 3.5.1.                | Details of Start-up Sequence                                  |    |

| 3.6.                  | •                                                             |    |

| 3.6.1.<br>3.6.2.      | State Transition                                              |    |

| 3.6.2.                | Condition on Transition to Low Power Mode                     |    |

| 3.6.4.                | Condition on Return from Low Power Mode                       |    |

| 3.6.5.                | Acquisition of Wake-up Factor and Return from Low Power Mode  |    |

|                       | ctions                                                        |    |

| 4.1.                  | Bluetooth® Wireless Communication                             |    |

| 4.1.1.                | Supported Functions                                           |    |

| 4.1.2.                | RF Function                                                   |    |

| 4.2.                  | Output Power Setting                                          |    |

| 4.3.                  | Auto-advertise Function                                       | 34 |

| 4.4.                  | Power Supply                                                  | 35 |

| 4.4.1.                | VBAT and VDDIO                                                |    |

| 4.4.2.                | Voltage Step-Down DC/DC Converter and LDO Regulator           |    |

| 4.5.                  | Reset Interface                                               |    |

| 4.5.1.                | Feature                                                       |    |

| 4.5.2.                | Connection Example                                            | 36 |

| 4.6.                  | General-purpose I/O (GPIO) Function                           | 37 |

# TC35680FSG-002/TC35681FSG-002

# **TOSHIBA**

| 4.6.1.             | Feature                                                      | 37 |

|--------------------|--------------------------------------------------------------|----|

| 4.6.2.             | GPIO Pin Setting                                             |    |

| 4.6.3.             | General-purpose Input Function                               |    |

| 4.6.4.             | General-purpose Output Function                              |    |

| 4.6.5.             | I/O Latch Function                                           |    |

| 4.6.6.             | Interrupt Function                                           |    |

| 4.6.6.1.           | Interrupt in Active Mode                                     |    |

| 4.6.6.2.           | Wake-up in Sleep Mode or Backup Mode                         |    |

| 4.6.6.3.           | Wake-up in Deep Sleep Mode (GPIO0 and GPIO15 Wake-up)        |    |

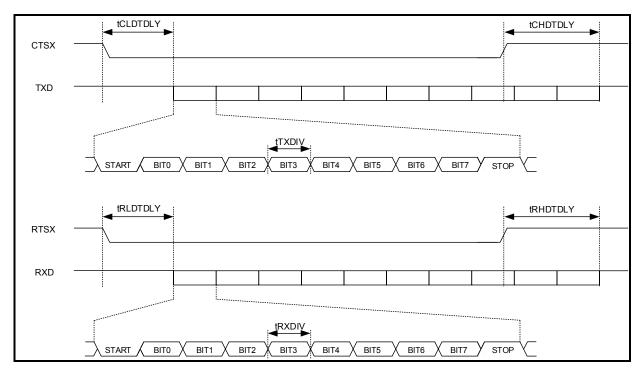

|                    | RT Interface                                                 |    |

| 4.7.1.             | Feature                                                      |    |

| 4.7.1.             | Connection Example (Host Interface in HCl Mode)              |    |

| 4.7.2.             | Frame Format                                                 |    |

| 4.7.4.             | Flow Control Function                                        |    |

| 4.7.5.             | Baud Rate Setting                                            |    |

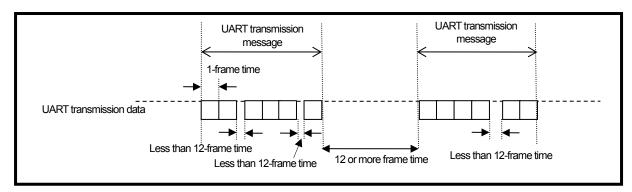

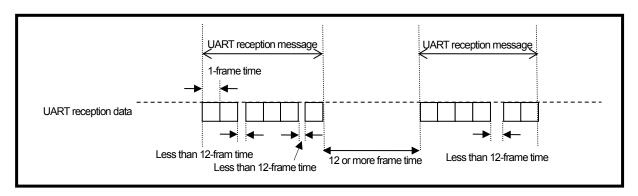

| 4.7.6.             | UART Message Recognition Function (Spacing between Messages) |    |

| 4.7.7.             | Error Detection Function                                     |    |

| 4.7.7.<br>4.7.7.1. | Reception Timeout Error                                      |    |

|                    | Reception Overrun Error                                      |    |

| 4.7.7.2.           | ·                                                            |    |

| 4.7.7.3.           | Reception Framing Error                                      |    |

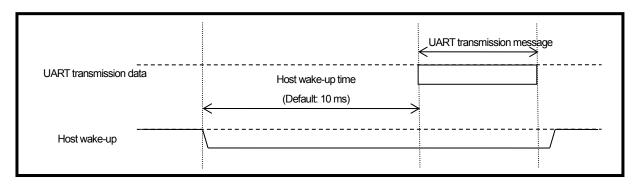

| 4.7.8.             | Host Wake-up Function                                        |    |

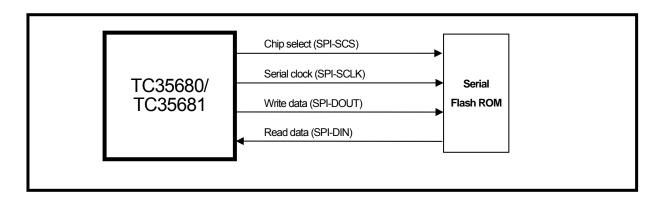

|                    | I Interface                                                  |    |

| 4.8.1.             | Feature                                                      |    |

| 4.8.2.             | Connection Example                                           |    |

| 4.8.3.             | Frame Format                                                 |    |

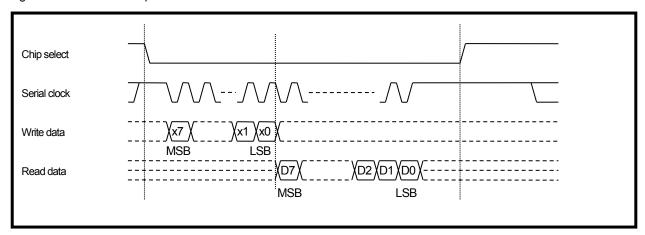

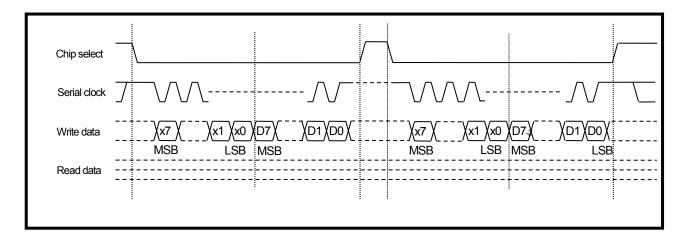

| 4.8.4.             | SPI Clock                                                    |    |

|                    | Interface                                                    |    |

| 4.9.1.             | Feature                                                      |    |

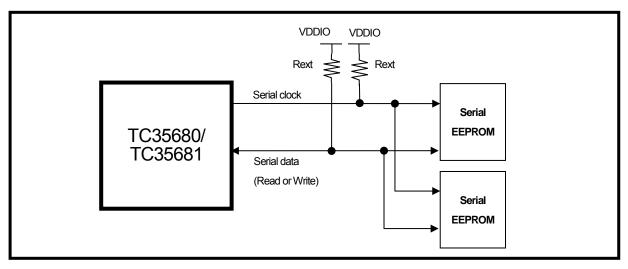

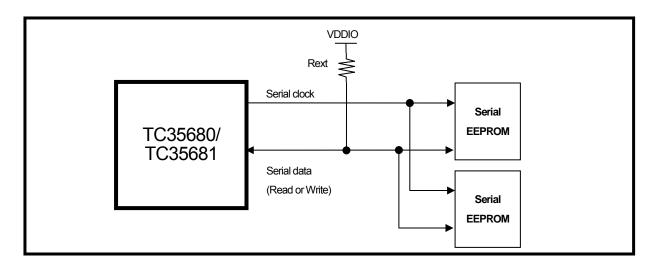

| 4.9.2.             | Connection Example                                           | 54 |

| 4.9.3.             | Value of External Pull-up Resistor                           |    |

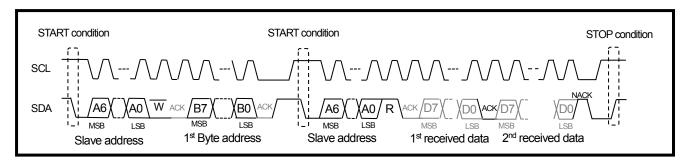

| 4.9.4.             | Transfer Format                                              |    |

| 4.10. PW           | /M Interface                                                 |    |

| 4.10.1.            | Feature                                                      |    |

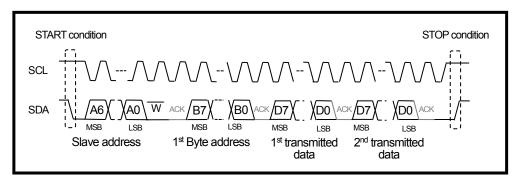

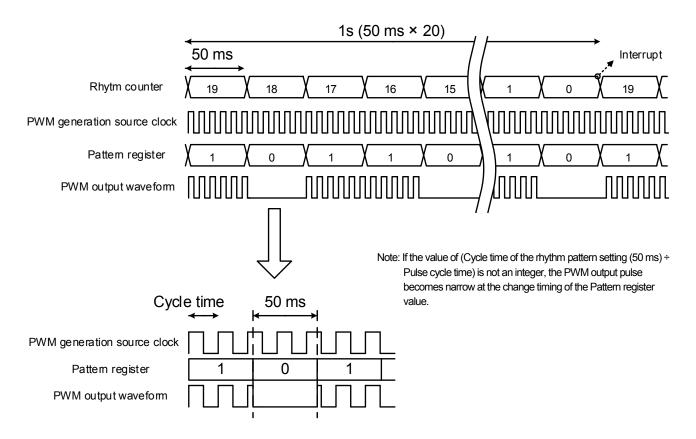

| 4.10.2.            | Pulse Generation Function                                    | 57 |

| 4.10.3.            | Rhythm Function (Output Masking)                             |    |

| 4.11. AD           | C (AD Converter)                                             | 59 |

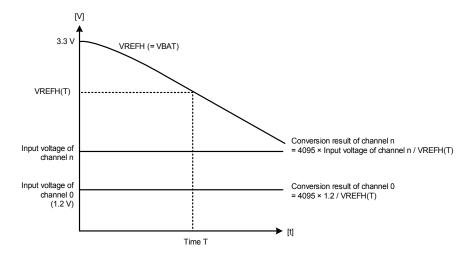

| 4.11.1.            | Feature                                                      | 59 |

| 4.11.2.            | Function                                                     | 59 |

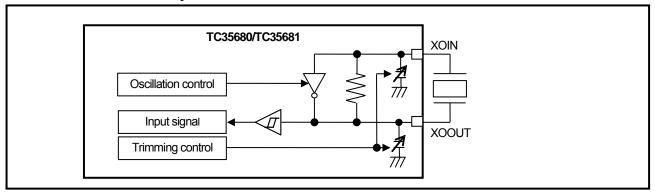

| 4.12. Ref          | ference Clock Interface                                      | 61 |

| 4.12.1.            | Feature                                                      | 61 |

| 4.12.2.            | Adjustment of Oscillation Frequency of Reference Clock       | 61 |

| 4.12.3.            | Low Power Mode and Adjustment Value                          | 61 |

| 4.12.4.            | Connection of Crystal Resonator                              | 62 |

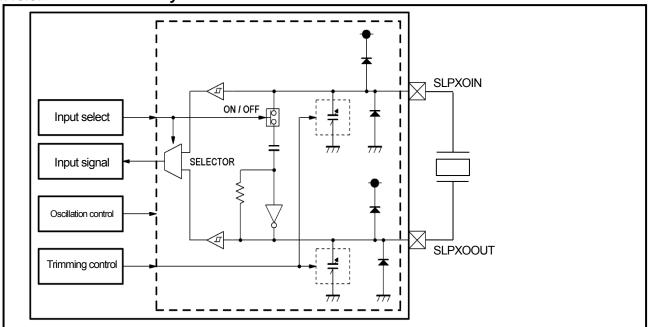

| 4.13. Sle          | ep Clock Interface                                           | 63 |

| 4.13.1.            | Feature                                                      | 63 |

| 4.13.2.            | Selection of Sleep Clock Source                              | 63 |

| 4.13.3.            | Use of Crystal Resonator                                     | 63 |

| 4.13.4.            | Adjustment of Oscillation Frequency of Sleep Clock           | 64 |

| 4.13.5.            | Connection of Crystal Resonator                              | 64 |

| 4.13.6.            | Use of External Crystal Oscillator                           | 64 |

| 4.13.7.            | Built-in Silicon Oscillator (SiOSC)                          | 65 |

# TC35680FSG-002/TC35681FSG-002

# **TOSHIBA**

| 4.14.    | Sleep Clock Output Function                                                                             | 66      |

|----------|---------------------------------------------------------------------------------------------------------|---------|

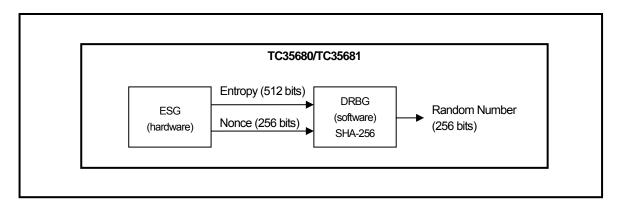

| 4.15.    | TRNG (True Random Number Generator) Function                                                            | 66      |

| 4.16.    | Auto-patch Function                                                                                     | 67      |

| 4.17.    | Patch Function                                                                                          | 67      |

| 4.18.    | CPU                                                                                                     | 67      |

| 5. Ele   | ctrical Characteristics (TC35680FSG/TC35681FSG)                                                         | 68      |

| 5.1.     | Absolute Maximum Ratings                                                                                | 68      |

| 5.2.     | Operating Condition (Design Target Value)                                                               | 69      |

| 5.3.     | DC Characteristics                                                                                      | 70      |

| 5.3.1.   | Current Consumption (Design Target Value)                                                               | 70      |

| 5.4.     | Built-in Regulator Characteristics                                                                      | 72      |

| 5.5.     | ADC Characteristics                                                                                     | 72      |

| 5.6.     | RF Characteristics (Design Target Values)                                                               | 73      |

| 5.7.     | AC Characteristics (Design Target Values)                                                               | 76      |

| 5.7.1.   | UART Interface                                                                                          | 76      |

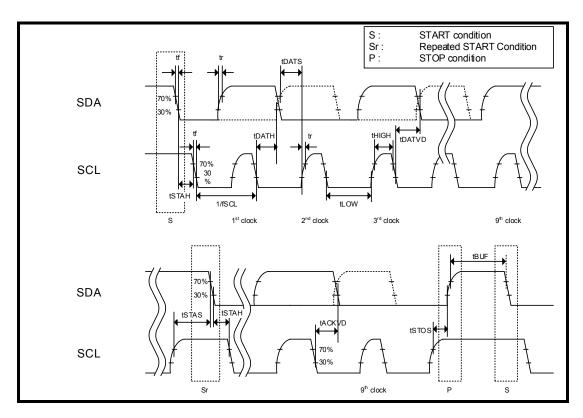

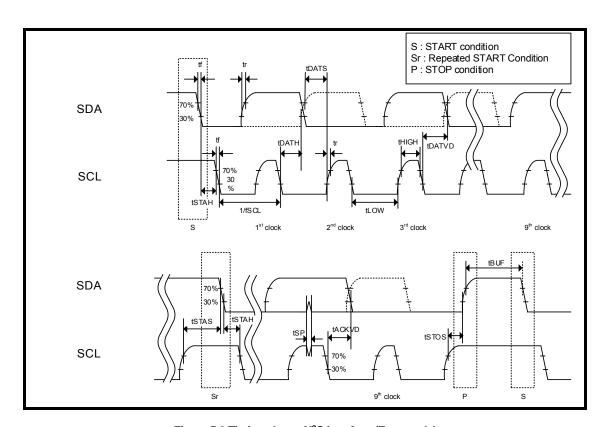

| 5.7.2.   | I <sup>2</sup> C Interface                                                                              | 77      |

| 5.7.2    | 2.1. Standard Mode                                                                                      | 77      |

| 5.7.2    | 2.2. Fast mode                                                                                          | 78      |

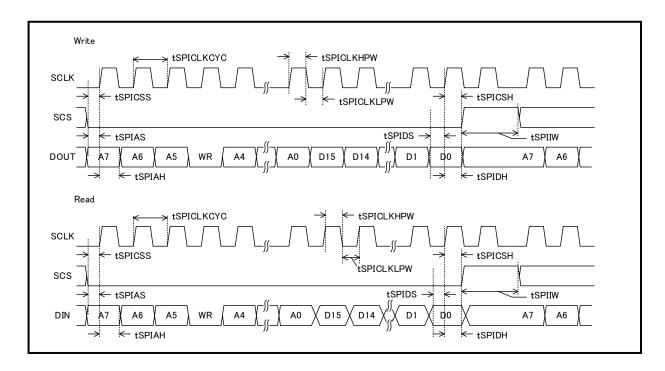

| 5.7.3.   | SPI Interface                                                                                           |         |

| 5.8.     | Characteristics of Flash Memory (Only TC35680)                                                          |         |

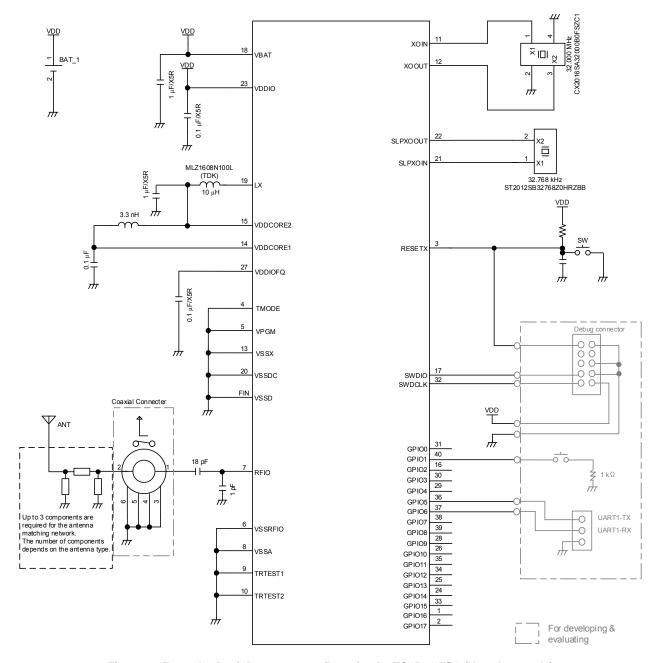

| 6. Sys   | tem Configuration Example                                                                               | 81      |

| 6.1.     | Configuration Example for User-App Mode (TC35680)                                                       | 81      |

| 6.2.     | Configuration Example for HCI Mode (TC35680)                                                            | 82      |

| 6.3.     | Connection Example for User-App Mode (TC35681 downloads a user application program from an external EEF | PROM)83 |

| 6.4.     | Connection Example for User-App Mode (TC35681 downloads a user application program from a host)         | 84      |

| 6.5.     | Connection Example for HCI Mode (TC35681)                                                               | 85      |

| 6.6.     | External Circuit Configuration for LDO Regulator (Common to TC35680 and TC35681)                        |         |

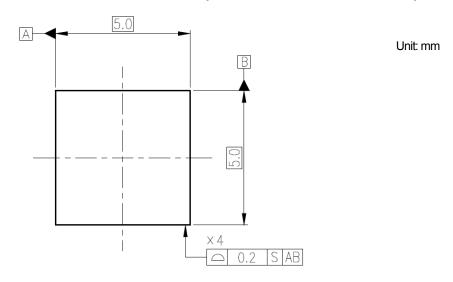

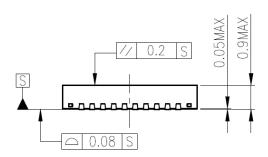

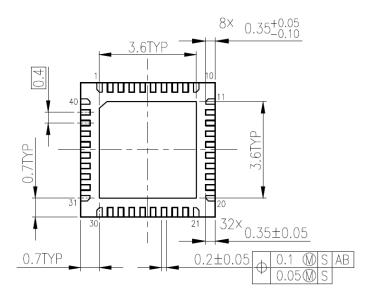

| 7. Pac   | kage                                                                                                    | 87      |

| 7.1.     | Package Outline of TC35680FSG/TC35681FSG (P-VQFN40-0505-0.40-005/F01)                                   | 87      |

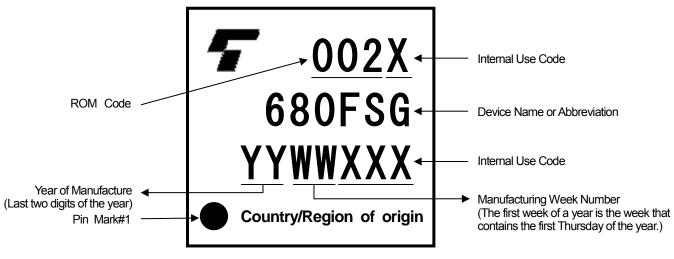

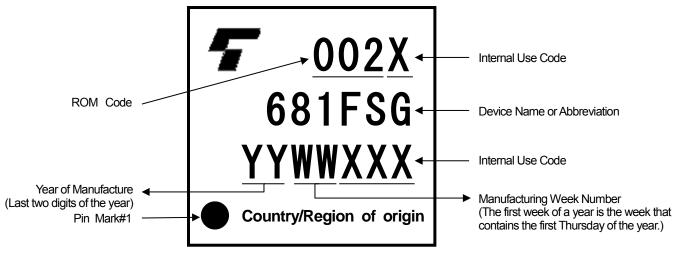

| 7.2.     | Marking                                                                                                 | 88      |

| 7.2.1.   | Marking of TC35680FSG                                                                                   | 88      |

| 7.2.2.   | Marking of TC35681FSG                                                                                   |         |

|          | of Products                                                                                             |         |

| 9. Rev   | vision History                                                                                          | 90      |

| DESTRICT | TONS ON DOOD ICT USE                                                                                    | 01      |

#### **Preface**

# **Related Documents**

- TC35680/TC35681 Hardware Application Note

- TC35680/TC35681-002 Software Development Startup Guide

- TC35680/TC35681 Register description

- TC35680/TC35681-002 Command Document

- TC35680/TC35681-002 Programming Guide

- TC35680/TC35681-002 Known Issues

- Bluetooth® Core Specification

#### **Technical Terms and Abbreviations**

The following technical terms and abbreviations are used in this document.

| Terms or Abbreviations    | Description                                                                                                                                                                                                                                                                           |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Active mode               | Normal operating mode. The packet transmission and reception procedure of the <b>Bluetooth</b> ® connection and the other internal CPU activities are executed in this mode. Refer to Section 3.6.                                                                                    |  |  |

| Sleep mode                | One of the low power modes. The reference clock stops to save power. The <b>Bluetooth® connection</b> is kept in this mode. Refer to Section 3.6.                                                                                                                                     |  |  |

| Backup mode               | One of the low power modes. This mode consumes same or less power than the Sleep mode. The power supply of the CPU stops as well as the reference clock. Refer to Section 3.6.                                                                                                        |  |  |

| Complete mode             | One of the operating modes. A host operates this device using TCU commands (Control API in the GATT/SM layer). Refer to Section 3.4.                                                                                                                                                  |  |  |

| Deep Sleep mode           | One of the low power modes. This mode saves more power than the Backup mode. The Sleep clock stops as well as the power supply of the CPU and the reference clock. Refer to Section 3.6.                                                                                              |  |  |

| HCI mode                  | One of the operating modes. A host operates this device using HCl commands. Refer to Section 3.4.                                                                                                                                                                                     |  |  |

| PMU                       | Power Management Unit. Integrated PMU controls the power save procedure of this device. In order to save power, it switches the built-in DC/DC converter and the LDO regulator properly, and also controls the output voltage at the same time. Refer to Section 3.1 and Section 3.6. |  |  |

| User-App mode             | One of the operating modes. A user application is executed by the built-in CPU in this device. Refer to Section 3.4.                                                                                                                                                                  |  |  |

| Auto-Advertising function | Advertising packets are transmitted without software control in the Backup mode. This function enables the packet transmission even in the low power mode.                                                                                                                            |  |  |

5 2018-09-13

#### 1. Function Outlines and Features

#### 1.1. Function Outlines

TC35680FSG/TC35681FSG series (hereafter, TC35680/TC35681 series) are compliant with 2.4 GHz wireless communication **Bluetooth**® Low Energy Ver.5.0 specification. Each device has an MCU based on Arm® Cortex-M0® processor and integrates RF analog circuit and baseband digital circuits. The following functions in the **Bluetooth**® core specifications are supported; the LE Long Range feature, LE 2-Mbps feature, HCI (Host Control Interface) feature, Low Energy GATT Profile feature, and others.

The TC35680/TC35681 series line-up is as follows:

- ✓ TC35680FSG (hereafter, TC35680): Flash memory is included to store user application program.

- ✓ TC35681FSG (hereafter, TC35681): Flash memory is not included.

TC35680/TC35681 series support both controlled by an external CPU and standalone operation.

Table 1-1 shows the main application and features of each device.

Table 1-1 Applications and features of TC35680/TC35681 series

| Product                                      | TC35680FSG                              | TC35681FSG                                                                  |  |

|----------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------|--|

| Main application                             | General-purpose (Note 1)     Standalone | General-purpose (Note 1)     Standalone (Note 2)     Host-controlled system |  |

| Flash memory                                 | Built-in                                | None                                                                        |  |

| No. 27 pin                                   | VDDIOFQ                                 | VSSD1                                                                       |  |

| Minimum VBAT operation voltage (VBATopr)     | 1.9 V                                   | 1.8 V (-40 to 105°C)                                                        |  |

| Ambient temperature                          | -40°C to +85°C                          | 2.0 V (-40 to 120°C)                                                        |  |

| Number of General-purpose I/O (GPIO)         | 18                                      |                                                                             |  |

| Number of UART channels<br>(Note 3)          | 2                                       |                                                                             |  |

| Number of I <sup>2</sup> C channels (Note 3) |                                         | 2                                                                           |  |

| Number of SPI channels (Note 3)              |                                         | 2                                                                           |  |

| Number of AD Converter channels (Note 3)     |                                         | 5                                                                           |  |

| Number of PWM channels<br>(Note 3)           | 4                                       |                                                                             |  |

| Sleep clock output function (Note 3)         | Yes                                     |                                                                             |  |

| Package                                      | 5.0 mm × 5                              | QFN40<br>5.0 mm × 5.0 mm × 0.9 mm<br>0.4-mm pitch                           |  |

Note 1: Except "UNINTENDED USE" described in "RESTRICTIONS ON PRODUCT USE"

Note 2: An external EEPROM is necessary in the standalone system.

Note 3: These pins are shared with the GPIO pins.

#### 1.2. Features

- Wireless communication function

- Compliant with Bluetooth® Low Energy Ver.5.0 specification.

- Built-in Bluetooth® baseband circuit

- Built-in Bluetooth® RF circuit

- Maximum output power: +8 dBm

- Maximum RX sensitivity: -105.0 dBm (in case of Coded PHY and S = 8)

- RSSI accuracy: ±2 dB (in case of -90 to -10 dBm input)

- HCl commands/Extended HCl commands (implemented in the mask ROM)

- Control API in GATT/SM layer (TCU commands: <u>Toshiba Command Unit</u>) (implemented in the mask ROM)

- Auto-advertising feature

- Output power setting feature

- Microcontroller unit

- Built-in Arm® Cortex®-M0 processor (Maximum operating frequency is 32 MHz.)

- Built-in mask ROM

- Boot loader

- API for the hardware control

- Bluetooth® wireless function API

- Bluetooth® protocol stack

- > Built-in retention SRAM (User area is 76 KB out of total 144 KB.)

- > Built-in serial Flash memory (TC35680 only)

- Memory capacity: 128 KB

- Sector size: 4 KB

- Endurance: 100,000 times

- Interface, AD converter, and Debug function

- ➤ General-purpose I/O (GPIO) (18 pins)

- General-purpose serial interfaces

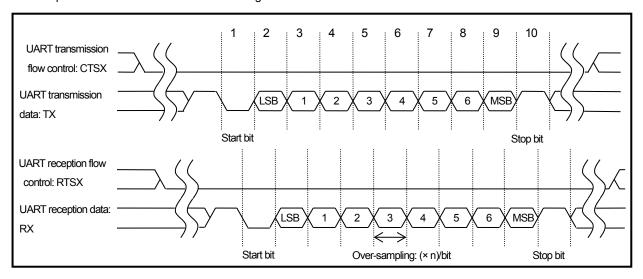

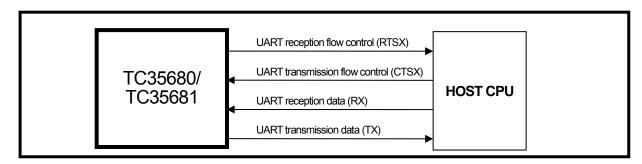

- UART interface (2 channels. Shared with the GPIO pins.)

- ➤ HCI mode: One channel is used as a host interface (9600 bps to 921.6 kbps)

- User-App mode: 600 to 2000 kbps (Maximum baudrate may be 2000 kbps or less and depends on user-application program.)

- SPI interface (2 channels. Shared with the GPIO pins.)

- I<sup>2</sup>C interface (2 channels. Shared with the GPIO pins.)

- > TC35681 uses one channel as the interface to the EEPROM for User-App mode.

- > PWM interface (4 channels. Shared with the GPIO pins.)

- Pulse generation function

- "Rhythm function" (function to mask a pulse signal)

- AD converter (ADC)

- General-purpose voltage measurement (5 channels. Shared with the GPIO pins.)

- Power supply voltage (VBAT) measurement (1 channel. Connected internally.)

- Interface for Emulator debug control

- SWD (Serial Wire Debug): 2-wire system (1 channel)

- Clock

- > Reference clock (32 MHz)

- Built-in crystal oscillator with a frequency adjustment function

- ➤ Sleep clock (32.768 kHz)

- Built-in crystal oscillator with a frequency adjustment function

- External clock input is supported.

- Built-in silicon oscillator (SiOSC)

- Sleep clock output function (Shared with the GPIO pins.)

#### Power supply

- Power supply circuit

- Support for wide range of the input power voltage

- DC/DC converter and LDO regulator are integrated.

- Built-in Power Management Unit for the low power consumption function.

- Independent power pins for the I/O circuits (VDDIO)

#### System function

- 2 system configurations are supported.

- Host-controlled system (A host CPU controls this device.)

- Standalone system (The operation of this device is controlled by its own CPU.)

- 3 operating modes are supported.

- HCI mode

- Control by HCl and Extended HCl commands

- User application (firmware) programming

- For radio certification tests in different countries and regions

- For Bluetooth® qualification test

- > For other RF tests

- Complete mode

- Control of this device by the TCU commands (Control commands in the GATT/SM layer)

- User-App mode

- Download function of a user application program to this device

- Download from the built-in Flash memory or host CPU (TC35680)

- ♦ Download from an external EEPROM or a host CPU (TC35681)

- Execution of a user application program

- Low power system feature

- 3 low power modes (Sleep, Backup, and Deep Sleep)

- Support for Interrupts

- Patch support

- Patch function (maximum 4)

- Auto-patch function

- DMA support

- Built-in 7-channel DMA controller (2 to 6 channels are available for a user.)

- Clock and Timer

- RTC

- RTC function with the accuracy of sleep clock frequency

- Clock and Calendar function: YY/MM/DD hh:mm:ss (24-hour clock) and day of the week

- Alarm function: Alarm setting by hh:mm and either a date or a day, and an interrupt by the alarm generation

- Leap year function (the exceptional procedure for every 100 years is not supported.)

- RTC is working even in the Sleep and Backup modes.

- Timer

- BCTimer

- > 3-channel hardware timer (One channel is dedicated to the system.)

- 16-bit counter which can be loaded automatically every 1 μs at minimum.

- The count of the timer stops in low power mode.

- GTimer

- 1-channel hardware timer

- Built-in prescaler to divide the clock (1 to 1024 division). The minimum interval is 38 ns to 39 μs.

- > 16-bit counter which can be loaded automatically.

- The count of the timer stops in low power mode.

- OS timer (1-second timer and 1-ms timer)

- Timer controlled by the OS

- Watchdog timer (WDT) function

8 2018-09-13

#### ■ Security

- > True Random Number Generator (TRNG)

- A random number of 256 bits at maximum is generated by DRBG and ESG.

- Compliant with NIST SP800-22 and BSI random number test.

- Hardware encryption engine (AES128, only encryption)

#### Package

TC35680FSG/TC35681FSG: QFN package [40 pins, 5 mm x 5 mm, 0.4-mm pitch, and 0.9-mm thickness]

9 2018-09-13

# 2. Pin Assignment

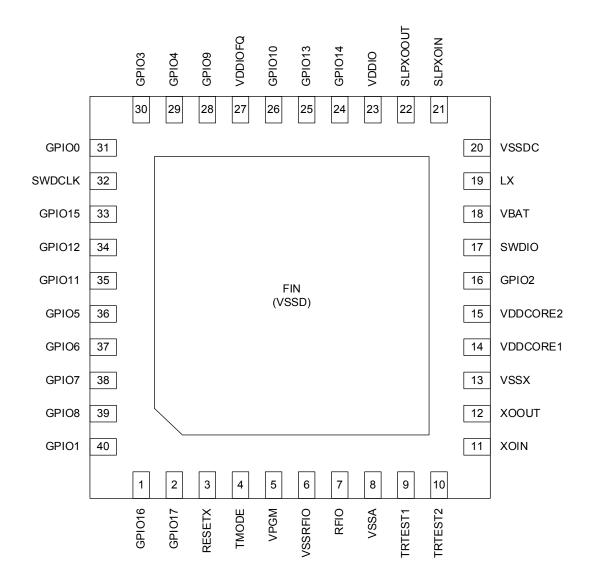

# 2.1. Pin Assignment of TC35680FSG (Top View)

Figure 2-1 Pin assignment of TC35680FSG (Top view)

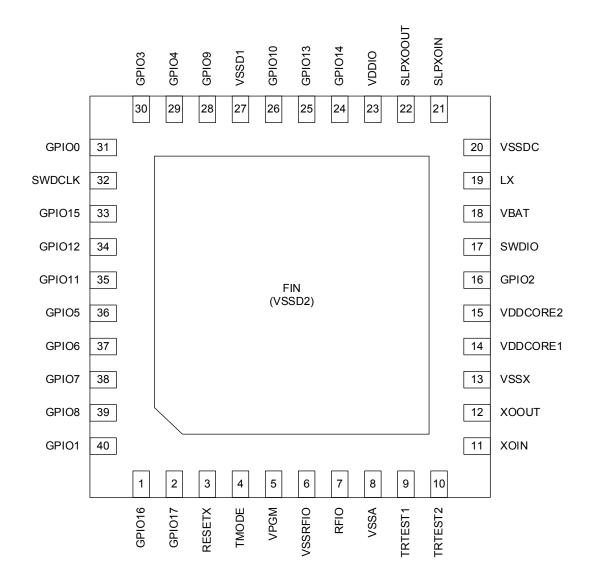

# 2.2. Pin Assignment of TC35681FSG (Top View)

Figure 2-2 Pin assignment of TC35681FSG (Top view)

11

# 2.3. Function of Each Pin

The attribute, the status as output or input, and other functions of each pin are shown in Table 2-1.

The power supply pins are shown in Table 2-6.

Table 2-1 Function of each pin

|            | Pin No. | Attribute          |                                                                             |

|------------|---------|--------------------|-----------------------------------------------------------------------------|

| Pin name   | OFN     | Power supply group | Description                                                                 |

| 1 III IIII | QFN     | Signal direction   | Description                                                                 |

|            | Package | I/O Type           |                                                                             |

| RESETX     | 3       | VDDIO              | Hardware reset input pin.                                                   |

|            |         | IN                 | Low level asserts the reset.                                                |

|            |         | Schmitt trigger    |                                                                             |

| XOIN       | 11      | VDDCORE1           | Input pin for the reference clock oscillation.                              |

|            |         | IN                 | A 32-MHz crystal resonator with accuracy of $\pm$ 50 ppm or less should     |

|            |         | osc                | be connected to the XOIN pin and the XOOUT pin.                             |

|            |         |                    | The crystal oscillation circuit includes a variable capacitor (a capacitor  |

|            |         |                    | array) to adjust the oscillation frequency.                                 |

| XOOUT      | 12      | VDDCORE1           | Output (feedback) pin for the reference clock oscillation.                  |

|            |         | OUT                |                                                                             |

|            |         | osc                |                                                                             |

| SLPXOIN    | 21      | VDDIO              | Input pin for the sleep clock oscillation by a crystal resonator.           |

|            |         | IN                 | A 32.768-kHz crystal resonator with accuracy of ± 500 ppm or less           |

|            |         | osc                | should be connected to the SLPXOIN pin and the SLPXOOUT pin.                |

|            |         |                    | The crystal oscillation circuit includes a variable capacitor (a capacitor  |

|            |         |                    | array) to adjust the oscillation frequency.                                 |

|            |         |                    | When an external clock is used, the clock should be input to this pin.      |

| SLPXOOUT   | 22      | VDDIO              | Output (feedback) pin for the 32.768-kHz oscillation.                       |

|            |         | OUT                |                                                                             |

|            |         | OSC                |                                                                             |

| RFIO       | 7       | VDDCORE1           | RF signal input and output pin.                                             |

|            |         | IN/OUT             | The impedance matching of 50 $\Omega$ can be done by connecting a proper    |

|            |         | Analog             | capacitor between the RFIO pin and GND.                                     |

|            |         |                    | When this pin is connected to an antenna for communication, a series        |

|            |         |                    | capacitor should be connected, because the signal of this pin has a DC      |

|            |         |                    | bias. For the details, refer to the "Hardware Application Note" of this     |

|            |         |                    | device.                                                                     |

| GPIO0      | 31      | VDDIO              | General-purpose I/O pins.                                                   |

| GPIO15     | 33      | IN/OUT             | Following functions can be set by software;                                 |

|            |         | Pull-up/Pull-down  | ✓ Switch as input or output.                                                |

|            |         | resistors          | ✓ Connection or disconnection of a pull-up and a pull-down                  |

|            |         | Schmitt trigger    | resistors (Note 1)                                                          |

|            |         |                    | ✓ Selection of output drivability.                                          |

|            |         |                    | ✓ Setting of an interrupt.                                                  |

|            |         |                    | The interrupt can also be used to wake up from the Deep Sleep mode          |

|            |         |                    | to the Active mode.                                                         |

|            |         |                    | For details of the function assignment, the low power consumption           |

|            |         |                    | function, and the interrupt, refer to Section 2.4, Section 3.6, and Section |

|            |         |                    | 4.6, respectively.                                                          |

|          | Pin No. | Attribute          |                                                                             |

|----------|---------|--------------------|-----------------------------------------------------------------------------|

| Pin name | QFN     | Power supply group | Description                                                                 |

|          | Package | Signal direction   |                                                                             |

|          |         | I/O Type           |                                                                             |

| GPIO1    | 40      | VDDIO              | General-purpose I/O pins.                                                   |

| GPIO2    | 16      | IN/OUT             | Following functions can be set by software;                                 |

| GPIO5    | 36      | Pull-up/Pull-down  | ✓ Switch as input or output.                                                |

| GPIO6    | 37      | resistors          | ✓ Connection or disconnection of a pull-up and a pull-down                  |

| GPIO7    | 38      | Schmitt trigger    | resistors (Note 1)                                                          |

| GPIO8    | 39      |                    | ✓ Selection of output drivability.                                          |

| GPIO11   | 35      |                    | ✓ Setting of an interrupt.                                                  |

| GPIO12   | 34      |                    | For details of the function assignment, the low power consumption           |

| GPIO13   | 25      |                    | function, and the interrupt, refer to Section 2.4, Section 3.6, and Section |

| GPIO16   | 1       |                    | 4.6, respectively.                                                          |

| GPIO17   | 2       |                    |                                                                             |

| GPIO3    | 30      | VDDIO              | ADC input and general-purpose I/O pins.                                     |

| GPIO4    | 29      | IN/OUT             | Following functions can be set by software;                                 |

| GPIO9    | 28      | Pull-up/Pull-down  | ✓ Switch of input or output.                                                |

| GPIO10   | 26      | resistors          | ✓ Connection or disconnection of a pull-up and a pull-down                  |

| GPIO14   | 24      | Schmitt trigger    | resistors (Note 1)                                                          |

|          |         |                    | ✓ Selection of output drivability.                                          |

|          |         |                    | ✓ Setting of an interrupt.                                                  |

|          |         |                    | ✓ ADC input                                                                 |

|          |         |                    | For the details of the function assignment, the low power consumption       |

|          |         |                    | function, the interrupt, and the ADC, refer to Section 2.4, Section 3.6,    |

|          |         |                    | Section 4.6, and Section 4.11, respectively.                                |

| SWDCLK   | 32      | VDDIO              | SWD clock pin.                                                              |

|          |         | IN                 | Input pin of the Serial Wire Debug clock.                                   |

|          |         | Pull-up/Pull-down  | When the function is not used, this pin should be open.                     |

|          |         | resistors          |                                                                             |

|          |         | Schmitt trigger    |                                                                             |

| SWDIO    | 17      | VDDIO              | SWD data pin or Operating mode switching pin.                               |

|          |         | IN/OUT             | Input or output data pin for the Serial Wire Debug.                         |

|          |         | Pull-up/Pull-down  | When the functions of this pin are not used, this pin should be open.       |

|          |         | resistors          | This pin is also used to switch an operating mode. For the details of       |

|          |         | Schmitt trigger    | switching the operation mode, refer to Section 3.4.                         |

| TMODE    | 4       | VDDIO              | Test setting pin.                                                           |

|          |         | IN                 | This pin is used for a manufacturing test. It should be connected to GND    |

|          |         | Schmitt trigger    | when this device is used.                                                   |

| TRTEST1  | 9       | VDDCORE1           | Test pins for analog.                                                       |

| TRTEST2  | 10      | IN/OUT             | This pin is used for a manufacturing test. It should be connected to GND    |

|          |         | Analog             | when this device is used.                                                   |

| <u></u>  |         |                    |                                                                             |

Note 1: The values of the built-in pull-up and pull-down resistors vary widely; about 20 k $\Omega$  to 100 k $\Omega$ .

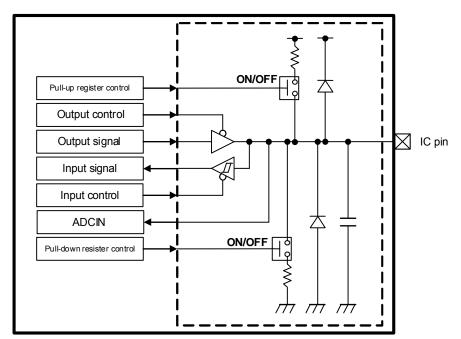

#### 2.4. List of Functions of GPIO Pins

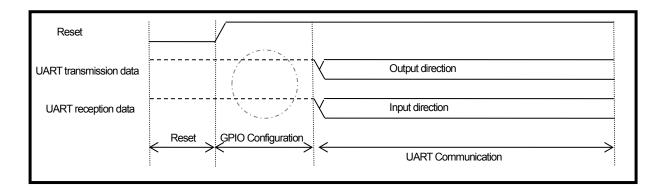

Some GPIO pins are used as multiplexed function pins. They have multiple functions such as a serial interface and others as well as a general-purpose I/O. The basic setting of the assignment of the function is done at boot timing by the built-in firmware program in the mask ROM. After boot up, a user application or a proper command from the host CPU can set expected functions to the corresponding GPIO pins.

Table 2-2 shows the status of each GPIO pin before the built-in firmware finishes the boot setting. And the functions which can be assigned to each GPIO by a user application program are shown in the same table. Unused pins can be open. "Disable" in the table means that both the input and output functions are disabled.

Some examples of the function setting are shown in Table 2-3.

Since it is not possible to assign one function to multiple GPIO pins simultaneously, care should be taken in function assignment for GPIO pins.

For details of the GPIO function, refer also to Section 4.6.

**Table 2-2 Multiple functions of GPIO**

| Pin name          | I/O function/Pi          | n status                                           | Function 4                | Function 2          | Function 2                | Function 4        | ADC           |

|-------------------|--------------------------|----------------------------------------------------|---------------------------|---------------------|---------------------------|-------------------|---------------|

| (Function 0)      | During reset             | Boot setting                                       | Function 1                | Function 2          | Function 3                | Function 4        | ADC           |

| GPIO0             | Disable/Hi-Z             |                                                    | _                         | _                   | _                         | _                 | _             |

| GPIO1<br>(Note 1) | Disable/<br>Pull-up      | Input/Pull-up<br>or<br>Input/Pull-down<br>(Note 2) | _                         | _                   | _                         | _                 | _             |

| GPIO2             | Disable/Pull-u           | р                                                  | PWM1 output               | _                   | _                         | _                 |               |

| GPIO3             | Disable/Hi-Z             |                                                    | PWM2 output               | SPI-DOUT1 output    | _                         | _                 | ADC1 input    |

| GPIO4             | Disable/Hi-Z             |                                                    | PWM3 output               | SPI-DIN1<br>input   | _                         | _                 | ADC2<br>input |

| GPIO5             | Disable/Pull-u           | p (Note 3)                                         | UART1-TX output           | _                   | _                         | _                 | _             |

| GPIO6             | Disable/Pull-u           | p (Note 4)                                         | UART1-RX input            | _                   | _                         | _                 | _             |

| GPIO7             | Disable/Pull-u           | p (Note 5)                                         | I2C-SCL1 input and output | _                   | SPI-SCS1 input and output | UART1-RTSX output | _             |

| GPIO8             | Disable/Pull-up (Note 5) |                                                    | I2C-SDA1 input and output | _                   | SPI-SCLK1 output          | UART1-CTSX input  | _             |

| GPIO9             | Disable/Hi-Z             |                                                    | I2C-SCL2 input and output | _                   | _                         | _                 | ADC3 input    |

| GPIO10            | Disable/Hi-Z             |                                                    | I2C-SDA2 input and output | _                   | _                         | _                 | ADC4 input    |

| GPIO11            | Disable/Pull-u           | p                                                  | I2C-SCL2 input and output | SPI-DOUT2<br>output | _                         | _                 | _             |

| GPIO12            | Disable/Pull-u           | p                                                  | I2C-SDA2 input and output | SPI-DIN2 input      | _                         | _                 | _             |

| GPIO13            | Disable/Pull-up          |                                                    | UART1-RTSX output         | PWM0<br>output      | SPI-SCS2 input and output | UART2-RTSX output | _             |

| GPIO14            | Disable/Hi-Z             |                                                    | UART1-CTSX input          | SLEEPCLK output     | SPI-SCLK2<br>output       | UART2-CTSX input  | ADC5 input    |

| GPIO15            | Disable/Hi-Z             |                                                    | _                         | _                   | _                         | _                 | _             |

| GPIO16            | Disable/Pull-u           | p                                                  | UART2-TX output           | _                   | _                         | _                 | _             |

| GPIO17            | Disable/Pull-u           | p                                                  | UART2-RX input            | _                   | _                         | _                 | _             |

Note 1: This pin is used to switch an operating mode at the reset deassertion.

Note 2: "Input/Pull-up" in the User-App mode, and "Input/Pull-down" in the HCI mode or the Complete mode.

Note 3: "Disable/Pull-up" in the User-App mode, and "Output" in the HCI mode and the Complete mode. Function 1 is assigned.

Note 4: "Disable/Pull-up" in the User-App mode, and "Input/Pull-up" in the HCI mode and the Complete mode. Function 1 is assigned.

Note 5: When TC35681 is used, Function 1 is assigned in the User-App mode.

# 2.4.1. Example of GPIO Function Setting

Table 2-3 shows examples of the GPIO function settings.

Table 2-3 Example of GPIO function setting (QFN package)

| Function setting | Function setting 1 | Function setting 2          | Function setting 3          | Function setting 4          | Function setting 5          |

|------------------|--------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Application      | UART: 1 channel    | UART: 1 channel             | UART: 1 channel             | UART: 1 channel             | UART: 1 channel             |

|                  | (4-wire system)    | (4-wire system)             | (4-wire system)             | (4-wire system)             | (2-wire system)             |

|                  | UART: 1 channel    | I <sup>2</sup> C: 1 channel | I <sup>2</sup> C: 1 channel | I <sup>2</sup> C: 1 channel | I <sup>2</sup> C: 1 channel |

|                  | (2-wire system)    | ADC: 2 channels             | ADC: 2 channels             | SPI: 1 channel              |                             |

|                  | SPI: 1 channel     | PWM: 3 channels             | PWM: 3 channels             | ADC: 2 channels             |                             |

|                  | ADC: 2 channels    |                             |                             |                             |                             |

|                  | PWM: 3 channels    |                             |                             |                             |                             |

| GPIO0            | GPIO0              | GPIO0                       | GPIO0                       | GPIO0                       | GPIO0                       |

| GPIO1            | GPIO1              | GPIO1                       | GPIO1                       | GPIO1                       | GPIO1                       |

| GPIO2            | PWM1               | PWM1                        | PWM1                        | GPIO2                       | GPIO2                       |

| GPIO3            | PWM2               | PWM2                        | PWM2                        | SPI-DOUT1                   | GPIO3                       |

| GPIO4            | PWM3               | PWM3                        | PWM3                        | SPI-DIN1                    | GPIO4                       |

| GPIO5            | UART1-TX           | UART1-TX                    | UART1-TX                    | UART1-TX                    | UART1-TX                    |

| GPIO6            | UART1-RX           | UART1-RX                    | UART1-RX                    | UART1-RX                    | UART1-RX                    |

| GPIO7            | UART1-RTSX         | UART1-RTSX                  | I2C-SCL1                    | SPI-SCS1                    | I2C-SCL1                    |

| GPIO8            | UART1-CTSX         | UART1-CTSX                  | I2C-SDA1                    | SPI-SCLK1                   | I2C-SDA1                    |

| GPIO9            | ADC3               | ADC3                        | ADC3                        | ADC3                        | GPIO9                       |

| GPIO10           | ADC4               | ADC4                        | ADC4                        | ADC4                        | GPIO10                      |

| GPIO11           | SPI-DOUT2          | I2C-SCL2                    | GPIO11                      | I2C-SCL2                    | GPIO11                      |

| GPIO12           | SPI-DIN2           | I2C-SDA2                    | GPIO12                      | I2C-SDA2                    | GPIO12                      |

| GPIO13           | SPI-SCS2           | GPIO13                      | UART1-RTSX                  | UART1-RTSX                  | GPIO13                      |

| GPIO14           | SPI-SCLK2          | GPIO14                      | UART1-CTSX                  | UART1-CTSX                  | GPIO14                      |

| GPIO15           | GPIO15             | GPIO15                      | GPIO15                      | GPIO15                      | GPIO15                      |

| GPIO16           | UART2-TX           | GPIO16                      | GPIO16                      | GPIO16                      | GPIO16                      |

| GPIO17           | UART2-RX           | GPIO17                      | GPIO17                      | GPIO17                      | GPIO17                      |

# 2.4.2. Limitation on Assignment of UART Function to GPIO

The UART which can be assigned to GPIO in TC35680/TC35681 is shown in Table 2-4. The GPIO's which can be assigned to the UART interface depend on an operating mode.

Table 2-4 GPIO assignment of 2 UART interfaces (QFN package)

| Operating mode | HCI mode/Complete mode          | User-App mode                                |

|----------------|---------------------------------|----------------------------------------------|

| UART1-TX       | GPIO5 is used. (Non-modifiable) | GPIO5 can be used.                           |

| UART1-RX       | GPIO6 is used. (Non-modifiable) | GPIO6 can be used.                           |

| UART1-RTSX     | Only GPIO7 can be used.         | Either GPIO7 or GPIO13 can be used. (Note 1) |

| UART1-CTSX     | Only GPIO8 can be used.         | Either GPIO8 or GPIO14 can be used. (Note 1) |

| UART2-TX       | Not assigned                    | GPIO16 can be used.                          |

| UART2-RX       | Not assigned                    | GPIO17 can be used.                          |

| UART2-RTSX     | Not assigned                    | GPIO13 can be used. (Note 1)                 |

| UART2-CTSX     | Not assigned                    | GPIO14 can be used. (Note 1)                 |

Note 1: GPIO13 cannot be assigned to both UART1-RTSX and UART2-RTSX at the same time.

GPIO14 cannot be assigned to both UART1-CTSX and UART2-CTSX at the same time.

# 2.4.3. Limitation on Assignment of I<sup>2</sup>C Function to GPIO

TC35681 uses GPIO7 and GPIO8 as the channel 1 of  $I^2$ C1 interface to an EEPROM which stores a user application program. Another channel of the  $I^2$ C interface cannot be assigned in the start-up sequence.

Table 2-5 Assignment of 2 I<sup>2</sup>C interfaces

| Product        | TC35680                                  |                    |                            | TC35681                         |

|----------------|------------------------------------------|--------------------|----------------------------|---------------------------------|

| Operating mode | HCI mode/<br>Complete mode User-App mode |                    | HCI mode/<br>Complete mode | User-App mode                   |

| I2C-SCL1       | GPIO7 can be used.                       |                    | GPIO7 can be used.         | GPIO7 is used. (Non-modifiable) |

| I2C-SDA1       | GPIO8 can be used.                       |                    | GPIO8 can be used.         | GPIO8 is used. (Non-modifiable) |

| I2C-SCL2       | GPIO9 and GP                             | IO11 can be used.  | GPIO9 an                   | d GPIO11 can be used.           |

| I2C-SDA2       | GPIO10 and GF                            | PIO12 can be used. | GPIO10 ar                  | nd GPIO12 can be used.          |

# 2.5. Power Supply Pins

The attribute and the normal operation voltage of each power supply pin are shown in Table 2-6.

Table 2-6 Power supply pin

|          | Pin No.         | Attribute |                                                                 |  |  |

|----------|-----------------|-----------|-----------------------------------------------------------------|--|--|

| Pin name | QFN             | Туре      | Description                                                     |  |  |

|          | Package VDD/GND |           |                                                                 |  |  |

|          |                 |           | VDD/GND                                                         |  |  |

| VPGM     | 5               | TEST      | Power supply pin for test.                                      |  |  |

|          |                 | _         | This pin should be connected to GND.                            |  |  |

| VBAT     | 18              | VBAT      | Power supply pin for DC/DC converter/LDO regulator and the      |  |  |

|          |                 | VDD       | sleep circuit.                                                  |  |  |

|          |                 |           | An external power supply should be connected to this pin to     |  |  |

|          |                 |           | operate the built-in DC/DC converter and LDO regulator.         |  |  |

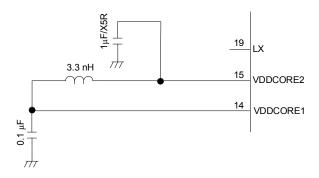

| LX       | 19              | VBAT      | DC/DC converter output pin.                                     |  |  |

|          |                 | VDD       | When the DC/DC converter is used, the power is supplied to      |  |  |

|          |                 |           | VDDCORE1 and VDDCORE2 from this pin. An external coil           |  |  |

|          |                 |           | for the DC/DC converter should be connected.                    |  |  |

|          |                 |           | For details, refer to Section 4.4.                              |  |  |

|          |                 |           | Any other use is not possible.                                  |  |  |

| VDDCORE1 | 14              | _         | Power supply input pin for the analog circuit.                  |  |  |

|          |                 | VDD       | The LX pin supplies power when the DC/DC converter is           |  |  |

|          |                 |           | used. And the VDDCORE2 pin supplies power when the              |  |  |

|          |                 |           | transition to a low power mode is done or when the LDO is       |  |  |

|          |                 |           | used. This pin should be connected to the VDDCORE2 pin.         |  |  |

|          |                 |           | For details, refer to Section 4.4.                              |  |  |

|          |                 |           | Any other use is not possible.                                  |  |  |

| VDDCORE2 | 15              | _         | A feedback input pin for the DC/DC converter. It is also a      |  |  |

|          |                 | VDD       | power supply pin for the analog and digital circuits, and the   |  |  |

|          |                 |           | output pin of the built-in LDO regulator, as well.              |  |  |

|          |                 |           | When the DC/DC converter is used, this pin is a feedback        |  |  |

|          |                 |           | input pin. A coil should be connected between this pin and the  |  |  |

|          |                 |           | LX pin. When the built-in LDO regulator is used, this pin is an |  |  |

|          |                 |           | output pin of the regulator. The internal circuits connected to |  |  |

|          |                 |           | VDDCORE1 and VDDCORE2 are supplied with the power.              |  |  |

|          |                 |           | For details, refer to Section 4.4.                              |  |  |

| ) (DDIO  |                 | ) (DD) (C | Any other use is not possible.                                  |  |  |

| VDDIO    | 23              | VDDIO     | Power supply pin for I/O.                                       |  |  |

|          |                 | VDD       | The power of the proper voltage for the GPIO circuits should    |  |  |

|          |                 |           | be supplied. The voltage should not exceed the VBAT value.      |  |  |

|          |                 |           | For details, refer to Section 4.4.                              |  |  |

|          |                 |           | Any other use is not possible.                                  |  |  |

|              | Pin No. | Attribute |                                                                 |

|--------------|---------|-----------|-----------------------------------------------------------------|

| Pin name     | QFN     | Туре      | Description                                                     |

|              | Package | VDD/GND   |                                                                 |

| VDD/GND      |         |           |                                                                 |

| VDDIOFQ      | 27      | VDDIOFQ   | (Only TC35680)                                                  |

|              |         | VDD       | This pin should be connected to an external capacitor for the   |

|              |         |           | power supply of the built-in Flash memory (output).             |

|              |         |           | This pin is connected to the power supply of the built-in Flash |

|              |         |           | memory. A load capacitor of 0.1 µF or more in the operation     |

|              |         |           | temperature range should be connected for the LDO               |

|              |         |           | regulator.                                                      |

|              |         |           | Any other use is not possible.                                  |

| VSSD1        | 27      | Digital   | (Only TC35681)                                                  |

|              |         | GND       | This pin should be connected to GND.                            |

| VSSA         | 8       | Analog    | GND pin for the analog circuits.                                |

|              |         | GND       | This pin should be connected to GND.                            |

| VSSRFIO      | 6       | Analog    | GND pin for RFIO.                                               |

|              |         | GND       | This pin should be connected to GND.                            |

| VSSX         | 13      | Analog    | GND pin for OSC.                                                |

|              |         | GND       | This pin should be connected to GND.                            |

| VSSDC        | 20      | Digital   | GND pin for the DC/DC converter.                                |

|              |         | GND       | This pin should be connected to GND.                            |

| VSSD         | FIN     | Digital   | Die pad GND (FIN).                                              |

| VSSD2(Note1) |         | GND       | This pin is shared with the GND of the digital circuits.        |

|              |         |           | The die pad on the bottom of the package should be              |

|              |         |           | connected to GND.                                               |

Note1:Only TC35681

#### 3. Device Overview

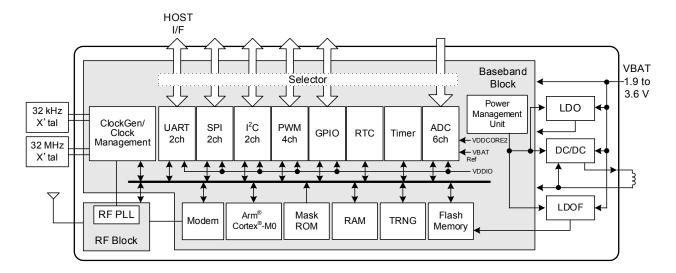

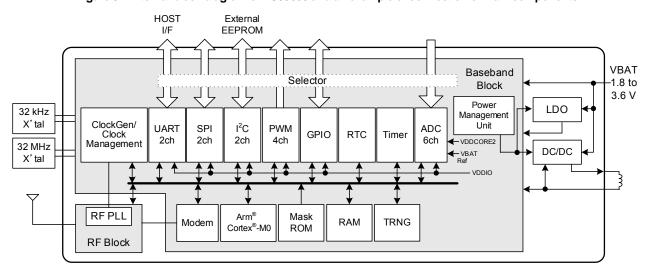

#### 3.1. Internal Block Diagram

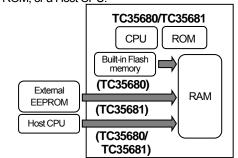

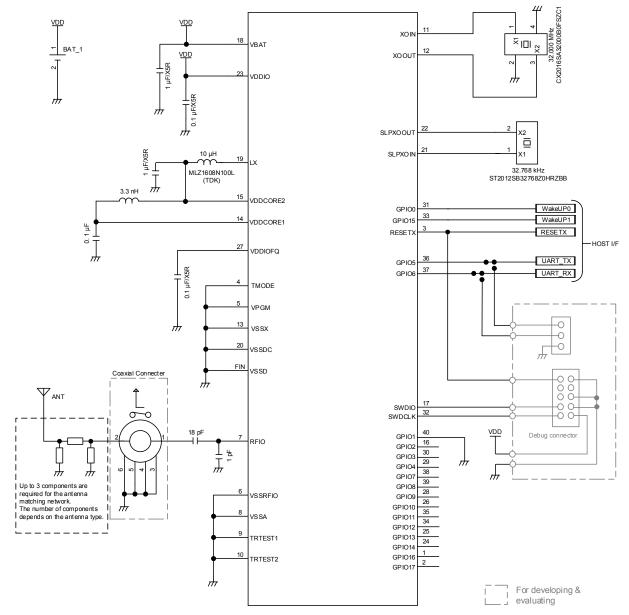

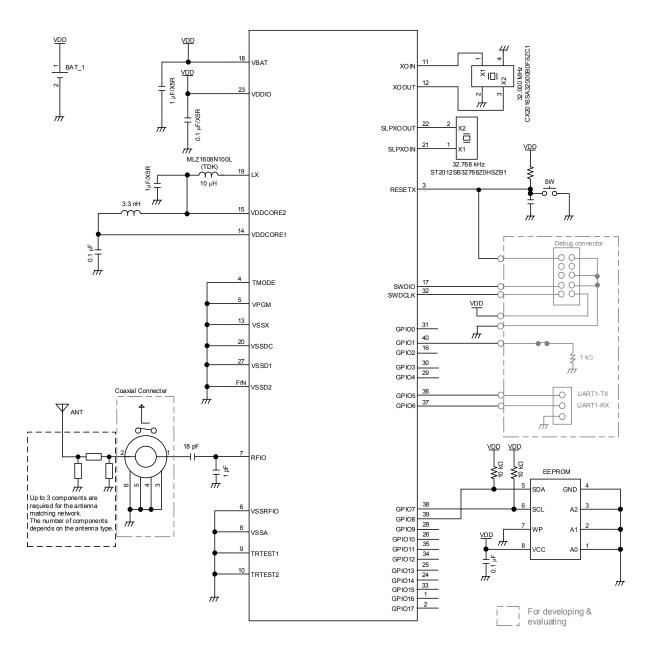

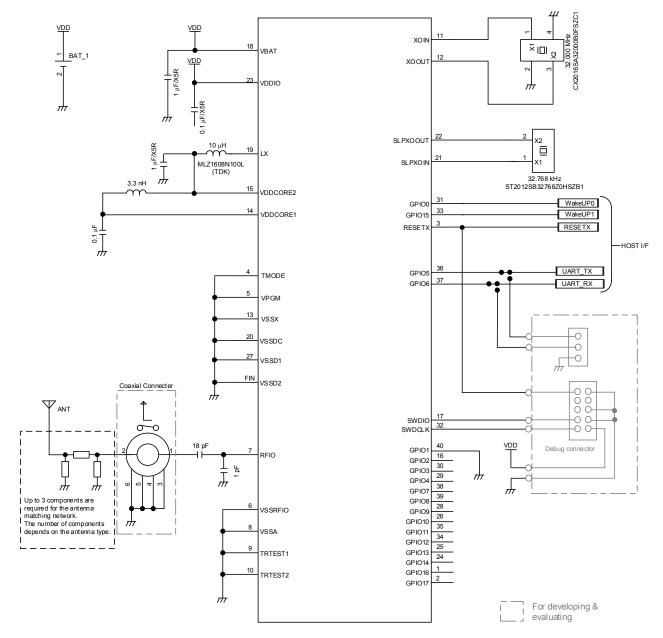

The internal block diagrams of TC35680 and TC35681 are shown in Figure 3-1 and Figure 3-2, respectively. An example of connection of main components is shown in each figure, as well.

Figure 3-1 Internal block diagram of TC35680 and an example of connection of main components

Figure 3-2 Internal block diagram of TC35681 and an example of connection of main components

#### 3.1.1. Power Supply System

TC35680/TC35681 integrate a DC/DC converter and multiple LDO regulators. Many circuits in the device are supplied with power from step-down power supply. Power Management Unit (PMU) switches the power supplies dynamically and controls the output voltage to optimize power efficiency according to low power modes.

The power dedicated to the digital interface can be supplied on the VDDIO pin. So system design or user application need not care about the power control done by the PMU.

For details of the power supply system, refer also to Section 3.6 and Section 4.4.

#### 3.1.2. Clock System

The frequency of the reference operation clock is 32 MHz. And the frequency of the sleep clock is 32.768 kHz. Each clock circuit has its own clock divider, so each block including the CPU can be supplied with an optimized clock. For the setting parameters for each block, refer to the function description in Chapter 4. For the details of the reference clock and the sleep clock, refer to Section 4.12 and Section 4.13, respectively.

The source of the sleep clock of TC35680/TC35681 can be selected from among the following three clock sources. At start-up, the built-in silicon oscillator (hereafter, SiOSC) is used.

- SiOSC

- Crystal resonator (A crystal oscillation circuit is used.)

- External sleep clock input

The frequency accuracy of the SiOSC is not compliant with the **Bluetooth**® connection. It cannot be used for the application which executes the **Bluetooth**® **connection**. The SiOSC can be used for application which includes advertising only, and others. For the details of the sleep clock, refer to Section 4.13.

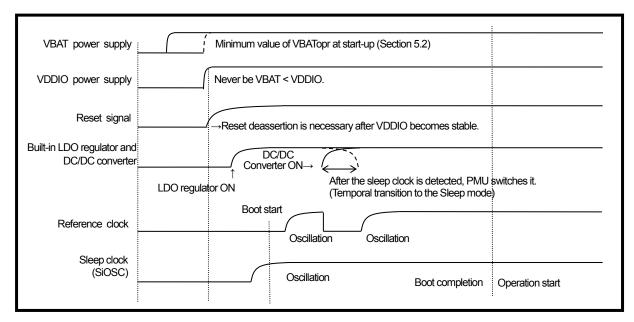

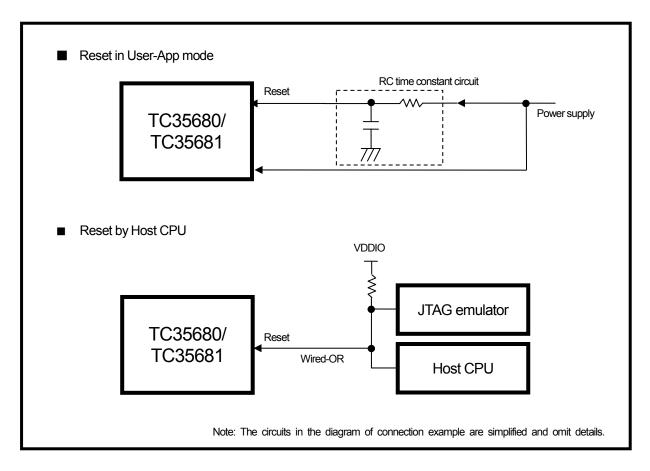

#### 3.1.3. Hardware Start-up Sequence

The sequence of the start-up of the power supply and the reset deassertion are shown in Figure 3-3. For sequence of the start-up of the built-in firmware, refer to Section 3.5. For details of the reset, refer to Section 4.5.

The VBAT power should be supplied first. The VDDIO power can be supplied simultaneously. The voltage of the VDDIO, however, should not exceed the voltage of the VBAT. The reset should be deasserted after the voltage of the VBAT reaches the minimum value of VBATopr in Section 5.2 and the voltage of the VDDIO also reaches the minimum value of VDDIOopr.

When the reset is deasserted, the crystal oscillator for the reference clock starts to operate.

And the SiOSC starts oscillating to supply the sleep clock.

The reference clock should become stable in 1.5 ms for a circuit of TC35680/TC35681. It is needed that a stable time of the reference clock keeps within 1.5 ms

Figure 3-3 Hardware start-up sequence

21

### 3.2. System Configuration and Operating Mode

TC35680/TC35681 support two system configurations and three operating modes, as shown in Figure 3-4.

- System configuration

- Configuration that this device is controlled by an external host CPU (Host-controlled system)

- Configuration that this device is controlled by its own CPU using a user application program (Standalone system)

#### Operating mode

- Controlled by HCI/Extended HCI commands in the Host-controlled system (HCI mode).

- Controlled by TCU commands in the Host-controlled system (Complete mode).

- > Controlled by the built-in CPU in TC35680 or TC35681 using a user application program (User-App mode) Following 3 methods are available to download a user application program;

- ✓ Download from the built-in Flash memory (TC35680)

- ✓ Download from an external EEPROM (TC35681)

- ✓ Download via the UART interface (TC35680/TC35681)

For the details of the selection of the operating mode, refer to Section 3.4.

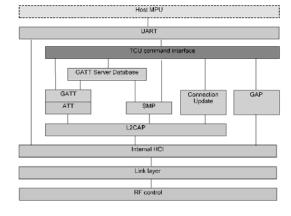

#### ■ HCI mode/Complete mode

Controlled by a host CPU.

# Host CPU Commands TC35680/ TC35681

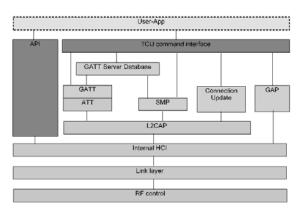

#### ■ User-App mode

Controlled by a user application program in the built-in Flash ROM, an external EEPROM, or a Host CPU.

Figure 3-4 Example of system configuration of TC35680/TC35681

# 3.3. System Configuration

## 3.3.1. Standalone System

When the standalone system is configured, a user application program should be stored in the built-in Flash memory (TC35680) or an external EEPROM (TC35681) in the User-App mode.

In the User-App mode, a boot loader in the mask ROM reads the user application program from the built-in Flash memory or an external EEPROM and writes to the RAM in the standalone system, then the user application program is executed. An external CPU is not necessary in the system. Then, the standalone operation is enabled.

# 3.3.2. Host-Controlled System

The host-controlled system can be configured by the following three methods;

- ✓ Using the HCI mode.

- ✓ Using the Complete mode.

- ✓ Using the User-App mode.

The built-in firmware is used to configure the system in the HCI and the Complete modes.

In the User-App mode, a user application program is executed by the CPU in TC35680/TC35681. And in the system, the host can operate together with it.

# 3.4. Selection and Setting of Operating Mode

The following two methods are available to set an operating mode.

- Setting is done by the status of the GPIO1 and SWDIO pins at start-up

- ✓ Setting is done by the HCI\_SET\_MODE command after start-up in the HCI mode. (The Complete mode or the User-App mode can be selected.)

Table 3-1 shows the application of each operating mode and its setting at start-up.

When the User-App mode is selected at start-up, it is not possible to switch directly to the HCl mode. A restart (a hardware reset assertion) is necessary to switch from the User-App mode or the Complete mode to another operating mode.

Table 3-1 Application of each operating mode and its setting at start-up

| Operating mode | Setting at start-up |       | Application                                                   |  |

|----------------|---------------------|-------|---------------------------------------------------------------|--|

| Operating mode | GPIO1               | SWDIO | Application                                                   |  |

| User-App mode  | Н                   | 1     | ✓ Execution of a user application program                     |  |

| HCI mode       | L                   | Н     | ✓ RF test                                                     |  |

|                |                     |       | <ul> <li>✓ Radio Frequency (RF) Certification test</li> </ul> |  |

|                |                     |       | <ul> <li>✓ Bluetooth® Qualification test</li> </ul>           |  |

|                |                     |       | ✓ Programming of a user application program (firmware)        |  |

|                |                     |       | <ul> <li>✓ Control by HCI/Extended HCI commands</li> </ul>    |  |

| Complete mode  | L                   | Н     | ✓ Device control by TCU commands                              |  |

|                |                     |       | (Control commands in the GATT/SM layer)                       |  |

| Test mode      | L                   | L     | This setting is prohibited.                                   |  |

Note: The built-in firmware assigns the input function with the pull-up resistor ON to the GPIO1 pin at start-up. So, when the pin is open at start-up, the User-App mode is selected. When the setting pins are pulled down with external resistors, respectively, the values of the resistors should be sufficiently lower than the values of the internal pull-up resistors.  $1 \text{ k}\Omega$ , for example, is OK.

24 2018-09-13

#### 3.4.1. **HCI Mode**

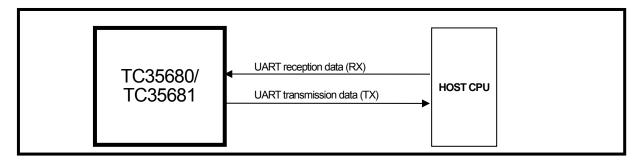

In the HCI mode, a host CPU controls TC35680/TC35681 using the HCI commands and the Extended HCI commands which are stored in the built-in firmware. The host CPU is connected to TC35680/TC35681 with the UART interface. The HCI mode is used for the following purposes;

- > TC35680/TC35681 are controlled using the HCI commands and the Extended HCI commands.

- Bluetooth® Qualification test and Radio Frequency (RF) Certification test in different countries and regions.

- A user application program (firmware) is programmed to the built-in Flash memory.

- > RF test is done.

- > The operating mode is changed by the HCl command.

The program for the HCI mode is stored in the mask ROM as a built-in firmware. So, in HCI mode, the TC35680/TC35681 do not execute a user application program which is executed by the CPU of the TC35680/TC35681. After start-up, the GPIO5 pin (UART1-TX) and the GPOO6 pin (UART1-RX) are assigned to the UART interface pins by the built-in firmware.

The initial setting of the UART interface in the HCI mode is shown in Table 3-2.

Table 3-2 Initial setting of UART interface in HCI mode

| Baud rate    | 115.2 kbps |

|--------------|------------|

| Parity bit   | None       |

| Data length  | 8 bits     |

| Stop bit     | 1 bit      |

| Flow control | None       |

| Protocol     | HCI        |

#### 3.4.2. Complete Mode

After start-up in the HCl mode, a proper command can switch to the Complete mode. Then a TCU command can be used to control the system. The TCU command is a control API in the GATT/SM layer, and it is stored in the mask ROM.

The HCI\_SET\_MODE command is used to switch the HCI mode to the Complete mode.

#### 3.4.3. User-App Mode

In the User-App mode, a user application program is executed by the CPU in TC35680/TC35681. The user application program can use the **Bluetooth**® Low Energy protocol stack and a hardware control API in the built-in firmware. In this document, the control function that can be used in the User-App mode is described as "API".

TC35680/TC35681 download a user application program with one of the following methods, and execute the program.

- ✓ Download of the user application program which is stored in the built-in Flash memory (TC35680) or an external EEPROM (TC35681) in the proper format

- ✓ Download of a user application program from the host CPU via the UART interface

The storage memory of a user application program is the built-in Flash memory in TC35680 or an external EEROM for T35681. TC35681 and the EEPROM should be connected with the  $I^2C$  interface (GPIO7 and GPIO8).

A user application program cannot occupy all resources of the CPU. The built-in firmware also uses resources of the CPU. So user should fully evaluate that a desired functions are executed as expected and the performance reaches the target level.

#### 3.5. Start-up Sequence

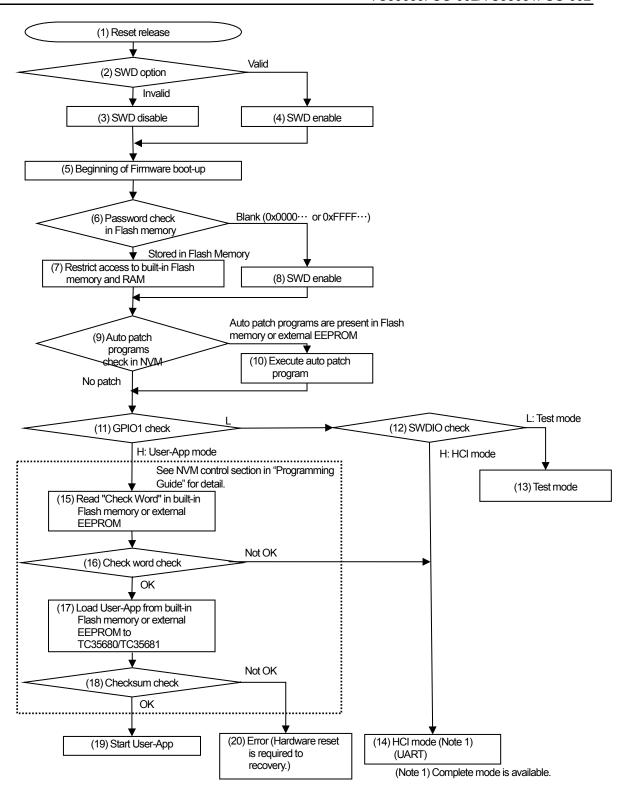

The boot loader and the built-in firmware in TC35680/TC35681 recognize the operating mode and complete the start-up procedure, as shown in Figure 3-5.

The download procedure via the UART interface and the execution procedure are done by the HCl command after TC35680/TC35681 start up in the HCl mode.

#### 3.5.1. Details of Start-up Sequence

- (1) Reset is deasserted.

- (2) "enable" or "disable" setting of SWD in this device is checked.

- (3) When the result is "disable", the SWD function is set to disabled.

- (4) When the result is "enable", the SWD function is set to enabled.

- (5) The firmware start-up is executed.

- (6) The password for the SWD in the built-in Flash memory is checked.

- (7) When the password for the SWD is stored in the built-in Flash memory, an access to the built-in Flash memory and RAM spaces are restricted.

- (8) When the password for the SWD is not stored in the built-in Flash memory, the SWD is set to being enabled.

- (9) The presence of the auto-patch programs are checked.

- For the details of the auto-patch function, refer to Section 4.16.

- (10) When the auto-patch programs are present in the built-in Flash memory or the external EEPROM, the auto-patch programs are adopted.

- (11) When the auto-patch programs have been adopted or when the auto-patch programs are not present, the status of the GPIO1 pin is checked.

- (12) When the GPIO1 pin is Low, the status of the SWDIO pin is checked.

- (13) When the SWDIO pin is Low, this device enters a test mode. This setting is not usable.

- (14) When the SWDIO pin is High, this device starts up in the HCI mode.

- (15) When the GPIO1 pin is High, "Check word" in the user application program stored in the built-in Flash memory or the external EEPROM is read.

- (16) A match between "Check word" and a preset value is checked.

When "Check word" does not match with the preset value, this device starts up in the HCI mode.

- (17) When "Check word" matches with the preset value, the user application program in the built-in Flash memory or the external EEPROM is downloaded to TC35680/TC35681.

- (18) A checksum value stored in the built-in Flash memory or the external EEPROM is compared with the checksum value which is calculated using the downloaded user application program.

- (19) When those checksum values matched, the built-in firmware executes the user application program.

- (20) When those checksum values did not match, the error occurs. The hardware reset is needed.

Figure 3-5 TC35680/TC35681 boot sequence

#### 3.6. Low Power System

TC35680/TC35681 support the following three low power modes to save power consumption.

- Sleep

- Backup

- Deep Sleep

The power consumption decreases in the order of the Sleep, the Backup, and the Deep Sleep modes. The lowest power consumption is realized in the Deep Sleep mode.

The low power consumption function are independent of the operation mode (the HCI mode, the Complete mode or the User-App mode).

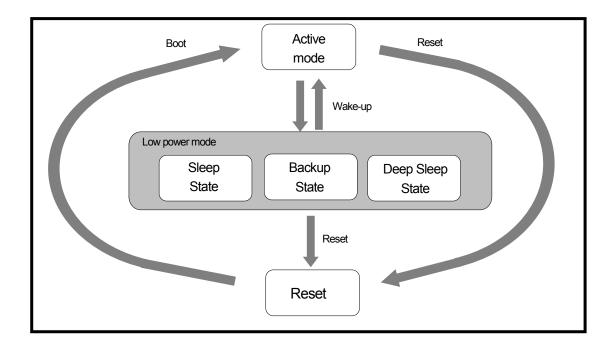

#### 3.6.1. State Transition

Figure 3-6 shows the state transition diagram of TC35680/TC35681. There are three main states.

- Active mode

- Reset

- Low power mode

The Active mode is a normal operating state. The Reset is the state when a hardware reset is asserted. The Low power mode is either the Sleep, the Backup or the Deep Sleep state.

In this document, the transition from the Low power mode to the Active mode is defined as "Wake-up". And the transition from the Active mode to the Low power mode is defined as "Sleeping".

The transition from the Active mode to the Low power mode can be done by Sleeping. The direct transition among the low power states is not possible.

Figure 3-6 State transition diagram

# 3.6.2. Available Functions in Each Low Power Mode

Available functions in each low power mode are shown in Table 3-3.

A suitable low power mode should be selected. For the details of the current consumption, refer to Section 5.3.

#### **Table 3-3 Available functions**

| Fun                     | ction                                                                                                                                                                                                                                                    | Active mode                                                                                      | Sleep mode                                                                                                                                                                                                                                        | Backup mode                                                                         | Deep Sleep mode (Note 1)                                                                                                                                 |