## ISL71010B25

Ultra Low Noise, 2.5V Precision Voltage Reference

FN8960

Rev.1.00

Apr 12, 2018

The [ISL71010B25](#) is an ultra low noise, high DC accuracy precision voltage reference with a wide input voltage range from 4V to 30V. The ISL71010B25 uses the dielectrically isolated PR40 process to achieve  $1.9\mu\text{V}_{\text{P-P}}$  noise at 0.1Hz to 10Hz with an initial voltage accuracy of  $\pm 0.05\%$ .

The ISL71010B25 offers a 2.5V output voltage with  $10\text{ppm}/^{\circ}\text{C}$  temperature coefficient and also provides excellent line and load regulation. The device is offered in an 8 Ld SOIC package.

The ISL71010B25 is ideal for high-end instrumentation, data acquisition, and processing applications requiring high DC precision where low noise performance is critical.

### Applications

- Low Earth Orbit (LEO)

- High altitude avionics

- Precision instruments

- Data acquisition systems for space applications

- Strain and pressure gauges for space applications

- Active sources for sensors

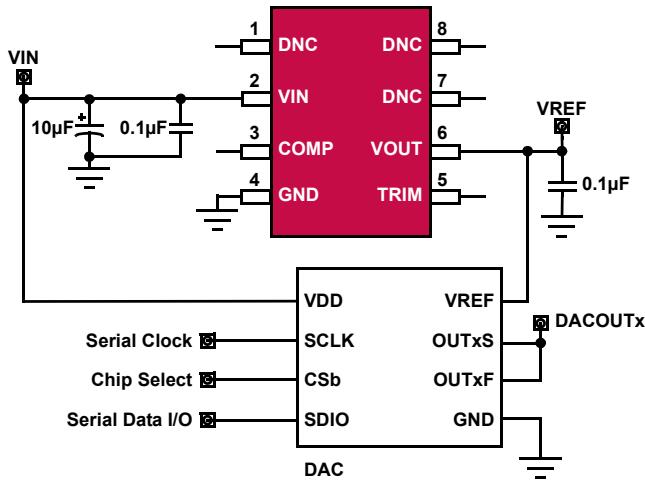

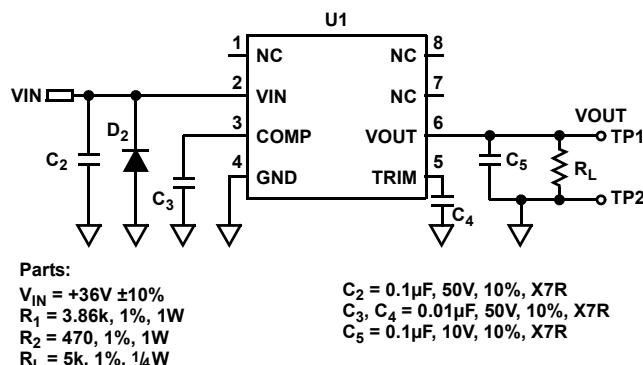

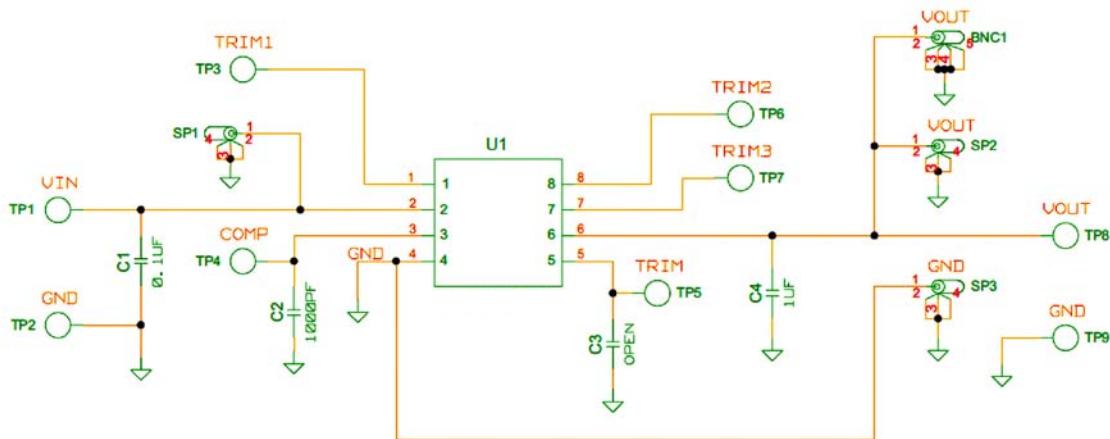

Figure 1. ISL71010B25 Typical Application Diagram

### Features

- Reference output voltage:  $2.5\text{V} \pm 0.05\%$

- Accuracy over temperature/radiation:  $\pm 0.15\%$

- Output voltage noise:  $1.9\mu\text{V}_{\text{P-P}}$  typical (0.1Hz to 10Hz)

- Supply current:  $930\mu\text{A}$  (typical)

- Temperature coefficient:  $10\text{ppm}/^{\circ}\text{C}$  (max)

- Output current capability: 20mA

- Line regulation:  $18\text{ppm}/\text{V}$  (max)

- Load regulation:  $17\text{ppm}/\text{mA}$  (max)

- NiPdAu-Ag lead finish (Sn free)

- Dielectrically isolated PR40 process

- Operating temperature range:  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

- Passes NASA Low Outgassing Specifications

- Characterized radiation level:

- Low dose rate (10mrad(Si)): 30krad(Si)

- Single event burnout LET: 43MeV•cm<sup>2</sup>/mg

### Related Literature

For a full list of related documents, visit our website

- [ISL7101B25](#) product page

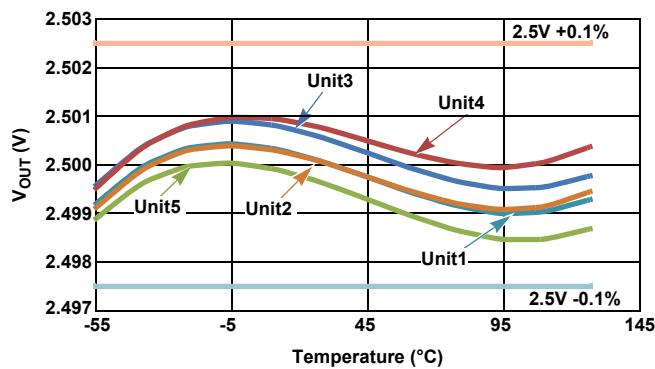

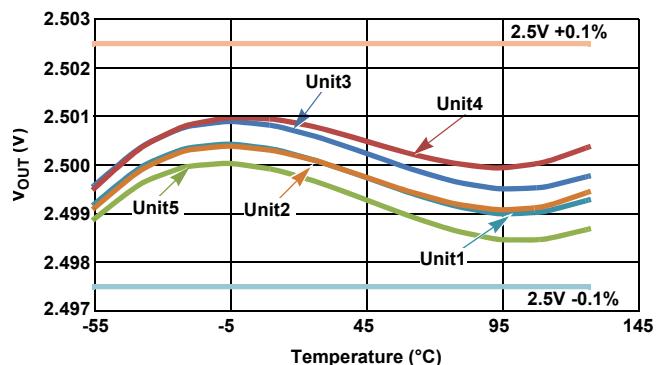

Figure 2.  $\text{V}_{\text{OUT}}$  vs Temperature

## 1. Overview

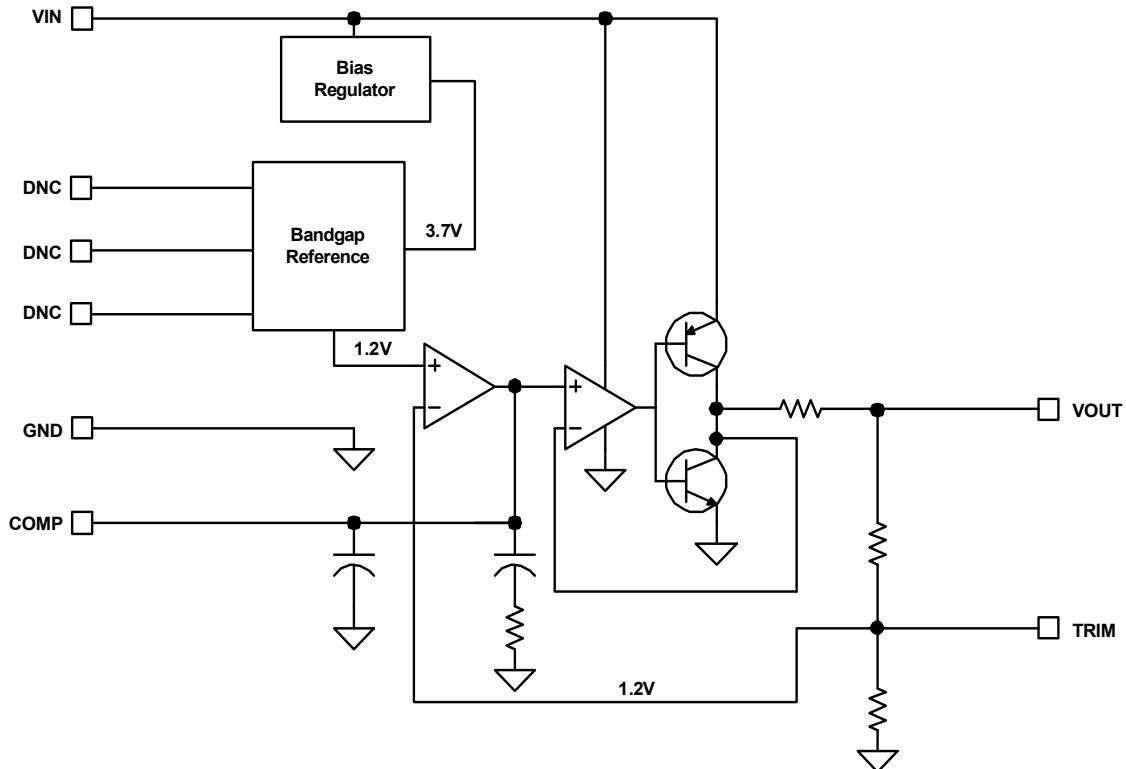

### 1.1 Functional Block Diagram

Figure 3. Functional Block Diagram

### 1.2 Ordering Information

| Part Number<br>( <a href="#">Notes 2, 3</a> )   | Part<br>Marking  | V <sub>OUT</sub> Option<br>(V) | Accuracy<br>(%) | Tempco<br>(ppm/°C) | Temp Range<br>(°C) | Tape and Reel<br>(Units) | Package<br>(RoHS<br>Compliant) | Pkg.<br>Dwg. # |

|-------------------------------------------------|------------------|--------------------------------|-----------------|--------------------|--------------------|--------------------------|--------------------------------|----------------|

| ISL71010BMB25Z                                  | 71010 BMZ25      | 2.50                           | ±0.05           | 10                 | -55 to +125        | -                        | 8 Ld SOIC                      | M8.15          |

| ISL71010BMB25Z-TK<br>( <a href="#">Note 1</a> ) | 71010 BMZ25      | 2.50                           | ±0.05           | 10                 | -55 to +125        | 1k                       | 8 Ld SOIC                      | M8.15          |

| ISL71010BM25EV1Z                                | Evaluation Board |                                |                 |                    |                    |                          |                                |                |

Notes:

1. Refer to [TB347](#) for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials and NiPdAu-Ag plate -e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the [ISL71010B25](#) product information page. For more information about MSL refer to [TB363](#).

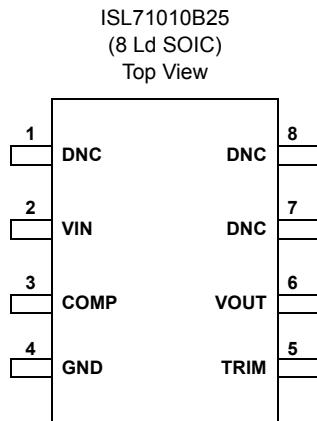

### 1.3 Pin Configuration

### 1.4 Pin Description

| Pin Number | Pin Name | ESD Circuit | Description                                |

|------------|----------|-------------|--------------------------------------------|

| 1, 7, 8    | DNC      | 3           | Do not connect. Internally terminated.     |

| 2          | VIN      | 1           | Input voltage connection                   |

| 3          | COMP     | 2           | Compensation and noise reduction capacitor |

| 4          | GND      | 1           | Ground connection.                         |

| 5          | TRIM     | 2           | Voltage reference trim input               |

| 6          | VOUT     | 2           | Voltage reference output                   |

**ESD Circuit 1**

Capacitively Triggered Clamp

**ESD Circuit 2**

Pins 3, 5, 6

**ESD Circuit 3**

DNC

## 2. Specifications

### 2.1 Absolute Maximum Ratings

| Parameter                                                  | Minimum                                | Maximum         | Unit       |

|------------------------------------------------------------|----------------------------------------|-----------------|------------|

| Max Voltage                                                |                                        |                 |            |

| $V_{IN}$ to GND                                            | -0.5                                   | +40             | V          |

| $V_{OUT}$ to GND (10s)                                     | -0.5                                   | $V_{OUT} + 0.5$ | V          |

| Voltage on any Pin to Ground                               | -0.5                                   | $V_{OUT} + 0.5$ | V          |

| Voltage on DNC pins                                        | No connections permitted to these pins |                 |            |

| Input Voltage Slew Rate (Max)                              |                                        | 0.1             | V/ $\mu$ s |

| ESD Rating                                                 | Value                                  |                 | Unit       |

| Human Body Model (Tested per JS-001-2014)                  | 3                                      |                 | kV         |

| Machine Model (Tested per JESD22-A115-C)                   | 200                                    |                 | V          |

| Charged Device Model (Tested per JS-002-2014)              | 2                                      |                 | kV         |

| Latch-Up (Tested per JESD-78E; Class 2, Level A) at +125°C | $\pm 100$                              |                 | mA         |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

### 2.2 Outgas Testing

| Specification (Tested per ASTM E 595, 1.5)                         | Value | Unit |

|--------------------------------------------------------------------|-------|------|

| Total Mass Lost ( <a href="#">Note 4</a> )                         | 0.06  | %    |

| Collected Volatile Condensable Material ( <a href="#">Note 4</a> ) | <0.01 | %    |

| Water Vapor Recovered                                              | 0.03  | %    |

Notes:

4. Results meet NASA low outgassing requirements of "Total Mass Lost" of <1% and "Collected Volatile Condensable Material" of <0.1%.

### 2.3 Thermal Information

| Thermal Resistance (Typical)                     | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|--------------------------------------------------|----------------------|----------------------|

| 8 Ld SOIC Package ( <a href="#">Notes 5, 6</a> ) | 110                  | 60                   |

Notes:

5.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. See [TB379](#).

6. For  $\theta_{JC}$ , the "case temp" location is taken at the package top center.

| Parameter                                                   | Minimum                        | Maximum | Unit |

|-------------------------------------------------------------|--------------------------------|---------|------|

| Continuous Power Dissipation ( $T_A = +125^\circ\text{C}$ ) |                                | 217     | mW   |

| Maximum Junction Temperature ( $T_{JMAX}$ )                 |                                | +150    | °C   |

| Storage Temperature Range                                   | -65                            | +150    | °C   |

| Pb-Free Reflow Profile                                      | Refer to <a href="#">TB493</a> |         |      |

## 2.4 Recommended Operating Conditions

| Parameter         | Minimum | Maximum | Unit |

|-------------------|---------|---------|------|

| $V_{IN}$          | 4.0     | +30     | V    |

| Temperature Range | -55     | +125    | °C   |

## 2.5 Electrical Specifications

$V_{IN} = 5V$ ,  $I_{OUT} = 0mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $COMP = 1nF$  unless otherwise specified. **Boldface** limits apply over the operating temperature range,  $-55^{\circ}C$  to  $+125^{\circ}C$ .

| Description                                                          | Parameter                         | Test Conditions                                            | Min<br>( <a href="#">Note 8</a> ) | Typ  | Max<br>( <a href="#">Note 8</a> ) | Unit              |

|----------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------|-----------------------------------|------|-----------------------------------|-------------------|

| Output Voltage                                                       | $V_{OUT}$                         | $V_{IN} = 5V$                                              |                                   | 2.5  |                                   | V                 |

| $V_{OUT}$ Accuracy at $T_A = +25^{\circ}C$                           | $V_{OA}$                          | $V_{OUT} = 2.5V$ ( <a href="#">Note 7</a> )                | -0.05                             |      | +0.05                             | %                 |

| $V_{OUT}$ Accuracy at $T_A = -55^{\circ}C$ to $+125^{\circ}C$        |                                   | $V_{OUT} = 2.5V$ ( <a href="#">Note 7</a> )                | -0.15                             |      | +0.15                             | %                 |

| Output Voltage Temperature Coefficient<br>( <a href="#">Note 9</a> ) | TC $V_{OUT}$                      |                                                            |                                   |      | <b>10</b>                         | ppm/°C            |

| Input Voltage Range                                                  | $V_{IN}$                          | $V_{OUT} = 2.5V$                                           | <b>4</b>                          |      | <b>30</b>                         | V                 |

| Supply Current                                                       | $I_{IN}$                          |                                                            |                                   | 0.92 | <b>1.28</b>                       | mA                |

| Line Regulation                                                      | $\Delta V_{OUT} / \Delta V_{IN}$  | $V_{IN} = 4V$ to $30V$ , $V_{OUT} = 2.5V$                  |                                   | 6    | <b>18</b>                         | ppm/V             |

| Load Regulation                                                      | $\Delta V_{OUT} / \Delta I_{OUT}$ | Sourcing: $0mA \leq I_{OUT} \leq 20mA$                     |                                   | 2.5  | <b>17</b>                         | ppm/mA            |

|                                                                      |                                   | Sinking: $-10mA \leq I_{OUT} \leq 0mA$                     |                                   | 2.5  | <b>17</b>                         | ppm/mA            |

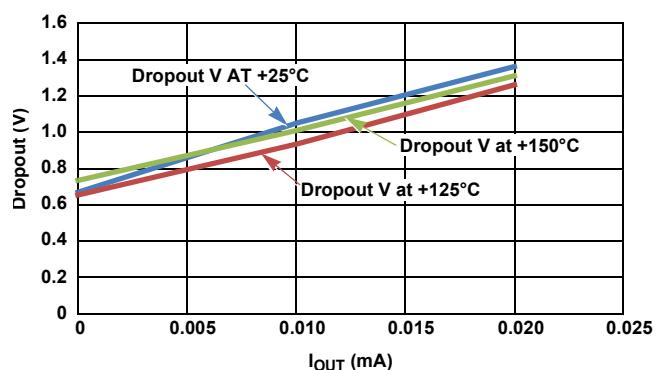

| Dropout Voltage ( <a href="#">Note 10</a> )                          | $V_D$                             | $V_{OUT} = 2.5V$ at $10mA$                                 |                                   | 1.1  | <b>1.7</b>                        | V                 |

| Short-Circuit Current                                                | $I_{SC+}$                         | $T_A = +25^{\circ}C$ , $V_{OUT}$ tied to GND               |                                   | 54   | 75                                | mA                |

| Short-Circuit Current                                                | $I_{SC-}$                         | $T_A = +25^{\circ}C$ , $V_{OUT}$ tied to $V_{IN}$          | -100                              | -60  |                                   | mA                |

| Turn-on Settling Time                                                | $t_R$                             | 90% of final value, $C_L = 1.0\mu F$ , $C_C = \text{open}$ |                                   | 150  |                                   | μs                |

| Ripple Rejection                                                     |                                   | $f = 120Hz$                                                |                                   | 90   |                                   | dB                |

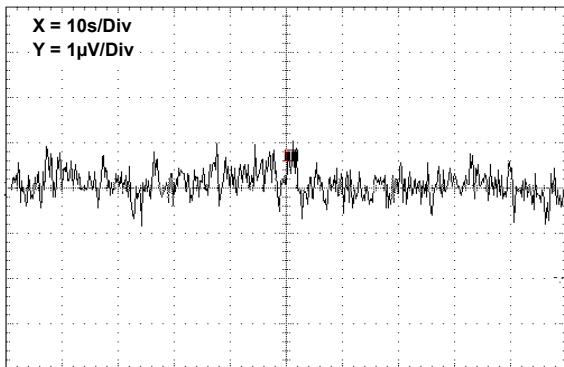

| Noise Voltage                                                        | $e_{np-p}$                        | $0.1Hz \leq f \leq 10Hz$ , $V_{OUT} = 2.5V$                |                                   | 1.9  |                                   | μV <sub>P-P</sub> |

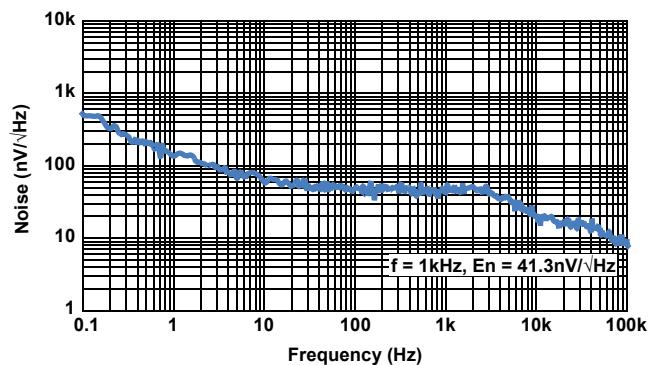

| Broadband Voltage Noise                                              | $V_n$                             | $10Hz \leq f \leq 1kHz$ , $V_{OUT} = 2.5V$                 |                                   | 1.6  |                                   | μV <sub>RMS</sub> |

| Noise Voltage Density                                                | $e_n$                             | $f = 1kHz$ , $V_{OUT} = 2.5V$                              |                                   | 50   |                                   | nV/√Hz            |

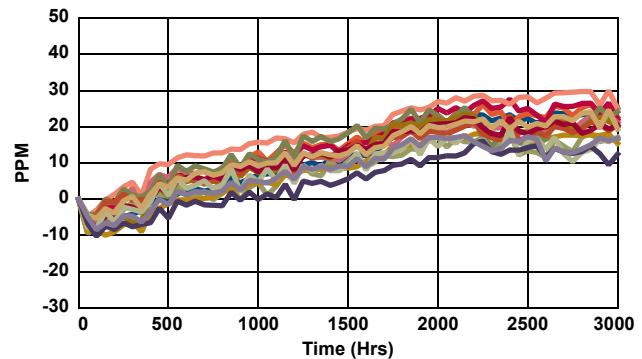

| Long Term Stability                                                  | $\Delta V_{OUT} / \Delta t$       | $T_A = +25^{\circ}C$                                       |                                   | 20   |                                   | ppm               |

Notes:

- Post-reflow drift for the ISL71010B25 devices can exceed  $100\mu V$  to  $1.0mV$  based on experimental results with devices on FR4 double sided boards. The system engineer must take this into account when considering the reference voltage after assembly.

- Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

- Over the specified temperature range. Temperature coefficient is measured by the box method whereby the change in  $V_{OUT}$  is divided by the temperature range; in this case,  $-55^{\circ}C$  to  $+125^{\circ}C = +180^{\circ}C$ . See "[Specifying Temperature Coefficient \(Box Method\)](#)" on page 11 for more information.

- Dropout Voltage is the minimum  $V_{IN} - V_{OUT}$  differential voltage measured at the point where  $V_{OUT}$  drops  $1mV$  from  $V_{IN}$  = nominal at  $T_A = +25^{\circ}C$ .

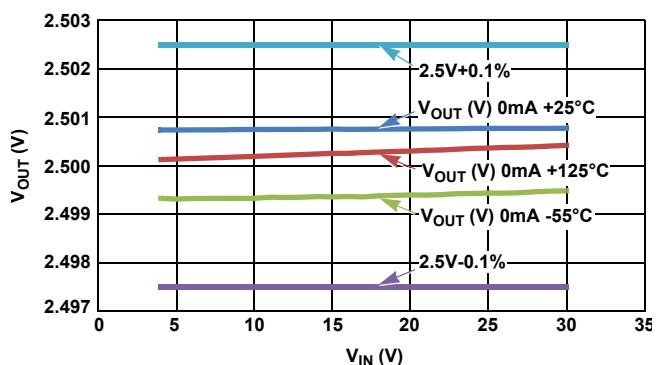

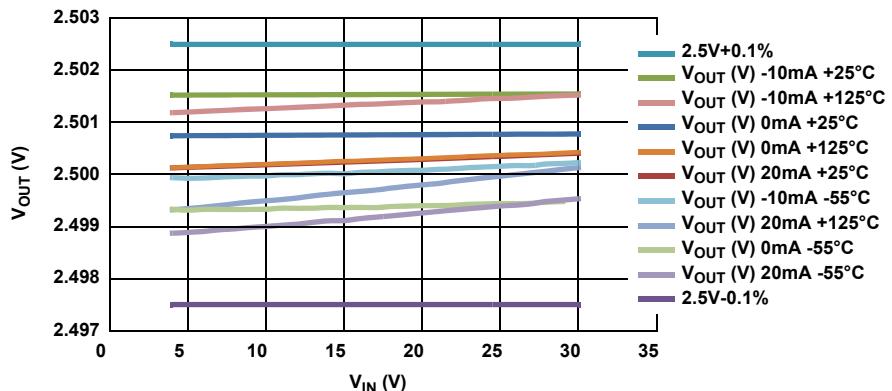

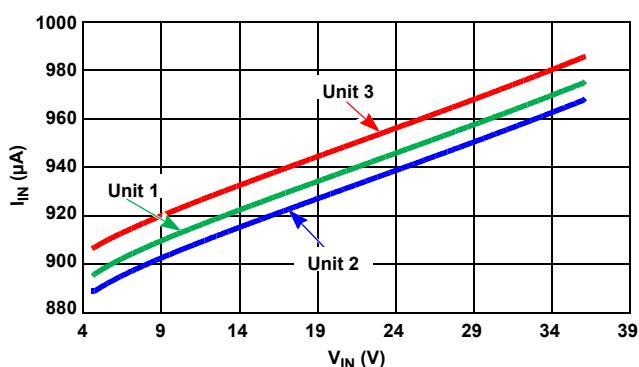

### 3. Typical Performance Curves

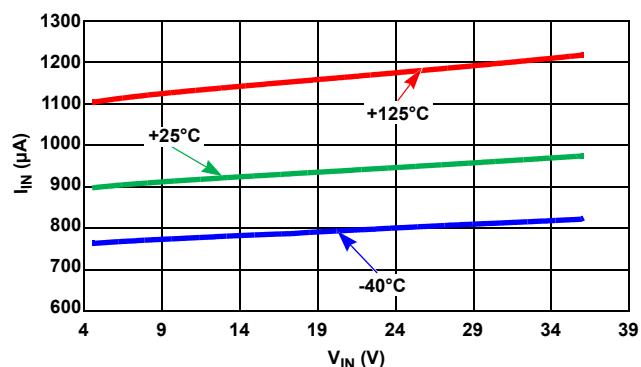

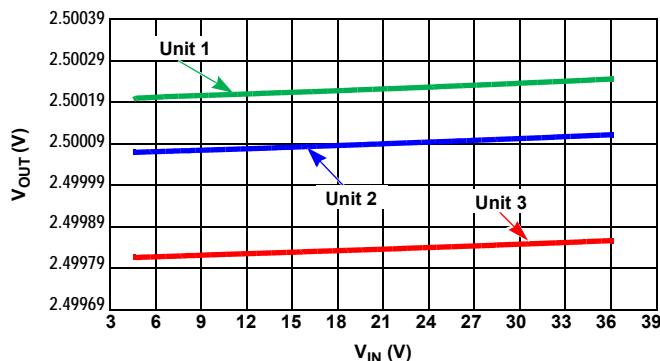

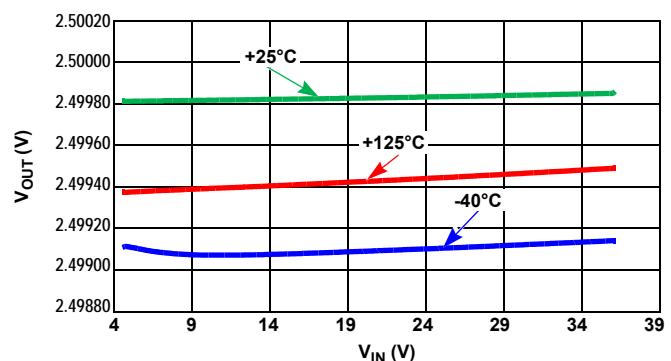

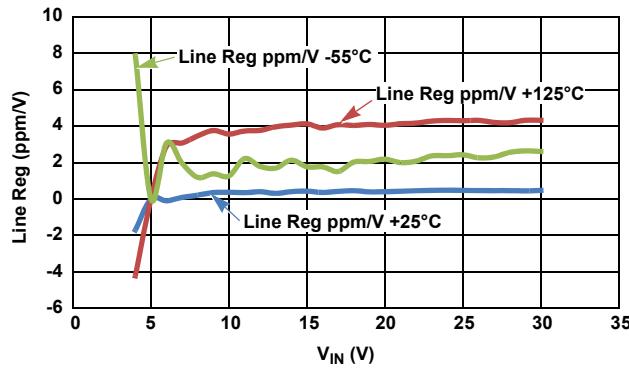

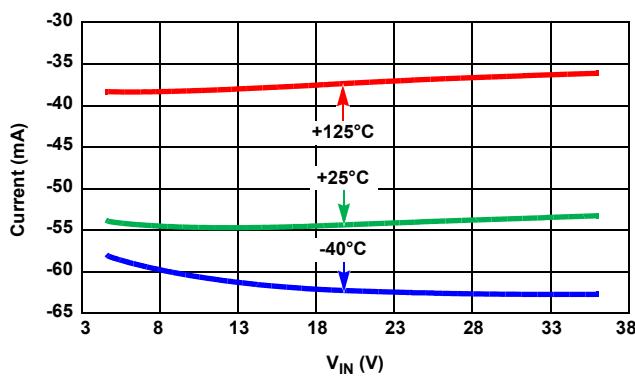

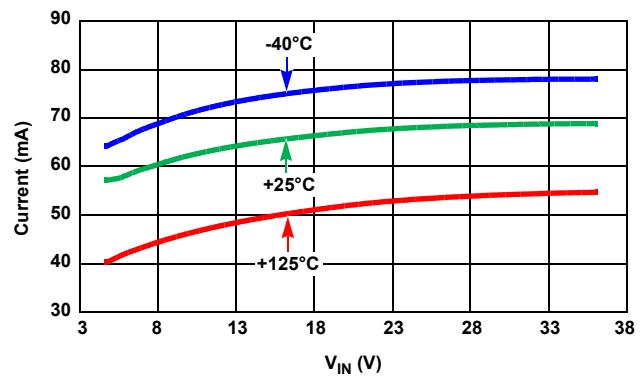

Figure 4.  $V_{OUT}$  vs Temperature, Five UnitsFigure 5.  $V_{OUT}$  Accuracy Over-TemperatureFigure 6.  $V_{OUT}$  vs  $V_{IN}$  at 0mA, 20mA, and -10mAFigure 7.  $I_{IN}$  vs  $V_{IN}$ , Three UnitsFigure 8.  $I_{IN}$  vs  $V_{IN}$ , Three Temperatures

Figure 9. Line Regulation, Three Units

Figure 10. Line Regulation, Three Temperatures

Figure 11. Line Regulation Over-Temperature (0mA)

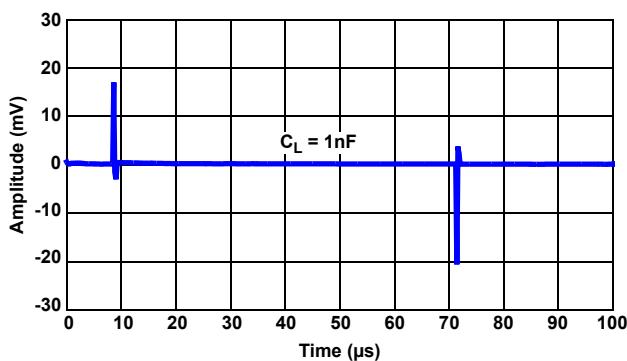

Figure 12. Line Transient with 1nF Load ( $\Delta V_{IN} = \pm 500mV$ )Figure 13. Line Transient with 100nF Load

( $\Delta V_{IN} = \pm 500mV$ )

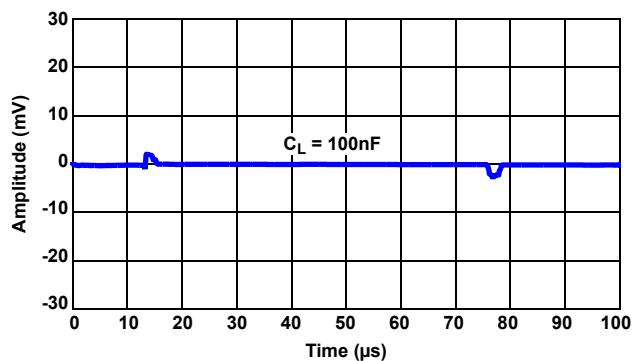

Figure 14. Load Regulation, Three Temperatures

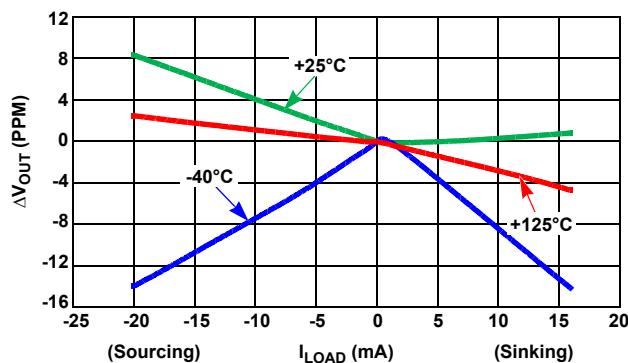

Figure 15. Load Transient ( $\Delta I_{LOAD} = \pm 1\text{mA}$ )

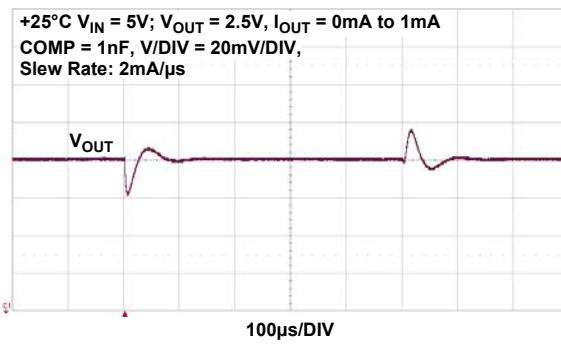

Figure 16. Load Transient (0mA to 1mA)

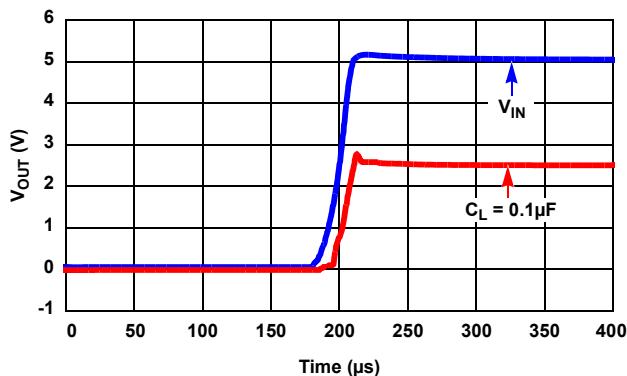

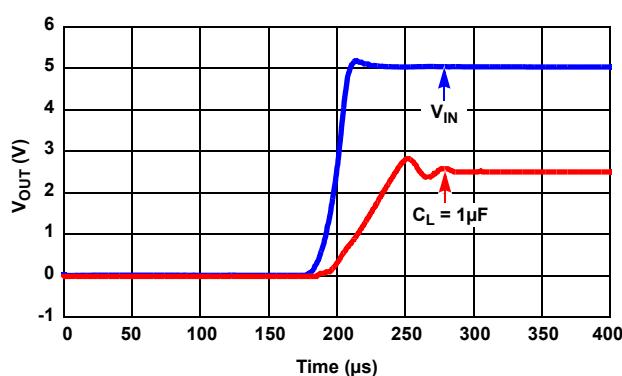

Figure 17. Turn-On Time with  $0.1\mu\text{F}$ Figure 18. Turn-On Time with  $1\mu\text{F}$

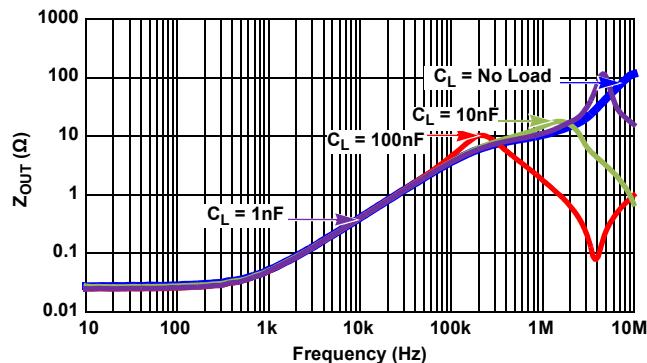

Figure 19.  $Z_{OUT}$  vs Frequency

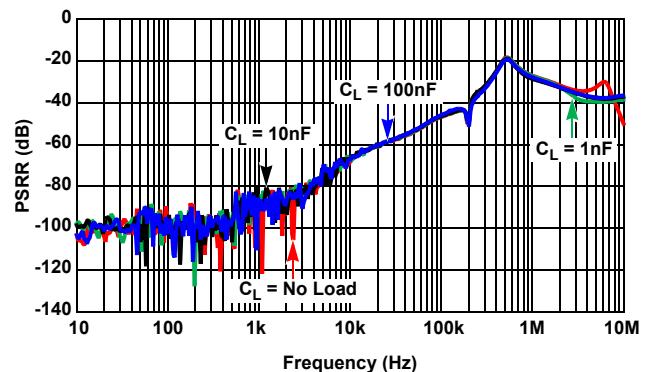

Figure 20. PSRR at Different Capacitive Loads

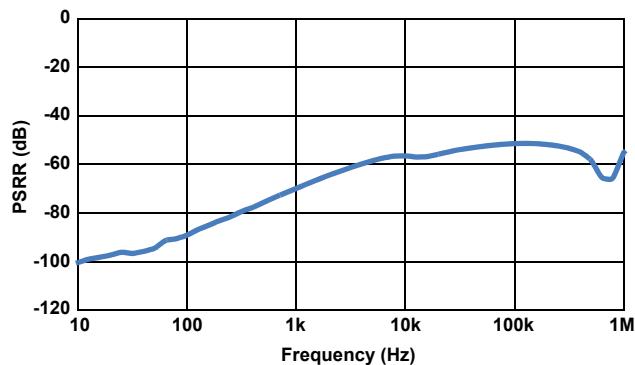

Figure 21. PSRR ( $+25^{\circ}\text{C}$ ,  $V_{IN} = 5\text{V}$ ,  $V_{OUT} = 2.5\text{V}$ ,  $I_{OUT} = 0\text{mA}$ ,  $C_{IN} = C_{OUT} = 0.1\mu\text{F}$ ,  $\text{COMP} = 1\text{nF}$ ,  $\text{VSIG} = 300\text{mV}_{\text{P-P}}$ )

Figure 22. Long Term Stability

Figure 23. Short-Circuit to GND

Figure 24. Short-Circuit to  $V_{IN}$

Figure 25. Dropout with -10mA Load

Figure 26. Dropout Voltage for 2.5V

Figure 27. V\_OUT vs Noise, 0.1Hz to 10Hz

Figure 28. Noise Density vs Frequency ( $V_{IN} = 5.0V$ ,  $I_{OUT} = 0mA$ ,  $C_{IN} = 0.1\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $COMP = 1nF$ )

## 4. Applications Information

### 4.1 Bandgap Precision Reference

The ISL71010B25 uses a bandgap architecture and special trimming circuitry to produce a temperature compensated, precision voltage reference with high input voltage capability and moderate output current drive. Low noise performance is achieved using optimized biasing techniques. Key features for precision low noise portable applications, such as handheld meters and instruments, are supply current (930 $\mu$ A) and noise (1.9 $\mu$ V<sub>P-P</sub>, 0.1Hz to 10Hz bandwidth). Data converters in particular can use the ISL71010B25 as an external voltage reference. Low power DAC and ADC circuits will realize maximum resolution with the lowest noise. The device maintains output voltage during conversion cycles with fast response, although it is helpful to add an output capacitor, typically 1 $\mu$ F.

### 4.2 Board Mounting Considerations

For applications requiring the highest accuracy, the board mounting location should be considered. The device uses a plastic SOIC package, which subjects the die to mild stresses when the Printed Circuit Board (PCB) is heated and cooled, which slightly changes the shape. Because of these die stresses, placing the device in areas subject to slight twisting can degrade the reference voltage accuracy. It is normally best to place the device near the edge of a board, or on the shortest side, because the axis of bending is most limited in that location. Mounting the device in a cutout also minimizes flex. Obviously, mounting the device on flexprint or extremely thin PC material will likewise cause loss of reference accuracy.

### 4.3 Board Assembly Considerations

Some PCB assembly precautions are necessary. Normal output voltage shifts of 100 $\mu$ V can be expected with Pb-free reflow profiles or wave solder on multi-layer FR4 PCBs. Precautions should be taken to avoid excessive heat or extended exposure to high reflow or wave solder temperatures.

### 4.4 Noise Performance and Reduction

The output noise voltage in a 0.1Hz to 10Hz bandwidth is typically 1.9 $\mu$ V<sub>P-P</sub> ( $V_{OUT} = 2.5V$ ). The noise measurement is made with a bandpass filter. The filter is made of a 1-pole high-pass filter, with a corner frequency at 0.1Hz, and a 2-pole low-pass filter, with a corner frequency (3dB) at 9.9Hz, to create a filter with a 9.9Hz bandwidth. Noise in the 10Hz to 1kHz bandwidth is approximately 1.6 $\mu$ V<sub>RMS</sub> ( $V_{OUT} = 2.5V$ ), with 0.1 $\mu$ F capacitance on the output. This noise measurement is made with a 2 decade bandpass filter. The filter is made of a 1-pole high-pass filter with a corner frequency at 10Hz of the center frequency, and 1-pole low-pass filter with a corner frequency at 1kHz. Load capacitance up to 10 $\mu$ F can be added, but will result in only marginal improvements in output noise and transient response.

### 4.5 Turn-On Time

Normal turn-on time is typically 150 $\mu$ s. The circuit designer must take this into account when looking at power-up delays or sequencing.

### 4.6 Specifying Temperature Coefficient (Box Method)

The limits stated for temperature coefficient (Tempco) are governed by the method of measurement. The overwhelming standard for specifying the temperature drift of a reference is to measure the reference voltage at two temperatures, which provide for the maximum voltage deviation. Divide the total variation, ( $V_{HIGH} - V_{LOW}$ ) by the temperature extremes of measurement ( $T_{HIGH} - T_{LOW}$ ). The result is divided by the nominal reference voltage (at  $T = +25^{\circ}C$ ) and multiplied by  $10^6$  to yield ppm/ $^{\circ}C$ . This is the "Box" method for specifying temperature coefficient.

## 4.7 Output Voltage Adjustment

The output voltage can be adjusted above and below the factory-calibrated value using the trim terminal. The trim terminal is the negative feedback divider point of the output operational amplifier. The voltage at the TRIM pin is set at approximately 1.216V by the internal bandgap and amplifier circuitry of the voltage reference.

The suggested method to adjust the output is to connect a  $1\text{M}\Omega$  external resistor directly to the trim terminal and connect the other end to the wiper of a potentiometer that has a  $100\text{k}\Omega$  resistance and with outer terminals that connect to  $V_{OUT}$  and ground. If a  $1\text{M}\Omega$  resistor is connected to trim, the output adjust range will be  $\pm 6.3\text{mV}$ . The TRIM pin should not have any capacitor tied to its output. It is important to minimize the capacitance on the trim terminal during layout to preserve output amplifier stability. It is also best to connect the series resistor directly to the trim terminal, to minimize that capacitance and also to minimize noise injection. Small trim adjustments will not disturb the factory-set temperature coefficient of the reference, but trimming near the extreme values can.

## 4.8 Output Stage

The output stage of the device has a push-pull configuration with a high-side PNP and a low-side NPN. This helps the device to act as a source and sink. The device can source 20mA and sink 10mA.

## 4.9 Use of COMP Capacitors

The reference can be compensated for the  $C_{OUT}$  capacitors used by adding a capacitor from the COMP pin to GND. See [Table 1](#) for recommended values of the COMP capacitor.

**Table 1. COMP Capacitor Recommended Values**

| $C_{OUT}$ ( $\mu\text{F}$ ) | $C_{COMP}$ ( $\text{nF}$ ) |

|-----------------------------|----------------------------|

| 0.1                         | 1                          |

| 1                           | 1                          |

| 10                          | 10                         |

## 5. Radiation Tolerance

The ISL71010B25 is a radiation tolerant device for commercial space applications, Low Earth Orbit (LEO) applications, high altitude avionics, launch vehicles, and other harsh environments. This device's response to Total Ionizing Dose (TID) radiation effects and Single-Event Effects (SEE) has been measured, characterized, and reported in the following sections. However, TID performance is not guaranteed through radiation acceptance testing, nor is the SEE characterized performance guaranteed.

### 5.1 Total Ionizing Dose (TID) Testing

#### 5.1.1 Introduction

This test was conducted to determine the sensitivity of the part to the total dose environment. Down points were 0krad(Si), 10krad(Si), 20krad(Si), and 30krad(Si). The irradiations were followed by a biased anneal for 168 hours at +100°C.

Total dose testing was performed using a Hopewell Designs N40 panoramic  $^{60}\text{Co}$  irradiator. The irradiations were performed at 0.00875rad(Si)/s. A PbAl box was used to shield the test fixture and devices under test against low energy secondary gamma radiation.

The characterization matrix consisted of 23 samples irradiated under bias and 12 samples irradiated with all pins grounded. Two control units were used to ensure repeatable data. Two different wafers were used. The bias configuration is shown in [Figure 29](#).

**Figure 29. Irradiation Bias Configuration and Power Supply Sequencing for the ISL71010B25**

All electrical testing was performed outside the irradiator using the production Automated Test Equipment (ATE), with data logging at each down point (including anneal). Downpoint electrical testing was performed at room temperature.

### 5.1.2 Results

[Table 2](#) summarizes the attributes data. “Bin 1” indicates a device that passes all datasheet specification limits.

**Table 2. ISL71010B25 Total Dose Test Attributes Data**

| Dose Rate<br>(mrad(Si)/s) | Bias                      | Sample Size | Down<br>Point | Bin 1 | Rejects |

|---------------------------|---------------------------|-------------|---------------|-------|---------|

| 8.75                      | <a href="#">Figure 29</a> | 23          | Pre-rad       | 23    | 0       |

|                           |                           |             | 10krad(Si)    | 23    | 0       |

|                           |                           |             | 20krad(Si)    | 23    | 0       |

|                           |                           |             | 30krad(Si)    | 23    | 0       |

|                           |                           | 11          | Anneal        | 11    | 0       |

| 8.75                      | Grounded                  | 12          | Pre-rad       | 12    | 0       |

|                           |                           |             | 10krad(Si)    | 12    | 0       |

|                           |                           |             | 20krad(Si)    | 12    | 0       |

|                           |                           |             | 30krad(Si)    | 12    | 0       |

|                           |                           |             | Anneal        | 12    | 0       |

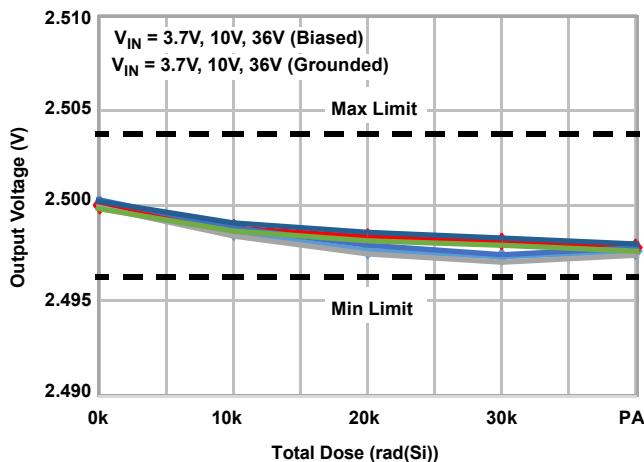

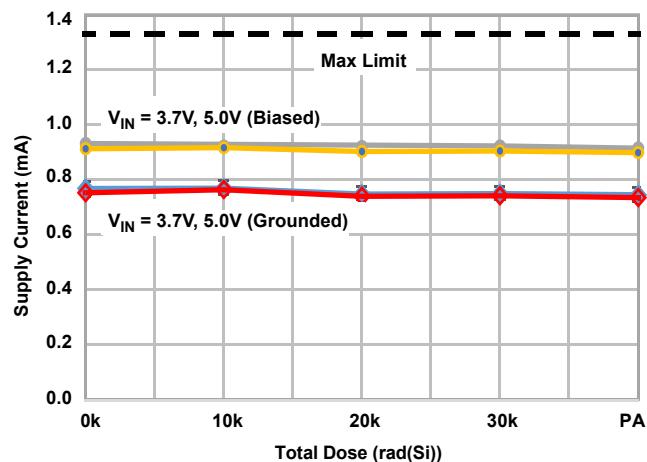

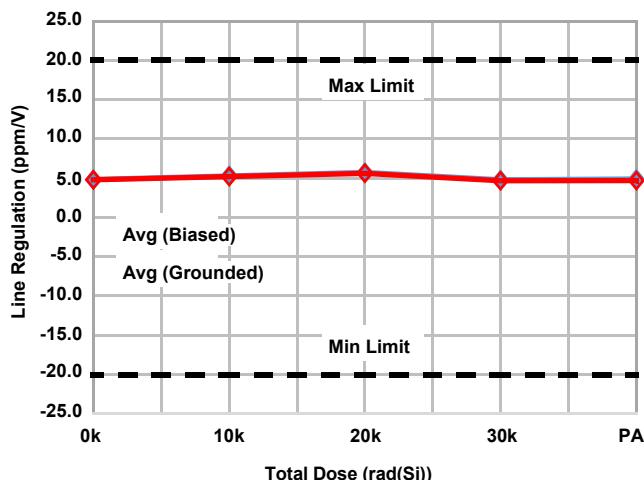

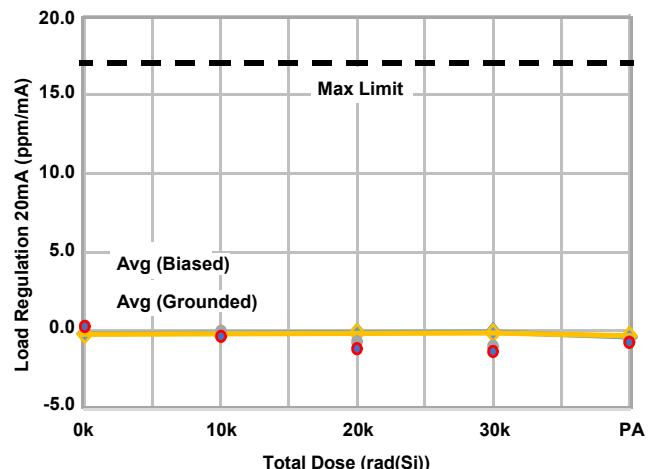

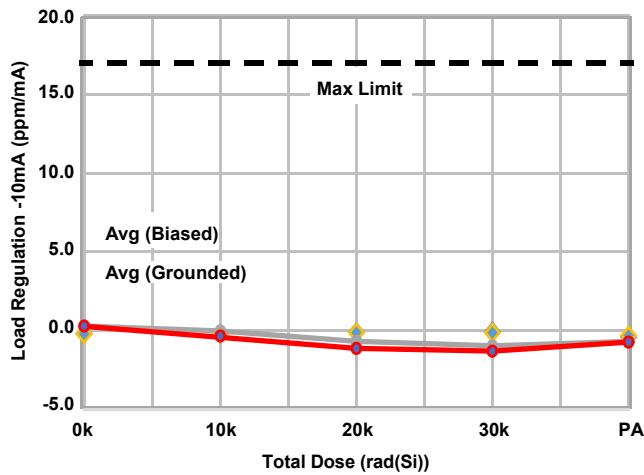

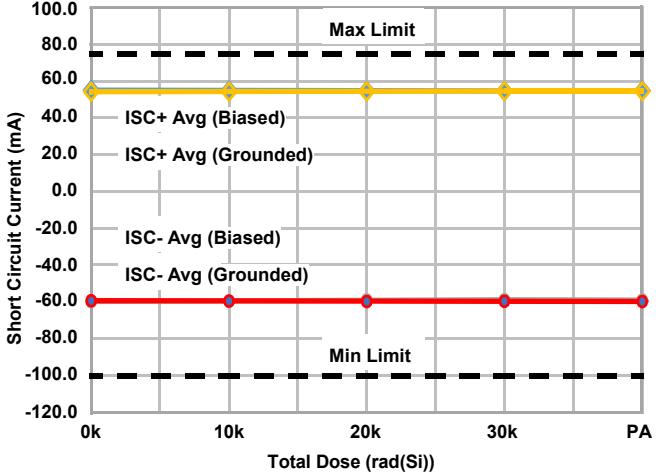

The plots in [Figures 30](#) through [35](#) show data for key parameters at all down points. The plots show the average as a function of total dose for each of the irradiation conditions; we chose to use the average because of the relatively large sample sizes. All parts showed excellent stability over irradiation.

[Table 3 on page 16](#) shows the average of the key parameters with respect to total dose in tabular form.

## 5.2 Data Plots

**Figure 30.  $V_{REF}$  Output Voltage vs TID**

**Figure 31. Supply Current vs TID**

Figure 32. Line Regulation vs TID

Figure 33. Load Regulation 20mA Sourcing vs TID

Figure 34. Load Regulation -10mA Sinking vs TID

Figure 35. Short-Circuit Current vs TID

### 5.2.1 Conclusion

ATE characterization testing showed no rejects to the datasheet limits at all down points. Variables data for selected parameters is presented in [Figures 30](#) through [35](#). No differences between biased and unbiased irradiation were noted, and the part is not considered bias sensitive.

**Table 3. ISL71010B25 Response of Key Parameters vs TID**

| Parameter             | Symbol                            | Condition                                     | Bias     | 0krad(Si) | 10krad(Si) | 20krad(Si) | 30krad(Si) | Anneal   | Unit   |

|-----------------------|-----------------------------------|-----------------------------------------------|----------|-----------|------------|------------|------------|----------|--------|

| Output Voltage        | $V_{OUT}$                         | $V_{IN} = 10V$                                | Biased   | 2.500080  | 2.498605   | 2.497645   | 2.497313   | 2.497611 | V      |

|                       |                                   |                                               | Grounded | 2.500000  | 2.498824   | 2.498346   | 2.498124   | 2.497802 |        |

|                       |                                   | $V_{IN} = 3.7V$                               | Biased   | 2.499935  | 2.498409   | 2.497462   | 2.497026   | 2.497399 |        |

|                       |                                   |                                               | Grounded | 2.499851  | 2.498677   | 2.498152   | 2.497917   | 2.497603 |        |

|                       |                                   | $V_{IN} = 36V$                                | Biased   | 2.500326  | 2.498840   | 2.497926   | 2.497422   | 2.497796 |        |

|                       |                                   |                                               | Grounded | 2.500239  | 2.499098   | 2.498607   | 2.498295   | 2.497983 |        |

| Supply Current        | $I_{IN}$                          | $V_{CC} = 3.7V$                               | Biased   | 0.76974   | 0.77023    | 0.74926    | 0.75103    | 0.74642  | mA     |

|                       |                                   |                                               | Grounded | 0.75359   | 0.76480    | 0.74092    | 0.74276    | 0.73603  |        |

|                       |                                   | $V_{CC} = 5.0V$                               | Biased   | 0.93293   | 0.92385    | 0.92188    | 0.92347    | 0.91606  |        |

|                       |                                   |                                               | Grounded | 0.91372   | 0.91735    | 0.90389    | 0.90546    | 0.89972  |        |

| Line Regulation       | $\Delta V_{OUT} / \Delta V_{IN}$  | $V_{IN} = 4V \text{ to } 30V, V_{OUT} = 2.5V$ | Biased   | 4.843     | 5.348      | 5.744      | 4.807      | 4.909    | ppm/V  |

|                       |                                   |                                               | Grounded | 4.807     | 5.214      | 5.626      | 4.687      | 4.712    |        |

| Load Regulation       | $\Delta V_{OUT} / \Delta I_{OUT}$ | 20mA Sourcing                                 | Biased   | -0.193    | -0.219     | -0.108     | -0.079     | -0.388   | ppm/mA |

|                       |                                   |                                               | Grounded | -0.221    | -0.200     | -0.128     | -0.135     | -0.314   |        |

|                       |                                   | -10mA Sinking                                 | Biased   | 0.296     | -0.026     | -0.684     | -0.978     | -0.681   |        |

|                       |                                   |                                               | Grounded | 0.285     | -0.350     | -1.133     | -1.315     | -0.736   |        |

| Short-Circuit Current | $I_{SC+}$                         | $V_{OUT} = GND$                               | Biased   | 55.141    | 54.819     | 54.668     | 54.693     | 54.805   | mA     |

|                       |                                   |                                               | Grounded | 54.246    | 54.329     | 54.520     | 54.541     | 54.617   |        |

|                       | $I_{SC-}$                         | $V_{OUT} = V_{IN}$                            | Biased   | -59.807   | -59.662    | -59.012    | -58.797    | -58.995  |        |

|                       |                                   |                                               | Grounded | -59.332   | -59.485    | -59.814    | -59.613    | -59.724  |        |

## 5.3 Single-Event Effects Testing

### 5.3.1 Introduction

The intense heavy ion environment encountered in space applications can cause a variety of Single-Event Effects (SEE). SEE can lead to system-level performance issues including disruption, degradation, and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response. The following is a summary of the ISL71010B25 SEE testing.

### 5.3.2 SEE Test Setup

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility.

A schematic of the ISL71010B25 SEE test circuit is shown in [Figure 42 on page 19](#). The test circuit is configured to accept an input voltage from 4V to 30V and generate the 2.5V nominal output voltage. The output current of the reference was adjusted using fixed load resistors on test board. The output capacitor,  $C_4$ , and the compensation capacitor  $C_2$  were 0.1 $\mu$ F and 1nF, respectively.

Digital multimeters were used to monitor input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and input current ( $I_{IN}$ ). A LeCroy Waverunner digital oscilloscope was used to monitor, capture and store key signal waveforms. The scope was configured to trigger with  $V_{OUT}$  signal levels of  $\pm 20mV$ .

### 5.3.3 SEB Testing Results

For the SEB tests, conditions were selected to maximize the electrical and thermal stresses on the Device Under Test (DUT), thus insuring worst-case conditions. The input voltage ( $V_{IN}$ ) was initially set to 35V and then increased in 1V increments. The output current ( $I_{OUT}$ ) was set to 20mA which is the maximum recommended current rating for load regulation of the device. Case temperature was maintained at +125°C by controlling the current flowing into a resistive heater bonded to the underside of the DUT. Four DUTs were irradiated with Ag ions at a normal incident angle, resulting in an effective LET of 43MeV•cm<sup>2</sup>/mg.

The failure criterion for destructive SEE was an increase in operating input current ( $I_{IN}$ ) greater than 5% measured at 20mA output current.  $I_{IN}$  is defined as the total current drawn by the device. Failed devices were not further irradiated.

Four parts passed irradiation to  $1 \times 10^7$  ions/cm<sup>2</sup> with 43MeV•cm<sup>2</sup>/mg at 39V and +125°C case temperature.

### 5.3.4 Single-Event Transient Testing

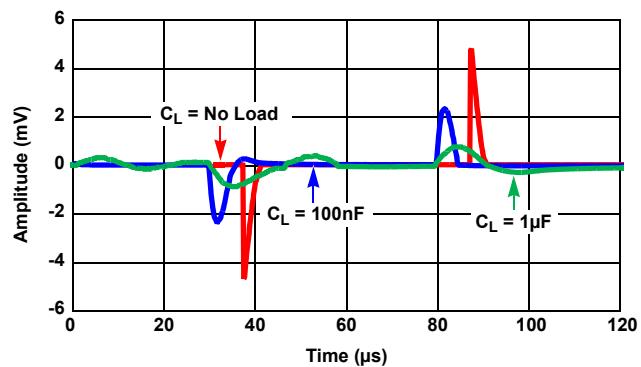

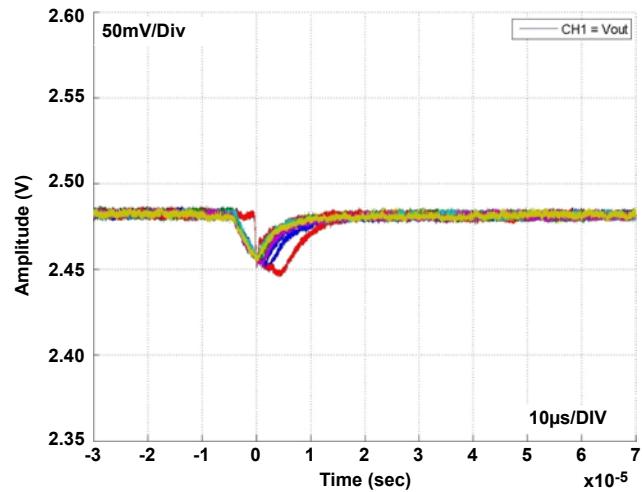

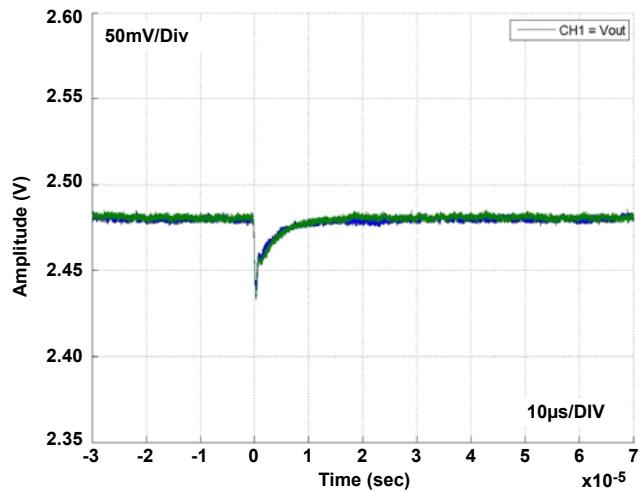

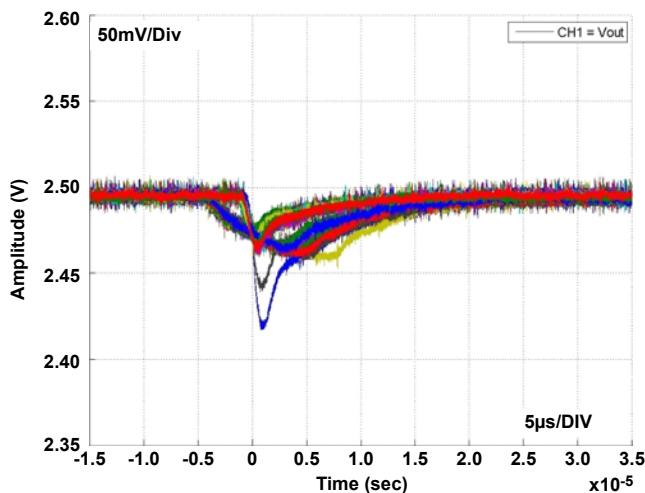

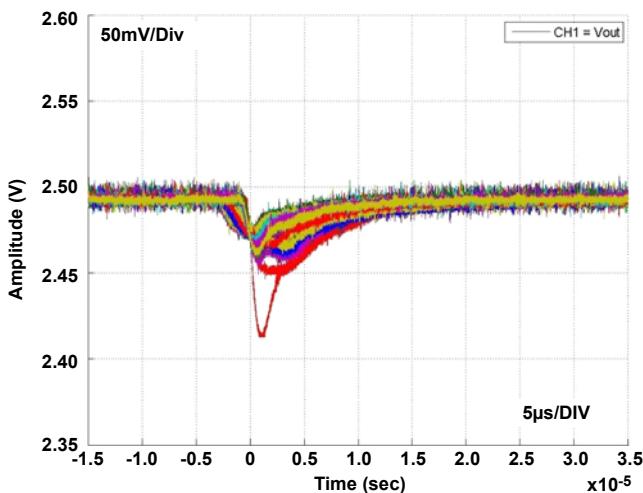

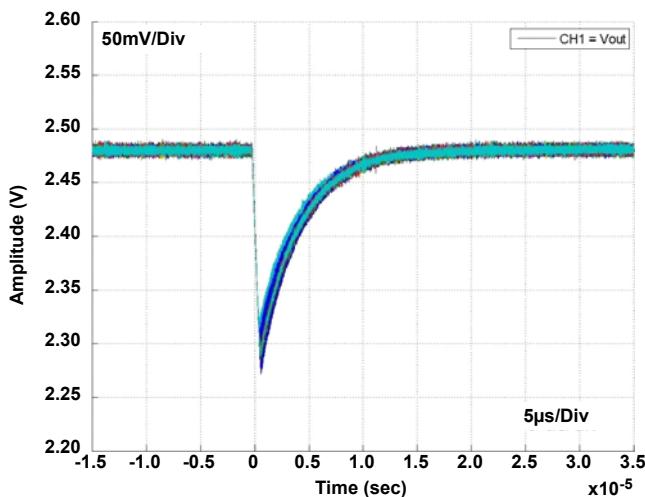

SET testing was done on four samples of the ISL71010B25, which were irradiated at room temperature across a range of LET from 2.7MeV•cm<sup>2</sup>/mg to 28MeV•cm<sup>2</sup>/mg to observe SET performance. Samples were separately tested to  $V_{IN}$  of 4V and 30V. The parts were configured with a 0.1μF output capacitor, a 1nF compensation capacitor, and a 20mA load current to set up the worst conditions for negative going transients. [Table 4](#) shows the SET summary giving the cross section for each input voltage and LET level.

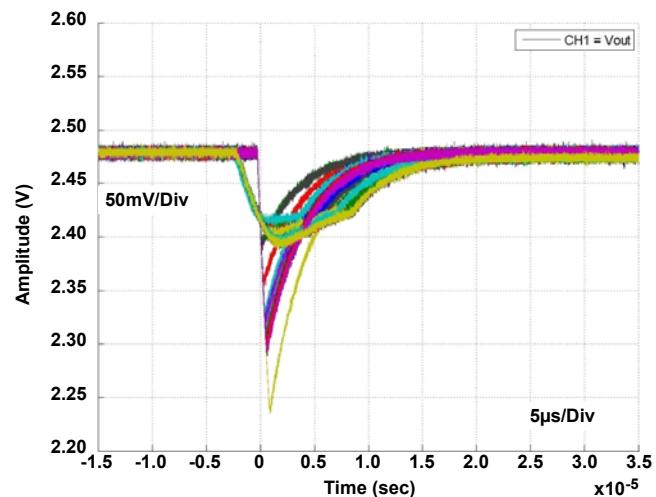

[Figures 36](#) through [41](#) represent output waveform responses of the DUTs at the respective bias conditions and LET levels. The plots are composites of all the transients captured on the scope.

The worst case SET appeared for the case of LET = 28 and  $V_{IN}$  = 30V with about 235mV in negative SET and a recovery time of about 20μs.

**Table 4. SET Summary of the Fully Functional ISL71010B25**

| Supply Voltage (V) | Ion/Angle | Eff LET (MeV•cm <sup>2</sup> /mg) | Fluence per Run (Particles/cm <sup>2</sup> ) | Number of Runs | Total SET | Events CS (cm <sup>2</sup> ) |

|--------------------|-----------|-----------------------------------|----------------------------------------------|----------------|-----------|------------------------------|

| 4                  | Ne/0      | 2.7                               | 2.00E+06                                     | 4              | 40        | 5.00E-06                     |

| 30                 | Ne/0      | 2.7                               | 2.00E+06                                     | 4              | 6         | 7.50E-07                     |

| 4                  | Ar/0      | 8.5                               | 2.00E+06                                     | 4              | 256       | 3.20E-05                     |

| 30                 | Ar/0      | 8.5                               | 2.00E+06                                     | 4              | 365       | 4.56E-05                     |

| 4                  | Kr/0      | 28                                | 2.00E+06                                     | 4              | 439       | 5.49E-05                     |

| 30                 | Kr/0      | 28                                | 2.00E+06                                     | 4              | 754       | 9.43E-05                     |

Note: Samples at 4.0V and 30V input voltage,  $C_{OUT}$  = 0.1μF,  $C_{COMP}$  = 1nF and  $I_{OUT}$  = 20mA. Trigger level for the output voltage set to ±20mV.

### 5.3.5 Data Plots

Figure 36. Composite SET Plot for ISL71010B25 at LET 2.7

$V_{IN} = 4V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

Figure 37. Composite SET Plot for ISL71010B25 at LET 2.7

$V_{IN} = 30V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

Figure 38. Composite SET Plot for ISL71010B25 at LET 8.5

$V_{IN} = 4V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

Figure 39. Composite SET Plot for ISL71010B25 at LET 8.5

$V_{IN} = 30V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

Figure 40. Composite SET Plot for ISL71010B25 at LET 28

$V_{IN} = 4V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

Figure 41. Composite SET Plot for ISL71010B25 at LET 28

$V_{IN} = 30V$ ,  $I_{OUT} = 20mA$ ,  $C_{OUT} = 0.1\mu F$ ,  $C_{COMP} = 1nF$

### 5.3.6 Conclusion

SEE testing has demonstrated that the ISL71010B25 is not susceptible to Single Event Burnout (SEB) at an LET of  $43\text{MeV}\cdot\text{cm}^2/\text{mg}$  with an input voltage of 39V and a load current of 20mA. This represents conditions that are over 30% above the recommended input voltage of 30V and 100% of the load regulation drive capability of the IC (20mA).

SET testing demonstrated that all transients are negative and the higher the LET level, the greater the magnitude of the negative transient. At LET =  $28\text{MeV}\cdot\text{cm}^2/\text{mg}$  and  $V_{IN} = 30V$  with  $C_{OUT} = 0.10\mu F$ , showed a 235mV negative transient during an SET event. The longest recovery times were about  $20\mu s$ .

A larger  $C_{OUT}$  capacitance value will suppress the SET magnitude but the SET disturbance duration will stretch out. Capacitor selection represents a compromise between SET magnitude and recovery duration.

Figure 42. SEE Testing Schematic for the ISL71010B25

## 6. Revision History

| Rev. | Date         | Description                                                                                                                                                                                                       |

|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00 | Apr 12, 2018 | Added Outgassing Feature bullet.<br>Updated Ordering information by adding -TK part to table and updated Note 1.<br>Added Outgassing specification information.<br>Removed About Intersil and updated disclaimer. |

| 0.00 | Sep 26, 2017 | Initial release                                                                                                                                                                                                   |

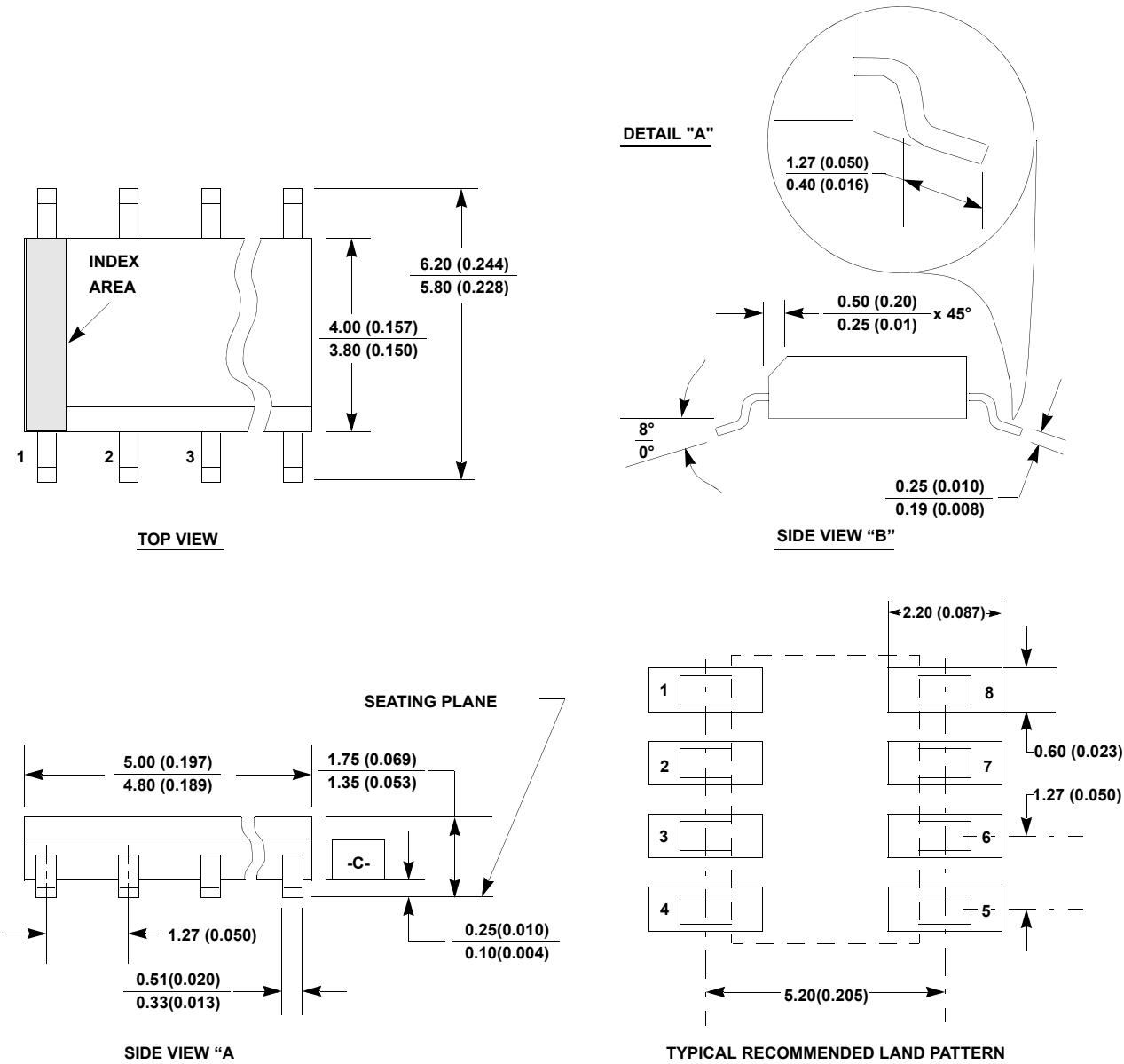

## 7. Package Outline Drawing

M8.15

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

Rev 4, 1/12

For the most recent package outline drawing, see [M8.15](#).

### NOTES:

1. Dimensioning and tolerancing per ANSI Y14.5M-1994.

2. Package length does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

3. Package width does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

5. Terminal numbers are shown for reference only.

6. The lead width as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

7. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

8. This outline conforms to JEDEC publication MS-012-AA ISSUE C.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

**Данный компонент на территории Российской Федерации****Вы можете приобрести в компании MosChip.**

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

<http://moschip.ru/get-element>

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибуторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ Р В 0015-002 и ЭС РД 009

**Офис по работе с юридическими лицами:**

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: [info@moschip.ru](mailto:info@moschip.ru)

Skype отдела продаж:

moschip.ru

moschip.ru\_4

moschip.ru\_6

moschip.ru\_9