### TISP61089D, TISP61089SD, TISP61089AD, TISP61089ASD

IPP = 100 A, 2/10

12

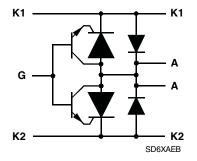

### DUAL FORWARD-CONDUCTING P-GATE THYRISTORS PROGRAMMABLE OVERVOLTAGE PROTECTORS

BOURNS®

## **TISP61089 Gated Protector Series**

#### **Overvoltage Protection for Negative Rail SLICs**

#### Dual Voltage-Tracking Protectors

- '61089A for Battery Voltages to ......-100 V

### Rated for GR-1089-CORE and K.44 Impulses

| Impulse W       | IPPSM     |    |

|-----------------|-----------|----|

| Voltage Current |           | Α  |

| 2/10            | 2/10 2/10 |    |

| 10/700          | 5/310     | 40 |

| 10/1000         | 10/1000   | 30 |

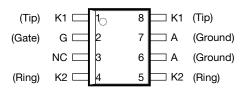

### D Package Top View and Device Symbol for Feed-Thru Pin-Out

NC - No internal connection Terminal typical application names shown in parenthesis MDEXEDa

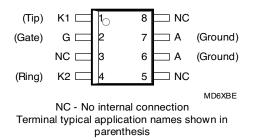

### D Package Top View and Device Symbol for Shunt (SD) Pin-Out

Diode 8

2/10 Overshoot Voltage Specified

Element

SCR

Package Options - Surface Mount 8-pin Small-Outline Line Feed-Thru Connection (D) Shunt Version Connection (SD)

#### How To Order

| Device                              | Package           | Carrier | Order As          | Device             | Package           | Carrier | Order As        |

|-------------------------------------|-------------------|---------|-------------------|--------------------|-------------------|---------|-----------------|

| TISP61089                           | D (Small-Outline) | R†      | TISP61089DR-S     | TISP61089A         | D (Small-Outline) | R†      | TISP61089ADR-S  |

| TISP61089S                          | D (Small-Outline) | R†      | TISP61089SDR-S    | TISP61089AS        | D (Small-Outline) | R†      | TISP61089ASDR-S |

| † Carrier R is Embossed Tape Reeled |                   |         | † Carrier R is Em | bossed Tape Reelec | 1                 |         |                 |

\*RoHS Directive 2002/95/EC Jan 27 2003 including Annex NOVEMBER 1995 - REVISED JULY 2008 Specifications are subject to change without notice. Customers should verify actual device performance in their specific applications.

# BOURNS®

### Description

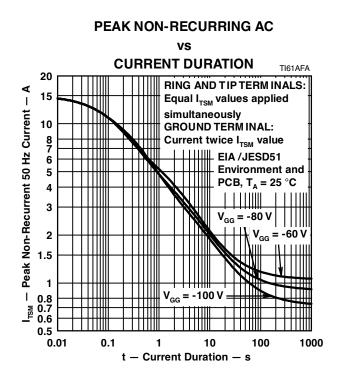

These '61089 parts are all dual forward-conducting buffered p-gate thyristor (SCR) overvoltage protectors. They are designed to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. The '61089 limits voltages that exceed the SLIC supply rail voltage. The '61089 parameters are specified to allow equipment compliance with Telcordia (formally Bellcore) GR-1089-CORE and ITU-T recommendations K.20, K.21 and K.45.

The SLIC line driver section is typically powered from 0 V (ground) and a negative (battery) voltage. The protector gate is connected to this negative supply. This references the protection (clipping) voltage to the negative supply voltage. The protection voltage will then track the negative supply voltage and the overvoltage stress on the SLIC is minimized.

Positive overvoltages are clipped to ground by diode forward conduction. Negative overvoltages are initially clipped close to the SLIC negative supply rail value. If sufficient current is available from the overvoltage, then the protector SCR will switch into a low voltage on-state condition. As the overvoltage subsides the high holding current of '61089 SCR helps prevent d.c. latchup.

The '61089 is intended to be used with a series resistance of at least 25  $\Omega$  and a suitable overcurrent function for Telcordia compliance. Power fault conditions require a series overcurrent element which either interrupts or reduces the circuit current before the '61089 current rating is exceeded. For equipment compliant to ITU-T recommendations K.20 or K.21 or K.45 only, the series resistor value is set by the coordination requirements. For coordination with a 400 V limit GDT, a minimum series resistor value of 10  $\Omega$  is recommended.

The '61089 buffered gate design reduces the loading on the SLIC supply during overvoltages caused by power cross and induction. The regular pin-out for surface mount and through-hole packages is a feed through configuration. Connection to the SLIC is made via the '61089, Ring through pins 4 - 5 and Tip through pins 1 - 8. A non-feed-through surface mount (D) package is available. This shunt (SD) version pin-out does not make duplicate connections to pin 5 and pin 8 which increases package creepage distance from ground of the other connections from about 0.7 mm to over 3 mm. High voltage ringing SLICs, with battery voltages below -100 V and down to -155 V, can be protected by the TISP61089B device. Details of this device are in the TISP61089B data sheet.

### Absolute Maximum Ratings, -40 $^{\circ}C \le T_{,I} \le 85 ^{\circ}C$ (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                                                                                                                                                                                                 |                   | Symbol                           | Value       | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|-------------|------|

| Repetitive peak off-state voltage, $V_{GK} = 0$                                                                                                                                                                                                                                                                                                                                        | V <sub>DRM</sub>  | -100<br>-120                     | v           |      |

| Repetitive peak gate-cathode voltage, V <sub>KA</sub> = 0                                                                                                                                                                                                                                                                                                                              | V <sub>GKRM</sub> | -85<br>-120                      | v           |      |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)<br>10/1000 μs (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Se<br>5/320 μs (ITU-T K.20, K.21& K.45, K.44 open-circuit voltage wave shape 10/<br>1.2/50 μs (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Sect<br>2/10 μs (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Section | IPPSM             | 30<br>40<br>100<br>120           | А           |      |

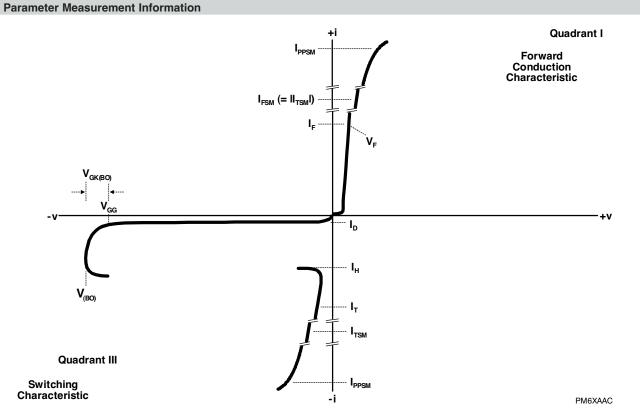

| Non-repetitive peak on-state current, V <sub>GG</sub> = -75 V, 50 Hz to 60 Hz (see Notes 1 and 2<br>0.1 s<br>1 s<br>5 s<br>300 s<br>900 s                                                                                                                                                                                                                                              | I <sub>TSM</sub>  | 11<br>4.8<br>2.7<br>0.95<br>0.93 | A           |      |

| Non-repetitive peak gate current, 1/2 $\mu s$ pulse, cathodes commoned (see Notes 1 a                                                                                                                                                                                                                                                                                                  | nd 2)             | IGSM                             | +40         | A    |

| Operating free-air temperature range                                                                                                                                                                                                                                                                                                                                                   |                   |                                  | -40 to +85  | °C   |

| Junction temperature                                                                                                                                                                                                                                                                                                                                                                   |                   | Tj                               | -40 to +150 | °C   |

| Storage temperature range                                                                                                                                                                                                                                                                                                                                                              |                   | T <sub>stg</sub>                 | -40 to +150 | °C   |

NOTES: 1. Initially the protector must be in thermal equilibrium with -40 °C ≤ T<sub>J</sub> ≤ 85 °C. The surge may be repeated after the device returns to its initial conditions. Gate voltage ranges are -20 V to -75 V for the '61089 and -20 V to -100 V for the '61089A.

2. The rated current values may be applied either to the Ring to Ground or to the Tip to Ground terminal pairs. Additionally, both terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the rated current value of an individual terminal pair). Above 85 °C, derate linearly to zero at 150 °C lead temperature.

# BOURNS®

### **Recommended Operating Conditions**

|                                          | Component                                                                           |     |     | Max | Unit |

|------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>G</sub> Gate decoupling capacitor |                                                                                     | 100 | 220 |     | nF   |

|                                          | Series resistor for GR-1089-CORE first-level surge survival                         | 25  |     |     | Ω    |

| P.                                       | Series resistor for GR-1089-CORE first-level and second-level surge survival        |     |     |     | Ω    |

| ns                                       | R <sub>S</sub> Series resistor for GR-1089-CORE intra-building port surge survival  |     |     |     | Ω    |

|                                          | Series resistor for K.20, K.21 and K.45 coordination with a 400 V primary protector |     |     |     | Ω    |

### Electrical Characteristics, T<sub>J</sub> = 25 $^{\circ}$ C (Unless Otherwise Noted)

| Parameter                             |                                                                                                                          | Test Conditions                                                                                                         | Min  | Тур | Мах | Unit |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|

| ID Off-state current                  | $V_D = V_{DBM}, V_{GK} = 0$ $T_J = 25 °C$                                                                                |                                                                                                                         |      | -5  | μA  |      |  |

| U                                     | On-State Current                                                                                                         | $T_{\rm J} = 85 ^{\circ}{\rm C}$                                                                                        |      |     | -50 | μΑ   |  |

|                                       |                                                                                                                          | 2/10 μs, I <sub>PP</sub> = -56 A, R <sub>S</sub> = 45 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF               |      | -57 |     | v    |  |

| V <sub>(BO)</sub>                     | Breakover voltage                                                                                                        | 2/10 μs, I <sub>PP</sub> = -100 A, R <sub>S</sub> = 50 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF              |      | -60 |     |      |  |

| • (BO)                                | Diodito vol voltago                                                                                                      | 1.2/50 μs, I <sub>PP</sub> = -53 A, R <sub>S</sub> = 47 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF             |      | -60 |     | •    |  |

|                                       |                                                                                                                          | 1.2/50 μs, I <sub>PP</sub> = -96 A, R <sub>S</sub> = 52 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF             |      | -64 |     |      |  |

|                                       |                                                                                                                          | 2/10 μs, I <sub>PP</sub> = -56 A, R <sub>S</sub> = 45 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF               |      | 9   |     |      |  |

| Vara                                  | Gate-cathode impulse                                                                                                     | 2/10 μs, I <sub>PP</sub> = -100 A, R <sub>S</sub> = 50 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF              |      | 12  |     | v    |  |

| V <sub>GK(BO)</sub> breakover voltage | 1.2/50 μs, I <sub>PP</sub> = -53 A, R <sub>S</sub> = 47 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF              |                                                                                                                         | 12   |     | v   |      |  |

|                                       | 1.2/50 $\mu$ s, I <sub>PP</sub> = -96 A, R <sub>S</sub> = 52 $\Omega$ , V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF |                                                                                                                         | 16   |     |     |      |  |

| V <sub>F</sub>                        | Forward voltage                                                                                                          | $I_F = 5 \text{ A}, t_w = 200 \ \mu \text{s}$                                                                           |      |     | 3   | V    |  |

| , Peak forward recovery               | 2/10 μs, I <sub>PP</sub> = 56 A, R <sub>S</sub> = 45 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF                 |                                                                                                                         | 6    |     |     |      |  |

|                                       | Peak forward recovery                                                                                                    | 2/10 μs, I <sub>PP</sub> = 100 A, R <sub>S</sub> = 50 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF               |      | 8   |     | v    |  |

| V <sub>FRM</sub>                      | voltage                                                                                                                  | 1.2/50 μs, I <sub>PP</sub> = 53 A, R <sub>S</sub> = 47 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF              |      | 8   |     |      |  |

|                                       |                                                                                                                          | 1.2/50 $\mu$ s, I <sub>PP</sub> = 96 A, R <sub>S</sub> = 52 $\Omega$ , V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF |      | 12  |     |      |  |

| Ι <sub>Η</sub>                        | Holding current                                                                                                          | I <sub>T</sub> = -1 A, di/dt = 1A/ms, V <sub>GG</sub> = -48 V                                                           | -150 |     |     | mA   |  |

|                                       | 0.1                                                                                                                      | $T_{\rm J} = 25 ^{\circ}{\rm C}$                                                                                        |      |     | -5  | μΑ   |  |

| I <sub>GKS</sub>                      | Gate reverse current                                                                                                     | $V_{GG} = V_{GK} = V_{GKRM}, V_{KA} = 0$ $T_{J} = 85 \text{ °C}$                                                        |      |     | -50 | μA   |  |

| I <sub>GT</sub>                       | Gate trigger current                                                                                                     | $I_T = -3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s},  V_{GG} = -48 \text{ V}$                                             |      |     | 5   | mA   |  |

| V <sub>GT</sub>                       | Gate-cathode trigger voltage                                                                                             | $I_T = -3 \text{ A}, t_{p(g)} \ge 20 \mu\text{s}, V_{GG} = -48 \text{ V}$                                               |      |     | 2.5 | V    |  |

| Q <sub>GS</sub>                       | Gate switching charge                                                                                                    | 1.2/50 μs, I <sub>PP</sub> = -53 A, R <sub>S</sub> = 47 Ω, V <sub>GG</sub> = -48 V, C <sub>G</sub> = 220 nF             |      | 0.1 |     | μC   |  |

| 0                                     | Cathode-anode off-                                                                                                       | $V_D = -3 V$                                                                                                            |      |     | 100 | pF   |  |

| C <sub>KA</sub>                       | state capacitance                                                                                                        | f = 1 MHz, $V_d$ = 1 V, $I_G$ = 0, (see Note 3)<br>$V_D$ = -48 V                                                        |      |     | 50  | pF   |  |

NOTES: 3. These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

### **Thermal Characteristics**

| Parameter        |                                         | Test Conditions                                                                                   |           | Min | Тур | Мах | Unit |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|------|

| R <sub>0JA</sub> | Junction to free air thermal resistance | $T_A = 25 \text{ °C}, EIA/JESD51-3$<br>PCB, EIA/JESD51-2<br>environment, P <sub>TOT</sub> = 1.7 W | D Package |     |     | 120 | °C/W |

BOURNS®

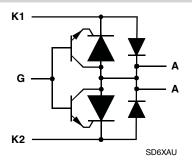

Figure 1. Voltage-Current Characteristic Unless Otherwise Noted, All Voltages are Referenced to the Anode

BOURNS®

Thermal Information

Figure 2. Non-repetitive Peak On-State Current against Duration (Gate Voltage Ranges are -20 V to -75 V for the '61089 and -20 V to -100 V for the '61089A)

## BOURNS®

### **APPLICATIONS INFORMATION**

### **Gated Protectors**

This section covers three topics. First, it is explained why gated protectors are needed. Second, the voltage limiting action of the protector is described. Third, an example application circuit is described.

#### **Purpose of Gated Protectors**

Fixed voltage thyristor overvoltage protectors have been used since the early 1980s to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. As the SLIC was usually powered from a fixed voltage negative supply rail, the limiting voltage of the protector could also be a fixed value. The TISP1072F3 is a typical example of a fixed voltage SLIC protector.

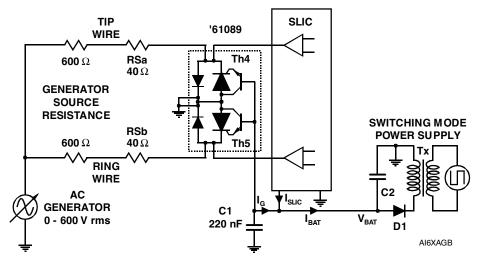

SLICs have become more sophisticated. To minimize power consumption, some designs automatically adjust the supply voltage, V<sub>BAT</sub>, to a value that is just sufficient to drive the required line current. For short lines the supply voltage would be set low, but for long lines, a higher supply voltage would be generated to drive sufficient line current. The optimum protection for this type of SLIC would be given by a protection voltage which tracks the SLIC supply voltage. This can be achieved by connecting the protection thyristor gate to the SLIC supply, Figure 3. This gated (programmable) protection arrangement minimizes the voltage stress on the SLIC, no matter what value of supply voltage.

#### **Operation of Gated Protectors**

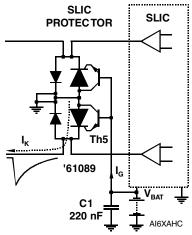

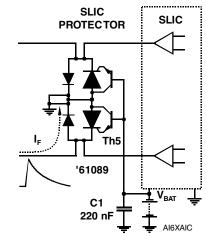

Figures 4 and 5 show how the '61089 device limits negative and positive overvoltages. Positive overvoltages (Figure 5) are clipped by the antiparallel diodes in the '61089 protector and the resulting current is diverted to ground. Negative overvoltages (Figure 4) are initially clipped close to the SLIC negative supply rail value ( $V_{BAT}$ ). If sufficient current is available from the overvoltage, then the protector (Th5) will crowbar into a low voltage on-state condition. As the overvoltage subsides the high holding current of the crowbar prevents d.c. latchup. The protection voltage will be the sum of the gate supply ( $V_{BAT}$ ) and the peak gate-cathode voltage ( $V_{GK(BO)}$ ). The protection voltage will be increased if there is a long connection between the gate decoupling capacitor, C1, and the gate terminal. During the initial rise of a fast impulse, the gate current ( $I_G$ ) is the same as the cathode current ( $I_{K}$ ). Rates of 70 A/µs can cause inductive voltages of 0.7 V in 2.5 cm of printed wiring track. To minimize this inductive voltage increase of protection voltage, the length of the capacitor to gate terminal tracking should be minimized. Inductive voltages in the protector cathode wiring will also increase the protection voltage. These voltages can be minimized by routing the SLIC connection through the protector as shown in Figure 3.

#### **Application Circuit**

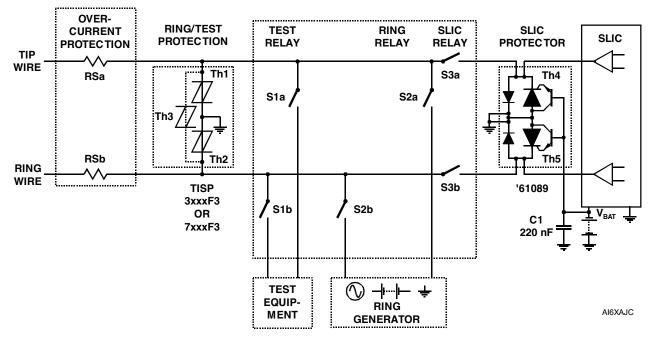

Figure 6 shows a typical '61089 part SLIC card protection circuit. The incoming line conductors, Ring (R) and Tip (T), connect to the relay matrix via the series overcurrent protection. Fusible resistors, fuses and positive temperature coefficient (PTC) thermistors can be used for overcurrent protection. Resistors will reduce the prospective current from the surge generator for both the '61089 device and the ring/test

## BOURNS®

### **APPLICATIONS INFORMATION**

### **Application Circuit (Continued)**

protector. The TISP7xxxF3 protector has the same protection voltage for any terminal pair. This protector is used when the ring generator configuration may be ground or battery-backed. For dedicated ground-backed ringing generators, the TISP3xxxF3 gives better protection as its inter-conductor protection voltage is twice the conductor to ground value.

Relay contacts 3a and 3b connect the line conductors to the SLIC via the '61089 protector. The protector gate reference voltage comes from the SLIC negative supply ( $V_{BAT}$ ). A 220 nF gate capacitor sources the high gate current pulses caused by fast rising impulses.

Figure 4. Negative Overvoltage Condition

Figure 5. Positive Overvoltage Condition

Figure 6. Typical Application Circuit

# BOURNS®

### **MECHANICAL DATA**

### **Device Symbolization Code**

Devices will be coded as below.

| Device          | Symbolization Code |

|-----------------|--------------------|

| TISP61089DR-S   | P61089             |

| TISP61089SDR-S  | 61089S             |

| TISP61089ADR-S  | 61089A             |

| TISP61089ASDR-S | 1089AS             |

"TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.З, офис 1107

### Данный компонент на территории Российской Федерации

Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г.Москва, ул.Щербаковская д.3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж: moschip.ru moschip.ru\_4

moschip.ru\_6 moschip.ru\_9