## **MAX13253**

## 1A, Spread-Spectrum, Push-Pull, Transformer Driver for Isolated Power Supplies

## **General Description**

The MAX13253 is a 1A, push-pull, transformer driver designed to provide a simple solution for low-EMI isolated power supplies. The MAX13253 has an internal oscillator and operates from a single +3.0V to +5.5V supply. The transformer's secondary-to-primary winding ratio defines the output voltage, allowing selection of virtually any isolated output voltage with galvanic isolation.

The MAX13253 features an integrated oscillator driving a pair of n-channel power switches. The driver includes pin-selectable spread-spectrum oscillation and a well-controlled slew rate to reduce EMI. The MAX13253 can optionally be driven by an external clock to further manage EMI. Internal circuitry guarantees a fixed 50% duty cycle to prevent DC current flow through the transformer, regardless of which clock source is used.

The MAX13253 operates with up to 1A of continuous current and features integrated protection including fault detection, overcurrent protection, and thermal shutdown.

The MAX13253 includes a low-current shutdown mode to reduce the overall supply current to less than  $5\mu A$  (max) when the driver is disabled.

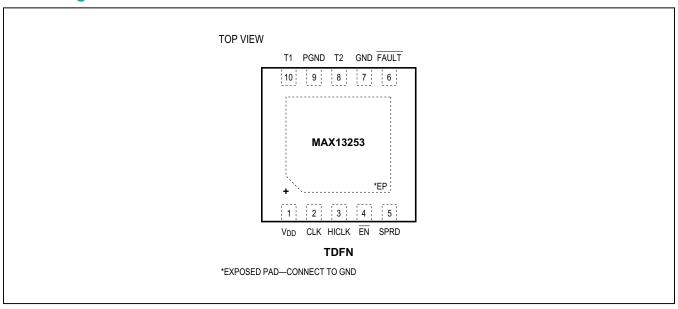

The MAX13253 is available in a small 10-pin (3mm x 3mm) TDFN package and is specified over the -40°C to +125°C temperature range.

#### **Features and Benefits**

- Simple, Flexible Design

- +3.0V to +5.5V Supply Range

- Low R<sub>ON</sub> 300mΩ (max) at 4.5V

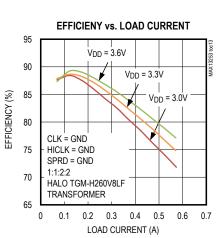

- · Up to 90% Efficiency

- · Provides Up to 1A to the Transformer

- · Internal or External Clock Source

- Internal Oscillator Frequency: 250kHz or 600kHz

- · Optional Spread-Spectrum Oscillation

- -40°C to +125°C Temperature Range

- Integrated System Protection

- · Fault Detection and Indication

- · Overcurrent Limiting

- · Undervoltage Lockout

- · Thermal Shutdown

- · Saves Space on Board

- Small 10-Pin TDFN Package (3mm x 3mm)

## **Applications**

- Power Meter Data Interface

- · Isolated Fieldbus Interface

- Medical Equipment

- Isolated Analog Front-End

- Isolated USB Power

Ordering Information appears at end of data sheet.

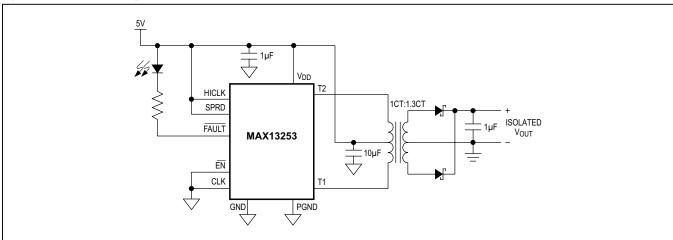

## **Typical Operating Circuit**

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX13253.related.

## **Absolute Maximum Ratings**

| (All voltages referenced to GND.)              |                |

|------------------------------------------------|----------------|

| V <sub>DD</sub> , FAULT, CLK, HICLK, SPRD, EN  | 0.3V to +6V    |

| T1, T2                                         | 0.3V to +16.5V |

| T1, T2 Maximum Continuous Current              | +1.75A         |

| FAULT Maximum Continuous Current               | +50mA          |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

| TDFN (Multilayer Board)                        |                |

| (derate 24.4mW/°C above +70°C)                 | 1951.2mW       |

| TDFN (Single-Layer Board)         |                |

|-----------------------------------|----------------|

| (derate 18.5mW/°C above +70°C)    | 1481.5mW       |

| Operating Temperature Range       | 40°C to +125°C |

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

|                                   |                |

## **Package Thermal Characteristics (Note 1)**

| TDFN (Multilayer)                                               |

|-----------------------------------------------------------------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )41°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )9°C/W     |

| TDFN (Single Layer)                                       |        |

|-----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 54°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    | 9°C/W  |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{DD}$  = +3.0V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = +5.0V and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                    | SYMBOL                 | CONDITIO                                                                                                  | NS                                   | MIN | TYP  | MAX | UNITS      |

|----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------|-----|------|-----|------------|

| DC CHARACTERISTICS                           |                        |                                                                                                           |                                      | •   |      |     |            |

| Supply Voltage Range                         | V <sub>DD</sub>        |                                                                                                           |                                      | 3.0 |      | 5.5 | V          |

| Supply Current                               | 1                      | $V_{\overline{EN}} = 0V$ , $V_{CLK} = 0V$ ,                                                               | V <sub>HICLK</sub> = 0V              |     | 1.1  | 1.8 | mA         |

| Supply Current                               | I <sub>DD</sub>        | V <sub>SPRD</sub> = 0V, T1 and T2<br>not connected                                                        | V <sub>HICLK</sub> = V <sub>DD</sub> |     | 2.1  | 3.5 | IIIA       |

| Disable Supply Current                       | I <sub>DIS</sub>       | V <sub>EN</sub> = V <sub>DD</sub> , T1, T2, CLK, SPRD, HICLK connected to GND or V <sub>DD</sub> (Note 3) |                                      |     |      | 5   | μA         |

| Driver Output Decistores                     | Б                      | I - 500mA                                                                                                 | V <sub>DD</sub> = 3.0V               |     | 160  | 350 | <b>~</b> 0 |

| Driver Output Resistance                     | R <sub>O</sub>         | I <sub>OUT</sub> = 500mA                                                                                  | V <sub>DD</sub> = 4.5V               |     | 145  | 300 | mΩ         |

| Undervoltage Lockout<br>Threshold            | V <sub>UVLO</sub>      | V <sub>DD</sub> rising                                                                                    |                                      | 2.6 | 2.75 | 2.9 | V          |

| Undervoltage Lockout<br>Threshold Hysteresis | V <sub>UVLO_HYST</sub> |                                                                                                           |                                      |     | 250  |     | mV         |

| T4 T2 Commont Limit                          |                        | 3.0V < V <sub>DD</sub> < 3.6V                                                                             |                                      | 1.1 | 1.3  | 1.5 | ^          |

| T1, T2 Current Limit                         | ILIM                   | 4.5V < V <sub>DD</sub> < 5.5V                                                                             |                                      | 1.2 | 1.4  | 1.6 | A          |

| T1, T2 Leakage Current                       | I <sub>LKG</sub>       | $V_{\overline{EN}} = V_{DD}$ , $V_{CLK} = 0V$ ; T1, T2 = 0V or $V_{DD}$                                   |                                      | -1  |      | +1  | μA         |

## **Electrical Characteristics (continued)**

$(V_{DD}$  = +3.0V to +5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = +5.0V and  $T_A$  = +25°C.) (Note 2)

| PARAMETER                         | SYMBOL                | CONDITIO                                      | ONS                                  | MIN | TYP                 | MAX  | UNITS  |

|-----------------------------------|-----------------------|-----------------------------------------------|--------------------------------------|-----|---------------------|------|--------|

| LOGIC SIGNALS (CLK, EN,           | HICLK, SPRD, Ī        | FAULT)                                        |                                      |     |                     |      | ,      |

| Input Logic-High Voltage          | V <sub>IH</sub>       |                                               |                                      | 2   |                     |      | V      |

| Input Logic-Low Voltage           | V <sub>IL</sub>       |                                               |                                      |     |                     | 0.8  | V      |

| Input Leakage Current             | I <sub>IL</sub>       | EN, CLK, SPRD, HICLK =                        | 0V or 5.5V                           | -1  |                     | +1   | μΑ     |

| SPRD Pulldown Current             | I <sub>PD</sub>       | V <sub>SPRD</sub> = V <sub>DD</sub>           |                                      | 5   | 10                  | 20   | μΑ     |

| FAULT Output Logic-Low<br>Voltage | V <sub>OL</sub>       | I <sub>SINK</sub> = 10mA                      |                                      |     |                     | 0.4  | V      |

| FAULT Leakage Current             | l <sub>LKGF</sub>     | V <sub>FAULT</sub> = 5.5V, FAULT dea          | asserted                             |     |                     | 1    | μΑ     |

| AC CHARACTERISTICS                |                       |                                               |                                      | •   |                     |      |        |

| Ouitabia a Farance                | t.                    | Figure 2, V <sub>CLK</sub> = 0V,              | V <sub>HICLK</sub> = 0V              | 237 | 250                 | 263  | 1-1-1- |

| Switching Frequency               | f <sub>SW</sub>       | V <sub>SPRD</sub> = 0V                        | V <sub>HICLK</sub> = V <sub>DD</sub> | 564 | 600                 | 636  | kHz    |

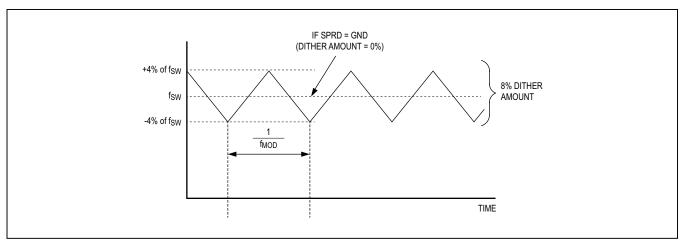

| Frequency Spread                  | Δf <sub>SW</sub>      | Figure 1, V <sub>SPRD</sub> = V <sub>DD</sub> | •                                    |     | ±4                  |      | %      |

| Spread Medulation Data            | f                     | Figure 1 V = V                                | V <sub>HICLK</sub> = 0V              |     | f <sub>SW</sub> /12 | kHz  |        |

| Spread Modulation Rate            | f <sub>MOD</sub>      | Figure 1, V <sub>SPRD</sub> = V <sub>DD</sub> | V <sub>HICLK</sub> = V <sub>DD</sub> |     | f <sub>SW</sub> /28 |      | KHZ    |

| CLK Input Frequency               | f <sub>EXT</sub>      |                                               |                                      | 200 |                     | 2000 | kHz    |

| CLK to T1, T2 Propagation Delay   | t <sub>PD</sub>       | T1/T2 switching low                           |                                      |     | 230                 |      | ns     |

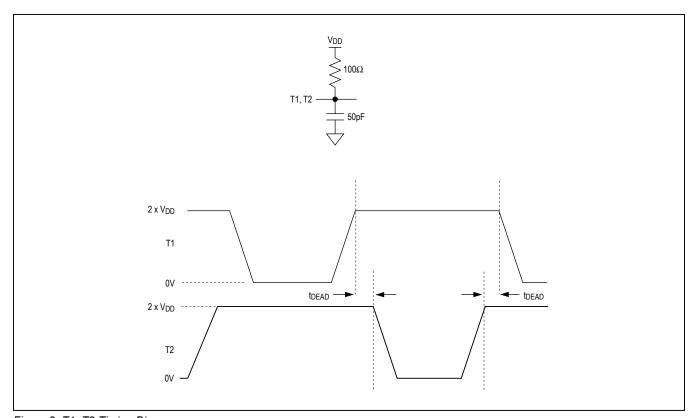

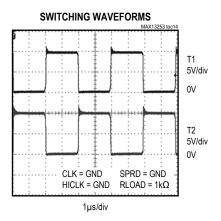

| T1, T2 Duty Cycle                 | D                     | Internal or external clockin                  | g                                    |     | 50                  |      | %      |

| T1, T2 Slew Rate                  | t <sub>SLEW</sub>     | Figure 2                                      |                                      |     | 200                 |      | V/µs   |

| Crossover Dead Time               | t <sub>DEAD</sub>     | Figure 2                                      |                                      |     | 50                  |      | ns     |

| Watchdog Timeout                  | twDOG                 |                                               |                                      | 20  | 35                  | 55   | μs     |

| PROTECTION                        | •                     |                                               |                                      |     |                     |      |        |

| Thermal-Shutdown<br>Threshold     | T <sub>SHDN</sub>     |                                               |                                      |     | +160                |      | °C     |

| Thermal-Shutdown<br>Hysteresis    | T <sub>SHDN_HYS</sub> |                                               |                                      |     | 30                  |      | °C     |

Note 2: All units are 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

Note 3: Disable supply current includes output switch-leakage currents.

Figure 1. Frequency Spread Timing Diagram

Figure 2. T1, T2 Timing Diagram

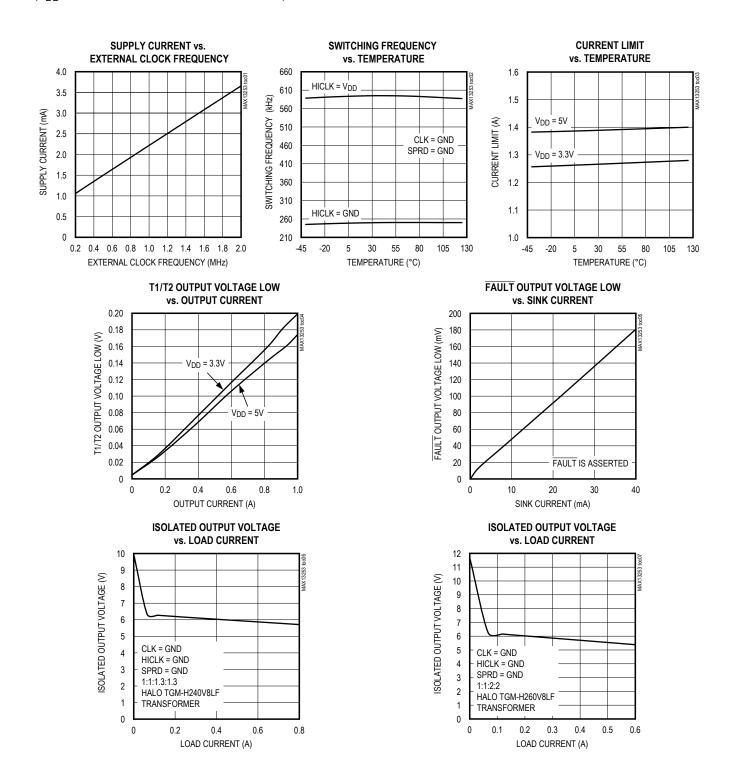

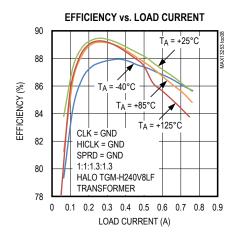

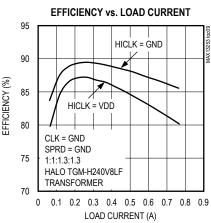

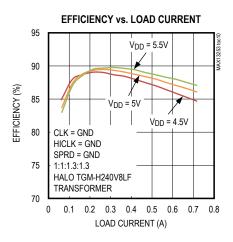

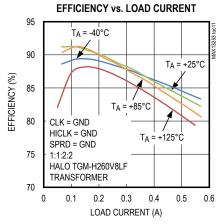

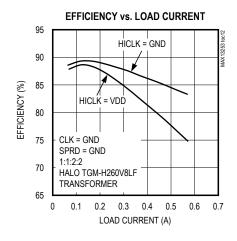

## **Typical Operating Characteristics**

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Pin Configuration**

## **Pin Description**

| PIN                                                                                                                                                                                                                                                                                                               | NAME                                                                                                                                                                                                                             | FUNCTION                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub>                                                                                                                                                                                                                  | Power-Supply Input. Bypass V <sub>DD</sub> to GND with a 1µF capacitor as close as possible to the device.                                                                                                   |

| 2                                                                                                                                                                                                                                                                                                                 | CLK                                                                                                                                                                                                                              | Clock Input. Connect CLK to GND to enable internal clocking. Apply a clock signal to CLK to enable external clocking.                                                                                        |

| 3                                                                                                                                                                                                                                                                                                                 | HICLK                                                                                                                                                                                                                            | Internal Oscillator Frequency Select Input. Drive HICLK high to set the internal oscillator to a 600kHz switching frequency. Drive HICLK low to set the internal oscillator to a 250kHz switching frequency. |

| 4                                                                                                                                                                                                                                                                                                                 | ĒΝ                                                                                                                                                                                                                               | Active-Low Enable Input. Drive $\overline{EN}$ low to enable the device. Drive $\overline{EN}$ high to disable the device.                                                                                   |

| 5                                                                                                                                                                                                                                                                                                                 | Spread-Spectrum Enable Input. Drive SPRD high to enable ±4% spread spectrum on the internal oscillator. Drive SPRD low or leave it unconnected to disable spread spectrum. SPRD does not heffect when an external clock is used. |                                                                                                                                                                                                              |

| 6                                                                                                                                                                                                                                                                                                                 | FAULT                                                                                                                                                                                                                            | Active-Low Fault Open-Drain Output. The FAULT open-drain transistor turns on when an overcurrent or overtemperature condition occurs.                                                                        |

| 7                                                                                                                                                                                                                                                                                                                 | GND Logic and Analog Ground                                                                                                                                                                                                      |                                                                                                                                                                                                              |

| 8                                                                                                                                                                                                                                                                                                                 | T2                                                                                                                                                                                                                               | Transformer Drive Output 2                                                                                                                                                                                   |

| PGND Power Ground. The transformer primary current flows through PGND. Ensure a low-resistance connection to ground.  T1 Transformer Drive Output 1  EP Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to maximize the performance; not intended as an electrical connection point. |                                                                                                                                                                                                                                  | i i                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                  | Transformer Drive Output 1                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                  | Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to maximize thermal performance; not intended as an electrical connection point.                                                |

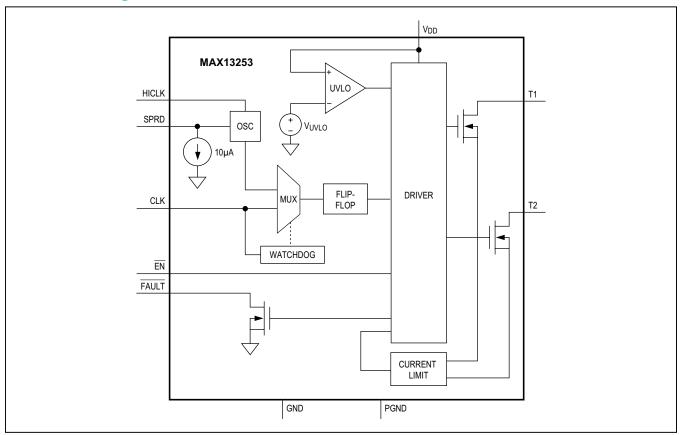

## **Functional Diagram**

## **Detailed Description**

The MAX13253 is an integrated primary-side transformer driver for low-EMI isolated power-supply circuits. An on-board oscillator, protection circuitry, and internal MOSFETs provide up to 1A of drive current to the primary windings of a center-tapped transformer. The MAX13253 features an internal oscillator for autonomous operation and an external clock source input to synchronize multiple MAX13253 devices. Regardless of the clock source used, an internal flip-flop stage guarantees a fixed 50% duty cycle to prevent DC current flow in the transformer.

The MAX13253 operates from a single +3.0V to +5.5V supply and includes undervoltage lockout for controlled startup. Overcurrent protection and thermal shutdown circuitry provides additional protection against excessive power dissipation.

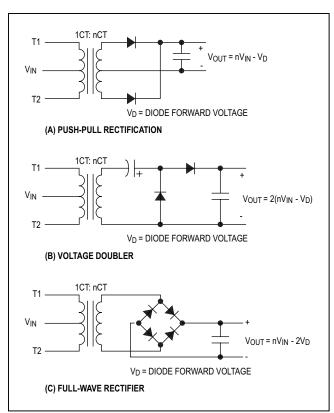

#### **Isolated Power-Supply Application**

The MAX13253 allows a versatile range of secondary-side rectification circuits (see Figure 3). The primary-to-

secondary transformer winding ratio can be chosen to adjust the isolated output voltage. The MAX13253 allows up to 1A of current into the primary transformer winding with a supply voltage up to +5.5V.

#### **Clock Source**

Either the internal oscillator or an external clock provides the switching signal for the MAX13253. Connect CLK to ground to select the internal oscillator. Provide an external signal to CLK to automatically select external clocking.

#### **Internal Oscillator Mode**

The MAX13253 includes an internal oscillator with a guaranteed 50% duty cycle. Drive the HICLK input high to set the internal oscillator frequency to 600kHz (typ). Drive the HICLK input low to set the internal oscillator frequency to 250kHz (typ).

The MAX13253 features spread-spectrum oscillation for reducing EMI peaks. Drive the SPRD input high to enable spread spectrum on the internal oscillator. Drive the

Figure 3. Secondary-Side Rectification Topologies

SPRD input low or leave unconnected to disable spread spectrum on the internal oscillator. SPRD has an internal 10µA pulldown to ground.

#### **External Clock Mode**

The MAX13253 provides an external clock mode for synchronizing multiple MAX13253 devices. Apply an external clock source to the CLK input to enable external clock mode. An internal flip-flop divides the external clock by two in order to generate a switching signal with a guaranteed 50% duty cycle. As a result, the MAX13253 outputs switch at one-half of the external clock frequency. T1 and T2 switch on the rising edge of the external clock signal.

SPRD has no effect when an external signal is applied to CLK.

#### Watchdog

When the MAX13253 is operating in external clock mode, a stalled clock can cause excessive DC current to flow through the primary winding of the transformer. The MAX13253 integrates internal watchdog circuitry to prevent damage from this condition. The internal oscilla-

tor provides the switching signal to the driver whenever the period between edges on CLK exceeds the watchdog timeout period of 20us (min).

#### Slew-Rate Control

The T1 and T2 drivers feature a controlled slew rate to limit EMI.

#### **Disable Mode**

The MAX13253 includes a pin-selectable disable mode to reduce current consumption. In disable mode the device consumes less than  $5\mu A$  (max) of supply current. The T1 and T2 outputs are high impedance in disable mode.

## **Power-Up and Undervoltage Lockout**

The MAX13253 provides an undervoltage lockout feature to ensure controlled power-up state and prevent operation before the oscillator has stabilized. On power-up and during normal operation, if the supply voltage drops below the  $V_{\rm UVLO}$ , the undervoltage-lockout circuit forces the device into disable mode. The T1 and T2 outputs are high impedance in disable mode.

### **Overcurrent Limiting**

The MAX13253 features overcurrent limiting to protect the IC from excessive currents when charging large capacitive loads or driving into short circuits. Current limiting is achieved in two stages: internal circuity monitors the output current and detects when the peak current rises above 2A. When the 2A limit is exceeded, internal protection circuitry is immediately enabled, reducing the output current and regulating it to the 1.4A (typ) current-limit threshold. The MAX13253 monitors the driver current on a cycle-bycycle basis, and the driver output current is regulated to the current-limit threshold until the short is removed.

The MAX13253 can dissipate large amounts of power during overcurrent limiting, causing the IC to enter thermal shutdown.

### **FAULT** Output

The FAULT output is asserted low during an overcurrent or overtemperature fault. FAULT is an open-drain output.

#### **Thermal Shutdown**

The MAX13253 is protected from overtemperature damage by integrated thermal-shutdown circuitry. When the junction temperature ( $T_J$ ) exceeds +160°C (typ), the device is disabled and  $\overline{FAULT}$  is asserted.  $\overline{FAULT}$  is asserted for the duration of either an overcurrent or overtemperature event. The device resumes normal operation when  $T_J$  falls below +130°C (typ).

## **Applications Information**

#### **Power Dissipation**

The power dissipation of the device is approximated by:

$$P_D = (R_O \times I_{PRI}^2) + (I_{DD} \times V_{DD})$$

where  $R_O$  is the resistance of the internal FET drivers and  $I_{PRI}$  is the load current flowing into T1 and T2. Ensure that the power dissipation of the MAX13253 is kept below the *Absolute Maximum Ratings* for proper operation.

### **High-Temperature Operation**

When the MAX13253 is operated under high ambient temperatures, the power dissipated in the package can raise the junction temperature close to the thermal shutdown threshold. Under such temperature conditions, the power dissipation should be held low enough that the junction temperature observes a factor of safety margin. The maximum junction temperature should be held below +140°C. Use the package's thermal resistance to calculate the junction temperature.

### **Power-Supply Decoupling**

Bypass  $V_{\mbox{\scriptsize DD}}$  to ground with a  $1\mu\mbox{\scriptsize F}$  ceramic capacitor as close as possible to the device.

Connect at least  $10\mu F$  between  $V_{DD}$  and ground as close as possible to the primary-side center tap of the transformer. This capacitor helps to stabilize the voltage on the supply line and protects the IC against large voltage spikes on  $V_{DD}$ .

### **Output Voltage Regulation**

For many applications, the unregulated output of the MAX13253 circuit meets output voltage tolerances. This configuration represents the highest efficiency possible. When the load currents on the transformer's secondary side are low, the output voltage of the rectifier can strongly increase. To protect downstream circuitry, limit the output voltage when operating the circuit under low load conditions. If the minimum output load current is less than approximately 5mA, connect a zener diode from the output node of the rectifier to ground to limit the output voltage to a safe value.

For applications requiring a regulated output voltage, Maxim provides several solutions. In the following examples, assume a tolerance of  $\pm 10\%$  for the input voltage.

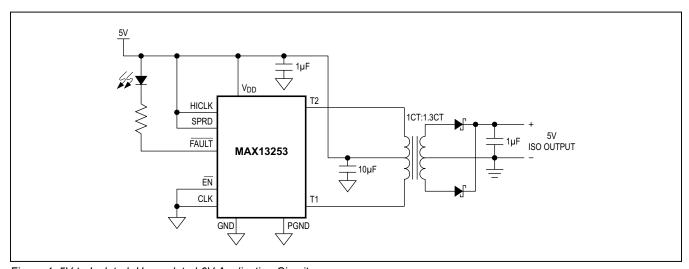

#### Example 1: 5V to Isolated, Unregulated 6V

In the circuit of <u>Figure 4</u>, the MAX13253 is used to generate an isolated 6V output. For a minimum input voltage of 5V, the output voltage of the rectifier is approximately 6V.

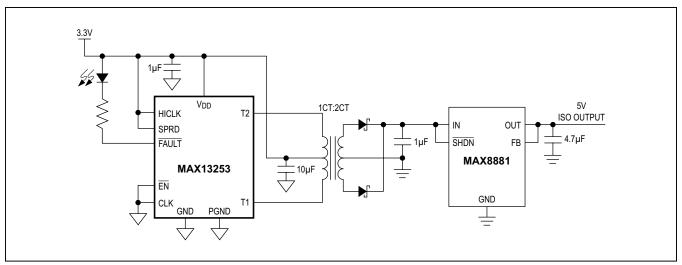

#### Example 2: 3.3V to Isolated, Regulated 5V

In the circuit of <u>Figure 5</u>, the MAX8881 low-dropout linear regulator regulates the isolated output voltage to 5V. A 1:2 center-tapped transformer is used to step-up the secondary side voltage from a 3.3V input. For a minimum input voltage of 3.3V, the output voltage of the rectifier is approximately 5V.

Figure 4. 5V to Isolated, Unregulated 6V Application Circuit

Figure 5. 3.3V to Isolated, Regulated 5V Application Circuit

## Isolated USB/RS-485/RS-232 Isolated Applications

The MAX13253 can provide isolated power for USB/RS-485/RS-232 applications. The 1A output current capability of the MAX13253 allows multiple RS-485/RS-232 transceivers to operate simultaneously.

### **PCB Layout Guidelines**

As with all power-supply circuits, careful PCB layout is important to achieve low switching losses and stable operation. Connect the exposed pad to a solid copper ground plane for optimum thermal performance.

The traces from T1 and T2 to the transformer must be low-resistance and low-inductance paths. Locate the transformer as closely as possible to the MAX13253 using short, wide traces.

If possible, use a power plane for all  $V_{DD}$  connections to the MAX13253 and the primary-side of the transformer. If a power plane is not available, avoid damage to the IC by ensuring that the current flowing through the primary-side center tap of the transformer does not flow through the same trace that connects the supply pin of the MAX13253 to the  $V_{DD}$  source, and connect the primary-side center tap to the  $V_{DD}$  supply using a very low-inductance connection.

When the internal oscillator is used, it is possible for high frequency switching on T1 and T2 to couple into the CLK circuitry through PCB parasitic capacitance. This capacitive coupling can induce duty cycle errors in the oscillator, resulting in a DC current through the transformer. For proper operation, ensure that CLK has a solid ground connection.

### **Exposed Pad**

For optimal thermal performance, ensure that the exposed pad has a low thermal resistance connection to the ground plane. Failure to provide a low thermal impedance path to the ground plane results in excessive junction temperatures when dissipating high power.

## **Component Selection**

#### **Transformer Selection**

Transformer selection for the MAX13253 can be simplified by the use of the ET product. The ET product relates the maximum allowable magnetic flux density in a transformer core to the voltage across a winding and switching period. Inductor magnetizing current in the primary winding changes linearly with time during the switching period of the MAX13253. Each transformer has a minimum ET product, though not always stated on the transformer data sheet. Ensure that the transformer selected for use with the MAX13253 has an ET product of at least ET =  $V_{DD}/(2 \ x \ f_{SW})$  for each half of the primary winding, where  $f_{SW}$  is the minimum switching frequency of the T1 and T2 ouputs.

Select a transformer with sufficient ET product for each half of the primary winding to ensure that the transformer does not saturate during operation. Saturation of the magnetic core results in significantly reduced inductance of the primary, and therefore in a large increase in current flow. This can cause the current limit to be reached even when the load is not high.

For example, when the internal oscillator is used to drive the outputs and HICLK is low, the required transformer ET product to the center tap for an application with  $V_{DD}$  (max) = 5.5V, is 13.1V- $\mu$ s. An application with  $V_{DD}$  (max) = 3.3V has a transformer ET product to the center tap requirement of 7.9V- $\mu$ s.

In addition to the constraint on ET product, choose a transformer with low leakage inductance and low DC-winding resistance. Power dissipation of the transformer due to the copper loss is approximated as:

$$P_{D} T_{X} = I_{LOAD}^{2} x (R_{PRI}/N^{2} + R_{SEC})$$

where  $R_{PRI}$  is the DC winding resistance of the primary, and  $R_{SEC}$  is the DC winding resistance of the secondary. In most cases, an optimum is reached when  $R_{SEC}$  =  $R_{PRI}/N^2$ . For this condition, the power dissipation is equal for the primary and secondary windings.

As with all power-supply designs, it is important to optimize efficiency. In designs incorporating small transformers, the possibility of thermal runaway makes low transformer efficiencies problematic. Transformer losses produce a temperature rise that reduces the efficiency of the transformer. The lower efficiency, in turn, produces an even larger temperature rise.

To ensure that the transformer meets these requirements under all operating conditions, the design should focus on the worst-case conditions. The most stringent demands on ET product arise for maximum input voltage, minimum switching frequency, and maximum temperature and load current. Additionally, the worst-case values for transformer and rectifier losses should be considered.

The primary must be center-tapped; however the secondary winding may or may not be center-tapped, depending on the rectifier topology used. The phasing between primary and secondary windings is not critical.

The transformer turns ratio must be set to provide the minimum required output voltage at the maximum anticipated load with the minimum expected input voltage. In addition, include in the calculations an allowance for the worst-case losses in the rectifiers. Since the turns ratio determined in this manner will ordinarily produce a much higher voltage at the secondary under conditions of high input voltage and/or light loading, be careful to prevent an overvoltage condition from occurring.

Transformers for use with the MAX13253 are typically wound on a high-permeability magnetic core. To minimize radiated electromagnetic emissions, select a toroid, pot core, E/I/U core, or equivalent.

#### **Diode Selection**

The high switching speed capability of the MAX13253 necessitates high-speed rectifiers. Ordinary silicon signal diodes such as the 1N914 or 1N4148 can be used for low-output current levels (less than 50mA), but at high output current levels, their reverse recovery times might degrade efficiency. At higher output currents, select low forward-voltage Schottky diodes to improve efficiency. Ensure that the average forward current rating for the rectifier diodes exceeds the maximum load current of the circuit. For surface-mount applications, Schottky diodes such as the B230A, MBRS230, and MBRS320 are recommended.

### **Suggested External Component Manufacturers**

**Table 1. Component Manufacturers**

| MANUFACTURER     | COMPONENT    | WEBSITE                 |  |

|------------------|--------------|-------------------------|--|

| Halo Electronics | Transformers | www.haloelectronics.com |  |

| Diodes Inc.      | Diodes       | www.diodes.com          |  |

| Murata Americas  | Capacitors   | www.murataamericas.com  |  |

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX13253ATB+ | -40°C to +125°C | 10 TDFN-EP* |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND        |

|------------|---------|----------------|-------------|

| TYPE       | CODE    | NO.            | PATTERN NO. |

| 10 TDFN-EP | T1033+1 | <u>21-0137</u> | 90-0003     |

<sup>\*</sup>EP = Exposed Pad

## MAX13253

## 1A, Spread-Spectrum, Push-Pull, Transformer **Driver for Isolated Power Supplies**

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                   | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 3/13             | Initial release                                                                                               | _                |

| 1                  | 4/13             | Updated TOC parameters, updated Figure 4, replaced Figure 5, updated <i>Output Voltage Regulation</i> section | 5, 6, 10, 11     |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru\_6 moschip.ru\_4 moschip.ru\_9