#### PROTECTED HIGH FREQUENCY HIGH SIDE SWITCH

#### **Features**

Up to 30Khz PWM switching capability

Charge pump for DC operation

Active di/dt control to reduce EMI

Load current feedback

Short-circuit protection

Programmable over current shutdown

Over temperature shutdown

Diagnostic feedback

Under voltage shutdown

Gnd, IN and bootstrap pin loss protection

E.S.D protection

Low power mode

Lead-free, RoHS compliant

## **Applications**

Fan engine cooling Air conditioning blower Pumps (oil, fuel, water...) Compressor

#### **Description**

The AUIR3330s is a 7 terminals high side switch for variable speed DC motor. It features simplify the design of the DC motor drive with a microcontroller. The Mosfet switches the power load proportionally to the input signal duty cycle at the same frequency and provides a current feedback on the Ifbk pin. The over-current shutdown is programmable from 5A to 50A. Over-current, over-temperature latch OFF the power switch and provide a digital diagnostic status on the input pin. In sleep mode, the device consumes typically less then 1uA.

Further integrated protections such as ESD and GND disconnect protection guarantee safe operation in harsh conditions of the automotive environment.

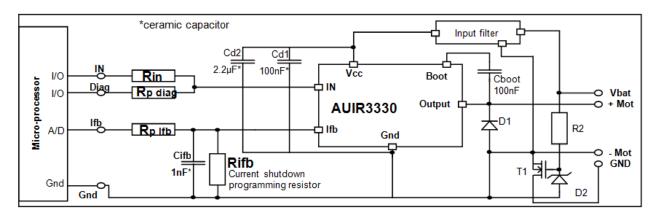

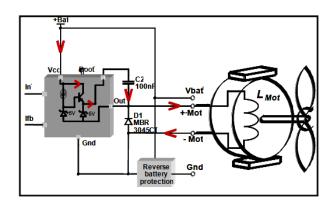

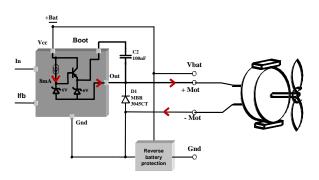

## Typical connection with reverse battery protection

May 29, 2014

## **Qualification Information**<sup>†</sup>

|                      |                     | Automotive                                                         |  |  |  |  |  |

|----------------------|---------------------|--------------------------------------------------------------------|--|--|--|--|--|

|                      |                     | (per AEC-Q100)                                                     |  |  |  |  |  |

| Qualification Le     | evel                | Comments: This family of ICs has passed an Automotive              |  |  |  |  |  |

|                      |                     | qualification. IR's Industrial and Consumer qualification level is |  |  |  |  |  |

|                      |                     | granted by extension of the higher Automotive level.               |  |  |  |  |  |

|                      |                     | 1401 / 2000                                                        |  |  |  |  |  |

| Moisture Sensi       | tivity Level        | MSL1 260°C                                                         |  |  |  |  |  |

|                      | ,                   | (per IPC/JEDEC J-STD-020)                                          |  |  |  |  |  |

|                      | Machine Model       | Class M3 (+/-350V)                                                 |  |  |  |  |  |

|                      | Machine Model       | (per AEC-Q100-003)                                                 |  |  |  |  |  |

| ESD                  | Human Body Model    | Class H4 (+/-4000V)                                                |  |  |  |  |  |

| LOD                  | Tidinali Body Model | (per AEC-Q100-002)                                                 |  |  |  |  |  |

| Charged Device Model |                     | Class C4 (Pass +/-1000V)                                           |  |  |  |  |  |

|                      |                     | (per AEC-Q100-011)                                                 |  |  |  |  |  |

| IC Latch-Up Test     |                     | Class II Level A                                                   |  |  |  |  |  |

| To Later-op Test     |                     | (per AEC-Q100-004)                                                 |  |  |  |  |  |

| RoHS Complian        | nt                  | Yes                                                                |  |  |  |  |  |

<sup>†</sup> Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. (Tj= -40°C..150°C, Vcc=6..18V unless otherwise specified).

| Symbol   | Parameter                                                                                     | Min.   | Max.    | Units |

|----------|-----------------------------------------------------------------------------------------------|--------|---------|-------|

| Vout     | Maximum drain to source voltage                                                               | GND-5V | Vcc+0.3 | V     |

| Vin      | Maximum input voltage                                                                         | -0.3   | 5.5     | V     |

| Vcc max. | Maximum Vcc voltage                                                                           | _      | 36      | V     |

| Vcc cont | Maximum continuous Vcc voltage                                                                |        | 28      | V     |

| lin max. | Maximum input current                                                                         | -0.3   | 10      | mA    |

| Ifb max  | Maximum Ifb current                                                                           | -50    | 10      | mA    |

| Pd       | Maximum power dissipation Rth=60°C/W Tambient=25°C, Tj=150°C Rth=40°C/W D²Pack 6cm² footprint | _      | 2.5     | W     |

| Tj max.  | Max. storage & operating temperature junction temperature                                     | -40    | 150     | °C    |

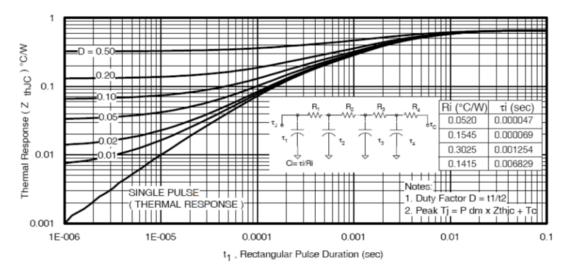

### **Thermal Characteristics**

| Symbol | Parameter                                                               | Тур. | Max. | Units |

|--------|-------------------------------------------------------------------------|------|------|-------|

| Rth1   | Thermal resistance junction to ambient D <sup>2</sup> Pak Std footprint | 60   |      |       |

| Rth2   | Thermal resistance junction to ambient D²pak 6cm² footprint             | 40   |      | °C/W  |

| Rth3   | Thermal resistance junction to case D²pak                               | 0.65 |      |       |

# Recommended Operating Conditions These values are given for a quick design.

| Symbol  | Parameter                                                                 | Min. | Max. | Units |

|---------|---------------------------------------------------------------------------|------|------|-------|

| Vcc op. | Operating voltage range                                                   | 6    | 18   | V     |

| lout    | DC output current Tj=145°C, Tamb=85°C, Rth=5°C/W                          | _    | 45   | Α     |

| Cboot   | Bootstrap capacitor                                                       | 100  | 220  | nF    |

| Cd1     | Decoupling ceramic capacitor                                              | 100  |      | nF    |

| Cd2     | Decoupling ceramic capacitor                                              | 2.2  |      | μF    |

| R In    | Recommended resistor in series with In pin                                | 1    | 5    | kΩ    |

| Rp diag | Recommended resistor in series with In pin to read the diagnostic         | 10   | 50   | kΩ    |

| Clfb    | Recommended Ifb filter capacitor                                          | 1    | 2.2  | nF    |

| RIfb    | Recommended resistor to program over current shutdown                     | 0.6  | 5    | kΩ    |

| Rp Ifb  | Recommended resistor in series with RIfb pin to read the current feedback | 10   | 25   | kΩ    |

| F max.  | Maximum recommended input frequency, duty cycle=10% to 90%                |      | 30   | kHz   |

## **Static Electrical Characteristics**

-40°C < Tj < 150°C, 6V < Vcc < 18V, (unless otherwise specified)

| Symbol      | Parameter                                                      | Min. | Тур. | Max. | Units | Test Conditions               |

|-------------|----------------------------------------------------------------|------|------|------|-------|-------------------------------|

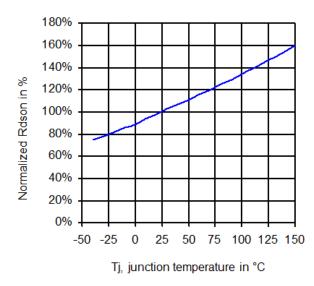

| Ddo on      | ON state resistance Tj=25°C                                    | —    | 3    | 3.5  | ····  | lout=30A                      |

| Rds on      | ON state resistance Tj=150°C <sup>1</sup>                      | —    | 5.5  | 6.2  | mΩ    | lout=30A                      |

| Rds on Lv   | ON state resistance low voltage Tj=25°C                        |      | 3    | 3.5  | mΩ    | lout=15A Vcc=6V               |

| Vf Mos      | Forward voltage of the Mosfet body diode                       | 0.6  |      | 1.1  | V     | lout = -50A                   |

| Vbrk out    | Breakdown voltage between Vcc and Vout (MOSFET body diode)     | 39   | 40   | _    | V     |                               |

| I Vcc Slp   | Supply current in sleep mode (IC + MOSFET leakage)             |      | 1    | 2    | μΑ    | Vin=0V Vcc = 14V<br>Tj = 25°C |

| I bias Boot | Bootstrap regulator biasing current (flows through the output) |      | 5.5  | 14   | mA    | Vout = 0V                     |

| I Vcc Wke   | Vcc current when the device is woken up (IC + Ibias Boot)      |      | 14   | 20   | mA    | I_boot = 0A Vout = 0V         |

| V In Wke    | Input threshold voltage to wake up the device                  | 0.35 | 0.75 | 1.3  | V     |                               |

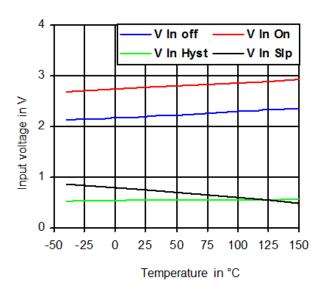

| V In Off    | In voltage threshold to turn off                               | 1.9  | 2.2  |      | V     |                               |

| V In On     | In voltage threshold to turn on                                |      | 2.8  | 3.2  | V     |                               |

| V In Hyst   | Input threshold hysteresis                                     | 0.4  |      | 0.7  | V     |                               |

| C In        | Input pin capacitor                                            | -    | 10   | -    | pF    |                               |

| I In on     | On state input current                                         | 10   | 20   | 30   | μA    | Vin = 5V                      |

| I Bt Chrge  | Bootstrap current charge                                       | 0.4  | _    | 1.5  | Α     | Vout = 0V<br>Cboot =500nF     |

| V Bt Chrge  | Bootstrap voltage                                              | 4.9  | 5.5  | 6.3  | V     | Cboot =500nF                  |

Guaranteed by design.

## **Switching Electrical Characteristics**

-40°C < Tj < 150°C, 6V < Vcc < 18V, Rin =  $5k\Omega$  (unless otherwise specified)

| Symbol      | Parameter                                            | Min. | Тур. | Max. | Units | Conditions                                       |

|-------------|------------------------------------------------------|------|------|------|-------|--------------------------------------------------|

| Td Vout on  | Turn-on output voltage delay time                    | 0.7  | 1    | 1.4  | μs    | between 50% of IN and 30% of Vout, lout = 14A    |

| Tr Vout     | Ouput voltage rise time                              | 500  | 800  | 1300 | ns    | Between 15% and 85%;<br>Vcc = 14v, lout=14A      |

| Tr lout     | Ouput current rise time                              | 0.7  | 1.2  | 1.85 | μs    | Between 5A and 40A;<br>Vcc = 14v, lout=45A       |

| dv/dt on    | Turn on dv/dt                                        | 10   | 20   | 28   | V/µs  | Between 25% and 70%;<br>Vcc = 14v                |

| di/dt on    | Turn on di/dt                                        | 21   | 40   | 51   | A/µs  | Between lout 15A and 35A; Vcc = 14v              |

| Td Vout off | Turn-off delay time                                  | 0.9  | 1.2  | 1.7  | μs    | between 50% of IN and<br>90% of Vout, lout = 14A |

| Tf Vout     | Output voltage fall time                             | 250  | 430  | 650  | ns    | Between 90% and 10%;<br>Vcc = 14v, lout=14A      |

| Tf lout     | Output current fall time                             | 0.55 | 1    | 1.45 | μs    | Between 40A and 5A;<br>Vcc = 14v, lout=45A       |

| dv/dt off   | Turn off dv/dt                                       | 28   | 50   | 67   | V/µs  | Between 30% and 70%;<br>Vcc = 14v                |

| di/dt off   | Turn off di/dt                                       | 30   | 40   | 51   | A/µs  | Between lout 35A and 15A; Vcc = 14v              |

| T Trfct Ld  | Input output transfer function for low duty cycle    | 8.5  | 10   | 11.5 | μs    | lout = 1A;<br>In pulse time =10µS                |

| T Trfct Hd  | Input output transfer function for high duty cycle   | 38.5 | 39.5 | 40.5 | μs    | lout = 1A;<br>In pulse time =40µS                |

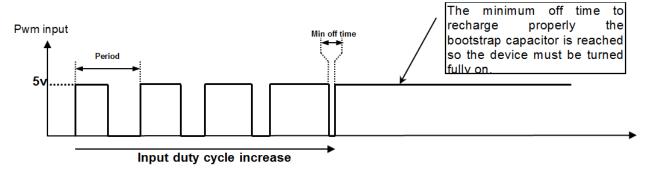

| T Off Min   | Minimum off time to recharge the bootstrap capacitor | _    | _    | 2    | μs    | Cboot = 100nF                                    |

## **Protection Characteristics**

-40°C < Tj < 150°C, 6V < Vcc < 18V (unless otherwise specified).

| Symbol      | Parameter                                           | Min. | Тур. | Max. | Units | Conditions                |

|-------------|-----------------------------------------------------|------|------|------|-------|---------------------------|

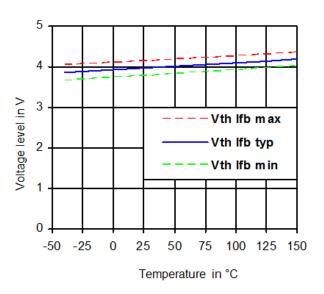

| Vth Ifb     | IFB over current threshold voltage                  | 3.65 | 4    | 4.35 | V     |                           |

| Isd fix     | sd fix Maximum internal over current shutdown       |      | 70   | 90   | Α     |                           |

| lsd prog 2  | Programmable current shutdown                       | 11   | 17   | 24   | Α     | Rifb = $1.5k\Omega$       |

| Isd prog 1  | Programmable current shutdown                       | 30   | 40   | 50   | Α     | Rifb = $640\Omega$        |

| Tsd         | Over temperature threshold <sup>2</sup>             | 150  | 165  | 175  | °C    |                           |

| Vth Vds OVP | Vds threshold to activate the over power protection |      | 0.75 | _    | V     | Tj=25°C                   |

| Td Vds OVP  | Vds delay to turn off after OVP detection           | 6    | 10   | 15   | μs    |                           |

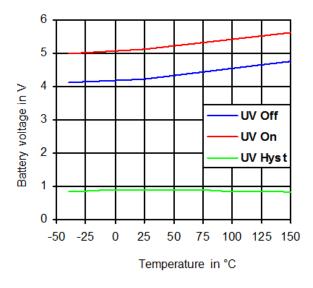

| UV On       | Under voltage threshold to turn on                  |      | 5.3  | 6.3  | V     |                           |

| UV Off      | Under voltage threshold to turn off                 |      | 4.3  | 5.3  | V     |                           |

| UV Hyst     | Under voltage hysteresis                            | 0.5  | _    | 1.25 | V     |                           |

| T slp       | Sleep mode time and fault reset                     | 20   | 30   | 50   | ms    |                           |

| T rst       | Time to reset the latched fault                     |      | 50   |      | μs    | Tj=25°C                   |

| T wke min   | Minimum pulse width to wake up                      | 2    | _    | _    | μs    |                           |

| Tpwr_on_rst | Power on reset time                                 | 5    | 8    | 15   | μs    |                           |

| F Dg OT     | Over temperature diagnostic frequency               |      | 260  |      | Hz    |                           |

| F Dg OC     | Over current diagnostic frequency                   | 35   | 70   | 95   | Hz    |                           |

| V Dg Dft    | DG voltage when fault                               | _    |      | 400  | mV    | Vin = 5V Rin = $5k\Omega$ |

### **Current Sense Characteristics**

-40°C < Tj < 150°C, 6V < Vcc < 18V (unless otherwise specified), Rifbk=1k $\Omega$

| Symbol   | Parameter                             | Min. | Тур. | Max. | Units | Conditions        |

|----------|---------------------------------------|------|------|------|-------|-------------------|

| I offset | Load current diagnostic offset        | -2.7 | 0.62 | 4    | Α     | Range 5A to 40A   |

| Ratio    | (I load + I offset) / Ifb             | 5400 | 6400 | 7200 |       | Range 5A to 40A   |

| Ratio Tc | Iload/Ifbk variation over temperature | -3.5 | -    | 1.5  | %     | Tj=-40°C to 150°C |

<sup>&</sup>lt;sup>2</sup> Guaranteed by design.

## **Leads Assignment**

| PART NUMBER                                                                     | AUIR3330S     |

|---------------------------------------------------------------------------------|---------------|

| 1 : Ifb<br>2 : In<br>3 : Gnd<br>4 : Vcc (Tab)<br>5 : Boot<br>6 : Out<br>7 : Out | D2Pak 7 leads |

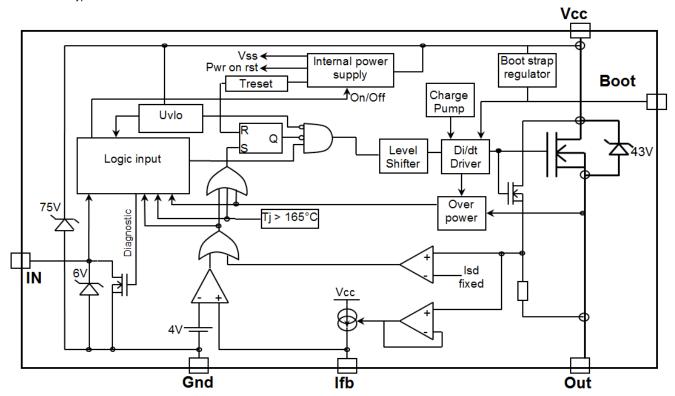

## **Functional Block Diagram**

All values are typical

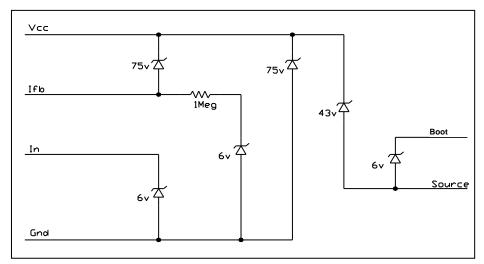

## Internal diode schematic

All values are typical

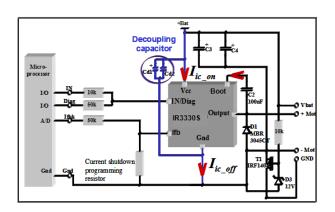

## Design: basic schematic with microprocessor

The basic circuit is giving all the functionality to drive a 50A DC motor. RIfb set both the current shutdown and the current feedback reading scale. The In signal provides the Pwm frequency and duty cycle order to the AUIR3330S. D1 is the free wheeling diode during PWM operation. As the equivalent circuit between Vbat and – Mot is 2 diode in series (the body diode of the AUIR3330S and D1), the system requires T1, D2, R1 and R2 to sustain the reverse battery. (Cf: Typical connection with reverse battery protection).

#### DC to 30 kHz operation

The AUIR3330S is able to operate in DC and high speed switching operation. To be able to switch at 30 kHz, a bootstrap capacitor is used externally. The device integrates the power supply of the bootstrap capacitor. In DC operation, when the capacitor is discharged, the charge pump maintains the device ON.

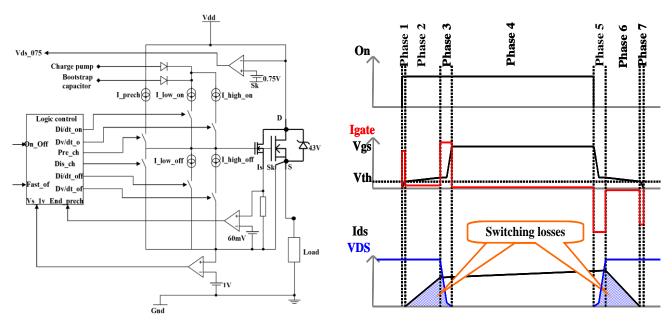

## Active di/dt control to reduce EMI and switching losses

The AUIR3330S includes a special gate drive, managing the Mosfet di/dt controlled internally, by managing the gate voltage dynamically. This di/dt trade-off is set internally to an optimum value, between power dissipation versus noise. This feature brings to the designer less EMI versus switching losses. The system has three phases during the turn on sequence and three phases during the turn off sequence. First the driver injects a high current in the gate until the gate voltage reaches the Vth. Then it injects a low current to control the di/dt value until the gate voltage reaches the miller plate. And after it injects a high current to fully turn on quickly the MOSFET to reduce the dv time (reducing the switching losses). The turn off sequence is the same than the turn on but in the opposite direction: First reduce the dv time after control the di/dt and then discharge totally the gate.

## Sense Load current feedback and programmable current shutdown

The Ifb pin allows an analog measurement of the load current and with an external resistor allows to program the over current shutdown level from 10A to 50A. The voltage threshold level of the Ifb pin is internally set to 4v (See the formulas below). It is also possible to dynamically adjust the current shutdown protection versus time by adding some external components. This protection is latched and turns off the output MOSFET without di/dt sequence to reduce the device and the application stress. The operating mode is recovered after resetting by the sleep mode.

$$Rifb = \frac{Vifb\_gnd\min}{Imax\_appli + Ioffset\min} \times Ratio\min$$

$$Vifb\min@T^{\circ}C = \frac{Iload-Ioffset\max@T^{\circ}C}{Ratio\max@T^{\circ}C} \times Rifb$$

$$Ishd\max = MAX [Ishd\max@-40^{\circ}C; Ishd\max@25^{\circ}; Ishtd\max@150^{\circ}C]$$

$$Vifb\max@T^{\circ}C = \frac{Iload-Ioffset\min@T^{\circ}C}{Ratio\min@T^{\circ}C} \times Rifb$$

$$Ishd\max@T^{\circ}C = \left[\frac{Vifb\_gnd\max}{Rifb(calculated)} \times Ratio\max@T^{\circ}C\right] + Ioffset\max@T^{\circ}C$$

#### Where:

Imax appli is the maximum application current Ishtd max is the maximum output shutdown current

#### Internal over current shutdown

The maximum current shutdown threshold value is internally fixed to 65A typ. This protection is latched and turns off the output MOSFET without di/dt sequence to reduce the device and the application stress. The operating mode is recovered after resetting by the sleep mode.

#### **Under voltage lock-out**

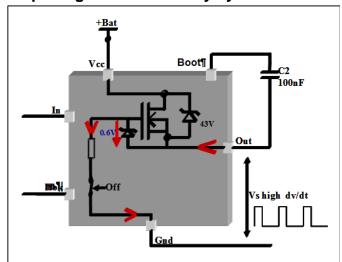

The AUIR3330S remains operational from UV off threshold. Under this continuous voltage, the device will be locked until the voltage recovers the operating range, according to an internal hysteresis fixed to 0,5V min. The maximum rating voltage is given by the Trench VDMOS technology where the avalanche voltage is up to 43V typically.

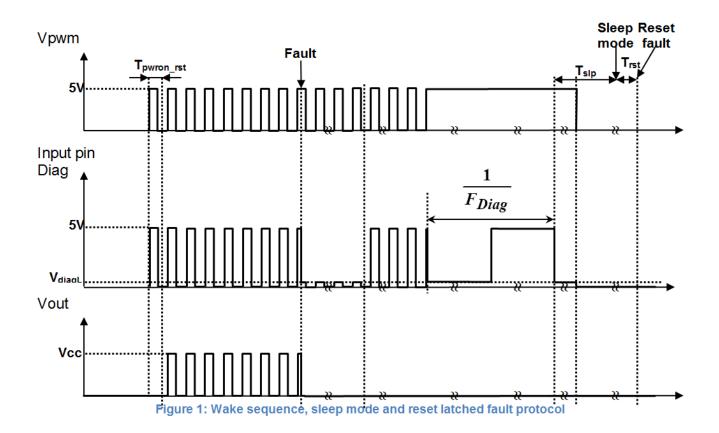

#### Sleep mode and reset fault:

The sleep mode is enabled if the IN pin stay low (Vin < V In Slp) more than T Slp time. The consumption in sleep mode is Icc off. The AUIR3330S wakes up at first rise edge on the IN pin (Vin > V In Slp). This mode allows resetting all the latched faults after Trst time (Cf. **Error! Reference source not found.**). This filter time allows memorizing and maintaining the fault latched even if the power supply is removed (ISO pulses latch protection).

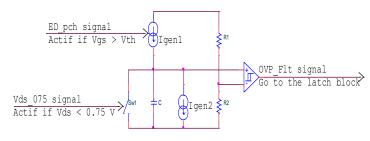

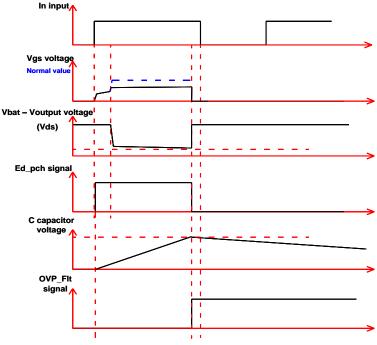

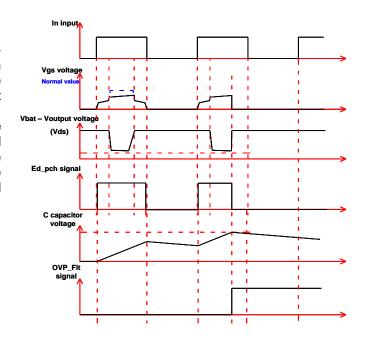

#### Over-power protection

The AUIR3330S have an internal over-power protection. This feature allows protecting the silicon device and the application against several critical issues:

- The bootstrap capacitor missing.

- Abnormal leakage on the bootstrap capacitor.

- Abnormal leakage on the power MOSFET gate.

- Very low impedance output short circuit.

Time to charge the capacitor and latch a fault (Igen1 + C) =  $9\mu s$  Time to discharge the capacitor (Igen2 + C) = 11ms

- The time constant Ign1 + C represent the thermal silicon time constant

- The time constant Ign2 + C represent the thermal package time constant (T(ign2 + C) < T Slp)</li>

- Igen1 is on if the gate voltage (of the output MOSFET) is higher than its Vth

- Ign2 is always switching on.

- Sw1 is close if the Vbat out voltage (Vds) is lower than 0.75V

When the Output MOSFET gate voltage reaches its output MOSFET Vth value, the current generator Igen1 start to charge the capacitor C. Then three scenarios are possible:

1. The device turn on properly (Vds < 0.75v) and the capacitor C is discharged by the switch sw1. The device is ready for the next pulse. It is the normal

case.

2. The device can not turn on properly (Vds stay > 0.75v no capacitor reset) and the on time duration (duty cycle) is enough long to charge completely the capacitor C. The comparator detects the fault, stop the device and latch it. This fault could be reset by a sleep mode

3. The device can not turn on properly (Vds stay > 0.75v no capacitor reset) but the ON time duration (duty cycle) is not enough long to charge completely the capacitor C. So the fault is not detected by the comparator and it is not latched. But the picture of energy value dissipated by the MOSFET during the almost turn on value is stored in the capacitor C. And at the next pulse the current generator Igen1 resume to charge the capacitor until it reach the comparator value and latch the fault (this sequence could be on several pulse). It could be reset by a sleep mode.

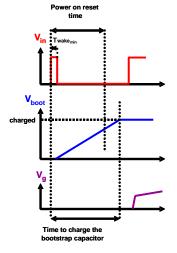

#### Wake up sequence:

The AUIR3330S has an internal power on reset. After waking it up by the IN signal, the device waits for Tpwron\_rst before activating the output power mosfet. This time is required to charge properly the bootstrap capacitor and to stabilize the internal power supply (Cf. Error! Reference source not found.).

## In pin and digital diagnostic

The IN has two functions. In normal working condition, the output follows the IN pin digital level. In latched fault condition (over current and over temperature shutdown), the IN pin provides a digital feedback to the  $\mu$ -processor. This digital diagnostic gives a different frequency signal according to the fault type.

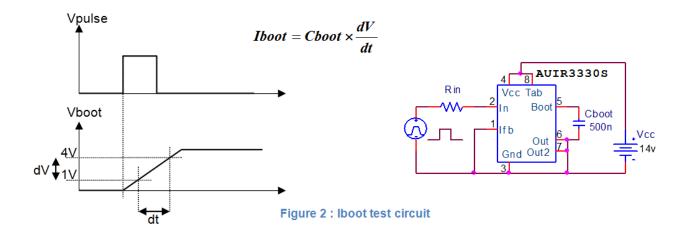

#### **Bootstrap current measurement:**

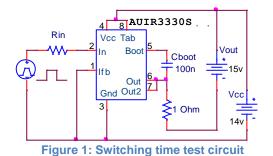

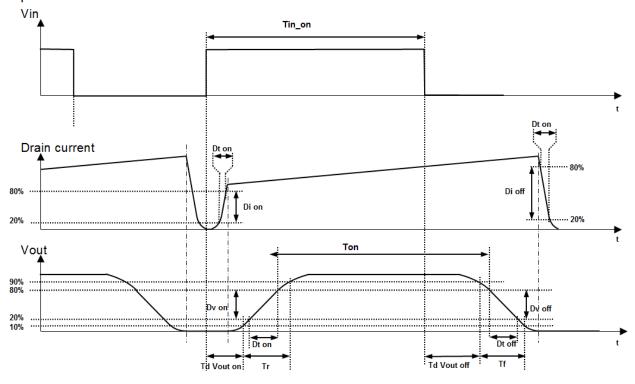

## Switching time definition:

As the opposite schematic shows, the dv/dt on & off and the Td Vout on & off switching time are measured at zero current value and with a simulated continuous conduction condition to avoid the di/dt impact (see also the chronogram above).

Due the inductive load, the drain current level impacts directly the delay to switch on the output voltage. So the output voltage duty cycle value changes with the current level. The output current duty cycle is higher than the output voltage duty cycle. The di/dt on limit value allows calculating the complete delay (here named Tcdon and off) to switch on the output voltage.

$$Tcdon_{\max} = Td \_Vout \_on_{\max} + \frac{Id}{didt \_on_{\min}}$$

$$Tcdon_{\min} = Td\_Vout\_on_{\min} + \frac{Id}{didt\_on_{\max}} \quad Ton_{\min} = Tin\_on - Tdcon_{\max} + Tcdoff_{\min}$$

$$Tcdoff_{\min} = Td\_Vout\_off_{\min}$$

$$Ton_{\max} = Tin_{on} - Tdcon_{\min} + Tcdoff_{\max}$$

$$Tcdoff_{max} = Td \_Vout \_off_{max}$$

All switching time values (except the Td Vout on & off parameters) could change with the application schematic (output snubber filter) and with the PCB layout. Due to the internal pad, the input pin of the device has a parasitic capacitor Cin. This capacitor and the Rin (the recommended input resistor) create low pass filter and add an additional delay in the Tdcon value.

The minimum off time is the time to charge the bootstrap capacitor (recover the value before turn on the MOSFET) during the high duty cycle operation. In the high duty cycle value condition, due to the di/dt driver, the internal gate continues to move whereas the output voltage doesn't go down under 6v (from vbat). So the device still need energy from the bootstrap capacitor but it can not charge it. When the bootstrap capacitor is discharged the circuit goes in linear mode and it is stopped by the over power protection. To avoid this situation, the microprocessor must turn fully on the device after the minimum off time is reached as it is describe in the **Error! Reference source not found.**. The minimum off time is the minimum time to charge properly the bootstrap capacitor.

Figure 4: Switching time chronogram

Figure 5: High duty cycle operation recommendation

#### **Notes:**

#### **Decoupling capacitors:**

During the turn on and off phase, a high current (about a hundred mA) flows through the Vcc, the gnd and the boot. So the bootstrap capacitor and the decoupling must be as closer as possible. And it is forbidden to implement a resistor in series with the Gnd pin.

### **Bootstrap capacitor charge:**

The power on reset is necessary to charge the bootstrap capacitor before turns on the power mosfet. The bootstrap capacitor gets its charge through the load. So the time to charge it depends of the load.

But the power on reset doesn't monitor the bootstrap capacitor voltage. Its time is set internally to allow starting the most of load without implement a special sequence:

• If the inductance of the load is lower than 500µH, the power on reset is enough long to charge the bootstrap capacitor before turns on the power mosfet.

• If the inductance of the load is higher than  $500\mu H$ , the power on reset is not enough long to charge completely the bootstrap capacitor before turns on the power mosfet. So the micro-processor need to implement a special sequence to start the device without activates the output power mosfet. The  $\mu p$  send one short pulse (Twake min < short pulse < Tpwr\_on\_rst) then wait for the bootstrap capacitor is totally charged and after provide the appropriate duty cycle.

The bootstrap charge depends of the battery voltage, the bootstrap capacitor value and the inductance load value.

## Output high dv/dt immunity system:

The IR3330S has a high dv/dt immunity system. This function creates a negative gate biasing if the output voltage exceed 1.7V. So this device can be implemented in an H-bridge configuration.

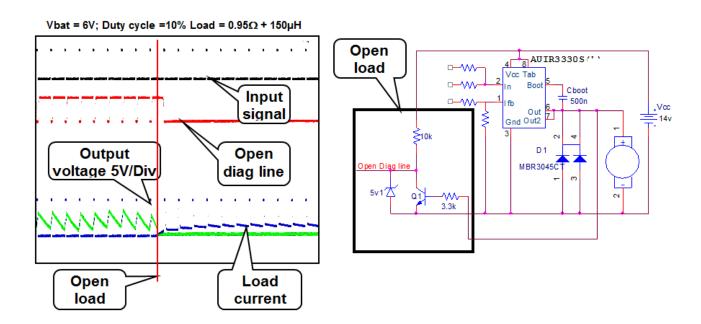

## **Open load detection function:**

The bootstrap regulator bias provides a current on device output. If the impedance between the Output and ground is too high, after the turn off of the output mosfet, the output never reaches the ground. So it becomes possible to detect easily an open load condition when the device switches. In fully on condition the open load condition will detect by the current feedback (easy thanks to a high current condition).

In the schematic below the component R7, Q1, R8, D2 create the detection open load and provide a logic level diagnostic (open diag line) even if the battery in low voltage condition.

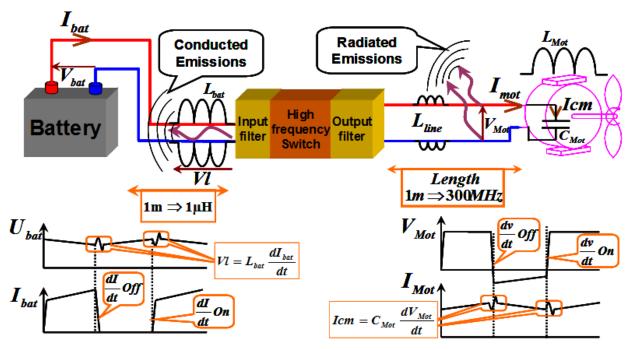

#### **EMI** consideration:

#### At vehicle level:

This is typical schematic of a high frequency power module in a vehicle (see: Error! Reference source not found.) with the parasitic element create by the connection wire. Between the battery and the module, the voltage is almost constant and the current switch at the application frequency. The power line creates a parasitic inductance with the current variation that generates voltage spike on the battery line. The level of this spike is directly linked to the conducted emissions level on the battery line. So control the current variation or the di/dt value reduces the conducted EMI level on the battery line. In this case use the AUIR3330 (active di/dt control) allows reducing significantly the conduced EMI level.

By analogy between the module and the load (see: Error! Reference source not found.), due to the high inductance value of the motor, the current is almost constant and the voltage switches at the application frequency. Due to the parasitic capacitor of the load each voltage variation create current spike on the load line. The level of this spike is directly linked to the radiated emissions level on the load line. So control the voltage variation or the dv/dt value reduces the radiated EMI level. In this case use the AUIR3340 (active dv/dt control) allows reducing significantly the radiated EMI level.

Figure 6: Typical schematic of a power module in a vehicle

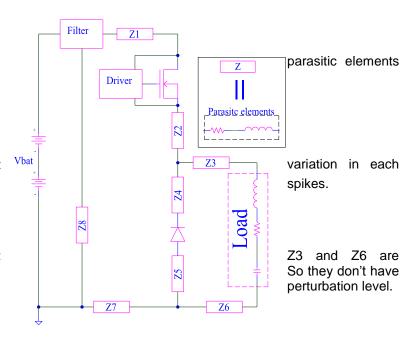

#### At module level:

This typical schematic takes into account the created by the PCB tracks. Its impedance is  $Ztrace = R + jL\omega$ .

$$\omega = 2\pi F$$

Due to the  $jL\omega$  element, the current line must be smooth to avoid the over voltage

$$U_l = L \frac{Di}{Dt}$$

The impedance value of the parasitic element negligible compare to the motor impedance. an important influence on the EMI

Figure 2: typical schematic of a power module

The parasitic component evaluation for DC and low frequency conditions are:

•

$$R = \rho \frac{l}{S}$$

•

$$L = 0.2 \times 10^{-6} \times l \times \left[ \ln(\frac{2 \times l}{d+e}) + 0.5 + 0.22(\frac{d+e}{l}) \right]$$

Where:

•  $\rho$ : material resistivity Cu = 1.7x10

l : track length in m

• S: track section in m<sup>2</sup> (d x e)

• d: track width in m

• e: track thickness in m

#### Example:

If the copper track characteristic between the MOSFET pin and the free wheeling diode (parasitic element Z2) is:

I = 2 cm

d = 1mm

$e = 35 \mu m$

So

$R = 0.9 m\Omega$

L = 8nH

If the MOSFET switches without any slope control, the di/dt can reach 100A/µs. The overvoltage spike created by the current variation in the parasitic inductance is then

•

$$U_1 = 8n * (100/1E-6) = 800mv$$

Now, if the MOSFET slope is controlled and limited to 40A/µs. Then, the overvoltage spike created by the current variation in the parasitic inductance is:

•

$$U_1 = 8n * (40/1E-6) = 320mV$$

Even if the PCB tracks are short, their parasitic impedances are not negligible in 20 kHz application. Limiting the current variation in these parasitic impedances reduces the overvoltage spikes so the noise level. For further information about the PCB impedance effect see the application note named "Using the AUIR3330/40: PCB layout recommendation" on the IR web site (www.irf.com).

#### Measured impact of the di/dt control:

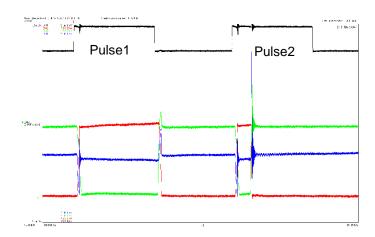

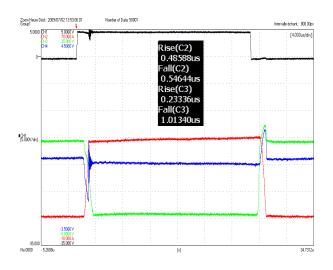

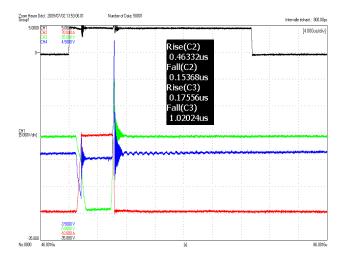

If the device detects an over current condition, it turns off the output MOSFET without di/dt sequence to reduce application stress. So a simple test, consists to look at the waveform before (pulse1) and during the over current protection shutdown (pulse 2) to see the di/dt impact with the same condition (even if the dv/dt stay constant).

- Black (Ch1) = In pwm 5V/div

- Red (Ch2) = drain current 10A/div

- Green (Ch3) = Vds (drain source voltage) 5V/div

- Blue (Ch4) = Vbat (battery voltage) in AC mode 1V/div

## Pulse1) <u>Oscilloscope screenshot in normal condition:</u>

The perturbation on the Vbat line during the turn on is due to the discontinuity of the current in the diode and intensified by the current loop implemented between the input filter and the device to measure the drain current (di/dt).

## 2) Oscilloscope screenshot during the over current shutdown:

This screenshot is the next pulse after this one shows previously. The perturbation on the Vbat line during the turn on is due to the discontinuity of the current in the diode and intensified by the current loop implemented between the input filter and the device to measure the drain current (di/dt).

Remove the di/dt sequence only on the turn off increase strongly the perturbation level (more than 20dB) on the power line even if the output dv/dt value doesn't change.

Note that in this example, the di/dt on sequence is still activated. By analogy with the turn off, we can easily guessed that the over all noise level will be increase if we could only keep the dv/dt on and remove the di/dt on.

#### Parameters curves:

Figure 8: Input parameters vs. temperature

Figure 9: Vth lfb vs. temperature

Figure 10: Under voltage parameters vs. temperature

Figure 11: Normalized Rdson Vs Tj

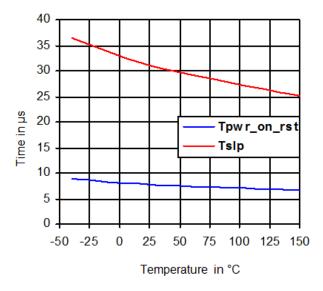

Figure 12: Tpwr\_on\_rst & Tslp vs. temperature

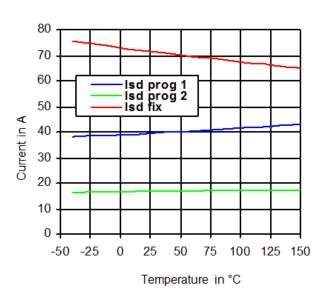

Figure 13: Current shutdown vs. temperature

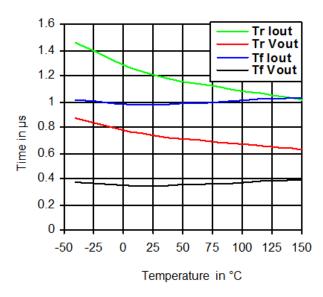

Figure 14: Rise and fall time vs. temperature

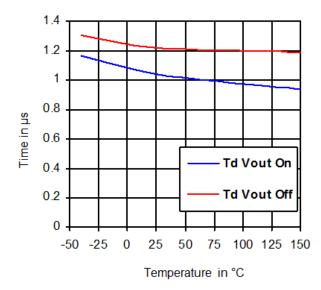

Figure 15: Tdon & off vs. temperature

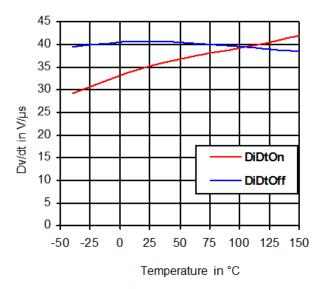

Figure 16: Dv/dt on & off vs. temperature

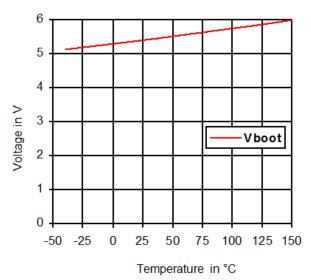

Figure 17: Bootstrap voltage vs. temperature

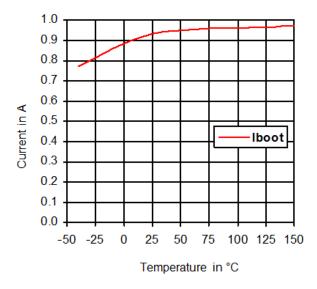

Figure 18: Current bootstrap vs. temperature

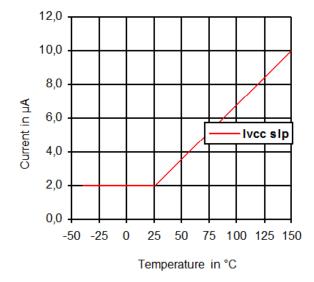

Figure 19: Vcc leakage current in sleep mode vs. temperature

Figure 20: Transient thermal impedance and model vs. time

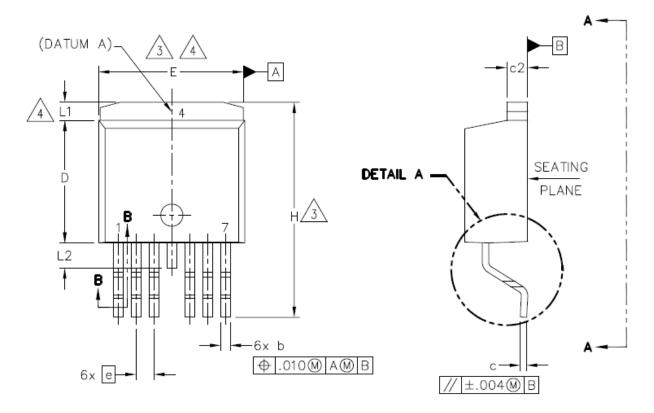

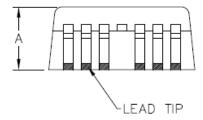

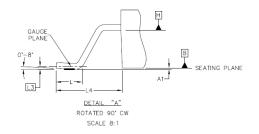

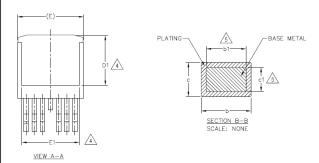

## **Case Outline 7L D2PAK**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING AS PER ASME Y14.5M-1994

- 2. DIMENSIONS ARE SHOWN IN MILLIMETERS [INCHES].

- 3. DIMENSION D & E DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.127 [.005"] PER SIDE. THESE DIMENSIONS ARE MEASURED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY AT DATUM H.

- 4. THERMAL PAD CONTOUR OPTIONAL WITHIN DIMENSION E, L1, D1 & E1.

- 5. DIMENSION 61 AND c1 APPLY TO BASE METAL ONLY.

- 6. DATUM A & B TO BE DETERMINED AT DATUM PLANE H.

- 7. CONTROLLING DIMENSION: INCH.

- OUTLINE CONFORMS TO JEDEC OUTLINE TO-263CB.

| S<br>Y<br>M | DIMENSIONS |       |      |                  |     |  |

|-------------|------------|-------|------|------------------|-----|--|

| B           | MILLIM     | ETERS | INC  | O<br>T<br>E<br>S |     |  |

| L           | MIN.       | MAX.  | MIN. | MAX.             | S   |  |

| Α           | 4.06       | 4.83  | .160 | .190             |     |  |

| A1          | _          | 0.254 | _    | .010             |     |  |

| b           | 0.51       | 0.99  | .020 | .036             |     |  |

| b1          | 0.51       | 0.89  | .020 | .032             | 5   |  |

| С           | 0.38       | 0.74  | .015 | .029             |     |  |

| c1          | 0.38       | 0.58  | .015 | .023             | 5   |  |

| c2          | 1.14       | 1.65  | .045 | .065             |     |  |

| D           | 8.38       | 9.65  | .330 | .380             | 3   |  |

| D1          | 6.86       | _     | .270 |                  | 4   |  |

| Ε           | 9.65       | 10.67 | .380 | .420             | 3,4 |  |

| E1          | 6.22       | _     | .245 |                  | 4   |  |

| е           | 2.54       | BSC   | .050 | BSC              |     |  |

| Н           | 14.61      | 15.88 | .575 | .625             |     |  |

| L           | 1.78       | 2.79  | .070 | .110             |     |  |

| L1          | _          | 1.68  | _    | .066             | 4   |  |

| L2          | _          | 1.78  | _    | .070             |     |  |

| L3          | 0.25       | BSC   | .010 | BSC              | ]   |  |

| L4          | 4.78       | 5.28  | .188 | .208             |     |  |

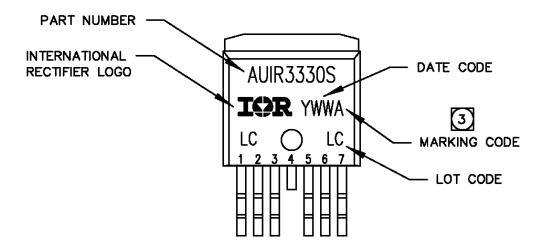

## **Part Marking Information**

**Ordering Information**

| Base Part Number |                    | Standard Pag        | Committee Boot Novel |                      |  |  |  |

|------------------|--------------------|---------------------|----------------------|----------------------|--|--|--|

| base Fait Number | Package Type       | Form                | Quantity             | Complete Part Number |  |  |  |

|                  | D2-Pak-7-<br>Leads | Tube                | 50                   | AUIR3330S            |  |  |  |

| AUIR3330S        |                    | Tape and reel left  | 800                  | AUIR3330STRL         |  |  |  |

|                  | Loads              | Tape and reel right | 800                  | AUIR3330STRR         |  |  |  |

#### **IMPORTANT NOTICE**

Unless specifically designated for the automotive market, International Rectifier Corporation and its subsidiaries (IR) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or services without notice. Part numbers designated with the "AU" prefix follow automotive industry and / or customer specific requirements with regards to product discontinuance and process change notification. All products are sold subject to IR's terms and conditions of sale supplied at the time of order acknowledgment.

IR warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with IR's standard warranty. Testing and other quality control techniques are used to the extent IR deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

IR assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using IR components. To minimize the risks with customer products and applications, customers should provide adequate design and operating safeguards.

Reproduction of IR information in IR data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alterations is an unfair and deceptive business practice. IR is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of IR products or serviced with statements different from or beyond the parameters stated by IR for that product or service voids all express and any implied warranties for the associated IR product or service and is an unfair and deceptive business practice. IR is not responsible or liable for any such statements.

IR products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of the IR product could create a situation where personal injury or death may occur. Should Buyer purchase or use IR products for any such unintended or unauthorized application, Buyer shall indemnify and hold International Rectifier and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that IR was negligent regarding the design or manufacture of the product.

Only products certified as military grade by the Defense Logistics Agency (DLA) of the US Department of Defense are designed and manufactured to meet DLA military specifications required by certain military, aerospace or other applications. Buyers acknowledge and agree that any use of IR products not certified by DLA as military-grade, in applications requiring military grade products, is solely at the Buyer's own risk and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

IR products are neither designed nor intended for use in automotive applications or environments unless the specific IR products are designated by IR as compliant with ISO/TS 16949 requirements and bear a part number including the designation "AU". Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, IR will not be responsible for any failure to meet such requirements.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

#### **WORLD HEADQUARTERS:**

101 N. Sepulveda Blvd., El Segundo, California 90245 Tel: (310) 252-7105

## **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

## Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

#### http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

### Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru 4 moschip.ru 9