# XR33152/56/58

# ±60V Fault Tolerant 3.0V to 5.5V TIA-485/TIA-422 Transceivers

## **Description**

The XR33152, XR33156 and XR33158 family of high performance TIA-485/TIA-422 devices are designed for improved performance in noisy industrial environments and increased tolerance to system faults.

The analog bus pins can withstand direct shorts up to ±60V and are protected against ESD events up to ±15kV HBM. An extended ±25V common mode operating range allows for more reliable operation in noisy environments.

The receivers include full fail-safe circuitry, guaranteeing a logic high receiver output when the receiver inputs are open, shorted or undriven. The XR33152 receiver input impedance is at least  $120k\Omega$  (1/10 unit load), allowing more than 320 devices on the bus. The XR33156/58 receiver input impedance is at least  $30k\Omega$  (1/2.5 unit load), allowing more than 80 devices on the bus.

The drivers are protected by short circuit detection as well as thermal shutdown and maintain high impedance in shutdown or when powered off. The XR33152 driver is slew limited for reduced EMI and error-free communication over long or unterminated data cables.

The XR33152/56/58 family of high performance TIA-485/TIA-422 devices are designed for improved performance in noisy industrial environments and increased tolerance to system faults.

The devices with DE and RE pins include hot swap circuitry to prevent false transitions on the bus during power up or live insertion and can enter a 1nA low current shutdown mode for extreme power savings.

#### **FEATURES**

- 3.0V to 5.5V operation

- ±60V fault tolerance on analog bus pins

- Extended ±25V common mode operation

- Robust ESD protection: ±15kV HBM (bus pins)

- □ ± 4kV HBM (non-bus pins)

- 1.65V to 5.5V logic Interface VL pin (full-duplex package option)

- Invert control to correct for reversed bus pins

- Enhanced receiver fail-safe protection for open, shorted or terminated but idle data lines

- Hot swap glitch protection on DE and RE pins

- Driver short-circuit current limit and thermal shutdown for overload protection

- Reduced unit loads allows up to 320 devices on bus

- Industry standard 8 and 14-pin **NSOIC** packages

- -40°C to 85°C ambient operating temperature range

#### **APPLICATIONS**

- Industrial control networks

- **HVAC** networks

- Building and process automation

- Remote utility meter reading

- Energy monitoring and control

- Long or unterminated transmission lines

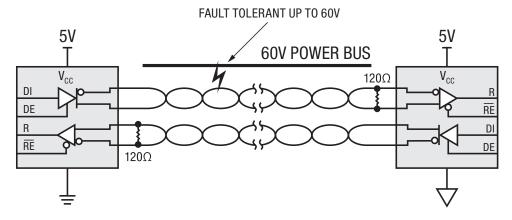

## **Typical Application**

Figure 1. Typical Application

RFV1A 1/19

## **Absolute Maximum Ratings**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections to the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

| V <sub>CC</sub>                                                                                           | -0.3V to 7.0V                        |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|

| V <sub>L</sub>                                                                                            | $V_L \le V_{CC}$                     |

| Input voltage at control and driver input (DE, DI and INV) XR33152/58                                     | -0.3V to (V <sub>CC</sub> + 0.3V)    |

| Receiver output voltage (RO) XR33152/58                                                                   | -0.3V to (V <sub>CC</sub> + 0.3V)    |

| Input voltage at control (RE) XR33156                                                                     | -0.3V to (V <sub>L</sub> + 0.3V)     |

| Input voltage at control and driver input (DE, DI, R <sub>INV</sub> , D <sub>INV</sub> , and INV) XR33156 | -0.3V to 7.0V                        |

| Receiver output voltage (RO) XR33156                                                                      | -0.3V to (V <sub>L</sub> + 0.3V)     |

| Driver output voltage (A, B, Y and Z)                                                                     | ±60V                                 |

| Receiver input voltage (A and B, half or full duplex)                                                     | ±60V                                 |

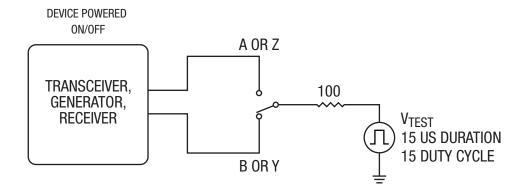

| Transient voltage pulse, through 100Ω (Figure 7)                                                          | ±100V                                |

| Driver output current                                                                                     | ±250mA                               |

| Storage temperature range                                                                                 | -65°C to 150°C                       |

| Lead temperature (soldering, 10s)                                                                         | 300°C                                |

| Package power dissipation 8-pin NSOIC $\theta_{JA}$ = 128.4°C/W 14-pin NSOIC $\theta_{JA}$ = 86°C/W       | Maximum junction temperature = 150°C |

#### CAUTION:

ESD-sensitive (electrostatic discharge) device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

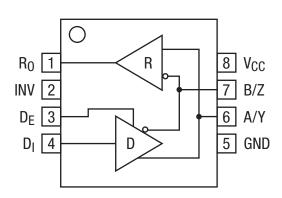

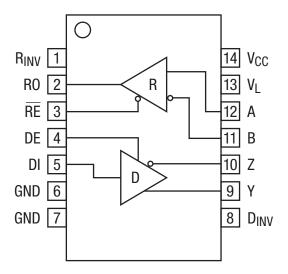

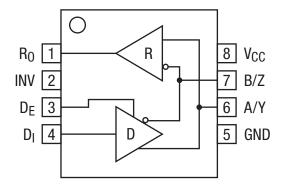

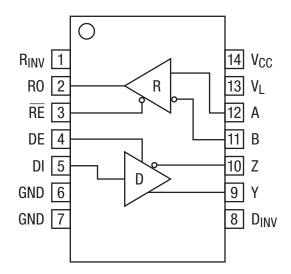

# **Pin Configuration**

# **Pin Functions**

| Half Duplex | Full Duplex |                  |       |                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------|------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XR33152     | XR33156     | Pin Name         | Type  | Pin Function                                                                                                                                                                                                                                                                                                              |

| XR33158     |             | 1 III I Vallic   | Турс  | THIT GIOLOTT                                                                                                                                                                                                                                                                                                              |

| Pin Nı      | umber       |                  |       |                                                                                                                                                                                                                                                                                                                           |

| -           | 1           | R <sub>INV</sub> | ln    | Receiver invert control (active high). When enabled, the polarity of the receiver bus pins (A & B) is reversed: A = inverting and B = non-inverting. When disabled, the receiver bus pins (A & B) operate normally: A = non-inverting and B = inverting. The $R_{\text{INV}}$ pin has a 150K $\Omega$ pull-down resistor. |

| 1           | 2           | RO               | Out   | Receiver output, when $\overline{\text{RE}}$ is low and if (A-B) $\geq$ 200mV, RO is high. If (A-B) $\leq$ -200mV, RO is low If inputs are left floating, shorted together or terminated and undriven for more than 2 $\mu$ s the output is high.                                                                         |

| 2           | -           | INV              | ln    | Driver and receiver invert control (active high). When enabled, the polarity of the driver input and receiver input bus pins is inverted. When disabled, the driver input and receiver inputs operate normally: A = non-inverting and B = inverting. The INV pin has a $150 \text{k}\Omega$ pull-down resistor.           |

| -           | 3           | RE               | In    | Receiver output enable (hot swap). When $\overline{RE}$ is low, RO is enabled. When $\overline{RE}$ is high, RO is high impedance. $\overline{RE}$ should be high and DE should be low to enter shutdown mode.                                                                                                            |

| 3           | 4           | DE               | In    | Driver output enable (hot swap). When DE is high, outputs are enabled. When DE is low, outputs are high impedance. DE should be low and RE should be high to enter shutdown mode.                                                                                                                                         |

| 4           | 5           | DI               | ln    | Driver input. With DE high, a low level on DI forces non-inverting output low and inverting output high. Similarly, a high level on DI forces non-inverting output high and inverting output low.                                                                                                                         |

| 5           | 6, 7        | GND              | Power | Ground.                                                                                                                                                                                                                                                                                                                   |

| 6           | -           | A/Y              | I/O   | Non-inverting receiver input and non-Inverting driver output.                                                                                                                                                                                                                                                             |

| 7           | -           | B/Z              | I/O   | Inverting receiver input and Inverting driver output.                                                                                                                                                                                                                                                                     |

# **Pin Functions**

| Half Duplex | Full Duplex |                  |       |                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------|-------------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XR33152     | XR33156     | Pin Name         | Type  | Pin Function                                                                                                                                                                                                                                                                                                                 |  |  |  |

| XR33158     |             | 1 III I tallio   | 1,750 | Pili Pulicion                                                                                                                                                                                                                                                                                                                |  |  |  |

| Pin Number  |             |                  |       |                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 8           | 14          | V <sub>CC</sub>  | Power | 3.0V to 5.5V power supply input bypass to ground with 0.1µF capacitor.                                                                                                                                                                                                                                                       |  |  |  |

| -           | 12          | А                | In    | Non inverting receiver input.                                                                                                                                                                                                                                                                                                |  |  |  |

| -           | 11          | В                | In    | Inverting receiver input.                                                                                                                                                                                                                                                                                                    |  |  |  |

| -           | 9           | Y                | Out   | Non-inverting driver output.                                                                                                                                                                                                                                                                                                 |  |  |  |

| -           | 10          | Z                | Out   | Inverting driver output.                                                                                                                                                                                                                                                                                                     |  |  |  |

| -           | 8           | D <sub>INV</sub> | In    | Driver invert control (active high). When enabled, the polarity of the driver input pin is inverted causing the driver output (Y & Z) polarities to be inverted. When disabled, the driver bus pins (Y & Z) operate normally: Y = non-inverting and Z = inverting. The $D_{INV}$ pin has a 150k $\Omega$ pull-down resistor. |  |  |  |

| -           | 13          | V <sub>L</sub>   | Power | Logic interface power supply.                                                                                                                                                                                                                                                                                                |  |  |  |

# **Pin Functions**

XR33156 (Full Duplex - 14 Pins)

|                  | Transmitting |      |    |                   |   |  |  |  |

|------------------|--------------|------|----|-------------------|---|--|--|--|

|                  | ln           | puts |    | Outputs           |   |  |  |  |

| D <sub>INV</sub> | RE           | DE   | DI | Υ                 | Z |  |  |  |

| 0                | ×            | 1    | 1  | 1                 | 0 |  |  |  |

| 0                | ×            | 1    | 0  | 0                 | 1 |  |  |  |

| 1                | ×            | 1    | 1  | 0                 | 1 |  |  |  |

| 1                | ×            | 1    | 0  | 1                 | 0 |  |  |  |

| Х                | 0            | 0    | Х  | High-Z            |   |  |  |  |

| Х                | 1            | 0    | Х  | High-Z (shutdown) |   |  |  |  |

XR33156 (Full Duplex - 14 Pins)

|                  | Receiving |        |                                 |                   |  |  |  |  |

|------------------|-----------|--------|---------------------------------|-------------------|--|--|--|--|

|                  |           | Inputs |                                 | Output            |  |  |  |  |

| R <sub>INV</sub> | RE        | DE     | V <sub>A</sub> - V <sub>B</sub> | RO                |  |  |  |  |

| 0                | 0         | X      | ≥ 200mV                         | 1                 |  |  |  |  |

| 0                | 0         | X      | ≤ -200mV                        | 0                 |  |  |  |  |

| 0                | 0         | Х      | Open/shorted                    | 1                 |  |  |  |  |

| 1                | 0         | X      | ≥ 200mV                         | 0                 |  |  |  |  |

| 1                | 0         | X      | ≤ -200mV                        | 1                 |  |  |  |  |

| 1                | 0         | Х      | Open/shorted                    | 1                 |  |  |  |  |

| Х                | 1         | 1      | Х                               | High-Z            |  |  |  |  |

| Х                | 1         | 0      | Х                               | High-Z (shutdown) |  |  |  |  |

## XR33152 and XR33158 (Half Duplex - 8 Pins)

| Transmitting |    |    |        |      |  |  |  |

|--------------|----|----|--------|------|--|--|--|

| Inputs       |    |    | Out    | outs |  |  |  |

| INV          | DE | DI | A/Y    | B/Z  |  |  |  |

| 0            | 1  | 1  | 1      | 0    |  |  |  |

| 0            | 1  | 0  | 0      | 1    |  |  |  |

| 1            | 1  | 1  | 0      | 1    |  |  |  |

| 1            | 1  | 0  | 1      | 0    |  |  |  |

| X            | 0  | Х  | High-Z |      |  |  |  |

XR33152 and XR33158 (Half Duplex - 8 Pins)

| Receiving |        |                                 |    |  |  |  |  |

|-----------|--------|---------------------------------|----|--|--|--|--|

|           | Inputs |                                 |    |  |  |  |  |

| INV       | DE     | V <sub>A</sub> - V <sub>B</sub> | RO |  |  |  |  |

| 0         | 0      | ≥ 200mV                         | 1  |  |  |  |  |

| 0         | 0      | ≤ -200mV                        | 0  |  |  |  |  |

| 1         | 0      | Open/shorted                    | 1  |  |  |  |  |

| 1         | 0      | ≥ +200mV                        | 0  |  |  |  |  |

| 1         | 0      | ≤ -200mV                        | 1  |  |  |  |  |

| 1         | 0      | Open/shorted                    | 1  |  |  |  |  |

Unless otherwise noted:  $V_{CC} = 3.0V$  to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$ °C.

| Symbol            | Parameter                                                                        | Conditions                                                                                | Min                 | Тур | Max                 | Units |

|-------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|-----|---------------------|-------|

|                   |                                                                                  | Driver DC Characteristics                                                                 |                     |     |                     |       |

| V <sub>CC</sub>   | Supply voltage range                                                             |                                                                                           | 3.0                 |     | 5.5                 | V     |

| V <sub>L</sub>    | I/O logic supply voltage range                                                   | V <sub>L</sub> ≤ V <sub>CC</sub>                                                          | 1.65                |     | 5.5                 | V     |

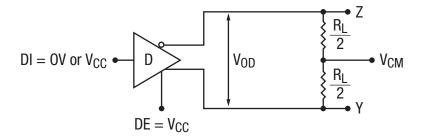

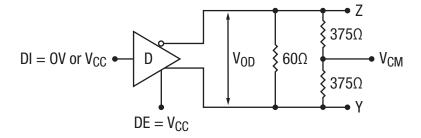

|                   |                                                                                  | $R_L$ = 100Ω (TIA-422), Figure 4                                                          | 2                   |     | V <sub>CC</sub>     | V     |

| V <sub>OD</sub>   | Differential driver output,<br>$4.5V \le V_{CC} \le 5.5V$                        | $R_L = 54\Omega$ (TIA-485), Figure 4                                                      | 1.5                 |     | V <sub>CC</sub>     | V     |

|                   | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V                                                    | -25V ≤ V <sub>CM</sub> ≤ 25V, Figure 5                                                    | 1.5                 |     | V <sub>CC</sub>     | V     |

| .,                | Differential driver output,                                                      | $R_L$ = 100Ω (TIA-422), Figure 4                                                          | 0.85                |     | V <sub>CC</sub>     | V     |

| V <sub>OD</sub>   | 3.0V ≤ V <sub>CC</sub> ≤ 4.5V                                                    | R <sub>L</sub> = 54Ω (TIA-485), Figure 4                                                  | 0.65                |     | V <sub>CC</sub>     | V     |

| ΔV <sub>OD</sub>  | Change in magnitude of differential output voltage, Note 1                       |                                                                                           |                     |     | ±0.2                | V     |

| V <sub>CM</sub>   | Driver common-mode output voltage (steady state)                                 | RL = 100Ω (TIA-422) or<br>RL = 54Ω (TIA-485), Figure 4                                    | 1                   |     | 3                   | V     |

| $\Delta V_{CM}$   | Change in magnitude of common-mode output voltage, Note 1                        |                                                                                           |                     |     | ±0.2                | V     |

| V                 | Logic high input thresholds                                                      | V <sub>CC</sub> = 3.3V, for XR33152/58                                                    | 2.0                 |     |                     | V     |

| V <sub>IH</sub>   | (DI, DE and INV)                                                                 | V <sub>CC</sub> = 5.0V, for XR33152/58                                                    | 2.4                 |     |                     | V     |

| V <sub>IL</sub>   | Logic low input thresholds (DI, DE and INV)                                      | For XR33152/58                                                                            |                     |     | 0.8                 | V     |

| V <sub>IH</sub>   | Logic high input thresholds (DI, DE, RE, D <sub>INV</sub> and R <sub>INV</sub> ) | $V_L \le V_{CC}$ , for XR33156                                                            | (2/3)V <sub>L</sub> |     |                     | V     |

| V <sub>IL</sub>   | Logic low input thresholds (DI, DE, RE, D <sub>INV</sub> and R <sub>INV</sub> )  | $V_L \le V_{CC}$ , for XR33156                                                            |                     |     | (1/3)V <sub>L</sub> | V     |

| V <sub>HYS</sub>  | Input hysteresis<br>(DI, DE, RE, D <sub>INV</sub> , R <sub>INV</sub> and INV)    |                                                                                           |                     | 100 |                     | mV    |

|                   | Logic input current (DI, DE and RE)                                              | 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> , for XR33152/58<br>After first transition, Note 2 |                     |     | ±1                  | μΑ    |

|                   | Logic input current (INV)                                                        | $V_{IN} = V_{CC} = 5.5V$ , for XR33152/58                                                 | 25                  | 33  | 55                  | μΑ    |

| I <sub>IN</sub>   | Logic input current (DI, DE and RE)                                              | $0V \le V_{IN} \le V_{L} = V_{CC} = 5.5V$ , for XR33156<br>After first transition, Note 2 |                     |     | ±1                  | μΑ    |

|                   | Logic input current (D <sub>INV</sub> and R <sub>INV</sub> )                     | $V_{IN} = V_{L} = V_{CC} = 5.5V$ , for XR33156                                            | 25                  | 33  | 55                  | μΑ    |

| I <sub>INHS</sub> | Logic input current hot swap (DE and RE)                                         | Until first transition, Note 2                                                            |                     | 100 | ±200                | μA    |

|                   |                                                                                  | V <sub>CC</sub> = 0V or 5.5V, V <sub>OUT</sub> = 12V,<br>DE = 0V, for XR33152             |                     |     | 100                 | μΑ    |

| 1. 5              | Input current (A and B)                                                          | V <sub>CC</sub> = 0V or 5.5V, V <sub>OUT</sub> = -7V,<br>DE = 0V, for XR33152             | -80                 |     |                     | μА    |

| I <sub>A, B</sub> | input current (A and B)                                                          | V <sub>OUT</sub> = 12V, DE = 0V,<br>V <sub>CC</sub> = 0V or 5.5V, for XR33156/58          |                     |     | 400                 | μΑ    |

|                   |                                                                                  | V <sub>OUT</sub> = -7V, DE = 0V,<br>V <sub>CC</sub> = 0V or 5.5V, for XR33156/58          | -320                |     |                     | μΑ    |

#### NOTES:

<sup>2.</sup> The hot swap feature disables the DE and  $\overline{\text{RE}}$  inputs for the first 10µs after power is applied. Following this time period, these inputs are weakly pulled to their disabled state (low for DE, high for  $\overline{\text{RE}}$ ) until the first transition, after which they become high impedance inputs.

<sup>1.</sup> Change in magnitude of differential output voltage and change in magnitude of common mode output voltage are the changes in output voltage when DI input changes state.

Unless otherwise noted:  $V_{CC}$  = 3.0V to 5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC}$  = 5.0V,  $T_A$  = 25°C.

| Symbol              | Parameter                                                                                                | Conditions                                                                                                  | Min                   | Тур   | Max  | Units |

|---------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|

|                     | Output leakage (Y and Z)                                                                                 | V <sub>OUT</sub> = 12V, DE = 0V, V <sub>CC</sub> = 0V or 5.5V                                               |                       |       | 100  | μΑ    |

| I <sub>OL</sub>     | Full duplex                                                                                              | V <sub>OUT</sub> = -7V, DE = 0V, V <sub>CC</sub> = 0V or 5.5V                                               | -80                   |       |      | μΑ    |

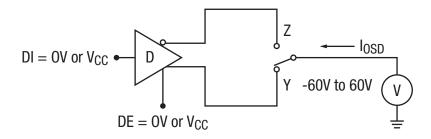

| I <sub>OSD</sub>    | Driver short-circuit output current                                                                      | -60V ≤ V <sub>OUT</sub> ≤ 60V, Figure 6                                                                     |                       |       | ±250 | μΑ    |

|                     |                                                                                                          | Driver Thermal Characteristics                                                                              |                       |       |      |       |

| T <sub>TS</sub>     | Thermal shutdown temperature                                                                             | Junction temperature, Note 1                                                                                |                       | 175   |      | °C    |

| T <sub>TSH</sub>    | Thermal shutdown hysteresis                                                                              | Note 1                                                                                                      |                       | 15    |      | °C    |

|                     |                                                                                                          | Receiver DC Characteristics                                                                                 |                       |       |      |       |

| V <sub>STH</sub>    | Receiver differential input signal threshold voltage (V <sub>A</sub> - V <sub>B</sub> )                  | -25V ≤ V <sub>OUT</sub> ≤ 25V                                                                               |                       | ±85   | ±200 | mV    |

| ΔV <sub>STH</sub>   | Receiver differential input signal hysteresis                                                            |                                                                                                             |                       | 170   |      | mV    |

| V <sub>FSTH</sub> - | Negative going receiver differential input failsafe threshold voltage (V <sub>A</sub> - V <sub>B</sub> ) | -25V ≤ V <sub>OUT</sub> ≤ 25V                                                                               | -200                  | -125  | -40  | mV    |

| V <sub>FSTH+</sub>  | Positive going receiver differential input failsafe threshold voltage (V <sub>A</sub> - V <sub>B</sub> ) | -25V ≤ V <sub>OUT</sub> ≤ 25V                                                                               |                       | -100  | -10  | mV    |

| $\Delta V_{FSTH}$   | Receiver differential input failsafe hysteresis                                                          |                                                                                                             |                       | 25    |      | mV    |

| V <sub>OH</sub>     | Receiver output high voltage (RO)                                                                        | I <sub>OUT</sub> = -4mA, for XR33152/58                                                                     | V <sub>CC</sub> - 0.6 |       |      | V     |

| V <sub>OL</sub>     | Receiver output low voltage (RO)                                                                         | I <sub>OUT</sub> = 4mA, for XR33152/58                                                                      |                       |       | 0.4  | V     |

| V <sub>OH</sub>     | Receiver output high voltage (RO)                                                                        | $3.0V \le V_L \le 5.5V$ , $I_{OUT} = -4mA$ ,<br>$1.6V \le V_L \le 3.0V$ , $I_{OUT} = -1mA$ ,<br>for XR33156 | V <sub>L</sub> - 0.6  |       |      | V     |

| V <sub>OL</sub>     | Receiver output low voltage (RO)                                                                         | $3.0V \le V_L \le 5.5V$ , $I_{OUT} = 4mA$ ,<br>$1.6V \le V_L \le 3.0V$ , $I_{OUT} = 1mA$ ,<br>for XR33156   |                       |       | 0.4  | V     |

| I <sub>OZR</sub>    | High-Z receiver output current                                                                           | $0V \le V_{OUT} \le V_{CC}$ , for XR33152/58<br>$0V \le V_{OUT} \le V_{L}$ , for XR33156                    |                       |       | ±1   | μΑ    |

| Б                   | DV insult registers                                                                                      | -25V ≤ V <sub>CM</sub> ≤ 25V, for XR33152                                                                   | 120                   |       |      | kΩ    |

| R <sub>IN</sub>     | RX input resistance                                                                                      | -25V ≤ V <sub>CM</sub> ≤ 25V, for XR33156/58                                                                | 30                    |       |      | kΩ    |

|                     | RX output short-circuit current                                                                          | $0V \le V_{RO} \le V_{CC}$ , for XR33152/58                                                                 |                       |       | 110  | mA    |

| I <sub>OSC</sub>    | RX output short-circuit current                                                                          | $0V \le V_{RO} \le V_L$ , for XR33156                                                                       |                       |       | 110  | mA    |

|                     |                                                                                                          | Supply Current                                                                                              |                       |       |      |       |

| I <sub>CC</sub>     | Supply current                                                                                           | No load, $\overline{RE} = 0V$ or $V_{CC}$ , $DE = V_{CC}$ , $DI = 0V$ or $V_{CC}$                           |                       |       | 4    | mA    |

| I <sub>SHDN</sub>   | Supply current in shutdown mode                                                                          | $\overline{RE} = V_{CC}, DE = 0V$                                                                           |                       | 0.001 | 1    | μΑ    |

|                     |                                                                                                          | ESD Protection                                                                                              |                       |       |      |       |

|                     | ESD protection for A, B, Y, and Z                                                                        | Human body model                                                                                            |                       | ±15   |      | kV    |

|                     | ESD protection for all other pins                                                                        | Human body model                                                                                            |                       | ±4    |      | kV    |

#### NOTES:

<sup>1.</sup> This spec is guaranteed by design and bench characterization.

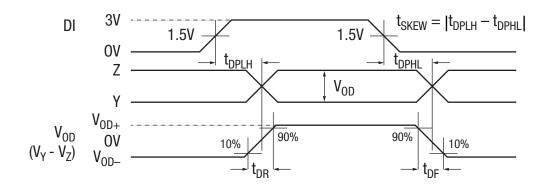

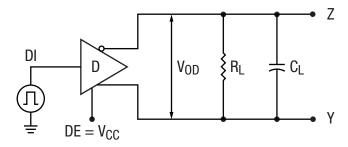

## Driver AC Characteristics - XR33152 (250kbps)

Unless otherwise noted:  $V_{CC} = 3.0V$  to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$ °C.

| Symbol                                  | Parameter                                    | Conditions                                   | Min | Тур | Max  | Units |

|-----------------------------------------|----------------------------------------------|----------------------------------------------|-----|-----|------|-------|

| t <sub>DPLH</sub>                       | Driver prop. delay (low to high)             |                                              | 350 |     | 1500 | ns    |

| t <sub>DPHL</sub>                       | Driver prop. delay (high to low)             | $C_L = 50 pF, R_L = 54 \Omega,$              | 350 |     | 1600 | ns    |

| It <sub>DPLH</sub> -t <sub>DPHL</sub> I | Differential driver output skew              | Figure 8                                     |     | 20  | 200  | ns    |

| t <sub>DR</sub> , t <sub>DF</sub>       | Driver differential output rise or fall time |                                              | 400 |     | 1500 | ns    |

|                                         | Maximum data rate                            | 1/t <sub>UI</sub> , duty cycle 40% to 60%    | 250 |     |      | kbps  |

| t <sub>DZH</sub>                        | Driver enable to output high                 |                                              |     | 200 | 2500 | ns    |

| t <sub>DZL</sub>                        | Driver enable to output low                  | $C_L = 50pF, R_L = 500\Omega,$               |     | 200 | 2500 | ns    |

| t <sub>DHZ</sub>                        | Driver disable from output high              | Figure 9                                     |     |     | 250  | ns    |

| t <sub>DLZ</sub>                        | Driver disable from output low               |                                              |     |     | 250  | ns    |

| t <sub>RZH(SHDN)</sub>                  | Driver enable from shutdown to output high   | $C_L = 50 pF, R_L = 500 \Omega,$<br>Figure 9 |     |     | 5500 | ns    |

| t <sub>RZL(SHDN)</sub>                  | Driver enable from shutdown to output low    |                                              |     |     | 5500 | ns    |

| t <sub>SHDN</sub>                       | Time to shutdown                             | Notes 1 and 2                                | 50  | 200 | 600  | ns    |

## Receiver AC Characteristics - XR33152 (250kbps)

Unless otherwise noted:  $V_{CC} = 3.0V$  to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$ °C.

| Symbol                                  | Parameter                          | Conditions                                                                   | Min | Тур | Max | Units |

|-----------------------------------------|------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|-------|

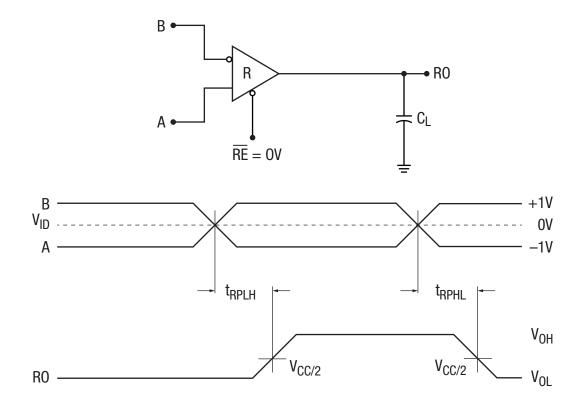

| t <sub>RPLH</sub>                       | Receiver prop. delay (low to high) | $C_L$ = 15pF, $V_{ID}$ = ±2V, $V_{ID}$ rise and fall times < 15ns, Figure 10 |     |     | 200 | ns    |

| t <sub>RPHL</sub>                       | Receiver prop. delay (high to low) |                                                                              |     |     | 200 | ns    |

| It <sub>RPLH</sub> -t <sub>RPHL</sub> I | Receiver propagation delay skew    |                                                                              |     |     | 30  | ns    |

|                                         | Maximum data rate                  | 1/t <sub>UI</sub> , duty cycle 40% to 60%                                    | 250 |     |     | kbps  |

#### NOTES

8/19

<sup>1.</sup> The transceivers are put into shutdown by bringing RE high and DE low simultaneously for at least 600ns. If the control inputs are in this state for less than 50ns, the device is guaranteed to not enter shutdown. If the enable inputs are held in this state for at least 600ns, the device is ensured to be in shutdown. Note that the receiver and driver enable times increase significantly when coming out of shutdown.

<sup>2.</sup> This spec is guaranteed by design and bench characterization.

## Driver AC Characteristics - XR33156 and XR33158 (20Mbps)

Unless otherwise noted:  $V_{CC} = 3.0V$  to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$ °C.

| Symbol                                  | Parameter                                    | Conditions                                  | Min | Тур | Max  | Units |

|-----------------------------------------|----------------------------------------------|---------------------------------------------|-----|-----|------|-------|

| t <sub>DPLH</sub>                       | Driver prop. delay (low to high)             |                                             |     |     | 25   | ns    |

| t <sub>DPHL</sub>                       | Driver prop. delay (high to low)             | $C_L = 50pF, R_L = 54\Omega,$               |     |     | 25   | ns    |

| It <sub>DPLH</sub> -t <sub>DPHL</sub> I | Differential driver output skew              | Figure 8                                    |     |     | 5    | ns    |

| t <sub>DR</sub> , t <sub>DF</sub>       | Driver differential output rise or fall time |                                             |     |     | 15   | ns    |

|                                         | Maximum data rate                            | 1/t <sub>UI</sub> , duty cycle 40% to 60%   | 20  |     |      | Mbps  |

| t <sub>DZH</sub>                        | Driver enable to output high                 |                                             |     |     | 60   | ns    |

| t <sub>DZL</sub>                        | Driver enable to output low                  | $C_L = 50pF, R_L = 500\Omega,$              |     |     | 60   | ns    |

| t <sub>DHZ</sub>                        | Driver disable from output high              | Figure 9                                    |     |     | 250  | ns    |

| t <sub>DLZ</sub>                        | Driver disable from output low               |                                             |     |     | 250  | ns    |

| t <sub>DZH(SHDN)</sub>                  | Driver enable from shutdown to output high   | $C_L = 50$ pF, $R_L = 500\Omega$ , Figure 9 |     |     | 2200 | ns    |

| t <sub>DZL(SHDN)</sub>                  | Driver enable from shutdown to output low    |                                             |     |     | 2200 | ns    |

| t <sub>SHDN</sub>                       | Time to shutdown                             | Notes 1 and 2                               | 50  | 200 | 600  | ns    |

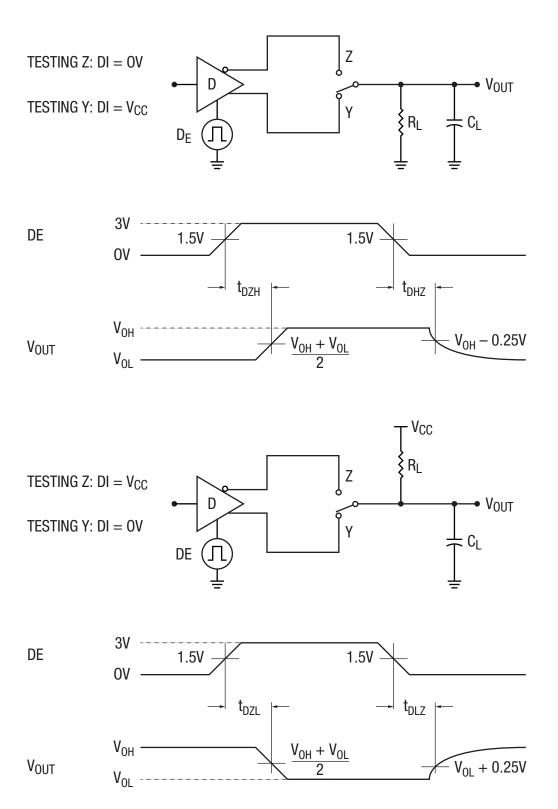

## Receiver AC Characteristics - XR33156 and XR33158 (20Mbps)

Unless otherwise noted:  $V_{CC} = 3.0V$  to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ . Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$ °C.

| Symbol                                  | Parameter                                    | Conditions                                                                                   | Min | Тур | Max  | Units |

|-----------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|------|-------|

| t <sub>RPLH</sub>                       | Receiver prop. delay (low to high)           | C = 15pE V = +10V                                                                            |     |     | 60   | ns    |

| t <sub>RPHL</sub>                       | Receiver prop. delay (high to low)           | C <sub>L</sub> = 15pF, V <sub>ID</sub> = ±2V,<br>V <sub>ID</sub> rise and fall times < 15ns, |     |     | 60   | ns    |

| It <sub>RPLH</sub> -t <sub>RPHL</sub> I | Receiver propagation delay skew              | Figure 10                                                                                    |     |     | 5    | ns    |

|                                         | Maximum data rate                            | 1/t <sub>UI</sub> , duty cycle 40% to 60%                                                    | 20  |     |      | Mbps  |

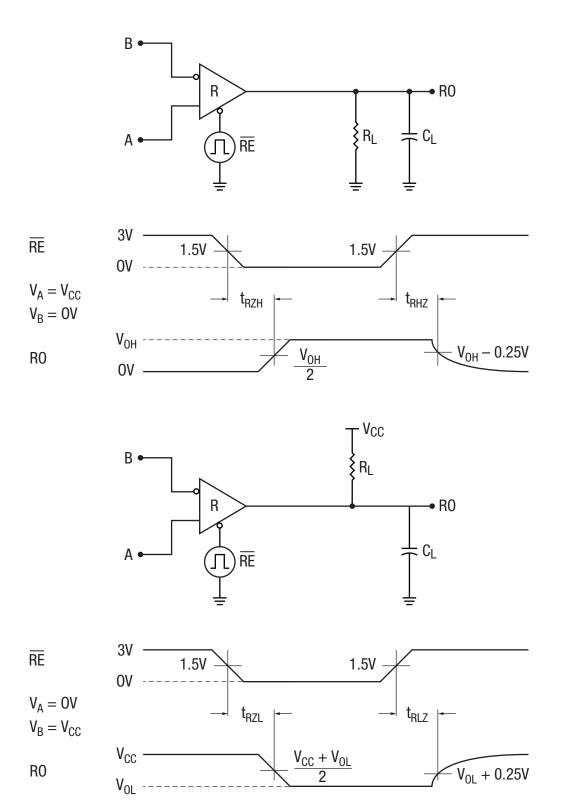

| t <sub>RZH</sub>                        | Receiver enable to output high               |                                                                                              |     |     | 50   | ns    |

| t <sub>RZL</sub>                        | Receiver enable to output low                | $C_L$ = 15pF, $R_L$ = 1k $\Omega$ , Figure 11, for XR33156                                   |     |     | 50   | ns    |

| t <sub>RHZ</sub>                        | Receiver disable from output high            |                                                                                              |     |     | 50   | ns    |

| t <sub>RLZ</sub>                        | Receiver disable from output low             |                                                                                              |     |     | 50   | ns    |

| t <sub>RZH(SHDN)</sub>                  | Receiver enable from shutdown to output high | $C_L = 15pF, R_L = 1k\Omega,$                                                                |     |     | 2200 | ns    |

| t <sub>RZL(SHDN)</sub>                  | Receiver enable from shutdown to output low  | Figure 11, for XR33156                                                                       |     |     | 2200 | ns    |

| t <sub>SHDN</sub>                       | Time to shutdown                             | Notes 1 and 2, for XR33156                                                                   | 50  | 200 | 600  | ns    |

#### NOTES

<sup>2.</sup> This spec is guaranteed by design and bench characterization.

<sup>1.</sup> The transceivers are put into shutdown by bringing  $\overline{\text{RE}}$  high and DE low simultaneously for at least 600ns. If the control inputs are in this state for less than 50ns, the device is guaranteed to not enter shutdown. If the enable inputs are held in this state for at least 600ns, the device is ensured to be in shutdown. Note that the receiver and driver enable times increase significantly when coming out of shutdown.

Figure 2. Half Duplex (XR33152, and XR33158)

Figure 3. Full Duplex (XR33156)

Figure 4. Differential Driver Output Voltage

Figure 5. Differential Driver Output Voltage Over Common Mode

Figure 6. Driver Output Short Circuit Current

Figure 7. Transient Overvoltage Test Circuit

Figure 8. Driver Propagation Delay Test Circuit and Timing Diagram

Figure 9. Driver Enable and Disable Timing Test Circuits and Timing Diagrams

Figure 10. Receiver Propagation Delay Test Circuit and Timing Diagram

Figure 11. Receiver Enable and Disable Test Circuits and Timing Diagrams

The XR33152/56/58 TIA-485/TIA-422 devices are part of Exar's high performance serial interface product line. The analog bus pins can survive direct shorts up to  $\pm 60V$  and are protected against ESD events up to  $\pm 15kV$ .

#### **Enhanced Failsafe**

Ordinary TIA-485 differential receivers will be in an indeterminate state whenever the data bus is not being actively driven. The enhanced failsafe feature of the XR33152/56/58 family guarantees a logic-high receiver output when the receiver inputs are open, shorted or when they are connected to a terminated transmission line with all drivers disabled. In a terminated bus with all transmitters disabled, the receivers' differential input voltage is pulled to 0V by the termination. The XR33152/56/58 family interprets 0V differential as a logic high with a minimum 50mV noise margin while maintaining compliance with the TIA-485 standard of ±200mV. Although the XR33152/56/58 family does not need failsafe biasing resistors, it can operate without issue if biasing is used.

### **Receiver Input Filtering**

The XR33152 receivers incorporate internal filtering in addition to input hysteresis. This filtering enhances noise immunity by ignoring signals that do not meet a minimum pulse width of 30ns. Receiver propagation delay increases slightly due to this filtering. The high speed XR33156 and XR33158 devices do not have this input filtering.

#### **Hot Swap Capability**

When  $V_{CC}$  is first applied the XR33152/56/58 family holds the driver enable and receiver enable inactive for approximately 10 $\mu$ s. During power ramp-up, other system ICs may drive unpredictable values or tristated lines may be influenced by stray capacitance. The hot swap feature prevents the XR33152/56/58 family from driving any output signal until power has stabilized. After the initial 10 $\mu$ s, the driver and receiver enable pins are weakly pulled to their disabled states (low for DE and high for RE) until the first transition. After the first transition, the DE and RE pins operate as high impedance inputs.

If circuit boards are inserted into an energized backplane (commonly called "live insertion" or "hot swap") power may suddenly be applied to all circuits. Without the hot swap capability, this situation could improperly enable the transceiver's driver or receiver, driving invalid data onto shared buses and possibly causing driver contention or device damage.

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention. First, a driver current limit on the output stage provides immediate protection against short circuits over the whole common-mode voltage range. Second, a thermal shutdown

circuit forces the driver outputs into a high impedance state if junction temperature becomes excessive.

#### **Line Length**

The TIA-485/TIA-422 standard covers line lengths up to 4000ft. Maximum achievable line length is a function of signal attenuation and noise. Termination prevents signal reflections by eliminating the impedance mismatches on a transmission line. Line termination is generally used if rise and fall times are shorter than the round trip signal propagation time. Higher output drivers may allow longer cables to be used.

#### ±15kV ESD Protection

ESD protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the XR33152/56/58 family has extra protection against static electricity. Exar uses state-of-the-art structures to protect these pins against ESD of  $\pm 15 \text{kV}$  without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown and powered down. After an ESD event, the XR33152/56/58 keep operating without latch up or damage.

ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the XR33152/56/58 are characterized for protection to the following limits:

- ±15kV using the Human Body Model, TIA-485 bus pins

- ±4kV using the Human Body Model, all other pins

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Exar for a reliability report that documents test setup, methodology and results.

#### **Maximum Number of Transceivers on the Bus**

The standard TIA-485 receiver input impedance is  $12k\Omega$  (1 unit load). A standard driver can drive up to 32 unit loads. The XR33152 transceiver has a 1/10th unit load receiver input impedance of  $120k\Omega$ , allowing up to 320 transceivers to be connected in parallel on a communication line. The XR33156/58 transceivers have a 1/2.5 unit load receiver input impedance of  $30k\Omega$ , allowing up to 80 transceivers to be connected in parallel on a communication line. Any combination of these devices and other TIA-485 transceivers up to a total of 32 unit loads may be connected to the line.

REV1A 15/19

#### **Low Power Shutdown Mode**

The XR33156 has a low-power shutdown mode that is initiated by bringing both  $\overline{\text{RE}}$  high and DE low simultaneously. While in shutdown the XR33156 draws less than 1µA of supply current. DE and  $\overline{\text{RE}}$  may be tied together and driven by a single control signal. Devices are guaranteed not to enter shutdown if  $\overline{\text{RE}}$  is high and DE is low for less than 50ns. If the inputs are in this state for at least 600ns, the parts will enter shutdown.

XR33156 enable times,  $t_{ZH}$  and  $t_{ZL}$ , apply when the part is not in low power shutdown state. Enable times,  $t_{ZH}(SHDN)$  and  $t_{ZL}(SHDN)$  apply when the part is shutdown. The driver and receiver take longer to become enabled from low power shutdown  $t_{ZH}(SHDN)$  and  $t_{ZL}(SHDN)$  than from driver or receiver disable mode ( $t_{ZH}$  and  $t_{ZL}$ ).

## **Product Selector Guide**

| Part Number | Operation   | Data Rate | Shutdown | Receiver/Driver<br>Enable | Nodes<br>On Bus | Footprint |

|-------------|-------------|-----------|----------|---------------------------|-----------------|-----------|

| XR33152     | Half duplex | 250kbps   | No       | No/Yes                    | 320             | 8-NSOIC   |

| XR33156     | Full duplex | 20Mbps    | Yes      | Yes/Yes                   | 80              | 14-NSOIC  |

| XR33158     | Half duplex | ZOIVIDPS  | No       | No/Yes                    | 80              | 8-NSOIC   |

# **Package Description**

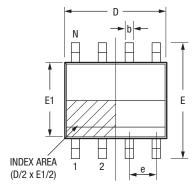

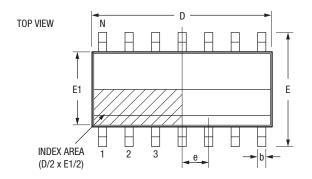

# 8-Pin NSOIC Package

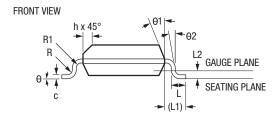

#### SIDE VIEW

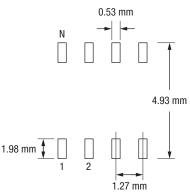

#### RECOMMENDED PCB LAND PATTERN

| FRONT VIEW                               | \ Q1   <b></b>                       |

|------------------------------------------|--------------------------------------|

| R1 R R C C C C C C C C C C C C C C C C C | 01 02 L2 GAUGE PLANE A SEATING PLANE |

|                                          | -1 (L1) 1-                           |

| 8-Pin NSOIC (JEDEC MS-012) |                                   |          |      |                                      |               |       |

|----------------------------|-----------------------------------|----------|------|--------------------------------------|---------------|-------|

| Symbols                    | Dimension in mm<br>(Control unit) |          |      | Dimension in inches (Reference unit) |               |       |

|                            | Min                               | Nom      | Max  | Min                                  | Nom           | Max   |

| Α                          | 1.35                              | -        | 1.75 | 0.053                                | -             | 0.069 |

| A1                         | 0.10                              | -        | 0.25 | 0.004                                | -             | 0.010 |

| A2                         | 1.25                              | -        | 1.65 | 0.049                                | -             | 0.065 |

| b                          | 0.31                              | -        | 0.51 | 0.012                                | -             | 0.020 |

| С                          | 0.17                              | -        | 0.25 | 0.007 - 0.010                        |               |       |

| Е                          | 6.00 BSC                          |          |      | 0.236 BSC                            |               |       |

| E1                         | 3.90 BSC 0.154 BSC                |          |      |                                      | ;             |       |

| е                          | 1.27 BSC                          |          |      | 0.050 BSC                            |               |       |

| h                          | 0.25                              | -        | 0.50 | 0.010                                | 0.010 - 0.020 |       |

| L                          | 0.40                              | -        | 1.27 | 0.016                                | -             | 0.050 |

| L1                         |                                   | 1.04 Ref |      | 0.041 Ref                            |               |       |

| L2                         | 0.25 BSC                          |          |      | 0.010 BSC                            |               |       |

| R                          | 0.07                              | -        | -    | 0.003                                | -             | -     |

| R1                         | 0.07                              | -        | -    | 0.003                                | -             | -     |

| θ                          | 0°                                | -        | 8°   | 0°                                   | -             | 8°    |

| θ1                         | 5°                                | -        | 15°  | 5°                                   | -             | 15°   |

| θ2                         | 0°                                | -        | -    | 0°                                   | -             | -     |

| D                          | 4.90 BSC                          |          |      | 0.193 BSC                            |               |       |

| N                          | 8 8                               |          |      |                                      |               |       |

# **Package Description**

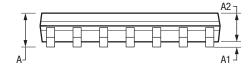

# 14-Pin NSOIC Package

SIDE VIEW

| 14-Pin NSOIC (JEDEC MS-012) |                                   |          |      |                                      |           |       |  |

|-----------------------------|-----------------------------------|----------|------|--------------------------------------|-----------|-------|--|

| Symbols                     | Dimension in mm<br>(Control unit) |          |      | Dimension in inches (Reference unit) |           |       |  |

|                             | Min                               | Nom      | Max  | Min                                  | Nom       | Max   |  |

| А                           | 1.35                              | -        | 1.75 | 0.053                                | -         | 0.069 |  |

| A1                          | 0.10                              | -        | 0.25 | 0.004                                | -         | 0.010 |  |

| A2                          | 1.25                              | -        | 1.65 | 0.049                                | -         | 0.065 |  |

| b                           | 0.31                              | -        | 0.51 | 0.012                                | -         | 0.020 |  |

| С                           | 0.17                              | -        | 0.25 | 0.007 - 0.010                        |           | 0.010 |  |

| Е                           | 6.00 BSC 0.236 BSC                |          |      | ;                                    |           |       |  |

| E1                          | 3.90 BSC                          |          |      |                                      | 0.154 BSC |       |  |

| е                           |                                   | 1.27 BSC |      | 0.050 BSC                            |           |       |  |

| h                           | 0.25                              | -        | 0.50 | 0.010                                | -         | 0.020 |  |

| L                           | 0.40                              | -        | 1.27 | 0.016                                | -         | 0.050 |  |

| L1                          |                                   | 1.04 Ref |      | 0.041 Ref                            |           |       |  |

| L2                          | 0.25 BSC                          |          |      | 0.010 BSC                            |           |       |  |

| R                           | 0.07                              | -        | -    | 0.003                                | -         | -     |  |

| R1                          | 0.07                              | -        | -    | 0.003                                |           | -     |  |

| θ                           | 0°                                | -        | 8°   | 0°                                   | -         | 8°    |  |

| θ1                          | 5°                                | -        | 15°  | 5°                                   | -         | 15°   |  |

| θ2                          | 0°                                | -        | -    | 0°                                   | -         | -     |  |

| D                           | 8.65 BSC                          |          |      | 0.341 BSC                            |           |       |  |

| N                           | 14                                |          |      |                                      | 14        |       |  |

## **Order Information**

| Part Number   | Operation   | Data Rate | Package     | Environmental<br>Rating | Operating<br>Temperature Range |

|---------------|-------------|-----------|-------------|-------------------------|--------------------------------|

| XR33152ID-F   | Half duplex | 250kbps   | 8-pin SOIC  | Green/RoHS              | -40°C to 85°C                  |

| XR33152IDTR-F | пан ииріех  |           | 6-piii 3010 |                         |                                |

| XR33156ID-F   | Full dupley | - 20Mbps  | 14-pin SOIC |                         |                                |

| XR33156IDTR-F | Full duplex |           |             |                         |                                |

| XR33158ID-F   | Half duplay |           | 8-pin SOIC  |                         |                                |

| XR33158IDTR-F | Half duplex |           |             |                         |                                |

48760 Kato Road Fremont, CA 94538 USA Tel.: +1 (510) 668-7000 Fax: +1 (510) 668-7001 Email: support@exar.com

Exar Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. Exar Corporation conveys no license under any patent or other right and makes no representation that the circuits are free of patent infringement. While the information in this publication has been carefully checked, no responsibility, however, is assumed for inaccuracies.

Exar Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Exar Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of Exar Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of Exar Corporation is prohibited. Exar, XR and the XR logo are registered trademarks of Exar Corporation. All other trademarks are the property of their respective owners.

©2015 Exar Corporation

# **ПОСТАВКА** ЭЛЕКТРОННЫХ КОМПОНЕНТОВ

Общество с ограниченной ответственностью «МосЧип» ИНН 7719860671 / КПП 771901001 Адрес: 105318, г.Москва, ул.Щербаковская д.3, офис 1107

# Данный компонент на территории Российской Федерации Вы можете приобрести в компании MosChip.

Для оперативного оформления запроса Вам необходимо перейти по данной ссылке:

## http://moschip.ru/get-element

Вы можете разместить у нас заказ для любого Вашего проекта, будь то серийное производство или разработка единичного прибора.

В нашем ассортименте представлены ведущие мировые производители активных и пассивных электронных компонентов.

Нашей специализацией является поставка электронной компонентной базы двойного назначения, продукции таких производителей как XILINX, Intel (ex.ALTERA), Vicor, Microchip, Texas Instruments, Analog Devices, Mini-Circuits, Amphenol, Glenair.

Сотрудничество с глобальными дистрибьюторами электронных компонентов, предоставляет возможность заказывать и получать с международных складов практически любой перечень компонентов в оптимальные для Вас сроки.

На всех этапах разработки и производства наши партнеры могут получить квалифицированную поддержку опытных инженеров.

Система менеджмента качества компании отвечает требованиям в соответствии с ГОСТ Р ИСО 9001, ГОСТ РВ 0015-002 и ЭС РД 009

## Офис по работе с юридическими лицами:

105318, г. Москва, ул. Щербаковская д. 3, офис 1107, 1118, ДЦ «Щербаковский»

Телефон: +7 495 668-12-70 (многоканальный)

Факс: +7 495 668-12-70 (доб.304)

E-mail: info@moschip.ru

Skype отдела продаж:

moschip.ru moschip.ru\_6 moschip.ru\_4 moschip.ru\_9