# **IQS266 Datasheet**

# 2x3 Channel projected capacitive trackpad controller with selfcapacitive wake-up

The IQS266 ProxSense<sup>®</sup> IC is a 2x3 projected capacitive trackpad designed for low power mobile applications. This trackpad is perfect to implement on a single sided ITO touch screen for wearables. A self-capacitive channel is used for wake-up which keeps the power consumption in low-power less than 5 uA. Other features include automatic tuning for sense electrodes, internal reference capacitor and internal regulator to reduce total system cost.

# **Features**

- Capacitive sensing

- Parasitic capacitive load cancellation

- Fully adjustable sensing options

- Self capacitive prox channel (CH0)

- 2x3 Projected capacitive trackpad (CH1-6)

- Zoom and Low power options for minimal power consumption

- **Multiple integrated UI** options based on years of experience in sensing on fixed and mobile platforms:

- Proximity / Touch

- **Proximity wake-up from low power** using distributed proximity channel

- RoHS compliant

QFN(3x3)-16 package Representation only

- Gesture recognition:

- Swipes: Up, down, left, right (segment indication for left & right swipes)

- Adjustable swipe length and time limitations

- Taps: Single taps with segment indication

- Adjustable tap size and time limitation

- Automatic Tuning Implementation (ATI)

- Minimal external components

- Fast **I**<sup>2</sup>**C** compatible interface

- **RDY indication** for event mode operation

- Event or Streaming mode

- Small package size: QFN(3x3)-16

- Supply voltage: 1.8V to 3.3V

### **Applications**

- Wearables

- Navigational controls

- White goods and appliances

- Office equipment, toys, sanitary ware

- Proximity detection that enables backlighting activation (Patented)

- Wake-up from standby applications

- Replacement for electromechanical switches and keypads

- GUI trigger and GUI control proximity detection

- Electronic Keypads or Pin pads

| Available Packages |             |  |  |  |  |

|--------------------|-------------|--|--|--|--|

| T <sub>A</sub>     | QFN(3x3)-16 |  |  |  |  |

| -20°C to 85°C      | IQS266      |  |  |  |  |

# **Table of Contents**

| LI | ST OF AI   | 3BREVIATIONS                                        | 4    |

|----|------------|-----------------------------------------------------|------|

| 1  | INTR       | ODUCTION                                            | 5    |

|    | 1.1        | FUNCTIONAL OVERVIEW                                 |      |

|    | 1.2        | PACKAGING AND PIN-OUT                               |      |

|    | 1.3        | REFERENCE DESIGN                                    | 7    |

| 2  | USEF       | CONFIGURABLE OPTIONS                                | 8    |

|    | 2.1        | ProxSetting0                                        | 8    |

|    | 2.2        | ProxSettings1                                       |      |

|    | 2.3        | PROXSETTINGS2                                       | 9    |

|    | 2.4        | PROXSETTINGS3                                       |      |

|    | 2.5        | EVENT MASK                                          | . 11 |

|    | 2.6        | ZOOM TIMEOUT                                        | . 11 |

|    | 2.7        | HALT TIMEOUT                                        | . 11 |

|    | 2.8        | RDY TIMEOUT                                         | . 11 |

|    | 2.9        | NORMAL MODE (NM) PERIOD                             | . 11 |

|    | 2.10       | LOW POWER (LP) PERIOD                               | . 11 |

|    | 2.11       | PROXIMITY THRESHOLD CH0                             | . 12 |

|    | 2.12       | TOUCH THRESHOLDS                                    | . 12 |

|    | 2.13       | ATI TARGET                                          | . 12 |

|    | 2.14       | BASE VALUES                                         | . 12 |

| 3  | CON        |                                                     | 16   |

|    | 3.1        | Control Byte                                        | 10   |

|    | 3.1<br>3.2 | I <sup>2</sup> C READ                               |      |

|    | 3.2<br>3.3 | I <sup>2</sup> C WRITE                              |      |

|    | 3.4        | END OF COMMUNICATION SESSION / WINDOW               |      |

|    | 3.5        | I <sup>2</sup> C Sub-address                        |      |

|    | 3.6        | RDY HAND-SHAKE ROUTINE                              |      |

|    | 3.7        | I <sup>2</sup> C SPECIFIC COMMANDS                  |      |

|    | 3.8        | I <sup>2</sup> C I/O CHARACTERISTICS                |      |

| 4  |            |                                                     |      |

| 4  | IVIEN      |                                                     |      |

|    | 4.2        | 0x00 Device INFO                                    | . 20 |

|    | 4.3        | 0x01 FLAGS                                          | . 21 |

|    | 4.4        | 0x02 – 0x03 Trackpad data                           | . 23 |

|    | 4.5        | 0x04 Prox & Touch data                              | . 24 |

|    | 4.6        | 0x05 – 0x0B AC filtered channel count data          |      |

|    | 4.7        | 0x0C – 0x12 LTA DATA                                | -    |

|    | 4.8        | 0x13 – 0x19 DELTAS                                  | -    |

|    | 4.9        | 0x80 – 0x81 Prox settings                           |      |

|    | 4.10       | 0x82 Event mask                                     |      |

|    | 4.11       | 0x82 offset 1 – 0x83 offset 1 Timeout periods       | . 30 |

|    | 4.12       | Ox84 Report rates                                   | -    |

|    | 4.13       | 0x85 – 0x88 Thresholds                              |      |

|    | 4.14       | 0x89 – 0x8A Channel settings                        |      |

|    | 4.15       | 0x8B TAP GESTURE SETTINGS                           |      |

|    | 4.16       | OX8C SWIPE GESTURE SETTINGS.                        |      |

|    | 4.17       | 0x8D – 0x93 Multipliers and compensation: CH0 – CH6 | . 38 |

| 5  | ELEC       | TRICAL CHARACTERISTICS                              | 40   |

|    | 5.1        | Absolute Maximum Specifications                     | . 40 |

|    | 5.2        | Power On-reset/Brown out                            | . 41 |

| _  |            |                                                     |      |

### IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

|    | 5.3    | DIGITAL INPUT/OUTPUT TRIGGER LEVELS  | 41  |

|----|--------|--------------------------------------|-----|

|    | 5.4    | CURRENT CONSUMPTION                  | 42  |

|    | 5.5    | DEVICE TIMING DESCRIPTIONS.          | 42  |

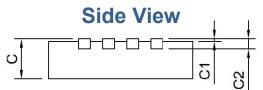

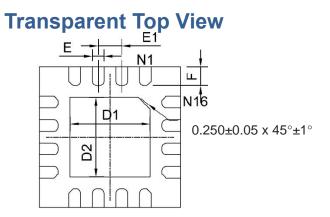

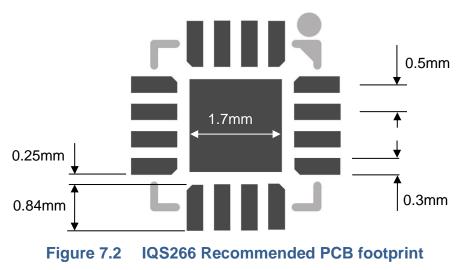

| 6  | PAC    | AGE INFORMATION                      | .43 |

|    | 6.1    | PACKAGE AND FOOTPRINT SPECIFICATIONS |     |

|    | 6.2    | RECOMMENDED PCB FOOTPRINT            | 43  |

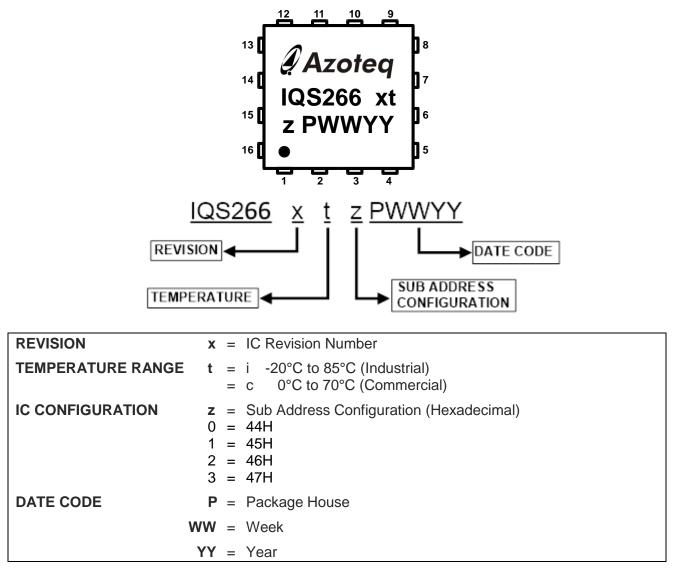

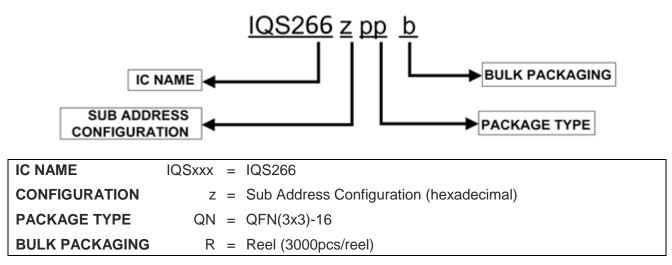

|    | 6.3    | DEVICE MARKING                       | 44  |

|    | 6.4    | ORDERING INFORMATION                 | 44  |

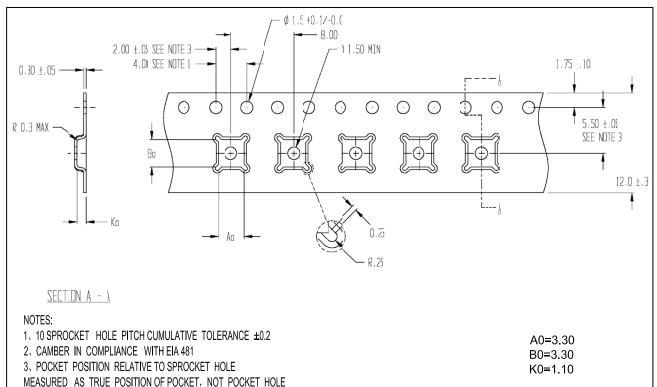

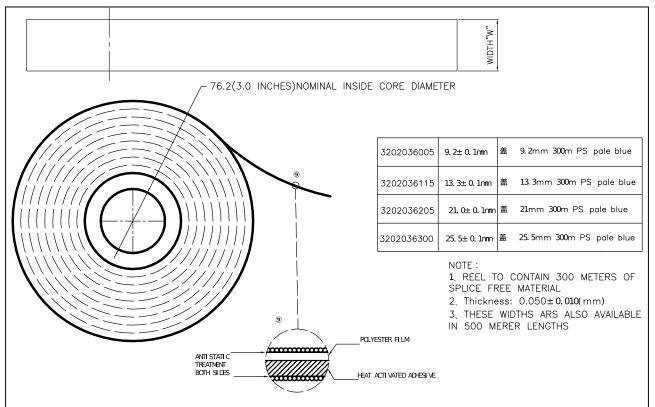

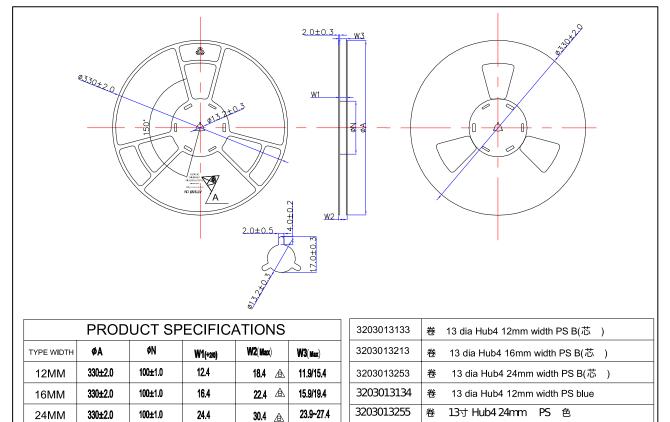

|    | 6.5    | TAPE AND REEL SPECIFICATION          | 45  |

|    | 6.6    | MSL LEVEL                            | 46  |

| 7  |        | ASHEET REVISIONS                     |     |

|    | 7.1    | REVISION HISTORY                     | 47  |

|    | 7.2    | ERRATA                               | 47  |

| AP | PENDIX | A. CONTACT INFORMATION               | .48 |

# List of abbreviations

- ATI Automatic Tuning Implementation

- AC Alternating Current

- ACF AC Filtered Counts

- CH Channel

- CS Sampling capacitor

- CX Self capacitive electrode

- I<sup>2</sup>C Inter-Integrated Circuit

- LTA Long Term Average

- N/C Not connect

- NM Normal Mode

- LP Low Power

- RX Receiving electrode

- RDY Ready interrupt signal

- SCL I<sup>2</sup>C serial clock signal

- SDA I<sup>2</sup>C serial data signal

- TX Transmitting electrode

# 1 Introduction

# **1.1 Functional overview**

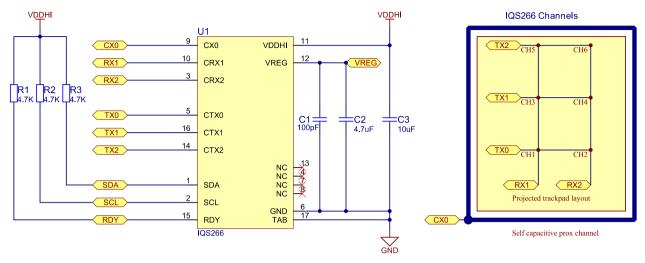

The **IQS266** is a single self capacitive proximity and 6 channel projected trackpad sensor featuring an internal voltage regulator and reference capacitor (C<sub>s</sub>).

The device has 6 pins for the connection of sense electrodes, which consist of 1 self electrode, for proximity wake-up, as well as 2 receivers and 3 transmitters, for a 2x3 trackpad. Three pins are used for serial data communication through the  $I^2C^{TM}$  compatible protocol, including an optional RDY pin.

The device automatically tracks slow varying environmental changes via various filters, detects swipe and tap gestures in various directions and segments on the trackpad. The device is equipped with an Automatic Tuning Implementation (ATI) to adjust the device for optimal sensitivity.

# **1.2 Packaging and Pin-Out**

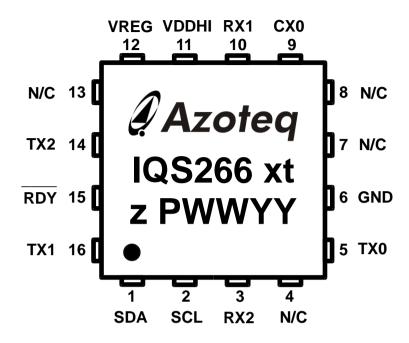

### Figure 1.1 IQS266 Pin layout (representation only device marking differs)

| Pin | Name  | Туре                                  | Function                     |

|-----|-------|---------------------------------------|------------------------------|

| 1   | SDA   | Digital                               | I <sup>2</sup> C Serial Data |

| 2   | SCL   | Digital I <sup>2</sup> C Serial Clock |                              |

| 3   | RX2   | Analogue                              | Receive Electrode            |

| 4   | N/C   | -                                     | Not Connected                |

| 5   | TX0   | Transmitter                           | Transmit Electrode           |

| 6   | GND   | Supply Input                          | GND Reference                |

| 7   | N/C   | -                                     | Not Connected                |

| 8   | N/C   | -                                     | Not Connected                |

| 9   | CX0   | Analogue                              | Receive Electrode            |

| 10  | RX1   | Analogue                              | Receive Electrode            |

| 11  | VDDHI | Supply Input                          | Supply Voltage Input         |

| 12  | VREG  | Analogue Output                       | Internal Regulator Pin       |

| 13  | N/C   | -                                     | Not connected                |

| 14  | TX2   | Transmitter                           | Transmit electrode           |

| 15  | RDY   | Digital Output                        | Serial Ready Interrupt       |

| 16  | TX1   | Transmitter                           | Transmit electrode           |

#### Table 1.1 IQS266 Pin-out

#### IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

# 1.3 Reference Design

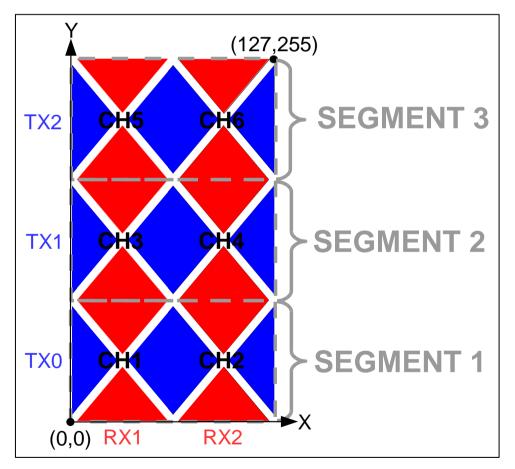

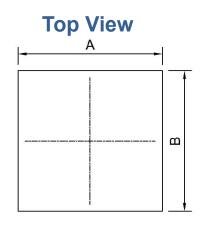

Figure 1.3 IQS266 Recommended trackpad layout (top view) with coordinate system and segment allocation

# 2 User configurable options

# 2.1 ProxSetting0

### 2.1.1 Disable ATI

The **IQS266** can automatically retune sensor electrodes when the counts drift outside a predefined <u>ATI band</u>. This allows the **IQS266** to keep optimal sensitivity during different environment. To disable the feature, the "ATI OFF" bit needs to be set in the <u>ProxSettings0</u> <u>register (0x80; byte 0)</u>. Disabling this feature only disables the automatic retuning; the MCU can at any time still force retuning with the <u>Redo-ATI</u> command.

### 2.1.2 Partial ATI

If it is required to have the ATI time reduced, the **IQS266** can use partial ATI by setting the "ATI Partial" bit in the <u>ProxSettings0 register</u> (0x80; byte 0). The designer must also specify the sensitivity multiplier (option 1 to 4) as the **IQS266** will only calculate the compensation multiplier and compensation. The Partial ATI option reduces start-up and re-tuning times, but does require the designer to verify that the base values achieved are within the desired range.

### 2.1.3 ATI Band

The user has the option to select the re-tuning band as ¼ of the ATI target (default is 1/8 of the ATI target) if it is desired to have a wider range for the counts to drift with environmental change before the device retune the electrodes. The wider band is achieved by setting the "ATI BAND" bit in the <u>ProxSettings0</u> register (0x80; byte 0).

### 2.1.4 Redo-ATI

The **IQS266** can be forced to ATI at any time, regardless of present events. To force retuning set the "Redo ATI" bit in the <u>ProxSettings0 register (0x80; byte 0)</u>. The "Redo ATI" bit will automatically clear after having been set.

### 2.1.5 Reseed

The **IQS266** LTA filters can be reseeded to the count values at any time to clear any output event. If count values are outside the ATI band, retuning will be triggered. To reseed set the "Reseed" bit in the <u>ProxSettings0 register</u>

(0x80; byte 0). The "Reseed" bit will automatically clear after having been set.

Setting the Reseed bit will shift all LTA filters to a value of  $LTA_{new} = CS + 8$  (CS – 8 for Self). The LTA will then track the CS value until they are even.

Performing a reseed action on the LTA filters, will effectively clear any proximity and/or touch conditions that may have been established prior to the reseed call.

### 2.1.6 Debug ATI

In order to facilitate faster start-up and retuning times, the communication windows are stopped during ATI on the **IQS266**. If the designer would like to be able to read data after every charge cycle during ATI, the communication can be enabled by setting the "Debug ATI" bit in the <u>ProxSettings0 register</u> (0x80; byte 0). A communication window can still be forced by the MCU with a RDY handshake (pulling the RDY line low) at any time even if the "Debug ATI" bit is not set.

### 2.1.7 Increase stability

The **IQS266's** analogue circuitry settling time can be increased (at the cost of higher current consumption) in order to have a more stable conversion in respect to the internal regulator. The longer settling time is enabled by setting the "Increase stability" bit in the <u>ProxSettings0</u> register (0x80; byte 0).

#### 2.1.8 Force Halt

The user has the option to halt the LTA to avoid any reseed or re-tuning events from taking place. This can be used in situations where the counts are expected to go in the wrong direction as a result of a controlled action in the application. To freeze the LTA filters set the "Force Halt" bit in the <u>ProxSettings0 register (0x80; byte 0)</u>.

# 2.2 ProxSettings1

### 2.2.1 Comms WDT off

The WDT (watchdog timer) is used to reset the IC if a problem (for example a voltage spike) occurs during communication. The WDT will time-out (and thus reset the device) after  $t_{WDT}$  if no valid communication occurred during this time.

The WDT can be disabled during development by setting the "WDT Off" bit in the <u>ProxSettings1 register (0x80; byte 1)</u>. It is not recommended to disable the WDT for production.

### 2.2.2 Event Mode

By default, the device operates in full streaming mode. There is an option for an event-driven I<sup>2</sup>C communication mode (also called "Event Mode"), with the RDY pin ONLY indicating a communication window after a prescribed event has occurred.

These events include:

- LP (low power) event

- Swipes (up / down / left / right)

- Tap

- ATI

- TP (trackpad) event

- Touch

- Proximity

The RDY pin will indicate events in the following manner:

- 1. **LP event:** Single RDY low on LP entry and again on exit

- 2. **Swipe Detected:** Single RDY low on swipes

- 3. Tap Detected: Single RDY low

- 4. **ATI:** RDY low on ATI start & again on ATI completing

- 5. **TP event:** RDY pin low after completion of every charge cycle while a touch remains detected on a channel.

- 6. **Touch:** RDY low on each touch entry and exit occurring.

- 7. Prox: RDY low on entry and exit

For trackpad events, the device will stream data continuously (after every charge cycle) when a touch is present on one of the channels, even if Event Mode is enabled.

Event Mode can be enabled by setting the "Event Mode" bit in the <u>ProxSettings1 register</u> (0x80; byte 1).

Note: The device is also capable of functioning **without** a RDY line on a polling basis. To

change settings during event mode the <u>RDY</u> <u>Hand-Shake Routine</u> should be followed.

### 2.2.3 LTA Beta

The speed at which the LTA will follow the counts when no event is present (no filter halt) can be changed by adjusting the beta values for the LTA filter. Four options are available by setting the "LTA Beta" bits in the ProxSettings1 register (0x80; byte 1).

### 2.2.4 AC Filter

The AC filter is implemented to provide better stability of Counts (CS) in electrically noisy environments.

The filter also enforces a longer minimum sample time for detecting proximity events on CH0, which will result in a slower response rate when the device enters low power modes. The filter can be disabled.

The count filter is implemented only on CH0, to aid in the trackpad coordinate calculations, but touch events are (by default) determined on unfiltered count values.

The count filter can be disabled, or the speed (amount of filtering) adjusted by setting the "ACF" bits in the <u>ProxSettings1 register (0x80; byte 1)</u>.

# 2.3 ProxSettings2

### 2.3.1 Wake both directions

The **IQS266** can wake from low power in both directions of count movement (of the proximity threshold). This could be used to sense release events from low power mode. To enable sensing in both directions, set the "Wake both dir" bit in the <u>ProxSettings2</u> register (0x81; byte 0).

### 2.3.2 Clear TP flags

If the **IQS266** outputs a TP event by setting a TP flag, the flag will remain set until the TP flags register is read. To clear the TP flags with each valid comms window, set the "Clear TP flags" bit in the <u>ProxSettings2 register (0x81; byte 0)</u>.

### 2.3.3 NP segment rate

The **IQS266** does a NP (normal power) conversion during low power where all active channels are charged even though the IC are

only monitoring CH0 for a wake-up event. To change the rate of the NP segments, configure the lower three bits called "NP segment rate" in the <u>ProxSettings2 register (0x81; byte 0)</u>. The rate is calculated as a desired multiple of the "Low power period"

### 2.4 ProxSettings3

#### 2.4.1 ACK Reset

After start-up, and after every reset event, the "Show Reset" flag will be set in the <u>System</u> <u>Flags register (0x01; byte 0)</u>.

The "Show Reset" bit can be read to determine whether a reset has occurred on the device (it is recommended to be continuously monitored). This bit will be set '1' after a reset.

The SHOW\_RESET bit will be cleared (set to '0') by writing a '1' into the "ACK Reset" bit in <u>Prox settings 3 register (0x81; byte 1)</u>. A reset will typically take place if a timeout during communication occurs.

### 2.4.2 Off mode

The **IQS266** has the option to switch the device off during inactive states of operation. The device will only wake up again on activity on the SDA line (all device register memory will be lost). A reset will occur when the device wakes up and the IC needs to be setup again. This is suitable for applications that require no device operation during defined operation states. To switch to off mode set the "Off mode" bit in the <u>ProxSettings3 register (0x81; byte 1)</u>.

### 2.4.3 Projected Bias

The **IQS266** has the option to change the bias current of the Rx channels during projected sensing mode. A larger bias current is required when using larger electrodes, but will also increase the IC power consumption. The bias current is default on  $5\mu$ A, and can be changed to  $10\mu$ A. To select 10  $\mu$ A set the "Proj Bias" bit in the <u>ProxSettings3 register (0x81; byte 1)</u>.

### 2.4.4 Float CX

During the charge transfer process, the channels (CX0 electrode for CH0 Self or Rx electrodes for projected trackpad channels) that are not being processed during the

current conversion are effectively grounded to decrease the effects of noise-coupling between the sense electrodes. Grounding these traces is useful in applications with long tracks between IC and sense electrode.

There is the option to float the CX (or Rx) lines in between charging. This is particularly useful for applications with a self-capacitive CH0 button with a thick overlay, where more sensitivity is required, or in application that need to avoid false triggers from water on the overlays. To float channels set the "Float Cx" bit in the <u>ProxSettings3 register (0x81; byte 1)</u>.

#### 2.4.5 Halt charge mode

The charging sequence of the IQS266 can be halted on command. This function is useful for applications where the IQS266 can be completely halted without resetting the registers. The device will enter a low-power mode without doing conversions on the channels. To enable "Halt charge" set bit in the ProxSettings3 register (0x81; byte 1). To disable "Halt charge" toggle the RDY line. LP period register (0x84; byte 1) should be greater than 0 when "Halt charge" is activated. The LP period should be chosen based on the required low-power current consumption and the required time to wake up from halt-charge mode.

### 2.4.6 CH0 distributed

The **IQS266** device by default performs a self capacitive conversion for channel 0 on the CX0 pin. An option bit is provided to change channel 0 to a distributed self capacitive prox channel charging on pins CX0, RX1 & RX2 simultaneously. To enable this function for channel 0 set the "CH0 distributed" bit in the **ProxSettings3 register** (0x81; byte 1).

#### 2.4.7 Charge transfer frequency slow CH1 – 6

The **IQS266** can reduce the charge transfer frequency for applications that require extra sensitivity (for example very thick overlays). The charge transfer frequency can be halved. The default charge transfer frequency for projected operation is 2MHz and can be slowed down to 1MHz by setting the "Xfer slow CH1 – 6" bit in the <u>ProxSettings3 register (0x81; byte 1)</u>.

# 2.4.8 Charge transfer frequency slow CH0

The **IQS266** can reduce the charge transfer frequency for applications that require extra sensitivity (for example very thick overlays). The charge transfer frequency can be halved. The default charge transfer frequency for self capacitive operation is 1MHz and can be slowed down to 500kHz. If the channel 0 distributed setting is used the charge transfer frequency for the projected operation is 2MHz and can be slowed down to 1MHz by setting the "Xfer slow CH0" bit in the <u>ProxSettings3</u> register (0x81; byte 1).

### 2.5 Event mask

The **IQS266** can be configured to report only desired events by masking out unwanted events from the <u>Events register (0x01; byte 1)</u>. This is only applied during event mode and is particularly useful where communication is only required on certain desired events while still having the **IQS266** waking from low power and sensing as required without interrupting the master/MCU. Clearing the corresponding bits in the <u>Event mask register (0x82; byte 0)</u> will disable or mask an event from reporting during event mode.

# 2.6 Zoom timeout

A normal power mode is defined for the **IQS266** during which normal power conversions is performed. The zoom timeout defines the time to remain in the normal power mode before switching to low power mode. The zoom timeout can be set in periods of 500ms. Any event triggered (proximity or touch) before timeout occurs will clear the timer and start timing again from the last reported event. Configure <u>Zoom timeout</u> register (0x82; byte 1).

# 2.7 Halt timeout

The LTA filter for all channels will halt on proximity or touch events. A halt timeout is implemented for the **IQS266** to terminate a halted filter condition to ensure that no stuck conditions remain indefinitely active. A halt timeout occurs during a stationary touch or prox condition on one or more channels without any change in events/flags for the configured timeout period. After timeout is reached a redo ATI command is self-induced by the **IQS266** in order to recalibrate all channels and clear any stuck activations. The halt timeout can be set in decimal increments of 500ms. Any additional event triggered or active event cleared before timeout occurs will clear the timer and start timing again. Configure <u>Halt timeout register (0x83; byte 0)</u>.

# 2.8 RDY timeout

If no communication is initiated from the master/host MCU within the first t<sub>COMMS</sub> = 2.56ms default) of the RDY line indicating that data is available (i.e. RDY = low), the device will resume with the next cycle of charge transfers and the data from the previous conversions will be lost. The timeout time is adjustable in steps of 0.64ms in the <u>RDY</u> timeout register (0x83; byte 1). There is also a WDT (t<sub>I2C</sub>) that cannot be disabled, for when communication has started but not been completed, for example when the bus is being held by another device. t<sub>I2C</sub> = 62ms.

# 2.9 Normal mode (NM) period

The **IQS266** normal mode period specifies the sampling time for normal mode conversions (fastest possible conversion period for all channels active). The default normal mode period is 10ms and can be configured in increments of 1ms using the <u>NM period register (0x84; byte 0)</u>.

# 2.10 Low power (LP) period

The LP period of the **IQS266** specifies the sampling time for channel 0 during low power mode and halt charge mode. By default, the low power mode period is equal to zero which means that the **IQS266** will not enter low power. For any other configured period in increments of 16ms, low power will be entered

upon zoom timeout and use that sampling period. Use the <u>LP period register (0x84; byte</u> <u>1)</u> to configure the low power sampling period of channel 0. The VREG voltage should not drop with more than 50 mV. A bigger capacitor on VREG can be used for longer LP periods.

# 2.11 Proximity threshold CH0

A proximity threshold for channel 0 can be selected for the application, to obtain the desired proximity trigger level. The proximity threshold is selectable between 1 (most sensitive) and 255 (least sensitive) counts. These threshold values (i.e. 1-255) are specified in Counts (CS) in the <u>Proximity</u> <u>threshold CH0 register (0x85; byte 0)</u>. The default proximity threshold is 6 counts. For a proximity threshold, higher than CH0 touch threshold a proximity event will be forced during a touch.

# 2.12 Touch Thresholds

A touch threshold for each channel can be selected by the designer to obtain the desired touch sensitivity and is selectable between 1/256 (most sensitive) to 255/256 (least sensitive). The touch threshold is calculated as a fraction of the Long-Term Average (LTA) given by,

$$T_{THR} = \frac{x}{256} \times LTA$$

With lower target values (therefore lower LTA's) the touch threshold will be lower and vice versa.

Individual touch thresholds can be set for each channel (including channel 0), by writing to the touch threshold registers. Registers start from 0x85; byte 0 and continues to 0x88; byte 1 for channels 0 to 6. The default touch threshold is 40/256 times the LTA.

# 2.13 ATI target

The **IQS266** ATI targets for channel 0 and all the other channels (1-6) can be adjusted independently. The ATI target should be selected during product design and development and corresponding prox and touch thresholds should be selected and evaluated according to the desired target value. The ATI target can be adjusted in multiple increments of 8 counts (0-255 \* 8counts) using either <u>ATI target CH1-6</u> <u>register (0x89; byte 0)</u> or <u>ATI target CH0</u> (0x89; byte 1).

# 2.14 Base values

The **IQS266** has the option to change the base value of the proximity channel (CH0) and the trackpad channels (CH1 to CH6) during the Full ATI algorithm. This provides the user with another option to select the sensitivity of the **IQS266** without changes in the hardware (RX/TX sizes and routing, etc.).

The base values are set by writing to the <u>Base</u> value register (0x8A; byte 0). There are 16 different options to choose from. To choose a custom base value, select <u>partial ATI</u>.

The base value influences the overall sensitivity of the channel and establishes a base count which is used during the ATI algorithm. A lower base value will typically result in a higher sensitivity of the respective channel, as lower multipliers will be selected, and more compensation would be required.

# 3 **ProxSense<sup>®</sup> Module**

The **IQS266** contains a ProxSense<sup>®</sup> module that uses patented technology to provide detection of proximity and touch conditions on numerous sensing lines.

The ProxSense<sup>®</sup> module is a combination of hardware and software, based on the principles of charge transfer measurements.

# 3.1 Charge Transfer Concept

On ProxSense<sup>®</sup> devices like the **IQS266**, capacitance measurements are taken with a charge transfer process that is periodically initiated.

For projected capacitive sensing, the device measures the capacitance between 2 electrodes referred to as the transmitter (TX) and receiver (RX).

The measuring process is referred to as a charge transfer cycle and consists of the following:

- Discharging of an internal sampling capacitor (C<sub>s</sub>) and the electrode capacitors (mutual: TX & RX) on a channel.

- charging of TX's connected to the channel

- and then a series of charge transfers from the RX's to the internal sampling capacitors (C<sub>s</sub>), until the trip voltage is reached.

The number of charge transfers required to reach the trip voltage on a channel is referred to as the Current Samples (**CS**) or Count value (Counts).

Please note: Attaching scope probes to the CTX/CRX pins will influence the capacitance of the sense electrodes and therefore the related CS values of those channels. This will have an instant effect on the CS measurements.

# 3.2 Rate of Charge Cycles

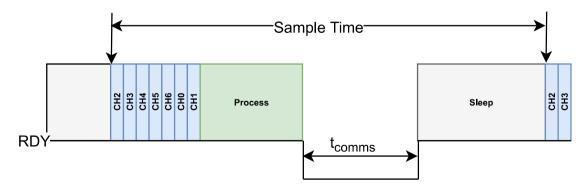

The **IQS266** samples all its active channels (up to 6 projected channels and 1 capacitive channel). The charge sequence (as measured on the receive electrodes) is shown in Figure 3.1. After the channels are charged the IQS266 process the channel data and go to sleep until the sampling period ends. If the sampling period ends a communication window will be available and is shown by RDy active low.

Typical timings of the charge sequence will differ with each application, depending on the setup of the **IQS266**. For example, the sense (or charge time) is affected by the target counts and charge transfer frequency, while process time is dependent on ATI checking for counts within the allowed band and filter settings. Communication time is affected by the amount of data read (as well as the sequence thereof) and I2C communication frequency.

#### Figure 3.1 IQS266 Charge Sequence timing diagram.

# 3.3 LTA vs Reference Values

The Long-term Average (LTA) and reference values can be seen as the baseline. The baseline values are calculated to continuously adapt to any environmental drift. These values are calculated from the CS value for each channel.

For **CH0** a Long Term Average (**LTA**) is calculated (16 bit unsigned integer values). The count (CS) values (16 bit unsigned integer values) are processed and compared to the LTA to detect Touch and Proximity events on **CH0**.

For **Ch1-Ch6** a reference value of each channel's counts is taken during the normal power update in Low Power. This reference value is compared to the counts during normal power to calculate the trackpad coordinates and detect proximity and touch events for each channel.

# **3.4 Determine Touch or Prox**

An event is determined by comparing the CS value with the LTA (Ch0) or Reference (Ch1-6) Since the CS reacts differently when comparing the self- with the mutual capacitance technology, the user should consider only the conditions for the technology used.

An event is recorded if:

- Self (Ch0): CS < LTA **Threshold**

- Projected(Ch1-6): CS > REF + **Threshold**

**Threshold** can be either a Proximity or Touch threshold, depending on the current channel being processed.

Note that a proximity condition will be forced enabled if there is a touch condition on any channel.

Please refer to **Section 2.11** and **2.12** for proximity and touch threshold selections.

# 3.5 ATI

The Automatic Tuning Implementation (ATI) is a sophisticated technology implemented on the new ProxSense<sup>®</sup> series devices. It allows for optimal performance of the devices for a wide range of sense electrode capacitances, without modification or addition of external components.

The ATI allows the tuning of two parameters, an ATI Multiplier and an ATI Compensation, to adjust the Count values for an attached sense electrode.

ATI allows the designer to optimize a specific design by adjusting the sensitivity and stability of each channel through the adjustment of the ATI parameters.

The **IQS266** has a full ATI function. The full-ATI function is default enabled, but can be disabled by setting the AUTO\_ATI\_OFF bit, or changed to partial by setting the ATI\_PARTIAL bit in PROX\_SETTINGS\_0.

The ATI\_BUSY bit will be set while an ATI event is busy.

For more information regarding the ATI algorithm, please contact Azoteq at: <u>ProxSenseSupport@azoteq.com</u>

### 3.5.1 ATI Sensitivity

On the **IQS266 device**, the user can specify the BASE value and the TARGET value for Channel 0 and for Channel 1-6.

A rough estimation of sensitivity can be calculated as:

$$Sensitivity \propto \frac{TARGET}{BASE}$$

As can be seen from this equation, the sensitivity can be increased by either increasing the Target value or decreasing the Base value. It should, however, be noted that a higher sensitivity will yield a higher noise susceptibility.

### 3.5.2 ATI Target

The target value is reached by adjusting the COMPENSATION bits for each channel (ATI target limited to 2048 counts).

The target value is written into the respective channel's TARGET registers. The value written into these registers multiplied by 8 will yield the new target value.

### 3.5.3 ATI Base (Multiplier)

The following parameters will influence the base value:

- PROJ\_BIAS bits: Adjusts the biasing of some analogue parameters in the mutual capacitive operated IC. (Only applicable in mutual capacitance mode.)

- Charge Transfer Frequency

- MULTIPLIER bits.

The base value used for the ATI function can be implemented in 2 ways:

- ATI\_PARTIAL = 0. ATI automatically adjusts MULTIPLIER bits to reach a selected base value<sup>1</sup>.

- ATI\_PARTIAL = 1. The designer can specify the multiplier settings. These settings will give a custom base value from where the compensation bits will be automatically implemented to reach the required target value. The base value is determined by two sets of multiplier bits. Sensitivity Multipliers which will also scale the compensation to normalise the sensitivity and Compensation Multipliers to adjust the gain.

#### 3.5.4 Re-ATI

An automatic re-ATI event will occur if the counts are outside its re-ATI limits. The re-ATI limit or ATI boundary is calculated as the target value divided by 8. For example:

- Target = 512, Re-ATI will occur if CS is outside 512±64.

A re-ATI event can also be issued by the host MCU by setting the REDO\_ATI bit. The REDO\_ATI bit will clear automatically after the ATI event was started. Note: Re-ATI will automatically clear all proximity, touch and halt status bits.

### 3.5.5 ATI ERROR

The ATI error bit (read only) indicates to the user that the ATI targets where not reached. Adjustments of the base values or ATI BANDs are required.

<sup>&</sup>lt;sup>1</sup> ATI function will use PROJ\_BIAS (if applicable) and will only adjust the MULTIPLIER bits to reach the base values.

# 4 Communication

The **IQS266** device interfaces to a master controller via a 3-wire (SDA, SCL and RDY) serial interface bus that is  $I^2C^{TM}$  compatible, with a maximum communication speed of 400kbit/s.

# 4.1 Control Byte

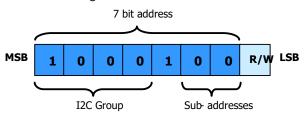

The Control byte indicates the 7-bit device address (44H default) and the Read/Write indicator bit. The structure of the control byte is shown in Figure 4.1.

Figure 4.1 IQS266 Control Byte.

The I<sup>2</sup>C device has a 7-bit Slave Address (default 0x44H) in the control byte as shown in Figure 4.1. To confirm the address, the software compares the received address with the device address. Sub-address values can be set by OTP programming options.

# 4.2 I<sup>2</sup>C Read

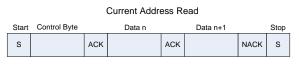

To read from the device a *current address read* can be performed. This assumes that the address-command is already setup as desired.

#### Figure 4.2 Current Address Read.

If the address-command must first be specified, then a *random read* must be performed. In this case a WRITE is initially performed to setup the address-command, and then a repeated start is used to initiate the READ section.

# I<sup>2</sup>C Write

To write settings to the device a *Data Write* is performed. Here the Address-Command is always required, followed by the relevant data bytes to write to the device.

| DATA WRITE |              |     |                     |     |        |     |          |     |      |

|------------|--------------|-----|---------------------|-----|--------|-----|----------|-----|------|

| Start      | Control Byte |     | Address-<br>Command |     | Data n |     | Data n+1 |     | Stop |

| s          | Adr + WRITE  | АСК |                     | ACK |        | ACK |          | ACK | s    |

### Figure 4.3 I<sup>2</sup>C Write

# 4.3 End of Communication Session / Window

Similar to other Azoteq I<sup>2</sup>C devices, to end the I<sup>2</sup>C communication session, a STOP command must be issued. When sending numerous read and write commands in one communication cycle, a repeated start command must be used to stack them together (since a STOP will jump out of the communication window, which is not desired).

The STOP will then end the communication, and the **IQS266** will return to process a new set of data. After the conversion, the communication window will again become available (RDY set LOW; after each conversion during streaming mode operation; only after an event detection during event mode operation).

### 4.4 I<sup>2</sup>C Sub-address

The **IQS266** has four available sub addresses, 44H (default) to 47H, which allows up to four devices on a single I<sup>2</sup>C bus.

#### 4.4.1 Internal sub-address selection

Selecting the sub-address via OTP bits allows the user 4 different options:

#### Table 4.1 I<sup>2</sup>C sub-address selection

| FG25 | FG26 | Device Address |

|------|------|----------------|

| 0    | 0    | 0x44           |

| 0    | 1    | 0x45           |

| 1    | 0    | 0x46           |

| 1    | 1    | 0x47           |

# 4.5 RDY Hand-Shake Routine

The master or host MCU has the capability to request a communication window at any time, by pulling the RDY line low. The communication window will open directly following the current conversion cycle. For more details please refer to the communication interface guide.

# 4.6 I<sup>2</sup>C Specific Commands

### 4.6.1 Show Reset

After start-up, and after every reset event, the "Show Reset" flag will be set in the <u>System Flags register (0x01H; byte 0)</u>.

The "Show Reset" bit can be read to determine whether a reset has occurred on the device (it is recommended to be continuously monitored). This bit will be set '1' after a reset.

The SHOW\_RESET bit will be cleared (set to '0') by writing a '0' into the "Show Reset" bit. A reset will typically take place if a timeout during communication occurs.

### 4.6.2 I2C Timeout

If no communication is initiated from the master/host MCU within the first  $t_{COMMS}$  ( $t_{COMMS}$  = 2.56 ms default) of the RDY line indicating that data is available (i.e. RDY =

low), the device will resume with the next cycle of charge transfers and the data from the previous conversions will be lost. The timeout time is adjustable in steps of 0.64ms in the <u>RDY timeout register (0x83;</u> byte 1). There is also a timeout ( $t_{12C}$ ) that cannot be disabled, for when communication has started but not been completed, for example when the bus is being held by another device.  $t_{12C} = 62ms$ .

# 4.7 I<sup>2</sup>C I/O Characteristics

The **IQS266** requires the input voltages given in Table 4.2, for detecting high ("1") and low ("0") input conditions on the  $I^2C$  communication lines (SDA, SCL and RDY).

### Table 4.2 IQS266 I<sup>2</sup>C Input voltage

|                    | Input Voltage (V) |

|--------------------|-------------------|

| Vin <sub>LOW</sub> | 0.3*VDDHI         |

| Vinнigн            | 0.7*VDDHI         |

Table 4.3 provides the output voltage levels of the IQS266 device during  $I^2C$  communication.

### Table 4.3 IQS266 I<sup>2</sup>C Output voltage

|          | Output Voltage (V) |

|----------|--------------------|

| Vout∟ow  | GND +0.2 (max.)    |

| Vouthigh | VDDHI – 0.2 (min.) |

# 5 Memory map

### Table 5.1 IQS266 Memory map index

| Full<br>Address              | Byte<br>offset | Group Name          | Item Name           | Data<br>Access |

|------------------------------|----------------|---------------------|---------------------|----------------|

| 0×00                         | 0              | Dovino info         | PRODUCT_NUM         | Read-Only      |

| 0x00                         | 1              | Device info         | VERSION_NUM         | Read-Only      |

| 001                          | 0              | Flore               | SYSFLAGS0           | Read-Only      |

| 0x01                         | 1              | <u>Flags</u>        | <u>EVENTS</u>       | Read-Only      |

| 000                          | 0              |                     | TP_FLAGS            | Read-Only      |

| 0x02                         | 1              | The slope of slote  | Reserved            | Read-Only      |

| 000                          | 0              | Trackpad data       | X_CURR              | Read-Only      |

| 0x03                         | 1              |                     | Y_CURR              | Read-Only      |

| 0.04                         | 0              |                     | PROX_CHANNEL0       | Read-Only      |

| 0x04                         | 1              | Prox & Touch data   | TOUCH_CHANNELS      | Read-Only      |

| 0.05                         | 0              |                     | ACF_CH0_LOW         | Read-Only      |

| 0x05                         | 1              |                     | ACF_CH0_HIGH        | Read-Only      |

|                              | 0              |                     | CH1_LOW             | Read-Only      |

| 0x06                         | 1              |                     | CH1_HIGH            | Read-Only      |

|                              | 0              |                     | CH2 LOW             | Read-Only      |

| 0x07                         | 1              |                     | CH2_HIGH            | Read-Only      |

| 0x08                         | 0              |                     | CH3 LOW             | Read-Only      |

|                              | 1              | Channel Counts data | CH3_HIGH            | Read-Only      |

| 0x09                         | 0              |                     | <u>CH4_LOW</u>      | Read-Only      |

| 0x09                         | 1              |                     | CH4_HIGH            | Read-Only      |

|                              | 0              |                     | CH5 LOW             | Read-Only      |

| 0x0A                         | 1              |                     | CH5_HIGH            | Read-Only      |

|                              | 0              |                     | CH6_LOW             | Read-Only      |

| 0x0B                         | 1              |                     | CH6_HIGH            | Read-Only      |

|                              | 0              |                     | LTA_CH0_LOW         | Read-Only      |

| 0x0C                         | 1              |                     | LTA_CH0_ LOW        |                |

|                              |                |                     |                     | Read-Only      |

| 0x0D                         | 0              |                     | REF_CH1_LOW         | Read-Only      |

|                              | -              |                     | REF_CH1_HIGH        | Read-Only      |

| 0x0E                         | 0              |                     | REF_CH2_LOW         | Read-Only      |

|                              | 1              |                     | REF_CH2_HIGH        | Read-Only      |

| 0x0F                         | 0              | LTA and REF data    | REF_CH3_LOW         | Read-Only      |

|                              | 1              |                     | REF_CH3_HIGH        | Read-Only      |

| 0x10                         | 0              |                     | REF_CH4_LOW         | Read-Only      |

|                              | 1              |                     | REF_CH4_HIGH        | Read-Only      |

| 0x11                         | 0              |                     | REF_CH5_LOW         | Read-Only      |

|                              | 1              |                     | <u>REF_CH5_HIGH</u> | Read-Only      |

| 0x12                         | 0              |                     | REF CH6 LOW         | Read-Only      |

| •                            | 1              |                     | REF_CH6_ HIGH       | Read-Only      |

| 0x13                         | 0              |                     | DELTA_CH0_LOW       | Read-Only      |

|                              | 1              |                     | DELTA CHO HIGH      | Read-Only      |

| 0x13<br>0x14<br>0x15<br>0x16 | 0              |                     | DELTA CH1 LOW       | Read-Only      |

|                              | 1              |                     | DELTA_CH1_HIGH      | Read-Only      |

|                              | 0              |                     | DELTA CH2 LOW       | Read-Only      |

|                              | 1              | <u>Deltas</u>       | DELTA CH2 HIGH      | Read-Only      |

|                              | 0              |                     | DELTA_CH3_LOW       | Read-Only      |

|                              | 1              |                     | DELTA_CH3_HIGH      | Read-Only      |

| 0-17                         | 0              |                     | DELTA CH4 LOW       | Read-Only      |

| 0x17                         | 1              |                     | DELTA_CH4_HIGH      | Read-Only      |

| 0x18                         | 0              |                     | DELTA_CH5_LOW       | Read-Only      |

#### IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

|              |                 |                          |                      | _          |

|--------------|-----------------|--------------------------|----------------------|------------|

|              | 1               |                          | DELTA CH5 HIGH       | Read-Only  |

| 0.40         | 0               |                          | DELTA_CH6_LOW        | Read-Only  |

| 0x19         | 1               |                          | DELTA_CH6_HIGH       | Read-Only  |

| 0,200        | 0               |                          | PROX_SETTINGS0       | Read-Write |

| 0x80         | 1               | Drov oottingo            | PROX_SETTINGS1       | Read-Write |

| 0x81<br>0x82 | 0               | Prox settings            | PROX_SETTINGS2       | Read-Write |

| UXOI         | 1               |                          | PROX_SETTINGS3       | Read-Write |

| 0.463        | 0               | Event mask               | EVENT_MASK           | Read-Write |

| 0202         | 1               |                          | ZOOM_TIMEOUT         | Read-Write |

| 0x83         | 0               | Timeout periods          | HALT_TIMEOUT         | Read-Write |

| 0.00         | 1               |                          | <u>RDY_TIMEOUT</u>   | Read-Write |

| 0x84         | 0               | Report rates             | <u>NM_PERIOD</u>     | Read-Write |

| 0704         | 1               | <u>Report lates</u>      | LP_PERIOD            | Read-Write |

| 0x85         | 0               |                          | PROX_THR_CH0         | Read-Write |

| 0.03         | 1               |                          | TOUCH_THR_CH0        | Read-Write |

| 0x86         | 0               | Thresholds               | TOUCH_THR_CH1        | Read-Write |

| 0,00         | 1<br>Thresholds | TOUCH_THR_CH2            | Read-Write           |            |

| 0x87         |                 | Thresholds               | TOUCH_THR_CH3        | Read-Write |

| 0,01         | 1               |                          | TOUCH_THR_CH4        | Read-Write |

| 0x88         | 0               |                          | TOUCH_THR_CH5        | Read-Write |

| 0,00         | 1               | 1                        | TOUCH_THR_CH6        | Read-Write |

| 0x89         | 0               |                          | ATI_TARGET_CH1-6     | Read-Write |

|              | 1               | Channel settings         | ATI_TARGET_CH0       | Read-Write |

| 0x8A         | 0               | <u></u>                  | BASE_VALUE_CH1-6_CH0 | Read-Write |

|              | 1               |                          | ACTIVE_CHANNELS      | Read-Write |

| 0x8B         | 0               | Tap gesture settings     | TAP TIMER LIMIT      | Read-Write |

|              | 1               | <u> </u>                 | TAP_THRESHOLD        | Read-Write |

| 0x8C         | 0               | Swipe gesture settings   | SWIPE_TIMER_LIMIT    | Read-Write |

|              | 1               |                          | SWIPE THRESHOLD      | Read-Write |

| 0x8D         | 0               |                          | SENS & COMP 0        | Read-Write |

|              | 1               |                          | COMPENSATION 0       | Read-Write |

| 0x8E         | 0               |                          | SENS & COMP 1        | Read-Write |

|              | 1               |                          | COMPENSATION 1       | Read-Write |

| 0x8F         | 0               |                          | SENS & COMP 2        | Read-Write |

|              | 1               | N Assister Discovers and | COMPENSATION 2       | Read-Write |

| 0x90         | 0               | Multipliers and          | SENS & COMP 3        | Read-Write |

|              |                 | <u>compensation</u>      | COMPENSATION 3       | Read-Write |

| 0x91         | 0               |                          | SENS & COMP 4        | Read-Write |

| 0x91         | 1               |                          | COMPENSATION 4       | Read-Write |

| 0x92         | 0               |                          | SENS & COMP 5        | Read-Write |

|              | 1               |                          | COMPENSATION 5       | Read-Write |

| 0x93         | 0               |                          | SENS & COMP 6        | Read-Write |

|              |                 |                          | COMPENSATION 6       | Read-Write |

# 5.2 0x00 Device info

#### 5.2.1 Product number

|                | PRODUCT_NUM (0x00, offset 0) |                |   |        |        |   |   |   |  |

|----------------|------------------------------|----------------|---|--------|--------|---|---|---|--|

| Bit<br>Number  | 7                            | 6              | 5 | 4      | 3      | 2 | 1 | 0 |  |

| Data<br>Access | R                            | R              | R | R      | R      | R | R | R |  |

| Name           |                              | Product number |   |        |        |   |   |   |  |

| Default        | 0                            | 1              | 0 | 0      | 1      | 0 | 1 | 0 |  |

| Delault        |                              |                |   | 0x4A : | = D'74 |   |   |   |  |

Bit definitions:

• Bit 7-0: Device product number

#### 5.2.2 Version number

|                | VERSION_NUM (0x00, offset 1) |                |   |      |       |   |   |   |  |

|----------------|------------------------------|----------------|---|------|-------|---|---|---|--|

| Bit<br>Number  | 7                            | 6              | 5 | 4    | 3     | 2 | 1 | 0 |  |

| Data<br>Access | R                            | R              | R | R    | R     | R | R | R |  |

| Name           |                              | Version Number |   |      |       |   |   |   |  |

| Default        | 0                            | 0              | 0 | 0    | 0     | 0 | 1 | 0 |  |

| Delault        |                              |                |   | 0x02 | = D'2 |   |   |   |  |

Bit definitions:

• Bit 7-0: Device software version number

# 5.3 0x01 Flags

### 5.3.1 System flags

|                | SYSFLAGS0 (0x01, offset 0) |                   |              |   |                  |        |                          |              |  |  |  |  |

|----------------|----------------------------|-------------------|--------------|---|------------------|--------|--------------------------|--------------|--|--|--|--|

| Bit<br>Number  | 7                          | 6                 | 5            | 4 | 3                | 2      | 1                        | 0            |  |  |  |  |

| Data<br>Access | R                          | R                 | R            | - | R                | R      | R                        | R            |  |  |  |  |

| Name           | SHOW<br>RESET              | NP_SEG<br>LT_N_UP | ATI<br>ERROR | - | NP SEG<br>ACTIVE | IN ATI | IGNORE<br>GLOBAL<br>HALT | LP<br>ACTIVE |  |  |  |  |

Bit definitions:

- Bit 7: Show reset

- o 0: No reset event

- 1: A device reset has occurred and needs to be acknowledged.

- Bit 6: NP segment LTA Update

- 0: LTA updates enable

- 1: LTA updates blocked

- Bit 5: ATI error

- 0: No ATI error occurred

- 1: An ATI error occurred

- Bit 3: NP segment active

- 0: Normal power segment is inactive

- 1: Normal power segment is active

- Bit 2: In ATI

- 0: No channels are in ATI

- o 1: System is busy executing an ATI

- Bit 1: Ignore global halt

- 0: Global halt is not ignored

- o 1: Global halt is ignored

- Bit 0: Low power active

- o 0: Low power mode is inactive

- o 1: Low power mode is active

#### 5.3.2 Events

|                | Events (0x01, offset 1) |   |                |              |              |             |                |               |  |  |  |

|----------------|-------------------------|---|----------------|--------------|--------------|-------------|----------------|---------------|--|--|--|

| Bit<br>Number  | 7                       | 6 | 5              | 4            | 3            | 2           | 1              | 0             |  |  |  |

| Data<br>Access | R                       | - | R              | R            | R            | R           | R              | R             |  |  |  |

| Name           | LP<br>EVENT             | - | SWIPE<br>EVENT | TAP<br>EVENT | ATI<br>EVENT | TP<br>EVENT | TOUCH<br>EVENT | PROX<br>EVENT |  |  |  |

Bit definitions:

- Bit 7: Low power event flag

- 0: No event to report

- 1: A low power event has occurred to signal low power mode entry

- Bit 5: Swipe event flag

- 0: No event to report

- 1: A swipe event has occurred and should be handled

- Bit 4: Tap event flag

- o 0: No event to report

- 1: A tap event has occurred and should be handled

- Bit 3: ATI event flag

- 0: No event to report

- 1: An ATI event has occurred and should be handled

- Bit 2: Trackpad event flag

- 0: No event to report

- 1: A trackpad event has occurred and should be handled

- Bit 1: Touch event flag

- o 0: No event to report

- 1: A touch event has occurred and should be handled

- Bit 0: Proximity event flag

- o 0: No event to report

- 1: A proximity event has occurred and should be handled

# 5.4 0x02 – 0x03 Trackpad data

### 5.4.1 Trackpad flags

|                | TP_FLAGS (0x02, offset 0) |       |                |               |               |             |     |              |  |  |  |  |

|----------------|---------------------------|-------|----------------|---------------|---------------|-------------|-----|--------------|--|--|--|--|

| Bit<br>Number  | 7                         | 6     | 5              | 4             | 3             | 2           | 1   | 0            |  |  |  |  |

| Data<br>Access | R                         | R     | R              | R             | R             | R           | R   | R            |  |  |  |  |

| Name           | SEG_1                     | SEG_0 | SWIPE<br>RIGHT | SWIPE<br>LEFT | SWIPE<br>DOWN | SWIPE<br>UP | TAP | TP<br>ACTIVE |  |  |  |  |

Bit definitions:

- Bit 7-6: Trackpad segment

- o 00: No trackpad segment event activation

- 01: Segment 1 trackpad event activation (Y: 0 85)

- 10: Segment 2 trackpad event activation (Y: 85 170)

- 11: Segment 3 trackpad event activation (Y: 170 255)

- Bit 5: Swipe right

- o 0: No swipe event to report

- Bit 4: Swipe left

- $\circ$  0: No swipe event to report

- Bit 3: Swipe down

- $\circ$   $\,$  0: No swipe event to report

- Bit 2: Swipe up

- $\circ$  0: No swipe event to report

- Bit 1: Tap

- o 0: No tap event to report

- Bit 0: TP active

- $\circ$  0: Trackpad not actively in use

- 1: Swipe right event occurred

- 1: Swipe left event occurred

- o 1: Swipe down event occurred

- o 1: Swipe up event occurred

- 1: Tap event occurred

- o 1: Trackpad actively in use

### 5.4.2 X current position

|        | X_CURR (0x03, offset 0) |                 |   |   |   |   |   |   |  |  |  |

|--------|-------------------------|-----------------|---|---|---|---|---|---|--|--|--|

| Bit    | 7                       | 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |  |  |  |

| Number |                         |                 |   |   |   |   |   |   |  |  |  |

| Data   | R                       | R               | R | R | R | R | R | R |  |  |  |

| Access | IX.                     |                 |   |   |   |   |   |   |  |  |  |

| Name   | X_CURR                  |                 |   |   |   |   |   |   |  |  |  |

Bit definitions:

• Bit 0 – 7:

o 0 – 127: X current position in decimal

#### 5.4.3 Y current position

|                | Y_CURR (0x03, offset 1)  |   |   |   |   |   |   |   |  |  |  |

|----------------|--------------------------|---|---|---|---|---|---|---|--|--|--|

| Bit<br>Number  | <b>r</b> 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |   |  |  |  |

| Data<br>Access | R                        | R | R | R | R | R | R | R |  |  |  |

| Name           | Y_CURR                   |   |   |   |   |   |   |   |  |  |  |

Bit definitions:

- Bit 0 7:

- o 0 255: Y current position in decimal

### 5.5 0x04 Prox & Touch data

#### 5.5.1 Prox channel 0

|                | PROX_CHANNEL0 (0x04, offset 0) |   |   |   |   |   |   |   |  |  |  |

|----------------|--------------------------------|---|---|---|---|---|---|---|--|--|--|

| Bit<br>Number  |                                |   |   |   |   |   |   |   |  |  |  |

| Data<br>Access | -                              | - | - | - | - | - | - | R |  |  |  |

| Name           |                                |   |   |   |   |   |   |   |  |  |  |

Bit definitions:

- Bit 1: Channel 0 Prox

- o 0: No prox condition present on channel 0

- 1: A prox condition is present on channel 0

#### 5.5.2 Touch channels

|                | TOUCH_CHANNELS (0x04, offset 1) |   |   |   |   |   |   |   |  |  |  |

|----------------|---------------------------------|---|---|---|---|---|---|---|--|--|--|

| Bit<br>Number  |                                 |   |   |   |   |   |   |   |  |  |  |

| Data<br>Access | R                               | R | R | R | R | R | R | R |  |  |  |

| Name           |                                 |   |   |   |   |   |   |   |  |  |  |

Bit definitions:

- Bit 6: Channel 6 touch

- o 0: No touch on channel 6

- Bit 5: Channel 5 touch

- $\circ$   $\,$  0: No touch on channel 5  $\,$

- Bit 4: Channel 4 touch

- o 0: No touch on channel 4

- Bit 3: Channel 3 touch

- 0: No touch on channel 3

- Bit 2: Channel 2 touch

- o 0: No touch on channel 2

- Bit 1: Channel 1 touch

- o 0: No touch on channel 1

- Bit 0: Channel 0 touch

- $\circ$  0: No touch on channel 0

- o 1: Touch present on channel 6

- 1: Touch present on channel 5

- 1: Touch present on channel 4

- o 1: Touch present on channel 3

- 1: Touch present on channel 2

- 1: Touch present on channel 1

- 1: Touch present on channel 0

# 5.6 0x05 – 0x06 AC filtered channel count data

|                | ACF_CH0          |                 |    |    |    |    |   |   |  |  |  |  |

|----------------|------------------|-----------------|----|----|----|----|---|---|--|--|--|--|

| Bit<br>Number  | 7                | 6               | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |

| Data<br>Access | R                | R               | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |                  | ACF Channel Low |    |    |    |    |   |   |  |  |  |  |

| Bit<br>Number  | 15               | 14              | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |  |

| Data<br>Access | R                | R R R R R R R   |    |    |    |    |   |   |  |  |  |  |

| Name           | ACF Channel High |                 |    |    |    |    |   |   |  |  |  |  |

Bit definitions:

• Bit 0-15: AC filtered or raw value counts

# 5.7 0x07 – 0x0B Channel count data

|                | Counts_CH1-6        |                    |    |    |    |    |   |   |  |  |  |  |

|----------------|---------------------|--------------------|----|----|----|----|---|---|--|--|--|--|

| Bit<br>Number  | 7                   | 6                  | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |

| Data<br>Access | R                   | R                  | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |                     | Channel Counts Low |    |    |    |    |   |   |  |  |  |  |

| Bit<br>Number  | 15                  | 14                 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |  |

| Data<br>Access | R                   | R R R R R R R      |    |    |    |    |   |   |  |  |  |  |

| Name           | Channel Counts High |                    |    |    |    |    |   |   |  |  |  |  |

Bit definitions:

• Bit 0-15: Raw value counts

# 5.8 0x0C – 0x0D LTA data

|                | LTA CH0 |                  |    |    |    |    |   |   |  |  |  |  |

|----------------|---------|------------------|----|----|----|----|---|---|--|--|--|--|

| Bit<br>Number  | 7       | 6                | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |

| Data<br>Access | R       | R                | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |         | LTA Channel Low  |    |    |    |    |   |   |  |  |  |  |

| Bit<br>Number  | 15      | 14               | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |  |

| Data<br>Access | R       | R                | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |         | LTA Channel High |    |    |    |    |   |   |  |  |  |  |

Bit definitions:

• Bit 0-15: LTA filter value output

# 5.9 0x0E – 0x12 REF data

|                | REF CH1-6 |                  |    |    |    |    |   |   |  |  |  |  |

|----------------|-----------|------------------|----|----|----|----|---|---|--|--|--|--|

| Bit<br>Number  | 7         | 6                | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |

| Data<br>Access | R         | R                | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |           | REF Channel Low  |    |    |    |    |   |   |  |  |  |  |

| Bit<br>Number  | 15        | 14               | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |  |

| Data<br>Access | R         | R R R R R R R    |    |    |    |    |   |   |  |  |  |  |

| Name           |           | REF Channel High |    |    |    |    |   |   |  |  |  |  |

Bit definitions:

• Bit 0-15: Reference value output

# 5.10 0x13 - 0x19 Deltas

|                | Delta CHx          |                   |    |    |    |    |   |   |  |  |  |  |

|----------------|--------------------|-------------------|----|----|----|----|---|---|--|--|--|--|

| Bit<br>Number  | 7                  | 6                 | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |

| Data<br>Access | R                  | R                 | R  | R  | R  | R  | R | R |  |  |  |  |

| Name           |                    | Delta Channel Low |    |    |    |    |   |   |  |  |  |  |

| Bit<br>Number  | 15                 | 14                | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |  |

| Data<br>Access | R                  | R R R R R R R     |    |    |    |    |   |   |  |  |  |  |

| Name           | Delta Channel High |                   |    |    |    |    |   |   |  |  |  |  |

Bit definitions:

- Bit 0-15: Delta value of channel

- $\circ$  Delta = LTA ACF (CH0)

- Delta = ACF- REF (CH1-6)

# 5.11 0x80 – 0x81 Prox settings

#### 5.11.1 Prox settings 0

|                | PROX_SETTINGS_0 (0x80, offset 0) |                |             |             |              |              |              |               |  |  |  |

|----------------|----------------------------------|----------------|-------------|-------------|--------------|--------------|--------------|---------------|--|--|--|

| Bit<br>Number  | 7                                | 6              | 5           | 4           | 3            | 2            | 1            | 0             |  |  |  |

| Data<br>Access | R/W                              | R/W            | R/W         | R/W         | R/W          | R/W          | R/W          | R/W           |  |  |  |

| Name           | AUTO<br>ATI_OFF                  | ATI<br>PARTIAL | ATI<br>BAND | REDO<br>ATI | DO<br>RESEED | DEBUG<br>ATI | INC<br>STABL | FORCE<br>HALT |  |  |  |

| Default        | 0                                | 0              | 0           | 0<br>0x(    | 0            | 0            | 0            | 0             |  |  |  |

Bit definitions:

- Bit 7: Auto ATI

- 0: Auto ATI on

- Bit 6: ATI partial

- o 0: Normal ATI active

- Bit 5: ATI band

- o 0: Normal ATI band

- Bit 4: Redo ATI

- 0: None

- Bit 3: Do reseed

- 0: None

- Bit 2: Debug ATI

- 0: No communication during ATI

- Bit 1: Increase stability

- $\circ$  0: Normal analogue settling time

- Bit 0: Force halt

- 0: Normal halting

- o 1: Auto ATI off

- 1: Partial ATI active (Sensitivity multipliers are selected by the user and kept fixed)

- o 1: Large ATI band

- $\circ$  1: Redo an ATI

- 1: Do a reseed operation

- 1: Communication during ATI allowed

- 1: Increased analogue settling time for more stability

- o 1: Force halt Ch0 LTA and Ch1-6 REF

#### 5.11.2 Prox settings 1

|                |                  | PRO           | X_SETTI | NGS_1 (0x | 80, offset | 1)  |        |        |

|----------------|------------------|---------------|---------|-----------|------------|-----|--------|--------|

| Bit<br>Number  | 7                | 6             | 5       | 4         | 3          | 2   | 1      | 0      |

| Data<br>Access | R/W              | R/W           | R/W     | R/W       | R/W        | R/W | R/W    | R/W    |

| Name           | COMMS<br>WDT OFF | EVENT<br>MODE | Ch0 LTA | FILTER    | -          | -   | Ch0 AC | FILTER |

| Default        | 0                | 0             | 0       | 1         | 0          | 0   | 0      | 1      |

| Delault        |                  |               |         | 0x2       | 11         |     |        |        |

Bit definitions:

- Bit 7: Communication watch dog timer off

- 0: Communication watch dog timer enabled. Reset will occur if timeout occurs.

- 1: Communication watch dog timer disabled. Reset will not occur upon timeout.

It is not advised to disable the communication watch dog timer.

- Bit 6: Event mode:

- 0: Streaming mode communication enabled

- 1: Event mode communication enabled

- Bit 5-4: CH0 LTA filter beta selection

- 00: LTA beta = 1/512

- 01: LTA beta = 1/256

- Bit 1-0: CH0 AC filter beta selection

- $\circ$  00: AC filter off

- 01: ACF beta = 1

- 10: LTA beta = 1/128

- 11: LTA beta = 1/64

- 10: ACF beta = 2

- 11: ACF beta = 3

### 5.11.3 Prox settings 2

|                | PROX_SETTINGS_2 (0x81, offset 0) |   |                     |   |                      |                 |     |     |  |  |  |  |

|----------------|----------------------------------|---|---------------------|---|----------------------|-----------------|-----|-----|--|--|--|--|

| Bit<br>Number  | 7                                | 6 | 5                   | 4 | 3                    | 2               | 1   | 0   |  |  |  |  |

| Data<br>Access | -                                | - | R/W                 | - | R/W                  | R/W             | R/W | R/W |  |  |  |  |

| Name           | -                                | - | WAKE<br>BOTH<br>DIR | - | CLEAR<br>TP<br>FLAGS | NP_SEGMENT_RATE |     |     |  |  |  |  |

| Default        | 0                                | 0 | 0                   | 0 | 0                    | 0               | 1   | 1   |  |  |  |  |

| Donaun         | 0x03                             |   |                     |   |                      |                 |     |     |  |  |  |  |

Bit definitions:

- Bit 5: Wake both directions

- $\circ~$  0: Normal activation in only one direction of count movement respective to LTA/REF.

- o 1: Activation in both directions of count movement respective to LTA/REF.

- Bit 4: Clear trackpad flags

- o 0: Trackpad flags stay set from last active trackpad event

- o 1: Trackpad flags are cleared after each communication window

- Bit 2-0: NP\_SEGMENT\_RATE

- 0 7: Normal power segment rate =  $2^{(NP\_SEGMENT\_RATE)}$

- b'000 = 0: 1

- b'001 = 1: 2

- b'010 = 2: 4

- b'011 = 3: 8

- b'100 = 4: 16

- b'101 = 5: 32

- b'110 = 6: 64

- b'111 = 7: 128

### 5.11.4 Prox settings 3

|                |              | F           | PROX_SET     | TINGS_3 (   | 0x81, offset   | 1)          |                       |                     |

|----------------|--------------|-------------|--------------|-------------|----------------|-------------|-----------------------|---------------------|

| Bit<br>Number  | 7            | 6           | 5            | 4           | 3              | 2           | 1                     | 0                   |

| Data<br>Access | R/W          | R/W         | R/W          | R/W         | R/W            | R/W         | R/W                   | R/W                 |

| Name           | ACK<br>RESET | OFF<br>MODE | PROJ<br>BIAS | FLOAT<br>CX | HALT<br>CHARGE | CH0<br>DIST | XFER<br>SLOW<br>CH1-6 | XFER<br>SLOW<br>CH0 |

| Default        | 0            | 0           | 0            | 0           | 0              | 0           | 0                     | 0                   |

| Delault        | 0x00         |             |              |             |                |             |                       |                     |

Bit definitions:

- Bit 7: Acknowledge reset

- o 0: None

- 1: Command to clear the SHOW RESET flag

- Bit 6: Off mode

- 0: IC in on mode

- 1: IC in off mode

- Bit 5: Projected bias current setting

- 0: Normal projected biasing current (5µA)

- 1: Increased projected biasing current (10μA)

- Bit 4: Float Cx pins

- o 0: Ground Cx pins while not actively charged

- o 1: Float Cx pins while not actively charged

- Bit 3: Halt charge

- 0: Normal charging

- 1: Halt all channel charging

- Bit 2: Channel 0 distributed

- o 0: Self capacitive charging on CX0 pin. No distributed prox channel.

- 1: Distributed self capacitive prox channel charging on pins CX0, RX1 & RX2 simultaneously.

- Bit 0: Slow charging frequency on channel 1-6

- 0: Normal charging frequency: 2MHz

- 1: Slow charging frequency: 1MHz

- Bit 0: Slow charging frequency on channel 0

- 0: Normal charging frequency: 1MHz

- 1: Slow charging frequency: 500kHz

# 5.12 0x82 Event mask

|                | Event mask (0x82, offset 0) |   |                        |                      |                      |                     |                        |                       |  |  |  |  |

|----------------|-----------------------------|---|------------------------|----------------------|----------------------|---------------------|------------------------|-----------------------|--|--|--|--|

| Bit<br>Number  | 7                           | 6 | 5                      | 4                    | 3                    | 2                   | 1                      | 0                     |  |  |  |  |

| Data<br>Access | R                           | - | R                      | R                    | R                    | R                   | R                      | R                     |  |  |  |  |

| Name           | LP<br>EVENT<br>AMSK         | - | SWIPE<br>EVENT<br>MASK | TAP<br>EVENT<br>MASK | ATI<br>EVENT<br>MASK | TP<br>EVENT<br>MASK | TOUCH<br>EVENT<br>MASK | PROX<br>EVENT<br>MASK |  |  |  |  |

| Default        | 1                           | - | 1                      | 1<br>0x              | 1<br>FF              | 1                   | 1                      | 1                     |  |  |  |  |

Bit definitions:

- Bit 7: Low power event mask

- 0: Event is masked out

- Bit 5: Swipe event mask

- 0: Event is masked out

- Bit 4: Tap event mask

- $\circ$  0: Event is masked out

- Bit 3: ATI event mask

- o 0: Event is masked out

- Bit 2: Trackpad event mask

- o 1: Event is active

- o 1: Event is active

- 1: Event is active

- o 1: Event is active

- o 0: Event is masked out

- Bit 1: Touch event mask

- o 0: Event is masked out

- Bit 0: Proximity event mask

- o 0: Event is masked out

- o 1: Event is active

- o 1: Event is active

- o 1: Event is active

# 5.13 0x82 offset 1 – 0x83 offset 1 Timeout periods

### 5.13.1 Zoom timeout period

|                | Zoom timeout (0x82, offset 1) |     |     |           |            |     |     |     |  |  |  |

|----------------|-------------------------------|-----|-----|-----------|------------|-----|-----|-----|--|--|--|

| Bit<br>Number  | 7                             | 6   | 5   | 4         | 3          | 2   | 1   | 0   |  |  |  |

| Data<br>Access | R/W                           | R/W | R/W | R/W       | R/W        | R/W | R/W | R/W |  |  |  |

| Name           |                               |     |     | Zoom time | out period |     |     |     |  |  |  |

| Default        | 0                             | 0   | 0   | 0         | 1          | 0   | 1   | 0   |  |  |  |

| Default        | 0x0A = D'10 * 500ms = 5sec    |     |     |           |            |     |     |     |  |  |  |

Bit definitions:

• Bit 7-0:

o 0-255: Zoom timeout period in 500ms increments.

### 5.13.2 Halt timeout period

|                | Halt timeout (0x83, offset 0) |     |     |              |            |       |     |     |  |  |  |

|----------------|-------------------------------|-----|-----|--------------|------------|-------|-----|-----|--|--|--|

| Bit<br>Number  | 7                             | 6   | 5   | 4            | 3          | 2     | 1   | 0   |  |  |  |

| Data<br>Access | R/W                           | R/W | R/W | R/W          | R/W        | R/W   | R/W | R/W |  |  |  |

| Name           |                               |     | Nor | mal mode s   | ampling pe | eriod |     |     |  |  |  |

| Default        | 0                             | 0   | 1   | 0            | 1          | 0     | 0   | 0   |  |  |  |