Le88266/286

#### Dual Channel Auto Battery Switching (ABS)

# Wideband VoicePort<sup>™</sup> - VE880 Series

#### Features

- Complete BORSCHT Functions for 2 Channels in a Single VoicePort<sup>™</sup> Device

- Integrated Power Management

- Integrated high voltage switching regulator controllers generates supplies for VBH, VBM & VBL

- · Low power Idle and On-hook transmission states

- Worldwide Programmability

- Input impedance, Balance Impedance, Gain

- · DC feed voltage and current limit

- Ringing frequency, voltage and current limit

- 12 kHz and 16 kHz Metering

- Programmable supervision thresholds

- Ringing

- 5 REN with pin for pin compatible 100-V (Le88266) and 120-V (Le88286) devices

- Up to 110-Vpk internal balanced ringing with programmable DC offset

- Powerful Signal Generator

- Universal Caller ID generation

- Up to 4 simultaneous tones

- VoicePath<sup>™</sup> API-II Software Available to Implement FXS Functions

- · Supports device calibration

- Line configuration via VoicePath Profile Wizard

- VeriVoice<sup>™</sup> Test Suite Subscriber Loop Test

- Seamless integration with VP-API-II software

- · Utilizes integrated self test capabilities

- · Line fault detection and reporting

- Pin Selectable PCM/MPI or GCI Interface

- G.711 μ-law, A-law, or 16 bit Linear Coding

- Wideband 16 kHz Sampling Mode

- Integrated 150 mW 3-V Relay Driver

- · External catch diode required

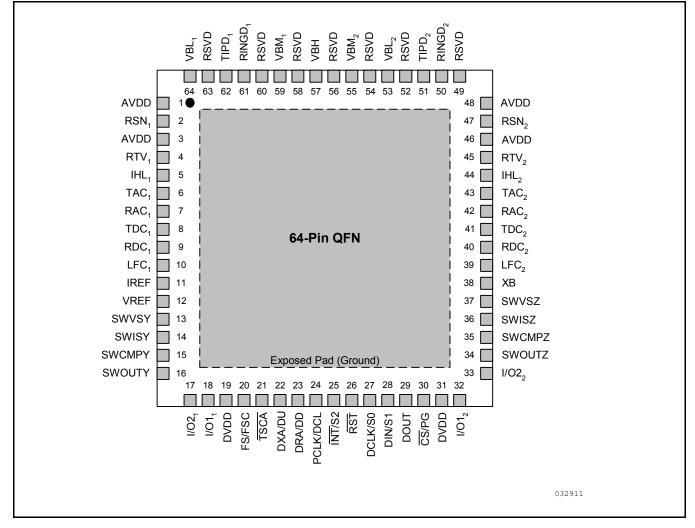

- Small Footprint Package Exposed Pad 64-pin QFN

- Minimal External Discrete Components Required

#### Document ID#: 126939

July 2014

#### **Ordering Information**

| Le88266TQC 64-pin QFN (0 | Green) <sup>1</sup> Tray <sup>2</sup>  |

|--------------------------|----------------------------------------|

| Le88286TQC 64-pin QFN (0 | Green) <sup>1</sup> Tray <sup>2</sup>  |

| Le88266DLC 80-pin eLQFP  | (Green) <sup>1</sup> Tray <sup>2</sup> |

| Le88286DLC 80-pin eLQFP  | (Green) <sup>1</sup> Tray <sup>2</sup> |

- The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- 2. For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

#### Applications

- · Voice enabled Cable EMTA's

- DSL Gateways and IAD's

- Fiber to the Building/Home (FTTB/H) Optical Network Terminals (ONT)

- Wireless Local Loop (WLL), PBX

#### Description

The Microsemi<sup>®</sup> Le88266/286 Automatic Battery Switching (ABS) VoicePort device implements a dualchannel telephone line interface from the high voltage subscriber line to the PCM / MPI digital interface.

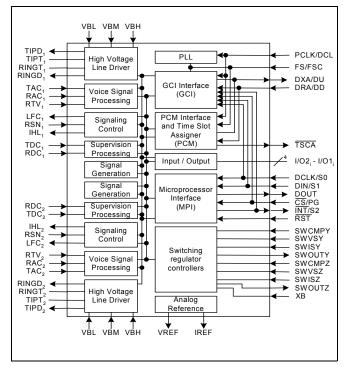

Figure 1 - VoicePort Device Block Diagram

# **Table of Contents**

|     | Product Description                                                                 |            |

|-----|-------------------------------------------------------------------------------------|------------|

|     | Detailed Features of the Le88266/286 Device                                         |            |

| 3.0 | Block Descriptions                                                                  |            |

|     | 3.1 Digital Interfaces                                                              | 6          |

|     | 3.3 Microprocessor Interface (MPI).                                                 | . 9        |

|     | 3.3 Microprocessor Interface (MPI)                                                  | . 11       |

|     | 3.5 Internal Configuration Registers                                                | . 20       |

|     | 3.6 Input / Output Block                                                            | . 20       |

|     | 3.8 Signal Generation and Cadence Control.                                          | .20        |

|     | 3.9 Signaling Control                                                               | . 26       |

|     | 3.10 Supervision Processing                                                         | . 30       |

|     | 3.11 Analog Reference Circuits.         3.12 High Voltage Line Driver               | . 32       |

|     | 3.13 Internal Test Termination.                                                     | . 32       |

|     | 3.14 Test Load Switch (Le88286DLC only).                                            | . 32       |

|     | 3.15 Line Testing                                                                   | . 32       |

|     | 3.16 Switching Regulator Controllers                                                |            |

|     | Connection Diagrams and Pin Descriptions                                            |            |

| 5.0 | Absolute Maximum Ratings                                                            |            |

|     | 5.1 Thermal Resistance. 5.2 Package Assembly                                        | .41        |

| 6.0 | Operating Ranges                                                                    |            |

|     | 6.1 Recommended Operating Conditions                                                | .41        |

| 7.0 | Electrical Characteristics                                                          |            |

|     | 7.1 Test Conditions                                                                 | . 42       |

|     | 7.2 Supply Currents and Power Dissipation                                           | . 42       |

|     | 7.3 DC Characteristics.<br>7.4 DC Feed and Signaling                                |            |

|     | 7.5 Test Load Switch (Le88286DLC Device Only)                                       | .44        |

|     | 7.6 Metering                                                                        | . 44       |

|     | 7.7 Ringing                                                                         | . 45       |

|     | 7.8 Switching Regulator Controller                                                  | . 45<br>46 |

|     | 7.10 Transmission Characteristics - Narrowband Codec Mode                           | .47        |

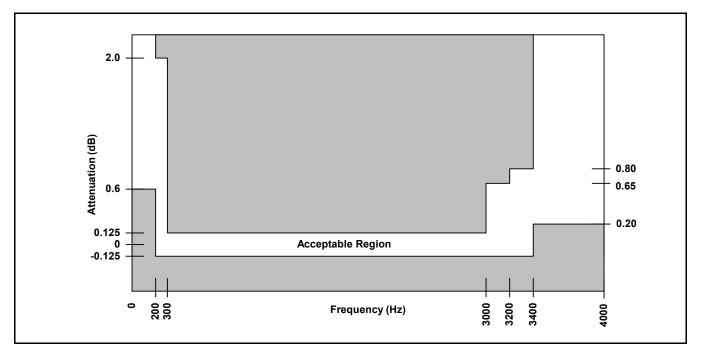

|     | 7.11 Attenuation Distortion - Narrowband Codec Mode                                 | . 48       |

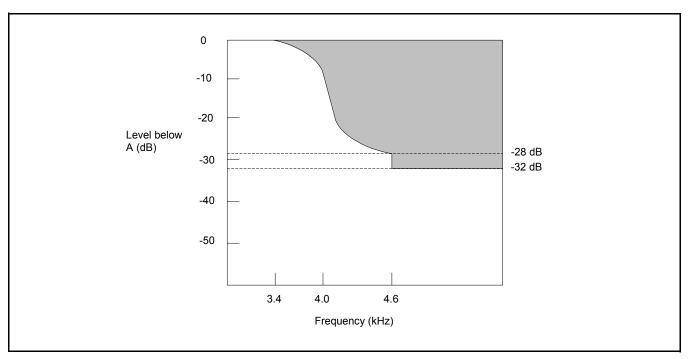

|     | 7.12 Discrimination Against Out-of-Band Input Signals - Narrowband Codec Mode       | . 49       |

|     | 7.13 Discrimination Against 12- and 16-kHz Metering Signals - Narrowband Codec Mode | . 49       |

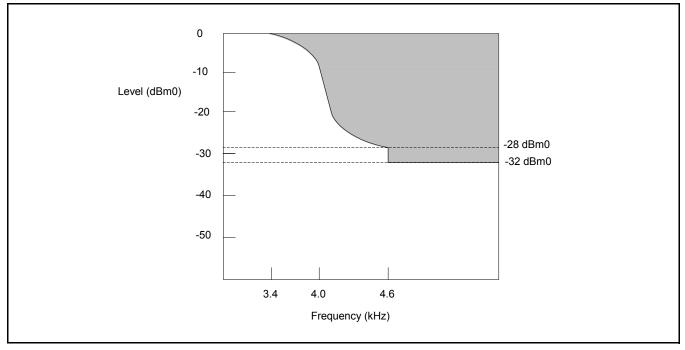

|     | 7.14 Spurious Out-of-Band Signals at the Analog Output - Narrowband Codec Mode      | . 50       |

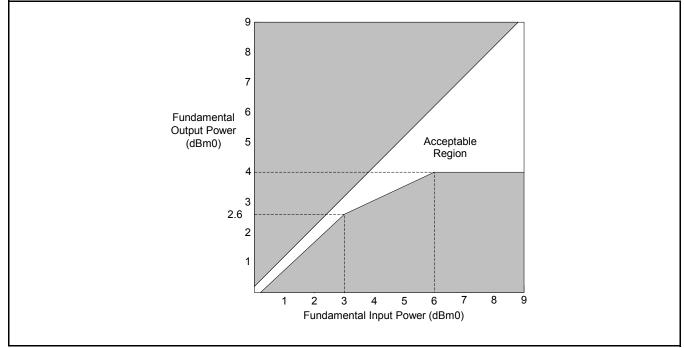

|     | 7.16 Gain Linearity - Narrowband Codec Mode                                         | . 51       |

|     | 7.17 Total Distortion Including Quantizing Distortion - Narrowband Codec Mode       | . 52       |

|     | 7.18 Group Delay Distortion - Narrowband Codec Mode                                 | . 53<br>54 |

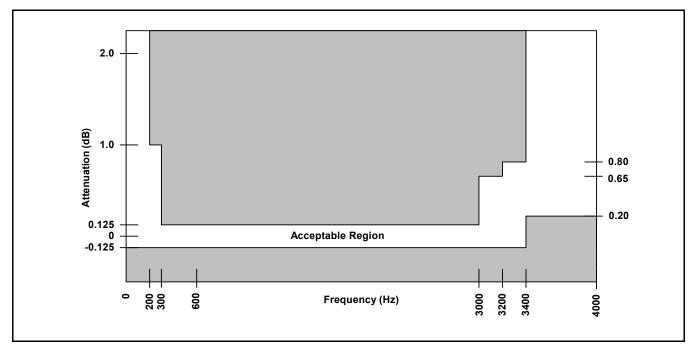

|     | 7.20 Attenuation Distortion - Wideband Codec Mode                                   |            |

|     | 7.21 Group Delay Distortion - Wideband Codec Mode                                   | . 56       |

| 8.0 | Switching Characteristics and Waveforms                                             |            |

|     | 8.1 Microprocessor Interface Timing                                                 | . 57       |

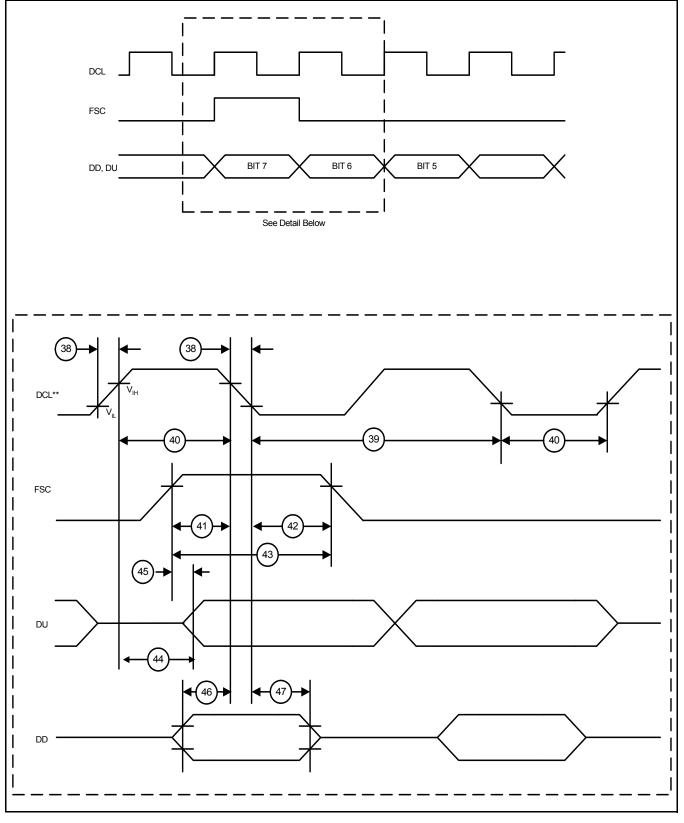

|     | 8.3 GCI Timing                                                                      |            |

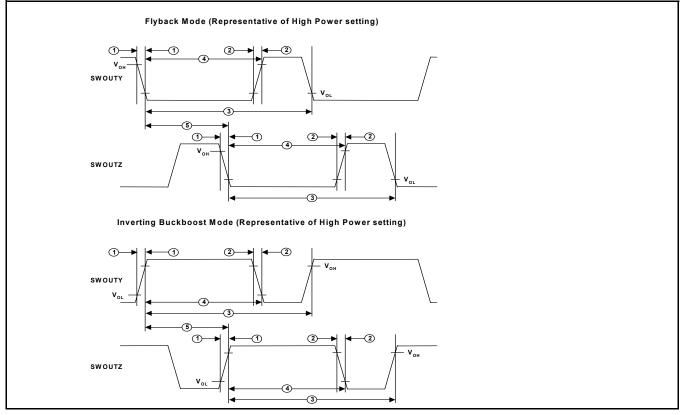

|     | 8.4 Switcher Output Timing                                                          |            |

| 9.0 | Applications                                                                        |            |

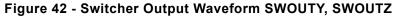

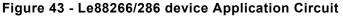

|     | 9.1 Application Circuit                                                             | . 66       |

|     | 9.2 Le88266/286 VoicePort™ Device Parts List                                        |            |

| 10. | Command Description and Formats                                                     |            |

|     | 10.1 Command Field Summary         10.2 MPI Description                             |            |

|     | 10.3 Summary of Commands                                                            | .70        |

|     | 10.4 Detailed Descriptions Of Commands                                              | . 72       |

# **Table of Contents**

|                                                                           | 70    |

|---------------------------------------------------------------------------|-------|

| 02h Software Reset                                                        |       |

| 04h Hardware Reset                                                        | 72    |

| 06h No Operation                                                          | . 72  |

| 40/41h Write/Read Transmit Time Slot                                      | 72    |

| 42/43h Write/Read Receive Time Slot                                       | 72    |

| 42/450 White/Read Receive Time Slot                                       | 75    |

| 44/45h Write/Read Transmit and Receive Clock Slot and Transmit Clock Edge |       |

| 46/47h Write/Read Device Configuration Register                           | 73    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register              | 74    |

| 4D/4Fh Read Signaling Register                                            | 75    |

| 50/51h Write/Read Voice Path Gains                                        | 77    |

| 52/53h Write/Read Input/Output Data Register                              |       |

|                                                                           |       |

| 54/55h Write/Read Input/Output Direction Register                         |       |

| 56/57h Write/Read System State                                            |       |

| 5E/5Fh Write/Read Device Mode Register                                    | 79    |

| 60/61h Write/Read Operating Functions                                     | 80    |

| 68/69h Write/Read System State Configuration                              | 81    |

| 6C/6Dh Write/Read Interrupt Mask Register                                 | 82    |

| 70/71h Write/Read Operating Conditions                                    | 82    |

| 73h Read Revision and Product Code Number (RCN,PCN)                       | 02    |

|                                                                           |       |

| 80/81h Write/Read GX Filter Coefficients                                  |       |

| 82/83h Write/Read GR Filter Coefficients                                  |       |

| 86/87h Write/Read B Filter FIR Coefficients                               | 84    |

| 88/89h Write/Read X Filter Coefficients                                   | 85    |

| 8A/8Bh Write/Read R Filter Coefficients                                   |       |

| 96/97h Write/Read B Filter IIR Coefficients                               |       |

| 98/99h Write/Read Z Filter FIR Coefficients                               |       |

|                                                                           |       |

| 9A/9Bh Write/Read Z Filter IIR Coefficients                               |       |

| A6/A7h Write/Read Converter Configuration                                 | 88    |

| C2/C3h Write/Read Loop Supervision Parameters                             | 90    |

| C6/C7h Write/Read DC Feed Parameters                                      | 90    |

| CA/CBh Write/Read Digital Impedance Scaling Network (DISN)                |       |

| CDh Read Transmit PCM/Test Data                                           | 01    |

|                                                                           |       |

| CFh Read Test Data Buffer                                                 |       |

| D0/D1h Write/Read Metering Parameters                                     |       |

| D2/D3h Write/Read Signal Generator A, B and Bias Parameters.              |       |

| D4/D5h Write/Read Signal Generator C and D Parameters.                    | 96    |

| DE/DFh Write/Read Signal Generator Control                                | 97    |

| E0/E1h Write/Read Cadence Timer                                           |       |

| E2/E3h Write/Read Caller Identification Number Data                       |       |

| E4/E5h Write/Read Switching Regulator Parameters                          |       |

|                                                                           |       |

| E6/E7h Write/Read Switching Regulator Control                             |       |

| E8/E9h Write/Read Battery Calibration Register                            |       |

| EA/EBh Write/Read Caller Identification Number Parameters                 |       |

| EC/EDh Write/Read Internal Configuration Register 1                       | . 103 |

| EE/EFh Write/Read Internal Configuration Register 2                       |       |

| F2/F3h Write/Read Internal Configuration Register 3                       |       |

| F4/F5h Write/Read Internal Configuration Register 4                       |       |

|                                                                           |       |

| FA/FBh Write/Read Internal Configuration Register 5                       |       |

| FC/FDh Write/Read DC Calibration Register                                 |       |

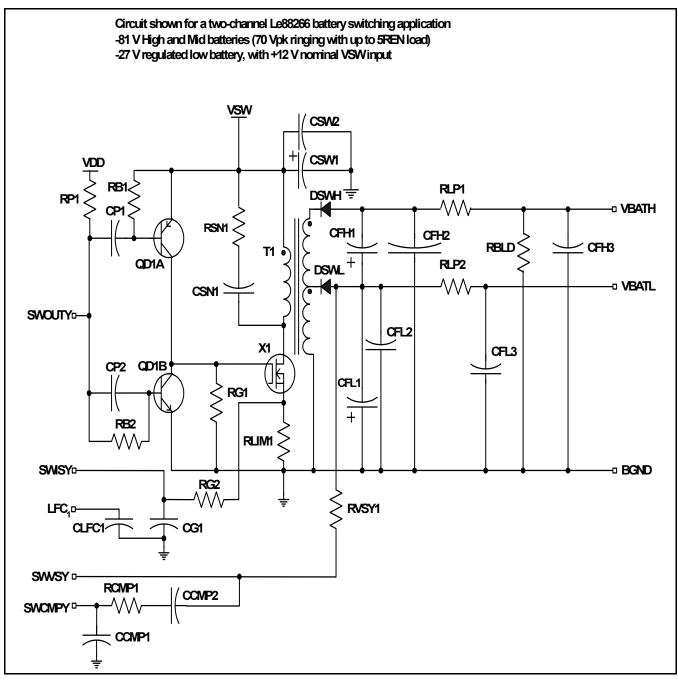

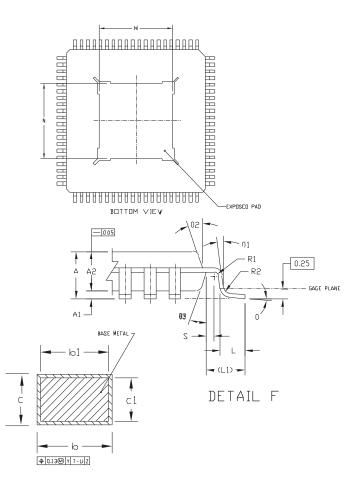

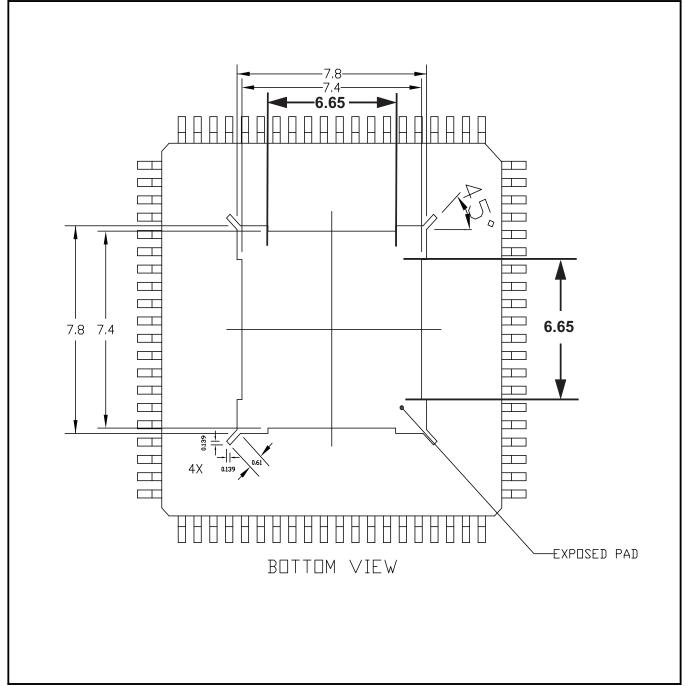

| 11.0 Physical Dimensions                                                  | . 106 |

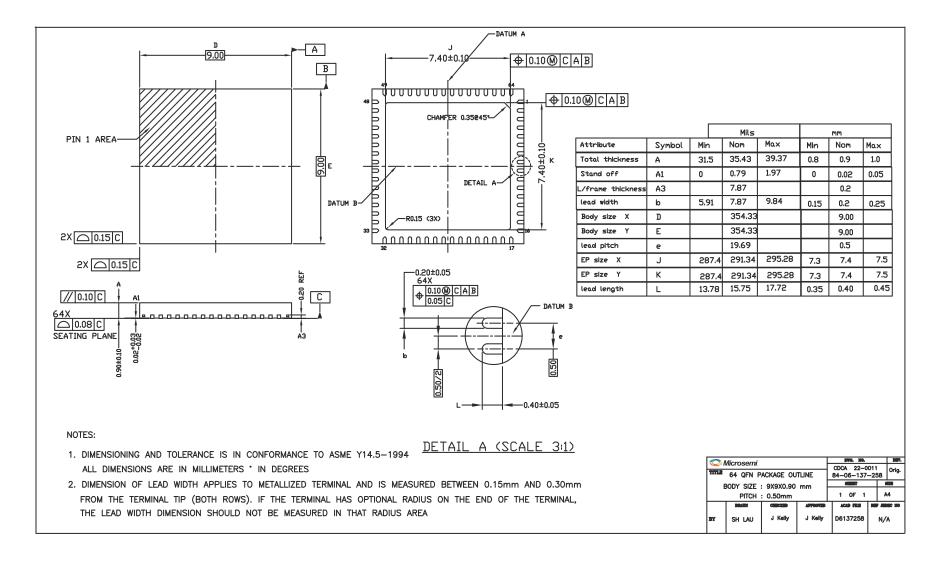

| 11.1 Detailed Bottom View of 80-Pin eLQFP                                 | . 108 |

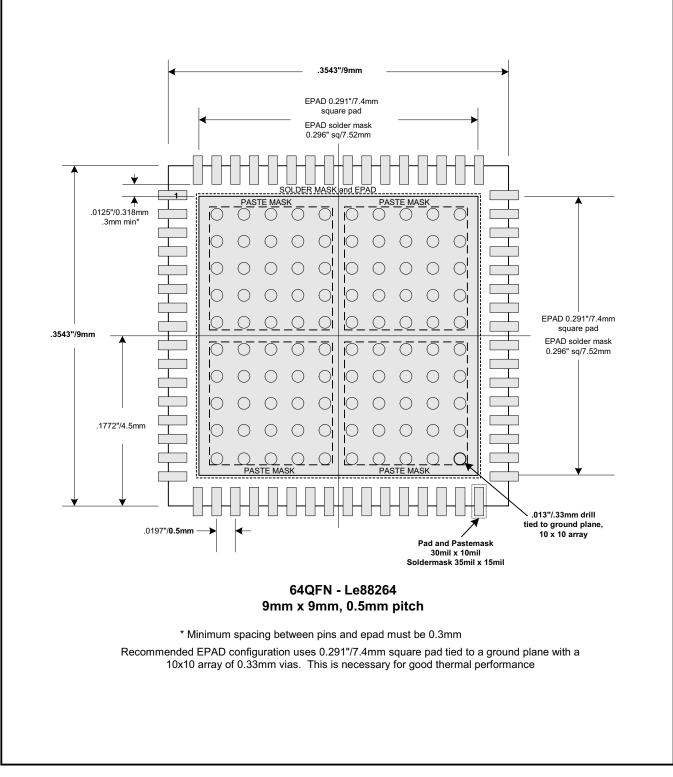

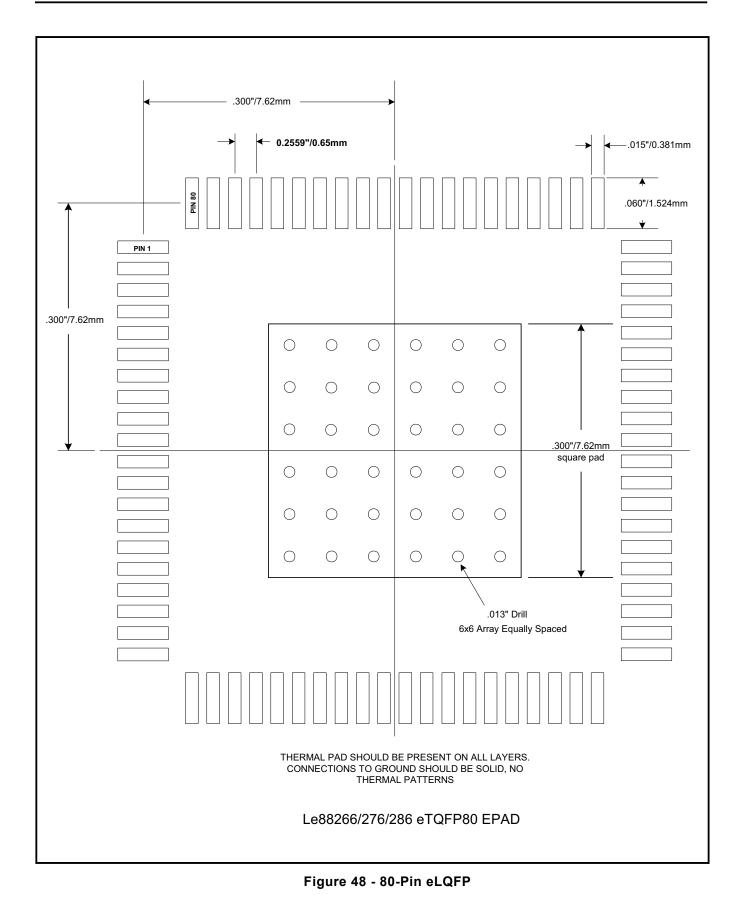

| 12.0 Recommended Land Patterns                                            |       |

|                                                                           |       |

| 13.0 Related Collateral                                                   |       |

| 13.1 Documentation                                                        | . 111 |

| 13.2 Development Hardware                                                 |       |

| 13.3 Development Software                                                 |       |

| 14.0 Revision History                                                     | . 112 |

# List of Figures

| Figure 1 - VoicePort Device Block Diagram                                        | 1    |

|----------------------------------------------------------------------------------|------|

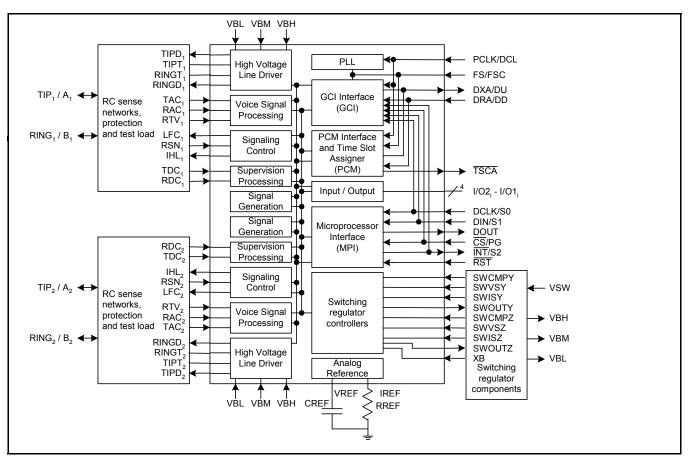

| Figure 2 - Le88266/286 VoicePort™ Block Diagram                                  | 6    |

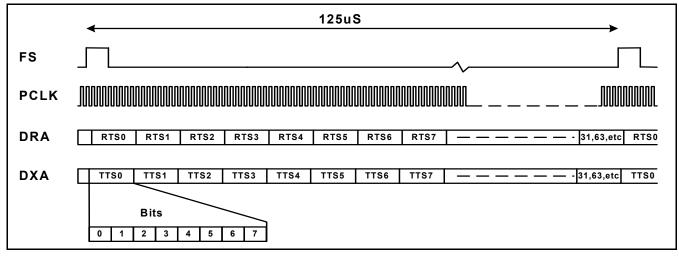

| Figure 3 - PCM highway structure                                                 | 7    |

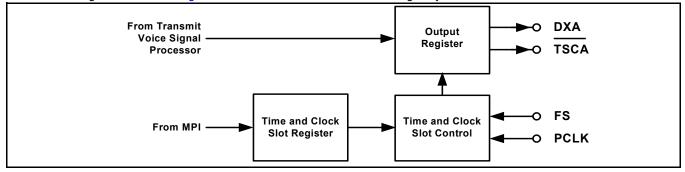

| Figure 4 - Transmit PCM interface                                                | 8    |

| Figure 5 - Receive PCM Interface                                                 | 8    |

| Figure 6 - PCM Interface Timing for XE = 0 (Transmit Data On Negative PCLK Edge) | 9    |

| Figure 7 - Microprocessor Interface Timing                                       | . 10 |

| Figure 8 - Multiplexed GCI Time Slot Structure                                   | . 12 |

| Figure 9 - GCI Interface and Packet Time Slot Selection                          | . 13 |

| Figure 10 - Security Procedure For C Downstream Byte.                            | . 14 |

| Figure 11 - Maximum Speed Monitor Handshake Timing                               | . 16 |

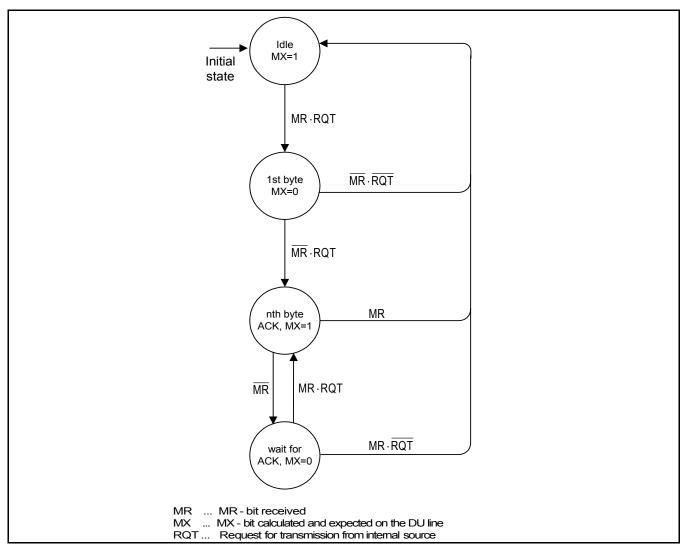

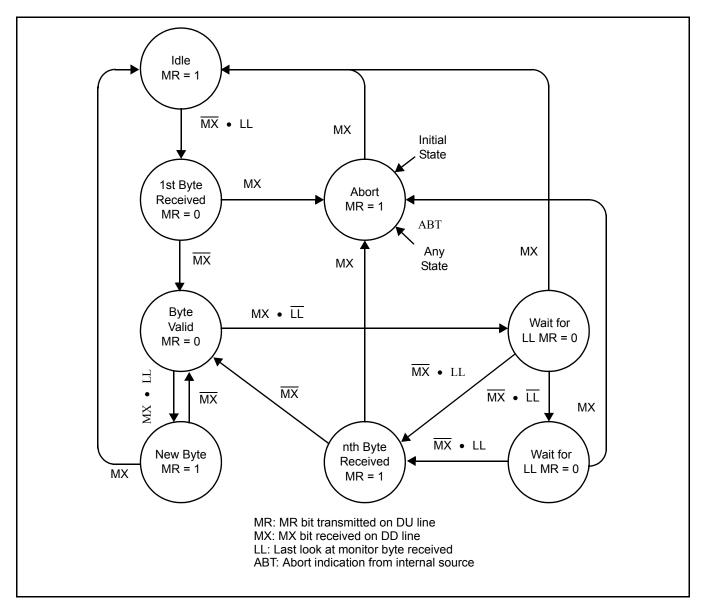

| Figure 12 - Monitor Transmitter Mode Diagram                                     | . 16 |

| Figure 13 - Monitor Receiver Mode Diagram                                        | . 17 |

| Figure 14 - Voice Signal Processing Block Diagram                                |      |

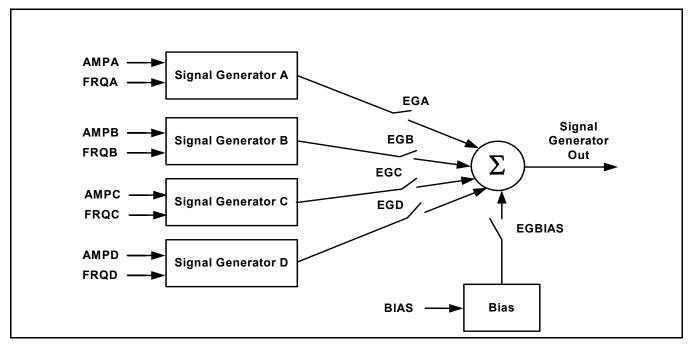

| Figure 15 - Signal Generator                                                     |      |

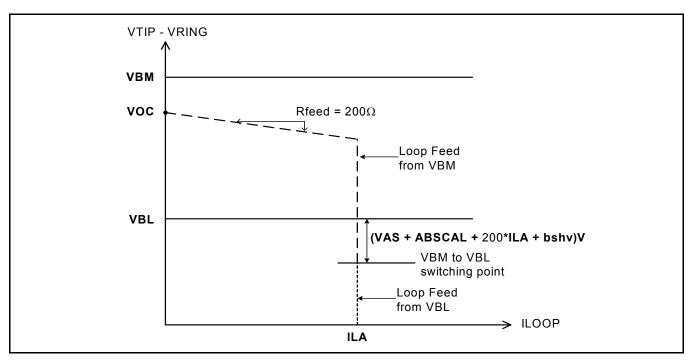

| Figure 16 - Active State DC Feed I / V Characteristic                            |      |

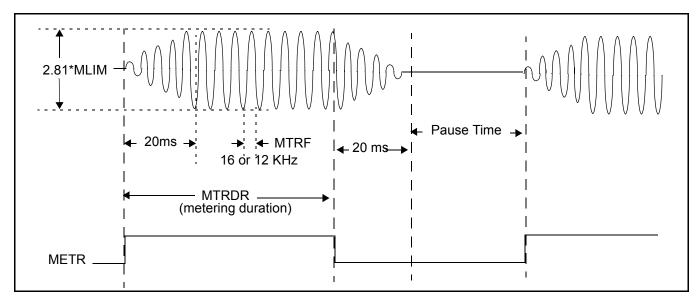

| Figure 17 - Metering Pulse Definitions.                                          |      |

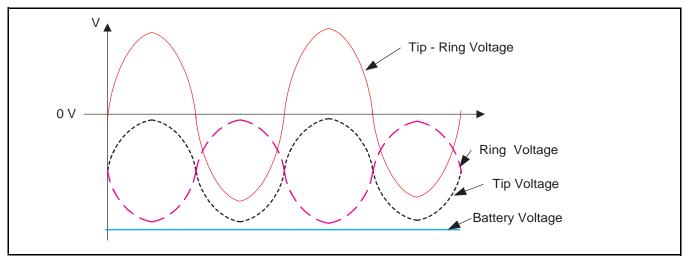

| Figure 18 - Balanced Ringing with Fixed Tracking Supply.                         |      |

| Figure 19 - Le88266/286 Device 64-Pin QFN Package (Top View).                    |      |

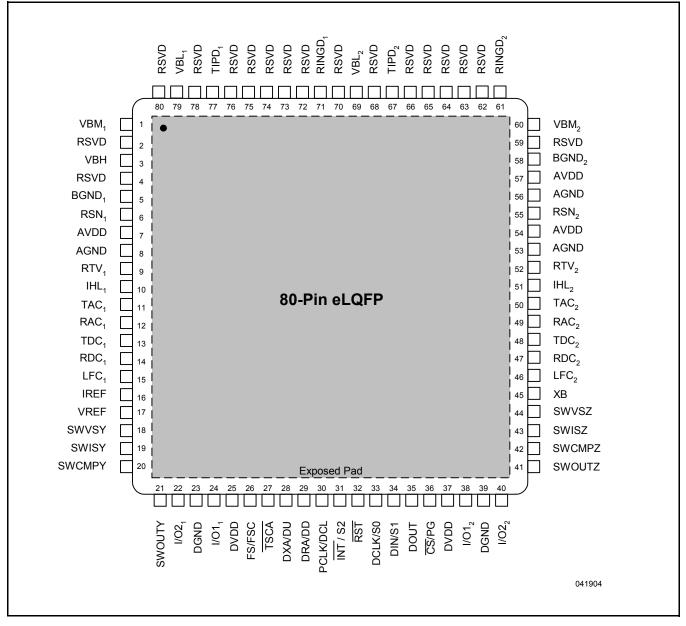

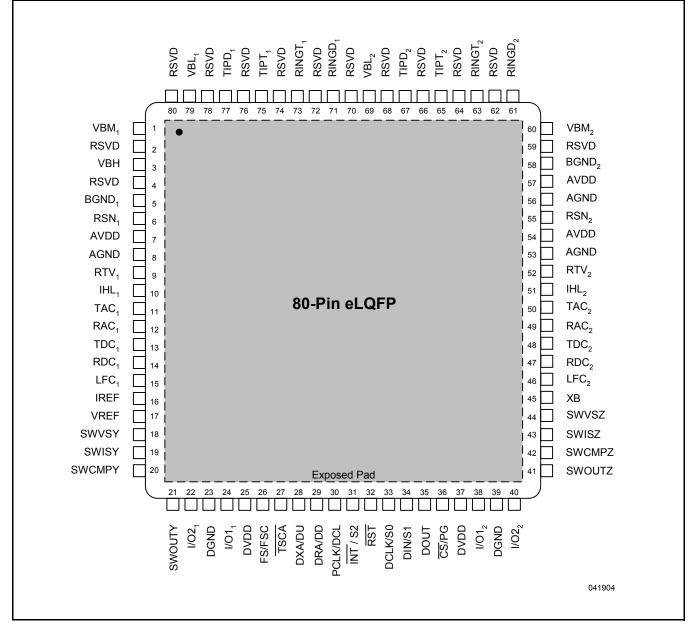

| Figure 20 - Le88266 Device 80-Pin eLQFP Package (Top View)                       | . 35 |

| Figure 21 - Le88286 Device 80-Pin eLQFP Package (Top View)                       |      |

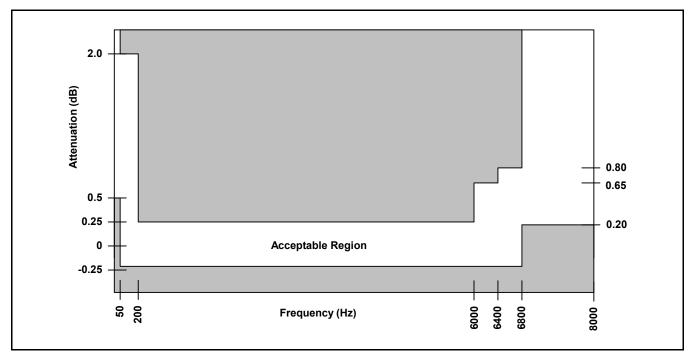

| Figure 22 - Transmit Path Attenuation vs. Frequency                              |      |

| Figure 23 - Receive Path Attenuation vs. Frequency                               |      |

| Figure 24 - Discrimination Against Out-of-Band Signals                           |      |

| Figure 25 - Spurious Out-of-Band Signals                                         |      |

| Figure 26 - Analog-to-Analog Overload Compression                                |      |

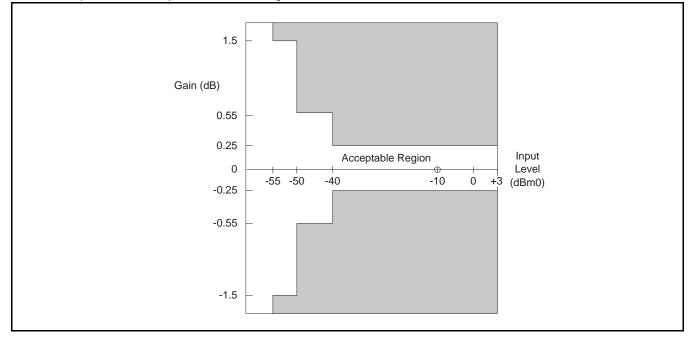

| Figure 27 - A-law Gain Linearity with Tone Input (Both Paths)                    |      |

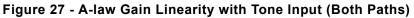

| Figure 28 - μ-law Gain Linearity with Tone Input (Both Paths).                   |      |

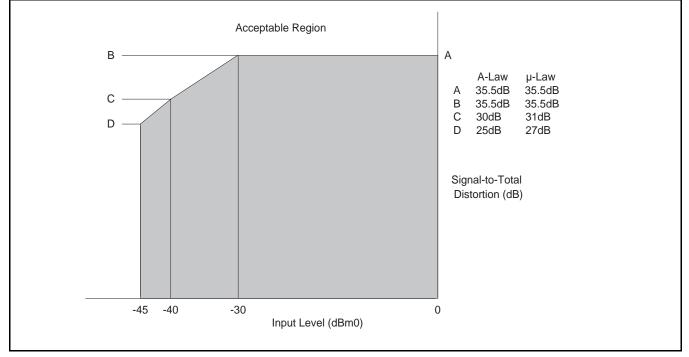

| Figure 29 - Total Distortion with Tone Input (Both Paths).                       |      |

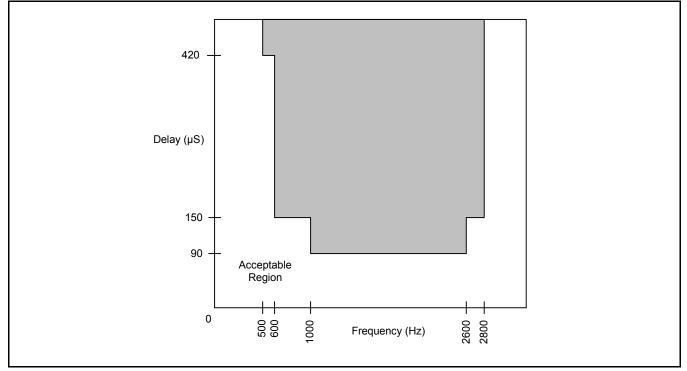

| Figure 30 - Group Delay Distortion                                               |      |

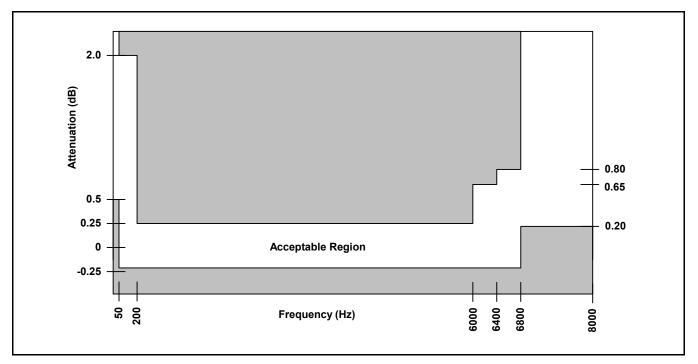

| Figure 31 - Transmit Path Attenuation vs. Frequency                              |      |

| Figure 32 - Receive Path Attenuation vs. Frequency                               |      |

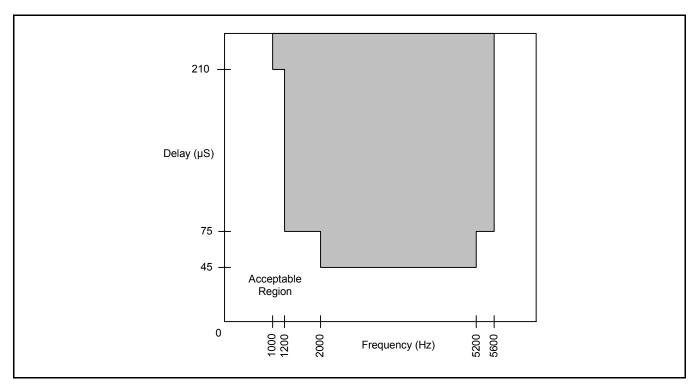

| Figure 33 - Group Delay Distortion                                               |      |

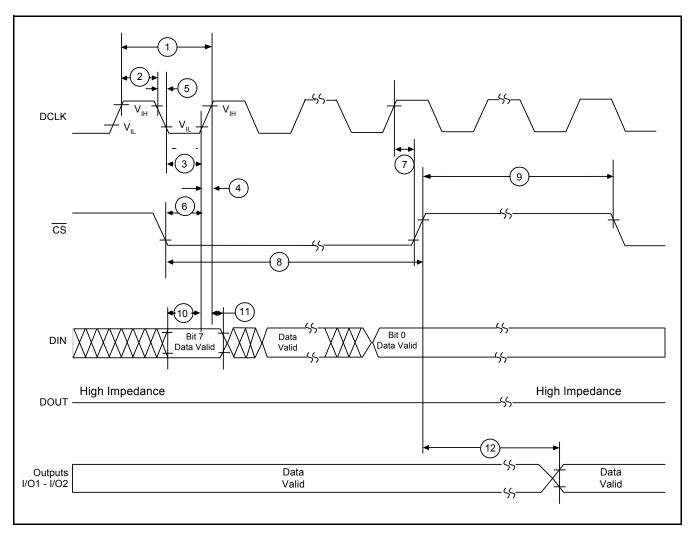

| Figure 34 - Microprocessor Interface (Input Mode)                                |      |

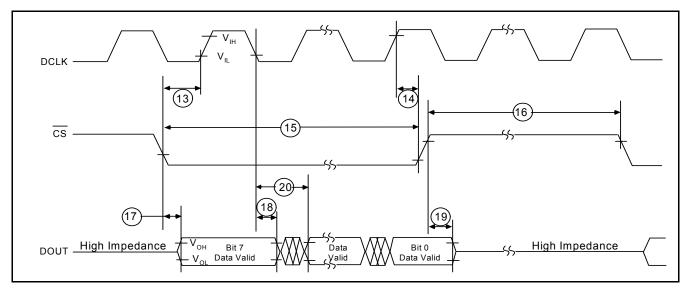

| Figure 35 - Microprocessor Interface (Output Mode).                              |      |

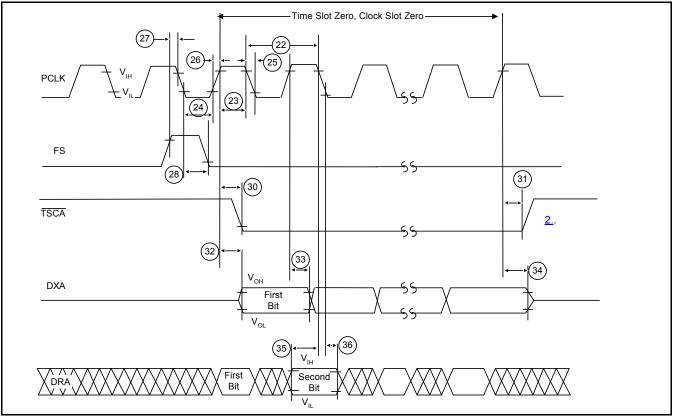

| Figure 36 - PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge)       |      |

| Figure 37 - PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge)       |      |

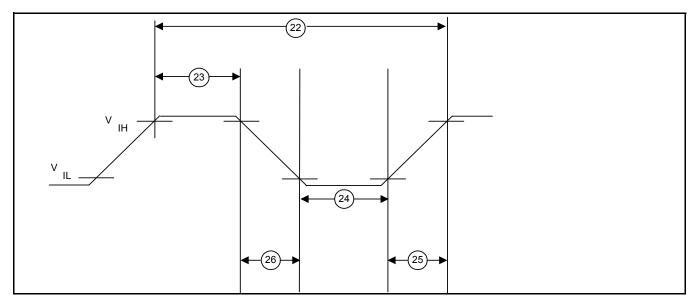

| Figure 38 - PCM Clock Timing                                                     |      |

| Figure 39 - Input and Output Waveforms for AC Tests                              |      |

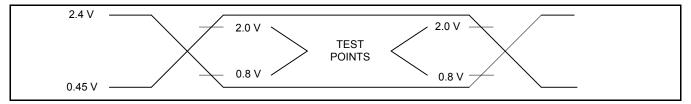

| Figure 40 - 4.096 MHz DCL Operation                                              |      |

| Figure 41 - 2.048 MHz DCL Operation                                              |      |

| Figure 42 - Switcher Output Waveform SWOUTY, SWOUTZ                              |      |

| Figure 43 - Le88266/286 device Application Circuit                               |      |

| Figure 44 - Le88266/286 Switching Regulator Circuit                              |      |

| Figure 45 - 64-Pin QFN                                                           |      |

| Figure 46 - 80-Pin eLQFP                                                         |      |

| Figure 47 - 64-Pin QFN                                                           |      |

| Figure 48 - 80-Pin eLQFP                                                         |      |

|                                                                                  |      |

## 1.0 Product Description

The Le88266/286 device implements a dual-channel universal telephone line interface. This enables the addition of a dual, low cost, high performance, software programmable line interface to cable EMTA's, fiber ONTs, Integrated Access Devices, DSL modems, SMTA's or set top boxes for multiple country applications worldwide. The Le88266/286 device performs all necessary voice telephony functions from driving a high voltage subscriber telephone line to DSP codec functions for two lines. All AC, DC, and signaling parameters are fully programmable via microprocessor interfaces. The Le88266/286 device has integrated high voltage switching regulator controllers which can generate the high voltages needed for efficiently powering and ringing analog telephones. The high performance architecture permits high efficiency in all operating states and corresponding low power dissipation. Additionally, the Le88266/286 has self-test and line-test support to allow the system to resolve faults to the line or line circuit. The integrated digital access to important line information such as AC and DC line voltage on Tip or Ring and Metallic or Longitudinal currents is crucial for remote applications where dedicated test hardware is not cost effective.

The dual-channel Le88266/286 device is a highly functional voice-over-broadband system that meets the needs of short and medium loop customers. The Le88266/286 devices are targeted toward voice applications and provide all BORSCHT functions. The Le88266 device has up to 92-Vpk internal ringing capability that has been optimized for short loop applications. The Le88286DLC device has 110-Vpk internal ringing capability that has been optimized for short loop and medium loop applications, can operate in a balanced or unbalanced ringing mode, and offers an integrated test load switch to control an external load.

The Le88266/286 device selectively interfaces with a PCM or GCI backplane and can be controlled over the MPI or GCI interface.

The software programmed transmission filter coefficients and supervision data are easily calculated with the WinSLAC<sup>™</sup> software, which allows the designer to enter a description of system requirements. WinSLAC then returns the necessary data and plots the predicted system results. This data is then processed by the Profile Wizard and compiled into the VoicePath<sup>™</sup> API-II software to allow easy integration with system software and quickly enable implementation of the required product features.

# 2.0 Detailed Features of the Le88266/286 Device

The Le88266/286 device supports the following features:

- Single chip solution provides high voltage line driving, digital signal processing, and high voltage power generation for two or more lines

- Wideband 7 kHz and narrowband 3.4 kHz codec modes

- Exceeds GR-909 transmission requirements

- Single hardware design meets worldwide requirements through software programming of:

- -Ringing waveform, frequency and amplitude

- -DC loop-feed characteristics and current-limit

- -Loop-supervision detection thresholds

- -Off-hook debounce circuit

- -Ground-key and ring-trip filters

- -Two-wire AC impedance

- -Transhybrid balance impedance

- -Transmit and receive gains

- -Transmit and receive equalization

- -Digital I/O pins

- -A-law/µ-law and linear coding selection

- -Switching Power Supply

- Supports both loop-start and ground-start signaling

- On-hook transmission

- Power/service denial mode

- Smooth polarity reversal

- Supports wink function

- Neon lamp driving capability

- Metering generation with envelope shaping

- Programmable metering duration

- Self-contained ringing generation and control

- Programmable Ringing Cadencing

- Internal battery-backed balanced or unbalanced, sine or trapezoidal ringing

- Integrated ring-trip filter and software enabled manual or automatic ring-trip mode

- Flexible tone generation

- Call progress tone generation

- DTMF tone generation

- Universal Caller ID generation

- Howler tone generation with VP-API-II

- Only 3.3 V logic and single battery supply needed

- · Integrated switching regulator controller

- Can generate the battery voltages for each line

- Line-feed characteristics independent of battery voltage

- MPI, PCM or GCI interfaces

- Supports most required PCM clock frequencies from 1.024MHz to 8.192 MHz

- Compatible with inexpensive protection networks

- Monitors two-wire interface voltages and currents for subscriber line diagnostics implemented by VeriVoice Test Suite software

- Built-in voice-path test modes

- Integrated self-test features

- Internal Test Termination

- Internal 3-V relay driver (Catch diode required)

- –40°C to 85°C operation

# 3.0 Block Descriptions

The Le88266/286 device provides a complete software-configurable solution to BORSCHT functions from digital interface to Tip and Ring for two channels.

The device comprises a CMOS device that includes a PLL to generate the necessary clocks for the internal processing functions, digital interfaces implemented in the PCM, MPI and GCI blocks, digital I/O, analog references, switching regulator controllers, voice signal processors, supervision, signalling and signal generation blocks as well as high voltage line drivers.

Figure 2 - Le88266/286 VoicePort™ Block Diagram

#### 3.1 Digital Interfaces

The Le88266/286 device offers two digital interface options. The first is PCM/MPI mode, in which separate serial control and voice data interfaces are provided. Voice data is interfaced via a PCM highway with time slot assignment capability, and control information is communicated over the Micro-Processor Interface (MPI). The second is GCI mode, in which a single serial interface supports both voice data and control. Wideband mode is only available in PCM/MPI mode.

The two modes are mutually exclusive and have different advantages and disadvantages. The PCM/MPI mode is most flexible and <u>allows</u> a wide range of DCLK (MPI data clock) and PCLK (PCM data clock) frequencies. PCM/MPI mode also allows use of the INT interrupt pin to signal pending interrupts to the external controller. GCI mode offers the advantage of using only four signals (FSC, DCL, DU, DD) to carry voice and control data. PCM/MPI mode uses twice as many signals (FS, PCLK, DXA, DRA for voice data and CSL, DCLK, DIN, DOUT for control data) to carry the same information. GCI mode has several disadvantages, however: only 2.048 MHz and 4.096 MHz DCL frequencies are allowed; the control interface is slow (250 µS/byte maximum throughput); and interrupt handling is more complex due to the lack of an interrupt pin. Multifunction pins are implemented to support these different modes while keeping the pin count low.

#### 3.1.1 PCM and GCI Mode Selection

The Le88266/286 device enters PCM/MPI or GCI modes based on the conditions outlined in Table 1.

The PCM / GCI select pin (CS/PG) is used in combination with the DCLK pin to determine which mode the device is in on power up. If PG is held Low and DCLK is held static, GCI mode is entered 1 ms after power up or hardware reset and the application of valid GCI DCLK and FSC signals. GCI mode will be exited at any time if PG is pulled high or a clock is detected on DCLK.

If PG is High then PCM/MPI mode is entered following power up. At this point, the mode can be changed to GCI if the GCI conditions are met. However, once a command is sent over the MPI interface, GCI mode cannot be entered without resetting the device.

| From Mode                     | To Mode | Requirement                                                                                                            |

|-------------------------------|---------|------------------------------------------------------------------------------------------------------------------------|

| Power On or Hardware<br>Reset | PCM     | CS/PG = 1 or DCLK has ac clock present                                                                                 |

| Power On or Hardware<br>Reset | GCI     | CS/PG = 0 and DCLK does not have ac clock present                                                                      |

| GCI                           | PCM     | CS/PG = 1 or DCLK has clock present                                                                                    |

| РСМ                           | GCI     | No commands yet sent in PCM state and $\overline{CS}/PG = 0$ (for more than 2 FS) and DCLK does not have clock present |

#### Table 1 - PCM/GCI Mode Selection

These methods are used to ensure the device operates in the desired mode at all times.

#### 3.2 PCM/MPI Interface and Time Slot Assigner (PCM)

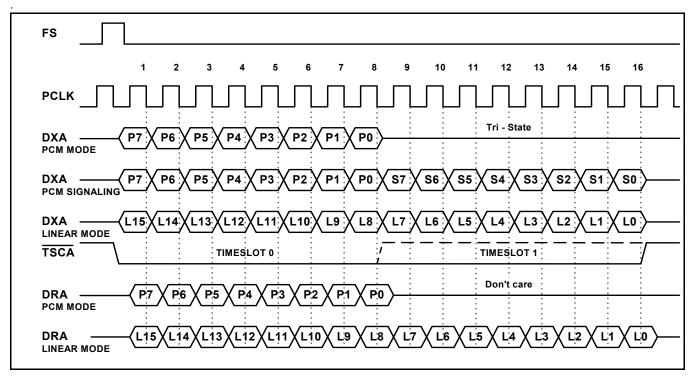

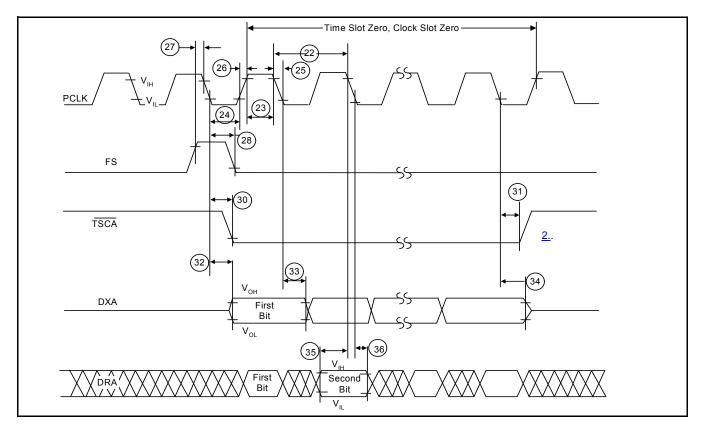

This is a synchronized serial mode of communication between the system and the Le88266/286 device. In PCM mode, data can be transmitted/received on a serial PCM highway. This highway uses FS and PCLK as reference.

Data is transmitted out of the DXA pin and received on the DRA pin. The Le88266/286 device transmits/receives single 8-bit time slot (A-law/µ-law) compressed voice data or 16-bit two's complement linear voice data, occupying two conventional time slots. The PCLK is a data clock supplied to the device that determines the rate at which the data is shifted in/out of the PCM ports. The Frame Sync (FS) pulse identifies the beginning of a transmit/receive frame and all time slots are referenced to it. For the Le88266/286 device, the frequency of the FS signal is 8 kHz. In wideband mode, two evenly spaced sets of time slots are exchanged in each frame. The user programs the first time slot and the second one is generated automatically and placed 125/2 µsec from the first time slot (the frame is assumed to have an even number of time slots). The PCLK frequency can be a number of fixed frequencies as defined by command <u>46/47h Write/Read Device Configuration Register</u>, on page 73. For each channel, voice data compression and type of coding is selected by the C/L (Compressed/Linear) and A/µ-law bits in command <u>60/61h</u> Write/Read Operating Functions, on page 80. The wideband mode is selected with the WBAND bit in command <u>4A/4Bh</u> Write/Read Channel Enable and Operating Mode Register, on page 74 and it affects both channels of the device.

#### Figure 3 - PCM highway structure

Datasheet

The Le88266/286 device command <u>44/45h Write/Read Transmit and Receive Clock Slot and Transmit Clock Edge</u>, on page 73 allows the time slots to be offset to eliminate any clock skew in the system. The Transmit Clock Slot and Receive Clock Slot fields are each three bits wide to offset the time slot assignment by 0 to 7 PCLK periods. The Transmit and Receive Clock Slot is a global command that is applied at the device level. Thus, for each channel, two time slots must be assigned — one for transmitting voice data and the other for receiving voice data. Figure 2 shows the PCM highway time slot structure.

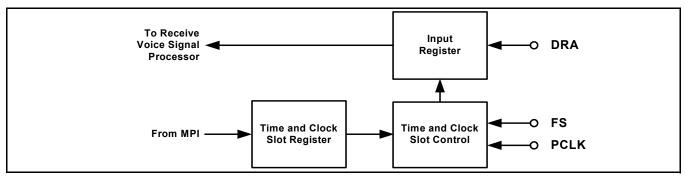

### 3.2.1 Transmit PCM Interface

The Transmit PCM interface receives a code from the voice signal processor (compressor), which may be either 8 bit compressed code (A-law/ $\mu$ -law) or a 16-bit two's complement linear code. The transmit PCM interface logic (Figure 4) controls the transmission of the data onto the PCM highway through the output port selection circuitry and the time and clock slot control block. The time slot control signal (TSCA) is low whenever PCM data is transmitted on the DXA pin. This signal can be used for arbitration when there are multiple Le88266/286 devices on the PCM bus. The data can be transmitted on either edge of the PCLK. The clock edge on which the data is transmitted is selected by the XE bit in the Transmit and Receive Clock Slot Register (Command 44h/45h).

Command <u>40/41h Write/Read Transmit Time Slot.</u> on page 72 allows the time slot of the selected channel to be programmed. The Transmit Time Slot Register allows up to 128 8-bit time slots (using a PCLK of 8.192 MHz) in each frame. The PCLK frequency can be a number of fixed frequencies as defined by command <u>46/47h Write/Read Device Configuration Register</u>, on page 73; this means that for compressed data the number of 8-bit time slots can vary between 24 and 128, while linear mode supports between 12 and 64 pairs of time slots. In wideband mode, the user must only program time slots in the lower half of the range. Note that linear mode requires two back-to-back time slots to transmit one voice channel. The data is transmitted in bytes with the most significant bit first. Figure 6 illustrates data flow on the PCM highway.

Figure 4 - Transmit PCM interface

# 3.2.2 Receive PCM Interface

The receive PCM interface logic (Figure 4) controls the reception of data bytes from the PCM highway. 8-bit compressed (A-law/µ-law) or 16-bit two's complement linear data is formatted and passed to the voice signal processor (expander).

Command <u>42/43h Write/Read Receive Time Slot</u>, on page 73 allows the time slot of the selected channel to be programmed. The Receive Time Slot Register is 7 bits wide and allows up to 128 8-bit time slots (using a PCLK of 8.192 MHz) in each frame. The PCLK frequency can be a number of fixed frequencies as defined by command <u>46/47h Write/Read Device Configuration Register</u>, on page 73; this means that for compressed data the number of 8-bit time slots can vary between 24 and 128, while linear mode

supports between 12 and 64 pairs of time slots. In wideband mode, the user must only program time slots in the lower half of the range. Note that linear mode requires two back-to-back time slots to transmit/receive one voice channel. The data is transmitted/received in bytes with the most significant bit first. Figure 6 illustrates data flow on the PCM highway.

#### 3.2.3 Signaling on the PCM Highway

Signaling information can be sent on the PCM output if A- or  $\mu$ -Law companding is selected and the SMODE bit in command <u>46/47h Write/Read Device Configuration Register</u>, on page 73 is set. In this case an extra time slot of signaling data is transmitted every frame immediately after the PCM voice data for the channel (see Figure 6) and is transmitted whether or not the voice channel is active. The signaling data is defined in Table 2.

|           | <b>S</b> 7 | S6                  | S5                 | S4               | <b>S</b> 3       | S2               | S1               | SO                |

|-----------|------------|---------------------|--------------------|------------------|------------------|------------------|------------------|-------------------|

| Channel 1 | CFAIL      | OCALMY <sub>1</sub> | TEMPA <sub>1</sub> | IO2 <sub>1</sub> | CAD <sub>1</sub> | CID <sub>1</sub> | GNK <sub>1</sub> | HOOK <sub>1</sub> |

| Channel 2 | DAT        | OCALMZ <sub>2</sub> | TEMPA <sub>2</sub> | 102 <sub>2</sub> | CAD <sub>2</sub> | CID <sub>2</sub> | GNK <sub>2</sub> | HOOK <sub>2</sub> |

#### Table 2 - PCM Highway Real Time Signaling Data Definition

Default settings, of consecutive time slots for Channel 2, cannot be used with PCM signaling. Also, the monitor A-->D converter output on the PCM highway is in linear mode which conflicts with PCM signaling.

Masking or unmasking of the interrupts in the interrupt mask register does not affect the real time signaling data. See command <u>4D/4Fh Read Signaling Register</u>, on page 75 for bit definitions

#### 3.3 MICROPROCESSOR INTERFACE (MPI)

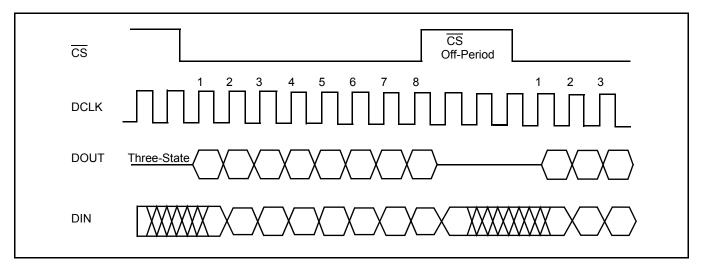

The microprocessor interface (MPI) block communicates with the external host microprocessor over a serial interface. It passes user control information to the other blocks, and it passes status information back to the external host.

The MPI physically consists of a serial data input (DIN) serial data output (DOUT), a data clock (DCLK), a chip select  $\overline{(CS)}$  and an interrupt signal (INT) (see Figure 7, *Microprocessor Interface Timing*, on page 10). The serial input consists of 8-bit commands that can be followed with additional bytes of input data, or can be followed by the Le88266/286 device sending out bytes of data. All data input and output is MSB (D7) first and LSB (D0) last. All data bytes are read or written one at a time, with CS going High

for at least a minimum off period (see <u>Microprocessor Interface Timing, on page 57</u>) before the next byte is read or written. Only a single channel should be enabled during read commands.

All commands that require additional input data to the device must have the input data as the next N words written into the device (for example, framed by the next N transitions of  $\overline{CS}$ ). All unused bits must be programmed to 0 to ensure compatibility with future parts. All commands that are followed by output data will cause the device to output data for the next N transitions of  $\overline{CS}$  going Low. The Le88266/286 device will not accept any commands until all the data has been shifted out. The output values of unused bits are not specified. Note that the Voice Channel Enable bits, EC1, EC2 in command <u>4A/4Bh Write/Read Channel Enable and</u> <u>Operating Mode Register</u>, on page 74 are used to control access to voice channel specific registers within the device.

#### Figure 7 - Microprocessor Interface Timing

An MPI cycle is defined by transitions of  $\overline{CS}$  and DCLK. If the  $\overline{CS}$  lines are held in the High state between accesses, the DCLK may run continuously with no change to the internal control data. Using this method, the same DCLK can be run to a number of Le88266/286 devices and the individual  $\overline{CS}$  lines will select the appropriate device to access. Between command sequences, DCLK can stay in the High state indefinitely with no loss of internal control information regardless of any transitions on the  $\overline{CS}$  lines. Between bytes of a multi byte read or write command sequence, DCLK can also stay in the High state indefinitely. DCLK can stay in the Low state indefinitely with no loss of internal control information, provided the  $\overline{CS}$  line remains at a High level. If the system controller has a single bi-directional serial data pin, the DOUT pin of the Le88266/286 device can be connected to its DIN pin.

If a low period of  $\overline{CS}$  contains less than 8 positive DCLK transitions, it is ignored. If it contains 8 to 15 positive transitions, only the last 8 transitions matter. If it contains 16 or more positive transitions, a hardware reset in the part occurs. If the chip is in the middle of a read sequence when  $\overline{CS}$  goes Low, data will be present at the DOUT pin even if DCLK has no activity.

### 3.3.1 Controlling Registers using read / modify / write.

In general, this coding method is not recommended for updating VoicePort device registers. The MPI interface is relatively slow speed, so operating on a local copy of this type of register data will provide higher performance.

In particular, some read / write registers are also accessed and modified by the internal state machine, especially on entering and exiting the Ringing States. This means that for these registers, a read modify write sequence can produce unpredictable results. The list of registers which must not be accessed using this technique is:

50/51h Write/Read Voice Path Gains, on page 77 56/57h Write/Read System State, on page 78 60/61h Write/Read Operating Functions. on page 80 70/71h Write/Read Operating Conditions, on page 82 A6/A7h Write/Read Converter Configuration, on page 88 CA/CBh Write/Read Digital Impedance Scaling Network (DISN), on page 91 E6/E7h Write/Read Switching Regulator Control, on page 100 EA/EBh Write/Read Caller Identification Number Parameters, on page 102

#### 3.3.2 Interrupt Servicing in MPI Mode

The Le88266/286 device has a well-defined interrupt structure. All the interrupts in the Le88266/286 device can be masked. Interrupts are caused only when a status bit is unmasked and the status bit is subsequently set or toggles (depending on the interrupt).

The Le88266/286 device generates interrupts in response to a number of line supervision events. When an interrupt is generated, its status is placed in the <u>4D/4Fh Read Signaling Register</u>, on page 75. Multiple interrupts can be reported in the signaling register. When the first interrupt occurs, the interrupt pin, INT, will be pulled Low to signal the external microprocessor that an interrupt has occurred. When the external microprocessor has serviced the interrupts by reading <u>4D/4Fh Read Signaling Register</u> and clearing the interrupt (Command 4Fh) or <u>CDh Read Transmit PCM/Test Data</u>, on page 91 (if ATI is set), the INT pin will go High. An interrupt is generated whenever a signaling register status bit changes (1 to 0 or 0 to 1) and the corresponding mask bit in <u>6C/6Dh</u> <u>Write/Read Interrupt Mask Register</u>, on page 82 is unmasked. Therefore, the software application is responsible for keeping track of the previous status and deciding the transition type (rising edge transition or falling edge transition). The interrupt pin drive mode can be programmed to be 3.3 V CMOS push/pull or open drain. Signaling status can also be polled without upsetting any pending interrupt status by using command 4Dh.

| CFAIL:               | PCM Clock (PCLK) or 8 kHz frame sync (FS) failure               |

|----------------------|-----------------------------------------------------------------|

| OCALMY:              | Switching regulator Y over voltage / current indication         |

| TEMPA <sub>1</sub> : | Thermal Fault has been detected                                 |

| IO2 <sub>1</sub> :   | Input 2 Status. The input value at IO2 <sub>1</sub> has changed |

| CAD <sub>1</sub> :   | Cadencer interrupt when programmed on period is completed       |

| CID <sub>1</sub> :   | Caller ID Buffer Ready                                          |

| GNK <sub>1</sub> :   | Ground-key status has changed                                   |

| HOOK <sub>1</sub> :  | Hook status has changed                                         |

| DAT:                 | Measurement data available in XDAT register                     |

| OCALMZ:              | Switching regulator Z over current indication                   |

| TEMPA <sub>2</sub> : | Thermal Fault has been detected                                 |

| IO2 <sub>2</sub> :   | Input 2 Status. The input value at IO2 <sub>2</sub> has changed |

| CAD <sub>2</sub> :   | Cadencer interrupt when programmed on period is completed       |

| CID <sub>2</sub> :   | Caller ID Buffer Ready                                          |

| GNK <sub>2</sub> :   | Ground-key status has changed                                   |

| HOOK <sub>2</sub> :  | Hook status has changed                                         |

The following status bits related to channel 1 and channel 2 can cause an interrupt to occur:

#### Table 1 - Definitions of Status Bits

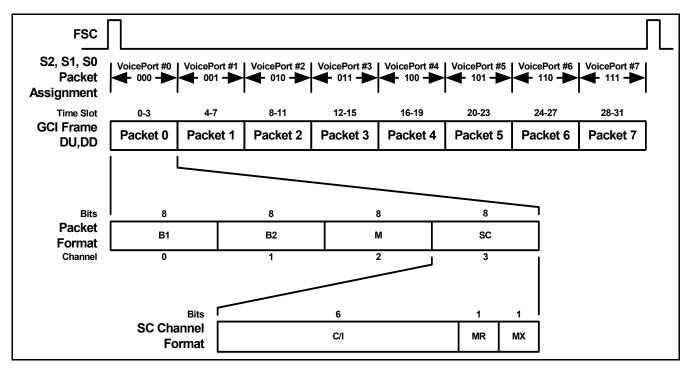

### 3.4 General Circuit Interface (GCI)

In GCI mode, this block carries both control and data on the same serial bus, replacing both MPI and PCM functionality. When the CS/PG pin is connected to DGND and DCLK/S0 is static (not toggling), GCI operation is selected. The Le88266/286 device conforms to the GCI standard where data for eight GCI packets are combined into one serial bit stream. A GCI packet contains the control and voice data for the two analog channels of the Le88266/286 device. The Le88266/286 device sends Data Upstream out of the DU pin and receives Data Downstream on the DD pin. Data clock rate and frame synchronization information goes to the Le88266/286 device on the DCL (Data Clock) and FSC (Frame Sync.) input pins, respectively.

The GCI block does not support the wideband (16kHz) sampling mode.

#### 3.4.1 GCI Format and Command Structure

The GCI interface provides communication of both control and voice data between the GCI highway and subscriber Voice Ports over a single pair of pins on the Le88266/286 device. A complete GCI frame is sent upstream on the DU pin and received downstream on the DD pin every 125  $\mu$ s. Each frame consists of eight 4-byte GCI packets that contain voice and control information for 8 pairs of channels. The overall structure of the GCI frame is shown in <u>Figure 8</u>. The four-time slot GCI packets contain the following:

- Two voice-data channels

- B1 provides compressed PCM data for Voice Channel 1

- B2 provides compressed PCM data for Voice Channel 2

- One Monitor (M) channel for reading and writing control data and coefficients to the chip set in combination with the MX and MR bits in the Signaling and Control channel

- One Signaling and Control (SC) channel containing a 6-bit Command/Indicate (C/I) field for real time control information and a two-bit field with Monitor Receive and Monitor Transmit (MR and MX) bits for handshaking functions linked to the Monitor channel. All principal signaling (real-time critical) information is carried on the C/I channel.

#### Figure 8 - Multiplexed GCI Time Slot Structure

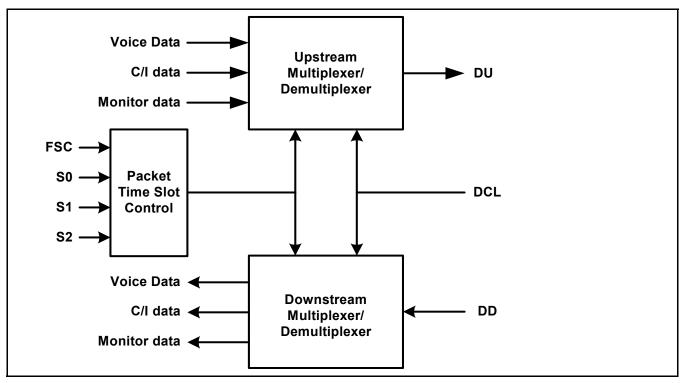

In the packet control block (shown in Figure 9), the Frame Sync (FSC) pulse identifies the beginning of the Transmit and Receive frames and all GCI packets are referenced to it. Voice (B1 and B2), C/I, and Monitor data are sent to the Upstream Multiplexer where they are combined and serially shifted out of the DU pin in the selected GCI packet time slots. The Downstream Demultiplexer uses the same packet control block information to demultiplex the incoming GCI packet into separate voice (B1 and B2), C/I, and Monitor channels.

| INT/S2 | DIN/S1 | DCLK/S0 | GCI Packet |

|--------|--------|---------|------------|

| DGND   | DGND   | DGND    | 0          |

| DGND   | DGND   | DVDD    | 1          |

| DGND   | DVDD   | DGND    | 2          |

| DGND   | DVDD   | DVDD    | 3          |

| DVDD   | DGND   | DGND    | 4          |

| DVDD   | DGND   | DVDD    | 5          |

| DVDD   | DVDD   | DGND    | 6          |

| DVDD   | DVDD   | DVDD    | 7          |

| Table 2 - GCI | Packet Assignmer | t Codes |

|---------------|------------------|---------|

|---------------|------------------|---------|

The external clock applied to the DCL pin must be either 2.048 MHz or 4.096 MHz. The Le88266/286 device determines the incoming clock frequency and adjusts internal timing automatically to accommodate single or double clock rates. Correct clock detection can be determined by reading the CSEL bits in <u>46/47h Write/Read Device Configuration Register</u>, on page 73. Upstream and Downstream Data is always transmitted at a 2.048 MHz data rate.

The Le88266/286 device supports access to all eight GCI packets (16 analog channels). The S0, S1 and S2 GCI Packet Assignment pins on the Le88266/286 device are encoded as shown in <u>Table 2</u>.

Figure 9 - GCI Interface and Packet Time Slot Selection

# 3.4.2 Signaling and Control (SC)

The downstream and upstream SC channels are continuously sending state control and loop supervision data every frame to and from the Le88266/286 device in the C/I field. This allows the upstream processor to have immediate access to the VoicePort line status. The MR and MX bits are used for handshaking during data exchange on the monitor channel.

The format of the downstream control (C) field is shown in <u>Table 3</u>. The Le88266/286 device receives the most significant bit first.

| Channel | D7 | D6    | D5 | D4      | D3         | D2 | D1 | D0 |

|---------|----|-------|----|---------|------------|----|----|----|

| 1       | А  | POLNR |    | System_ | State[3:0] |    | MR | MX |

| A:                                   | <ul> <li>Channel address bit.</li> <li>0: Select Channel 1 as the downstream data destination.</li> <li>1: Select Channel 2 as the downstream data destination.</li> </ul> |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POLNR:                               | VoicePort Feed Polarity<br>0: Normal Polarity feed - TipD more positive than RingD<br>1: Reverse Polarity feed - RingD more positive than TipD                             |

| SS3 <sub>i</sub> -SS0 <sub>i</sub> : | System State. Valid system states are listed here. All other codes are reserved.<br>0000: Disconnect, ACT = 0<br>0001: Tip Open, ACT = 0<br>0010: Ring Open, ACT = 0       |

0011: Active Low Battery, ACT = 1

0100: Idle, ACT = 0

0101: Longitudinal Test, ACT = 1

0110: Metallic Test, ACT = 1

0111: Balanced Ringing, ACT = 1

1000: Low Gain, ACT = 1

1010: Unbalanced Ringing, ACT = 1

1011: Active Mid Battery, ACT = 1

1111: Shutdown, ACT = 0

See 56/57h Write/Read System State, on page 78 for more description of the system states.

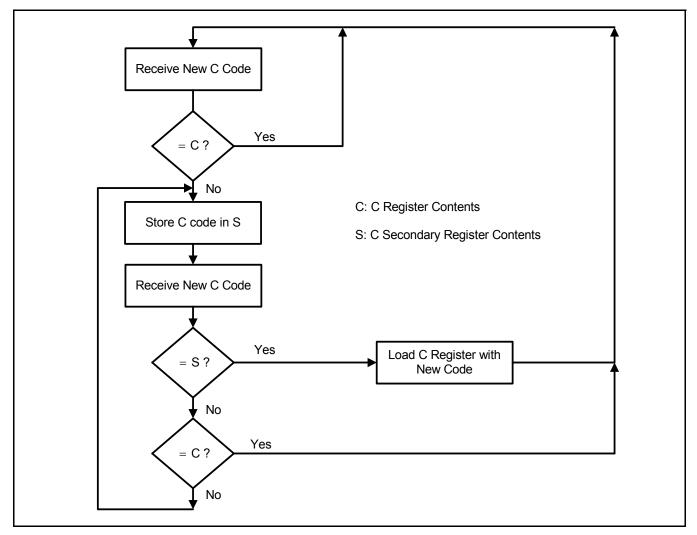

Figure 10 shows a flow chart describing the transmission protocol for the downstream channel, which provides a high level of security for the C field data exchange. Whenever the received pattern of C bits 6 through 1 is different from the pattern currently in the C input register, the new pattern is loaded into a secondary C register, and a latch is set. When the next pattern is received (in the following frame) while the latch is set, the following rules apply:

#### Figure 10 - Security Procedure For C Downstream Byte

- If the received pattern corresponds to the pattern in the secondary register, the new pattern is loaded into the C register, and the latch is reset.

- If the received pattern is different from the pattern in the secondary register and different from the pattern currently in the C register, the newly received pattern is loaded into the secondary C register, and the latch remains set.

• If the received pattern is the same as the pattern currently in the C register, the C register is unchanged, and the latch is reset.

The format of the upstream indication (I) field is shown in <u>Table 4</u>. The Le88266/286 device transmits the I field most significant bit first each frame.I

| D7                  | D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D5                                                          | D4                                                | D3                                                                                                                  | D2                                            | D1                          | D0             |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|----------------|--|

| SLCX2               | GNK <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HOOK <sub>2</sub>                                           | SLCX <sub>1</sub>                                 | GNK <sub>1</sub>                                                                                                    | HOOK <sub>1</sub>                             | MR                          | MX             |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Та                                                          | ble 4 - Upstre                                    | am SC Chan                                                                                                          | nel                                           |                             |                |  |

| SLCX2               | 1: One<br>0: None<br>This<br>the s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | or more of the u<br>e of the unmask<br>is a logic "or" of   | ed bits in the Sig<br>TEMPA <sub>2</sub> , DAT, I | g Register<br>h the Signaling R<br>gnaling Register<br>IO2 <sub>2</sub> , CAD <sub>2</sub> , GN<br>he 4F read and d | has toggled.<br>$K_2$ , HOOK <sub>2</sub> and | OCALM <sub>2</sub> . This I |                |  |

| GNK <sub>2</sub> :  | <ul> <li>Indication if a ground connection is taking place</li> <li>1: Ground connection</li> <li>0: No ground connection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |                                                   |                                                                                                                     |                                               |                             |                |  |

| HOOK <sub>2</sub> : | 1: Subs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |                                                   |                                                                                                                     |                                               |                             |                |  |

| SLCX <sub>1</sub>   | <ul> <li>Summary output of the Channel 1 Signaling Register</li> <li>1: One or more of the unmasked bits in the Signaling Register has toggled.</li> <li>0: None of the unmasked bits in the Signaling Register has toggled.<br/>This is a logic "or" of TEMPA<sub>1</sub>, CFAIL, IO2<sub>1</sub>, CAD<sub>1</sub>, GNK<sub>1</sub>, HOOK<sub>1</sub> and OCALM<sub>1</sub>. This bit is reset when the signalling register is read using the 4F read and clear interrupt from <u>4D/4Fh Read Signalin</u> <u>Register</u>, on page 75.</li> </ul> |                                                             |                                                   |                                                                                                                     |                                               |                             |                |  |

| GNK <sub>1</sub> :  | Indication if a ground connection is taking place 1: Ground connection 0: No ground connection                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |                                                   |                                                                                                                     |                                               |                             |                |  |

| HOOK <sub>1</sub> : | 1: Subs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | f loop condition<br>scriber is off-hoo<br>scriber is on-hoo |                                                   |                                                                                                                     |                                               |                             |                |  |

| Data from the lo    | pop supervision o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | circuitry (with ap                                          | plicable deboun                                   | cing) is latched t                                                                                                  | by a derivative o                             | f Frame Sync ev             | ery 125 µs. Th |  |

Data from the loop supervision circuitry (with applicable debouncing) is latched by a derivative of Frame Sync every 125 µs. This real-time latched data is transmitted upstream in the I field every frame (125 µs). Note that it is not the data in the Signaling Register. Hence masking or unmasking of the HOOK and GNK interrupts in the interrupt mask register will not affect the HOOK and GNK data in the SC channel.

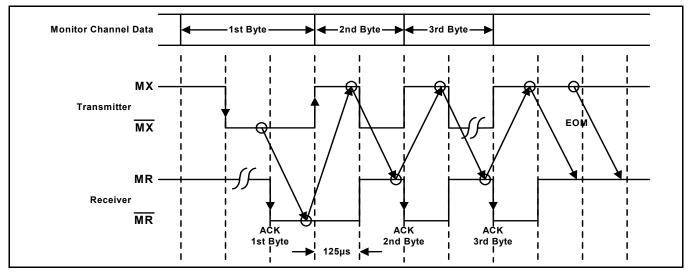

### 3.4.3 Monitor Channel Protocol

The Monitor (M) channel (see <u>Figure 11</u>) loads the Le88266/286 device internal registers, reads the status of the device and the contents of the internal registers, and provides supplementary signaling. Information is transferred on the Monitor Channel using the MR and MX bits of the third (SC) channel to provide a reliable method of data exchange between the higher level processor and the Le88266/286 device (see <u>Figure 11</u>).

The monitor channel is the third channel in the 4-channel packet sent and received every 125 µs. A monitor command consists of one address byte and one or more command bytes followed by additional bytes of input data. The command can be followed by the Le88266/286 device sending data bytes upstream via the DU pin.

Figure 12 - Monitor Transmitter Mode Diagram

- An inactive (High) MX and MR pair bit for two or more consecutive frames shows an idle state on the monitor channel and the end of message (EOM).

- <u>Figure 11</u> shows that transmission is initiated by the transition of the transmitter MX bit from the inactive to the active state. The transition coincides with the beginning of the first byte sent on the monitor channel. The receiver acknowledges the first byte by setting MR bit to active and keeping it active for at least one more frame.

- The same data must be received in two consecutive frames in order to be accepted by the receiver.

- The same byte is sent in each of the succeeding frames until either a new byte is transmitted, the message ends, or an abort occurs. Any abort command resets any pending commands in the Le88266/286 device. The device remains in the previous configuration and is ready to receive a new command.

- Any false MX or MR bit received by the receiver or transmitter leads to a request-for-abort or an abort, respectively.

- To obtain maximum data transfer speed, the transmitter anticipates the falling edge of the receiver's acknowledgment as shown in Figure 11.

Figure 12 and Figure 13 are state diagrams that define the operation of the monitor transmitter and receiver sections in the Le88266/286 device.

Figure 13 - Monitor Receiver Mode Diagram

#### 3.4.4 **Programming with the Monitor Channel**

The Le88266/286 device uses the monitor channel for the transfer of status or mode information to and from higher level processors. The higher level processor is synchronized to the Le88266/286 device using the time slot straps S0, S1 and S2.

The messages transmitted in the monitor channel have different structures. The first byte of monitor channel data in the GCI format indicates the address of the device either sending or receiving the data. All monitor channel messages to/from the Le88266/286 device begin with this address byte:

| Bit     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

| Address | 1 | 0 | 0 | А | В | 0 | 0 | С |

| ٨       |   |   |   |   |   |   |   |   |

| A |    |                                                                |

|---|----|----------------------------------------------------------------|

|   | 0: | Channel 1 is the source (upstream) or destination (downstream) |

|   | 1: | Channel 2 is the source (upstream) or destination (downstream) |

| В |    |                                                                |

| D | 0: | Data destination determined by A                               |

|   | 0. | Data destination determined by A                               |

|   | 1: | Both Channel 1 and 2 receive the data                          |

| С |    |                                                                |

| Ũ | 0: | Address for channel identification command                     |

|   | 0. |                                                                |

|   | 1: | Address for all other commands                                 |

|   |    |                                                                |

Transmission in the GCI monitor channel starts with an address byte followed by a command byte. If the command byte specifies a write, from 1 to 14 additional data bytes can follow (see <u>Table 5</u>). If the command byte specifies a read, additional data bytes can follow. The Le88266/286 device responds to the read command by sending out the original address byte and up to 14 bytes upstream that contain the information requested by the upstream controller. Generic byte transmission sequence over the GCI monitor channel is shown in <u>Table 5</u>.

| GCI Monitor Channel |              |  |  |  |  |  |

|---------------------|--------------|--|--|--|--|--|

| Downstream          | Upstream     |  |  |  |  |  |

| ADDRESS             |              |  |  |  |  |  |

| Control byte, write |              |  |  |  |  |  |

| Data byte 1*        |              |  |  |  |  |  |

| •                   |              |  |  |  |  |  |

| Data byte m*        |              |  |  |  |  |  |

| ADDRESS             |              |  |  |  |  |  |

| Control byte, read  |              |  |  |  |  |  |

|                     | Data byte 1  |  |  |  |  |  |

|                     | •            |  |  |  |  |  |

|                     | Data Byte n* |  |  |  |  |  |

| m ≤ 14              | n ≤ 14       |  |  |  |  |  |

#### Table 5 - Monitor Byte Transmission Sequence

#### Notes:

\* May or may not be present

#### 3.4.5 Channel Identification Command (CIC)

When the monitor channel address byte is 80H or 90H, a command of 00H is interpreted by the Le88266/286 device as a twobyte Channel Identification Command (CIC).

The format for this command is shown next:

|              | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|--------------|----------------|----------------|-------|----------------|-------|----------------|----------------|----------------|

| Address Byte | 1              | 0              | 0     | А              | 0     | 0              | 0              | 0              |

| Command Byte | 0              | 0              | 0     | 0              | 0     | 0              | 0              | 0              |

А

0: Channel 1 is the destination 1:

Channel 2 is the destination

Immediately after the last bit of the CIC command is received, the Le88266/286 device responds with the two-byte channel ID code indicating an analog transceiver device type in bits 6 and 7 of byte 2, with the following configuration options:

|        | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | D <sub>3</sub> | $D_2$ | D <sub>1</sub> | D <sub>0</sub> |

|--------|----------------|----------------|-------|----------------|----------------|-------|----------------|----------------|

| Byte 1 | 1              | 0              | 0     | А              | PCN5           | PCN4  | PCN3           | PCN2           |

| Byte 2 | 1              | 0              | 0     | 0              | 0              | 1     | 1              | 1              |

А

Channel 1 is the destination

Channel 2 is the destination

PCN[5:2] Product Code Number Ch Le88266 device Dh

0:

1:

Le88286 device

When the Le88266/286 device has completed transmission of the channel ID information, it sends an EOM (MX = 1 for two successive frames) on the upstream C/I channel. The Le88266/286 device also expects an EOM to be received on the downstream C/I channel before any further message sequences are received.

#### General Structure of Other Commands 3.4.6

When the monitor channel address byte is 81h, 89h, 91h, or 99h, the command byte is interpreted by the Le88266/286 device as either a Transfer Operation (TOP), Status Operation (SOP), or a Coefficient Operation (COP).

|              | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | $D_3$ | $D_2$ | D <sub>1</sub> | D <sub>0</sub> |

|--------------|----------------|----------------|-------|----------------|-------|-------|----------------|----------------|

| Address Byte | 1              | 0              | 0     | А              | В     | 0     | 0              | 1              |

A

Channel 1 is the source (upstream) or destination (downstream) 0:

1: Channel 2 is the source (upstream) or destination (downstream)

В

- 0: Data destination determined by A 1:

- Both Channel 1 and 2 receive the data

Commands are sent to the Le88266/286 device to:

- Read the status of the system without changing its operation

- Write/read the Le88266/286 device operating mode

- Write/read filter coefficients

#### 3.5 Internal Configuration Registers

The Le88266/286 device contains a block of Internal Configuration Registers (ICR). For correct operation, some of the bits in these registers must be written during operation. The general structure, command codes and operation of these registers is described on page 103.

Access to these registers is required to provide smooth transitions from disconnect to idle or active states (page 26), enable line voltage sensing in the Disconnect state (page 26), correctly configure the DC feed (page 27) and to control the test load switch on the Le88286DLC (page 32). Details of these settings are provided in the corresponding sections.

#### 3.6 Input / Output Block

This block controls general-purpose pins that can be configured by the user as inputs, outputs, or relay drivers. CMOS-compatible I/O pins (I/O1 and I/O2) are provided per channel. I/O1 can act either as a standard digital input or as a high current CMOS output capable of directly driving a 150-mW 3-V relay with an external catch diode. I/O2 is a standard digital I/O pin that can also generate interrupts when configured as an input. The pins are accessed using Command <u>52/53h Write/Read Input/Output Data Register</u>. on page <u>77</u>. The direction of the I/O pins (input or output) is specified by programming <u>54/55h Write/Read Input/Output Direction</u> <u>Register</u>, on page <u>78</u>.

#### 3.7 Voice Signal Processors

This block performs digital signal processing for the transmission and reception of voice. It includes G.711 compression/decompression, impedance matching, filtering, gain control, DTMF generation and general-purpose tone generators for each channel. Additionally caller ID FSK generation and metering generation are provided.

This block performs the codec and filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals.

The user-programmable filters perform the following functions:

- Sets the receive and transmit gain

- Performs the transhybrid balancing function

- Permits adjustment of the two-wire termination impedance

- Provides frequency attenuation adjustment (equalization) of the receive and transmit paths

All programmable digital filter coefficients can be calculated using Microsemi's WinSLAC software. The PCM codes can be either 16-bit linear two's-complement or 8-bit companded A-law or µ-law.

#### 3.7.1 Overview of Digital Filters

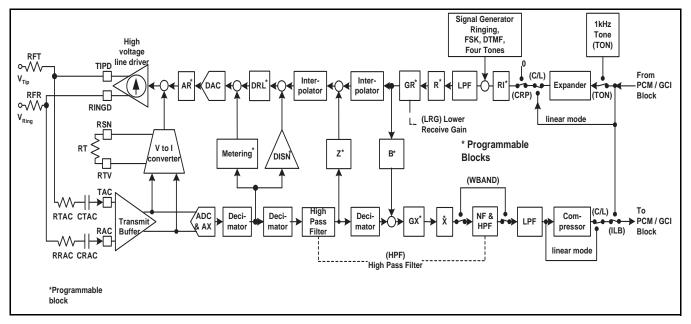

Several of the blocks in the signal processing section are user programmable. These allow the user to optimize the performance of the Le88266/286 device for the system. Figure 14 shows the Le88266/286 device signal processing for one channel and indicates the programmable blocks and how this section interfaces with the high voltage line driver and line sensing circuits.

The advantages of digital filters are:

- High reliability

- No drift with time or temperature

- Unit-to-unit repeatability

- Superior transmission performance

- Flexibility

- Maximum bandwidth for V.90 modems

Figure 14 - Voice Signal Processing Block Diagram

## 3.7.2 Analog Impedance Synthesis

The analog impedance synthesis loop is comprised of the high voltage line driver, the AC sense path components, the transmit amplifier, and a voltage to current converter. Nominally, this converter uses an external resistor,  $R_T$ .  $R_T$  synthesizes the nominal impedance in the analog domain.

### 3.7.3 Two-Wire Impedance Matching

Two feedback paths in the voice signal processor modify the two-wire input impedance by providing a programmable feedback path from the AC sense path to the line driver outputs.

The DISN path is comprised of the voice A/D and its first stage of decimation, a Digital Impedance Scaling Network (DISN), and the voice DAC. The DISN synthesizes a portion of the ac impedance which appears in parallel with R<sub>T</sub> and is used to modify the impedance set by the external analog network. The DISN is controlled by an 8-bit word. <u>See CA/CBh Write/Read Digital Impedance Scaling Network (DISN)</u>, on page 91.

The Z filter is a programmable digital filter providing an additional path and programming flexibility over the DISN in modifying the transfer function of the synthesis loop. Together, the RT, DISN, and Z-Filter enable the user to synthesize virtually all required telephony device input impedances. See 98/99h Write/Read Z Filter FIR Coefficients, on page 87. and 9A/9Bh Write/Read Z Filter IIR Coefficients, on page 87.

### 3.7.4 Frequency Response Correction and Equalization

The voice signal processor contains programmable filters in the receive (R) and transmit (X) directions that may be programmed for line equalization and to correct any attenuation distortion caused by the Z filter. <u>See 8A/8Bh Write/Read R Filter Coefficients</u>, on page 86. and <u>88/89h Write/Read X Filter Coefficients</u>, on page 85.

# 3.7.5 Transhybrid Balancing

The voice signal processor's programmable B filter is used to adjust transhybrid balance. The filter has a single pole IIR section (BIIR) and an eight-tap FIR section (BFIR), both operating at 16 kHz. See 86/87h Write/Read B Filter FIR Coefficients, on page 84. and <u>96/97h Write/Read B Filter IIR Coefficients</u>, on page 87.

#### 3.7.6 Gain Adjustment

The transmit path has two programmable gain blocks. Gain block AX is an analog gain of 0 dB or 6.02 dB (unity gain or gain of 2.0), located immediately before the A/D converter. See 50/51h Write/Read Voice Path Gains, on page 77. GX is a digital gain block that is programmable from 0 dB to +12 dB, with a worst-case step size of 0.1 dB for gain settings below +10 dB, and a worst-case step size of 0.3 dB for gain settings above +10 dB. The filters provide a net gain in the range of 0 dB to 18 dB. See 80/81h Write/Read GX Filter Coefficients, on page 83.

The receive voice path has three programmable gain blocks. GR is a digital loss block that is programmable from 0 dB to 12 dB, with a worst-case step size of 0.1 dB. <u>See 82/83h Write/Read GR Filter Coefficients</u>, on page 83. DRL is a digital loss block of 0 dB or 6.02 dB. AR is an analog gain of 0 dB or 6.02 dB (unity gain or gain of 2) or a loss of 6.02 dB (gain of 0.5), located immediately after the D/A converter. <u>See 50/51h Write/Read Voice Path Gains</u>, on page 77. This provides a net loss in the range of 0 dB to 18 dB. AR is limited to 0 or -6.02 dB when DRL is 0 dB, and +6.02 dB or 0 dB if DRL is 6.02 d of loss.

Metering is affected by the AR gain block. To achieve the specified levels, the DRL loss is enabled, and AR gain is applied whenever metering is used.

#### 3.7.7 Transmit Signal Processing

In the transmit path (A/D), the AC Tip - Ring analog input signal is sensed by the TAC and RAC pins, buffered, amplified by the analog AX gain and sampled by the A/D converter, filtered, companded (for A-law or µ-law), and made available to the PCM or GCI blocks. Linear mode is only available in the PCM/MPI mode. If linear format is selected, the 16-bit data will be transmitted in two consecutive time slots starting at the programmed time slot. The B, X, and GX digital filter blocks are user-programmable digital filter sections with coefficients stored in the coefficient RAM. The B, X, and GX filters can also be operated from an alternate set of default coefficients stored in ROM. See 60/61h Write/Read Operating Functions, on page 80.

The first high-pass filter is for DC rejection, and the second high pass and notch filters reject low frequencies such as 50 Hz or 60 Hz. In wideband mode, the second high pass and notch filters are bypassed as shown in Figure 14, Voice Signal Processing Block Diagram, on page 21. All of these filters may be disabled with the DHP bit in command <u>70/71h Write/Read Operating</u> Conditions, on page 82.

#### 3.7.8 Receive Signal Processing

In the receive path (D/A), the digital signal is expanded (for A-law or µ-law), filtered, interpolated, converted to analog, and driven onto the TIPD and RINGD pins by the high voltage line driver. The DRL, DISN, Z, R, and GR blocks are user-programmable filter sections with their coefficients stored in the coefficient RAM, while AR is an analog amplifier. The Z, R, GR and RI filters can also be operated from an alternate set of default coefficients stored in ROM. <u>See 60/61h Write/Read Operating Functions</u>, on page 80.

#### 3.7.9 Programmable Filters

The filter coefficients that the user sends to the voice ALU are in a form known as Canonical Signed Digits (CSDs). The coefficients take the following general form:

$$h = I0 + C1 \bullet 2^{-m1} \bullet (1 + C2 \bullet 2^{-m2} \bullet (1 + I3 \bullet C3 \bullet 2^{-m3} \bullet (1 + I4 \bullet C4 \bullet 2^{-m4})))$$

where:

Cj = -1 or +1 (represented as 1 or 0 in user programming)

mj = 0, 1, 2,... or 7 (user programming)

I0 = 1 for GX; I0 = 0 for all other coefficients

I4 = 1 for 4 • CSD coefficients; I4 = 0 otherwise

I3 = 1 for 3 and 4 CSD coefficients; I3 = 0 for 2 CSD coefficients

#### 3.7.10 Calculating Coefficients with WinSLAC<sup>™</sup> Software

The WinSLAC<sup>™</sup> software is a program that models the Le88266/286 device, the line conditions, and the external VoicePort components to calculate the coefficients of the programmable filters and predict important transmission performance plots.